#### AN ABSTRACT OF THE DISSERTATION OF

Robert Pawlowski for the degree of <u>Doctor of Philosophy</u> in <u>Electrical and</u> Computer Engineering presented on July 14 2014.

Title: Measurement and Analysis of Soft Error Vulnerability of Low-Voltage

Logic and Memory Circuits

| Abstract approved: |  |

|--------------------|--|

|                    |  |

#### Patrick Yin Chiang

Scaling the supply voltage into the sub/near-threshold domain is one of the most effective methods for improving the energy efficiency of next-generation electronic microsystems. Unfortunately, the relationship between low-voltage operation and radiation-induced soft error rate is not widely known, as little research has been previously performed and reported for soft-error susceptibility of on-chip memory and logic at very low supply voltages. This information is critical for low-voltage circuit designers, as many applications that would benefit from the energy efficiency of sub/near-threshold also require high reliability. This work first details the design and implementation of a portable soft error reference platform, specifically targeting very low-voltage operation. The circuit-level details of a TSMC 65nm test-chip design are given, along with an analysis of data from experiments performed at Los Alamos Neutron Science Center (LANSCE) and the OSU radi-

ation center. Once this soft-error rate is known, error resiliency techniques must be utilized for increased processor reliability. The design and implementation of an error-resilient, near-threshold SIMD processor in an IBM 45nm SOI process will also be covered. This prototype demonstrates both increased reliability and improved throughput over a conventional SIMD pipeline while operating in near-threshold.

©Copyright by Robert Pawlowski July 14 2014 All Rights Reserved

# Measurement and Analysis of Soft Error Vulnerability of Low-Voltage Logic and Memory Circuits

by

Robert Pawlowski

#### A DISSERTATION

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented July 14 2014 Commencement June 2015

| Doctor of Philosophy dissertation of Robert Pawlowski presented on July 14 2014.                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APPROVED:                                                                                                                                                                                                 |

| Major Professor, representing Electrical and Computer Engineering                                                                                                                                         |

| Director of the School of Electrical Engineering and Computer Science                                                                                                                                     |

| Dean of the Graduate School                                                                                                                                                                               |

|                                                                                                                                                                                                           |

|                                                                                                                                                                                                           |

| I understand that my dissertation will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my dissertation to any reader upon request. |

| Robert Pawlowski, Author                                                                                                                                                                                  |

#### ACKNOWLEDGEMENTS

I would like to first thank my major advisor, Professor Patrick Chiang. Your guidance and discussions on all topics over these past 5 years has been greatly appreciated. You have helped me to greatly improve my confidence and my skills as an engineer.

To my committee members, thank you so much for your time and valuable feedback. Thank you to Dr. Steve Reese and Dr. Ram Krishnamurthy for serving on my committee throughout the duration of my work. Also, thank you to Dr. Un-Ku Moon and Dr. Karl Schilke for making time to join my committee for the final defense. And to Dr. Karti Mayaram and Dr. Abi Farsoni, thank you very much for serving on my committee for the qualifying and preliminary exams.

Thank you to the Intel collaborators on the soft error project. Shekhar Borkar, Vivek De, and Jim Tschanz, your input was invaluable to the success of the project. Also to Heather Quinn and Tom Fairbanks from Los Alamos National Laboratory, as well as Scott Menn and Jim Darrough from the OSU radiation center: thank you so much for your help and expertise with running the radiation experiments. On the Synctium project, thanks to Dr. Evgeni Krimer and Prof. Mattan Erez from University of Texas at Austin for working with us!

To the members of the OSU VLSI research group: Joseph Crop, Jacob Postman, Neil Glover, Kang-min Hu, Hao Li, Rui Bai, Jiao Cheng, and Vahid Behravan. Thank you for the time spent discussing ideas, working on tapeouts, and writing papers together. I can't think of a better group people to work with.

Also, to all of the friends I have made throughout graduate school, thank you for all of the time spent playing soccer, going to conferences, going out for food/drinks, etc. You have all made it an experience I will always cherish.

Thank you to my fiancee, Laurel Jones, for putting up with my late nights and times of high stress. I can't imagine making it through the past 5 years without you, and I'm excited for the next step in our lives together.

Cynthia, Bryan, and Danny. Thanks for being great siblings. You all have been supportive and fun, and I love you guys very much. Thank you to all of my grandparents for your support, as well.

Finally, to my parents: Thank you for your love and help throughout my entire life. You both have believed in me and provided words of guidance for me whenever I've needed it. This work would not have been possible without your support!

# CONTRIBUTION OF AUTHORS

Dr. Joseph Crop was instrumental to the success of the work presented in Chapter 2.

Dr. Evgeni Krimer, Dr. Nariman Moezzi-Madani, and Prof. Mattan Erez were involved in the development of the work presented in Chapter 3.

# TABLE OF CONTENTS

|   |     | :                                                                                                         | Page |

|---|-----|-----------------------------------------------------------------------------------------------------------|------|

| 1 | Int | oduction                                                                                                  | 1    |

|   | 1.1 | Near-threhsold error sources and resiliency techniques                                                    | 1    |

|   | 1.2 | Radiation-Induced Soft Errors in Near-threshold                                                           | 2    |

|   | 1.3 | Synctium-I: A 10-Lane, Near-Threshold SIMD Processor Incorporating Timing Variation Resiliency Techniques | 3    |

| 2 | Ra  | liation-Induced Soft Errors in Near-threshold                                                             | 5    |

|   | 2.1 | $Introduction \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                           | 5    |

|   | 2.2 | Background                                                                                                | 8    |

|   |     | 2.2.1 Charge Collection and Upset Mechanism                                                               | 8    |

|   |     | 2.2.2 Critical Charge                                                                                     |      |

|   |     | 2.2.3 Soft Error vs. VDD Simulations                                                                      |      |

|   |     | 2.2.4 Sources of radiation                                                                                |      |

|   |     | 2.2.5 Related Work                                                                                        |      |

|   | 2.3 | Motivation                                                                                                | 25   |

|   | 2.4 | Chip Implementation                                                                                       |      |

|   |     | 2.4.1 SRAM                                                                                                |      |

|   |     | 2.4.2 Digital Logic                                                                                       |      |

|   |     | 2.4.3 Physical Implementation                                                                             |      |

|   | 2.5 | System Implementation                                                                                     |      |

|   |     | 2.5.1 Master Board                                                                                        |      |

|   |     | 2.5.2 Sub Board                                                                                           | 48   |

|   | 2.6 | Top Level Setup                                                                                           |      |

|   |     | 2.6.1 In-beam Test Setup                                                                                  |      |

|   |     | 2.6.2 Alpha test setup                                                                                    |      |

|   |     | 2.6.3 FPGA software architecture                                                                          |      |

|   |     | 2.6.4 Test sequence                                                                                       | 56   |

|   | 2.7 | Measurement Results                                                                                       |      |

|   |     | 2.7.1 SRAM                                                                                                |      |

|   |     | 2.7.2 Digital Logic                                                                                       | 65   |

|   | 2.8 | Design analysis                                                                                           | 74   |

# TABLE OF CONTENTS (Continued)

|   |       |                |                                                              | Page         |

|---|-------|----------------|--------------------------------------------------------------|--------------|

| 3 | Sy    | nctium-I       | : A 10-Lane, Near-Threshold SIMD Processor Incorporating Tin | n-           |

|   | ing   | y Variatio     | on Resiliency Techniques                                     | 79           |

|   | 3.1   | 3.1.1<br>3.1.2 | Ction                                                        | . 80<br>. 83 |

|   | 3.2   | 3.2.1          | n Resiliency Methods                                         | . 95         |

|   | 3.3   |                | plementation                                                 |              |

|   | 3.4   |                | Implementation                                               |              |

|   | 3.5   |                | ement Results                                                |              |

| 4 | Со    | nclusion       |                                                              | 121          |

| В | iblio | graphy         |                                                              | 122          |

# LIST OF FIGURES

| Fig | gure | $\frac{P_{i}}{r_{i}}$                                                                                      | age |

|-----|------|------------------------------------------------------------------------------------------------------------|-----|

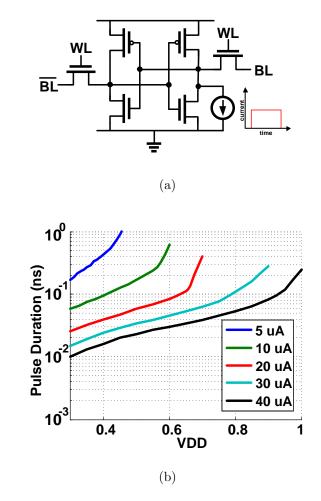

|     | 2.1  | Pulse duration vs. VDD simulations for 5 current magnitudes on a: (a) 6T bitcell; (b) Chain of 8 inverters | 14  |

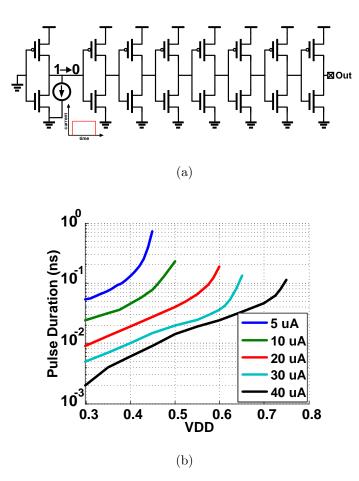

|     | 2.2  | Pulse duration vs. VDD simulations for 5 current magnitudes on a: (a) 6T bitcell; (b) Chain of 8 inverters | 16  |

|     | 2.3  | Combinational logic test circuit implemented in [29]                                                       | 24  |

|     | 2.4  | Combinational logic test circuit implemented in [30]                                                       | 25  |

|     | 2.5  | Top-level SRAM architecture                                                                                | 30  |

|     | 2.6  | Memory bit cell custom layouts: (a) 6T; (b) 8T                                                             | 32  |

|     | 2.7  | Top-level digital logic architecture                                                                       | 34  |

|     | 2.8  | Radiation hardened Dual-Interlocked Storage Cell (DICE) [38] used in the 5-bit counters                    | 36  |

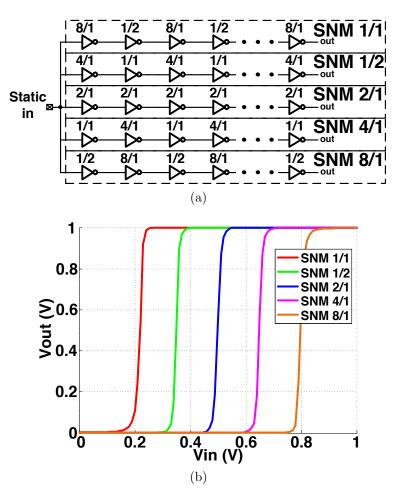

|     | 2.9  | Static noise margin: (a) test chains; (b) simulated switching thresholds                                   | 39  |

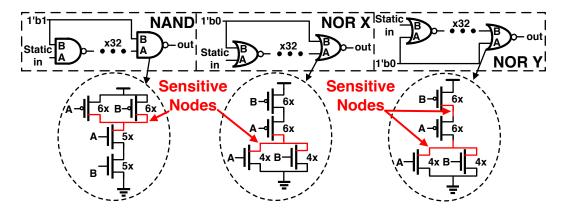

|     | 2.10 | NAND and NOR test chains and radiation sensitive nodes                                                     | 41  |

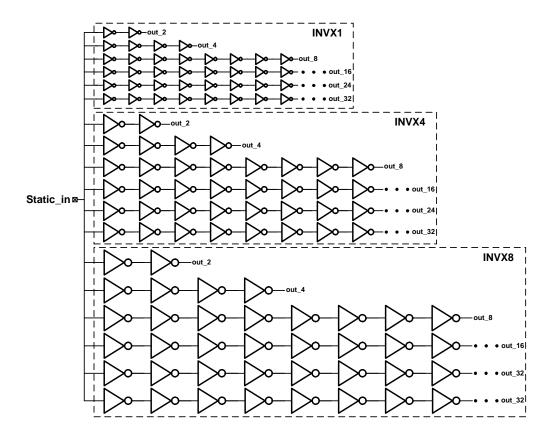

|     | 2.11 | Inverter chain size/legnth test schematic                                                                  | 43  |

|     | 2.12 | NAND and NOR test chains and radiation sensitive nodes                                                     | 45  |

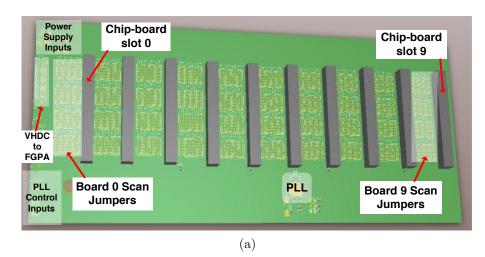

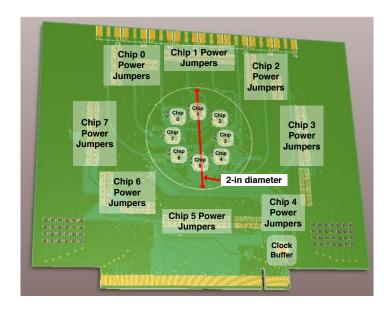

|     | 2.13 | Master board: (a) image; (b) block diagram, showing the scan signal routing jumpers                        | 47  |

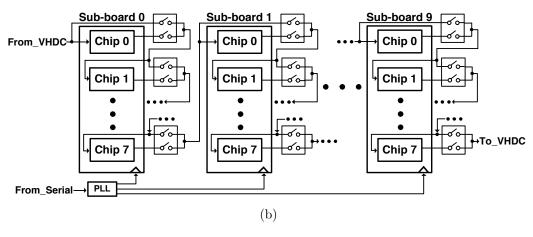

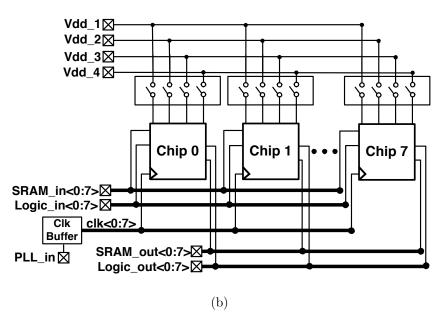

|     | 2.14 | Sub board: (a) image; (b) block diagram                                                                    | 49  |

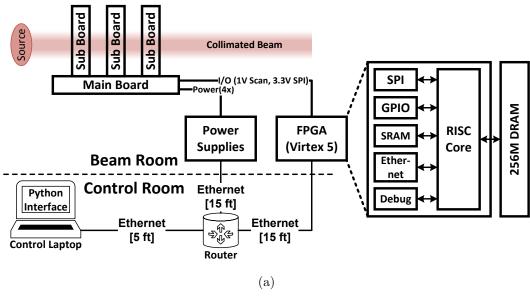

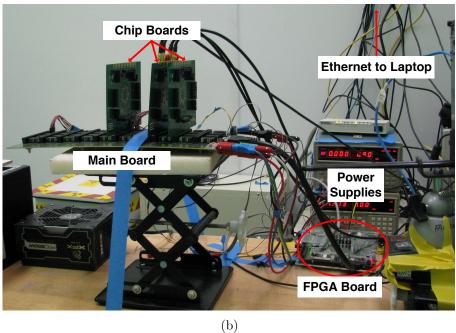

|     | 2.15 | Beam room test setup: (a) block diagram; (b) image                                                         | 52  |

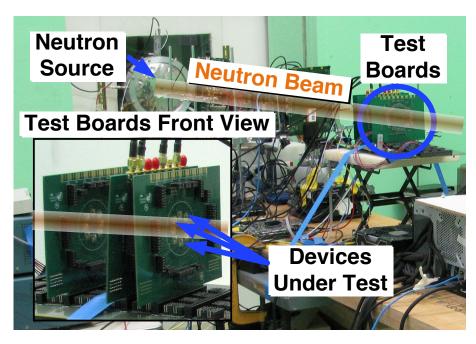

|     | 2.16 | Neutron beam test front view                                                                               | 53  |

|     | 2.17 | Alpha experiment setup                                                                                     | 55  |

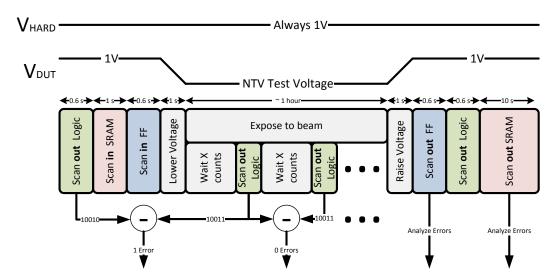

|     | 2.18 | Neutron beam test sequence                                                                                 | 57  |

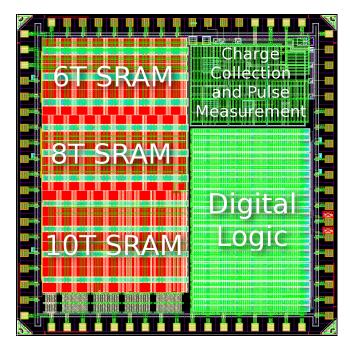

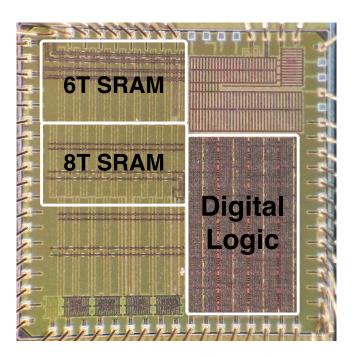

|     | 2.19 | Die Photograph                                                                                             | 58  |

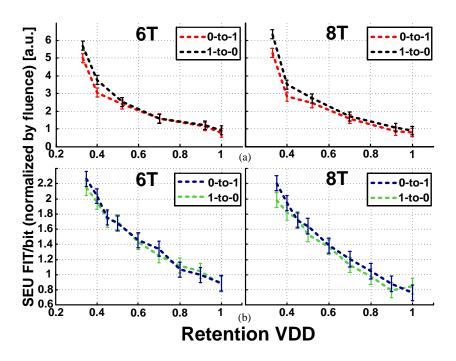

|     | 2.20 | SRAM/RF SER vs. Retention $V_{DD}$ for (a) neutron and (b) alpha radiation                                 | 60  |

# LIST OF FIGURES (Continued)

| F,18 | gure |                                                                                                                                                       | <u>P</u> | age |

|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----|

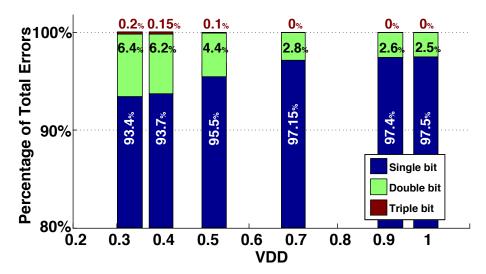

|      | 2.21 | SRAM MBU rate vs. $V_{DD}$ under neutron irradiation                                                                                                  |          | 63  |

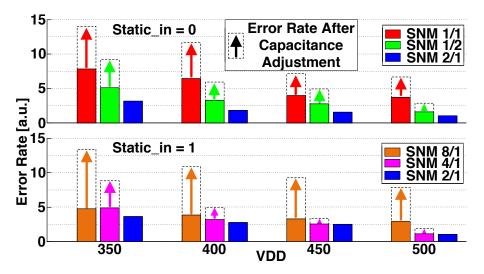

|      | 2.22 | Static noise margin test error rates vs. $V_{DD}$                                                                                                     |          | 66  |

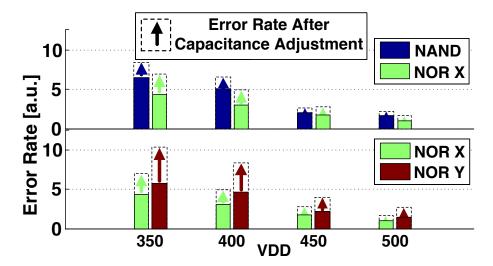

|      | 2.23 | NAND and NOR test error rates vs. $V_{DD}$                                                                                                            |          | 69  |

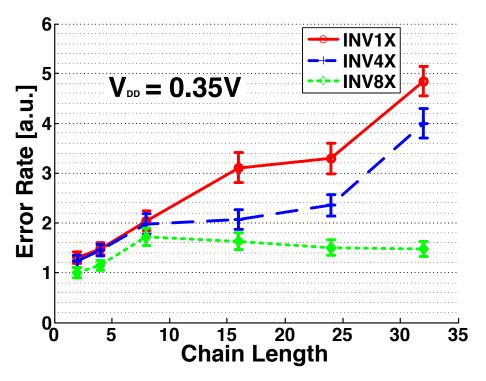

|      | 2.24 | Chain length vs. error rate for 3 different inverter sizes                                                                                            |          | 71  |

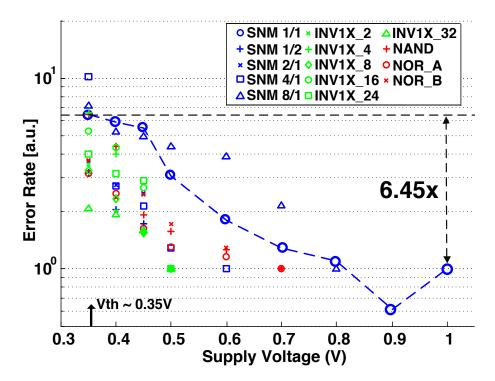

|      | 2.25 | All logic test error rates vs. $V_{DD}$                                                                                                               | •        | 73  |

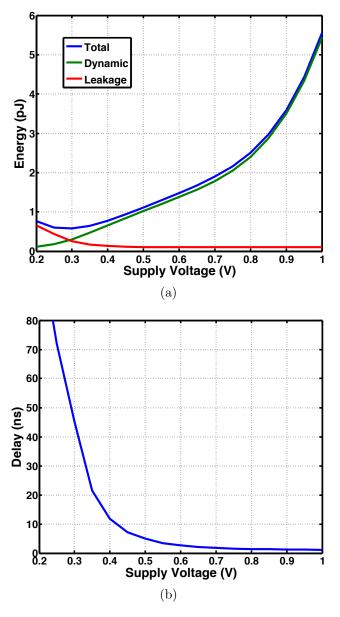

|      | 3.1  | Simulations of a<br>16-bit fixed point multiplier in 45nm SOI: (a) static and dynamic energy vs.<br>${\rm V}_{DD};$ (b) delay vs. ${\rm V}_{DD}$      |          | 81  |

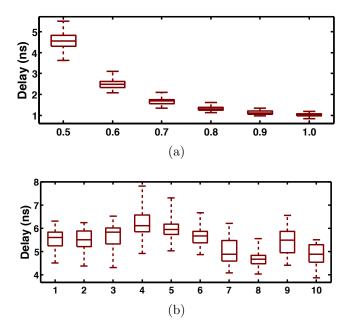

|      | 3.2  | Simulated delay variation for a 16-bit fixed point multiplier for: (a) Scaled supply voltage; (b) Spatial variation of 10 multipliers on the same die |          | 83  |

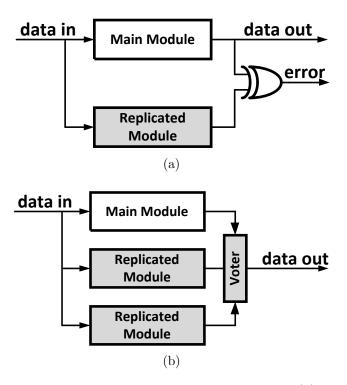

|      | 3.3  | Architecture level error-protection techniques (a) Dual Modular Redundancy; (b) Triple Modular Redundancy                                             | •        | 85  |

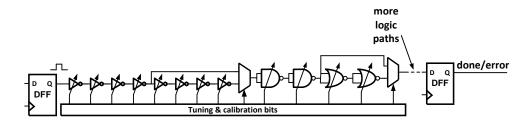

|      | 3.4  | A typical Tunable Replica Circuit (TRC)                                                                                                               |          | 87  |

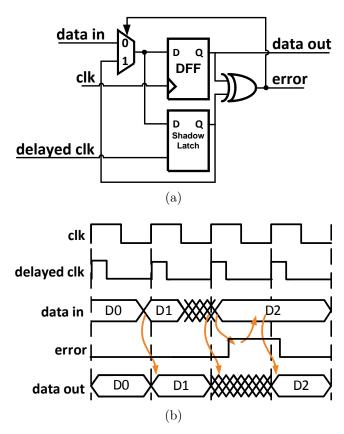

|      | 3.5  | Razor error detection sequential circuits (a) Circuit schematic; (b) Timing diagram                                                                   |          | 88  |

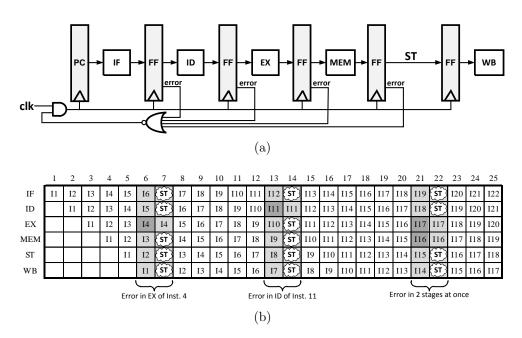

|      | 3.6  | <ul><li>(a) Pipeline modification for Clock Gating error recovery method;</li><li>(b) Clock Gating pipeline data path with errors</li></ul>           |          | 90  |

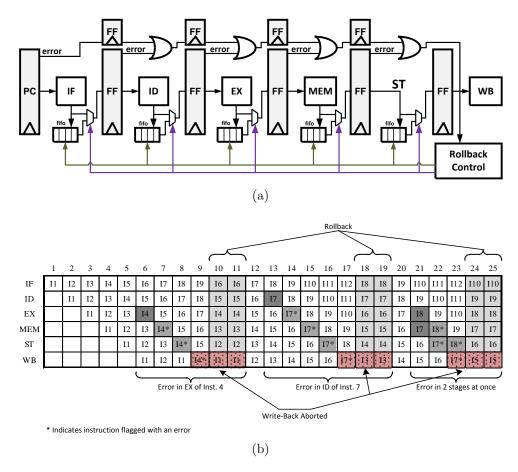

|      | 3.7  | <ul><li>(a) Pipeline modification for Micro-Rollback error recovery method;</li><li>(b) Micro-Rollback pipeline data path with errors</li></ul>       |          | 91  |

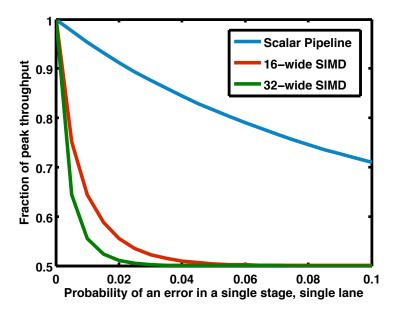

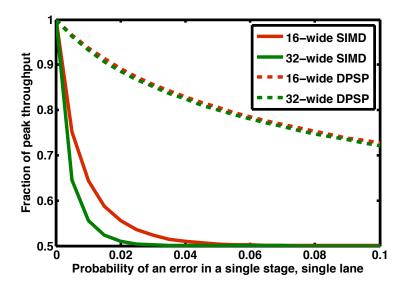

|      | 3.8  | Throughput degradation of SIMD architectures of different widths in the presence of timing errors, versus a scalar pipeline                           |          | 94  |

|      | 3.9  | Throughput improvement of DPSP for 16 and 32-wide SIMD architectures in the presence of timing errors                                                 |          | 97  |

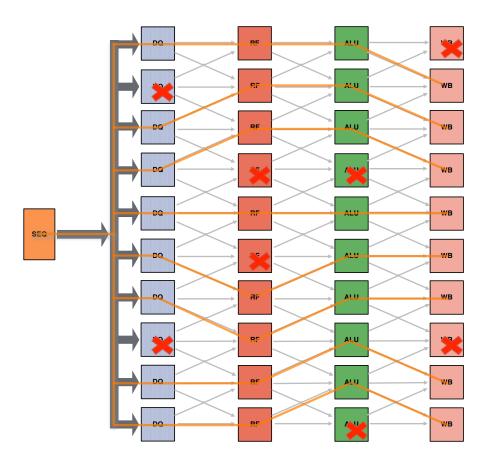

|      | 3.10 | Lane weaving connections for a 10-lane $(8+2)$ SIMD architecture .                                                                                    |          | 99  |

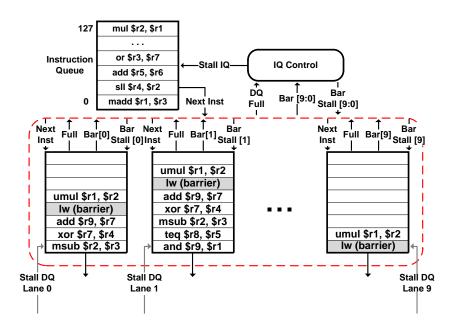

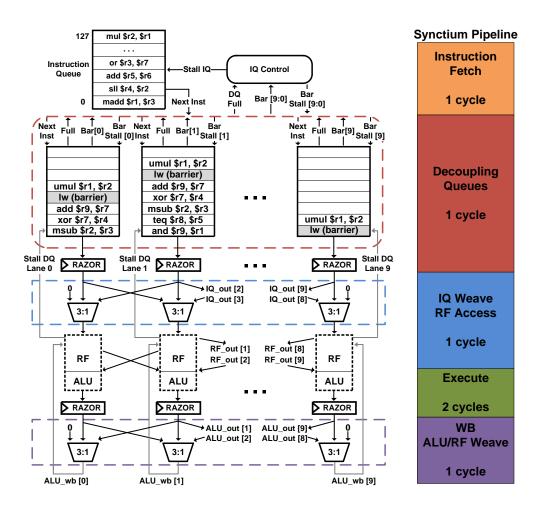

|      | 3.11 | Test-chip implementation of the sequencer and decoupling queues.                                                                                      | •        | 101 |

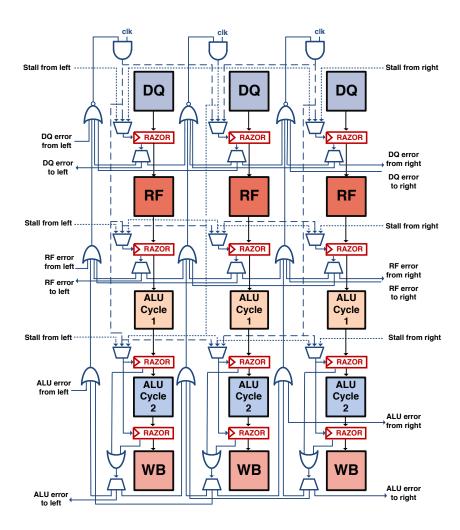

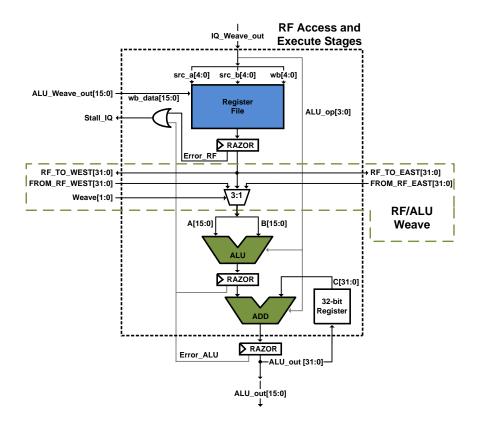

|      | 3.12 | Implementation of error detection/recovery on the pipeline                                                                                            |          | 103 |

# LIST OF FIGURES (Continued)

| <u>Figure</u> |                                                                             | Page |

|---------------|-----------------------------------------------------------------------------|------|

| 3.13          | Block diagram of 10-lane pipelined architecture                             | 105  |

| 3.14          | Detailed block diagram of RF/ALU portion of pipeline                        | 106  |

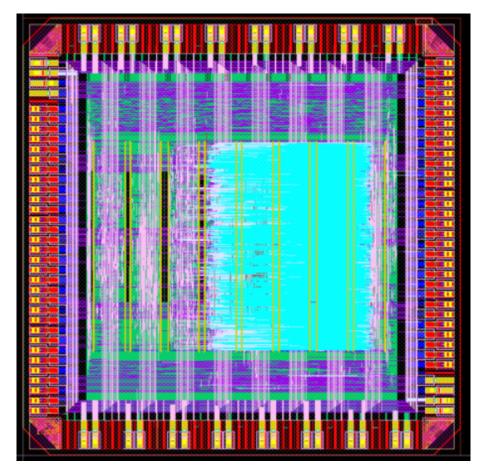

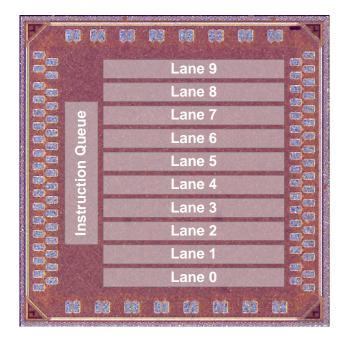

| 3.15          | Top level layout of Synctium test chip                                      | 108  |

| 3.16          | Die Photograph                                                              | 109  |

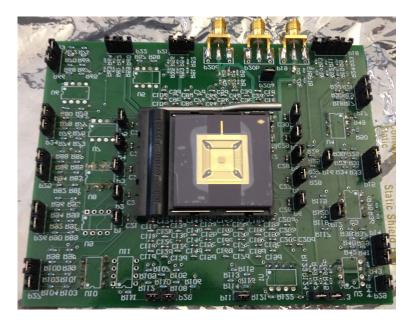

| 3.17          | Test board photograph                                                       | 111  |

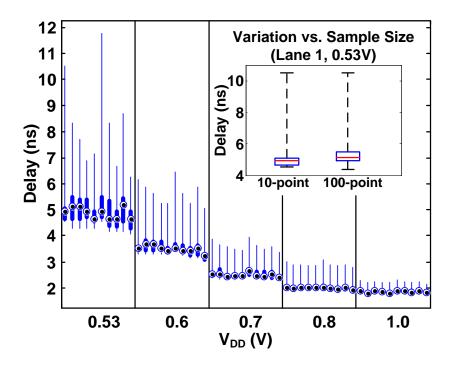

| 3.18          | Delay Variation of all 10 lanes across multiple voltages                    | 113  |

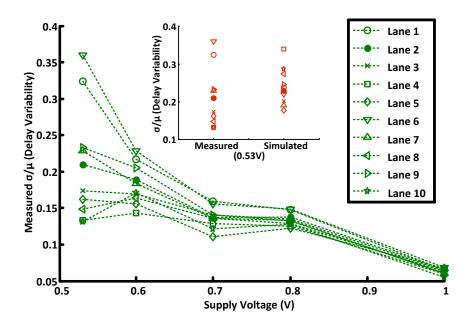

| 3.19          | Mean normalized delay variability for all 10 lanes across multiple voltages | 114  |

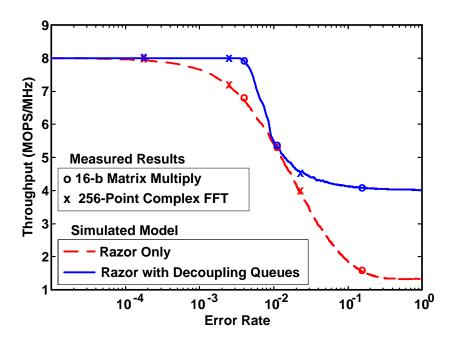

| 3.20          | Throughput effect of decoupling queues                                      | 115  |

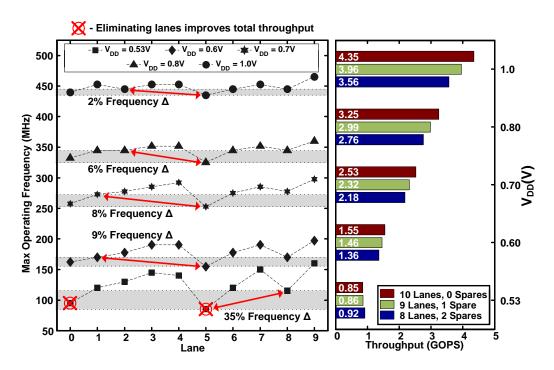

| 3.21          | Lane weaving effect on frequency and throughput across multiple voltages    | 116  |

# LIST OF TABLES

| <u>Table</u> |                                                                                 | I | Page |

|--------------|---------------------------------------------------------------------------------|---|------|

| 2.1          | n-Si-28 reaction products and the energy threshold of the incident neutron [19] |   | 19   |

| 2.2          | Design summary of the soft error test chip                                      |   | 59   |

| 3.1          | Area Breakdown                                                                  |   | 110  |

| 3.2          | Performance Summary                                                             |   | 118  |

## **Chapter 1: Introduction**

## 1.1 Near-threhsold error sources and resiliency techniques

The primary goals of this dissertation are to understand the relationship of radiation-induced soft errors and near-threshold operation of digital logic and memory circuits, and to enable and develop new techniques to combat these errors and increase the possibility of reliable near-threshold designs. Prior research has shown that near-threshold operation introduces a significant energy benefit, while also resulting in degraded performance and increased sensitivity to variation. [1]. Little work, however, has been done to understand the relationship between near-threshold operation and soft error rates for both combinational logic and memory.

Circuit designers need to understand the tradeoffs between low-voltage operation, process technology, and soft error rates before chip fabrication. In order to enable them to make these assessments, a simulation framework needs to be developed based on models built using empirical data. To gather this data correctly and consistently, a test platform should be developed that is robust across voltages, and easily portable across processes.

An analysis of this collected data reveals error rate trends that show that low-

ering the supply voltage results in a noticeable soft error rate increase in both the memory and logic circuits. Methods to detect and correct these radiation induced errors as well as errors due to timing variations are determined to be necessary for near-threshold. Additionally, utilizing a massively parallel architecture would help to increase the throughput at low voltages, making the design more attractive for low-power, high-throughput applications. Existing error detection methods, combined with new resiliency techniques to enable efficient error handling on a parallel pipeline are developed, tested, and presented in this work to help advance the concept of implementing practical and reliable low-voltage designs.

#### 1.2 Radiation-Induced Soft Errors in Near-threshold

As previously mentioned, a severe lack of experimental research exists that gives insight to the relationship between supply voltage and SER for on-chip memory. Additionally, little experimental neutron and alpha particle works exists for combinational logic at any supply voltage. Knowledge of how the radiation-induced soft error rate increases at low-voltages is essential, especially considering that many applications that require low power also require high reliability. A full experimental understanding of this relationship requires the development of robust and detailed test circuits that can help to characterize SER for many different circuit structures.

In chapter 2 a test platform for radiation characterization across supply voltages is introduced and implemented in a TSMC 65nm CMOS process. This test

chip is intended to be the first in a series of chips across process, that will eventually provide valuable information to circuit designers about the tradeoffs between process, supply voltage, and soft error rate. This chip includes commonly used 6T and 8T memory structures, as well as a variety of logic tests focusing on transient pulse propagation in NAND-based vs. NOR-based logic, the effect of inverter static noise margin on the occurrence of transient pulses, and pulse propagation distance vs. inverter size. Neutron experiments were performed at Lost Alamos Neutron Science Center, and alpha particle experiments were done at the Oregon State University radiation center. The test results presented in this chapter are for experiments that, to the authors knowledge, have not been performed for the particular test circuits across supply voltage.

# 1.3 Synctium-I: A 10-Lane, Near-Threshold SIMD Processor Incorporating Timing Variation Resiliency Techniques

The degraded performance of near-threshold operation, along with the increase in timing errors due to larger variations and increased combinational logic soft error rate makes these low voltage designs the ideal environment for error resiliency techniques. Beyond effective protection against soft errors, these techniques allow for operation at clock frequencies above the timing guard bands, which will result in low-voltage designs with a more acceptable level of performance. Imple-

menting these methods on a parallel architecture will increase throughput even more, enabling them for low-power applications that require a reasonable level of throughput.

In chapter 3 a 10-lane near-threshold SIMD processor is described and implemented in an IBM 45nm SOI process. The processor utilizes two error resiliency methods: lane weaving for static variations, and the Decoupled Parallel SIMD Pipeline to combat dynamic variations. The goal of this design is to increase throughput at low voltages by mitigating the effects of increased variations, while also demonstrating a method that can be used to combat increased soft error rates at near-threshold.

# Chapter 2: Radiation-Induced Soft Errors in Near-threshold

#### 2.1 Introduction

Operating integrated circuits in the near-threshold regime has become a viable design consideration, due to the significant improvement in energy efficiency [1]. Many emerging applications, such as biomedical devices and unmanned drones, demand low power and therefore could benefit from near-threshold operation. Recent work in this area includes a 64nW ECG SoC for arrhythmia diagnosis [2] and a chip for diagnosis of ventilator-associated pneumonia operating at 0.5V [3]. These devices also require the highest level of reliability, as unexpected errors could halt proper functionality and produce devastating results.

Other applications that are less safety-critical currently experience a tolerable number of soft errors operating as nominal voltages, however as power consumption becomes a higher focus and the operating voltages shift to the near-threshold domain, a certain level of reliability needs to be held to justify the practicality of this change. For example, in the mobile space, recent work includes a 0.48V Pixel-Video recording SoC [4]. Additionally, as the size of data centers increase,

the limitation of power consumption in the data centers while still maintaining high performance is the new design focus. Understanding how the reliability of the systems change is important to understand how ideal near-threshold operation is for these data centers.

Disadvantages of low  $V_{DD}$  operation, such as decreased performance and increased sensitivity to variation, are well known. However, little prior work has been performed to quantify and explain the correlation between radiation-induced soft error rate (SER) and low  $V_{DD}$  operation for both memory and digital logic. While the basic approach to the relationship between SER and  $V_{DD}$  is linear, many simulation models show more complexity based on the circuit response [5]. The non-linear operation of the transistor at low voltage could further complicate its soft error susceptibility and the resulting simulation model.

The goal of this work is to characterize and understand the relationship between circuits operating at a near-threshold supply voltage and their susceptibility to radiation-induced soft errors. Custom test circuits have been developed and tested under neutron and alpha radiation, with memory and logic measurement results that show SER versus  $V_{DD}$  that have not been previously performed. This work is the first version of a multi-year project with the intention of fully characterizing the relationship of  $V_{DD}$  and SER across processes. While this version will produce unique experimental results for logic and memory error trends across supply voltage, it will also provide valuable information on how to improve upon and expand the test circuits and overall infrastructure of the platform for future generations. The information learned from this test platform, fully portable to

future advanced processes, can help inform future IC designers about the design tradeoffs between circuit design, process technology, low  $V_{DD}$  operation, and SER. This information will help them to determine what kinds of circuit techniques will need to be implemented (whether it is more complex error correcting codes or redundancy on memory, radiation hardened memory cells and flip-flops, or error detection and correction on computational logic) in order to ensure the highest level of reliability in low  $V_{DD}$  designs.

This remainder of this chapter will be presented as follows. Section 2.2 will cover background information on radiation-induced soft errors by first describing the physical failure mechanism and the concept of critical charge. Results from some initial HSPICE simulations showing supply voltage vs. upset-inducing pulse width will be discussed, followed by a brief introduction of the types of radiation that will be focused on in this work. Existing work in the area of low  $V_{DD}$  SER characterization in memory and logic will then be covered. The motivation for this work is given in Section 2.3. Section 2.4 will detail both the memory and logic circuit structures included on the test-chip, giving information about the design and physical implementation of each circuit as well as what conclusions are hoping to be drawn from the data of each test. Section 2.5 will expand the scope to describe the test boards, which are portable to all future generations of the test platform. The top level setup in the radiation environments and a detailed description of the testing procedure will be discussed in Section 2.6. Section 2.7 will cover the experimental results and provide some analysis, highlighting interesting conclusions that can be drawn from the measurements. The chapter will close with an analysis of the design in Section 2.8, focusing not only on how the conclusions from the measurement results can help circuit designers now, but also on areas of improvement for future versions of the test platform.

## 2.2 Background

## 2.2.1 Charge Collection and Upset Mechanism

Before describing the main sources of radiation affecting integrated circuits, it is important to understand the interaction between the device and the radiation particle that leads to an upset in the circuit. This subsection describes the process of charge generation from an ionized particle passes through the Silicon. The resulting collection of charge at the nearest pn-junction will then be discussed, as well as the state of the transistor that is required to induce an upset in the circuit.

As an ionized particle passes through a material, energy is passed from the particle to that material. The rate (energy transferred per unit length) which this occurs is called the Linear Energy Transfer (LET). This value is dependent on the mass and energy of the particle, as well as the type of material it is passing through. The energy transferred to Silicon manifests itself as charge in the material, where every 3.6eV of energy transferred generates one electron-hole pair in the Silicon [6].

The charge collection process is described in [7], and is as follows. First, a cylindrical track of electron-hole pairs is created as the ionizing particle passes through the material. If the track crosses the depletion region of a pn-junction,

the carriers are separated and charge is collected at the junction via electric-field driven drift and the electrical potential is distorted into a funnel shape. This charge collection mechanism is large and fast, typically occurring within a few picoseconds in modern, submicron semiconductor devices [8]. This results in a large initial current spike, which in many cases is what causes the upset. Once the funnel collapses, or in cases where the particle never crosses the depletion region of the sensitive drain node, charges are either collected at junctions via diffusion, will end up recombining, or diffuse into the Silicon substrate. This will create the long tail on the current profile, or in cases where the particle does not pass through the depletion region it will result in a long, low current pulse that can last up to many nanoseconds.

The amount of charge collected at the junction and whether this can result in an upset depends on a variety of factors. The LET, location, and direction of the incident particle will strongly determine how much charge is transferred to the material, and subsequently collected at the sensitive node. For example, a high-LET particle passing tens of micrometers from the junction will result in a long, low diffusion-only current pulse, where a shorter low-LET particle passing straight through the junction may result in a pulse with a very high initial current spike, and will have a higher likelihood of causing an upset. Whether the type of device hit is a PMOS or an NMOS also matters, as the difference in carrier mobility of electrons and holes will affect how much charge is collected at the junction. At the circuit level, the type of transistor hit also will have an impact depending on whether the switching threshold is above or below 50%. This characteristic will be

discussed in detail later in this chapter.

Other device level characteristics that have an effect of the likely-hood of an upset are whether the strike happens in the substrate or a well, and if the transistor is 'on' or 'off'. [9] Investigates each of these cases and describes the process of the device response, and if it results in an upset. They find that the outside-the-well 'off' strike is the most sensitive strike location, as it results in the the current profile that is most likely to cause an upset. The drift and diffusion currents raise the struck node voltage and cause an SEU. The outside-the-well 'on' strike reinforces the stored logic state and does not result in an SEU. Inside-the-well 'off' strikes result in a bipolar effect that can cause an upset [10], with smaller gate lengths of more advanced processes only increasing the impact of this phenomenon. For inside-the-well 'on' strikes the bipolar current created tends to restore the node to its original state.

## 2.2.2 Critical Charge

A typical representation of a circuit's susceptibility to an SEU is critical charge  $(Q_{CRIT})$ , which is defined as the minimum amount of collected charge  $(Q_{COLL})$  needed to induce an upset.  $Q_{COLL}$  itself is dependent on factors previously mentioned, for example, the particle LET and its direction/location, and the semiconductor characteristics (i.e. doping concentrations and physical geometry).  $Q_{CRIT}$  is the most common tool used by circuit designers in assessing a circuits sensitivity to radiation, as increasing the  $Q_{CRIT}$  value decreases the probability that the

$Q_{COLL}$  will induce an upset.

$Q_{CRIT}$  is dependent on a number of circuit and device parameters, including which nodes in the circuit are most sensitive (PMOS or NMOS, diffusion area, node capacitance), the ionizing particle types that the circuit is subjected to and its resulting current waveform, and how the particular circuit will respond to a current pulse. To characterize the  $Q_{CRIT}$  value of their circuits, designers perform SPICE simulations using a independent current source model developed from 3D device simulations. The simplest model has been proposed by Roche et. al in [11], and is described in Equation 2.1:

$$Q_{CRIT} = C_{NODE} * V_{DD} (2.1)$$

where  $C_{NODE}$  is the capacitance of the sensitive node. This approach is insufficient for most cases, as the collection of charge is not instantaneous, and the circuit feedback and response could result in a much different result for a more realistic pulse.

Equation 2.2 shows the Freeman model, developed in [12] and used in [13]. This model incorporates the exponential decay of a time parameter, which is different for each technology and found through device simulations.

$$I(t) = \frac{2}{\sqrt{\pi}} * \frac{Q}{\tau} * \sqrt{\frac{t}{\tau}} * \exp\frac{-t}{\tau}$$

(2.2)

In this equation, Q is the total charge deposited by the ionizing particle, and  $\tau$  is the process-dependent timing parameter. This model results in a lower magnitude

initial current pulse when compared with the Roche model. However, it also has a much longer decaying tail, providing a more realistic non-instantaneous pulse model that includes the effects of the minority carrier diffusion after the funnel collapses.

The most popularly used model for  $Q_{CRIT}$  characterization is the Double Exponential model, which is described in Equation 2.3:

$$I(t) = \frac{Q}{\tau_f - \tau_r} * \left[ \exp \frac{-t}{\tau_f} - \exp \frac{-t}{\tau_r} \right]$$

(2.3)

where  $\tau_r$  and  $\tau_f$  are rise and fall constants that are process-dependent and determined through device simulations. This equation results in a similar waveform to Eq. 2.2, but with a smaller initial current peak and a wider and longer decaying tail. This current pulse is used for circuit simulations that involve determining the  $Q_{CRIT}$  in both SRAM bit cells and single event transients (SET) in combinational logic.

The Diffusion model [14], is intended to model strikes that do not pass straight through the junction, where the pulse is largely due to diffusion current. The model is described in Equation 2.4 as:

$$I(t) = I_{MAX} * \left[e * \frac{t_{MAX}}{t}\right]^{\frac{3}{2}} * \left[\exp \frac{-3 * t_{MAX}}{2 * t}\right]$$

(2.4)

$I_{MAX}$  is the maximum value of the current, and  $t_{MAX}$  is the point at which this is reached. As can be expected, this current waveform has a much smaller initial peak than any of the other models, with a much larger and longer decaying tail.

This model – used in combination with the double exponential model – is a good choice for assessment of the  $Q_{CRIT}$  sensitivity of low-voltage circuits, as the chance of a long, low pulse inducing an upset may be much greater for the slower devices with lower input thresholds operating in near-threshold.

#### 2.2.3 Soft Error vs. VDD Simulations

To better understand how circuits respond to a radiation-induced current pulse as  $V_{DD}$  scales, SPICE simulations were performed on 65nm post-layout extracted netlists of a 6T SRAM bitcell (Fig. 2.1a) and a chain of 8 minimum-sized inverters (Fig. 2.2a). The simulation setups use an independent current source to act as a strike on the off NMOS in both test cases. To get an idea of how low-amplitude, long-duration current pulses could affect lower-voltage circuits, a square wave input pulse was used for the simulations, rather than the double-exponential pulse that is commonly used throughout the existing literature. The simulation process involved sweeping the pulse duration with a constant amplitude. The pulse duration was increased, until an upset was observed. This process was repeated for multiple amplitude values at different supply voltages, to see the trend of upset-inducing current magnitude/pulse duration combinations vs.  $V_{DD}$ .

Fig. 2.1 shows the trend of upset-inducing pulse duration vs.  $V_{DD}$  for 5 different current magnitudes for a 6T SRAM bitcell. A medium-length (200ps), low (5 $\mu$ A) pulse can induce an upset at  $V_{DD}$ =0.3V, as the pulse-length allows for the output of the first inverter (longer delay due to low voltage operation) to rise high

Figure 2.1: Pulse duration vs. VDD simulations for 5 current magnitudes on a 6T SRAM bitcell

enough to cross the switching threshold of the feedback inverter and flip the bit. As  $V_{DD}$  increases, the required pulse duration also increases to overcome the increased strength of the cross-coupled inverter feedback. The switching threshold of the inverters also increases to the point where the magnitude of the current pulse is insufficient to induce an upset no matter the length of the pulse duration. The rate

of pulse duration increase as supply voltage increases ranges from incremental (the  $40\mu$ A magnitude sees an increase of 19ps from  $V_{DD}=0.3V$  to  $V_{DD}=0.6V$ ) to very large (the  $5\mu$ A magnitude sees an increase of 85ps from  $V_{DD}=0.3V$  to 0.45V), with the large increase happening towards the max supply voltage where that particular pulse magnitude can cause an upset. Upsets do not occur at  $V_{DD}=1V$  until the current pulse reaches  $40\mu$ A with a 300ps duration, 8x the minimum magnitude necessary to generate an upset at  $V_{DD}=0.3V$  with a similar pulse length.

The schematic for the logic simulations is shown in Fig. 2.2a. The current source is placed at the output of the first inverter stage (whose input takes a logic zero), while the output of the 8th inverter is observed for identification of SETs. This full setup of 8 inverters actually ended being unnecessary, as it was found that any SET that upset the 2nd inverter would pass through to the end of the chain. The current source reflects a strike on the off NMOS, pulling the node down to zero temporarily. At  $V_{DD}$ =0.3V and with a pulse magnitude of  $5\mu$ A, the minimum pulse duration required to generate a transient propagation for a least 8 inverter stages (Fig. 2.2b) is 2x smaller than an upset-inducing pulse in SRAM. As  $V_{DD}$  increases, the strength of the inverter driving the sensitive node and a rise in logic switching threshold prevent errors from occurring. While a  $5\mu$ A pulse can still cause an error at  $V_{DD}$ =0.3V, a  $40\mu$ A pulse cannot induce a transient error above VDD=0.75V, showing that combinational logic experiences a significant increase in soft error sensitivity as  $V_{DD}$  decreases.

Figure 2.2: Pulse duration vs. VDD simulations for 5 current magnitudes on a chain of 8 inverters

## 2.2.4 Sources of radiation

The applications that are the focus for applying what is learned from this project are terrestrial. That is, they are all subjected to the sources of radiation within the Earth's atmosphere. There are three main sources of terrestrial radiation that can affect on soft error rates, all of which are well understood in prior research. These areas are: high energy fast neutrons (greater than 1MeV), low energy thermal neutrons (much less than 0.001MeV), and alpha particles generated by radioactive isotopes located close to the active areas of the IC's. This subsection will provide background on the sources terrestrial radiation and how they interact with the chip materials.

## 2.2.4.1 Alpha particles

Beginning in the 1970s, alpha particles emitted by trace impurities in packaging materials were found to be a main contributor to DRAM and SRAM soft error rates [15]. The alpha particle is a doubly-ionized Helium atom (consisting of two protons and two neutrons), which is emitted from unstable isotopes such as uranium, thorium, or daughter products in the corresponding decay chains (Po-210, for example). The alpha particle itself is directly ionizing, meaning that it will deposit charge in the devices with an LET of about 0.5 MeV-cm2/mg for a 10MeV particle in Silicon [16].

The alpha particle energies that typically occur range from 2-10 MeV, meaning that the particles themselves only have a range of about  $100\mu$ m in Silicon. In air, the range of the alpha particles is only 2cm-3cm. Because of this, alpha particles emitted outside of the packaging materials are of little to no concern. Additionally, alphas can be easily shielded, so extra shielding layers on the chip can further limit their SER contribution. Through the use of these shielding layers, along with using purified materials in the manufacturing process, the alpha particle flux rates from

the semiconductor and packaging materials have significantly decreased from 100 cts/cm<sup>2</sup>/h in the 1970s to about 0.001 cts/cm<sup>2</sup>/h more recently [7]. The largest remaining contributor to alpha flux is the lead solder on the flip-chip IC, as Pb-210 can decay to Po-210 (a common alpha emitter). This is mostly fixed by moving to lead-free solders, though it has been shown that Uranium and Thorium still exist as alpha particle emitters in the lead-free material [17].

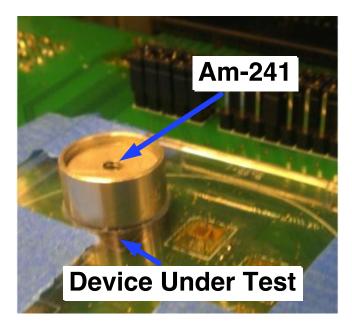

While no longer as large of a contributor to SER as they once were, alpha particles are still important for characterizing the overall reliability of an integrated circuit. For the purposes of this project, alpha tests are used along with neutron experiments for low-voltage radiation characterization. Because an alpha source is also much cheaper and easier to obtain, it is also useful for verifying the test setup functionality over extended periods of test time.

#### **2.2.4.2** Neutrons

Unlike the alpha particles, neutrons themselves do not directly create electron-hole pairs in the semiconductor. Instead, they cause soft errors through indirect ionization. That is, the inelastic reactions of the high energy neutrons with the chip materials create a number of different particles that can impart large amounts of charge on the devices. The most common material that is involved in these reactions is Si-28, as it is shown in [18] that accounting for only the n-Si reaction will result in a realistic soft error upset rates (with about a 10%-20% underestimation). As Table 2.1 shows, the products of these inelastic reactions depend on

the energy of the incident neutron. In the past, neutron-induced upset rates were dominated by the burst of energy deposited in a relatively small volume by heavy recoils. However, as  $Q_{CRIT}$  values decrease with technology scaling and operation at lower supply voltages, even light nuclear fragments, such as low-energy protons, might deposit sufficient energy in sensitive volumes, contributing to a much sharper increase in SER as supply voltage approaches near-threshold.

Table 2.1: n-Si-28 reaction products and the energy threshold of the incident neutron [19]

| Reaction Products          | Threshold (MeV) |

|----------------------------|-----------------|

| $^{25}Mg + \alpha$         | 2.75            |

| $^{28}Al + p$              | 4.00            |

| $27Mg + n + \alpha$        | 12.00           |

| $^{26}Mg + ^{3}He$         | 12.58           |

| $^{21}Ne + 2\alpha$        | 12.99           |

| $2^{7}Mg + 2p$             | 13.90           |

| $2^4Na + p + \alpha$       | 15.25           |

| $^{15}N + ^{14}N$          | 16.97           |

| $^{12}C + ^{16}O + n$      | 17.35           |

| 27Si + 2n                  | 17.80           |

| $2^{6}Mg + p + d$          | 18.27           |

| $^{12}C + \alpha + ^{13}C$ | 19.65           |

| $20Ne + n + 2\alpha$       | 20.00           |

Neutron radiation presents an issue for IC designers largely because, unlike alpha particles, steps (outside of circuit design techniques) cannot be taken to reduce the neutron flux seen by the chip. In order to reduce the flux via shielding concrete needs to be used, where the rate of shielding is only 1.4x lower flux per foot of concrete [20]. Adjusting the manufacturing process will also have little to

no effect, as terrestrial neutrons are created as a result of primary cosmic rays [21] reacting with the top layer of the Earth's atmosphere. The neutron flux is highly dependent on altitude [21], where at 20,000m they reach their peak, and as the altitude lowers, the flux decreases significantly as a result of cascading reactions between the neutrons and the Earth's atmosphere.

The altitude dependency of neutron flux provides a strong motivation for increased reliability of certain applications that operate at higher altitudes. For example, going from sea level to 40,000 ft. (flight altitude for commercial airlines) results in 300x increase in neutron flux. A 5 Mb SRAM that was characterized for 1 error every year at sea level will see about 1 error every 1.2 days of flight time. While the typical passenger is not on a flight for this length of time, passengers with safety-cricital medical devices cannot risk this significant increase error probability compounded with the decrease in reliability from low-voltage operation.

As previously mentioned, both fast neutron (greater than 0.5MeV) and thermal neutron (less than 0.2eV) reactions with the chip materials can result in soft errors in circuits. However, thermal neutrons are well below the threshold energy for Si-28 reactions, and therefore interact with other isotopes found within the semi-conductor. It has been found that the Boron-10 isotope found in the Boron-Doped Phosphosilicate Glass (BPSG) dielectric layer was the cause of many reliability issues related to thermal neutrons (Boron-10 has a very high thermal neutron cross-section) [22]. Since this discovery, B-10 has been removed from most advanced process flows, and soft errors due to thermal neutrons have been reduced, though SEU's due to thermal neutrons have still been found in 45nm and 90nm

technologies [23].

#### 2.2.5 Related Work

#### 2.2.5.1 SRAM

As mentioned in the introduction, a surprisingly limited amount of work has been done to experimentally measure and understand the relationship between  $V_{DD}$  and radiation-induced soft errors. Researchers in [24] have done a thorough investigation of neutron-induced SER in SRAM. They find an 18% increase in 90nm cache SRAM SER for every 10% decrease in  $V_{DD}$  down to 0.7V, staying well above the threshold voltage. They also look at the dependence of NMOS vs. PMOS diodes and diffusion area. Their results were very interesting, as they found that NMOS diodes had a 14% higher error rate, and also observed a linear relationship between diffusion area and SER.

An in-depth experiment in [25] and [26] of a 10T sub-threshold SRAM in 65nm exposed to both alpha and neutron radiation find an 8x and a 7.8X increase for alpha and neutron-induced SER, respectively, after scaling  $V_{DD}$  from 1.0V down to 0.3V. They also take an extended look at Multiple Cell Upsets (MCU) where consecutive bit cells on the same word line are upset by the same particle strike. This is an important effect to take a look at, as an increase in MCUs will require more complex error correcting codes. They find that once the supply voltage drops below 0.6V, the percentage of MCU to total errors begins to increase, topping out

at 3% at  $V_{DD} = 0.3V$ . MCUs are highly dependent on bit cell layout and the 10T sub-threshold cell has a much larger layout than the standard 6T cell, and therefore will yield a lower MCU rate at all voltages.

## 2.2.5.2 Combinational Logic

Even less experimental research has been presented for the relationship of  $V_{DD}$  and combinational logic SER. In [27] a ring oscillator is implemented in 130nm and monitored for harmonic oscillation, at which an upset event occurs. The threshold energy to induce an upset at each supply voltage is known, as tests are run using the two-photon absorption laser technique [28] and the strike location and energy are controlled. They find that the minimum threshold energy required to cause an upset in the ring oscillator decreases linearly as the power supply voltage decreases, until the circuit enters the sub threshold region at which point the single-event susceptibility remains constant.

While the ring oscillator is an effective method for identifying the threshold energy for SETs occurring on the inverters, trying to determine the error rate by monitoring the frequency changes in an accelerated neutron environment can be difficult. A more effective way to monitor the soft error rate is to have the logic chains output to a storage element, which is then monitored for error counts. This method of combinational logic soft error testing has been done in prior research, however, none of this research has run experiments at low-voltages. These circuits will now be covered, and any necessary changes to perform successful low-voltage

experiments will be discussed.

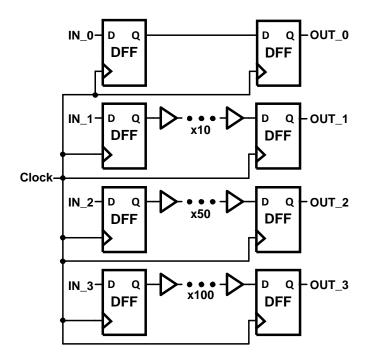

Researchers in [29] implement the circuit from Fig. 2.3 in 65nm. The test chip contains 4 different chains of 128 D-flip-flops. 3 of the chains have different numbers of inverters in them to see what the combinational logic contribution is at different frequencies ranging from 9.75MHz to 500MHz. They conclude from the heavy ion experimental data that the errors due to upsets in the flip-flops far outnumbered any errors due to logic single event transients being latched. This circuit itself does not focus so much on the soft error rate of combinational logic, as it more just develops an idea of if the combinational logic is as much of a concern as the sequential logic in the design. To shift the focus of the experiment, the sequential elements will need to be hardened to ensure that errors that are being seen are from the combinational logic. Also, the clock buffers will need to be hardened, as a strike on the clock tree could cause a glitch, and subsequently, false errors on multiple bits. This was identified as an issue in [29].

The data path test chip implementation in 32nm for [30] is shown in 2.4. They place 4 different versions of this path on the chip, with inverter chains of length 10 and 6, having both normal P/N ratios and skewed ratios to allow for longer SET propagation. Their on-chip clock generator also can output at speeds from 80MHz to 2GHz. The test chip was was exposed to alpha-particle and neutron radiation, and it was found that the combinational SER increases linearly with clock frequency. It was also found that the combinational SER contribution per sensitive static logic gate is less than 1% of the nominal latch SER at 1GHz at 0.75V. Expanding to the chip level, the total SER contribution of combinational

Figure 2.3: Combinational logic test circuit implemented in [29].

logic is well below 30% of the chip-level nominal latch SER.

Similar to [29], the focus of this work is to identify combinational logic SER trends in relation to clock frequency and to compare the SER of logic when compared with sequential logic. Once again, the FF's were not hardened to isolate the combinational logic itself. In this implementation the clock tree buffers were hardened to prevent unwanted errors from clock tree strikes, which they report to be successful as they saw minimal SER contributions from clock node strikes. While they do not report any supply voltage SER trends, this design as a whole would be acceptable for porting to low-voltages. Increased hardening for the FF's, clock tree, and counters would have to be implemented, possibly by operating them at

Figure 2.4: Combinational logic test circuit implemented in [30].

a separate, higher supply.

## 2.3 Motivation

As the push towards near-threshold design continues, all of the limitations need to be understood and information about them needs to be easily accessible for circuit designers. With more applications emerging where low-voltage operation would be useful, the reliability of these applications and the environment they are in should be well understood. It is important to fully understand the relationship between supply voltage and SER for different circuits within designs.

While some prior experimental research has begun to investigate the dependence on  $V_{DD}$  for SRAM SER, their overall assessments are incomplete in different ways. In [24], they do not scale  $V_{DD}$  down to the sub/near-threshold region. [25]

and [26] do take measurements down to  $V_{DD} = 0.3V$ , however, they perform this experimental work on a custom 10T sub threshold cell. The difference in physical cell size of this cell from the standard 6T bit cell may result in largely different MBU rates, which are of great importance. Additionally, the decoupled read and write ability of this cell adds extra capacitance to the internal storage nodes of the cell, resulting in a lower sensitivity to soft errors when compared with the 6T cell.

For digital logic, [29] and [30] present test circuits that are effective for finding the contribution of combinational logic to SER, but do not investigate different circuit characteristics in detail. Furthermore, they do not test at low-voltages, and would need to make some changes to their designs for effective measurements at low supply voltages. [27] uses a ring oscillator to detect SET's, however this focuses on inverter-based logic and this test setup would not be effective for neutron measurements, as they use a two-photon absorption laser with known, controlled energy levels. Most other work found does not involve measurement results, instead performing a simulation-based analysis [31].

The growing interest for near-threshold operation combined with a significant lack of existing research dictates the need for further experimental results in this area. Both commonly used SRAM and combinational logic should be considered. While not ideal for reading to or writing from at low operating voltages, static 6T cells in retention mode at low-voltages will be increasingly susceptible to radiation strikes. Focusing on those, and other more commonly used SRAM bit cells will provide more beneficial and widely-useable results. Sub/near-threshold experimental results for combinational logic will be interesting, and the first of its kind. Specific

results concerning different circuit characteristics also will provide a more in-depth analysis, and be more useful information for circuit designer. Logic measurements across process are also of great importance, as simulations from prior work predict a logic SER increase with process scaling [32].

The goal of the work described in this chapter is twofold. First, measurements taken from the presented test chip are the first of its kind, and will provide useful initial information to the community about some specific circuit dependencies pertaining to the relationship between  $V_{DD}$  and SER. Second, and perhaps more importantly, this is the initial version of an entire test platform meant for characterization across processes. The data collected over multiple technologies will then be used to create empirical models and develop a tool for circuit designers to use to determine how SER will factor into their particular design. This first version of the platform will provide useful information for future versions on how the circuits, system, test setup, and test sequence can be improved for more efficient and useful data collection.

# 2.4 Chip Implementation

Because the overall goal of this project is to characterize radiation induced soft errors at low-voltages for both SRAM and combinational logic (particularly taking into consideration different circuit characteristics in the combinational logic), a large variety of circuit structures on-chip are necessary. This raises the issue of test efficiency, as die size and available radiation exposure time can severely limit the total error count and the resulting statistical confidence of our measured data. Therefore, during chip design heavy considerations were made to maximize the available die space while still developing test circuits that would result in interesting results. Essentially, the goal in the chip design stage was to make the complexity of the test circuits themselves high, while maintaining a simple and robust test-interface.

This section will go into detail about the circuit design choices that were made for this test-chip. It will describe the circuit implementation, discuss why the circuits were chosen, and highlight what information will be drawn from the experimental results. Also noted will be the design decisions that were made to ensure the highest amount of data collection over a limited amount of testing time. Circuit architectures in the test interface to ensure successful low- $V_{DD}$  testing will also be discussed.

#### 2.4.1 SRAM

The focus of the SRAM portion of the reference design was to see how commonly used bit cell structures' soft error rates increase as supply voltage is scaled. For these tests, the decision was made to include the standard 6T cell and an 8T cell with a dynamic read port [33]. As mentioned in the previous section, the 6T cell used in commercial off-the-shelf SRAMs is not ideal for low- $V_{DD}$  operation as the low-margins result in read instability and weak write ability [34], [35]. However, the knowledge of the low- $V_{DD}$  SER is still of great use, as many applications will

put the memory cells into a low-power data-retention of 'sleep' mode where the supply voltage is dropped to reduce leakage power.

The 8T bit cell is a popular choice for high-speed or low-power caches, where the read-stability is improved by decoupling the read-line. In [33] they can operate the bit cell down to  $V_{DD}$ =0.41V in 65nm. Because of this, SER measurements for this bit cell are of use both for applications that utilize a low-voltage retention mode and where the 8T cell is implemented in caches and always operating at low- $V_{DD}$ .

A straight comparison to the 6T cells is of use to further assess the merits of increasing memory area by implementing the 8T cells in the design. For example, the effect of added capacitance from the gate of the read-line transistor at sensitive internal feedback nodes should have an effect on per-bit SER. Additionally, different cell layouts (increased size in the 8T cells, different location of sensitive nodes) also should have an effect on multiple bit upset (MBU) measurements.

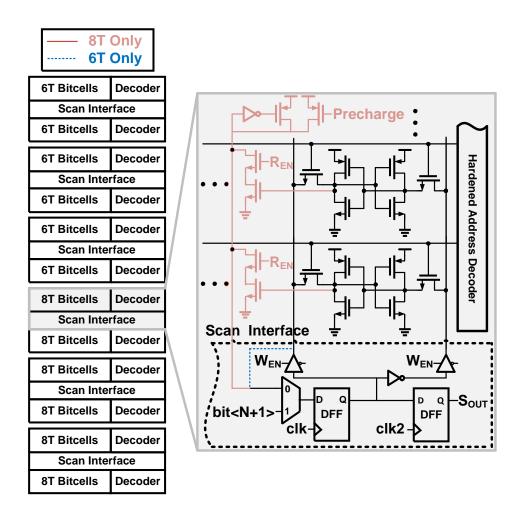

The high-level implementation of the memory test structures is shown in Fig. 2.5. The structure of both the 6T and 8T bit cell arrays are shown on the right portion of the figure. Portions of the circuit drawn in black are included for both the 6T and 8T structures, circuits drawn in red are included only for the 8T, and dotted blue lines are included only on the 6T section. For both structures, each column contains 32 cells on a shared bit line, with well taps placed on both the top and bottom of each column. The 6T and 8T arrays have 560 and 462 cells, respectively, on a shared horizontal word line. The left portion of Fig. 2.5 shows the block diagram of the memory floor plan. Two banks of memory arrays share

Figure 2.5: Top-level SRAM architecture

one synthesized scan-chain block, such that each 6T and 8T scan chain block is 1120 and 924 bits, respectively. This grouping was copied 3 times for both the 6T and 8T cells to maximize the number of bits on-chip limited by the available die space.

Writing to/reading from the bit cells is done through a dual-clocked scan in-

the data could pass through consecutive scan-bits on one rising clock edge, resulting in lost bits. The scan chain schematic for each column of memory is shown on the bottom right portion of Fig. 2.5. The input to the first flip-flop (clocked by clk) takes either the read line value (the non-inverted bit line for the 6T array or the decoupled read line for the 8T array) in parallel mode, or the output of the previous bit in the scan chain in serial mode. This is determined by a multiplexor whose select input is controlled by a 'scan\_enable' signal that comes from off-chip. The output of the first flip-flop for each bit of the scan chain is connected to one column's bit lines, with the inverted value connected to the complemented bit line of each column in the memory array. Two tri-state buffers controlled by an enable bit (WEN) prevent the scan-chain input from incorrectly affecting the state of either bit line.

As shown on the left side of Fig. 2.5, each memory array bank has its own local hardened address decoder. All address decoders take the same address select inputs from an off-chip source. For word line activation, the desired address bits are input directly into the address decoder, which is hardened through logical masking by simply ANDing the decoder output with an enable signal to prevent an address from being incorrectly accessed during testing. This setup, while simple, is efficient for the types of test that we want to run, as a known set of bits will be clocked through the scan-chain and written to all of the columns simultaneously for scanin, and each word set will be loaded into the scan-chain and then clocked through on scan-out. Both of these procedures will only need to be repeated 32 times, once

for each bit in the column.

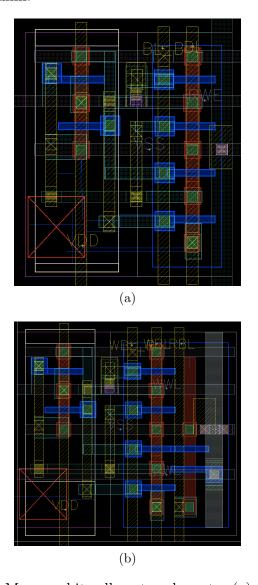

Figure 2.6: Memory bit cell custom layouts: (a) 6T; (b) 8T

Due to legal issues with placing the TSMC high density 6T cell provided by the foundry into our design, both the 6T and 8T SRAM bit cells utilized custom layout based on logic design rules. This resulted in physical cells (Fig. 2.6) that

were roughly twice as large. The large spacing had three major effects on the tests. The first, and most detrimental, was that the amount of memory that could be included on chip was cut in half, significantly affecting the test efficiency. Second, the custom cells were designed with the cross-coupled inverters having equal P/N ratios, meaning that the static noise margin of the inverter is shifted from %50 and will have an effect on the error rate (as a lower switching threshold should be more sensitive to current pulses). The third issue was that the lower density of the memory arrays – with sensitive internal nodes that were spaced farther apart - would lead to MBU results that were much lower than they would be for the standard 6T bit cell arrays. Using larger custom designed cells had a few positives, however, as this allowed for more control of internal node capacitance and the ability to monitor the physical layout effects on MBU's. For example, it can be seen in Fig. 2.6 that the PMOS and NMOS are isolated from each other to the left and right. Monitoring MBU trends for adjacent horizontal cell orientation will allow for observation of the effect of the placement of sensitive PMOS or NMOS drain nodes next to each other in local bit cells.

# 2.4.2 Digital Logic

The focus of the digital logic tests was to identify how particular implementations of combinational logic are affected by radiation-induced soft errors as the supply voltage is scaled. In order to achieve this, a variety of different test circuits on chip are necessary, all needing to be fully functional at low voltages. This requires

steps to be taken to increase test efficiency and accuracy. This subsection will describe the methods used to implement the combinational logic experiments. It will first describe the high-level architecture and test interface, and then go into more low-level circuit details about each of the tests.

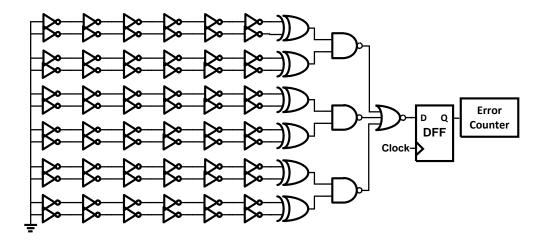

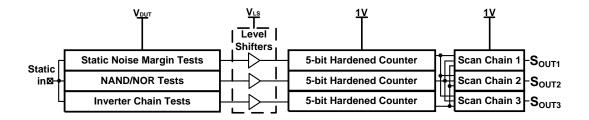

The high-level architectural diagram of the logic test structure is shown in Fig. 2.7. Each individual logic test consists of the following: The circuit under test, a level shifter, and a 5-bit counter. There are 20 unique logic chain implementations in each set – all with a synchronous and an asynchronous version – for a total of 40 different chains. Asynchronous tests were used for strict observation of the tests themselves, that is, any SET that occurs in the chain (As long as the pulse width is long enough) will be counted, which shows the direct effect of each circuit characteristic on whether or not SETs are occurring in the first place. The synchronous tests were placed with the purpose of testing the effect of timing masking and how the error rate changes with clock frequency. The timing masking effect is important when considering increasing error rates as voltage is scaled, as a lower clock frequency in the sub/near-threshold region will prevent many SETs from being clocked into flip-flops and actually manifesting themselves as errors.

Figure 2.7: Top-level digital logic architecture

Every set of 40 tests is duplicated 10 times (the maximum allowed by available die space) to increase the probability of an SET occurrence during testing and achieve a large enough sample size of errors. Even with this increase in tests, each test only totaled, at most, 320 logic gates on-chip. Recent work has shown that a standard sized inverter in 90nm has a FIT (Failures in Time – the number of failures for every billion hours of device operation) rate of  $4.4 \times 10^{-4}$  [36]. Comparing this values with a standard memory 90nm FIT rate of  $1 \times 10^{-3}$  gives a static logic SER per gate about 45% lower than the SER per memory bit [37]. Considering that there is 300x fewer cells per logic test on the chip when compared with the 6T array, it will take over 600x the amount of test time to obtain similar error numbers. While this was not ideal for the neutron tests and will need to be fixed for future test chip generations in this project, it was found that enough time was provided with the alpha tests to observe a sufficient number of errors.

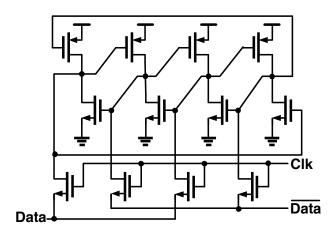

A 5-bit counter is used for each chain to detect a maximum of 32 errors during each test. The very short length of each test sequence essentially negated the chance that any more than a few errors could occur during any single run. Each of these counters is radiation-hardened through two methods. The first is to operate the counters at nominal voltage at all times no matter what voltage the circuit under test is operating at, and the second method is to use custom built DICE flip-flops (Fig. 2.8) for each bit. The DICE [38] storage element is a unique cell that is hardened by design, where a strike on any one node of the keeper portion of the cell will not change the value stored in the cell. A strike that upsets two nodes could still induce an upset, however, so steps were taken during the custom

physical layout to minimize the chance of a single particle strike upsetting multiple nodes. Additionally, any errors occurring on the counters were detectable through monitoring the change in error count over the sequence of scan-outs. For example if the data was scanned-out every 10 seconds, an increase in the counter greater than 2 was considered a result of an upset occurring on a flip-flop in the counter. Keeping with this methodology would result in only minor differences in the overall error counts.

Figure 2.8: Radiation hardened Dual-Interlocked Storage Cell (DICE) [38] used in the 5-bit counters

Each bit in the counter has a partner bit in the scan chain (which consists of unhardened flip-flops operating at a nominal supply voltage), so that the length of the logic scan chain is the total number of logic tests times 5-bits. Similar to the memory tests, TMR was used on the scan chains to detect any errors that may have occurred during scan out and each redundant scan-chain has its own input and output pin, to reduce test scan-in/scan-out time. Identification of scan-

chain errors was done during post-processing using a majority voting method. To prevent the possibility of an inadvertent particle strike on the reset line, the reset ability for the latches in the counters was removed. This eliminated the capability of zeroing out the counters prior to each test period. To account for this during the experiments, it was necessary to scan out from the counters twice: once before irradiation, and then again afterwards. Subtracting the initial value from the final value gave the total number of errors that occurred during that test period.

To ensure that an SET in the logic chain will always latch into the counter, no matter what voltage the logic under test is operating at, a buffer – serving as a level shifter – is placed between the end of the logic chain and the counter. This buffer is set to its own supply voltage  $(V_{LS})$  halfway between the logic chain voltage and counter voltage, and sized 2x minimum to properly drive the input of the DICE flip-flop. In order to account for the possible contribution of the level-shifter buffer on SETs, duplicate tests consisting of only a level-shifter connected to a counter are included. Any errors that occurred on these chains are then subtracted from the total of all other logic tests. No errors were actually detected for any of these level shifter circuits, most likely because the increased size of the cells used in the level shifters when compared with the logic under test.

As previously stated, all logic tests are duplicated to include both synchronous and asynchronous versions. The lone difference between the two versions is that the synchronous test places a clocked D-FF between the level shifter and counter in each logic chain, so that only errors caught on the rising clock edge are counted. The clock tree in the synchronous tests is hardened by increasing the size of the

buffers by 32x. The counters in both tests consist of toggle flip-flops, where the input comes straight from the level shifter in the asynchronous test, and from the clocked flip-flop in the synchronous test.

The following subsections will detail the individual circuit implementations of the digital logic tests. A variety of unique logic chains were implemented on-chip to isolate and analyze the VDD vs. SER relationship of different circuit characteristics. These characteristics include: inverter static noise margin (SNM); NAND-based vs. NOR-based logic (focusing on differences in the cell design that can lead to higher SER); and inverter size vs. transient pulse propagation. An important aspect of all of these tests is that they use a fully digital implementation with as many cells from the TSMC standard cell library as possible, thus making these tests easy to implement for future test chip versions.

# 2.4.2.1 Static Noise Margin

The purpose of the first test is to observe the effect of the switching threshold of an inverter on the probability of an SET occurrence. The conclusions drawn from this experiment are twofold. The first being an observation of the trend of how the error rate increases vs. increasing noise margin, a determination that can inform the circuit designer of how they can alter their logic to take advantage of the soft error protection provided by increasing the switching threshold. The second is to gain an idea of how effective increasing the noise margin is as a technique to use when the supply voltage is scaled. That is, similar radiation pulses will occur at

any supply voltage, so a pulse that induces an upset in an inverter operating at  $V_{DD}=1.0V$  with a 50% SNM should also induce an upset in an inverter operating at  $V_{DD}=0.5V$ , no matter what the SNM is. If the noise margin needs to be increased far above 50% under low-voltage operation this technique could become impractical, as the propagation delay of the inverter could increase significantly.

Figure 2.9: Static noise margin: (a) test chains; (b) simulated switching thresholds

Fig. 2.9a shows the schematic for the SNM test implementation. Each chain

consists of 32 inverters symmetrically sized to maintain identical switching thresholds within each node of the chain. All inverters in this test utilized a custom layout, for full control of the noise margins. The cells were then placed in the digital flow and inserted into the gate-level net list. The margins tested ranged from 20%-80%, in increments of 15%. A static input supplied by an off chip source sets the switching threshold (for 1 to 0 or 0 to 1) for each test. The simulated input thresholds with a static input value swept from 0 to 1 for each test are shown in 2.9b. A static input value of 1 reverses the margins of the tests so that the observed error rates should be the same for opposite tests, i.e. the error rate for 'SNM 1/1' with 'static in' = 0, should be the same as 'SNM 8/1' with 'static in'=1. For both cases, the error rate for 'SNM 2/1' should remain the same.

## 2.4.2.2 NAND-based vs. NOR-based Logic

This second combinational logic test looks at what approach to take when choosing what base cells to use for implementing digital logic circuits. NAND and NOR gates both exhibit the property of logical completeness, which means that any boolean function can be completed using either all NAND or all NOR gates. Because of this, often times in digital circuits are constructed strictly of NAND or NOR gates. Typical implementation at high speeds is done using NAND gates, as the propagation delay of the NOR-gate is higher. However at lower supply voltages where the operating frequency decreases significantly, using NOR-based logic is a more reasonable idea given its lower area and energy when compared with NAND

gates.

The details of the NAND/NOR tests are shown in Fig. 2.10. Each test is 32 gates, with the same input of every gate in the chain held to the same value to emulate the functionality of an inverter chain. There were three unique tests in this set included on the test chip. The first is 32 NAND-gates with the 'B' input held to a static '1', while the 'A' input takes the output of the previous gate, with the first gate in the chain taking its input from an off-chip source. The second test (labeled NOR-X in Fig. 2.10) is 32 NOR-gates in the same orientation as the NAND test, but all with their 'B' inputs held to a static '0'. The NOR-Y test switches the inputs from the NOR-X test, so that all of the 'A' inputs take a static '0', and the 'B' inputs take the output of the previous gate.

The bottom portion of Fig. 2.10 shows the transistor level schematics of the gates used in the test. Transistor sizes are indicated as a P/N multiplier value. Nodes that are most sensitive to a particle strike (the drain of an off transistor) at any point within the chain are identified and highlighted in red.

Figure 2.10: NAND and NOR test chains and radiation sensitive nodes.