#### AN ABSTRACT OF THE THESIS OF

<u>Nicole L. Dehuff</u> for the degree of <u>Master of Science</u> in <u>Electrical Engineering & Computer Science</u> presented on <u>March 7, 2005</u>. Title: <u>Fabrication and Characterization of Thin Film</u> Electromagnetic Coils and Heaters for Microchannel Applications

# Redacted for privacy

Abstract approved: \_

#### Thomas K. Plant

The focus of this thesis involves developing general fabrication processes relevant to the manufacture of two new devices for the Microscale technology Energy and Chemical Systems (MECS) program at Oregon State University. The two MECS devices developed, capture dots and transparent thin-film heaters (TTFHs), require unique process development for successful manufacture. Thick photolithography is required for the capture dots and its development is detailed. The capture dots also require copper electroplating. The copper electroplating system and process development are detailed. The TTFHs require a unique heater material, indium tin oxide (ITO). The heater deposition utilizes an ultrasonic lift-off method, also detailed. The complete manufacturing process steps of both the capture dots and the TTFHs are described. Both devices are successfully demonstrated and their electrical properties are discussed. <sup>©</sup>Copyright by Nicole L. Dehuff

à

March 7, 2005

All Rights Reserved

# Fabrication and Characterization of Thin-Film Electromagnetic Coils and Heaters for Microchannel Applications

3

by

Nicole L. Dehuff

### A THESIS

#### submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Master of Science

Presented March 7, 2005 Commencement June 2005

.

Master of Science thesis of Nicole L. Dehuff presented on March 7, 2005

APPROVED:

# Redacted for privacy

Major Professor, representing Electrical Engineering & Computer Science

# Redacted for privacy

Director of the School of Electrical Engineering & Computer Science

# Redacted for privacy

Dean of the Graduate School

I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my thesis to any reader upon request.

# Redacted for privacy

Nicol VI. Dehuff, Author

#### ACKNOWLEDGMENTS

Thank you to everyone who has helped shape the person I am today.

"For attractive lips, speak words of kindness. For lovely eyes, seek out the good in people. For a slim figure, share your food with the hungry. For beautiful hair, let a child run his/her fingers through it once a day. For poise, walk with the knowledge that you never walk alone. People, even more than things, have to be restored, renewed, revived, reclaimed, and redeemed; never throw out anyone. Remember if you ever need a helping hand, you will find one at the end of each of your arms. As you grow older, you will discover that you have two hands; one for helping yourself, and the other for helping others."

<u>,</u> 1

-Audrey Hepburn

# TABLE OF CONTENTS

è

|    |                                                |                                  |                                                                                                                                                                                                                                            | Page                                   |

|----|------------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 1. | INTRODUCTION                                   |                                  |                                                                                                                                                                                                                                            | 1                                      |

| 2. | LITERATURE REVIEW AND BACKGROUND               |                                  |                                                                                                                                                                                                                                            | . 3                                    |

|    | 2.1                                            | Devices                          |                                                                                                                                                                                                                                            | 3                                      |

|    | 2.2                                            | Photo                            | blithography                                                                                                                                                                                                                               | 5                                      |

|    |                                                | 2.2.1<br>2.2.2                   | Photoresist Composition<br>Photoresist Type<br>2.2.2.1 Negative PR<br>2.2.2.2 Positive PR                                                                                                                                                  | . 7<br>. 7                             |

|    | 2.3                                            | Elect                            | roplating                                                                                                                                                                                                                                  | . 14                                   |

|    |                                                | 2.3.1<br>2.3.2<br>2.3.3<br>2.3.4 | Electroplating Set-Up<br>Current Density<br>Plating Types<br>2.3.3.1 Direct Current Plating<br>2.3.3.2 Pulse Plating<br>Electroplating Bath Properties<br>2.3.4.1 Plating Solution<br>2.3.4.2 Bath Dimensions<br>2.3.4.3 Organic Additives | 17<br>19<br>20<br>22<br>23<br>24<br>25 |

| 3. | DEPOSITION, PROCESS AND CHARACTERIZATION TOOLS |                                  |                                                                                                                                                                                                                                            | 29                                     |

|    | 3.1                                            | Proce                            | ss Equipment Measurement Tools                                                                                                                                                                                                             | 29                                     |

|    |                                                | 3.1.1<br>3.1.2<br>3.1.3          | Thermocouple Gauge<br>Ionization Gauge<br>Crystal Monitor                                                                                                                                                                                  | 30                                     |

|    | 3.2                                            | Evapo                            | pration                                                                                                                                                                                                                                    | 31                                     |

|    | 3.3 Electroplating                             |                                  | roplating                                                                                                                                                                                                                                  | 34                                     |

|    |                                                | $3.3.1 \\ 3.3.2$                 | Electroplating Set-Up<br>Electroplating Solution                                                                                                                                                                                           | 35<br>37                               |

# TABLE OF CONTENTS (Continued)

|    |                       |                                      |                                                                 | <u> </u> |

|----|-----------------------|--------------------------------------|-----------------------------------------------------------------|----------|

|    |                       | 3.3.3                                | Plating Void of Additives                                       | 40       |

|    |                       | 3.3.4                                | Plating Uniformity                                              | 41       |

|    |                       | 3.3.5                                | Direct Current (DC) Plating                                     | 42       |

|    |                       | 3.3.6                                | Forward Pulse Plating                                           | 43       |

|    |                       | 3.3.7                                | Periodic Reverse                                                | 44       |

|    |                       |                                      | 3.3.7.1 Results                                                 | 45       |

|    | 3.4                   | .4 Sputtering                        |                                                                 | 46       |

|    |                       | 3.4.1                                | Ion Beam Sputtering                                             | 46       |

|    |                       | 3.4.2                                | CVD: Chemical Vapor Deposition                                  | 47       |

|    |                       | 3.4.3                                | RTA: Rapid Thermal Anneal                                       | 48       |

|    |                       | 3.4.4                                | RIE: Reactive Ion Etch                                          | 49       |

|    |                       | 3.4.5                                | Spin Coater/Mask Aligner                                        | 49       |

|    |                       | 3.4.6                                | Ultrasonic Cleaners                                             | 50       |

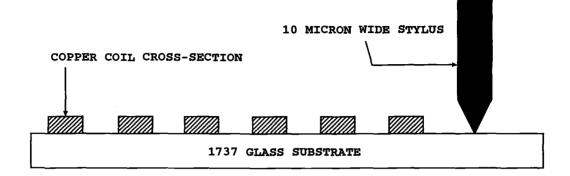

|    |                       | 3.4.7                                | Profilometer                                                    | 50       |

|    | 3.5                   | Sumn                                 | nary                                                            | 51       |

| 4. | CAP                   | TURE                                 | DOT FABRICATION                                                 | 52       |

|    | 4.1                   | Photolithography Process Development |                                                                 |          |

|    |                       | 4.1.1                                | Photoresist Selection                                           | 56       |

|    |                       | 4.1.2                                | SPR 220 Chemistry                                               | 56       |

|    |                       | 4.1.3                                | Photoresist Thickness                                           | 57       |

|    |                       |                                      | 4.1.3.1 Thin Photolithography $(1.2 \ \mu m) \dots \dots \dots$ | 58       |

|    |                       |                                      | 4.1.3.2 Thick Photolithography (7.0 $\mu$ m)                    | 58       |

|    |                       | 4.1.4                                | Spin Coating                                                    | 58       |

|    |                       | 4.1.5                                | Exposure Time                                                   | 59       |

|    |                       |                                      | Soft Bake Time(s)                                               | 59       |

|    |                       | 4.1.7                                | Development Step                                                | 60       |

|    |                       | 4.1.8                                | Photoresist Removal                                             | 61       |

|    | 4.2 Passivation Layer |                                      | vation Layer                                                    | 62       |

|    |                       | 4.2.1                                | Ion Beam Sputtered SiO <sub>2</sub>                             | 62       |

|    |                       | 4.2.2                                | PECVD SiO <sub>2</sub>                                          | 63       |

|    |                       | 4.2.3                                | Conclusions                                                     | 63       |

|    |                       |                                      |                                                                 |          |

# Page

÷

# TABLE OF CONTENTS (Continued)

÷

|            |      |                                                                                | Page |

|------------|------|--------------------------------------------------------------------------------|------|

|            | 4.3  | Etching Method(s)                                                              | 64   |

|            |      | 4.3.1 Reactive Ion Etch (RIE)                                                  | 64   |

|            |      | 4.3.2 Isotropic Chemical Etches                                                | 65   |

|            |      | 4.3.2.1 Copper Etch                                                            | 65   |

|            |      | 4.3.2.2 Titanium Etch                                                          | 67   |

|            |      | 4.3.2.3 Silicon Dioxide Etch                                                   | 67   |

|            | 4.4  | Capture Dot Fabrication                                                        | 68   |

|            | 4.5  | Electrical                                                                     | 71   |

|            | 4.6  | Conclusion                                                                     | 71   |

| 5.         | TRA  | NSPARENT CONDUCTIVE HEATERS                                                    | 72   |

|            | 5.1  | Transparent Conductive Oxide (TCO) Heater Fabrication                          | 72   |

|            |      | 5.1.1 Heater Material                                                          | 72   |

|            |      | 5.1.2 Heater Substrate                                                         | 73   |

|            |      | 5.1.3 Fabrication                                                              | 74   |

|            | 5.2  | ITO Heater Current-Voltage Measurements                                        | 75   |

|            | 5.3  | ITO Heating Effects                                                            | 79   |

|            | 5.4  | Conclusions                                                                    | 80   |

|            | 5.5  | Future Work                                                                    | 81   |

| BI         | BLIO | GRAPHY                                                                         | 82   |

| APPENDICES |      |                                                                                | 88   |

|            | Appe | endix A RIE: Reactive Ion Etch Instructions                                    | 89   |

|            | Appe | endix B Step-by-step Capture Dot Fabrication Steps                             | 91   |

|            | Appe | endix C Step-by-step Thin-Film Transparent Conductive Oxide Mi-<br>cro Heaters | 93   |

$\mathcal{L}_{n}$

# LIST OF FIGURES

à

.

| Figure |                                                                                                                                                        |      |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------|

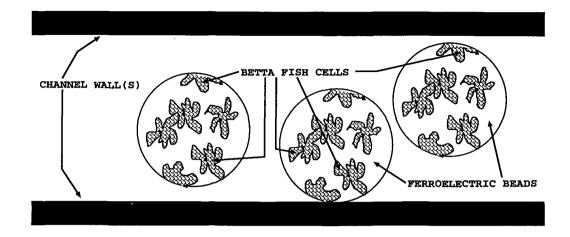

| 1.1    | Ferroelectric beads with Betta fish cells adhered to the outer surface of the beads.                                                                   | . 2  |

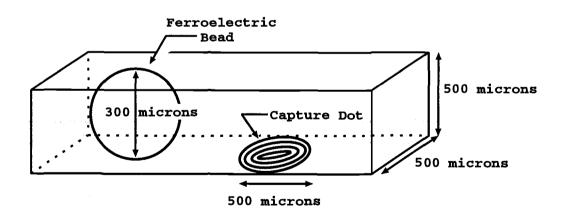

| 1.2    | Design for bead capture.                                                                                                                               | . 2  |

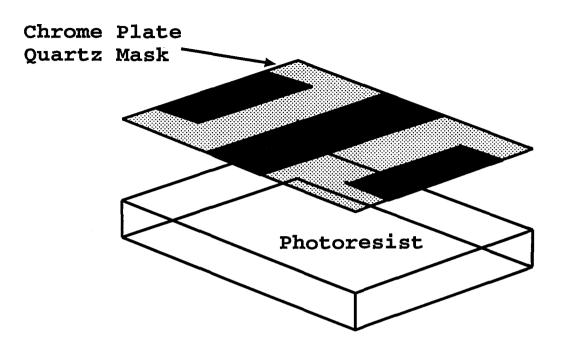

| 2.1    | Chrome mask aligned above unexposed photoresist                                                                                                        | . 8  |

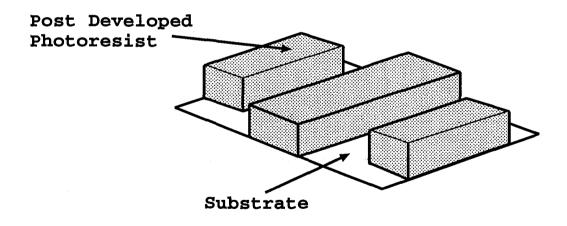

| 2.2    | Post Developed Positive Photoresist Image of Figure 2.1, after exposure and developing                                                                 | . 8  |

| 2.3    | Post Developed Negative Photoresist Image of Figure 2.1, after<br>exposure and developing.                                                             | . 9  |

| 2.4    | PAC to ICA conversion: During exposure, Development, and Post<br>Development                                                                           | 11   |

| 2.5    | Basic Electroplating Set-Up                                                                                                                            | 16   |

| 2.6    | Effects of electroplating on a non-uniform seed layer.                                                                                                 | 18   |

| 2.7    | Plating Current Schemes: (A) Direct Current (DC), (B) Periodic<br>Pulse (PP), (C) Periodic Pulse Reverse (PPR). All plots are current<br>versus time.  | 21   |

| 3.1    | Crucible holder with heated material depositing non-uniformly as<br>a Cosine distribution                                                              | 32   |

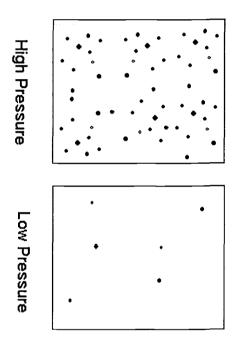

| 3.2    | Two boxes representing high and low pressure. As particles are<br>evacuated through the pumps, the pressure lowers and the mean<br>free path increase. | 33   |

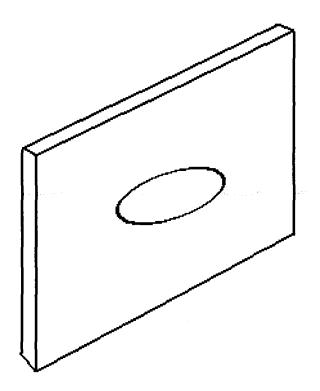

| 3.3    | Dam, separating anode and cathode. The hole in the dam acts as<br>a way of controlling the flow of ions                                                | 36   |

| 3.4    | Stylus.                                                                                                                                                | 51   |

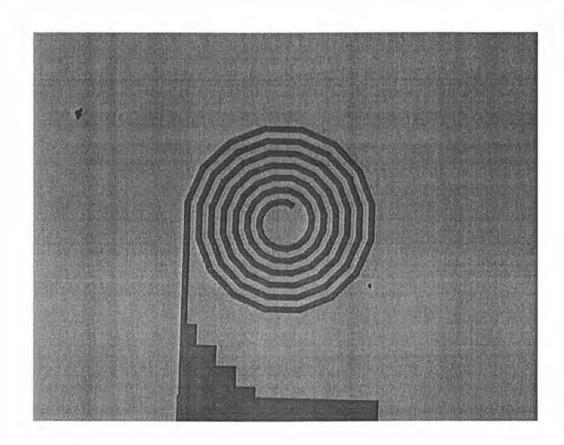

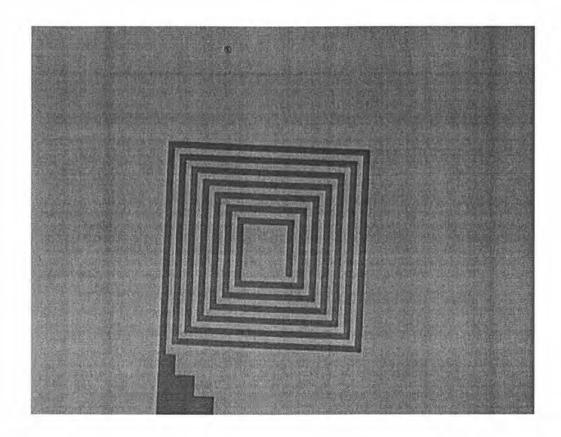

| 4.1    | Photoresist pattern of the first lithography layer of a square capture dot with 10 $\mu$ m lines and 10 $\mu$ m spacing between electroplated lines    | . 53 |

| 4.2    | Chrome plated quartz photomask for layer 1 of a 500 $\mu$ m circular capture dot with 100 $\mu$ m hole.                                                | 54   |

| 4.3    | Chrome plated quartz photomask for layer 1 of a 500 $\mu$ m square capture dot with 100 $\mu$ m hole                                                   | 55   |

# LIST OF FIGURES (Continued)

à

| Fig | ure                                                                                                                                                                                                                                                                              | Page |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

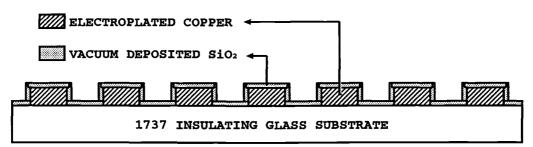

| 4.4 | Ideal film uniformity of the passivation layer between the two elec-<br>troplated copper layers.                                                                                                                                                                                 | . 62 |

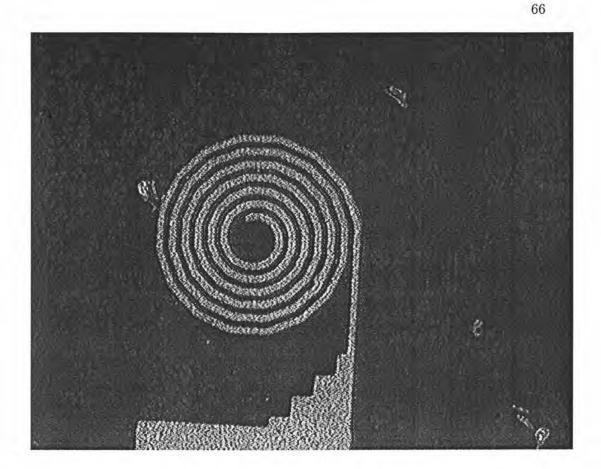

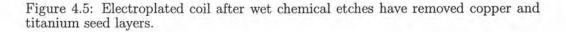

| 4.5 | Electroplated coil after wet chemical etches have removed copper<br>and titanium seed layers                                                                                                                                                                                     | . 66 |

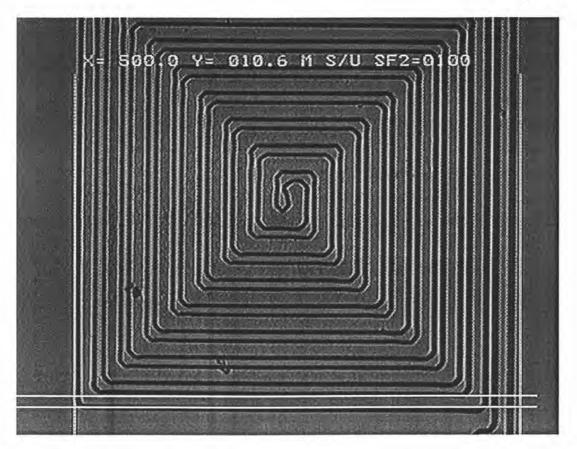

| 4.6 | Fully processed square pattern capture dot with $10\mu$ m line spacing<br>and 10 $\mu$ m electroplated copper line width                                                                                                                                                         | . 70 |

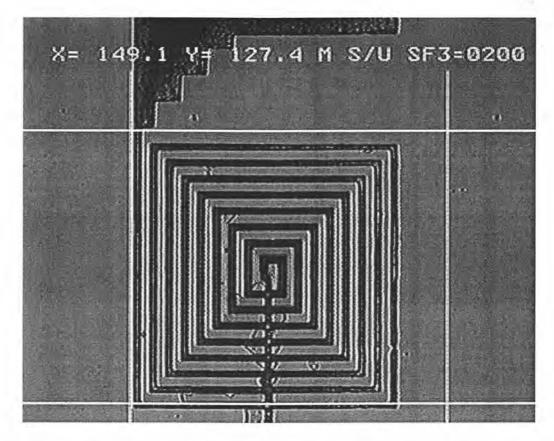

| 5.1 | Final heater structure.                                                                                                                                                                                                                                                          | . 76 |

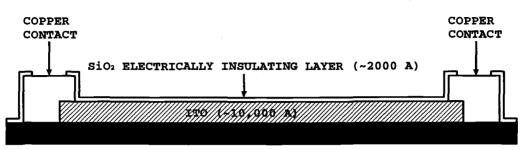

| 5.2 | Current-Voltage measurements of 1200 $\mathring{A}$ thick ITO thin-film heater<br>on 1737 glass substrate. The bottom line is the first pass (increas-<br>ing Voltage) of the I-V measurement and the top line is the second<br>pass (decreasing Voltage) of the I-V measurement | . 77 |

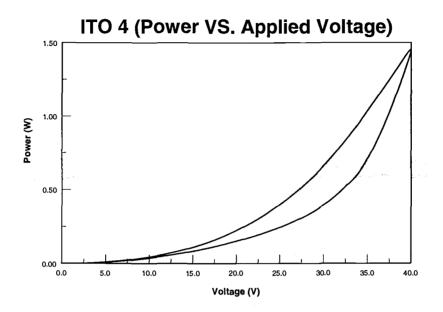

| 5.3 | Power-Voltage measurements of 1200 $\mathring{A}$ thick ITO thin-film heater<br>on 1737 glass substrate. The bottom line is the first pass (increasing<br>Voltage) of the P-V measurement and the top line is the second<br>pass (decreasing Voltage) of the P-V measurement     | . 79 |

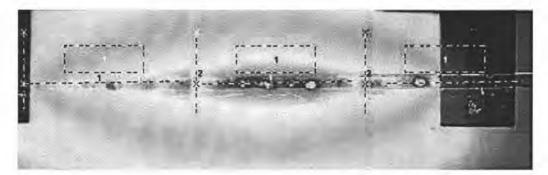

| 5.4 | Transparent Indium Tin Oxide (ITO) thin film heater shown with Infared (IR) Imaging to show relative heating. ITO 1 $\mu$ m thick on silicon substate.                                                                                                                           | . 80 |

# LIST OF TABLES

| Tab | ole          |                          | Page |

|-----|--------------|--------------------------|------|

| 3.1 | Basic Copper | Electroplating Solution. | 39   |

4

## FABRICATION AND CHARACTERIZATION OF THIN-FILM ELECTROMAGNETIC COILS AND HEATERS FOR MICROCHANNEL APPLICATIONS

# 1. INTRODUCTION

The goal of this thesis is to develop processes to fabricate thin-film electromagnetic coils and heaters for application in microchannel fluidic sensors and separators. The coils are devices that should produce a magnetic field strong enough to capture and hold, against channel flow, alginate beads with embedded ferroelectric/magnetic particles and sensor cells on the bead surface. This device is herein referred to as a "capture dot". The spherical, ferroelectric, alginate beads are approximately 300  $\mu$ m in diameter, flowing in a square channel 500  $\mu$ m by 500  $\mu$ m. Figure 1.1 shows an example of the ferroelectric beads. Betta fish cells are harvested and adhere to the outer surface of the beads. Figure 1.2 shows the design for examining these fish cells. As the beads flow gently along the channel, the capture dot is activated, producing enough magnetic field to attract and hold the ferroelectric bead. When the capture dot deactivates, the magnetic field is lost and the ferroelectric bead can continue down the channel.

Also discussed are processes developed for Nickel-Chromium (NiCr) and Indium Tin Oxide (ITO) long, thin film, microscale heaters needed for separation experiments. The unique lift-off process developed to fabricate these devices is also applied to transparent electronic devices and circuit fabrication. The heaters are fabricated with copper pads, and passivation is done with plasma enhanced chemical vapor deposition (PECVD). The heaters are then placed in microchannels, used to separate a Lithium-Bromide liquid flowing in a channel slightly narrower than the actual heater width.

Figure 1.1: Ferroelectric beads with Betta fish cells adhered to the outer surface of the beads.

Figure of plain ferro elect. beads in the Channel-3D

Figure 1.2: Design for bead capture.

# 2. LITERATURE REVIEW AND BACKGROUND

Micro Electro Mechanical Systems (MEMS) influence many areas of current technology [1]. This chapter reviews recent advances in MEMS devices. Also reviewed here are processing methods that enable MEMS technology to be manufactured. [2, 3, 4] MEMS encompasses a large body of research in industry and the academic setting. [5, 6, 7, 8] Medical devices, motor and novel electronic devices continue to become cheaper, mass produced, and more reliable with improvements made possible with MEMS technology. [9, 10] MEMS has been loosely defined as "an emerging set of technologies that make it possible to miniaturize and mass-produce large numbers of integrated sensors, actuators and computers" or as "a fabrication approach that conveys the advantages of miniaturization, multiple components and microelectronics to the design and construction of integrated electromechanical systems." [5]

### 2.1 <u>Devices</u>

MEMS devices can be as simple as tiny inductors, or as complicated as tiny motors involving multiple processing steps. [1, 11, 12] Development often demands researchers be innovative to achieve required benchmarks, pushing technology farther. [13] Novel MEMS processing has been particularly instrumental in the success of applications requiring the integration of biological components with novel electron devices, filling a void in the medical field.

One void to be filled involves cancer cell detection. Cancer research has left many doctors and patients frustrated, with needs of early detection necessary for successful treatment. To date the best method of early detection requires examining groups of polyps, looking for groups that have mutated. If groups of polyps do not hold enough mutated cells, the cancer is not detected since an average of all the cells is considered. Individual cells can be examined; however, this is time consuming and not realistic without an automated method. An automated method of examining these individual cells, flagging ones with potential mutations is in the works, involving the use of micro-actuated arms holding individual cells to be viewed.

Other MEMS devices currently improving the medical field include: variable capacitance type sensors. The variable capacitance sensors are used to measure three items: force, bending and torsion in artificial fertilization. A cell's ability to adhere to materials is of great importance for a device's ability to become compatible with existing procedures in the medical field. Without this knowledge, devices requiring cell screening could not move forward. MEMS force sensors have the ability to determine the strength of adhesion of individual cells, length of cell adhesion and mechanism of cell detachment. [14]

Reduction of device size is of continued interest. Reduction of actuator sizes, commonly found in automated systems in cars, condense systems to such a level that, one time, bulky measurement tools are now more accurate, light weight, often compact enough to fit into one's pocket. [15, 16] Electro-thermally and laterally driven polysilicon actuator devices act as micro tweezers as small voltages are applied, the 1  $\mu$ m by 2  $\mu$ m and 750  $\mu$ m long device is able to apply a force of 2.8  $\mu$ N. [15]

More involved than these devices are micro-motors. Today intricate magnetic micro-motors with excellent performance are reproducible and integrative as microactuators for future sensor applications. [16, 17] High speed rotation was demonstrated on the micron scale dating back to the late 50's. [18] These high speed motors are manufacturable and highly reliable thanks to LIGA. [17] LIGA, X-ray lithography, electroforming and molding. The LIGA acronym is actually derived from the German form of X-ray Lithography, Electroforming and molding.

The LIGA system was first demonstrated in the United States at Sandia National Laboratories in California. LIGA is a joint endeavor by Sandia and private industry. LIGA fabrication combines deep x-ray lithography and electroplating, rapidly producing intricate devices. [19] The LIGA system produces x-ray's for lithography by use of a synchrotron, this allows for extremely small critical dimension. The x-ray lithography allows both polarities of resist to be utilized. Common electroplated materials used in LIGA are copper and nickel. [20, 17]

# 2.2 Photolithography

Photolithography involves spin-coating photoresist onto a substrate, followed by a pre-bake, subsequent wavelength-critical exposure, development, and post-bake (optional). After the initial spin, a pre-bake removes much of the solvent required to keep the photoresist in a liquid form (necessary for spin coating). All photoresist has a range of possible thicknesses. [21, 22] The speed at which the resist is spun on determines the final thickness. The pre-bake leaves behind approximately 5% of the original solvent. Ultraviolet (UV) (350 nm-450 nm) or deep UV (193 nm-248 nm) exposure of the resist through a mask follows next using either a mercury lamp or excimer laser light. Masks used to patterning the photoresist in the UV/deep UV range are typically chrome-plated quartz plates (although other mask types, like Mylar, are used also). The substrate is next submerged in developer, leaving either the negative or positive of the exposed pattern. Depending on the subsequent processes the resist has to stand up to, occasionally a post bake is required. Finally, the exposed pattern is developed and either the positive or negative of the exposed mask image remains depending on the type of photoresist used. [23, 24, 25, 26]

#### 2.2.1 Photoresist Composition

Both polarities of optical resists, positive and negative, are composed of three components: a photoactive component (PAC), a resin and a solvent. How the resist components respond to radiation in the two separate polarities of photoresists is quite different. [26]

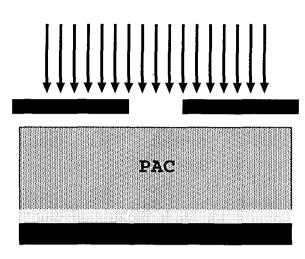

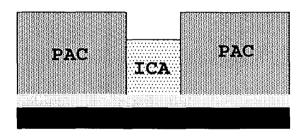

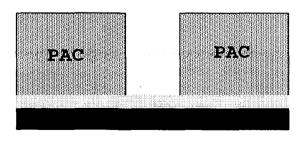

PAC, is the only component of photoresist that responds to light energy, encountered during exposure. The solvent and resin components remain unchanged throughout exposure. In **positive resists** the PAC photochemically decomposes into indene carboxylic acid (ICA). As more light energy is absorbed, more PAC converts to ICA, until all the underlying resist is converted to ICA. PAC positive optical resists (diazonaphthoquinones) are soluble in developer *but* dissolve slowly, their decomposed counterpart, ICA, is highly soluble in basic aqueous developers. In *negative* resists the PAC (bis-arylazide) is *soluble* in the organic solvent-based developer unless it has been irradiated. When exposed and developed, the PAC in negative resist forms nitrene, creating the cross linking between individual polymers.

Resin, in both resist polarities, dissolves rapidly in appropriate developers, even after experiencing suitable bake times and temperatures. Positive resists use novolac resin; negative resists use cyclized synthetic rubber resin. Resin gives the photoresist its "mechanical" properties: resistance to ion bombardment, resistance to chemical wet etches, and viscosity.

Solvent is designed to keep the photoresist in a liquid form until the resist is ready to be dispensed. Solvent in positive photoresist is propylene-glycolmonomethyl ether (PGME) or ethyl lactate or another similar compound is used. Negative resist is dissolved in an aromatic solvent to maintain a liquid form.

Positive developers are basic (pH > 7) aqueous solutions dissolving the previously mentioned ICA. Negative developers are organic solvents, requiring a nitrogen ambient to achieve best results. Positive developers are more environmentally and worker friendly. This makes positive resist attractive as public outcry for stricter environmental standards increases and employees demand safer working environments. Negative developers typically employ organic solvents toluene or xylene, both of which are known to cause birth defects.

# 2.2.2 Photoresist Type

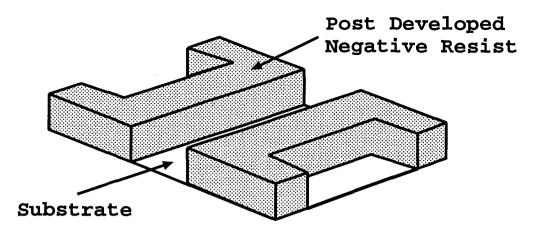

Optical photoresists have two polarities: positive or negative. Polarity is also the most general way to categorize photoresist. Figure 2.1 shows photoresist already spun onto a substrate, with an aligned chrome mask, awaiting exposure. This photoresist could be either positive or negative photoresist. With both resist types we start with a clean substrate, spin coat the photoresist at the appropriate spin speed (to achieve required film thickness), then expose with the appropriate wavelength. After the development stage, either the positive or negative patterns take form as seen in Figures 2.2 and 2.3, respectively. With the *positive* resist, shown in Figure 2.2, the "positive" image forms leaving solid photoresist remaining in the *unexposed* regions. For the *negative* resist, shown in Figure 2.3, the opposite exposed image forms, leaving photoresist only in the *exposed* regions; hence the naming convention.

## 2.2.2.1 Negative PR

Negative photoresist was the more popular choice for photolithography until device dimensions became small enough to become distorted by resist swelling during the development stage. During the developing phase the exposed negative photoresist crosslinks and absorbs a small amount of the organic developer, causing the photoresist pattern to swell.

Negative photoresist has superior adhesion to substrates, higher photosensitivity and is less costly. Adhesion is key for obvious reasons; if your photoresist does

Figure 2.1: Chrome mask aligned above unexposed photoresist.

Figure 2.2: Post Developed Positive Photoresist Image of Figure 2.1, after exposure and developing.

Figure 2.3: Post Developed Negative Photoresist Image of Figure 2.1, after exposure and developing.

not adhere properly to the substrate further, reproducible processing is doubtful. Positive resist often needs a costly pre-spin to promote adhesion. Since a pre-spin is omitted with negative resists, throughput is increased. Less energy is required to expose negative resists, reducing exposure times and improving throughput. Negative resists cost approximately a third the cost of positive resists.

Negative photoresist absorbs a portion of the solvent in the development stage, where crosslinking occurs. This absorbtion causes line width distortion for patterns less than 2 - 3  $\mu$ m, depending on the application. With increasingly smaller critical dimensions the development of deep-ultraviolet (DUV) negative resist is bringing back negative resists. [27, 28] Combine lower cost with increased throughput, lower power consumption due to negative resist having higher photosensitivity, reduced process complexity and better adhesion, the usefulness of negative resists becomes clear when printed image quality is not severely compromised.

#### 2.2.2.2 Positive PR

Positive photoresist was exclusively employed throughout industry by the late 90's and is still dominant due to its high resolution of small critical dimensions and the availability of relatively inexpensive i-Line (365 nm) and g-Line (436 nm) exposure sources. Positive photoresist is required when device critical dimensions fall below 2 - 3  $\mu$ m. [29, 26] This is primarily due to positive resists ability to withstand swelling in the development stage.

As stated earlier, both, i-Line and g-Line photoresists are composed of three components: a novolac resin, a solvent, and a PAC. Novolac resin provides the photoresist mechanical properties: thickness (e.g. 1.2  $\mu$ m thick or 7  $\mu$ m thick common for SPR 220), adhesion, flexibility, and is largely responsible for determining how well the resist will stand up to subsequent processing steps (e.g. ion implantation or etching). Solvent maintains the resist in a liquid state prior to photoresist spin coating. Diazonaphthoquinone PAC, used in i-line (365 nm) and g-line (436 nm) positive resist, is the only component chemically modified when irradiated.

The PAC has two purposes (see Figure 2.4). First, it acts as an *inhibitor*. When unexposed PAC is introduced to developer, the PAC withstands the developer, dissolving at a relatively slow rate. Second, PAC acts as an *enhancer*. The radiated PAC chemically decomposes to ICA. This chemical decomposition of PAC to ICA allows accelerated removal of the exposed resist in developer because ICA is highly soluble in basic (pH > 7) aqueous solutions.

Both exposed and unexposed areas in positive resist dissolve in a corresponding basic developer. General use resists have a dissolution rate ratio of exposed to unexposed resist of 100:1. Specialized resists have been manufactured to have dissolution ratio rates, exposed to unexposed, as good as 1000:1. With decreasing critical dimensions, PACs with a stronger resistance against dissolving are required.

UV LIGHT

Chrome Mask

Photoresist

Cu/Ti Seed Layer Substrate

Figure 2.4: PAC to ICA conversion: During exposure, Development, and Post Development

÷

Ion implantation, RIE, wet etching and electroplating also require thicker and/or more resistant resists. Current IC processing resists are typically 2  $\mu$ m to 3  $\mu$ m thick and need to withstand process steps (ion implantation, electroplating, etching) to protect underlying substrate regions.

After proper exposure, enough energy is absorbed to chemically decompose the PAC from the surface to the substrate into ICA. Once the pattern is exposed, it is developed, unless a post-bake is necessary. A post bake is used to drive out more solvent, helping to reduce standing wave patterns. Rate of pattern development and line width control is dictated primarily by developer concentration. The higher the concentration of developer, the faster ICA is removed. At first it may seem that faster development times are desirable due to increased throughput; however, the contrary is true. With the increased developer concentration the ICA rapidly dissolves but the PAC also dissolves more rapidly. Every resist and developer combination has a proper concentration of developer necessary to allow ICA dissolution to progress without detrimentally dissolving the PAC and causing unnecessary line width distortion.

Positive resists require corresponding developers, manufactured specifically for how the resist will most likely be used. General use positive resists, e.g. Shipley S1813, have concentrated developers requiring the process technician to dilute one part developer into three to five parts deionized water. The same resist will dissolve at different rates as developer concentration varies, yielding small variations in pattern thickness, sidewall angle among other details. To achieve best photolithography results environment and equipment set-up are considered. To determine the best operating conditions, sensitivity and contrast curves are needed. *Sensitivity* and *contrast* are important, descriptive features of optical photoresists. With knowledge of these features, excellent photoresist resolution can be achieved. Sensitivity, in positive resist, is the amount of light energy required to change the PAC to ICA. Higher sensitivity of a resist allows for shorter exposure times, yielding higher throughput. Sensitivity, as defined by Wolf, "the input energy required to cause a specified degree of chemical response in the resist, which results (after development), in the desired resist pattern." [30, 26]

$$\Phi \equiv Sensitivity Response \tag{2.1}$$

$$\Phi \equiv \frac{(number \ of \ photons) - (induced \ events)}{number \ of \ photons \ absorbed}$$

(2.2)

Resists are designed to respond to a specifically designed range of wavelengths. Some resist have a narrow range of wavelengths they decompose at; other resist, like multi-purpose photoresist respond to more than one range of wavelengths allowing for more than one source to be used. Resist sensitivity varies with different wavelengths and is therefore dependant on both the light source and the light sourceto-substrate spacing. Higher sensitivity is usually sought after. Two mercury light sources may require different exposure times due to spectral or intensity difference between the two sources.

Contrast  $(\gamma_p)$  (for positive photoresists) is in simplest terms this is the rate at which the appropriate resist decomposed or crosslinks, where  $\gamma$  is contrast. Higher contrast photoresists are most desirable. Resists with high  $\gamma$  result in the best resolution. Besides contrast aiding in resolution measurement, contrast can be used to calculate side wall angles and smallest printable feature size.

$$\gamma_p \equiv Contrast \tag{2.3}$$

$$\gamma_p \equiv \frac{1}{\log \frac{Dc}{Da}} \tag{2.4}$$

$$Dc \equiv Minimum \ Exposure \ Energy \ for \ 100\% \ Film \ Loss.$$

(2.5)

$$Do \equiv Maximum \ Exposure \ Energy \ for \ 0\% \ Film \ Loss.$$

(2.6)

Whether or not the contrast is good or poor depends on your process, only the process engineer can say if the contrast is good enough. However, as a general rule a higher number  $\gamma_p$  is desired, the closer to 1 the better. If Dc is far larger than Do, then a small contrast will result. Dc is the critical exposure dose required to completely remove the photoresist during development.

## 2.3 Electroplating

Electroplating (electrodeposition) is the process of producing a coating on a surface by electric current. When electroplating was first developed, direct current (DC) power supplies were utilized. Italian, Luigi V. Brugnatelli developed gold electroplating in 1805. Later in the 19th century copper plating was used extensively in Russia to plate religious statues. [31]

Electroplating is a reliable method of deposition. Devices requiring relatively thick films (on the order of microns), low temperature processing, large device areas, combined with uniform thickness require more effective deposition techniques than sputtering, evaporation, or chemical vapor deposition (CVD) and other high vacuum deposition techniques commonly used in the integrated circuit (IC) industry. Electroplating benefits include high throughput, simple, low temperature, non-vacuum

14

implementation and a wide range of possible deposition thicknesses: several hundred microns  $(10^{-6} \text{ m})$ , or as thin as several hundred Angstroms  $(10^{-10} \text{ m})$ , as device requirements dictate. [31]

In the past two decades, great attention has been paid to electroplating. [32] Although a wide variety of materials are deposited by electroplating, this section will focus entirely on copper electroplating used in the capture dot process (chapter 4). [33, 34] Copper is a low resistivity metal, highly prone to electromigration in silicon, an issue overcome by current IC manufacturers. [26] Electromigration is the movement of conducting atoms as a result of momentum transfer from current-carrying electrons. Printed circuit board and IC manufacturers have found that through-hole plating, deep trench filling and high-throughput interconnects for microprocessors can be effectively produced by electroplating. High-throughput manufacturing of electroplating allows for reduced device costs. An excellent source of information on copper electroplating can be found through Think and Tinker, Ltd.'s website: www.thinktink.com.

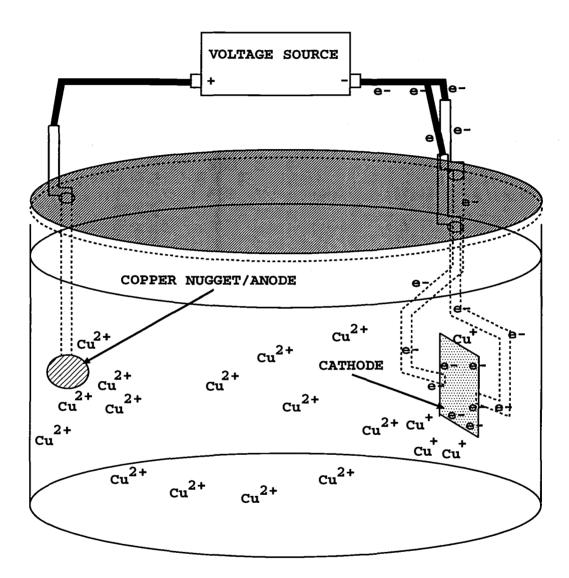

#### 2.3.1 Electroplating Set-Up

Figure 2.5 shows a basic acid bath copper electroplating setup: copper acid bath, anode, cathode, and a direct current (DC) power supply. The anode and cathode are submerged in the plating bath solution, a small voltage difference is applied across them. The positive terminal of the DC supply is connected to the solid copper anode, allowing a continuous supply of  $Cu^{2+}$  ions. The negative terminal of the DC supply is connected to the cathode, supplying electrons. The cathode is the conducting part onto which electroplating occurs.

The copper anode is not required for electroplating to proceed; however, without it the acid bath becomes depleted of copper ions. To maintain bath properties,

Figure 2.5: Basic Electroplating Set-Up

ŧ

the copper anode, a copper nugget 99.5% copper with 0.5% phosphorous, should be viewed as a requirement. The anode provides a continual supply of copper to be oxidized during electroplating. Reduction of copper occurs at the cathode, resulting in plating out of copper on all parts of the conducting sample, exposed directly to the electroplating solution.

As knowledge of electroplating chemistry progresses, so does the technology used in current, modern systems. Modern acid bath electroplating systems contain a cathode, anode, power supply, air/nitrogen sparger, dam, and a plating solution with proper additives, in a container with carefully designed dimensions. Complex bath chemistry (additives) and complex pulse plating methods further the usefulness of electroplating.

### 2.3.2 Current Density

Current density (amperes per unit area) determines the deposition rate at the cathode. When the seed layer (a thin, conducting film) on the cathode is uniform in thickness, the current density will also be uniform across the substrate and uniform deposition is achieved. [35] However, more commonly, the current density varies across the cathode which in turn varies the rate of deposition across the substrate (cathode). Areas of the cathode with greater current density plate more quickly than areas of lower current density, as shown in Figure 2.6.

Anything that goes into the plating bath affects the current density. For example: cell design, anode-to-cathode spacing, and additives all play important roles in current density distribution. It has been established by the printed circuit board (PCB) industry that cell geometry design, anode-to-cathode surface area ratio, air/nitrogen sparging (gentle bath agitation to break up the potential at the cathode) and anode replacement affect current density the greatest as first order

Figure 2.6: Effects of electroplating on a non-uniform seed layer.

effects. [36, 37] The acid bath chemistry (copper sulfate, sulfuric acid and chloride concentration) is a second order effect in current density. [38] Finally, additives are considered to play an even smaller role on effective current density, but even this third order effect requires great attention. Effects of current density distribution, relating to cell geometry and chemistry will be further investigated in Chapter 4.

Film quality is the final product and ultimately, if the quality is poor, changes need to be made to ensure a quality film. However, if film quality is poor, before going to costly thin-film analysis, like scanning electron microscopy (SEM), often examining how the cathode diffusion layer is affected by changes made to the electroplating system will yield valuable information even before electrodeposited films are made.

The cathode diffusion layer controls plating speed and uniformity, has low metal content, and is water rich. The cathode diffusion layer is a 10  $\mu$ m to 200  $\mu$ m thick region surrounding the cathode. The diffusion layer thickness is controlled by solution agitation, temperature, and metal concentration. With agitation or increased agitation the diffusion layer is decreased. As the diffusion layer decreases,

plating time is reduced. [39] Bath temperature affects several things, often the most obvious being the additives, since at higher temperature organic molecules can dissolve into smaller molecules. However, temperature also affects the convection-diffusion transport of ions (copper and chloride ions are used). [40] As the bulk (in solution) metal concentration decreases, the limiting current decreases, reducing cathode efficiency and slowing deposition rate. [41]

#### 2.3.3 Plating Types

DC electroplating has been around since the early 1810's and has remained acceptable for a wide range of plating applications. However, in recent years pulsed and reverse-pulsed plating has become a necessity for even plating of surfaces with small and/or deep feature sizes. [42, 43, 44] In 1991 IBM published the first demonstration of dual-damascene processing for IC's. Since this time, the IC industry has invested great time and resources into investigating the benefits of pulse plating current schemes. When examining different current plating schemes, Faraday's Law, current efficiency, and the cathode diffusion layer are given greater attention to discover the most appropriate current for a given process.

Faraday's law is a way of counting electrons. 96,400 amp-seconds = 1 gm of electrons. [45] The Electrochemisty Encyclopedia describes Faraday's Law as: "(1) In any electrolytic process the amount of chemical change produced is proportional of the total amount of electrical charge passed through the cell. (2) The mass of the chemicals changed is proportional to the chemicals' equivalent weight. The proportionality constant being the Faraday Number." The Faraday Number gives the amount of electrical charge needed to change one gram-equivalent of substance by electrochemical reaction. [46]

Current efficiency is the ratio between the actual amount of metal deposited to that expected theoretically from Faraday's law. [46] The current determines the quantity or amount of copper plated. During copper electroplating the following processes occurs at the anode and cathode:

$$Anode: Cu \to Cu^{2+} + 2e^{-} \tag{2.7}$$

$$Cathode: Cu^{2+} + 2e^{-} \to Cu^{o} \tag{2.8}$$

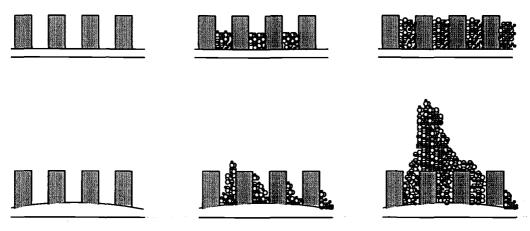

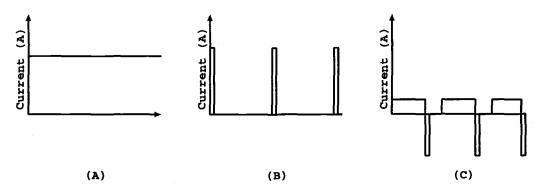

Electroplating systems employ one of several types of plating current schemes like: direct current (DC), pulse plating (PP), periodic reverse (PR) or pulsed periodic reverse (PPR) (shown in Figure 2.7). The type of plating current used depends on the application and material being deposited. In PCB copper through-hole plating, pulsed periodic reverse plating has had the greatest success for adequate filling of through holes. For damascene or dual-damascene structures, pulse plating is best for patterns with a seed layer while DC plating is best for non-critical plating. [47, 45]

# 2.3.3.1 Direct Current Plating

DC, direct current, plating has been used since electroplating was first developed. In DC plating the applied voltage remains constant throughout the plating process. In copper sulfate baths where additives are utilized, the current density (approximately 20 amps per square foot (ASF)) should remain low for optimal (uniformly thick, low stress, low porosity) film characteristics.

Initially, current density starts out high and consequently, the plating deposition rate also starts out high. However, as plating progresses, the total area of the

Figure 2.7: Plating Current Schemes: (A) Direct Current (DC), (B) Periodic Pulse (PP), (C) Periodic Pulse Reverse (PPR). All plots are current versus time.

cathode metal layer increases, decreasing the overall resistance, as shown below in equation 2.9. This decrease in resistance drives the current up (equation 2.10).

$$R \equiv \rho(L/A) \tag{2.9}$$

$$I \equiv V/R \equiv V/[\rho(L/A)] \tag{2.10}$$

R = resistance (cathode resistance), copper  $\rho = 1.77(10^{-8} \text{ ohm*meter})$ , L = length (total length of coils), A = area (cross-sectional area of coil trace), I = current, V = voltage (applied cathode-to-anode voltage)

With higher current, higher current density is seen in areas of low resistance and areas with high electric field like corners and edges. Any non-uniformity in the seed layer will experience an avalanche effect: sections with the least resistance and highest electric fields have greater deposition rates. This causes even larger electric fields which causes plating to occur more and more rapidly at that section of high electric field intensity. These areas, plating at a rapid rate, monopolize the reduced number of cupric ions in the diffusion layer, not allowing nearby areas to plate. The result is large dendrites (overplating growth) of copper surrounded by largely unplated sections. Nonuniform plating in DC plating can be reduced by the use of levellers (suppressors), an organic that suppresses currents. However, even levellers can not be expected to give uniform deposits with sub-micron patterns or with high aspect ratios. [45]

## 2.3.3.2 Pulse Plating

This section looks closely at pulse plating and periodic reverse plating, shown in Figure 2.7. [48, 49] The positive sections of the pulse are cathodic amp minutes, the negative pulses are anodic pulses. To plate, the cathode receives more cathodic amp minutes than anodic amp minutes; otherwise, the underlying copper seed layer will be removed.

During pulse electroplating deposition, crystal formation greatly depends on two processes: the rate of nucleation and grain growth. [50] During electroplating higher nucleation rate and slow grain growth are desirable for finer grained structures. With finer grain structure the copper has a lower porosity, higher tensile strength, higher elongation, and reduced stress.

The duty cycle of the pulse is the on time  $(t_{on})$  divided by the on plus off time  $(t_{off})$ . It is recommended that for seed layer plating, the duty cycle be close to 10%. [20] To reduce grain size, reduce the duty cycle; lower duty cycle has finer grains. However, copper can recrystalize into larger grains if the duty cycle drops below 10%. Grain size control is important: tensile strength is inversely proportional to the square root of the grain size. Typically, elongation is inversely proportional to grain size. Small grains pack together better and reduce porosity and stress. [45, 31] Nucleation, the initial stage in a phase transformation, is increased with increased current density. [51] Pulsing increases the probability of new grains forming. More new grains form at high current density. This high current density increases concentration of adatoms (electrodeposited copper atoms) on the surface and leads to more nucleation sites.

In pulse plating deposition, control of  $t_{on}$  and  $t_{off}$  yields control over pulse length, forward current, reverse current, time between pulses, peak current and average current. By varying these parameters, the cathodic overpotential (the deviation of an electrode potential from its equilibrium value required to produce a net flow of current across an electrode/solution interface) is controlled.

With cathodic overpotential control, the nucleation rate and activation energy of nucleation is controlled. High cathodic overpotential yields a low activation energy, increasing nuclei formation. The peak current and pulse length establish the number of ions discharged into the plating bath during a pulse. Higher deposition rates deplete the ion concentration near the cathode, so slower deposition rates are more desirable for smooth, uniform electrodepositions.

The time between pulses controls the repetition rate but this also determines the time for the  $Cu^{2+}$  ions to migrate toward the electrode (cathode).  $Cu^{2+}$  ions are continually introduced into the electroplating bath from the anode, the copper nugget.

#### 2.3.4 Electroplating Bath Properties

There are three common types of electroplating baths: cyanide, pyrophosphate, and acidic. [50] Acid baths and cyanide baths are the two plating bath types found most frequently in industry. Low cost, low toxicity and high deposition rates make acidic baths the most widely implemented copper electroplating bath. This section reviews the electroplating acid baths.

# 2.3.4.1 Plating Solution

In all copper electroplating solutions copper ions are available to be deposited. Typical acidic solutions contain copper sulfate, sulfuric acid and deionized water. [26, 50]

In an acid bath the following reactions take place:

$$CuSO_{4}(s) + H_{2}SO_{4}(aq) + 2H_{2}O(l) \rightarrow$$

$$Cu^{2+}(aq) + 2SO4^{2-}(aq) + 2H_{3}O^{+}(aq)$$

(2.11)

$$Cu^{2+} + e^- \to Cu^+ \tag{2.12}$$

$$Cu^+ + e^- \to Cu^0 \tag{2.13}$$

$$2Cu^{+} \rightarrow Cu^{2+} + Cu^{0}$$

(competing reaction)

$$(2.14)$$

When a voltage is applied between the anode and cathode, an electric field is established. The field lines begin at the positive charge, which is the anode, and end at the negative charge at the cathode. The  $Cu^{2+}$  ions (where the electric field starts) in the bath are attracted to the cathode (where the electric field ends). The  $Cu^{2+}$ ions are reduced by a single electron to a  $Cu^{+}$  ion (Equation 2.12). Two reactions can occur to this  $Cu^{+}$  ion. It can be reduced again to elemental copper (Equation 2.13) by another electron from the cathode and adhere to the cathode. This is the desired reaction. Otherwise, two  $Cu^+$  ions can combine to form elemental copper and the more favorable oxidation state,  $Cu^{2+}$ , this being the less desirable reaction.

## 2.3.4.2 Bath Dimensions

Proper spacing and positioning between anode and cathode is critical in copper electroplating. There are also minimum dimensions that are crucial for repeatable, manufacturable electroplating. The overall size of the plating bath depends on what tools are needed in the plating bath.

Common to plating designs are: air/N2 sparger (supplying many small bubbles to break up potential at cathode surface), heating elements (to maintain bath temperature), dams (to direct ion flow to cathode), and often multiple anodes and cathodes. In general, plating baths should be no less than 10 inches wide. After the substrate (i.e. cathode) is submerged into the final position, the substrate should be four inches from the bottom of the plating cell, have at least 1.5 inches of clearance on either side and should remain three inches away from other substrates if multiple substrates are plated simultaneously.

#### 2.3.4.3 Organic Additives

The most popular copper electroplating solution, the acid bath, is utilized for a variety of uses, from electroforming, to PCBs, to delicate interconnects on ICs. Surprisingly, acid bath electroplating chemistry changes little for this wide range of applications. However, much attention is granted to the small amounts of organic additives. [52, 53] Critical in electroplating are additive type and size. [37, 54] There are three possible organic additives: Levelers (brighteners), suppressors (carrier), accelerators, and one inorganic additive: chloride ion. [45] Levelers and suppressors slow down the electroplating by decreasing the current density. Levelers slow down plating by replacing accelerators as trenches are filled. Suppressors reduce current density at areas of unlevel copper deposition, where overplating has occurred. Accelerators increase current density; therefore, accelerating electroplating. Where accelerators accumulate, for example at the bottom of trenches or lithography patterns, absorption occurs, increasing current density and plating rate.

The amount of accelerator molecules needed varies greatly with the plating requirements. When through-hole plating, the bath will have an increased level of accelerators, allowing more even plating in the holes by increasing the current density and distributing the potential more evenly throughout the hole. Superfilling (filling of deep/narrow dimensions) also requires more accelerator molecules present. [55] Accelerators are most likely consumed by film incorporation. However, since superfilling is a recent requirement by IC manufacturers, it may be years before it will be known whether the accelerators are consumed by film incorporation or a chemical reaction on going in trenches, due to proprietary processes being highly guarded by industry.

Levelers and suppressors are relatively large organic molecules/polymers that slow the plating process, breaking up areas of high potential. This is useful because there are always small differences in the local resistance of the seed layer, changing the potential at different points on the electroplated seed layer. The areas of higher potential have high current density and as a result plate thicker and faster which can be disastrous, ruining the electroplated layer and the fabricated device. Brighteners are smaller molecules that accelerate plating in through-holes on PCB boards or in deep trenches. When balanced properly, levelers and brighteners allow nanostructures to be plated successfully. However, it is not just a matter of finding the right amount and size of organic additives that make an electroplating solution successful.

The organic additives' size and structure vary with the pH of the electroplating bath. [51] For example an organic additive, Zolotukhim, is a positive ion in an acid bath, has one negative charge when the bath is neutral, and has two negative charges in an alkaline bath, making the bath appear dark blue. The organic size relates closely to the grain size as plating occurs. Higher bath temperatures also cause variations in the organic size. Organics have an increased dissociation with higher temperatures, increasing  $Cu^{2+}$  concentration. This increased  $Cu^{2+}$  level reduces the cathodic overpotential forming larger grains. Once the electroplating bath solution, pH, temperature, and pulse parameters are chosen, the plating bath should never have to be replaced if taken care of properly. [56]

Great care in organic monitoring is critical for proper electroplating. [57, 58] As mentioned earlier in this section, superfilling technology depends on the organic additives levelers and accelerators. However, accelerators are consumed or decompose over short periods of time. SPS, an accelerator additive often used in superfilling plating baths, decomposes in 12 hours into smaller organics that impede plating. [53]

An array of organic molecules are used as additives in electroplating: carboxylic acid, tartaric acid, citric acid, malonic acid, and hydroxide groups. Organics specific to sub-micron trench filling issues for high aspect ratios, with seed layers of PVD copper, have been investigated in recent years with much success. [59, 60, 11] Chemists have identified multiple accelerator/suppressor/leveler specific combinations that have been successfully demonstrated. [52]

Employees at Dynatronix have shown that plating utilizing periodic reverse pulse plating (see Figure 2.7 c) without additives can be as effective as DC plating with organic additives. [61] They operate square wave pulses at 1 MHz or higher to take the place of the additives that allow for a high throw power. Plating is done at 100 to 120 ASF. It is beneficial to plate without additives since additives are costly and waste removal is more simple.

## 3. DEPOSITION, PROCESS AND CHARACTERIZATION TOOLS

This section covers the processing equipment utilized to create the capture dots and transparent thin-film heaters. A general overview is given of the process tools and the specific models used are covered. These process tools are used during typical micro-electro-mechanical-systems (MEMS) and microtechnology-energy and chemical-systems (MECS) development.

The high vacuum systems have two pumps. The first pump (mechanical pump) takes the process chamber from atmosphere to low vacuum pressures. The second pump (diffusion pump) takes the process chamber from low vacuum pressures to high vacuum pressures. The diffusion pump input must see pressures in low vacuum ranges to operate; therefore, after the mechanical pump takes the process chamber from atmosphere to low vacuum pressures the mechanical pump (s) back the diffusion pump(s) to maintain the process chamber at high vacuum levels.

#### 3.1 Process Equipment Measurement Tools

This section discusses the measurement tools used in many vacuum systems. All the vacuum equipment used at Oregon State University use one of all of these tools. The usefulness and limitations are explored to allow the reader to better understand the process equipment and procedure used.

### 3.1.1 Thermocouple Gauge

Thermocouple (TC) gauges are useful for measuring low pressure ranges seen in the process chamber when the mechanical fore pump(s) take the process chamber from atmospheric pressure (760 Torr) to lower pressure. Thermocouple gauges have the ability to give a reasonable measurement of the pressure, in the  $10-10^{-3}$  torr range. The thermocouple gauge gives an accurate reading within 10% of the actual pressure. This accuracy is only valid for the specific gas for which the gauge was calibrated for (usually N<sub>2</sub>). The gauge works by measuring the temperature change of a thin tungsten filament with a thermocouple. As pressure decreases, the filament temperature rises due to thermal conductivity of the gas decreasing with decreasing pressure. The TC gauge is a simple, accurate and effective gauge. [26]

## 3.1.2 Ionization Gauge

The Bayard-Alpert ionization gauge, more commonly called an "ion gauge", can measure pressure from  $10^{-3}$  to  $10^{-8}$  torr. The more user friendly model of the ion gauge uses a single thoriated tungsten filament. Thoriated tungsten has a lower work function than non-thoriated and can withstand failure when brought to atmosphere from low pressures. When vacuum equipment is not completely automated, often the ion gauge status (on/off) is regulated and monitored by the tool user. The thoriated filament is more forgiving to forgetful process tool users. An ionization gauge costs approximately \$100 U.S. dollars.

#### 3.1.3 Crystal Monitor

Many of the vacuum deposition equipment systems are outfitted with a crystal monitor to monitor the deposition rate of the material. The crystal monitor utilizes a thin, flat, half inch diameter thin-film gold deposited on quartz crystal oscillating at 5 MHz in a stainless steel holder. Using the density and impedance of the evaporated material, the monitor system calculates the deposition thickness from the change in the crystal oscillator frequency with mass of material deposited onto the crystal face. Crystal monitors common in evaporation and sputter deposition system are best suited for metal depositions, although they can be used for semiconducting and insulating materials, also. Film deposition rates are measured as the thickness of material deposited in an area per second,  $(\text{\AA}/(\text{cm}^{2*}\text{s}))$ .

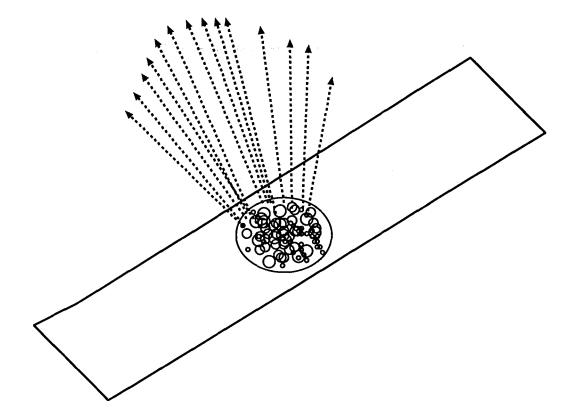

## 3.2 Evaporation

In evaporation, a thin-film deposition method, a crucible holder containing the material to be deposited is slowly heated, under mid or high vacuum conditions, until a controlled rate of the material deposited on the crystal and subsequently the substrate is achieved, see Figure 3.1. The deposition rate of the material is monitored by a crystal monitor (section 3.1.3). Evaporation is a point source deposition method. Point source deposition is a deposition that originates from a single source, radiating out, similar to a light bulb. As the crucible is heated, the material melts or sublimes (subliming is where the atoms of the material come directly from the material as a solid, without first melting), then adhere to the substrate.

Evaporation is a line-of-sight process. The evaporated material atoms adhere to the first item that interrupt the evaporated atoms path. We desire the substrate to be the end of the path, but at higher pressures more particles are present in the evacuated chamber, if the atom contact these particles the evaporated atoms will either not make it to the substrate or will incorporate some of these particles as they deposit on the substrate as a thin-film. Contaminates in deposited films and increased particle count come from: impurities in the evaporated source material, the source crucible, background gases and/or particles from previous evaporations. As more particles are evacuated the pressure reduces. The lower the pressure, the less evaporated material will be lost to particle collisions. This can also be explained in terms of the "mean free path".

Figure 3.1: Crucible holder with heated material depositing non-uniformly as a Cosine distribution.

ť

Figure 3.2: Two boxes representing high and low pressure. As particles are evacuated through the pumps, the pressure lowers and the mean free path increase.

The evaporated material has a longer mean free path length at lower pressures. The mean free path is a measure of how far (distance from material origin to collision) the atoms will travel before they collide with another particle, see Figure 3.2. The lower the pressure, the longer the mean free path and hence the fewer particles are present. Evaporation takes place in the mid-pressure range,  $10^{-6}$  torr, or lower.

Evaporated metals deposit as individual atoms or groups of atoms. NiCr (an alloy of 80% Ni, 20% Cr) atoms, like other alloys, are less tightly bound than pure metals or metal oxides. The nickel and chrome tend to evaporate almost completely independent of each other. These metals enter the vapor phase acting like "pure" metals, making evaporation less ideal for alloys than other vacuum deposition methods. Another limitation of evaporation is its has poor step coverage due to the line-of-site deposition. Poor step coverage is usually undesirable; however, is a necessity for lift-off.

At Oregon State University the Veeco evaporator system has a diffusion pump backed by a mechanical pump. The evaporation chamber is brought down from atmosphere (760 torr) to the mTorr range with the mechanical pump. The diffusion pump (backed by the mechanical pump) brings the chamber down from the mTorr range to the low  $\mu$ Torr range. Once the process chamber falls into low to mid- $\mu$ Torr range, the boat or crucible holding the material is heated and thermal evaporation is achieved. The pressures are monitored by a thermocouple and ionization gauge. Thin film deposition rates are monitored by a crystal monitor.

## 3.3 Electroplating

This section explores the electroplating set-up for copper electrodeposition, specific to the capture dot manufacturing (a more general discussion of electroplating can be found in section 2.3). Electroplating is a powerful deposition technique, providing excellent, uniform coverage to areas with large deposit area, concomitantly providing high quality films with high throughput. Many metals, alloys and transparent conductive oxides (TCO's) are deposited by electro- or electroless- plating. However, only copper electrodeposition will be detailed here.

## 3.3.1 Electroplating Set-Up

The plating set-up here follows the same requirements specified in chapter two. The largest print size of the capture dot photolithography layers is approximately 1 inch by 1.25 inches. A nine inch round (2.2 liter volume) Tupperware polyethylene container houses our electroplating solution, with proper anode/cathode placement. To remove undesired organics, the tupperware container is leached in 10% sulfuric acid solution, for more than two hours prior to use. Leaching is an acid soak: 10% sulfuric acid, 90% de-ionized water. [As with diluting all acids, add the acid to the water, NOT the other way around.]

To promote globally uniform depositions, a bubbler (interchangeable with a  $N_2$  sparger) and dam are included in the deposition design. Global uniformity, i.e. long range uniformity, is a measure of how uniform the deposition is across the entire substrate. The bubbler is a  $\frac{1}{4}$ " PVC tube. At half inch intervals  $\frac{1}{8}$  holes are drilled through the PVC tube, the end of the tube is capped. This PVC tube is submerged in the electroplating solution after leaching. The PVC tube runs one inch from the bottom of the tupperware container, out of the plating bath to a small fish tank aeration pump. The small fish tank aeration pump provides gentle air agitation. Air agitation, during plating, breaks up areas of high potential in front of the cathode, improving uniformity across the entire wafer area. The dam (Figure 3.3) has a two inch circular hole cut through it, centered between the cathode and

Figure 3.3: Dam, separating anode and cathode. The hole in the dam acts as a way of controlling the flow of ions.

anode, to provide a more directional flow for the cupric ions to flow through from the anode to the cathode.

All items which will contact the electroplating solution are leached for a minimum of four hours to reduce contamination. Once a successful electroplating solution has been developed, great care must be taken to ensure the electroplating solution is not compromised by foreign organics. As a final preventative measure to reduce foreign organics, an hour long pre-plating is completed to remove any particles that may have been introduced into the plating solution during development. If the electroplating bath has sat for any considerable length of time, sludge particles from the anode will enter the plating solution and pre-plating is needed to remove this. The great caution to reduce foreign organics will become clearer as the importance of organic additives is explored.

Foreign organics ruin electroplating baths and degrade film quality by introducing undesired particles into the depositing film and produce less ideal films; therefore steps are taken to remove particles before they enter the plating solution, such as leaching. Photoresist, an organic material, is often a culprit for introducing foreign organics into the electroplating bath. To reduce the chance of the photoresist organic polymer from becoming incorporated into the electroplating bath, the patterned photoresist is put back underneath the UV lamp and re-exposed the original time it was exposed prior to developing. If re-exposing films is not desired, re-baking an additional minute or so will yield a similar result. The extra exposure or bake makes more solvent drive out of the patterned photoresist, reducing the probability of organics inadvertently becoming incorporated to the plating solution.

#### 3.3.2 Electroplating Solution

A general purpose acid bath solution (see Table 1) is used in combination with an organic additive solution developed for MEMS circuits, similar to the capture dots. Lea Ronal, an organic additive with two classes of organics, levelers (also referred to as brighteners) and carriers, is used to control film growth. During plating, the recommended resistance,  $R = \frac{V}{I}$ , should remain between 0.015 and 0.025 ohms during operation. For pulse plating the average current and voltage are used. Our present acid bath solution has a resistance of approximately 140 ohms. The high resistance measured could be due a number of reasons; however, the method of measuring the electroplating bath was probably not accurate. To decrease the resistance the current density must increase. We maintain a low voltage, since we are plating onto a seed layer, burning the seed layer becomes more of a problem as the voltage is increased.

There are many ways to increase the current density. Additional organic additives can increase the current density; so can the inorganic additive. Chlorine (the inorganic additive), is necessary for high current densities since it aids in reducing the dendrite (tree-like) deposits. Decreasing the copper sulfate concentration decreases the resistance. More importantly as the sulfuric acid concentration increases a dramatic decrease in the resistance is witnessed. Had it been easy to change solution, increasing the sulfuric acid concentration and organic additives would have been investigated.

To determine the optimum plating time and current, we can use the follow equations. Acid baths employing Lea Ronal plate 28  $\mu$ m of copper an hour, at 20 ASF.

Electroplating time, t, assumes 5  $\mu$ m thick plated coils.

$$t = [5\mu m/(28\mu m/hr)]*60 min./hr.= 10.71 minutes$$

Plating current depends on the area of the device. It is reasonable to estimate the capture dot area by their pad areas:

Area = Length \* Width =

$$8e^{-6}$$

m<sup>2</sup>

There are 18 coil-pad combinations, for a total area of:

Total Area =

$$18 * 8e^{-6} m^2 = 0.000144 m^2$$

Plating occurs at 20 ASF, amps per foot. Totally area is converted to inches and current calculated:

$$\frac{20A}{144in^2}$$

\*  $\frac{0.2232in}{1}$  = 0.031 A<sup>2</sup> = Current

| Chemical   | DI H <sub>2</sub> O | Copper Sulfate Crystals | $H_2SO_4$ | $H_2SO_4$ | HCl   | Lea Ronal Copper |

|------------|---------------------|-------------------------|-----------|-----------|-------|------------------|

|            |                     | $CuSO_4 5H_2O$          | 98%       | 35%       | 35%   | Gleam PCM+       |

| Volume     | Liters              | Grams                   | Liters    | Liters    | ml    | ml               |

| 100 Liters | 70.9                | 7500                    |           | 28.6      | 16.6  | 500              |

| 2 Liters   | 1.786               | 150                     | 0.204     |           | 0.332 | 10               |

----

Ą

Table 3.1: Basic Copper Electroplating Solution.

## 3.3.3 Plating Void of Additives

Through out the development of the electroplating system, at Oregon State University, effects on deposited film uniformity have been examined using acid baths without organic additives. In the early stages of process development a DC supply without organic additives would not allow for even plating. Dendrite (striated deposited) areas of severe overgrowth, of copper were electroplated as thick as 73 microns, leaving areas on the cathode substrate with coils left unplated. The best copper electro-deposited films (using the aforementioned bath without the additives) are so non-uniform passivation is unachievable. These severely non-uniform films are due to non-uniform current density (from a non-uniform seed layer) balanced only with the inorganic Chloride additive. Areas of higher current density, furthering the imbalance because these areas with thicker layers of copper have increased current density, therefore attracting more cupric ions and increasing deposition in these areas exclusively.