#### AN ABSTRACT OF THE THESIS OF

<u>Kangmin Hu</u> for the degree of <u>Doctor of Philosophy</u> in <u>Electrical and Computer Engineering</u> presented on <u>June 8, 2011</u>.

Title: Analysis and Design on Low-Power Multi-Gb/s Serial Links.

Abstract approved:

#### Patrick Y. Chiang

High speed serial links are critical components for addressing the growing demand for I/O bandwidth in next-generation computing applications, such as many-core systems, backplane and optical data communications. Due to continued process scaling and circuit innovations, today's CMOS serial link transceivers can achieve tens of Gb/s per pin. However, most of their reported power efficiency improves much slower than the rise of data rate. Therefore, aggregate I/O power is increasing and will exceed the power budget if the trend for more off-chip bandwidth is sustained.

In this work, a system level statistical analysis of serial links is first described, and compares the link performance of Non-Return-to-Zero (2-PAM) with higher-order modulation (duobinary) signaling schemes. This method enables fast and accurate BER distribution simulation of serial link transceivers that include channel and circuit imperfections, such as finite pulse rise/fall time, duty cycle variation, and both receiver and transmitter forwarded-clock jitter.

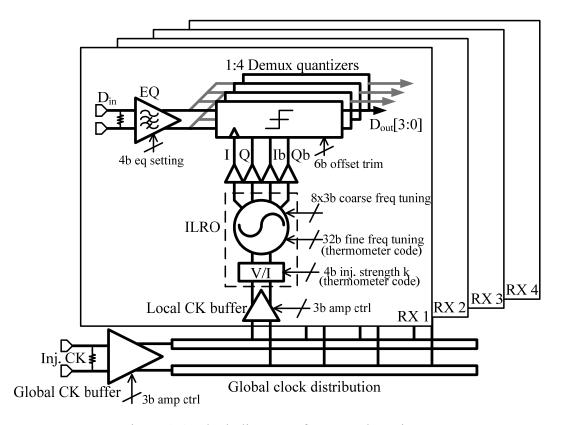

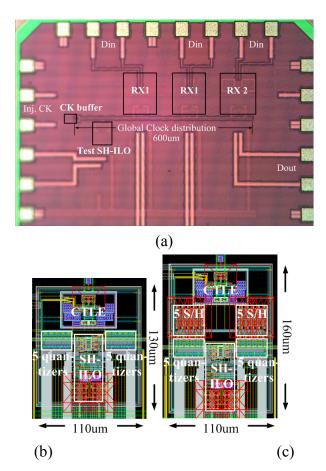

Second, in order to address link power efficiency, two test chips have been implemented. The first one describes a quad-lane, 6.4-7.2 Gb/s serial link receiver prototype using a forwarded clock architecture. A novel phase deskew scheme using injection-locked ring oscillators (ILRO) is proposed that achieves greater than one UI of phase shift for multiple clock phases, eliminating phase rotation and interpolation required in conventional architectures. Each receiver, optimized for power efficiency, consists of a low-power linear equalizer, four offset-cancelled quantizers for 1:4 demultiplexing, and an injection-locked ring oscillator coupled to a low-voltage swing, global clock distribution. Measurement results show a 6.4-7.2Gb/s data rate with BER < 10<sup>-12</sup> across 14 cm of PCB, and an 8Gb/s data rate through 4cm of PCB. Designed in a 1.2V, 90nm CMOS process, the ILRO achieves a wide tuning range from 1.6-2.6GHz. The total area of each receiver is 0.0174mm², resulting in a measured power efficiency of 0.6mW/Gb/s.

Improving upon the first test chip, a second test chip for 8Gb/s forwarded clock serial link receivers exploits a low-power super-harmonic injection-locked ring oscillator for symmetric multi-phase local clock generation and deskewing. Further power reduction is achieved by designing most of the receiver circuits in the near-threshold region (0.6V supply), with the exception of only the global clock buffer, test buffers and synthesized digital test circuits at nominal 1V supply. At the architectural level, a 1:10 direct demultiplexing rate is chosen to achieve low supply operation by exploiting high-parallelism. Fabricated in 65nm CMOS technology, two receiver prototypes are integrated in this test chip, one without and the other with front-end

boot-strapped S/Hs. Including the amortized power of global clock distribution, the proposed serial link receivers consume 1.3mW and 2mW respectively at 8Gb/s input data rate, achieving a power efficiency of 0.163mW/Gb/s and 0.25mW/Gb/s. Measurement results show both receivers achieve BER  $< 10^{-12}$  across a 20-cm FR4 PCB channel.

©Copyright by Kangmin Hu June 8, 2011 All Rights Reserved

### Analysis and Design on Low-Power Multi-Gb/s Serial Links

by Kangmin Hu

#### A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented June 8, 2011 Commencement June 2012

| <u>Doctor of Philosophy</u> thesis of <u>Kangmin Hu</u> presented on <u>June 8, 2011</u>                                                                                                      |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                               |  |

| APPROVED:                                                                                                                                                                                     |  |

|                                                                                                                                                                                               |  |

| Major Professor, representing Electrical and Computer Engineering                                                                                                                             |  |

|                                                                                                                                                                                               |  |

| Director of the School of Electrical Engineering and Computer Science                                                                                                                         |  |

|                                                                                                                                                                                               |  |

| Dean of the Graduate School                                                                                                                                                                   |  |

| Dean of the Graduate School                                                                                                                                                                   |  |

|                                                                                                                                                                                               |  |

|                                                                                                                                                                                               |  |

|                                                                                                                                                                                               |  |

| I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my thesis to any reader upon request. |  |

|                                                                                                                                                                                               |  |

| Kangmin Hu, Author                                                                                                                                                                            |  |

#### ACKNOWLEDGEMENTS

This Ph.D. work would never ever be accomplished without kind guidance, generous help and significant collaboration by my advisors, colleagues, friends, family and sponsors.

First and foremost, I would like to express my deepest gratitude to Professor Patrick Yin Chiang, my doctoral advisor. It was his foreseeing vision, broad knowledge and great encouragement that led me to the world of serial link design and eventually the ideas in this thesis. I would not forget the days we discussed about papers, worked closely, and drew layout overnight together. I was touched by an energetic young professor with such strong desire for academic achievements. I am deeply grateful to him for numerous advice and guidance throughout my research work.

Secondly, I would like to thank Professor Pavan Kumar Hanumolu for his advice on a collaborated Intel project as well as his teaching of analog circuit and PLL design. I also thank Professor Huaping Liu and Professor Thinh Nguyen for serving on my doctoral committee and being readers for this dissertation. I am indebted to Professor John Nairn for taking the time to serve as graduate council representative in my committee.

I would like to thank Professor Sam Palermo of Texas A&M University for his valuable advice on joint SRC project. His insights into serial link design helped me to focus on this research. I am deeply indebted to Professor Zhiliang Hong of Fudan

University, my master's advisor, for introducing me to the analog circuit design and for sponsoring of the forthcoming tapeout for our group. I also thank Professor Brian Otis and Dr. Julie Hu of University of Washington for their advice on tapeout and joint testing. I am extremely grateful to Dr. Frank O'Mahony, Dr. Ganesh Balamurugan and Bryan Casper of Intel's Circuit Research Laboratory for their advice on serial link design used in this thesis and for the permission to access their measurement equipment. I would like to thank Brent Close, Charlie Zhong and Freeman Zhong of LSI Corporation for generous support of lab and equipment time. I also thank Larry Wu, Yu Zhong, Dr. Leon Pu and Dr. Howard Yang of Montage Technology for the guidance and help on developing the system simulator of serial link when I was interned there.

I have been much honored to work in a research group with so many extraordinary students. I am deeply grateful for the help and collaboration of Jingguang Wang, Tao Jiang, Changhui Hu, Jacob Postman, Joe Crop, Rui Bai, Robert Pawlwski, Jiao Cheng, Lingli Xia, Nariman Moezzi, Chao Ma, Karthik Jayaraman, Divya Kesharwani, Sirikarn Woracheewan, Ben Goska, Eric Donkoh and Ryan Albright. Also, I wish to thank many exceptional students from other groups including, but not limited to Weilun Shen, Wenhuan Yu, Yan Wang, Xiaorao Gao, Chia-Hung Chen, Hurst Kuo, Jiaming Lin, Jinzhou Cao, Tao Wang, Tao Tong, Xin Meng, Wei Li and Sanghyeon Lee in Professor Gabor Temes' group, Wenjing Yin, Jeff Pai, Rajesh Inti, Amr Elshazly, Bangda Yang and Sachin Rao in Professor Pavan Kumar Hanumolu's group, Yue Hu, Jon Guerber, Dave Gubbins, Nima Maghari and

Tawfik Musah in Professor Un-Ku Moon's group, Jinjin He, Ruiqing Ye and Stephen Redfield in Professor Huaping Liu's group, Huarong Ni, Chao Shi and Yuhan Xie in Professor Terri Fiez's group, Na An in Professor Albrecht Jander's group, Younghoon Song and Ahmed Ragab in Professor Sam Palermo's group in Texas A&M University and Yue Lu in Professor Elad Alon's group in U. C. Berkeley, for valuable technical discussions and making my Ph.D. life so vivid and fantastic.

I would like to CDADIC, AFRL, SRC and Intel Corporation for funding my research and MOSIS, IBM and TSMC for chip fabrication.

Finally, I wish to offer my sincere gratitude to my entire family: my parents, girlfriend, cousins, grandparents, uncles and aunts who support my graduate work with their hearts.

## TABLE OF CONTENTS

|                                                   | <u>Page</u> |

|---------------------------------------------------|-------------|

| CHAPTER 1. INTRODUCTION                           | 1           |

| 1.1 Motivation                                    | 1           |

| 1.2 Thesis Organization                           | 4           |

| CHAPTER 2. ANALYSIS AND MODELLING ON SERIAL LINKS | 6           |

| 2.1 Overview of the Architectures                 | 6           |

| 2.2 Modeling of Serial Link                       | 8           |

| 2.2.1 Overview of NRZ and Duobinary Signaling     | 12          |

| 2.2.2. Background of Statistical Analysis         | 13          |

| 2.2.3 Statistical Analysis for Duobinary          | 15          |

| 2.2.4 Clock Non-idealities                        | 16          |

| 2.2.5 Sub-block Modeling of Serial Link           | 20          |

| 2.3 Behavioral Simulations on Link Performance    | 21          |

| 2.4 Clock Distribution Methods                    | 28          |

| 2.4.1 Inverter Chain                              | 29          |

| 2.4.2 CML Chain                                   | 31          |

| 2.4.3 Transmission Line                           | 32          |

| 2.4.4 Inductive Load                              | 34          |

| 2.4.5 Capacitively Driven Wires (CDW)             | 35          |

| 2.5 Summary                                       | 36          |

## TABLE OF CONTENTS (Continued)

|                                                                            | <u>Page</u> |

|----------------------------------------------------------------------------|-------------|

| CHAPTER 3. A SERIAL LINK RECEIVER USING LOCAL INJECTION-LO RING OSCILLATOR |             |

| RING OSCILLATOR                                                            | 38          |

| 3.1 Forwarded Clock Receiver Architectures                                 | 38          |

| 3.2 Analysis on Injection-Locked Ring Oscillators                          | 42          |

| 3.2.1 Previous Approaches                                                  | 42          |

| 3.2.2 Proposed Approach for ILRO Analysis                                  | 44          |

| 3.3 Circuit Implementation                                                 | 48          |

| 3.3.1 Proposed Injection-Locked Ring Oscillator                            | 48          |

| 3.3.2 Other Building Blocks                                                | 51          |

| 3.4 Experimental Results                                                   | 51          |

| 3.4.1 ILRO                                                                 | 52          |

| 3.4.2 Entire Receiver                                                      | 56          |

| 3.5 Summary                                                                | 60          |

| CHAPTER 4. A NEAR-THRESHOLD SERIAL LINK RECEIVER                           | 62          |

| 4.1 Receiver Implementation                                                | 62          |

| 4.2 Design of Super-harmonic ILO                                           | 66          |

| 4.3 Experimental Results                                                   | 68          |

| 4.4 Summary                                                                | 74          |

| Chapter 5. CONCLUSION                                                      | 76          |

| 5.1 Summary                                                                | 76          |

## TABLE OF CONTENTS (Continued)

|                                     | <u>Page</u> |

|-------------------------------------|-------------|

| 5.2 Recommendations for Future Work | 77          |

|                                     |             |

| Bibliography                        | 79          |

## LIST OF FIGURES

| <u>Page</u>                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

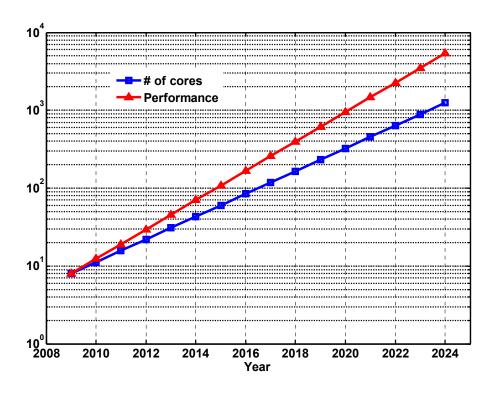

| Figure 1.1. SoC networking projections (performance scaled from 8-core implementation in 2009) [1].                                                                             |

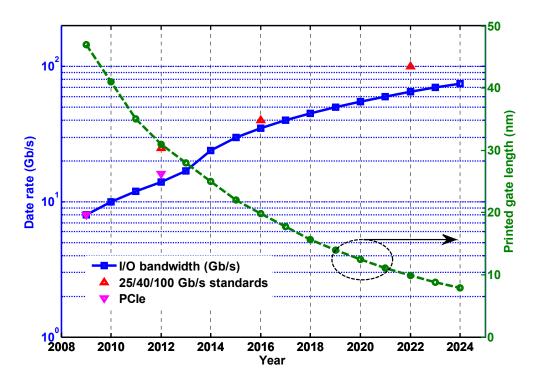

| Figure 1.2. I/O bandwidth projections [1]                                                                                                                                       |

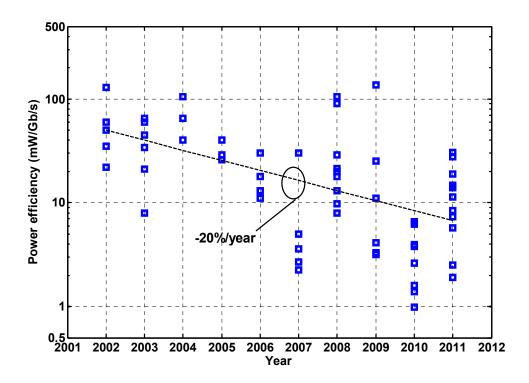

| Figure 1.3. Power efficiency of recent published serial links.                                                                                                                  |

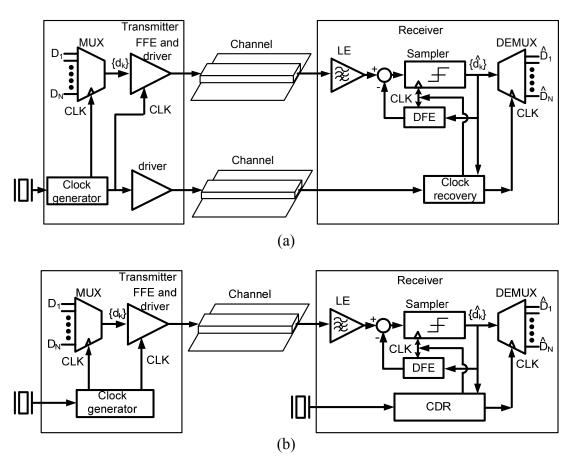

| Figure 2.1. Block diagram of serial link transceiver: (a) forwarded-clock architecture and (b) embedded-clock architecture.                                                     |

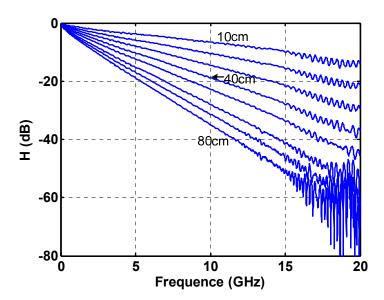

| Figure 2.2. Measured channel loss of 10cm to 80cm PCB traces (from top to bottom), showing -6,6dB, -18.9dB,-35dB loss at 10GHz for 10cm, 40cm and 80cm PCB traces respectively. |

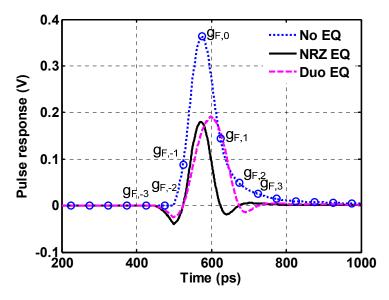

| Figure 2.3. Pulse response to a 50ps (20-Gb/s) pulse before equalization, after NRZ equalization, and duobinary equalization of 40cm PCB trace.                                 |

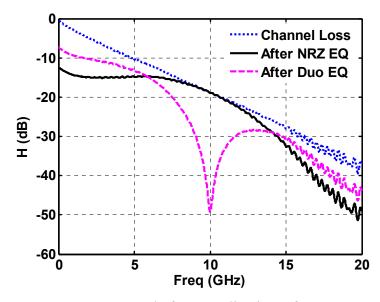

| Figure 2.4. Frequency response before equalization, after NRZ equalization and duobinary equalization of a 40cm PCB trace                                                       |

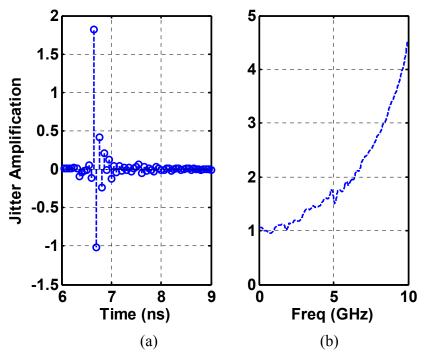

| Figure 2.5. (a) Jitter impulse response and (b) jitter transfer function of a 40cm PCB trace at 20-Gb/s.                                                                        |

| Figure 2.6. Schematic of receiver linear equalizer                                                                                                                              |

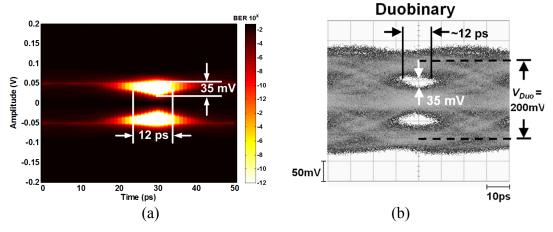

| Figure 2.7. Eye diagram of 40cm trace after NRZ equalization, (a) transient simulation of 10k random bits and (b) statistical analysis.                                         |

| Figure 2.8. Eye diagram of 40cm trace after duobinary equalization, (a) transient simulation of 10k random bits and (b) statistical analysis.                                   |

| Figure 2.9. (a) Simulation result for NRZ and (b) Measured eye diagram from Fig. 29 in [36]                                                                                     |

| Figure 2.10. (a) Simulation result for Duobinary and (b) Measured eye diagram from Fig. 29 in [36]                                                                              |

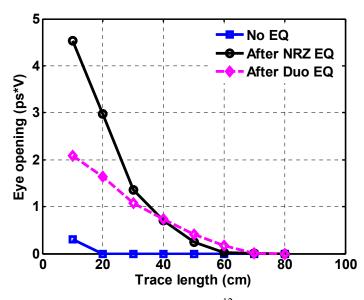

| Figure 2.11 Eye opening area for BER<10 <sup>-12</sup> with different length of traces                                                                                          |

# LIST OF FIGURES (Continued)

| <u>Figure</u>                                                                                                                                                                                        | <u>Page</u> |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

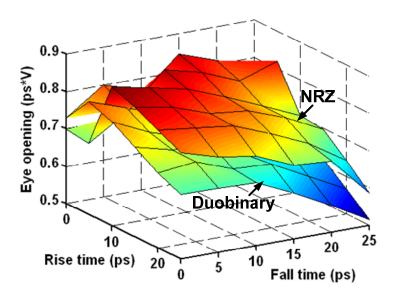

| Figure 2.12. Eye opening area for BER<10 <sup>-12</sup> with different rising and falling tit 40cm trace.                                                                                            |             |

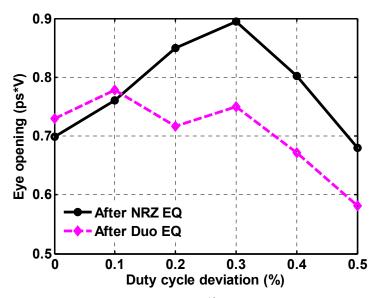

| Figure 2.13. Eye opening area for BER<10 <sup>-12</sup> with different duty cycle deviation 40cm trace.                                                                                              |             |

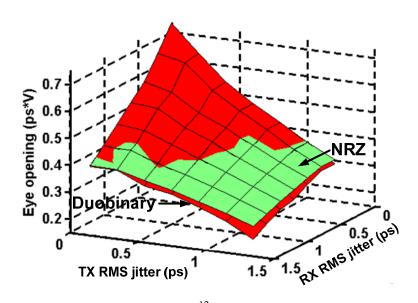

| Figure 2.14. Eye opening area for BER<10 <sup>-12</sup> with different receiver and transmer RMS jitter for 40cm trace.                                                                              |             |

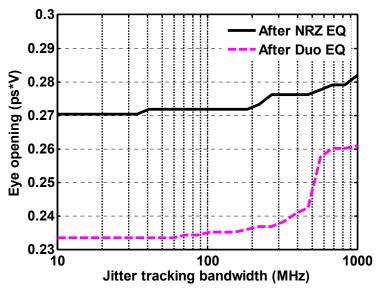

| Figure 2.15. Eye opening area for BER<10 <sup>-12</sup> with different jitter tracking band for 40cm trace with both 1ps RMS TX and RX jitter                                                        |             |

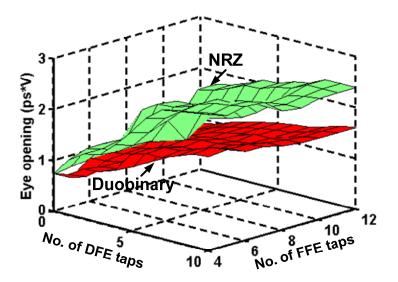

| Figure 2.16. Eye opening area for BER<10 <sup>-12</sup> with different FFE and DFE taps 40cm trace (for FFE, with 1 precursor tap and varying no. of postcursor taps)                                |             |

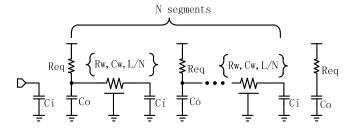

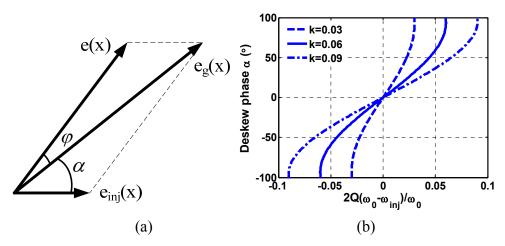

| Figure 2.17. Inverter chain.                                                                                                                                                                         | 29          |

| Figure 2.18. Modeling of chain.                                                                                                                                                                      | 29          |

| Figure 2.19. CML chain.                                                                                                                                                                              | 32          |

| Figure 2.20. Microstrip transmission line.                                                                                                                                                           | 33          |

| Figure 2.21. Inductive load.                                                                                                                                                                         | 34          |

| Figure 2.22. CDW.                                                                                                                                                                                    | 35          |

| Figure 2.23. Modeling of CDW.                                                                                                                                                                        | 35          |

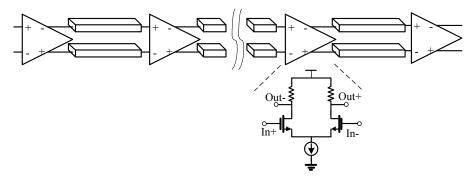

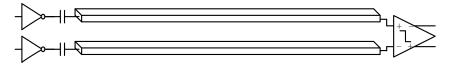

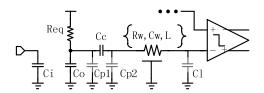

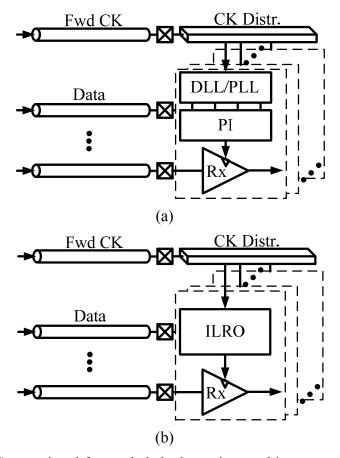

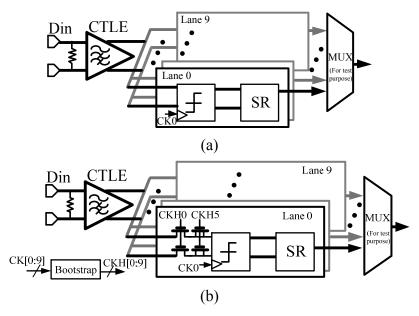

| Figure 3.1. (a).Conventional forwarded clock receiver architecture and (b) proparchitecture using ILRO for multiple serial links.                                                                    |             |

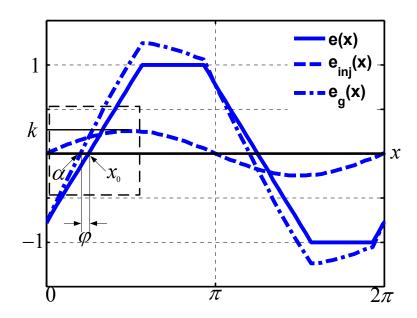

| Figure 3.2. (a) Phase vector diagram (injection signal $e_{inj}(x)$ , free-running tank s $e(x)$ and resultant output $e(x)$ ). (b) Deskew with different injection strength k, on Adler's equation. | based       |

| Figure 3.3. Superposition of waveforms.                                                                                                                                                              | 43          |

| Figure 3.4. Block diagram of proposed receiver                                                                                                                                                       | 47          |

# LIST OF FIGURES (Continued)

| <u>Figure</u> <u>P</u>                                                                                                                                                 | age |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

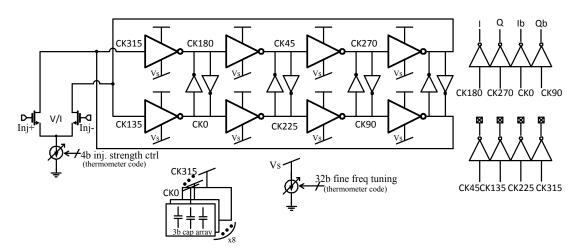

| Figure 3.5. Schematic of ILRO.                                                                                                                                         | 48  |

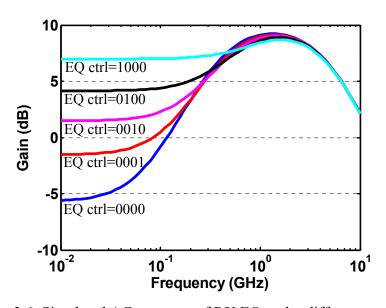

| Figure 3.6. Simulated AC response of RX EQ under different settings.                                                                                                   | 50  |

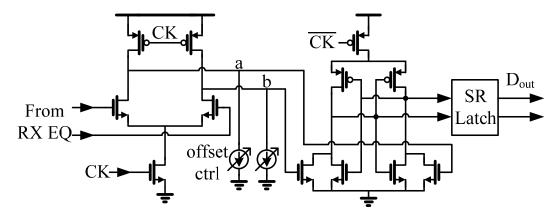

| Figure 3.7. Quantizer with offset control.                                                                                                                             | 50  |

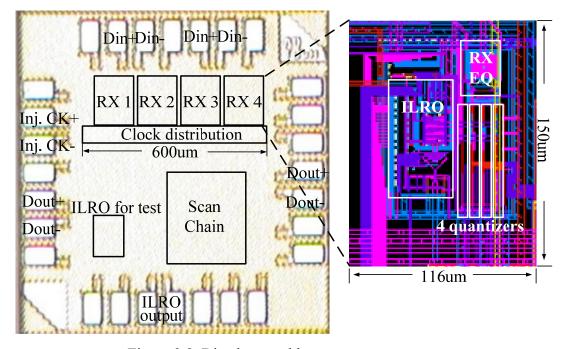

| Figure 3.8. Die photo and layout screen capture.                                                                                                                       | 52  |

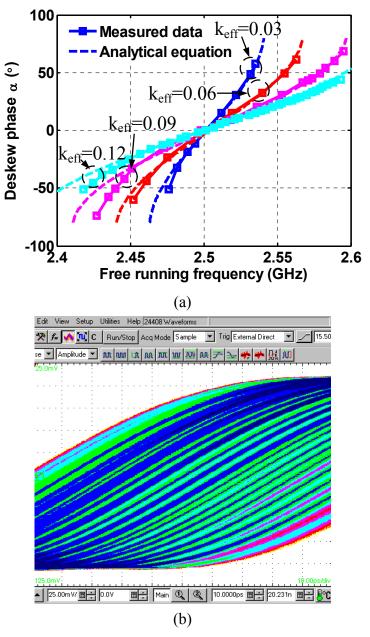

| Figure 3.9. (a) Deskew of ILRO (b) Overlaid waveforms by sweeping phase setting (vertical scale = 25mV/div, horizontal scale = 10ps/div).                              |     |

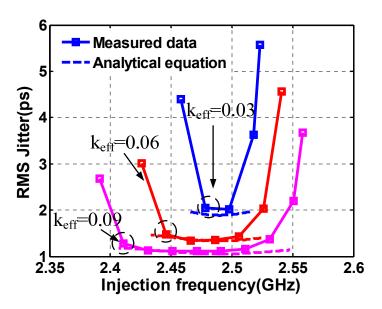

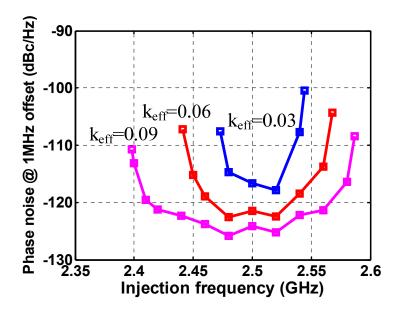

| Figure 3.10. Jitter performance of ILRO.                                                                                                                               | 55  |

| Figure 3.11. Measured phase noise performance of ILRO.                                                                                                                 | 55  |

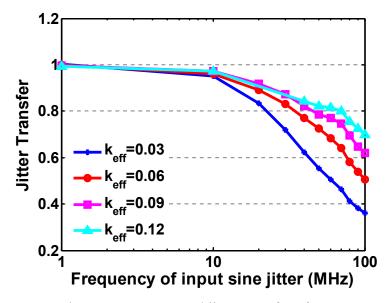

| Figure 3.12. Measured jitter transfer of ILRO.                                                                                                                         | 56  |

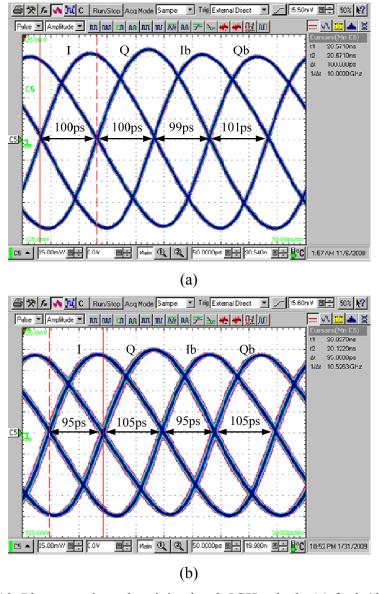

| Figure 3.13. Phase spacing when injecting 2.5GHz clock: (a). $f_0$ =2.49GHz, (b) $f_0$ =2.58GHz (vertical scale = 25mV/div, horizontal scale = 50ps/div)               | 57  |

| Figure 3.14. Eye diagrams of recovered data under (a) 4cm trace and (b) 14cm trace (input data rate=7.2Gb/s, vertical scale = 155mV/div, horizontal scale = 111ps/div) |     |

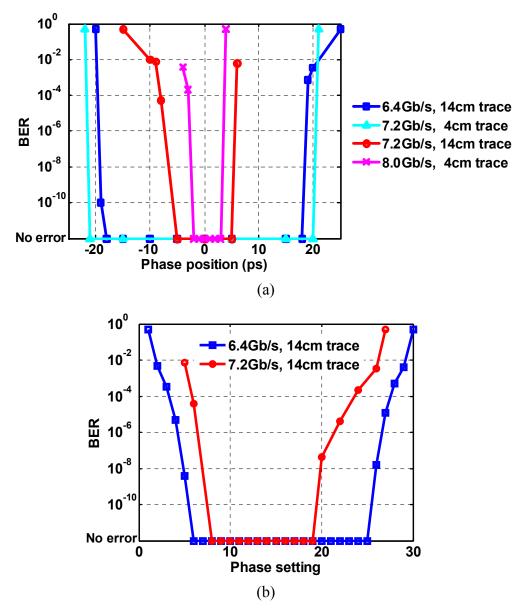

| Figure 3.15. BER measurements (a) by sweeping the delay in BERT and (b) by sweeping the phase setting of ILRO.                                                         | 59  |

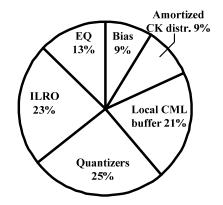

| Figure 3.16. Receiver power breakdown.                                                                                                                                 | 60  |

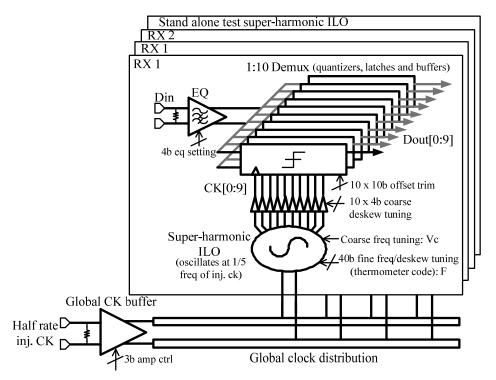

| Figure 4.1. Proposed receiver architecture.                                                                                                                            | 63  |

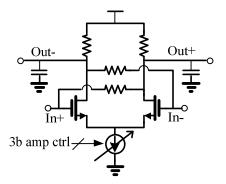

| Figure 4.2. Schematic of global clock buffer with parasitics.                                                                                                          | 64  |

| Figure 4.3. Block diagram of the receiver data lane (a) RX1 and (b) RX2                                                                                                | 65  |

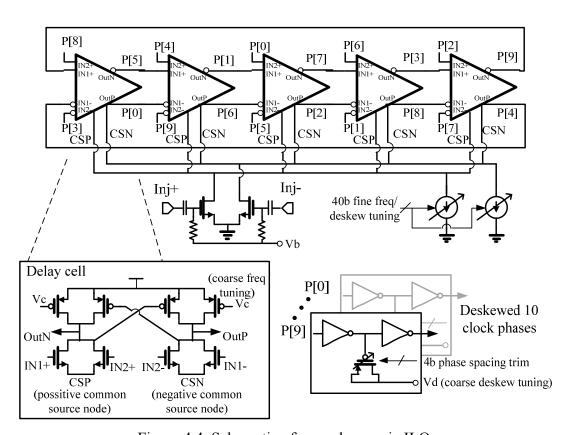

| Figure 4.4. Schematic of super-harmonic ILO.                                                                                                                           | 66  |

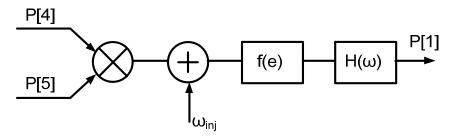

| Figure 4.5. Model of single stage of super-harmonic ILO.                                                                                                               | 67  |

| Figure 4.6 (a) Die photo. And layout screen capture of (b) RX1 and (c) RX2                                                                                             | 69  |

## LIST OF FIGURES (Continued)

| <u>Page</u>                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

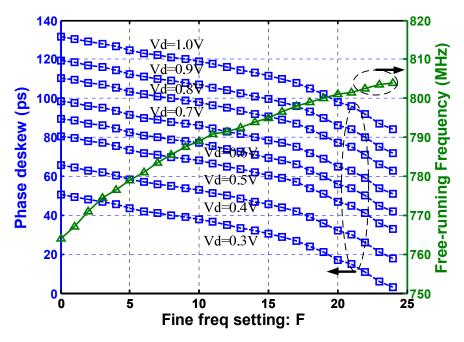

| Figure 4.7. Measured deskew range and free-running frequency of super-harmonic ILO across fine freq tuning                                                            |

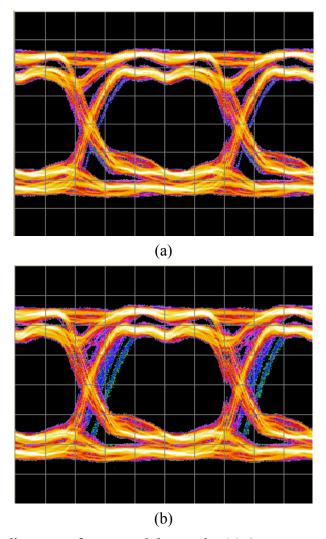

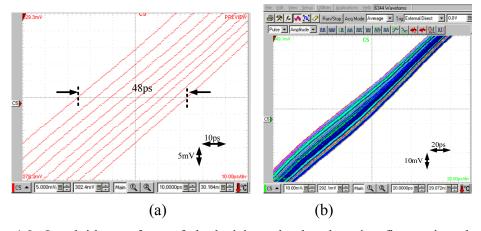

| Figure 4.8. Overlaid waveform of clock rising edge by changing fine tuning alone (a) with oscilloscope average mode on for clarity and (b) with grade color mode on 7 |

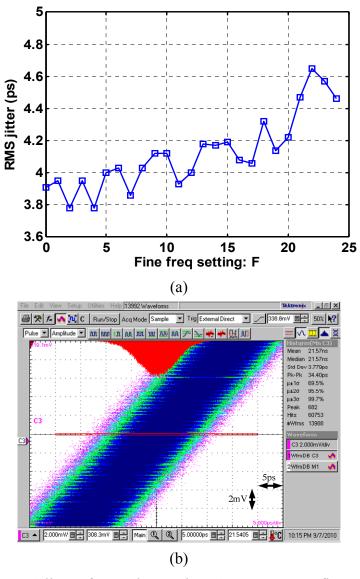

| Figure 4.9. (a) RMS jitter of super-harmonic ILO output across fine tuning settings, and (b) one of zoomed jitter measurement                                         |

| Figure 4.10. Output of SH-ILO after phase modulating 4G clock source by (a) 20MHz deviation and (b) 30MHz deviation                                                   |

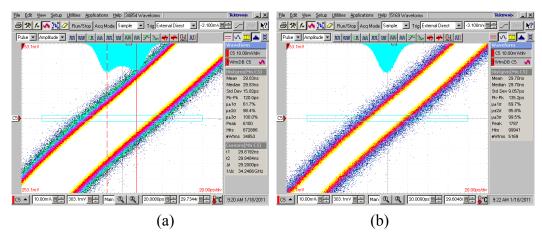

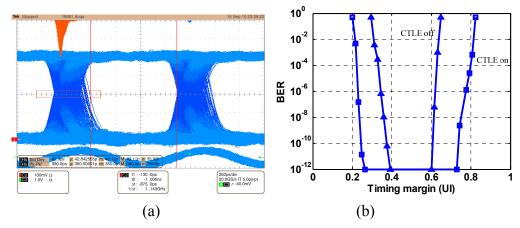

| Figure 4.11. RX1: (a) 800Mb/s 1:10 recovered data output (x=250ps/div, y=100mV/div), (b) BER bathtub curve at 8Gb/s over 20cm FR4                                     |

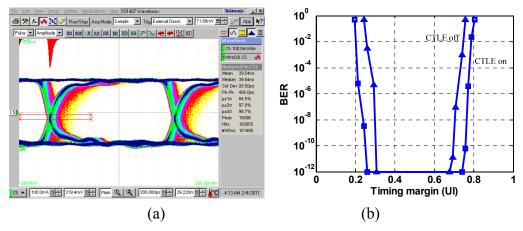

| Figure 4.12. RX2: (a) 800Mb/s 1:10 recovered data output (x=200ps/div, y=100mV/div), (b) BER bathtub curve at 8Gb/s over 20cm FR4                                     |

| Figure 4.13 Channel response of a 20cm FR4 PCB trace                                                                                                                  |

## LIST OF TABLES

| <u>Table</u> |                                        | <u>Page</u> |

|--------------|----------------------------------------|-------------|

| 2.1          | Comparison of Five Clock Distributions | 36          |

| 3.1          | Performance Summary                    | 61          |

| 4.1          | Power Breakdown                        | 74          |

| 4.2          | Comparison with Previous Works         | 75          |

## Analysis and Design on Low-Power Multi-Gb/s Serial Links

#### **CHAPTER 1. INTRODUCTION**

### 1.1 Motivation

The fast-growing demand of higher data rates has pushed the bottleneck to the off-chip I/O bandwidth for applications like future many-core microprocessor systems. According to the ITRS roadmap [1], as shown in Fig. 1.1, the number of cores is projected to increase 1.4x per year, and each core frequency by 1.05x per year. This will result in about 20x increase of the system processing performance in 2016 with

Figure 1.1. SoC networking projections (performance scaled from 8-core implementation in 2009) [1].

more than 80 cores in 22nm process relative to an 8-core system in 45nm in 2009. And it will even be roughly 1000x increase in 2024. These results indict that the aggregate chip-to-chip I/O bandwidth between cores and memories needs to scale with the same fashion in order to feed and keep the computation units well loaded to gain the best performance. However, due to practical limitations like channel loss and crosstalk, in Fig. 1.2, the data rate per pin is only projected to raise about 10x in 2024 relative to 2009, although CMOS technology is going to scale to 8nm. Given that the maximum pin number increases about 2x to 4x during the same period [1], there is a huge gap of aggregate bandwidth for link designers to meet the performance trend.

On the other hand, I/O power efficiency does not scale as aggressively as

Figure 1.2. I/O bandwidth projections [1].

Figure 1.3. Power efficiency of recent published serial links.

performance either. Based on the data in [2] and recent published serial link transceivers in ISSCC and VLSI symposium [3-34], the power efficiency on an average has been improved by only 20% per year, as shown in Fig 1.3. If this tendency sustains in the near future, as the trend of data rate increases much faster than the improvement of power efficiency, the total I/O power is going to increase. This not only will add the cost of thermal dissipation, but also will gain an unacceptable level of power of the whole system.

The purpose of this thesis is to explore these limitations and to develop new design techniques suitable for low-power multi-Gb/s CMOS serial links. A targeted

data rate is around 8Gb/s and the designs are focused on the power-efficient receivers for moderate loss channels.

### 1.2 Thesis Organization

This dissertation begins with an overview of serial link transceiver architectures, followed by a statistical modeling method of link performance at system level, a comparison of NRZ and duobinary modulation scheme and a discussion on clock distribution methods in Chapter 2.

Chapter 3 describes a quad-lane, 6.4-7.2 Gb/s serial link receiver test chip in 90nm CMOS process with a novel phase deskew scheme of injection-locked ring oscillator as a local deskew unit for each receiver. Significant power is saved by replacing the traditional power-hungry phase interpolators by this ring oscillator. This receiver achieves 0.6mW/Gb/s power efficiency in a nominal 1.2V supply. Some design issues and theoretical analysis on injection locked ring oscillators will also be discussed.

After that, Chapter 4 presents 8Gb/s serial link receivers in 65nm CMOS to further reduce the power by using proposed super-harmonic injection-locked ring oscillators for symmetric multi-phase local clock generation and deskewing. Combining this technique with higher parallelism in the receiver structure, low-supply

near-threshold operation and CMOS scaling, this receiver prototype improves power efficiency up to 0.163 mW/Gb/s for a -9.7dB loss channel with BER  $< 10^{-12}$ .

Finally, Chapter 5 summarizes the presented work and proposes some suggestions for further studies.

#### CHAPTER 2. ANALYSIS AND MODELLING ON SERIAL LINKS

#### 2.1 Overview of the Architectures

Depending on the way clock is generated in the receiver side, serial link transceivers can be generally divided into two classes: forwarded-clock architecture and embedded-clock architecture. As shown in Fig. 2.1 (a), in the forwarded-clock architecture, the clock in the receiver (RX) side is obtained directly from transmitter (TX), which ensures that clock frequencies of both the TX and RX are exactly the same. That is, there is no frequency offset otherwise will rise from the small variation of separate crystal oscillators between TX and RX. Therefore, the clock recovery block in the forwarded-clock architecture just needs to rotate the phase to make the clock samples the data at the center. On the other hand, in the embedded-clock architecture, shown in Fig. 2.1 (b), the sampling clock of RX is recovered from the received data instead. As a typical clock data recovery (CDR) circuit in this architecture has a local PLL loop in it to help recover the clock, it needs to tolerate small frequency difference between TX and RX due to different crystal oscillators. The jitter of the recovered clock will track up to the CDR loop bandwidth. However, it is usually smaller than the jitter tracking bandwidth of forwarded-clock architecture [35].

Compared with the embedded clock architecture, forwarded clock architectures reduce the power of clock recovery at the expense of an additional forwarded link to deliver the transmitted mesochronous clock. However, if the chip I/O interface requires many parallel serial lanes, the power and pin overhead of the additional forwarded clock can be amortized among all the data links.

For the data path, on the TX side, several data sequences are multiplexed, with the transmitted symbol pulse width and position determined by the clock shape and data multiplexing ratio. The multiplexed data sequence  $\{d_k\}$  is equalized by feed-

Figure 2.1. Block diagram of serial link transceiver: (a) forwarded-clock architecture and (b) embedded-clock architecture.

forward equalization (FFE) and sent to a channel by the output driver. The channel can be a combination of bonding wire, package trace, PCB trace on the board, connectors and co-axial cable. After passing through a receiver linear equalizer (LE) and/or nonlinear decision feedback equalizer (DFE), the data is then recovered and demultiplexed by the quantizer(s) and flip-flops. For NRZ signaling, the receiver uses the quantizer to slice the 2-level analog input into a single digital value. For higher order modulation, such as duobinary for example, an LSB distiller or 3-level ADC [36] (not shown in Fig. 2.1 for simplicity) is necessary to convert the recovered sequence to NRZ, resulting in two digital outputs for each 3-level duobinary analog input.

### 2.2 Modeling of Serial Link

Chip-to-chip communications can show widely varying channel losses (e.g. - 3dB to -30dB at Nyquist) due to variations in trace length, PCB material, connector type, via stubs, and proximity to aggressor signal coupling. Lossy channel bandwidth critically limits the maximum symbol rate due to inter-symbol interference (ISI), which makes designers to think using a higher order modulation (e.g. PAM-4, partial response such as duobinary) to get higher bit rate. For next generation multi-Gb/s serial links, such as in short-range chip-to-chip applications [37], the channel typically exhibits moderate losses of -20dB or less. Fig. 2.2 depicts the measured channel losses of typical FR4 PCB traces from 10cm to 80cm long, showing that for a 40cm trace

length, the measured channel loss at 10GHz is -18.9dB. While such channel losses may contribute to a reduced signal-to-noise ratio (SNR) in the eye opening, other non-ideal effects beyond channel losses may also contribute to performance degradation, such as PLL jitter, crosstalk, duty cycle distortion (DCD), jitter amplification, and finite rise/fall time of the data symbol.

Besides the issue of channel and circuit impairments, another critical problem is the difficulty in achieving simulation accuracy at the circuit transistor level for multi-Gb/s data rates. As date rate goes up, the time step for simulation becomes smaller. Therefore, excessive transient simulation time is required for the same accuracy; otherwise, simulation inaccuracy will appear due to the incomplete characterization of the link performance. For example, the simulation length of a

Figure 2.2. Measured channel loss of 10cm to 80cm PCB traces (from top to bottom), showing -6,6dB, -18.9dB,-35dB loss at 10GHz for 10cm, 40cm and 80cm PCB traces respectively.

random input sequence exhibiting error-free operation should be at least three times the inverse of the expected bit-error rate (BER), in order to obtain reasonable accuracy with a 95% confidence level [38]. For a typical serial link application with an expected BER of  $10^{-12}$ , the data sequence needs to be at least  $3x10^{12}$  symbols long, which requires a significant amount of simulation time even for a 64-bit workstation. Moreover, to accurately model the jitter, duty cycle variation and finite symbol rise/fall time, the time step of the simulator must be further reduced, again resulting in increased simulation time. Worst-case analysis has been proposed in [39], [40] for obtaining quick link estimation, but is unable to provide more complete link characteristics, such as BER versus eye sampling location.

Statistical analysis techniques [39], [41]-[44] enable accurate and more efficient methods to estimate the performance of serial links beyond conventional transient simulations. These simulators calculate the BER distribution plot by convolving the probability density function (PDF) of all individual cursors of the pulse response. While the PDF of interference sources such as crosstalk can be easily added by summing the corresponding aggressor responses, timing uncertainty such as accurate analysis of transmitter jitter is more difficult to perform [42]. For example, the original work in [39] simply treats transmitter jitter similarly to receiver jitter, though it has travelled through the lossy channel which causes jitter amplification. In [41], jitter from both the transmitter and receiver are converted to an equivalent voltage noise, based on a jittered pulse decomposition model that gives accurate

results in the voltage domain. Extending on the work in [39], a more accurate analysis of transmitter jitter was proposed in [42], [43], which requires extensive calculations to take almost every possible position of the transmitted pulse shapes into account according to the PDF of the transmitter jitter. However, this will degrade the efficiency of the statistical analysis. Furthermore, it treats individual transmit jitter shaped by the PDF separately as a time offset from an ideal pulse, regardless of its frequency content. This can be problematic, as the transmitted sequence will be fed to an ideal high-pass filter in order to capture the jitter amplification at high frequency [45], [35] -- resulting in the same inaccuracy problem as the conventional transient simulation mentioned above. For multi-Gb/s data rates or above, these timing uncertainties become even more critical for accurate analysis and prediction of link performance across various modulation schemes.

A statistical analysis technique for multi-Gb/s serial links that not only includes the effect of channel loss such as ISI and equalization, but also predicts the effects of transmitter jitter amplification, random receiver jitter, finite rise/fall time, and clock duty cycle variation, will be discussed. Based on this analysis, a comparison of at 20-Gb/s data rate between conventional NRZ signaling and duobinary modulation is made.

#### 2.2.1 Overview of NRZ and Duobinary Signaling

NRZ signaling is commonly used in high-speed chip-to-chip communications due to its simplicity and therefore straightforward design in both the transmitter and receiver circuit architectures. In the frequency domain, its main spectral lobe occupies bandwidth up to its data rate of  $1/T_b$ , where  $T_b$  is the period of a symbol. To relieve ISI due to channel loss, equalization is predominantly used to flatten the channel response. The tap coefficients of the equalization filter can be calculated by zero-forcing the nearby cursors except for the main cursor. For example, the coefficients  $(c_{-1} c_0 c_1 c_2)^T$  of a 4-tap FFE for a channel pulse response shown in Fig. 2.3 can be solved by

$$\begin{pmatrix} g_{-1} \\ g_{0} \\ g_{1} \\ g_{2} \end{pmatrix} = \begin{pmatrix} g_{F,0} & g_{F,-1} & g_{F,-2} & g_{F,-3} \\ g_{F,1} & g_{F,0} & g_{F,-1} & g_{F,-2} \\ g_{F,2} & g_{F,1} & g_{F,0} & g_{F,-1} \\ g_{F,3} & g_{F,2} & g_{F,1} & g_{F,0} \end{pmatrix} \begin{pmatrix} c_{-1} \\ c_{0} \\ c_{1} \\ c_{2} \end{pmatrix}$$

(2.1)

where targeted cursors  $(g_{-1} g_0 g_1 g_2)^T$  are  $(0 \ 1 \ 0 \ 0)^T$  for NRZ;  $g_F(t)$  is the pulse response of the channel and  $g_F(t-kT_b)$  is noted as  $g_{F,k}$ .

Duobinary is a partial response signaling scheme that introduces controlled ISI to reduce the transmitted bandwidth. Its main spectral lobe occupies bandwidth up to only half the data rate, or 1/2T<sub>b</sub>. In theory, duobinary is performed as the exclusive-or sum of the current bit and the preceding one within a NRZ sequence, resulting in a 3-level signaling constellation [46]. In practice, it can be achieved by combining both the channel low-pass characteristics and the transceiver equalization together. For example, the coefficients of a 4-tap FFE used for duobinary can be calculated from

Figure 2.3. Pulse response to a 50ps (20-Gb/s) pulse before equalization, after NRZ equalization, and duobinary equalization of 40cm PCB trace.

(2.1) with targeted cursors (g<sub>-1</sub> g<sub>0</sub> g<sub>1</sub> g<sub>2</sub>)<sup>T</sup> equivalent to (0 0.5 0.5 0)<sup>T</sup>. To prevent error propagation, a precoder and decoder must be implemented at baseband. Fig. 2.3 and Fig. 2.4 show the pulse and frequency responses before and after equalization for both NRZ and duobinary signaling, using a 4-tap FFE through a 40cm FR4 PCB trace at a 20-Gb/s data rate. The smaller bandwidth of duobinary modulation confirms its higher spectral efficiency, showing less loss than NRZ for the same date rate.

## 2.2.2. Background of Statistical Analysis

As mentioned previously, since BER for a typical serial link can be less than  $10^{-12}$  and random noises are boundless, transient simulations of eye diagrams and SNR are both excessively time-consuming and difficult to process (due to the large amount

Figure 2.4. Frequency response before equalization, after NRZ equalization and duobinary equalization of a 40cm PCB trace.

of sampled data). Statistical analysis, on the other hand, can give a detailed eye plot of the BER distribution across both different timing offsets and decision thresholds. Based on the transmitted pulse response through the channel, statistical analysis convolves all the PDFs of the residual ISI to produce the BER eye. For NRZ signaling, the PDF of the ISI from the k<sup>th</sup> preceding bit can be expressed as

$$ISI_{k} = P_{0}\delta(x) + P_{1}\delta(x - g_{F,k}), \quad k \neq 0$$

(2.2)

where  $P_0$  and  $P_1$  are the probability of transmitting ZERO and ONE symbols, with typical values of 0.5 for equal possibility of ZERO and ONE.  $\delta(x)$  is the unit impulse function. When k > 0, ISI results from the postcursor tails of previous bits, while when k < 0, the ISI arises from the precursor of proceeding bits. The total ISI is then calculated by convolving all the ISIs as:

$$ISI = \dots \otimes ISI_{-2} \otimes ISI_{-1} \otimes ISI_{1} \otimes ISI_{2} \otimes \dots$$

(2.3)

The PDFs of the main cursor with symbols ZERO and ONE are:

$$main_0 = \delta(x), \quad main_1 = \delta(x - g_{F,0})$$

(2.4)

Then the PDFs of ZERO and ONE interfered by the ISI are:

$$pdf_0 = main_0 \otimes ISI$$

,  $pdf_1 = main_1 \otimes ISI$  (2.5)

Hence, the BER of NRZ signaling for a given decision threshold  $y_T$  can be written as:

$$BER_{NRZ}(y_T) = P_0 \cdot P(D_1 | H_0) + P_1 \cdot P(D_0 | H_1)$$

$$= P_0 \int_{y_T}^{\infty} p df_0 dx + P_1 \int_{-\infty}^{y_T} p df_1 dx$$

(2.6)

where  $P(D_1|H_0)$  is the probability of transmitting a ZERO but mistaking it as a ONE at the receiver, while  $P(D_0|H_1)$  is the opposite scenario. The BER distribution at any single time instance is obtained by sweeping  $y_T$  across the input dynamic range. After repeating the above steps across one complete symbol period, the entire BER eye plot can be derived.

## 2.2.3 Statistical Analysis for Duobinary

Duobinary modulation introduces controlled ISI, implicit within the coding. Therefore, there exist two large distributions (one caused by the main cursor and the other by the first postcursor) in pdf<sub>0</sub> and pdf<sub>1</sub>, instead of only one as in case of NRZ.

Also because of the three-level signaling, two decision boundaries  $v_{TH1}$  and  $v_{TH2}$  need to be set in order to obtain the BER for duobinary:

$$BER_{duo}(y_{T}) = \begin{cases} \int_{y_{T}}^{v_{TH1}} (P_{0} \cdot pdf_{0} + P_{1} \cdot pdf_{1}) dx, & y_{T} \leq v_{TH1} \\ \int_{v_{TH1}}^{y_{T}} (P_{0} \cdot pdf_{0} + P_{1} \cdot pdf_{1}) dx, & v_{TH1} < y_{T} < v_{mid} \\ \int_{y_{T}}^{v_{TH2}} (P_{0} \cdot pdf_{0} + P_{1} \cdot pdf_{1}) dx, & v_{mid} \leq y_{T} < v_{VT2} \\ \int_{v_{TH2}}^{y_{T}} (P_{0} \cdot pdf_{0} + P_{1} \cdot pdf_{1}) dx, & v_{TH2} \leq y_{T} \end{cases}$$

$$(2.7)$$

where  $v_{mid}$  is the position of the peak impulse from the sum of pdf<sub>0</sub> and pdf<sub>1</sub>. The decision boundaries  $v_{TH1}$  and  $v_{TH2}$  can be obtained by searching for the minimum BER located around the position of  $v_{mid}\pm0.5max(gF(t))$ , such that the BER can be low enough to open the eye near the boundaries.

#### 2.2.4 Clock Non-idealities

In addition to ISI, clock non-idealities such as transmitter jitter, receiver jitter, rise/fall time and duty cycle variation will also degrade the performance of a serial link receiver.

When the jittery data sequence is transmitted through the channel and arrives at the input of the receiver, the jitter value will be increased, especially for its high frequency portion. This is typically referred to as jitter enhancement or jitter amplification in [45], [35], and it worsens as data rate increases. One way to quantify the amount of jitter amplification is to use the jitter impulse response (JIR) and jitter

Figure 2.5. (a) Jitter impulse response and (b) jitter transfer function of a 40cm PCB trace at 20-Gb/s.

transfer function (JTF). The JIR at a given data rate can be extracted by comparing the ideal zero-crossings with the zero-crossings of the response where the data sequence gives a single-shot of a small time offset. Then JTF can be obtained by calculating the Fourier transformation of the JIR. Fig. 2.5 shows the JIR and JTF of the 40cm FR4 PCB trace at a 20-Gb/s data rate. Assuming the transmitter jitter sequence  $J_{TX}$  is wide-sense stationary (WSS), the mean of the jitter response at the input of the receiver  $J_{TX}$  can be expressed as:

$$E\left[J_{TX}^{\prime}\right] = E\left[JIR \otimes J_{TX}\right] = E\left[J_{TX}\right] \int_{0}^{\infty} JIR \ dt = E\left[J_{TX}\right] JTF\left(0\right)$$

(2.8)

where E(x) is the expected value or mean of x [47].  $S_{TX}$  and  $S'_{TX}$ , which are the power spectral density (PSD) of the  $J_{TX}$  and  $J'_{TX}$ , can be related as the well-known equation:

$$S_{TX}^{\prime} = \left| JTF(f) \right|^2 S_{TX} \tag{2.9}$$

Then the auto-covariance C'<sub>TX</sub> of J'<sub>TX</sub> is

$$C'_{TX}(\tau) = R'_{TX}(\tau) - E^2 \left[ J'_{TX} \right] = \mathcal{F}^{-1}(S'_{TX}) - E^2 \left[ J'_{TX} \right]$$

(2.10)

where  $R'_{TX}$  is the auto-correlation of  $J'_{TX}$ , while the second equation comes from Wiener-Khinchin theorem. From (2.8)-(2.10), if the distribution of  $J_{TX}$  is known, we can obtain both the mean and auto-covariance of its response  $J'_{TX}$  through the channel. Moreover, if the input process  $J_{TX}$  is a Gaussian WSS random process, the output  $J'_{TX}$  will also be a Gaussian WSS random process [47]. Thus, the mean and auto-covariance will be sufficient to determine the distribution of  $J'_{TX}$ .

It should be noted that while the jitter is amplified as it passes through the channel, the sampling clock can track some amount of this jitter, such that the total degradation on BER can be mitigated. This jitter tracking is constrained by the bandwidth limitation of a CDR circuit [35] (which generates the clock for the receiver in Fig. 2.1) in an embedded clock architecture, or from the mismatch observed between the data and clock paths in the forwarded clock architecture. To model this effect, we assume a first order low-pass system to track the jitter up to its tracking bandwidth BW<sub>track</sub>, with only the portion outside this tracking bandwidth is integrated.

The transfer functions of "jitter tracking" and "not tracking" can be expressed as below:

$$H_{track} = \frac{1}{1 + \frac{j\omega}{BW_{track}}}, \quad H_{not\_track} = 1 - H_{track} = \frac{\frac{j\omega}{BW_{track}}}{1 + \frac{j\omega}{BW_{track}}}$$

(2.11)

By doing so, the transmitter jitter is converted to its equivalent jitter distribution at the receiver side.

The random timing jitter uncertainty at the receiver side can be modeled as a Gaussian distribution. Though a Gaussian distribution is boundless, the probability that the random variable exceeds  $7.0345\sigma$  is only  $10^{-12}$ , where  $\sigma$  is its standard deviation [47]. We include the range between  $\pm N_s \sigma$  in the calculation, where  $N_s$  is chosen as 8 in order to leave sufficient margin for a BER of  $10^{-12}$ . The time positions of the cursors in the pulse response  $g_F(t)$ , shown in Fig. 2.3, are disturbed by the presence of the jitter. Therefore, the PDFs of the ISI and the main cursor ONE can be modified from (2.2) and (2.4) to:

$$ISI_{k,j} = P_0 \delta(x) + P_1 \sum_{\tau = -N_s \sigma}^{N_s \sigma} \left[ \delta(x - g_F(t - kT - \tau)) \cdot gs(\tau) \right]$$

(2.12)

$$main_{1,j} = \sum_{\tau = -N_s \sigma}^{N_s \sigma} \left[ \delta \left( x - g_F \left( t - \tau \right) \right) \cdot gs(\tau) \right]$$

(2.13)

where  $gs(\tau)$  is the PDF of the jitter. Different PDFs of uncorrelated jitter sources can be convolved together to obtain the total equivalent PDF at the receiver side.

The effects of finite rise/fall time and duty cycle variation are added to this analysis by directly shaping the input symbol pulse according to its rise/fall time and pulse width, and then regenerating the pulse response through the channel.

# 2.2.5 Sub-block Modeling of Serial Link

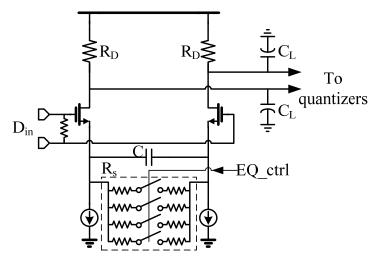

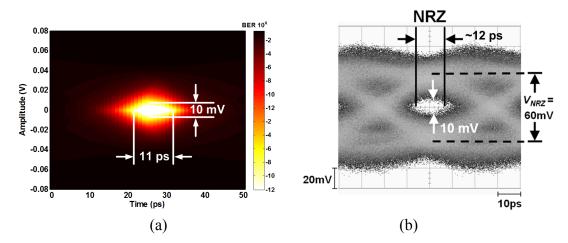

As shown in Fig. 2.1, the sub-blocks of a serial link transceiver includes the channel, FFE, LE and DFE. The channel pulse response can be extracted from the inverse FFT of the S-parameters of the channel [39]. Because the FFE and DFE are discrete-time in nature, they are easily included in the analysis, as the tap coefficients calculated from (2.1) can be used directly as the coefficients for the FIR filter of the FFE or DFE. The receiver front-end LE, on the other hand, is the analog component that works at the highest frequency of all the receiver blocks. It is usually implemented as a source-degenerated, linear equalizer [2], as shown in Fig. 2.6. Its voltage gain can be written as:

$$A_{v} = G_{m}R_{out} \approx \frac{g_{m}}{1 + g_{m}\left(R_{s} / / \frac{1}{j\omega C}\right)} \left(R_{D} / / \frac{1}{j\omega C_{L}}\right) = \frac{g_{m}R_{D}}{1 + g_{m}R_{s}} \frac{1 + j\omega / \omega_{z}}{\left(1 + j\omega / \omega_{p}\right)\left(1 + j\omega / \omega_{p,out}\right)}$$

$$(2.14)$$

where  $g_m$  is transconductance of the input transistor pair,  $\omega_z = 1/R_s C$ ,  $\omega_p = (1+g_m R_s)/R_s C = (1+g_m R_s)\omega_z$ , and output pole  $\omega_{p,out} = 1/R_D C_L$ . Therefore,  $R_s$  and C introduce a zero  $\omega_z$  before the pole  $\omega_p$ . If the output pole  $\omega_{p,out}$  is designed to be larger than the zero, the gain will be boosted between  $\omega_z$  and the smaller one of  $\omega_p$

Figure 2.6. Schematic of receiver linear equalizer.

and  $\omega_{p,out}$ . By increasing the value of the degenerated resistor R<sub>s</sub>, the DC gain will decrease and  $\omega_z$  will be smaller. However, the location of two poles will not change significantly, resulting in an effective high-pass filtering effect with a constant frequency peak that compensates for some of the channel loss. Finally, the BER distribution plot with equalization can be obtained from the resulting pulse response convolving with the impulse responses of the equalizers.

# 2.3 Behavioral Simulations on Link Performance

The above analysis is verified using behavioral simulations in MATLAB. Several FR4 PCB traces with two SMA connectors for different lengths from 10cm to 80cm were measured (Fig. 2.2). The impulse responses of the channels were derived from the measured S parameters. Unless otherwise stated, the default settings for the

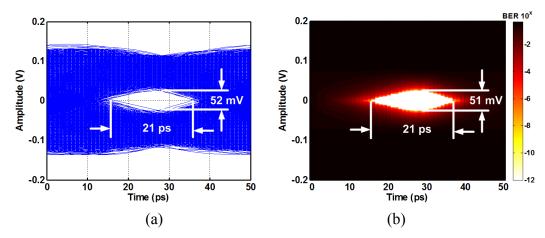

Figure 2.7. Eye diagram of 40cm trace after NRZ equalization, (a) transient simulation of 10k random bits and (b) statistical analysis.

Figure 2.8. Eye diagram of 40cm trace after duobinary equalization, (a) transient simulation of 10k random bits and (b) statistical analysis.

simulations in this section are 20-Gb/s data rate with 0.5V transmitter amplitude and 20mV tap coefficient resolution through the 40cm PCB trace.

Due to the large channel loss of the 40cm trace, the eye without equalization will be closed. Therefore, the effectiveness of the statistical analysis is verified by traditional transient simulation with 4-tap FFE equalization for both NRZ and

duobinary. The two methods exhibit similar horizontal and vertical openings, as shown in Fig. 2.7 and Fig. 2.8. Note that for the transient results, 10k bits are simulated in order to trade-off between accuracy and simulation time. The proposed statistical analysis not only provides similar eye diagram with less simulation time but also includes sufficient BER information. This BER eye plot can easily be converted to the conventional bathtub curve for a given decision threshold. By rebuilding the

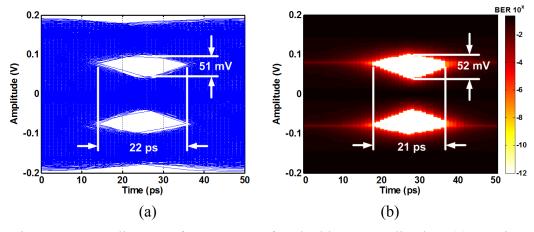

Figure 2.9. (a) Simulation result for NRZ and (b) Measured eye diagram from Fig. 29 in [36].

Figure 2.10. (a) Simulation result for Duobinary and (b) Measured eye diagram from Fig. 29 in [36].

pulse response, a comparison is also made between the statistical method and the measured results in [36], as shown in Fig. 2.9 and Fig. 2.10.

To fairly compare the performance of NRZ without equalization, NRZ with equalization and duobinary equalization, the tap coefficients of the 4-tap FFE are normalized. Each modulation scheme is analyzed by comparing the area of the region where BER<10<sup>-12</sup> in the BER eye plot, in unit ps\*V. As there are two eye openings for duobinary signaling, only the minimum of the two is counted as the worst case when there are uneven eyes for duobinary. As shown in Fig. 2.11, the eye is almost closed after 20cm if no equalization is performed. Because duobinary equalization consumes more voltage headroom than NRZ and it relies on a faster decreased channel loss in the frequency domain, it is not as effective as NRZ equalization for small channel losses. However, for severe loss channels like those longer than 40cm, its eye opens

Figure 2.11. Eye opening area for BER<10<sup>-12</sup> with different length of traces.

more compared with NRZ equalization.

The effects of finite rise/fall time and duty cycle deviation are shown in Fig.

Figure 2.12. Eye opening area for BER<10<sup>-12</sup> with different rising and falling times for 40cm trace.

Figure 2.13. Eye opening area for BER<10<sup>-12</sup> with different duty cycle deviations for 40cm trace.

2.12 and Fig. 2.13. Here it is observed that NRZ equalization dose not degrade as much as duobinary due to these variations. Interestingly, the eyes improve slightly

Figure 2.14. Eye opening area for BER<10<sup>-12</sup> with different receiver and transmitter RMS jitter for 40cm trace.

Figure 2.15. Eye opening area for BER<10<sup>-12</sup> with different jitter tracking bandwidth for 40cm trace with both 1ps RMS TX and RX jitter.

with small rise/fall time, because the finite transition times smooth the pulse shape and excite less interference.

Fig. 2.14 shows the BER eye openings of NRZ and duobinary signaling with different receiver and transmitter jitter values, where the eye opening of duobinary degrades faster than that of NRZ in the existence of jitter. Thus, while the eye opening of jitter-free duobinary is larger than that of NRZ, as the jitter value increases, duobinary performs worse than NRZ. Fig. 2.15 shows that a larger jitter tracking bandwidth will help to improve the BER performance. The eye openings for different FFE and DFE taps are plotted in Fig. 2.16. As the number of taps increases, residual ISI becomes less severe, opening the eyes of both NRZ and duobinary. However, as duobinary requires 3-level signaling, its eye is more likely to be limited by its voltage

Figure 2.16. Eye opening area for BER<10<sup>-12</sup> with different FFE and DFE taps for 40cm trace (for FFE, with 1 precursor tap and varying no. of postcursor taps).

headroom than by residual ISI. Therefore, when a large number of equalizing taps are used, the duobinary eye with limited voltage headroom may perform unfavorably when compared with NRZ.

#### 2.4 Clock Distribution Methods

In the previous sections, analysis and simulation of serial link performance are focused on the data path with abstract of clock information to jitter, rise/fall time, DCD etc. In this section, more discussions on detailed clock distribution methods will be presented.

Clock distribution methods can be classified into full swing propagation like inverter chain and low swing propagation such as current mode logic (CML), transmission line, inductive load and capacitively driven wires (CDW). Because dynamic power dissipation at frequency f can be expressed as

$$P_{dyn} = C_L V^2 f (2.15)$$

where CL is load capacitance and V is the propagation swing [70]. Low swing methods benefit from lower dynamic power and less aggressive to substrate and other circuits. But they may suffer from large static power consumption like CML. Also, auxiliary circuits such as level shifter are needed at local receiver side to convert to full swing.

#### 2.4.1 Inverter Chain

Inverter chain is the most traditional way for clock distribution. As shown in Fig. 2.17, it can be divided into several segments to minimize the propagation delay. For hand calculation, inverter chain can be modeled as Fig. 2.18. When an ideal step input excites a single-pole system, the output waveform can be written as

$$V_{out}(t) = V(\infty) + (V(0^+) - V(\infty))e^{-t/\tau}$$

(2.16)

where  $\tau$  is the time constant of the system, which is the product of the effective resistance and capacitance.  $V(\infty)$  and  $V(0^+)$  are final and initial voltages respectively. The delay time to reach the 50% point is well known as propagation delay:

$$t_p = \ln(2)\tau = 0.69\tau \tag{2.17}$$

According to Elmore model [70], propagation delay of inverter chain can be

Figure 2.17. Inverter chain.

Figure 2.18. Modeling of chain.

calculated as

$$t_{p} = N \left[ 0.69 R_{eq} c_{o} + \left( 0.69 R_{eq} + 0.38 \frac{R_{w}L}{N} \right) \frac{C_{w}L}{N} + 0.69 \left( R_{eq} + \frac{R_{w}L}{N} \right) c_{i} \right]$$

$$= N \left[ 0.69 \frac{R_{equ}}{m} m c_{ou} + \left( 0.69 \frac{R_{equ}}{m} + 0.38 \frac{R_{w}L}{N} \right) \frac{C_{w}L}{N} + 0.69 \left( \frac{R_{equ}}{m} + \frac{R_{w}L}{N} \right) m c_{iu} \right]$$

$$= 0.69 N R_{equ} \left( c_{ou} + c_{iu} \right) + 0.38 \frac{R_{w}C_{w}L^{2}}{N} + 0.69 \frac{R_{equ}C_{w}L}{m} + 0.69 m R_{w}L c_{iu}$$

$$(2.18)$$

where N is the number of segments.  $C_i$ ,  $C_o$ ,  $R_{eq}$  are the input, output capacitance and equivalent resistance of the inverter.  $R_w$ ,  $C_w$  are the unit resistance and capacitance of the metal wire. L is the total length of the metal wire.  $C_{iu}$ ,  $C_{ou}$ ,  $R_{equ}$  are the input, output capacitance and equivalent resistance of a unit strength inverter. Usually a unit strength inverter is defined, so that other inverters are m multiples of the unit inverter. The inverter chain can get minimum propagation delay when

$$N = 0.742L\sqrt{\frac{R_{w}C_{w}}{R_{equ}(c_{ou} + c_{iu})}} \text{ and } m = \sqrt{\frac{R_{equ}C_{w}}{R_{w}c_{iu}}}$$

(2.19)

In a specific CMOS 90nm process, for example, the sheet resistance and unit capacitance of the top thick metal 8 are  $R\Box=47m\Omega$ ,  $C\Box=0.25fF/um^2$ , and its minimum pitch is 560nm. It's not necessary to use minimum width for clock distribution. If 2x wider metal is chosen, then  $Rw=0.083\Omega/um$ , Cw=0.134fF/um. And it is assumed the metal wire is 5mm long. A unit strength inverter is designed as W/L of NMOS: 0.4u/0.1u, W/L of PMOS: 1u/0.1u. Simulated  $C_{iu}$  and  $C_{ou}$  are 1.3fF and 1fF

respectively. For hand calculation,  $R_{equ}$  is estimated by average the on resistance of unit inverter  $R_{on}$  at supply and half supply, as  $1/2(R_{on}(VDD)+R_{on}(VDD/2))\approx 6k\Omega$ . So the segment number N and multiple m for optimal delay can be calculated from (2.19) as N=3.33, round to 3, and m≈86. However, these numbers are not optimal for power and jitter performance because inverter is sensitive to supply noise. Less number of inverters is preferred in regard to jitter performance.

Simulations under the condition of 5mm long wire, 2.5 GHz clock and  $\pm 5\%$  supply variation shows minimum jitter ~36ps is achieved when segment N=3, multiple m=256, while minimum delay ~321ps is when N=3, m=128, and minimum power is when N=4, m=64. From the viewpoint of jitter-power product and delay-power product, N=3, m=128 gets the best performance.

#### 2.4.2 CML Chain

CML chain, as shown in Fig.2.19, can conduct much faster signal due to its current mode nature. It can be analyzed using the same model as Fig. 2.18. In the same process as above, a unit CML is designed with top load resistor  $200\Omega$  and 1mA current source. So the output swing is 0.2V and  $R_{equ}$  is  $200\Omega$  by this choice. W/L of input device pair is 20u/0.1u. Simulated  $C_{iu}$  and  $C_{ou}$  for CML are 30fF and 6fF respectively. Doing the same analysis as the inverter chain and also assuming 5mm long metal wire, we can get N $\approx$ 4 and m=3.3 for optimal delay from equation (2.19). Though power supply rejection ratio (PSRR) of CML is much better than inverter, it is

Figure 2.19. CML chain.

much power hungry due to its static power dissipation. Therefore, minimum number of segments is favorable for low power design. Since the delay of CML is smaller than inverter, its timing margin is relived, and it's not necessary to have to get optimal propagation time to meet the timing requirement.

Simulations show minimum jitter of CML chain in this process is  $\sim$ 0.5ps when N=2, m=8, while minimum delay  $\sim$ 182ps when N=4, m=8, and minimum power is N=2, m=1. From the viewpoint of jitter-power product and delay-power product, N=2, m=1 achieves a good tradeoff.

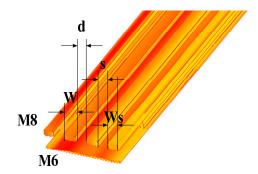

# 2.4.3 Transmission Line

Transmission line effect takes into effect when total resistance of metal wire is small enough regarding to the characteristic impedance  $Z_0$ . From this point, the distributed inductance of the wire starts to affect the delay behavior. The delay of transmission line is smallest among all the methods due to its speed-of-light

propagation velocity. As a passive element, it does not introduce jitter itself, but the driven circuits do.

The on-die transmission line can be realized by a coupled differential microstrip in top thick metal 8 with underneath ground shield in metal 6 as shown in Fig. 2.20. It's not necessary to make exactly standard  $100\Omega$  differential characteristic impedance as long as it's matched on-die by its source and load. Actually,  $Z_0$  is preferred to be designed large enough compared with the DC resistance of metal as mentioned before. And large  $Z_0$  also saves power of the driven CML circuit for the given swing. However,  $Z_0$  is limited by the parasitic capacitance on the die. After several trial and errors, we choose the transmission line with W=6um, space d=2.5um, ground wire width Ws=4um, and space between signal wire and ground wire s =4um. With this choice, the simulated differential characteristic impedance is  $120\Omega$  and DC resistance is  $42\Omega$ . It behaves as a lossy transmission line, and the signal amplitude would tamper a little along the line.

Simulation shows the delay is as small as 43ps and with only 0.18ps jitter. However, the driven CML circuit consumes 4mA.

Figure 2.20. Microstrip transmission line.

#### 2.4.4 Inductive Load

Other than taking advantage of distributed inductance as transmission line, a lumped on-die inductor can be employed to boost both the propagation time and voltage swing, as shown in Fig. 2.21 [2]. An estimation of inductance can be made by resonant frequency and total capacitance of the metal wire. Assume the same 5mm wire as inverter chain,  $C_{total} = C_w \cdot L = 670 \text{fF}$ , so the inductance to cancel this capacitance at 2.5G is about  $1/C_{total}\omega^2 = 6nH$ . Larger inductance can push the zero introduced by inductor to lower frequency band, thus causing more boost at desired frequency. However, this may cost more area on the chip. Since the area of inductor is directly related to its inductance and quality factor, careful choice is necessary to achieve these within reasonable area.

Die area for inductor can be saved by low inductance and low quality factor Q. Actually quality factor Q of the on-die inductor does not affect much on the performance, because the long metal wire resistance has dominated loaded Q anyway. Simulation show jitter is smaller than 1ps. Like transmission line, its swing also gets smaller along the wire.

Figure 2.21. Inductive load.

Figure 2.22. CDW.

Figure 2.23. Modeling of CDW.

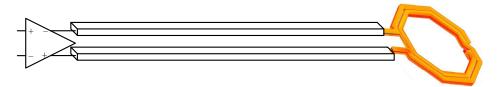

# 2.4.5 Capacitively Driven Wires (CDW)

Fig. 2.22 shows the capacitively driven method [71]. The capacitance seen by the inverter is significantly reduced due to the capacitor in series, so the power consumption is reduced too. The propagation time can be estimated as the model in Fig. 2.23.

$$t_p = 0.69R_{eq} \left( c_o + c_{p1} + c_c \right) + 0.19R_w C_w L^2$$

(2.20)

where  $C_i$ ,  $C_o$ ,  $R_{eq}$  are the input, output capacitance and equivalent resistance of the driven inverter,  $R_w$ ,  $C_w$  are the unit resistance and capacitance of the metal wire. L is the total length. Although minimum series capacitor  $C_c$  will reduce the delay and power, it also reduces the swing because of the capacitance divider. So its minimum value should be limited by the sensitivity of comparator at receiver side with some

margin. Although Cc blocks the DC, many methods can be implemented to control the DC bias [71].

CDW can achieve the minimum power dissipation in all five methods. Simulated in a 90nm CMOS process, their performances are summarized in Table 2.1. It shows transmission line gets the best jitter and delay performance. And CDW gives the minimum jitter-power product and delay-power product.

TABLE 2.1 COMPARISON OF FIVE CLOCK DISTRIBUTIONS

| Technology                  | 1.2V 90nm CMOS |            |           |

|-----------------------------|----------------|------------|-----------|

| Methods (with optimal       | Performance    |            |           |

| tradeoff)                   | Jitter (ps)    | Delay (ps) | Power(mW) |

| Inverter chain (N=3, m=128) | 36             | 321        | 11.5      |

| CML chain (N=2, m=1)        | 1              | 221        | 2         |

| Transmission line           | 0.18           | 43         | 4         |

| Inductive load (L=6nH, Q=2) | 0.42           | 55         | 4         |

| CDW (Cc=50f)                | 1.98           | 116        | 0.62      |

# 2.5 Summary

A statistical method to analyze serial link systems for NRZ and duobinary signaling is presented, incorporating non-ideal effects such as transmitter jitter and

receiver jitter, jitter tracking bandwidth, finite rise/fall time and duty cycle deviation. Using this analysis tool, a comparison of the performance between NRZ and duobinary at 20-Gb/s is then performed. While duobinary achieves less channel loss due to the reduced Nyquist bandwidth, in general, it suffers more than NRZ from non-idealities arising from the imperfect clock source. Only for long channels with significant attenuation does multi-level, duobinary signaling have a BER advantage over NRZ, given the expected amount of clock uncertainty. The proposed statistical analysis can therefore give early insight for quick and accurate system design tradeoffs for multi-Gb/s interconnections.

On the clock path, a comparison and design analysis regarding five clock distribution methods for serial links are presented. Simulations in a 90nm CMOS process have been performed to verify the design tradeoffs and show that transmission line can achieve least jitter and delay, while CDW consumes lowest power with reasonable jitter and delay performance.

# CHAPTER 3. A SERIAL LINK RECEIVER USING LOCAL INJECTION-LOCKED RING OSCILLATOR

In the previous chapter, design considerations of serial links have been addressed on a system level. In this chapter, some circuit techniques will be discussed to achieve high power efficiency.

Recent serial link receivers have shown improvements in power efficiency by focusing on reducing dynamic clock power using resonantly-tuned LC oscillators, both in global clock distribution [2], [48] and local clock demultiplexing [49], [50]. In this chapter, a multi-channel serial link receiver architecture will be presented, which exhibits further improvements in dynamic clock power consumption by implementing a low-voltage swing, global clock distribution to multiple link locations, where locally-tapped, injection-locked ring oscillators (ILRO) are used to generate tunable quadrature sampling clocks for receiver demultiplexing [51].

#### 3.1 Forwarded Clock Receiver Architectures

A conventional, forwarded clock receiver architecture [35] is shown in Fig. 3.1(a), which consists of the global clock distribution, as well as the local delay/phase locked loop (DLL/PLL) to generate multiple time-interleaved phases. The proceeding

Figure 3.1. (a).Conventional forwarded clock receiver architecture and (b) proposed architecture using ILRO for multiple serial links.

phase rotator use these phases to interpolate the appropriate phase position for the receiver to sample the incoming data. In this architecture, significant power is spent in the receiver clocking and phase generation as each link needs a local, phase rotator-based PLL to deskew the clock phase for recovery of the data [52]. For example, phase rotation alone occupies almost half the total receiver power in [2].

As an alternative to the phase rotator, injection-locked LC oscillators (IL-LCO) can enable clock deskew ability with less power and a lower voltage swing for the

global clock. Hence, injection-locking has recently been proposed for both clock distribution [48], [53] and serial link receivers [49], [54]. As shown from the phase vector diagram in Fig. 3.2(a), when the frequency of the injection signal  $e_{inj}(x)$  is different from the free-running frequency of the signal in the LC tank, e(x), a phase deskew  $\alpha$  will be generated between the resulting outputs  $e_g(x)$  and  $e_{inj}(x)$ . The value  $\alpha$  depends on the frequency difference and locking range, given by Alder's equation [55]:

$$\frac{d\alpha}{dt} = -\omega_{SL} \sin \alpha + \Delta \omega_0 \quad , \quad \omega_{SL} = k / \frac{d\varphi}{d\omega} = k \frac{\omega_0}{2Q}$$

(3.1)

where  $\alpha$  is the phase difference between the resultant output clock and the injection input clock,  $\phi$  is the phase difference between the free-running frequency  $\omega_0$  and the resultant output,  $\omega_{SL}$  is the single-sided locking range, k is the injection strength defined as the ratio of the injection current and the oscillator current, and  $\Delta\omega_0$  is the

Figure 3.2. (a) Phase vector diagram (injection signal  $e_{inj}(x)$ , free-running tank signal e(x) and resultant output e(x)). (b) Deskew with different injection strength k, based on Adler's equation.

frequency difference between  $\omega_0$  and the injection clock. Fig 3.2(b) plots an example of the deskew phase shift along the normalized frequency difference under three injection strength values.

Monolithic LC oscillators typically have better phase noise and jitter performance than their ring oscillator counterparts due to the band-pass nature of LC tank resonators, rejecting out-of-band frequencies and filtering power supply induced noise [56]. However, for highly-parallel serial link applications, per-channel, injection-locked LC oscillators are not desirable, as each receiver would require an individual on-chip inductor, resulting in significant area penalty. In addition, LC-based oscillators exhibit very limited tuning range, may exhibit oscillator pulling due to magnetic coupling from adjacent LC oscillators [57], and do not scale well with continued technology scaling.

Although the jitter performance of free-running ring oscillators is typically worse than LC oscillators, the large jitter transfer bandwidth of injection locking can suppress and high-pass filter a large amount of oscillator phase noise, as will be described in the next section. Therefore, a new forwarded clock receiver architecture using injection-locked ring oscillators (ILRO) is proposed, as shown in Fig. 3.1(b), to deskew the clock used to sample the incoming data.

Compared with the conventional receiver architecture, the ILRO can achieve large phase deskew ability without the power overhead required for the combined DLL, PLL and phase interpolation. Second, it can lock to relatively small voltage

swings of the injected global clock, saving power in the clock distribution. Third, the ILRO can achieve faster phase locking than a conventional PLL because while the loop bandwidth of a PLL is limited to approximately 1/10 of the reference clock [57], injection-locking exhibits non-linear loop bandwidth characteristics.

As shown in Fig. 3.2(b), nonlinearity can be observed in the deskew steps at the edge of locking range, when  $\alpha$  reaches around  $\pm 100^{\circ}$ . However, the linear deskew region can be increased as the injection strength k increases. To further avoid the use of the nonlinear deskew region, each receiver uses 1:4 demultiplexing, implemented with four quantizers clocked by quadrature sampling. Therefore, only  $\pm 45^{\circ}$  phase deskew range of the ring oscillator is required to enable each quadrature phase to achieve full UI range, limiting the deskew to only the linear region.

Compared with the IL-LCO, ILRO consumes less silicon area, larger tuning range, inherent multi-phase generation, and scalability to future CMOS processes. However, because previous analysis on the injection-locking phenomenon is applicable only to tank-based oscillators, new analysis is needed to further understand the behavior of the proposed ILRO.

# 3.2 Analysis on Injection-Locked Ring Oscillators

# 3.2.1 Previous Approaches

Several methods have been proposed in previous works to analyze injection locking in oscillators including: the phasor-based Adler's equation, the

perturbation-based projection vector (PPV) method, and the waveform-based timedomain derivation.

The classic Adler's equation [55] expresses the oscillator behavior under injection locking by using a phasor vector diagram, as shown in (3.1) and Fig. 3.2. Various time-domain solutions to Adler's equation are discussed in [58]-[60]. However, two main factors prevent this approach from being applicable to ring oscillators. First, the output waveform of ring oscillators usually does not exhibit sine wave behavior; however, the adoption of a vector-based analysis relies on the assumption that there exists only a single dominant frequency component [61]. Second, it is required to know the quality factor Q in order to solve  $d\phi/d\omega$  in equation (3.1), which is not well defined for nonharmonic ring oscillators.

The PPV [62] and the transient waveform-based methods [61] are capable of

Figure 3.3. Superposition of waveforms.

analyzing both LC and ring oscillators. However, the PPV method requires a full circuit description at both the transistor and numerical levels, and only the expression for locking range is derived [62]. The analysis in [61] provides good insight into analyzing injection locking in the time domain. However, neither of these two methods gives an analytical expression for evaluating the jitter performance of injection-locked oscillators.

#### 3.2.2 Proposed Approach for ILRO Analysis

Since Adler's equation is still quite simple and is proven useful for capturing the LC oscillator behavior in both the frequency and time domains, this work presents an expansion to Adler's equation that overcomes the two limitations mentioned above, making it suitable for injection-locked ring oscillators. By revisiting the process of Adler's derivation [55], it can be observed:

$$\frac{d\alpha}{dt} = \varphi / \frac{d\varphi}{d\omega} + \Delta\omega_0 \tag{3.2}$$

Note that (3.2) is held for both LC and ring oscillators, as neither the assumption of Q nor a vector diagram approach has been applied yet. Next, alternative methods for finding  $d\phi/d\omega$  as well as the relationship between  $\phi$  and  $\alpha$  are presented.

First,  $d\phi/d\omega$  can be solved directly from the small signal model of each delay cell. Assuming each delay cell contributes one dominant 3dB pole, the loop transfer function H of an N-stage ring oscillator is:

$$H(j\omega) = -\left(\frac{A_0}{1 + j\omega/\omega_{3dB}}\right)^N \tag{3.3}$$

such that its phase and derivative are:

$$\varphi(j\omega) = N \tan^{-1}(\omega/\omega_{3dB})$$

(3.4)

$$\left. \frac{d\varphi}{d\omega} \right|_{\omega = \omega_0} = \frac{N}{2\omega_0} \sin \frac{2\pi}{N} \tag{3.5}$$