#### AN ABSTRACT OF THE DISSERTATION OF

<u>Thomas Brown</u> for the degree of <u>Doctor of Philosophy</u> in Electrical and Computer Engineering presented on June 7, 2011.

Title:

Design and Analysis Techniques for Nano-Joule ADCs and Sampling Linearity

Abstract approved: \_\_\_\_\_

Terri S. Fiez

Two aspects of ADC system performance are addressed in this work. First, the combination of the ADC and its associated reference are co-designed for an energy constrained remote sensing system. Second, sampling linearity is mathematically analyzed as a function of frequency to provide enhanced understanding into an ADC's requisite sampling network. Low energy analog design techniques for emerging systems powered by energy scavenging are demonstrated in the context of an analog-to-digital converter system. It is composed of a variable gain sample-and-hold amplifier, a low voltage reference, a 1.5 bit per stage 9-b cyclic ADC, clock generation, reference buffers, and control logic. A novel Class-AB current mirror amplifier together with correlated level shifting enable wide swing and enhanced gain operation at low supply voltages while reducing current draw. The use of subthreshold

MOSFETs instead of bipolar junction transistors allows the use of traditional bandgap circuit techniques to be employed for a 530 mV reference that is less than a diode voltage drop. Operating from a 750 mV supply voltage and 20.48 kSPS, the ADC and reference consume  $9.5\mu$ A and  $1.5\mu$ A, respectively. The measured 7.9-bit ENOB results in an FoM of 2.24 pJ/step. The total energy consumption is 535 pJ per conversion for the entire system. A novel model predicts tracking nonlinearity (NL) in the form of harmonic distortion (HD) for weakly NL (i.e. SFDR>30dBc) first order open-loop sampling circuits. The mechanisms for the NL are exponential settling, amplitude modulation, phase modulation and discrete-time modulation. The model demonstrates that HD typically increases at 20 dB per decade over most standard operating ranges and is a function of input frequency, sampling bandwidth, input amplitude, the sample rate and component nonlinearity. Application of the model is reduced to the equivalent of frequency-independent nonlinearity analysis over this range, requiring only a Taylor series expansion of the NL time constant. Design insight is given for common MOS switch types, revealing a high correlation between HD and bandwidth. The first method to quantify the trade-off between thermal noise (SNR) and linearity (SFDR) for sampling circuits is presented. Measured HD2, HD3, HD4, and HD5 versus frequency at multiple sample rates of a Sample and Hold test chip fabricated in a  $0.25\mu \text{m}$  1P5M CMOS process and Spectre simulation results support the findings. The results broadly apply to switched capacitor circuits in general and sampling circuits specifically, regardless of technology.

©Copyright by Thomas Brown June 7, 2011 All Rights Reserved

### Design and Analysis Techniques for Nano-Joule ADCs and Sampling Linearity

by

Thomas Brown

### A DISSERTATION

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented June 7, 2011 Commencement June 2012 Doctor of Philosophy dissertation of <u>Thomas Brown</u> presented on June 7, 2011.

APPROVED:

Major Professor, representing Electrical and Computer Engineering

Director of the School of Electric Engineering and Computer Science

Dean of the Graduate School

I understand that my dissertation will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my dissertation to any reader upon request.

Thomas Brown, Author

### ACKNOWLEDGEMENTS

I would like to thank the National Science Foundation (NSF) for partial financial support for this work under grant EF-0529223, the U.S. Army Research Labs (ARL) for partial financial support, and Jazz Semiconductor for chip fabrication.

## TABLE OF CONTENTS

|   |                                            | —                                                                                                      | 0                                                                      |  |  |  |  |  |  |  |

|---|--------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 1 | duction and Objectives                     | 1                                                                                                      |                                                                        |  |  |  |  |  |  |  |

|   | 1.1                                        | Overview                                                                                               |                                                                        |  |  |  |  |  |  |  |

|   | 1.2                                        | ADC Systems for Nano-Joule Sensing1.2.1 Intended Application1.2.2 General Low-Power ADC Considerations | $     \begin{array}{c}       1 \\       2 \\       5     \end{array} $ |  |  |  |  |  |  |  |

|   |                                            | 1.2.3 Voltage Reference Power Implications                                                             | 7                                                                      |  |  |  |  |  |  |  |

|   | 1.3 Frequency Dependent Sampling Linearity |                                                                                                        |                                                                        |  |  |  |  |  |  |  |

|   | 1.4                                        | Outline of Dissertation                                                                                | 10                                                                     |  |  |  |  |  |  |  |

| 2 | A na                                       | no-Joule Analog-to-Digital Converter for Battery-free Sensing Systems                                  | 11                                                                     |  |  |  |  |  |  |  |

|   | 2.1                                        | Abstract                                                                                               | 11                                                                     |  |  |  |  |  |  |  |

|   | 2.2                                        | Introduction                                                                                           | 12                                                                     |  |  |  |  |  |  |  |

|   | 2.3                                        | Low Energy Design Fundamentals                                                                         | 14<br>15<br>17                                                         |  |  |  |  |  |  |  |

|   |                                            | 2.3.3       Time Duration                                                                              | 19<br>20                                                               |  |  |  |  |  |  |  |

|   | 2.4                                        | Circuit Implementation                                                                                 | 21<br>22<br>23<br>35<br>38                                             |  |  |  |  |  |  |  |

|   | 2.5                                        | Measurement Results                                                                                    | 39                                                                     |  |  |  |  |  |  |  |

|   | 2.6                                        | Conclusion                                                                                             | 42                                                                     |  |  |  |  |  |  |  |

| 3 | Frequency Dependent Sampling Linearity 46  |                                                                                                        |                                                                        |  |  |  |  |  |  |  |

|   | 3.1                                        | Abstract                                                                                               | 46                                                                     |  |  |  |  |  |  |  |

|   | 3.2                                        | Introduction                                                                                           | 47                                                                     |  |  |  |  |  |  |  |

|   | 3.3 System Linearity                       |                                                                                                        |                                                                        |  |  |  |  |  |  |  |

|   | 3.4                                        | Component Nonlinearity                                                                                 | 52<br>56<br>57<br>60                                                   |  |  |  |  |  |  |  |

|   |                                            |                                                                                                        |                                                                        |  |  |  |  |  |  |  |

### Page

# TABLE OF CONTENTS (Continued)

|       |                                                | $\underline{\text{Page}}$ |  |  |  |  |  |

|-------|------------------------------------------------|---------------------------|--|--|--|--|--|

|       | 3.4.4 High Frequency HD $(\omega \gg 1/\tau)$  |                           |  |  |  |  |  |

| 3.5   | Application to Circuits                        | . 65                      |  |  |  |  |  |

|       | 3.5.3 Transistor Level Simulation Examples     |                           |  |  |  |  |  |

| 3.6   | Design Implications                            |                           |  |  |  |  |  |

| 3.7   | Silicon Verification                           |                           |  |  |  |  |  |

|       | 3.7.2Measurement Setup3.7.3Measurement Results |                           |  |  |  |  |  |

| 3.8   | Conclusion                                     | . 82                      |  |  |  |  |  |

| 3.9   | Harmonic Distortion Derivation                 | . 84<br>. 85<br>. 87      |  |  |  |  |  |

| 4 Con | clusion and Directions for Future Work         | 91                        |  |  |  |  |  |

| 4.1   | 4.1 Conclusion                                 |                           |  |  |  |  |  |

| 4.2   | Directions for Future Work                     | . 92                      |  |  |  |  |  |

Bibliography

## LIST OF FIGURES

| Figure |                                                                                                                                                                                                                                                                                                   | Page  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 1.1    | Proposed passive sensor network.                                                                                                                                                                                                                                                                  | 3     |

| 1.2    | Sensor node block diagram.                                                                                                                                                                                                                                                                        | 4     |

| 1.3    | Estimated sensor node energy absorbed over a 5 minute duration<br>as a function of distance for a 1W peak (28.5 dBm) spread carrier.<br>50% conversion efficiency is assumed.                                                                                                                     | 6     |

| 2.1    | A system block diagram of an energy scavenging wireless sensor node                                                                                                                                                                                                                               | e. 13 |

| 2.2    | The ADC and reference voltage system block diagram                                                                                                                                                                                                                                                | 22    |

| 2.3    | Schematics of (a) the 1.5b per stage cyclic ADC architecture and (b) the switched capacitor implementation of a single stage                                                                                                                                                                      | 26    |

| 2.4    | Schematics of the comparator (a) switched capacitor top level that<br>uses two phase non-overlapping clocking, (b) the preamplifier, and<br>(c) the second stage dynamic latch.                                                                                                                   | 28    |

| 2.5    | Simplified schematic of multi-purpose switched capacitor amplifier that functions as a preamplifer SHA, temperature sensor signal processor and cyclic ADC stage                                                                                                                                  | 30    |

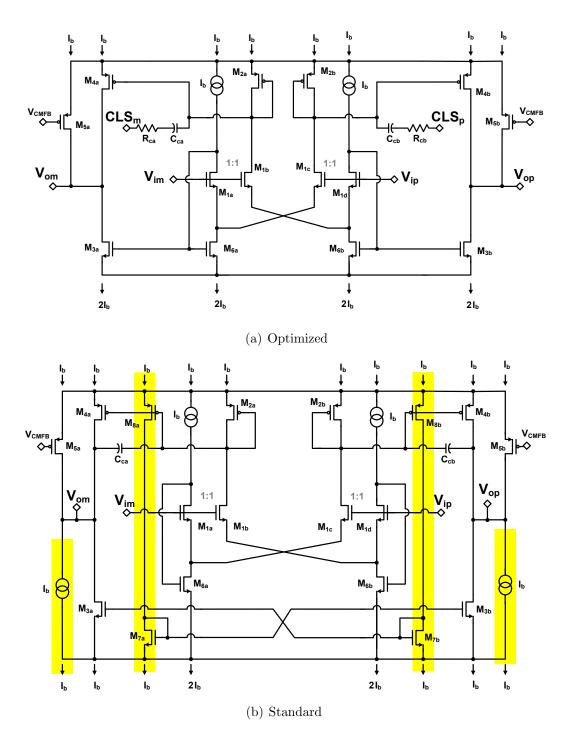

| 2.6    | Schematics of (a) the optimized version that saves power by elimi-<br>nating two current branches and (b) A fully differential version of<br>the class-AB current mirror OTA adapted from [39]. The compo-<br>nents eliminated from the optimized version in this work are shaded<br>for clarity. | 34    |

| 2.7    | (a) Simplified schematic of the low voltage reference circuit. Weak inversion PMOS devices $P_1$ and $P_2$ replace the BJTs in a traditional bandgap reference. (b) Simplified schematic of the chopper stabilized OTA.                                                                           | 36    |

| 2.8    | Schematic of the common-mode generator and buffer                                                                                                                                                                                                                                                 | 39    |

| 2.9    | Die photo of the 130 nm CMOS 1.475 mm by 2.4 mm integrated circuit.                                                                                                                                                                                                                               | 40    |

| 2.10   | Measured performance of the 9-bit ADC at 750 mV at 20.48 kSPS:<br>(a) spectrum, and (b) DNL and INL                                                                                                                                                                                               | 43    |

# LIST OF FIGURES (Continued)

| Figur | 2                                                                                                                                                                                                                                                                                                                                                                                           | Page |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1   | <ul> <li>Measured performance of the reference voltage at a 750 mV supply:</li> <li>(a) Noise. With chopping on, the reference noise is within the noise floor the the Audio Precision test system.</li> <li>(b) Reference voltage variation versus temperature.</li> </ul>                                                                                                                 | . 44 |

| 2.1   | 12 Plot of SNDR versus power consumption for ADCs from ISSCC and SVLSI from 1997-2011 [33].                                                                                                                                                                                                                                                                                                 | . 45 |

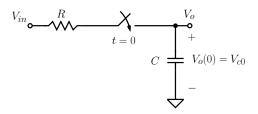

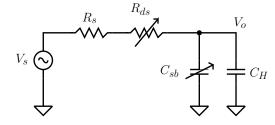

| 3.1   | Sampling circuit model.                                                                                                                                                                                                                                                                                                                                                                     | . 49 |

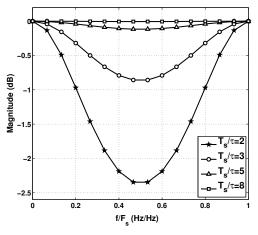

| 3.2   | 2 Frequency response of the discrete-time LPF due to not resetting<br>the sampling capacitor                                                                                                                                                                                                                                                                                                | . 53 |

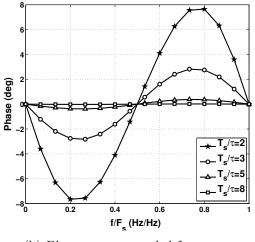

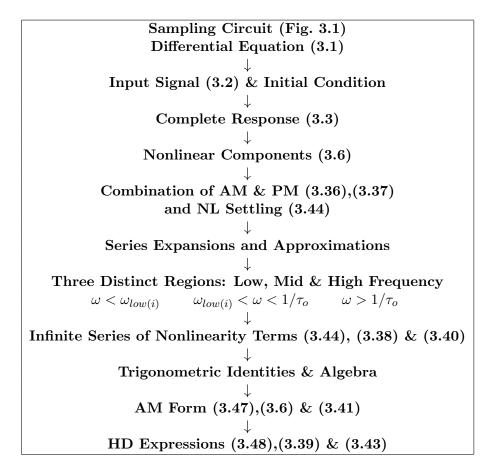

| 3.3   | 3 Overview of harmonic distortion derivation.                                                                                                                                                                                                                                                                                                                                               | . 54 |

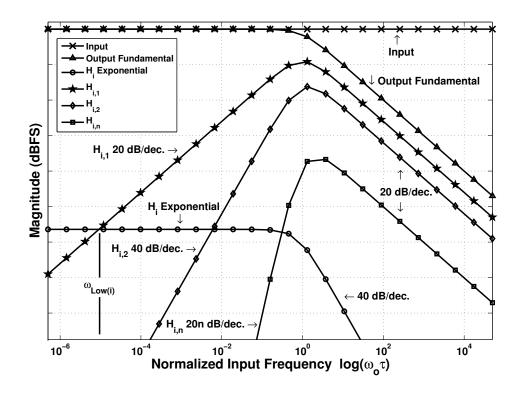

| 3.4   | 4 Each harmonic (e.g. HD2, HD3, etc.) may be represented as an infinite summation. The components of the summations are plotted along with the input and output fundamental tones for reference. The largest spurious component sets the HD value at a given frequency. In effect, this is a drawing of the NL terms that compose each harmonic as described mathematically in Appendix 3.9 | . 56 |

| 3.8   | 5 Sampling circuit reduced model                                                                                                                                                                                                                                                                                                                                                            | . 65 |

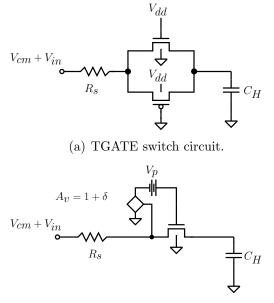

| 3.0   | 6 Circuit bias for Taylor series expansion of each of the switch types.                                                                                                                                                                                                                                                                                                                     | 67   |

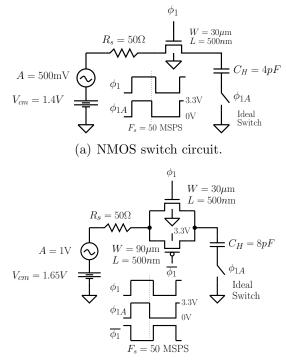

| 3.'   | 7 NMOS and TGATE switch circuits for Spectre transient simulations<br>using EKV device models.                                                                                                                                                                                                                                                                                              | . 68 |

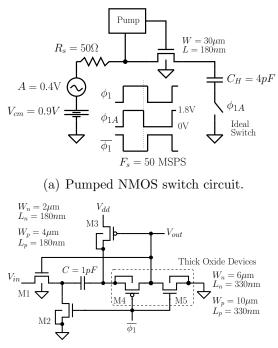

| 3.8   | Pumped NMOS switch circuit for Spectre transient simulations with $0.18\mu$ m BSIM3v3 device models.                                                                                                                                                                                                                                                                                        | . 69 |

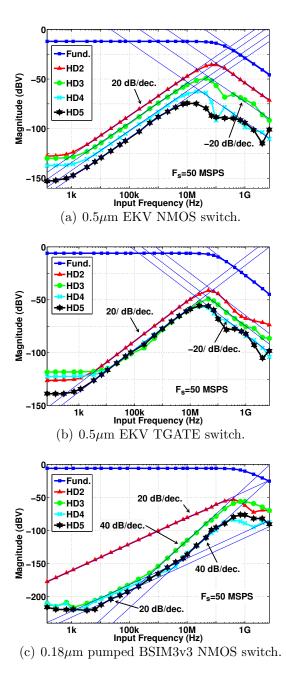

| 3.9   | Simulated HD2-HD5 vs input frequency of three switch types. Spectre transient simulations were run on the circuits in Fig. 3.7 and 3.8. Using strobed data at the end of the hold phase, DFTs were taken and the HD2-HD5 saved for plotting. These plots show what the harmonics would look like if all other effects were negligible. Some simulator artifacts are present.                | . 73 |

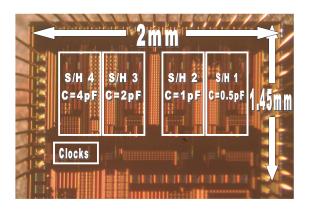

| 3.1   | 10 Die photo of the test chip                                                                                                                                                                                                                                                                                                                                                               | . 76 |

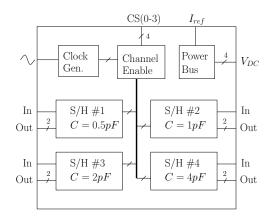

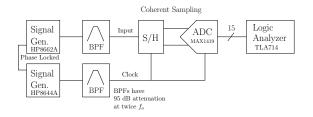

| 3.1   | 11 Top level block diagram of test chip                                                                                                                                                                                                                                                                                                                                                     | . 77 |

# LIST OF FIGURES (Continued)

| Figure |                                                                                                                                                                                                                           | Page |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

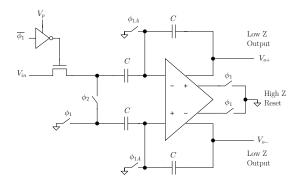

| 3.12   | Simplified S/H test circuit. An NMOS sampling switch of size $15/0.35 \ \mu m$ is used. Supply $V_p$ provides a means to adjust the sampling time constant to fit the HD curves within the limited measurement bandwidth. | . 77 |

| 3.13   | Measurement setup                                                                                                                                                                                                         | . 78 |

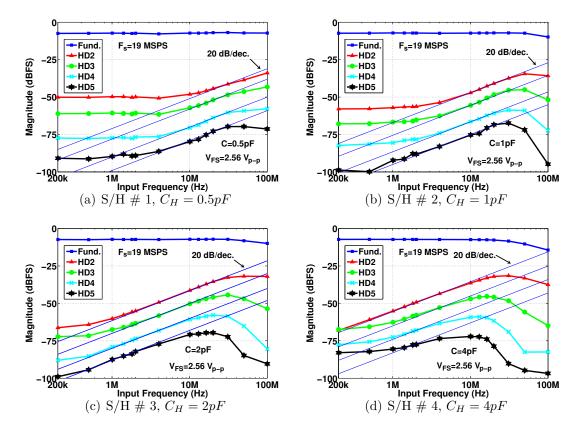

| 3.14   | Measured fundamental, HD2, HD3, HD4, and HD5 versus input frequency at $F_s = 19MSPS.$                                                                                                                                    | . 79 |

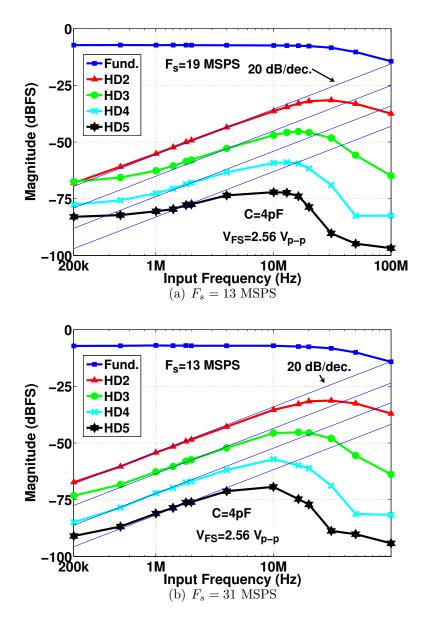

| 3.15   | Measured fundamental, HD2, HD3, HD4, and HD5 vs. Input Frequency on S/H #4, $C_H = 4pF$ .                                                                                                                                 | . 82 |

# LIST OF TABLES

| <u>Table</u> |                                                                                                                   | Page |

|--------------|-------------------------------------------------------------------------------------------------------------------|------|

| 1.1          | Micro-Power ADCs                                                                                                  | . 8  |

| 2.1          | Performance summary and comparison table of low power ADCs with and without on-chip reference voltage generation. | . 42 |

| 3.1          | $F_s = 19MSPS$ Mid Frequency Harmonic Distortion in dBFS                                                          | . 81 |

| 3.2          | Low Frequency, $f_{in} = 200 kHz$ , Harmonic Distortion, dBFS, due to charge injection and exponential settling.  | . 81 |

| 3.3          | Expansion of $\beta_{i,n}$ terms in (3.39) for each Harmonic                                                      | . 85 |

| 3.4          | Taylor Coefficients of $V_{o-N}(V_{in})$                                                                          | . 88 |

| 3.5          | Expansion of $\chi(k_l)$                                                                                          | . 88 |

| 3.6          | Expansion of $d(k_l(\alpha_i))$                                                                                   | . 89 |

#### Chapter 1 – Introduction and Objectives

#### 1.1 Overview

Analog-to-digital converters (ADC) are an essential part of modern digital systems because they translate the physical, real world, analog signals into quantized form to enable storage, processing and communication digitally. Various aspects of the ADC directly impact the performance of the overall system. These include speed, power, resolution, accuracy, and linearity. Two different aspects of ADC systems are considered in this work. First, the combination of an ultra-low-power ADC and its requisite reference voltage for passively powered sensor nodes is considered. The objective is the simultaneous reduction of both power and energy consumption. The second aspect considered is a detailed mathematical analysis into frequencydependent sampling linearity of an ADC's input network. This is particularly important for high-speed applications in communication systems. The result of the design and analysis techniques introduced in this work provides design intuition and results in optimized ADC performance.

#### 1.2 ADC Systems for Nano-Joule Sensing

Applications for low-resolution, ultra-low-power analog-to-digital converters have arisen in battery-free systems for sensing and measurement. These systems must

be able to accurately measure, collect, process, store, transmit and receive data. Research and product development are presently being conducted for applications such as Smart Dust [1], tire-pressure monitoring [2] and wireless sensor networks [3,4]. Moreover, many medical-monitoring applications with similar functionality are possible [5,6]. These battery-free systems derive power from energy scavenging from the environment and provide storage for use on demand. Possible energy sources include solar, kinetic (e.g., a rotating tire) and electro-magnetic (e.g., radio frequency (RF) carriers) [7,8]. Because the energy accumulation can currently and for the foreseeable future only provide limited reserves, power consumption is the most critical aspect in the design of these systems. Moreover, the power/energy budget is at least an order of magnitude more restrictive than that of traditional battery powered electronics. Consequently, this directly affects all aspects of design, from the system level all the way down to transistor sizing, all of which must primarily be geared toward power savings. To do so, both speed and resolution must be carefully considered. Thus the focus of this work is to develop low to medium resolution (6-9b) ADCs for low speed (<100 kSPS) with a reduction of power/energy consumption by an order of magnitude over the current state of the art [1,9].

#### 1.2.1 Intended Application

This work focuses on an ADCs for a proposed wireless temperature sensor network [10]. The network will be deployment in a watershed in the H.J. Andrews Long-term Ecological Research Site in the Oregon Cascade Mountains and log temperature fluctuations with high temporal and spacial resolution. The purpose is to enable better understanding of cold-air drainage which will enhance knowledge of ecological processes in watersheds. Figure 1.1 illustrates the planned deployment. The sensors, approximately 0.5m off the ground, will be spaced 10m apart in a radial pattern about the three 30m tall base-stations (BS). Data is to be transmitted in a peer-to-peer fashion radially toward the BS, with sensors up to 50m away from each BS.

Figure 1.1: Proposed passive sensor network.

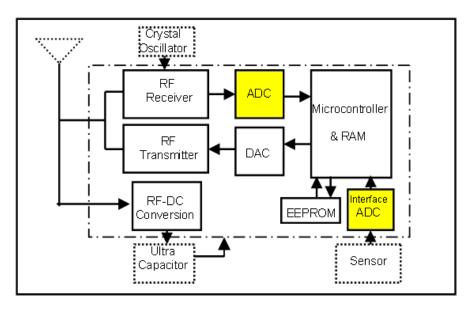

The passively powered peer-to-peer network operates in the 902-928 MHz licensefree ISM spectrum using differentially-coherent binary phase-shift keying (DBPSK) direct-sequence spread spectrum (DSSS) with time division multiple access (TDMA). A total of 1024 time slots will be allocated over a five minute span. Each sensor will have to wake up to measure temperature, compress and store the data, transmit data to its closest (inner) neighbor as well as receive data from its closest (outer) neighbor. Figure 1.2 shows the block diagram of the sensor node. There are two ADCs, one to measure temperature and another to quantize the RF receive channel for demodulation and processing. Sufficient signal-to-noise-and-distortion ratio (SNDR) in the receive path has been determined to be 30 dB, translating to a 5-6b converter with an effective number of bits (ENOB) of at least 4.69b. With a chip rate of 4.096 MCPS, the RF ADC must have 3-4 times the bandwidth of the chip rate for digital demodulation, necessitating a sample rate in the range of 24.6 MSPS to 32.8 MSPS. The sensor ADC must be able to resolve temperature to  $\pm 0.5^{\circ}$ C over a range from -10°C to +40°C, implying a 7-8b ADC; samples are to be taken once during each five minute time slot, leaving the choice of the sampling rate as an additional degree of freedom in the design.

Figure 1.2: Sensor node block diagram.

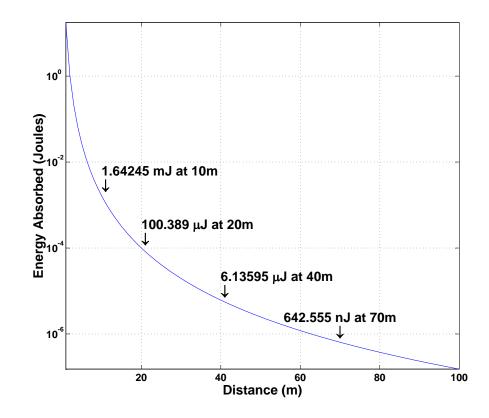

In order to comprehend just how little power can be dissipated in this application, it is insightful to know how much energy each sensor will accumulate over time. For a single 5 MHz channel in the 902-928 MHz license-free ISM spectrum, the maximum radiated power level is 1W peak [11]; a carrier from each BS will power the sensors from this source. Using Hata's path loss model [12], the received power level may be estimated<sup>1</sup>. Presuming conversion efficiency of 50%, the energy absorbed over the 5 minute span is graphed in Figure 1.3. A low-power (e.g., 1 mW) ADC would burn 300 mJ of energy if run continuously over the same 5 minute span. Yet the closest sensor would accumulate only approximately 1.6 mJ of energy. The factor of 187.5 difference underlies the need for ultra-low-power ADCs, as they may only use a fraction of the energy budget.

#### 1.2.2 General Low-Power ADC Considerations

Common to all low-power ADC design, regardless of where the particular design fits in the speed/power/accuracy space, there are general practices to adhere to. First, the number of active elements (e.g., amplifiers and comparators) should be minimized because they are the greatest power sinks in ADCs and analog design in general. After reducing the number of active elements, the power consumed by the active elements should be diminished. To do so, capacitance must be minimized; extra capacitance slows down amplifiers, requiring higher bias currents and

<sup>&</sup>lt;sup>1</sup>It should be noted that this model can at best give the order of magnitude of the received power because it was never intended to work over such short distances (< 200m). More accurate models for this type of environment are not available.

Figure 1.3: Estimated sensor node energy absorbed over a 5 minute duration as a function of distance for a 1W peak (28.5 dBm) spread carrier. 50% conversion efficiency is assumed.

hence power to charge them. The amplifiers may be slowed via either slew limiting or an increased feedback factor. Matching considerations dictated by the converter/stage resolution typically set the lower bound on capacitance. Techniques such as dynamic biasing [13,14] and optimal settling time compensation (i.e. phase margin) [15,16] can be used to diminish the requisite current dissipation in a given application. Moreover, circuit techniques (i.e. architecture or error compensation) that can tolerate less accurate components also lead to reduced power consumption. However, only a fractional improvement is available via optimization, shifting the burden to the system level for large (i.e. an order of magnitude or better) improvements by reducing the required speed and/or resolution.

Over 10 ADCs with power consumption less than  $500\mu$ W have been reported in the last decade [1,17–28]. Table 1.1 summarizes their characteristics. Architectures vary from SAR to various forms of  $\Delta\Sigma$  modulators and Extended Counting ( $\Delta\Sigma$  for MSBs and SAR/algorithmic for LSBs). Additionally, a logarithmic ADC using an integrating (Dual Slope) architecture has also been published [28]. Power dissipations range from just under  $1\mu$ W to  $340\mu$ W, with supply voltages from 0.7 V to 3.3 V, resolutions (ENOB) from 7-13b and bandwidths<sup>2</sup> up to 75 kHz. The energy per sample per effective bit ranges from 4.43 pJ/bit to 2.5nJ/bit, with the SAR ADCs outperforming the  $\Delta\Sigma$  modulators. This is underscored by the absence of on chip decimation filters for the  $\Delta\Sigma$  modulators.

#### 1.2.3 Voltage Reference Power Implications

A reference circuit that is independent of external parameters such as supply voltage and temperature variations is vital to an ADC's performance. Errors in the reference directly lead to errors in the quantized output. For this reason, using supply voltage as a reference [1, 30, 31] is not a robust solution since it is poorly controlled in battery-free systems. Consider that even a 5 % variation in the supply voltage used as a reference limits performance to 4.3 bits. Moreover, the reference

<sup>&</sup>lt;sup>2</sup>i.e. Effectively half the sample rate of an equivalent Nyquist rate ADC,  $F_s/2$ .

| Ref. | Power         | BW    | ENOB  | Vdd  | $\rm E/bit^*$ | Process           | Architecture                                 |

|------|---------------|-------|-------|------|---------------|-------------------|----------------------------------------------|

|      | (μ <b>W</b> ) | (kHz) | (b)   | (V)  | (pJ/b)        |                   |                                              |

| [1]  | 3.1           | 50    | 7.0   | 1    | 4.43          | $0.25 \mu m CMOS$ | SAR                                          |

| [17] | 40            | 16    | 10.01 | 0.9  | 124.92        | $0.5\mu m CMOS$   | $\Delta\Sigma$ -3, OSR=96                    |

| [18] | 37.7          | 10    | 12.0  | 0.9  | 157.08        | $0.18 \mu m CMOS$ | $\Delta\Sigma$ -2, OSR=200                   |

| [19] | 60            | 8     | 10.34 | 1    | 362.71        | $0.35 \mu m CMOS$ | $\Delta\Sigma$ -3, MASH 2-1, OSR=64          |

| [21] | 250           | 3.906 | 12.5  | 2    | 2560.5        | $1.0\mu m CMOS$   | $\Delta\Sigma$ -3, OSR=64                    |

| [20] | 230           | 20    | 12.5  | 3.3  | 460.06        | $1.2\mu m CMOS$   | Passive $\Delta\Sigma$ -2, OSR=250           |

| [29] | 340           | 8     | 11.17 | 1.95 | 1902.51       | $1.2 \mu m CMOS$  | $\Delta\Sigma$ -3, OSR=64                    |

| [23] | 216           | 24.3  | 8.68  | 2.7  | 512.17        | $2.0\mu m CMOS$   | $\Delta\Sigma$ -2, OSR=50                    |

| [24] | 30            | 75    | 8.21  | 1    | 24.35         | $0.18\mu m CMOS$  | SAR                                          |

| [24] | 0.85          | 2.05  | 6.9   | 0.5  | 30.04         | $0.18 \mu m CMOS$ | SAR                                          |

| [26] | 135           | 25    | 11.34 | 1.5  | 238.19        | $0.5\mu m CMOS$   | $\Delta\Sigma$ -3, OSR=48                    |

| [25] | 80            | 8     | 10.84 | 0.7  | 461.37        | $0.18\mu m CMOS$  | $\Delta\Sigma$ -3, OSR=64                    |

| [27] | 340           | 25    | 7.9   | 1    | 860.76        | $1.2\mu m CMOS$   | SAR                                          |

| [22] | 150           | 8     | 13.0  | 1.2  | 721.34        | $0.8\mu m CMOS$   | Extended Counting ( $\Delta\Sigma$ -1 & SAR) |

| [28] | 3             | 0.15  | 8     | 3    | 1250          | $1.5\mu m$ BiCMOS | Dual Slope (logarithmic)                     |

Table 1.1: Micro-Power ADCs

\* Calculated as Power/2/BW/ENOB

must be able to drive the ADC to meet current draw and settling without a loss in accuracy.

For micro-power ADCs, the power required to generate the reference voltage is significant. Even low power references consume power on the order of 10 to 100  $\mu$ A [32]. For a 1 V supply, this translates to power consumption of 10 to 100  $\mu$ W. With a 10  $\mu$ W ADC, an increase in power consumption by a factor of 2 to 10 results. Following this observation, power saving in the ADC are negated by the reference power consumption. Consequently, micro-power ADC systems require that the ADC and reference voltage be co-designed for the maximum possible power savings. For applications that require battery-free operation, ADC and reference co-design is of vital importance.

#### 1.3 Frequency Dependent Sampling Linearity

The sampling process converts a continuous time signal with a continuous amplitude range into a discrete-time signal with a continuous amplitude range. In other words, it quantizes the input into discrete time steps but leaves the amplitude unchanged. The quality of this process is vital to overall system performance because errors cannot be removed once they occur. ADCs require a high performance sample-and-hold amplifier (SHA) to change a fast moving signal into effectively a DC one that facilitates accurate quantization.

One of the most important characteristics of the sampling process is the linearity in terms of harmonic distortion. This is because harmonic distortion produces spurs in the frequency domain that corrupt the spectrum. Increasing input frequency exacerbates the problem as linearity degrades. In a communication system in particular, these spurs make it impossible to distinguish a small signal in the presence of the nonlinearity of a larger signal. Furthermore, large spurs limit the overall accuracy of the ADC that the SHA precedes in the form of total harmonic distortion (THD). The net effect is degradation of the ADC's signal to noise and distortion ratio (SNDR) and its the effective number of bits (ENOB), a measure of the effective resolution of the SHA and ADC system.

For these reasons, understanding the mechanisms by which a sampling circuit introduces harmonic distortion as a function of the input frequency plays a vital role in improving the performance of communication systems. Improved understanding of nonlinearity mechanism facilitates the transmission of more information in future communication systems. This work provides an in-depth analysis of the frequency dependent linearity of the sampling circuit.

#### 1.4 Outline of Dissertation

The remainder of this dissertation is as follows: Chapter II analyzes the ultra-lowpower/energy sensor ADC. Chapter III derives expressions for sampling circuit harmonic distortion terms as a function of the input frequency and provides design insight into sampling network design considerations. Chapter IV summarizes the findings, drawing conclusions, and points to directions for future research.

# Chapter 2 – A nano-Joule Analog-to-Digital Converter for Battery-free Sensing Systems

#### 2.1 Abstract

Low energy analog design techniques for emerging systems powered by energy scavenging are demonstrated in the context of an analog-to-digital converter system. It is composed of a variable gain sample-and-hold amplifier, a low voltage reference, a 1.5 bit per stage 9-b cyclic ADC, clock generation, reference buffers, and control logic. A novel Class-AB current mirror amplifier together with correlated level shifting enable wide swing and enhanced gain operation at low supply voltages while reducing current draw. The use of subthreshold MOSFETs instead of bipolar junction transistors allows the use of traditional bandgap circuit techniques for a 530 mV reference that is less than a diode voltage drop. Operating from a 750 mV supply voltage and 20.48 kSPS, the ADC and reference consume  $9.5\mu$ A and  $1.5\mu$ A, respectively. The measured 7.9-bit ENOB results in an FoM of 2.24 pJ/step. The total energy consumption is 535 pJ per conversion for the entire system.

#### 2.2 Introduction

Severely energy limited systems (ELS) present considerable design challenges compared to traditional battery powered applications. Whether passively powered by scavenging energy or running off of a single battery for long periods, ELS remain dormant in long sleep states and only wake up for brief bursts of activity before returning to sleep. In order to maximize performance and functionality, ELS must be optimized to minimize the energy, not power, required to perform any given operation. Moreover, because the peak power available from the energy storage device limits the maximum power available even in a short burst, low overall power draw is also a requirement.

Considerable work has been done to improve the energy efficiency of analogto-digital converters (ADC) in terms of energy per conversion step [33]. The most energy efficient ADCs are typically low resolution and low speed, consuming primarily dynamic energy [33]. While some reported designs do include the dynamic power drawn from voltage references or the input, they exclude the power required to generate the voltage reference and its associated buffers. At low speeds, where low energy ADCs have very low power consumption, this additional power easily exceeds that of the ADC core [9]. Consequently, for ELS that must generate a reference locally, energy optimization must include these additional blocks.

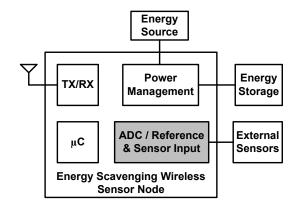

The goal of this work is to demonstrate core building blocks for signal processing, quantization, and sensing in an energy limited environment. A block diagram of such a system is shown in Fig. 2.1. The objective is to push the limits on power savings by reducing both the supply voltage and operating current. Simultaneous reduction in the 'on' time also decreases the energy consumption. Included in the prototype design are a subthreshold MOSFET voltage reference, a variable gain preamplifier for external small signal inputs, and a 9 bit ADC core. Systematic circuit optimization enables dramatic improvements in power and energy use without sacrificing precision.

Figure 2.1: A system block diagram of an energy scavenging wireless sensor node.

The remainder of this chapter is organized as follows: Section 2.3 describes the underlying principles to low energy design. Section 2.4 discusses the circuit design details of the prototype energy optimized system. Section 2.5 presents the measured performance of the prototype design. Finally, Section 2.6 summarizes the results and puts them in context compared to competing designs from the literature.

#### 2.3 Low Energy Design Fundamentals

Considerations for low power/energy design of analog circuitry in general and ADCs specifically are discussed. This directly leads to insight into ADC architecture choice, as well as design trade-offs therein. The larger ADC system that includes the reference voltage circuit and its buffer is also included. For low-power ADCs in particular, generating and buffering the reference consumes a nontrivial portion of the power/energy budget.

Low energy design differs from low power design in that the time duration over which a circuit operates also comes into play. Mathematically, the energy consumed may be expressed as

$$E = \int_0^T P dt, \qquad (2.1)$$

where E is energy, P is power, and T is the duration of the operation. Assuming constant values that do not vary as a function of time, (2.1) reduces to

$$E = VIT, (2.2)$$

where V is the voltage and I is the current. From (2.2) it is clear that there are three ways to reduce energy consumption: 1) reduce the supply voltage, 2) decrease the current draw, and 3) decrease the 'on' time duration. In the limit that T goes to infinity and the circuit operates continuously, low energy and low power design are equivalent. While it is possible to reduce energy consumption by decreasing only one of the three, the largest reductions come about through reductions in all three simultaneously. However, reductions in any of these terms entail circuit design trade-offs that limit the extent of the reduction that is attainable without adversely affecting other design requirements. The rest of this section delves into these trade-offs.

#### 2.3.1 Low Voltage

Reductions in the supply voltage provide a means to reduce power and energy at the expense of available headroom. This reduced headroom limits the maximum signal swing possible within the supply rails. Thus, an upper bound is placed upon the signal power. Consequently, for a given signal-to-noise ratio (SNR), the noise floor must be lowered at the expense of higher power consumption in the form of increased current draw. The noise power  $(V_n^2)$  for a given SNR and a rail-to-rail input signal bound by the power supply voltage  $V_{DD}$  is found by applying the definition of SNR:

$$V_n^2 = \frac{V_{DD}^2}{8SNR}.$$

(2.3)

At a 1V supply and SNR of 60 dB or equivalently 10 bits,  $V_n$  must be less than 353.6  $\mu$ V. Furthermore, as the required SNR increases, the noise floor requirement becomes even more difficult to meet such that 22.3  $\mu$ V is required at the 14 bit level. A three decibel improvement in SNR results for a fully-differential implementation since the signal adds directly while uncorrelated noise power combines in a rootsum-square manner. When considering the thermal noise for a MOSFET in strong inversion, the maximum noise floor can be directly related to the current draw. The thermal noise is expressed as  $V_n^2 = \frac{8K_B T \Delta f}{3g_m}$ , where  $K_B$  is the Boltzman's constant,  $g_m$  is the device's transconductance, T is the temperature in degrees Kelvin, and  $\Delta f$  is the bandwidth. After substituting  $g_m = \sqrt{2\mu C_{OX} \frac{W}{L} I_D}$ , where  $\mu$ , W, L, and  $C_{OX}$  are the electron mobility, transistor width, transistor length and oxide capacitance per unit area, respectively, the minimum drain current can be shown to be

$$I_{D,min} = \frac{(64K_B T \Delta f \ SNR)^2}{18\mu C_{OX} \frac{W}{L} V_{DD}^4}.$$

(2.4)

From (2.4), a 1 bit improvement, or a factor of 2 increase in SNR directly leads to a four fold increase in the required current.

Aside from SNR considerations, decreases in supply voltage complicate amplifier design. First, reduced headroom limits the ability to cascode transistors as a means to enhance output impedance and thus gain. While a cascode is possible at 1V, at 0.5V there is insufficient headroom. In either case, a wide swing output stage is required. Without a wide swing output stage, signal power must be reduced. Accounting for the range limitations of the output stage, the maximum peak-to-peak swing reduces to  $V_{DD} - 2V_{DSAT}$ , where  $V_{DSAT}$  is the minimum drain-source voltage to keep a MOSFET in saturation. Given this, the maximum root-mean-square noise floor decreases to

$$V_n^2 = \frac{(V_{DD} - 2V_{DSAT})^2}{8SNR}.$$

(2.5)

For comparison, the noise floor reduces to 212.1  $\mu$ V and 13.4  $\mu$ V for 10 and 14 bit systems, respectively, with  $V_{DSAT} = 200$  mV and  $V_{DD} = 1$ V. Because two gain stages are required to meet swing and gain requirements, additional current is drawn in the extra amplifier stages. Moreover, compensation for stable closed loop operation becomes more challenging since the additional poles introduced require higher current draw to push them to higher frequencies. These additional poles close dominant pole reduce the attainable bandwidth.

Dynamic energy due to capacitor charging and discharging decreases with the signal swing. This affects both digital gates and switched capacitor operation. The energy required to switch a capacitance is proportional to the value of the capacitance and the square of the voltage across it

$$E = \frac{1}{2}CV^2, \qquad (2.6)$$

where C is the capacitance and V is the switching voltage. Thus decreased voltage directly leads to energy savings proportional to the square of the voltage difference. The switching energy is independent of the time required to charge the capacitance.

#### 2.3.2 Low Current

The second means to reduce energy draw comes about by decreasing current consumption. Paramount in this is decreasing the loading that the active circuitry has to drive. Thus, resistances must be increased to reduce current, while capacitances decreased to reduce charge. Yet, each comes with design compromises discussed shortly. Furthermore, decreasing current draw in active circuits also increases thermal noise since the transconductance is reduced, thereby increasing the input referred noise.

Large resistances entail large physical areas with small widths that result in poor matching and large parasitic capacitances; the combination of large resistances and capacitances creates low frequency poles that limit the maximum obtainable bandwidth. Larger resistances result in a corresponding increase in thermal noise. Resistances become an issue for reference circuits in particular.

Since capacitors represent the primary loading in switched capacitor circuits, decreased capacitance provides an important means to decrease loading. Smaller capacitance reduces power in that poles are pushed to higher frequencies at a given current, while also increasing amplifier slew rates. The penalty for lower capacitance in switched capacitor circuitry is a degradation in matching and thus accuracy. Calibration may be required if the capacitances are decreased aggressively. However, capacitances can only be decreased to the thermal noise limit imposed by the band limited noise power in terms of  $K_BT/C$ .

Another means to reduce the current draw is to increase the current efficiency. Subthreshold biasing accomplishes this by decreasing the current density through increased device size. Significant savings can occur in this manner since the transconductance of a device in the subthreshold regime is proportional to the quiescent current. In traditional strong inversion operation, the transconductance is proportional to the square root of the quiescent current. A doubling of the transconductance entails a doubling of the current in weak inversion, while strong inversion operation necessitates a quadrupling of the current draw. Consequently, subthreshold operation realizes a factor of two reduction in current for a given transconductance.

However, subthreshold operation does not scale to very high frequencies because the larger physical size of the transistors results in comparatively large parasitic capacitances that decrease bandwidth. At low frequencies, this is not a concern. Subthreshold design also suffers from degraded matching relative to strong inversion because of an increased dependence on a transistor's threshold voltage leading to greater offset voltage and current mirror mismatches.

Significant current reductions occur from decreasing the number of active blocks needed to implement the desired function. Architecture choice and the associated algorithm that the circuit implements directly affect this. For example, a successive approximation ADC has only a single active component in its comparator, whereas a pipeline ADC requires multiple amplifiers and comparators [34]. If both structures are able to meet the design requirements, the successive approximation ADC will do so with a lower current due to the reduced number of active components.

#### 2.3.3 Time Duration

Finally, energy may be saved by reducing the duration that the active circuitry operates. Implicit in this is the assumption that the circuit does not operate

continuously. Thus, the circuit switches between active and sleep states. Assuming that the sleep state is sufficiently long, the duration of operation becomes a vital design parameter in low energy design. As a result, both the speed of operation as well as the latency of the algorithm implemented affect the 'on' time. This presents an opportunity in the form of an extra degree of freedom in the system design. A short duration typically entails a larger 'on' current draw than a longer duration, but lower current draw. Moreover, since speed does not increase linearly with increasing current, an optimum active duration results. However, other design constraints such as accuracy and power must also be balanced.

#### 2.3.4 Accuracy

Another consideration in low energy design is the accuracy required of the overall system and the individual components within it. Higher accuracy requirements directly lead to higher energy consumption because of the inherent speed-accuracy trade-off. In other words, higher accuracy requires larger power consumption due to the need for more complete settling and better matching. Because of this, careful allocation of system requirements to only the absolute minimum level required to implement the desired function becomes of paramount priority.

Quantifying the speed-accuracy-power trade-off is possible by relating the number of time constants needed to meet first-order exponential settling. For a single dominant pole  $\omega_o$  defined by its reciprocal time constant  $\tau$ , the resolution in number of bits N, and the clock period T,

$$\frac{1}{2^{N+1}} > e^{-T/\tau}.$$

(2.7)

Substituting  $1/\tau = \omega_o = g_m/C = \sqrt{2\mu C_{OX} \frac{W}{L} I_D}/C$  and  $T = \frac{1}{2F_{CLK}}$  in (2.7) and solving for the current,

$$I_D > \left(\frac{C}{2(N+1)F_{CLK}\ln(2)}\right)^2 \frac{L}{2\mu C_{OX}W}.$$

(2.8)

From (2.8), it is clear that the required current increases quadratically with changes in both the speed of operation and resolution in bits, in addition to the capacitive loading C.

#### 2.4 Circuit Implementation

The design of the sensor ADC for the remote sensing system discussed in Section 1.2 is now discussed. It includes a 9 bit ADC to achieve an 8 bit ENOB, the reference circuitry and all related bias and clocking. Considerations for low-power/energy design discussed in the previous section are applied to the prototype ADC and reference voltage system.

#### 2.4.1 System Architecture

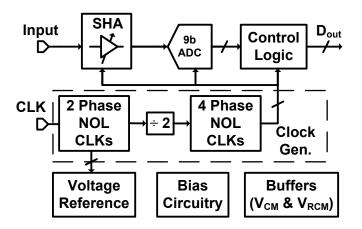

Fig. 2.2 shows the block level diagram of the prototype system. It contains a 9-bit ADC, a variable gain sample-and-hold amplifier (SHA), clock generation, a low-voltage reference, and common-mode drivers. The system operates at supply voltages from 1V down to 650mV. A single 200 kHz clock signal is used to generate full speed non-overlapping clock signals for the reference circuit, while half speed four phase non-overlapping clocks are required to implement correlated level shifting for gain and swing enhancement in the SHA and ADC core. All drivers for the reference and common-mode signals are included on-chip.

Figure 2.2: The ADC and reference voltage system block diagram.

The system is designed to minimize both the overall energy required for a single conversion as well as the peak power consumption while operating at low supply voltages. A successive approximation ADC architecture has traditionally been the first choice for minimum power consumption due to its single active component and mostly dynamic power consumption. However, its large capacitive load of  $2^N$  times the unit capacitance, C, presents a very large load for the reference buffer to drive for an N bit conversion. As a result, the burden of reducing the overall system power is merely moved to the reference and drivers in the system as opposed to the ADC core itself.

For this design, a cyclic ADC similar to a 1.5 bit per stage pipeline ADC is chosen. Such a structure reuses the first two stages of a pipeline ADC to save area and power at the expense of a reduced sample rate. This choice drastically reduces the capacitive load that the reference buffer must drive to 2C, a reduction on the order of  $2^{N-1}$  relative to an N bit SAR ADC. The overall power required for three amplifiers each driving a capacitive load on the order of the unit capacitance C is significantly less power than a single reference driver amplifier driving  $2^N C$ . A lower bound for the power savings may be approximated by the difference in the capacitance driven for each case. Furthermore, an amplifier is necessary to implement the sample-and-hold amplifier (SHA) for either ADC structure. With the cyclic ADC, one of the two amplifiers may be reused for this functionality without the need for additional hardware as is the case for a SAR ADC.

#### 2.4.2 1.5 b per stage Cyclic ADC

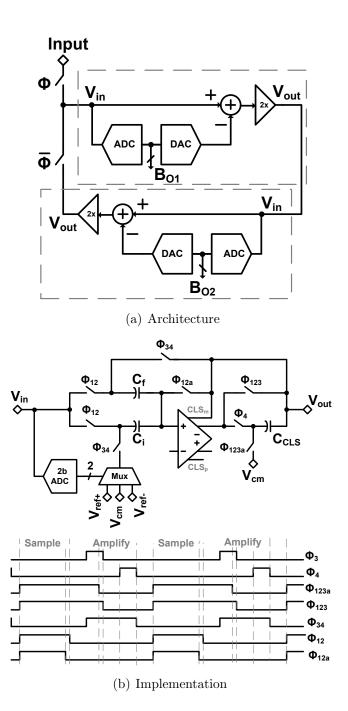

Fig. 2.3(a) shows a block diagram of the cyclic ADC architecture. It is a 1.5 bit per stage structure like that in [35]. When the clock is high, the input is sampled into the first stage. After the sample is taken, the clock goes low and the each stage resolves 1.5 bits per clock cycle and produces a residue voltage for the next stage to quantize. After a complete conversion, the clock goes high, a new sample is taken and the process is repeated. It does so in a cyclic manner, hence the name. A single 9 bit conversion including the sample-and-hold operation occurs in five clock cycles. Every half clock cycle a single bit is resolved. For a clock rate of 100 kHz, the sample rate is 20 kSPS.

A fundamental advantage of this ADC architecture is its tolerance to relatively large comparator errors due to redundancy and digital error correction. Consequently, the critical component limiting ADC performance is the amplifier in the multiplying digital-to-analog converter (MDAC) used to calculate the residue for the next phase of the conversion. The MDAC converting the first residue must settle to within half an LSB of the overall ADC accuracy. For a 9 bit system, it then follows that roughly 60 dB of open loop gain is necessary for the amplifier.

At low supply voltages simultaneously meeting both the swing and gain requirements while consuming only a few microamps of current is onerous. A switched capacitor technique that simultaneously improves both the limited gain and swing was presented in [36]. This allows a simpler, lower power and lower gain amplifier to be used. Correlated level shifting uses two level shifting capacitors at the output of the amplifier to first estimate the output. Next, the charged capacitors are reused as floating batteries to force the amplifier output to their common-mode level while simultaneously allowing the outputs to swing to nearly the supply rails. The result is both an increase in output swing and the effective gain. Power savings ensue because the simpler amplifier has fewer poles that have to be pushed to high frequency with quiescent current consumption. The cost is two settling phases that necessitate 4 phase clocking.

Fig. 2.3(b) shows the schematic of a single stage of the 1.5b per stage cyclic ADC along with the clock timing. For simplicity only one polarity of the differential structure is shown. Input sampling occurs during  $\phi_{12}$ . On the falling edge of  $\phi_{12a}$ , a three level comparison is made to determine whether the input  $V_{in}$  is within the following ranges: (00)  $-V_{ref} < V_{in} < -V_{ref}/4$ , (01)  $-V_{ref}/4 < V_{in} < V_{ref}/4$ , or (10)  $V_{ref}/4 < V_{in} < V_{ref}$ . Note that correlated double sampling [37] is used to sample the offset voltage of the amplifier during the sample phase ( $\phi_{12}$ ) and cancel it on the amplification phase ( $\phi_{34}$ ).

During the sample phase of  $\phi_{34}$ , the amplifier forces charge transfer resulting in a residue voltage of  $2 \times V_{in} + k \times V_{ref}$ , where k = 1 for code 00, k = 0 for code 01, and k = -1 for code 10. The estimation phase of correlated level shifting occurs during  $\phi_3$  and is exactly the same as the traditional switched capacitor settling phase. Here partial charge transfer from  $C_i$  to  $C_f$  occurs and the level shifting capacitor  $C_{CLS}$  is charged up to an estimate of the output. Next, during  $\phi_4$ , the charged level shifting capacitor acts as a floating battery to keep the amplifier output near the common-mode voltage while permitting the output nodes to swing to the supply rails, thus enhancing swing. Because charge transfer is more complete than for traditional switched capacitor operation [36], the effective amplifier gain is enhanced.

Figure 2.3: Schematics of (a) the 1.5b per stage cyclic ADC architecture and (b) the switched capacitor implementation of a single stage.

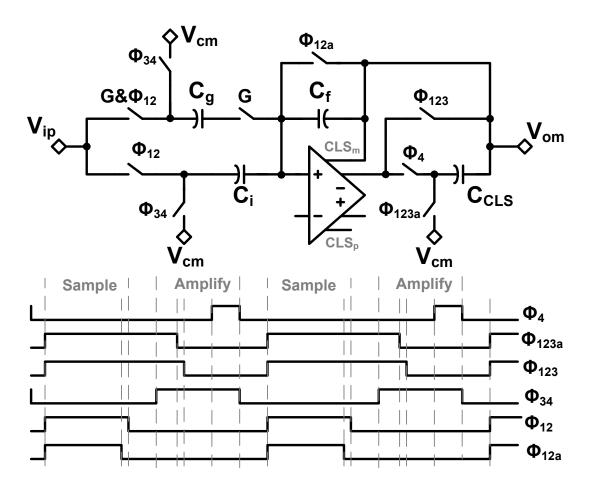

# 2.4.2.1 Comparator Design

The two bit sub-ADC used in each cyclic stage in Fig. 2.4.1 is composed of two comparators. From these two comparators, the two bit sub-ADC determines if the input with 1) less than  $-V_{ref}/4$ , 2) between  $-V_{ref}/4$  and  $V_{ref}/4$ , or 3) greater than  $-V_{ref}/4$ . The design of these comparators is now discussed.

A simplified schematic of one of the two comparators used in each two bit sub-ADC is shown in Fig. 2.4(a) [38]. Switched capacitor charge sharing synthesizes the required  $\pm V_{ref}/4$  values while simultaneously subtracting the input voltage such that the polarity of  $V_{in} - V_{ref}/4$  is determined.

A preamplifier, shown in Fig. 2.4(b), buffers the input switched capacitor circuitry from charge kickback from the dynamic latch that follows while also reducing the input referred offset do to the latch. Biased in weak inversion, the preamplifier consumes 375nA. Transistors M4a and M4b are sized with much larger lengths than widths to decrease their transconductance relative to the transconductances of M3a and M3b to realize a gain of approximately 5 dB.

The regenerative dynamic latch is the second stage of the comparator, Fig. 2.4(c). It has push-pull positive feedback from M3a, M3b, M6a, and M6b for enhanced gain and fast settling. While the clock  $\phi$  is high, the outputs are reset. On the falling edge of  $\phi$ , a decision is made. Devices M2a and M2b prevent input transistors M1a and M1b from conducting after a decision is made to save power. Not shown, a flip flop latches the settling output a quarter clock cycle after the falling edge of  $\phi$ .

Figure 2.4: Schematics of the comparator (a) switched capacitor top level that uses two phase non-overlapping clocking, (b) the preamplifier, and (c) the second stage dynamic latch.

# 2.4.2.2 SHA Circuit

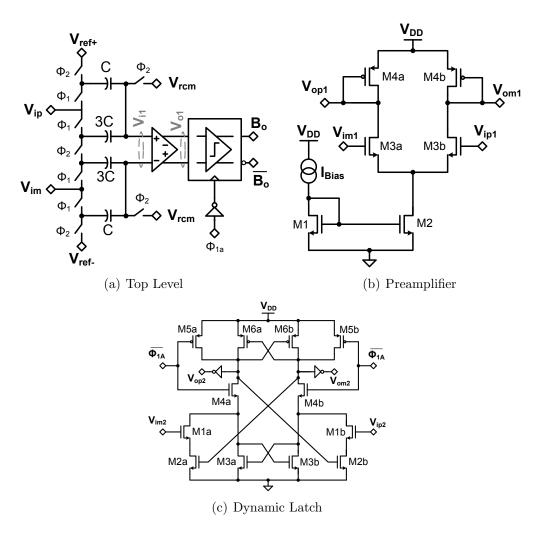

Figure 2.5 shows a simplified schematic of the switched capacitor circuit of the input cyclic ADC stage in SHA mode. It operates in SHA mode during the first of the five cycles of a conversion. During the other four states, it reconfigures to the circuit in Fig. 2.3(b). The default unity gain setting sets G = 0 (switch open), opening the  $C_g$  path. The gain in this mode is  $C_i/C_f = 1$  since  $C_i$  and  $C_f$  are identical. However, in high gain mode, G = 1 (switch closed) and the gain becomes  $(C_i + C_g)/C_f$ , resulting in a boost of 13 dB. As with the ADC operation in Fig. 2.3(b), correlated level shifting enhances both the gain and output swing of the amplifier for enhanced low voltage operation.

Figure 2.5: Simplified schematic of multi-purpose switched capacitor amplifier that functions as a preamplifier SHA, temperature sensor signal processor and cyclic ADC stage.

#### 2.4.2.3 OTA Design

Fig. 2.6(a) contains a schematic of the OTA used for both stages of the cyclic ADC. It is an enhanced fully differential version of an amplifier first reported in [39], shown in Fig. 2.6(b). The OTA is a fully differential Class-AB current mirror architecture. It eliminates redundant current mirror branches to save power, while providing a means to apply common-mode feedback directly to the output stage. Its extremely large slew rate and current efficiency reduces power by a factor of three to four compared to a traditional miller compensated two-stage amplifier.

A high slew rate is of critical importance for weak inversion operation since the bias currents are in the nano-Ampere range. Even modest capacitive loads of less than a pico-Farad, will result in low slew rates particularly when transistors are biased in weak inversion.

The Class-AB input circuit consists of transistors  $M_{1a}$ - $M_{1d}$  and  $M_{6a}$ - $M_{6b}$ . Transistors  $M_{1b}$  and  $M_{1c}$  correspond to those in a traditional differential pair. However, an opposite polarity signal is applied to each from the source terminals of  $M_{1a}$  and  $M_{1d}$ , driven by the source-follower action from the differential inputs. Therefore, the input signal applied to  $M_{1b}$  and  $M_{1c}$  is doubled, doubling the transconductance. An additional benefit is that the slew rate scales as the differential input voltage to the fourth order ( $V_{id}^4$ ) instead of second order ( $V_{id}^2$ ), reducing the required quiescent current to meet slew rate settling concerns. Together with the current mirror structure, the net result is the elimination of slew rate settling time with nearly the entire settling period now used for small signal exponential settling alone. Because of the small bias currents less than a micro-Ampere, this overcomes a fundamental limitation for weak inversion operation.

Examination of the optimized OTA in Fig. 2.6(a) compared to the conventional version in Fig. 2.6(b) reveals that two current branches consisting of transistors  $M_{7a}$ ,  $M_{7b}$ ,  $M_{8a}$  and  $M_{8b}$  are removed in the optimized version. This simplification is possible because the AC currents that  $M_{7a}$ ,  $M_{7b}$ ,  $M_{8a}$  and  $M_{8b}$  send to the pulldown output transistors  $M_{3a}$  and  $M_{3b}$  is already present in the bias transistors  $M_{6a}$  and  $M_{6b}$  of the Class-AB input stage. Simply mirroring the currents from  $M_{6a}$  and  $M_{6b}$  directly to output stage transistors  $M_{3a}$  and  $M_{3b}$  eliminates the superfluous current mirrors.

Additionally, since the currents of  $M_{6a}$  and  $M_{6b}$  contain a DC component that was not in the  $M_{7a}$ ,  $M_{7b}$ ,  $M_{8a}$  and  $M_{8b}$  branches, the DC portion must be subtracted from the output with  $M_{5a}$  and  $M_{5b}$ . This provides a simple means to apply common-mode feedback directly to the output stage. Typically, applying common-mode feedback directly to the output stage of a current mirror OTA requires additional current branches shunted to the output stage as seen in Fig. 2.6(b) with transistors  $M_{5a}$  and  $M_{5b}$  and the additional current sources. An enhancement of the output impedance and thus open loop gain results.

Each of the two OTAs in the ADC consume approximately 4.5  $\mu$ A including biasing. Compensated by Miller capacitors, the open loop gain is estimated to be 40 dB from simulations with a unity gain bandwidth of 3.5 MHz. When used with the correlated level shifting gain and swing enhancement, separate output terminals,  $CLS_p$  and  $CLS_m$  for the compensation capacitors provide a additional 6 dB gain boost [36].

Figure 2.6: Schematics of (a) the optimized version that saves power by eliminating two current branches and (b) A fully differential version of the class-AB current mirror OTA adapted from [39]. The components eliminated from the optimized version in this work are shaded for clarity.

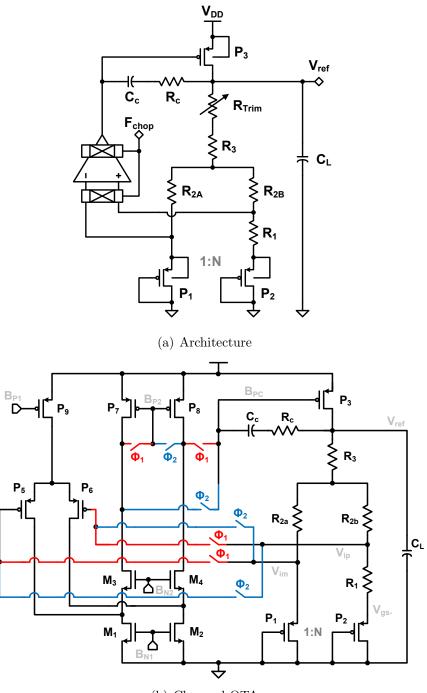

# 2.4.3 Low Voltage Reference

The minimum supply voltage of 650 mV required for this application precludes the use of a traditional band-gap [40, 41] or even its low voltage derivatives [42] since there is insufficient headroom for a diode drop, let alone a current source to bias it. Consequently, an alternative structure must be employed [9, 42–44].

A simplified schematic of the reference is shown in Fig. 2.7(a). It is a variation of a traditional bandgap reference that replaces the base emitter junction diode sensor with a MOSFET biased in weak inversion [9]. This enables low voltage operation due to the smaller diode drop of the subthreshold MOSFETs while also overcoming the problem posed by small current gain factors ( $\beta$ ) of parasitic bipolar transistors in CMOS technologies that result in inaccuracy without compensation due to collector current errors.

(b) Chopped OTA

Figure 2.7: (a) Simplified schematic of the low voltage reference circuit. Weak inversion PMOS devices  $P_1$  and  $P_2$  replace the BJTs in a traditional bandgap reference. (b) Simplified schematic of the chopper stabilized OTA.

The reference implements the function:

$$V_{REF} = V_{GS,P1} + n \frac{K_B T}{q} \ln\left(\frac{S1}{S2}\right) \frac{R_2 + 2R_3 + 2R_{Trim}}{R_1},$$

(2.9)

where  $V_{GS,P1}$  is the gate-source voltage of  $P_1$ , S1 and S2 are the sizes of the transistors P1 and P2 such that S1 = W1/L1 and S2 = W2/L2, and n is the weak inversion slope factor. The negative temperature coefficient of  $V_{GS,P1}$  is canceled by the scaled positive temperature coefficient of the difference in gate-source voltage of  $P_1$  and  $P_2$ ,  $\Delta V_{gs}$ . A reference voltage of 530 mV results. The proportional-to-absolute-temperature (PTAT) trimming technique from [41] provides a means to improve the accuracy further via resistor  $R_{Trim}$  and a single trim at room temperature. A 6-bit trimming code allows the reference voltage to be set within 250  $\mu$ V.

Since the amplifier loop forces its input terminals to the same potential, the current consumption in both P1 and P2 is then

$$I_{P1,2} = \frac{\Delta V_{gs}}{R_1},$$

(2.10)

$$\Delta V_{GS} = \frac{nK_BT}{q} \ln\left(\frac{S1}{S2}\right). \tag{2.11}$$

A value of 185 k $\Omega$  for R1 and S1/S2 = 4 set the current to approximately 600 nA in the output stage, a value sufficient to drive the low capacitive loading of the two ADC stages and reference common-mode circuit needed for the sub-ADC comparators. An additional 1.5  $\mu$ A is used in the amplifier and its bias circuitry

to set total reference current draw at  $2.1\mu$ A.

Ostensibly transistors with lower threshold voltage might seem advantageous for low voltage operation in the sensor diodes  $P_1$  and  $P_2$ . However, smaller threshold voltages for  $P_1$  and  $P_2$  limit the range of values for  $V_{gs-P1,P2}$  while remaining safely in weak inversion. At high temperatures with  $V_{gs-P1,P2}$  decreasing, drainsource voltages less than approximately 100 mV force the device to stop behaving with an exponential gate-source voltage to drain current relationship that is required for proper circuit operation. To overcome this limitation and extend the temperature range, high voltage I/O transistors with nominal threshold voltages of 0.7 V were used.

Fig. 2.7(b) shows a simplified schematic of the reference amplifier and chopping switches. The amplifier is a folded cascode with PMOS input transistors to accommodate the low input voltage level. A cascode is not used on the supply voltage side of the cascode stage so that low voltage operation is possible. All devices are biased in weak inversion. Chopping [37] reduces errors to to amplifier offset voltages and flicker noise. In order to reduce the output noise of the reference given its low quiescent current and nearly 1.5  $M\Omega$  total resistance, a 30 pF compensation capacitor ( $C_c$ ) and 0.1uF off-chip bypass capacitor ( $C_L$ ) are employed.

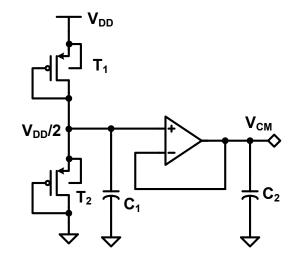

#### 2.4.4 Common-mode Buffers

Fig. 2.8 shows a schematic of the circuit used to derive the one half  $V_{DD}$  reference voltage and buffer to drive the switched capacitor common-mode circuits. It uses

Figure 2.8: Schematic of the common-mode generator and buffer.

diode-tied thick oxide PMOS devices to act as high impedance resistors to split the supply without consuming excess current, avoiding the use of resistors and saving area as well. The amplifier is a PMOS input differential pair with a current mirror active load. A similar circuit is employed to generate the  $V_{ref}/2$  signal used in the ADC's comparator signal processing. Less than  $1\mu$ A total current is consumed in both buffers combined.

# 2.5 Measurement Results

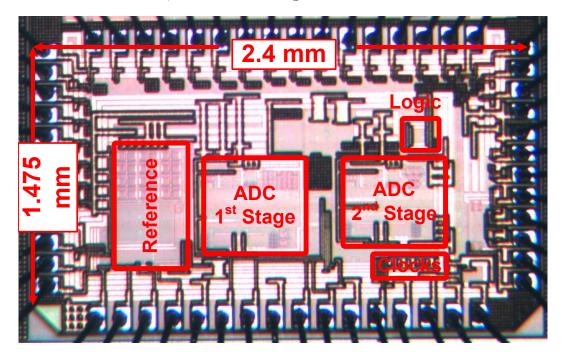

The prototype integrated circuit was fabricated in an IBM 1P8M CMOS process, Fig. 2.9. The total die area including pads encompasses 2.4 mm x 1.475 mm. The chip operates from supply voltages of 650 mV to 1.0 V. At a 750 mV supply voltage and 204.8 kHz clock rate, the total power consumption of the 9 bit ADC, reference voltage, buffers, logic and bias circuitry is 10.95  $\mu$ W. Of the total 14.6  $\mu$ A, 2.1  $\mu$ A is used in the reference voltage circuit, 4.5  $\mu$ A in each of the two amplifiers, with the rest used for buffers, clocks and biasing.

Figure 2.9: Die photo of the 130 nm CMOS 1.475 mm by 2.4 mm integrated circuit.

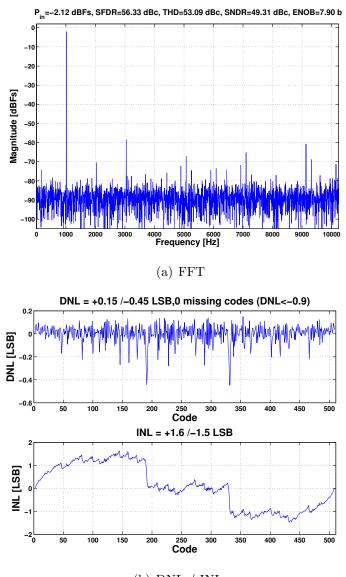

Fig. 2.10(a) shows a plot of the spectrum of the ADC and reference system at a sample rate of 20.48 kSPS and 750 mV supply voltage. The prototype 9 bit ADC and reference achieve an SNDR of 49.31 dB resulting in an ENOB of 7.9 bits. The SNDR is linearity limited, with a noise floor of -55.6 dBFs for zero input. With an external reference in lieu of the on-chip reference, there is negligible change in performance. With the SHA in high gain mode with a gain of 4.5 at 20.48 kSPS, the measured performance of 46.95 dB SNDR translates to an ENOB of 7.51 bits. In Fig. 2.10(b), the measured DNL and INL are seen to be +0.15/-0.45 LSB and +1.6/-1.5 LSB, respectively.

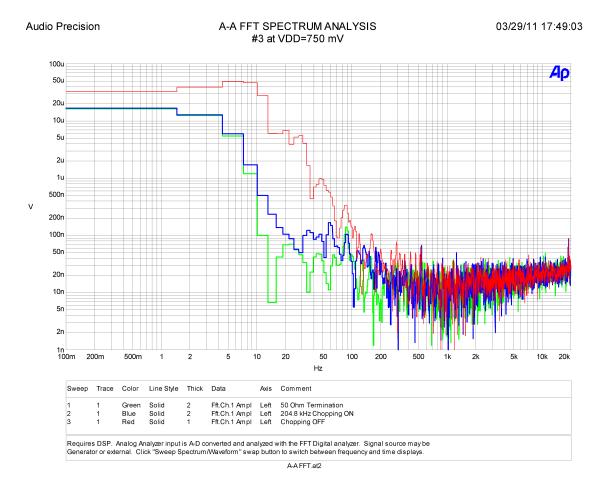

The measured noise performance of the on-chip reference voltage circuit is shown in Fig. 2.11. With chopping turned on, the flicker noise corner reduces from 500 Hz to within the noise of the Audio Precision used for measurements. Thermal noise is below the Audio Precision noise floor.

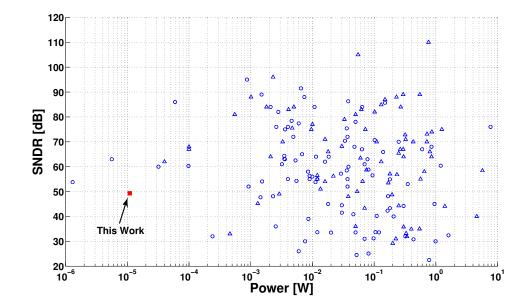

A performance summary and a comparison with state-of-the-art low power ADCs that include the reference circuit [1,9] is seen in Table 2.1. While [9] includes an on-chip reference that consumes  $11\mu$ W, [1] makes use of the supply voltage to save power. However, even a 5% variation in the supply voltage limits ADC performance to 4.3 bits. Comparatively, the reference in this work consumes only  $1.5\mu$ W, a seven fold improvement compared to [9] while working in a system that has three additional bits of resolution. The 35% overall power reduction and three additional bits of resolution compared to [9] underscore the effectiveness of the design techniques employed in this work. A highly digital flash ADC is presented in [45] demonstrates an alternative approach, but with 5.56b ENOB. In [46] a reconfigurable SAR ADC acheives very low power consumption and high energy efficiency, but requires an externally scaled supply voltage, an externally generated reference, and an external reference buffer.

Additional perspective into the effectiveness of the power reduction techniques in this work is seen by plotting SNDR versus power consumption. Fig. 2.12 plots this for this work and ADCs from ISSCC and SVLSI from 1997-2010 [33]. The power consumption of the ADC and reference combined for this work is less than the total power consumption for all but two ADCs [30, 31]. However both [30] and [31] use the supply voltage as the reference; this is not a practical solution

| Reference                | $V_{DD}$ | $V_{\rm ref}$   | Power              | Ref. Power         | $\mathbf{Fs}$ | Resolution | ENOB   | FoM                  | Technology |

|--------------------------|----------|-----------------|--------------------|--------------------|---------------|------------|--------|----------------------|------------|

|                          | [V]      | $[\mathbf{mV}]$ | $[\mu \mathbf{W}]$ | $[\mu \mathbf{W}]$ | [S/s]         | [bits]     | [bits] | $[\mathrm{pJ/step}]$ | [nm]       |

| Gambini (JSSC 11/2007)   | 0.5      | 260             | 17                 | 11                 | $1.5~{ m M}$  | 6          | 5.07   | 0.5                  | 90         |

| Scott (JSSC 7/2003)      | 1.4      | $V_{DD}$        | 4.2                | n/a                | 100 k         | 8          | 7      | 0.24                 | 250        |

| Daly (JSSC 11/2009)      | 0.4      | n/a             | 2.84               | n/a                | 400 k         | 6          | 5.56   | 0.15                 | 180        |

| Yip (ISSCC 2/2011)       | 0.55     | n/a             | 0.21               | n/a                | 20 k          | 10         | 8.84   | 0.022                | 65         |

| This Work (SHA Gain=1)   | 0.75     | 530             | 10.95              | 1.5                | 20.48 k       | 9          | 7.9    | 2.4                  | 130        |

| This Work (SHA Gain=4.5) | 0.75     | 530             | 10.95              | 1.5                | 20.48 k       | 9          | 7.5    | 3.2                  | 130        |

Table 2.1: Performance summary and comparison table of low power ADCs with and without on-chip reference voltage generation.

because even a low supply variation of 5% limits performance to 4.3 bits. Moreover, precision supply regulation consumes a significant amount of power for microwatt systems just as a reference circuit does. Even so, the difference in power consumption is less than  $10\mu$ W.

# 2.6 Conclusion

A 750 mV, 9 bit ADC including an on-chip 530 mV reference for remote sensing applications is presented. The system is optimized for energy minimization including subthreshold operation, a novel fully differential Class-AB current mirror OTA, and a low voltage reference. The measured performance 7.9 bit ENOB represents a 2.83 bit or equivalently a 17 dB improvement compared to prior low energy ADC and reference system performance.

(b) DNL / INL

Figure 2.10: Measured performance of the 9-bit ADC at 750 mV at 20.48 kSPS: (a) spectrum, and (b) DNL and INL.

Figure 2.11: Measured performance of the reference voltage at a 750 mV supply: (a) Noise. With chopping on, the reference noise is within the noise floor the the Audio Precision test system. (b) Reference voltage variation versus temperature.

Figure 2.12: Plot of SNDR versus power consumption for ADCs from ISSCC and SVLSI from 1997-2011 [33].

#### Chapter 3 – Frequency Dependent Sampling Linearity

### 3.1 Abstract