## AN ABSTRACT OF THE THESIS OF

<u>B. Robert Gregoire</u> for the degree of <u>Doctor of Philosophy</u> in <u>Electrical and Computer</u> <u>Engineering</u> presented on <u>December 10, 2008</u>.

Title:

Correlated Level Shifting as a Power-Saving Method to Reduce the Effects of

Finite DC Gain and Signal Swing in Opamps

Abstract approved:

### Un-Ku Moon

This thesis presents methods to reduce the effects of finite opamp DC gain, output voltage swing limitations in opamps, and component mismatches. The primary contribution of this thesis is a new switched-capacitor method named correlated level shifting (CLS). CLS enables true rail-to-rail operation by storing an estimate of the desired signal on a capacitor during an "estimate" phase, and subtracting the signal from the active circuitry (typically an opamp) during a "level shift" phase. This is done within the confines of a feedback loop. The effective loop-gain is the product of the loop-gains during the estimate and level shift phases. This enables, for example, a two-stage opamp to have the accuracy of a four-stage opamp. It also enables full utilization of the power supply since the gain block's output voltage can exceed the power supply. The thesis shows that the full utilization of the power supply and the increased DC effective loop gain leads to a significant power savings compared to existing techniques.

The methods are presented in the context of pipelined analog-to-digital converters, although the methods can be used with other circuits that use opamps or are sensitive to component mismatch. An overview of the detrimental effects of reduced signal swing and low DC gain is given with an emphasis on the cost in power to correct these deficiencies when limited to existing circuit techniques. CLS is then shown to correct these deficiencies without increasing power. A detailed explanation of CLS operation is given, as are measured results from a 12-bit pipelined analog-to-digital converter that was fabricated using a  $0.18\mu$  CMOS process. The results include greater than 10-bit performance with true rail-to-rail operation.

An overview of calibration is also given and the limitations are discussed. An argument is made that using CLS in addition to calibration will reduce power by increasing signal-to-noise ratio and reducing and linearizing the errors due to finite opamp gain. In addition, a method to reduce the effects of mismatch by measuring the relative size of elements is presented.

Finally, several avenues for future research into CLS are given.

©Copyright by B. Robert Gregoire December 10, 2008 All Rights Reserved Correlated Level Shifting as a Power-Saving Method to Reduce the Effects of Finite DC Gain and Signal Swing in Opamps

by B. Robert Gregoire

## A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented December 10, 2008 Commencement June 2009 Doctor of Philosophy thesis of B. Robert Gregoire presented on December 10, 2008

APPROVED:

Major Professor, representing Electrical and Computer Engineering

Director of the School of Electrical Engineering and Computer Science

Dean of the Graduate School

I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my thesis to any reader upon request.

### ACKNOWLEDGEMENTS

I would like to expresses sincere appreciation to Professor Un-Ku Moon, who was my major professor and advisor. My colleagues and I saw Dr. Moon freely share his time, wisdom, good spirits, laughs, encouragement, and even, to a lesser extent, his workload with us. And we benefited from all of his generosity. Most importantly he encouraged an atmosphere of collaboration in his group of the most impressive colleagues I have worked with. It was this collaborative atmosphere that drew me to his group and it proved better than I had imagined. These fellow researchers, many who first entered grade school the year I first entered industry, had so much knowledge to share. So many times they helped me reduce an idea to a circuit; it is no wonder they are recruited so heavily by the leaders of the industry.

Dr. Moon's group included Dave Gubbins from Ireland (who is "only" seven years my junior), Josh Carnes (U.S.), Ben Hershberg (U.S.), Volodymyr "Vova" Kratyuk (Ukraine), Peter Kurahashi (U.S.), Sunwoo Kwon (S. Korea), Ho-Young Lee (S. Korea), Naga Sasidhar Lingham (India), Nima Maghari (Iran), Tawfik Musah (Ghana), Omid Rajaee (Iran), Skyler Weaver (U.S.), and Ting Wu (China). I include their home countries to show the diversity of the group I was privileged to work with.

Drs. Kartikeya Mayaram, Gabor Temes, and Pavan Kumar Hanumolu are the most knowledgeable and generous teachers I have ever worked with and I am thankful that they were willing to serve on my committee. Brady Gibbons also took time out of his busy schedule to be on my committee as the graduate council representative.

My wife Ann is the love of my life and she led the family during the time I was pursuing this degree. And before and after for that matter. My children, Katie and Sam, ages seven and five at the time of this writing, sent me off every day with a supply of hugs and kisses carefully placed into my coat pockets – available at any time during the day if I needed them. Signaled by the sound of the garage door opening when I arrived home, Sam and Katie would run to me yelling "Daddy's home!" and

then "don't forget to turn off your blinky light!" referring to the rear blinking light on my bicycle.

Inspired by my constant drawing and redrawing of circuits, Sam and Katie took up the art of schematic capture, albeit with some unconventional circuit elements.

Sam with his elaborate RL circuit used to power the "idea" light bulb in the upper left corner. Note the error-reducing star connections.

Katie with her simple LC circuit using voltage sources with dual positive terminals, implicit grounds, and hair.

Finally, this work would have not been possible without Asahi Kasei EMD Corporation, who provided fabrication of several prototype ICs, and without the funding provided by Semiconductor Research Corporation under contract 2005-HJ-1308.

## TABLE OF CONTENTS

| P | a | g | e |

|---|---|---|---|

|   |   |   |   |

| 1   | The n    | eed for methods to reduce noise and low opamp-gain effects          | 1   |  |  |  |

|-----|----------|---------------------------------------------------------------------|-----|--|--|--|

|     | 1.1      | Document overview                                                   |     |  |  |  |

|     | 1.2      | The nature of noise                                                 | 2   |  |  |  |

|     | 1.3      | Modeling and reducing thermal noise from transistors                | 3   |  |  |  |

|     | 1.4      | Reducing kT/C noise                                                 | 4   |  |  |  |

|     | 1.5      | Signal to noise (SNR) and effective number of bits (ENOB)           | 5   |  |  |  |

|     | 1.6      | Effects of limited opamp output swing                               | 6   |  |  |  |

|     | 1.7      | The effect of low DC gain on pipelined ADC performance              | 9   |  |  |  |

|     | 1.8      | Accuracy/power tradeoffs                                            | 10  |  |  |  |

|     | 1.9      | The effects of capacitor mismatch on ADC performance                | 13  |  |  |  |

|     | 1.10     | Using correlated level shifting to reduce power                     | 13  |  |  |  |

| 2   | An O     | ver-60dB True Rail-to-Rail Performance Using Correlated Level Shift | ing |  |  |  |

| anc | l an Opa | mp with Only 30dB Loop Gain [1]                                     | 15  |  |  |  |

|     | 2.1      | Introduction                                                        | 15  |  |  |  |

|     | 2.2      | CLS overview                                                        | 17  |  |  |  |

|     | 2.2.     | 1 CLS applications                                                  | 17  |  |  |  |

|     | 2.2.2    | 2 CLS operation                                                     | 17  |  |  |  |

|     | 2.2.     | 3 Transient behavior and speed                                      | 18  |  |  |  |

|     | 2.2.4    | 4 CLS error reduction analysis                                      | 20  |  |  |  |

|     | 2.3      | Multi-stage opamp considerations                                    | 22  |  |  |  |

|   |        |                                                          | Page |

|---|--------|----------------------------------------------------------|------|

|   | 2.3.   | 1 Special considerations                                 | 22   |

|   | 2.3.2  | 2 Bandwidth considerations                               | 22   |

|   | 2.3.   | 3 Enhanced equivalent gain with Miller compensation      | 23   |

|   | 2.4    | CLS compared to CDS                                      | 24   |

|   | 2.4.   | 1 Equivalent gain of CDS                                 | 24   |

|   | 2.4.2  | 2 Noise and offset                                       | 25   |

|   | 2.4.   | 3 Complexity                                             | 26   |

|   | 2.4.4  | 4 Output offset storage (CDS at output)                  | 26   |

|   | 2.5    | Pipelined A/D converter implementation                   | 27   |

|   | 2.5.   | 1 Prior methods to reduce low opamp gain effects in ADCs | 27   |

|   | 2.5.2  | 2 CLS pipelined A/D topology                             | 28   |

|   | 2.6    | Experimental results                                     | 29   |

|   | 2.6.   | 1 True rail-to-rail performance                          | 29   |

|   | 2.6.2  | 2 INL                                                    | 31   |

|   | 2.6.   | 3 CLS vs. Non-CLS                                        | 32   |

|   | 2.7    | Sensitivity to level-shifting capacitance values         | 32   |

|   | 2.7.   | 1 Background                                             | 32   |

|   | 2.7.2  | 2 Dynamic range (noise) vs. C <sub>CLS</sub>             | 33   |

|   | 2.7.   | 3 Distortion vs. C <sub>CLS</sub>                        | 33   |

|   | 2.8    | Performance summary                                      | 34   |

|   | 2.9    | Conclusions                                              | 35   |

| 3 | Digita | al Self-Calibration of Pipeline-Type A/D Converters      | 37   |

|   | 3.1    | Introduction                                             | 37   |

|          |     |                  |                                                                | Page |

|----------|-----|------------------|----------------------------------------------------------------|------|

|          | 3.2 | Dig              | ital self-calibration categories                               | 38   |

|          |     | 3.2.1            | Foreground, true-background, and background                    | 38   |

|          | 3.3 | Dig              | ital self-calibration methods                                  | 39   |

|          |     | 3.3.1            | Pipelined A/D topology and calibration                         | 39   |

|          |     | 3.3.2            | A/D converter transfer curve                                   | 40   |

|          |     | 3.3.3            | Difference-based methods                                       | 41   |

|          |     | 3.3.4            | Radix-based methods                                            | 43   |

|          | 3.4 | Imp              | lementation of true-background calibration schemes             | 45   |

|          |     | 3.4.1            | Methods using only the input signal                            | 45   |

|          |     | 3.4.2            | Calibration using signal injection and correlation             | 45   |

|          |     | 3.4.3            | Error signals created from element rotation                    | 47   |

|          |     | 3.4.4            | Residue transfer function modulation                           | 47   |

|          |     | 3.4.5            | Split ADC topology                                             | 48   |

|          | 3.5 | Mul              | lti-bit calibration                                            | 49   |

|          | 3.6 | Lim              | itations of digital calibration                                | 50   |

|          | 3.7 | Cali             | ibration summary                                               | 53   |

| 4<br>[67 |     | Reducing 1<br>54 | the Effects of Component Mismatch Using Relative Size Informat | ion  |

|          | 4.1 | Intro            | oduction                                                       | 54   |

|          | 4.2 | Stra             | tegic element placement                                        | 55   |

|          |     | 4.2.1            | Average mismatch cancellation                                  | 55   |

|          |     | 4.2.2            | Selecting the median device                                    | 56   |

|          |     | 4.2.3            | Other applications                                             | 57   |

|   |       |        |                                                                   | Page |

|---|-------|--------|-------------------------------------------------------------------|------|

|   | 4.3   | Or     | der statistics                                                    | 58   |

|   | 4.3   | .1     | Properties of ordered elements                                    | 58   |

|   | 4.4   | So     | rting and grouping                                                | 60   |

|   | 4.4   | .1     | Better matched pairs using sub-elements                           | 60   |

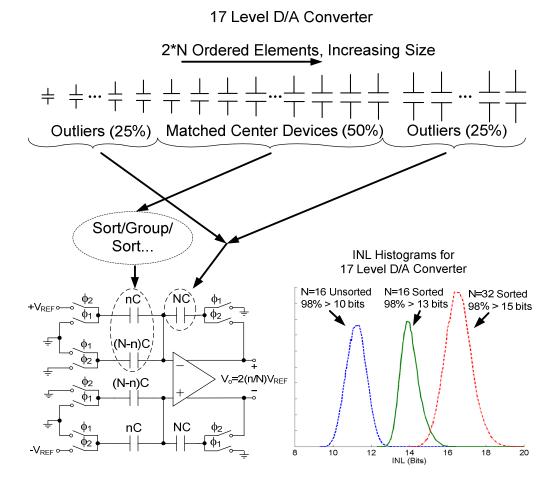

|   | 4.4   | .2     | Improved D/A converters                                           | 62   |

|   | 4.5   | Al     | highly linear 17 level D/A converter                              | 63   |

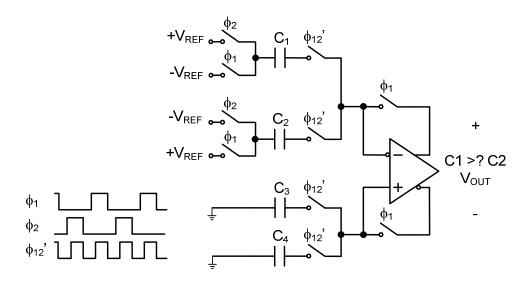

|   | 4.6   | Ca     | pacitor sorting circuit                                           | 64   |

|   | 4.7   | Lir    | mitations of using relative size information                      | 65   |

|   | 4.8   | Su     | mmary (using relative size information)                           | 66   |

| 5 | Othe  | r Ap   | plications of CLS                                                 | 67   |

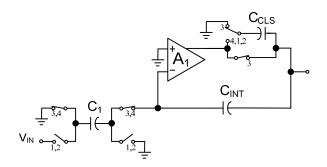

|   | 5.1   | Sw     | vitched-capacitor integrator using CLS                            | 67   |

|   | 5.2   | Lo     | ad Free CLS                                                       | 68   |

|   | 5.3   | Ne     | ested Load Free                                                   | 69   |

|   | 5.4   | Vii    | rtual Miller enhanced CLS (VMEC)                                  | 70   |

|   | 5.5   | De     | ecreasing settling time instead of increasing loop gain           | 72   |

| 6 | Conc  | clusic | on                                                                | 78   |

| 7 | Bibli | ogra   | iphy                                                              | 80   |

| 8 | Арре  | endix  | x I: CLS with Miller compensation (derivation)                    | 87   |

|   | 8.1   | De     | efinitions for Miller-compensated CLS derivation                  | 87   |

|   | 8.2   | Tra    | aditional: voltage sampled at opamp output                        | 89   |

|   | 8.3   | Dis    | scussion of Miller compensated CLS derivation                     | 91   |

|   | 8.4   | Lo     | ad Free [20]: voltage sampled by compensation capacitor ( $C_C$ ) | 91   |

|   |      |                                                                   | Page |

|---|------|-------------------------------------------------------------------|------|

| 9 | Appe | ndix II: CLS with cascode compensation (derivation)               | 93   |

|   | 9.1  | Definitions for cascode-compensated CLS derivation                | 93   |

|   | 9.2  | Traditional: voltage sampled at opamp output                      | 95   |

|   | 9.3  | Discussion of cascode compensated CLS derivation                  | 97   |

|   | 9.4  | Load Free [20]: voltage sampled by compensation capacitor $(C_c)$ | 97   |

## LIST OF FIGURES

| <u>Figure</u> <u>Page</u>                                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. A model of a MOSFET with thermal noise source included                                                                                                                                                                                              |

| <ul> <li>2. A model of an opamp including thermal noise source. Note that the current is the current in each element of the differential pair. The total opamp current is ~4x this current.</li> <li>3</li> </ul>                                      |

| 3. Simplified circuit with noisy signal at output                                                                                                                                                                                                      |

| 4. Distortion (clipping) caused by increasing the input signal beyond the linear range of the opamp                                                                                                                                                    |

| 5. Amount that the power needs to be scaled to maintain constant SNR with a 300mV loss in swing. The graph shows that if one could use the full supply when operating at 1V the required power would be cut in half compared to opamps available today |

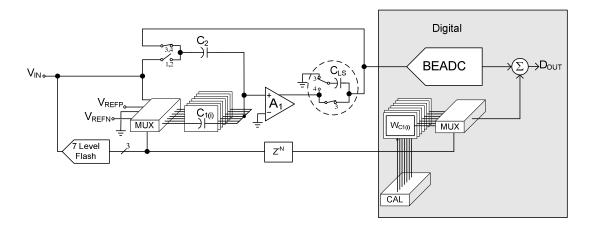

| <ul> <li>6. A simple pipelined ADC with one pipeline stage with a gain of 2 to increase the resolution of the BEACD by 1 bit. The analog operations of adding –VREF, 0, or +VREF and amplifying by two are mimicked in the digital domain</li></ul>    |

| 7. The classic block diagram of a feedback system showing the loss in accuracy due to finite A                                                                                                                                                         |

| 8. A simplified schematic of a multi-stage opamp. Each stage increases the open loop gain by a factor of $g_m r_o$ where $r_o$ represents the equivalent impedance at the point where the gain is taken                                                |

| 9. A simplified schematic of a telescopic cascode amplifier                                                                                                                                                                                            |

| <u>Figure</u> <u>Page</u>                                                                       |

|-------------------------------------------------------------------------------------------------|

| 10. Conceptual schematic of an amplifier using CLS. The passive CLS network                     |

| allows operation beyond the rail. It also achieves the gain of an N-stage amplifier             |

| with N/2 stages. These features save significant power                                          |

| 11. a) Simplified two stage amplifier with correlated level shifting (CLS) network, b)          |

| closed loop performance of the opamp with and without CLS                                       |

| 12. The three phases of correlated level shifting (CLS), and the waveform at the load.          |

| The opamps gains $A_{(EST)}$ and $A_{(LS)}$ are different because the opamp output is different |

| in the respective phases. Single ended is shown for simplicity                                  |

| 13. Transient response of a 30dB amplifier using CLS compared to a conventional                 |

| 60dB opamp 19                                                                                   |

| 14. CLS placement in a fully differential multi-stage amplifier with inter-stage                |

| compensation. The network should be inside the compensation loop to keep settling               |

| times the same during estimation and level-shifting phases                                      |

| 15. The three phases of correlated double sampling (CDS). Note difference in                    |

| operation compared to CLS shown in Fig. 12                                                      |

| 16. Simulated open loop gain versus output voltage using CLS or CDS with a 36dB                 |

| opamp. The gain is lowest near the 0 and 0.9V supplies. The gain with no                        |

| enhanacement (A <sub>(EST)</sub> ) is also shown for comparison                                 |

| 17. Output offset storage                                                                       |

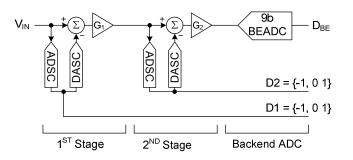

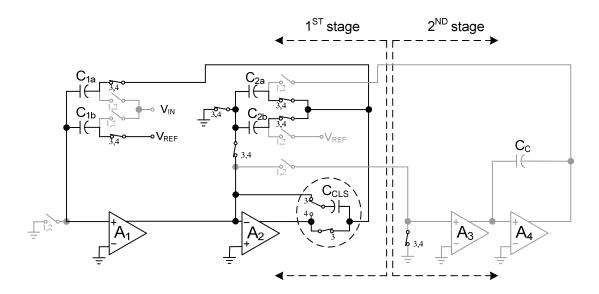

| 18. Topology of pipelined A/D converter (single ended shown for simplicity) 28                  |

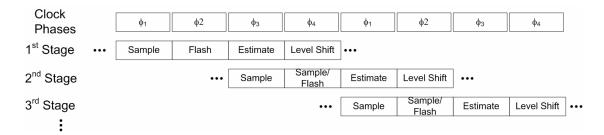

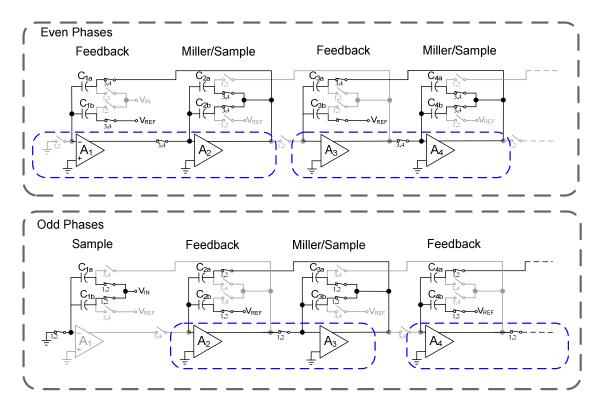

| 19. Timing of first three stages in the CLS pipelined A/D converter. For stages                 |

| beyond the first one, the flash sub-ADC converts the estimated signal of the previous           |

| stage, and thus can use the entire level-shift period to convert the signal                     |

| <u>Figure</u>                                                                       | Page |

|-------------------------------------------------------------------------------------|------|

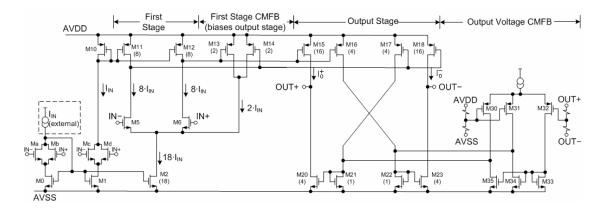

| 20. Fully differential opamp with CLS used in the pipelined A/D converter.          |      |

| Placement of the Miller compensation and CLS network are shown in Fig. 14           | . 29 |

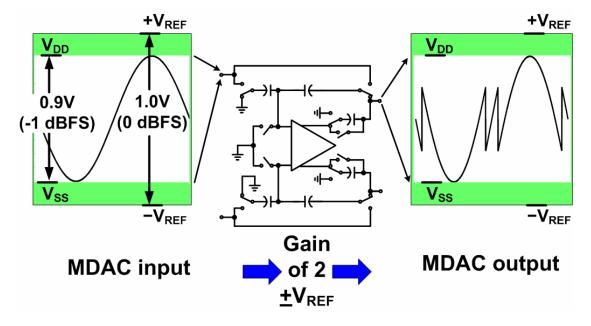

| 21. Reference scheme to prove performance beyond the rail. The reference is great   | ıter |

| than the supply so that at 0dBFS the output of the MDAC swings at least 50mV        |      |

| beyond the rails.                                                                   | . 30 |

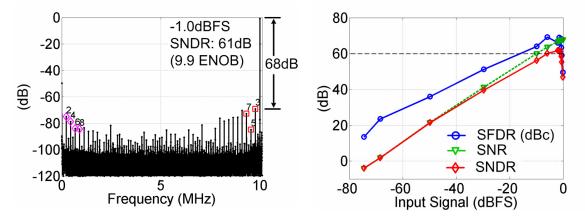

| 22. Spectrum for Nyquist signal showing more than 60dB performance with the         |      |

| MDAC operating true rail-to-rail.                                                   | . 30 |

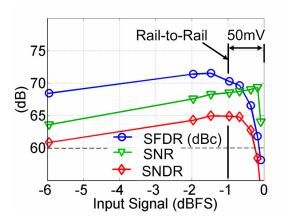

| 23. SFDR, SNR, and SNDR vs. input signal magnitude for a Nyquist input sampled      | d at |

| 20.2MHz. Dynamic range is 72dB                                                      |      |

|                                                                                     |      |

| 24. Performance vs. input signal sampling a 1MHz signal at 20.2MHz. Performance     | ce   |

| increases until the MDAC output starts swinging beyond the rails                    | . 31 |

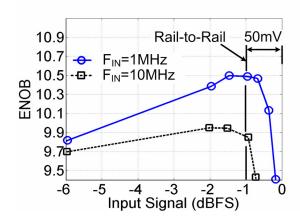

| 25. Effective number of bits (ENOB) vs input signal for 10MHz and 1MHz sample       | ed   |

| at 20MHz.                                                                           | . 31 |

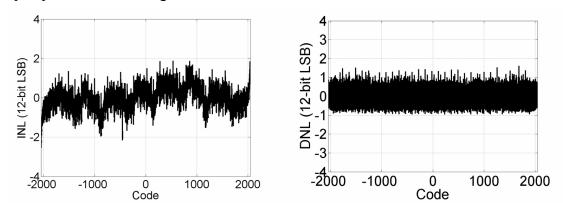

| 26. Measured INL and DNL.                                                           | 31   |

| 20. Weasured five and Dive.                                                         | . 51 |

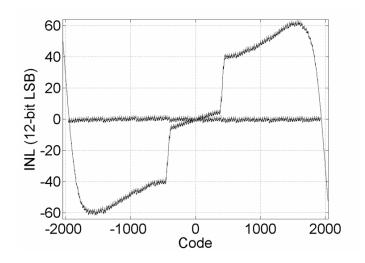

| 27. Measured INL with CLS and without CLS.                                          | . 32 |

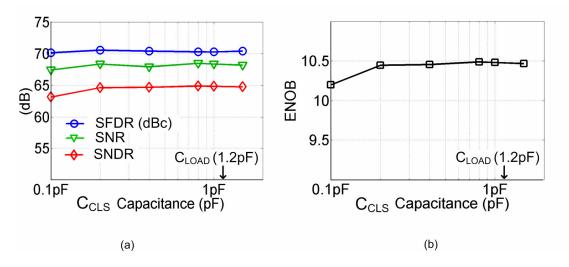

| 28. Dynamic range vs. level-shifting capacitance showing that $kT/C_{CLS}$ noise is |      |

| negligable.                                                                         | . 33 |

|                                                                                     |      |

| 29. Performance vs. level-shifting capacitance. The input is 1MHz, rail-to-rail (-  |      |

| 1dBFS). Good performance is maintained for $C_{CLS}$ as small at $C_L/6$            | . 34 |

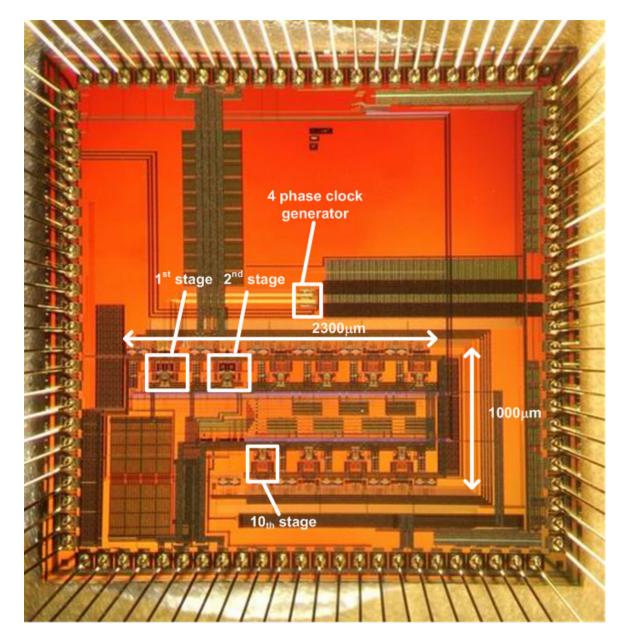

| 30. Die photo                                                                       | . 35 |

| 21 An 11b convertor with two 1.5 bit ninclined starss and an ideal backer of ADC    | 20   |

| 31. An 11b converter with two 1.5-bit pipelined stages and an ideal backend ADC.    | . 39 |

| 32. Detail of typical 1.5-bit per stage pipelined ADC converter Fig. 31.            | . 39 |

| <u>Figure</u> Page                                                                           |

|----------------------------------------------------------------------------------------------|

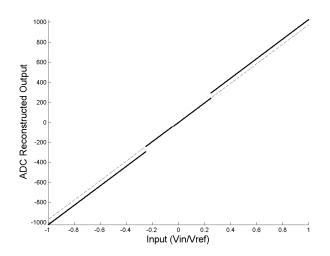

| 34. Reconstructed input/output curve. Solid: uncalibrated. Dashed: calibrated by             |

| adding the proper values for D1 and D2. Note gain error of dashed line – it falls short      |

| of spanning +/-1024 counts                                                                   |

|                                                                                              |

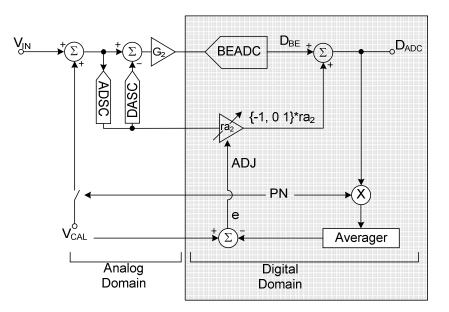

| 37. Signal recovery via correlation. A calibration signal is modulated with a                |

| pseudorandom sequence (PN) and added to the input sequence. The error of the                 |

| recovered calibration signal is then used to adjust the interstage gains of the ADC46        |

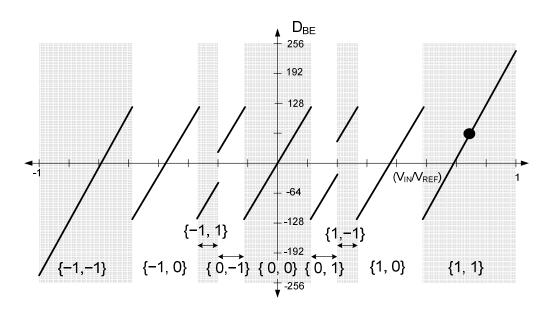

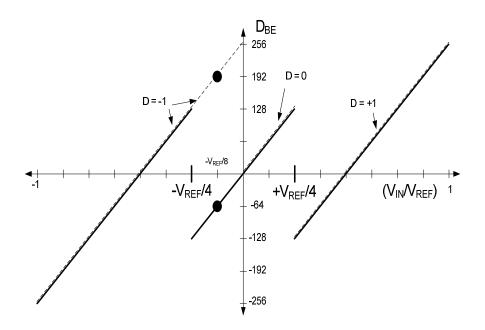

| 38. Residue transfer curve obtained by changing one comparator trip point from –             |

| Vref/4 (Solid) to 0 (Dashed). If the solid curve is used, a signal at $-V_{REF}/8$ will get  |

| converted to $\{D_{BE}=-64, D=0\}$ . If the dashed curve is used, the result will be         |

| $\{D_{BE}=192, D=-1\}$                                                                       |

|                                                                                              |

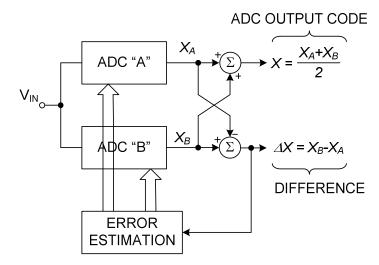

| 39. Split ADC. The output signal is the average of the two signals. The error is the         |

| difference                                                                                   |

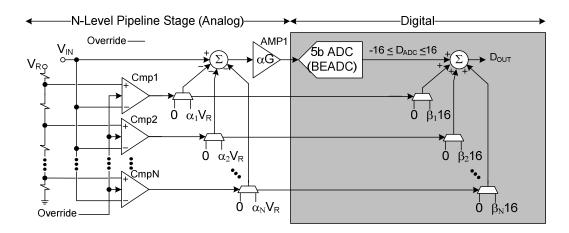

| 40. An N-level pipeline stage followed by a 5-bit BEADC. The errors in the analog            |

| path are modeled by the $\alpha_i$ terms                                                     |

|                                                                                              |

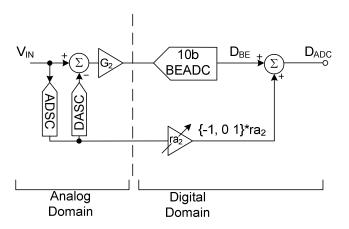

| 41. Simplified multi-bit pipelined A/D converter using CLS and calibration to reduce         |

| errors. Calibration adjusts the weights $W_{C1(i)}$ to match the actual amount the           |

| capacitors $C_{1(i)}$ remove (or add) to the signal to keep it within range of the BEADC. 52 |

| 42 Fully differential pair of two circuit and the reduced encoder the second site            |

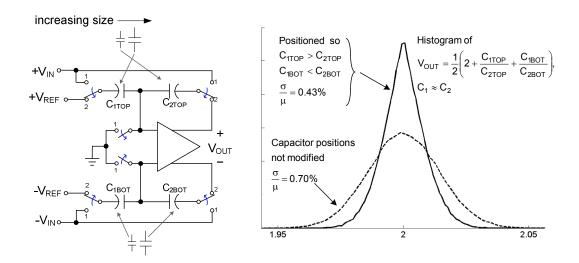

| 42. Fully differential gain of two circuit and the reduced spread when the capacitors        |

| are arranged based on relative size. The factor of 1.6 improvement in matching means         |

| that capacitors can be 2.56x smaller                                                         |

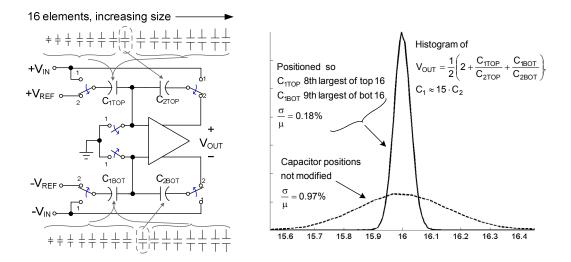

| 43. Gain of sixteen circuit and the reduced spread when the feedback device is chosen        |

| to be the median element of the ordered devices. Capacitors can be made nearly 30x           |

| smaller when this is done                                                                    |

|                                                                                              |

| <u>Figure</u> <u>Pag</u>                                                                        | e        |

|-------------------------------------------------------------------------------------------------|----------|

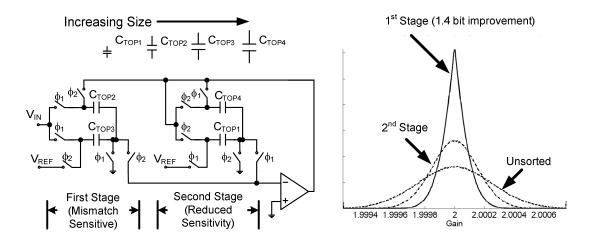

| 44. Op-amp sharing topology that allows for reduced spread by choosing the first                |          |

| stage capacitor pair from a group of four devices. No sub-elements are used in this             |          |

| example                                                                                         | 7        |

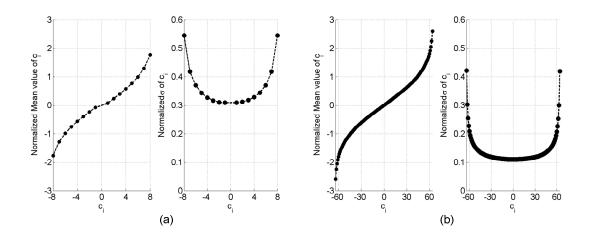

| 45. The expected mean and standard deviation of an (a) 16 element sorted array, (b)             |          |

| 128 element array                                                                               | )        |

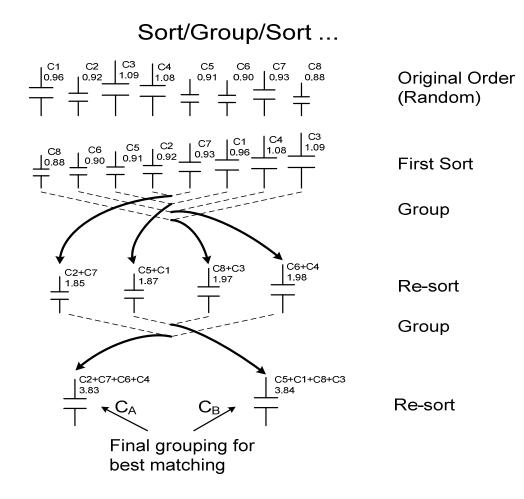

| 46. Sort and group operations to create two well matched capacitors from 8 sub-                 |          |

| elements                                                                                        |          |

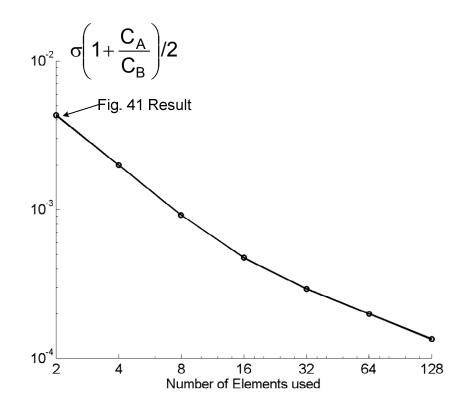

| 47. Reduction in $\sigma$ obtained for the circuit in Fig. 42 when the capacitor is broken into |          |

| sub-elements and sorted. Spread is roughly inversely proportional to the number of              |          |

| sub-elements used, even though total capacitor area stays the same                              | <u>,</u> |

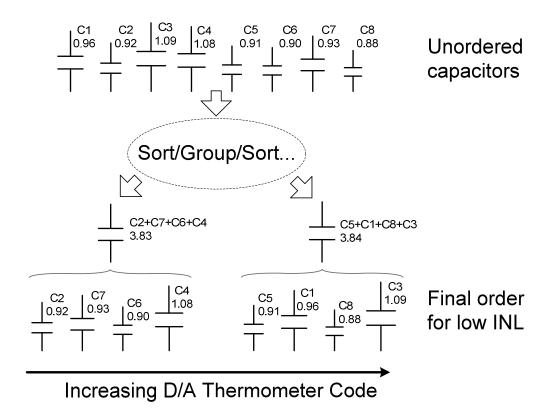

| 48. Using the sorting and grouping algorithm to order elements for a highly linear              |          |

| nine-level D/A converter                                                                        | ;        |

| 49. Highly linear 17 level D/A converter and INL histograms. Unordered capacitors               |          |

| limit INL to 10bits (98% yield). Simple ordering (Fig. 47) the same capacitors                  |          |

| increases linearity by 3 bits. Further improvement is obtained by creating a 33 level           |          |

| (N=32) D/A converter, and only using the even levels. Total capacitance is the same             |          |

| for all three D/A converters                                                                    | ł        |

| 50. Capacitor ranking circuit created using existing operational amplifier                      | ;        |

| 51. Switched capacitor integrator. The output is estimated during phase 3, and level            |          |

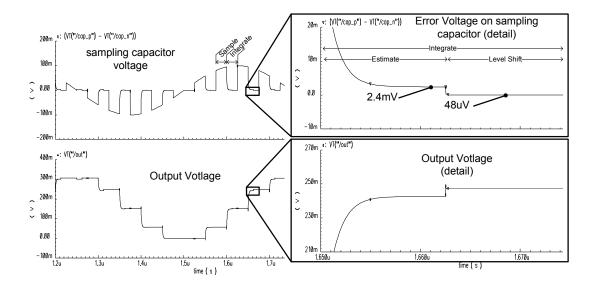

| shifted for phases 4, 1, and 2. The output is valid during the level shifting phase 67          | 7        |

| 52. Simulated output voltage of the integrator shown in Fig. 51. Open loop gain is              |          |

| 40dB. The top left signal is the voltage on the sampling capacitor $C_1$ . Top right is the     |          |

| detail showing the error voltage reduction during the level shift phase. The bottom             |          |

| curves are the output signal                                                                    | 3        |

| 53. Load-free implementation of CLS in a pipelined A/D converter MDAC stage 69                  | )        |

| <u>Figure</u> <u>Page</u>                                                                |

|------------------------------------------------------------------------------------------|

| 54. Nested load free implementation of CLS in a pipelined A/D converter to take          |

| advantage of the power savings from opamp sharing                                        |

| 55. Virtual Miller enhanced CLS (VMEC). When properly tuned, the Miller enhanced         |

| CLS circuit (top) produces voltages that replicate perfect virtual grounds at the inputs |

| of the opamp stages. The end result can be replicated using Virtual Miller enhanced      |

| CLS (bottom). A slow loop is used to tune the first stage gain                           |

| 56. Which circuit settles faster? Ideal opamp circuits to determine if CLS could be      |

| used to decrease settling times                                                          |

| 57. Ideal circuitry to realize the opamps in Fig. 56. Left, ideal opamp model. Right,    |

| opamp configured as a flip-around gain-of-two circuit. Compensation was varied to        |

| test the effect of phase margin                                                          |

| 58. Simulated results showing transient response of gain-of-two circuit using CLS to     |

| decrease settling time. Settling time to 54dB accuracy was 2.5nS without CLS, and        |

| 1.4nS with CLS                                                                           |

| 59. Simulated results showing transient response of gain-of-two circuit using CLS to     |

| decrease settling time. Settling time to 54dB accuracy was 2.5nS without CLS, and        |

| 1.4nS with CLS. Decreased settling times require the level shifting phase to be          |

| invoked during specific windows                                                          |

| 60. (Top) Output waveform without CLS. The signal settles in 2.5nS. (Bottom)             |

| Settling time as a function of when CLS is invoked. If CLS is invoked during the         |

| shaded time periods it will improve settling time                                        |

| 61. Results described in Fig. 60, except using an opamp with increased phase margin      |

| (less ringing)                                                                           |

| <u>Figure</u> <u>Page</u>                                                              |

|----------------------------------------------------------------------------------------|

| 62. CLS circuit for derivation of equivalent gain for a Miller compensated opamp. It   |

| can also represent load compensated OTAs by making $C_C=0$ . $C_P$ , the brainchild of |

| Tawfiq Musah, is optional, but can be used to enhancing equivalent gain                |

| 63. CLS circuit for derivation of equivalent gain for a cascode compensated opamp      |

| [9]. It can also represent load compensated OTAs by making $C_C=0$ . $C_P$ , the       |

| brainchild of Tawfiq Musah, is optional, but can be used to enhancing equivalent gain. |

|                                                                                        |

## LIST OF TABLES

| Table                                                                 | Page |

|-----------------------------------------------------------------------|------|

| 1. 12-bit ADC measured performance summary.                           | 34   |

| 2. Analog operation performed in each region                          | 41   |

| 3. Capacitor voltages at the end of each phase (Miller compensation)  | 88   |

| 4. Capacitor voltages at the end of each phase (cascode compensation) | 94   |

## **Correlated Level Shifting as a Power-Saving Method to Reduce the Effects of Finite DC Gain and Signal Swing in Opamps**

## 1 The need for methods to reduce noise and low opamp-gain effects

### **1.1 Document overview**

Noise and distortion are two very important factors that limit the performance of analog circuits. This thesis will focus on reducing the effects of noise and distortion in pipelined analog to digital converters (ADCs), although the principles presented in this thesis can be used in other circuits that require high performance operational amplifiers (opamps) and good matching of elements.

The remaining portion of section 1 will explain how noise, distortion from limited swing, distortion from finite opamp DC gain, and distortion caused by mismatches affect the accuracy of ADCs. With existing technologies the power must be increased significantly to eliminate this noise and distortion.

Section 2 presents a new method named correlated level shifting (CLS) that reduces the effects of noise and distortion described in section 1; noise effects are reduced by increasing the allowable signal swing; distortion effects are reduced by decreasing the effects of finite opamp DC gain, and also by extending the allowable signal swing.

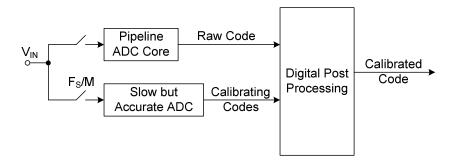

Section 3 discusses calibration methods that can be used reduce distortion. Calibration is a method that depends on accurately measuring the errors of the system. Once these errors are known, they can be easily corrected in the digital domain.

Section 4 introduces a method that estimates component mismatch by ranking them from smallest to largest. Component mismatch causes the same errors in ADCs as finite opamp DC gain, thus methods are needed to correct their effects. The field of order statistics shows that if we order a set of randomly sized components from smallest to largest we increase our ability to accurately estimate their size. We can then use this additional information to arrange the elements to minimize the errors (in a statistical sense) caused by their imperfect matching. Section 5 suggests several promising circuits that incorporate (or mimic) CLS.

Section 6 is a summary of the key concepts and applications presented in this thesis.

Finally, the appendices contain derivations of the gain improvement obtained using CLS for two circuit topologies: Miller compensated two-stage opamps and cascode compensated two-stage opamps. The performance of CLS when used with a single stage opamp can be derived from either of the topologies derived, so it is not presented.

### **1.2** The nature of noise

Noise is an additional random voltage added onto a signal. In a hand-waving sense, it is no surprise that one cannot determine a signal's value with a single sample to a precision greater than the value of the noise that is added to it. The type of noise that will be discussed in this thesis is thermal noise.

If one was to collect many samples of thermal noise over a period of time and put the values into a histogram, one would see that its distribution is Gaussian. The noise adds to the signal (at least to a good approximation since nonlinear circuits distort). The frequency spectrum of thermal noise is so large that it is modeled as if it contains all frequencies. Thus thermal noise is often described as additive Gaussian white noise.

When referring to measured voltages, mathematicians quantify the amplitude of Gaussian noise by its standard deviation ( $\sigma$ ). Electrical engineers usually quantify noise amplitude by its root-mean-square (RMS) value. The two values are exactly the same, but the engineering definition implies a bound to its value that does not exist. Noise follows the rules of Gaussian distributed variables. For example, noise amplitude will be greater than the RMS value approximately 32% of the time, and greater than twice the RMS value approximately 5% of the time.

Other types of noise such as flicker noise and cross talk also limit the performance and in many applications are very important. They can be treated in a similar fashion to white noise.

#### **1.3 Modeling and reducing thermal noise from transistors**

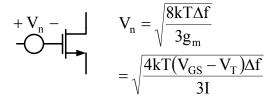

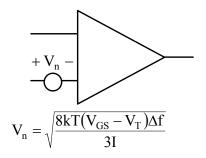

Thermal noise is modeled in a transistor by including a voltage (or current) source whose value is equal to the RMS value of the noise. This is shown in Fig. 1.

Fig. 1. A model of a MOSFET with thermal noise source included.

Note that we have written transconductance  $(g_m)$  in terms of the MOSFET's current and overdrive voltage  $(V_{GS}-V_T)$ . Also note that the only way  $g_m$  can be changed is to change its current or to adjust its dimensions to change its overdrive voltage. The equation for  $g_m$  is derived from the simplified "square-law" equation  $I=\beta(V_{GS}-V_T)^2$ but the conclusions that will be drawn in this section are not changed by using more elaborate models.

The noise in an opamp can be modeled by using the noise of its input differential pair because in most well designed opamp it is the dominant source. An opamp modeled in this fashion is shown in Fig. 2.

Fig. 2. A model of an opamp including thermal noise source. Note that the current is the current in each element of the differential pair. The total opamp current is  $\sim$ 4x this current.

The equation for noise in Fig. 2 clearly shows that there are only two choices to decrease the noise: increase current or decrease the overdrive voltage ( $V_{GS} - V_T$ ).

Realistically, the only choice is to increase current because  $(V_{GS} - V_T)$  is usually minimized to maximize  $g_m$  for a given amount of current. The noise source in Fig. 2 assumes the main contributor is the differential pair. If other components are contributors the main point remains: current must be increased to decrease noise.

Fig. 2 shows that reducing noise is very costly: noise is inversely proportional to the square-root of the current (1). For example, current must be quadrupled to decrease the noise by a factor of two. In reality current has to be increased more than that: to keep the ( $V_{GS} - V_T$ ) value constant the width of the device must also be increased by a factor of four, which increases the input capacitance by a factor of four. More current, over and above the existing 4x increase, will be required to keep the performance the same if the input capacitance increases.

RMS noise voltage

$$\propto \sqrt{\frac{1}{I_{BIAS}}}$$

(under the best of circumstances). (1)

The conclusion to be drawn from this brief analysis is that current has to be *at least* quadrupled to reduce the noise by a factor of two.

### 1.4 Reducing kT/C noise

Most A/D converters sample a signal onto a capacitor. It is well known that the RMS noise sampled onto a capacitor is equal to

RMS noise voltage (capacitor) =

$$\sqrt{\frac{kT}{C}}$$

, (2)

where T is absolute (Kelvin) temperature and k is Boltzman's constant.

To reduce the noise by a factor of two the capacitance has to be increased by a factor of four. In turn, the opamp current needs to be increased proportionally to maintain the bandwidth. Bandwidth is proportional to  $g_m/C$  so kT/C noise and thermal noise have the same current relationship: kT/C noise is inversely proportional to the square-root of the current because larger currents must be used to drive the reduced noise (i.e. larger) capacitors. Again, the conclusion is that reducing kT/C and thermal noise is very costly: the current must be increased quadratically.

### **1.5** Signal to noise (SNR) and effective number of bits (ENOB)

The signal to noise ratio (SNR) is a very important measurement. As its name suggests, it is the ratio of the root-mean-square (RMS) value of the signal to the RMS value of the noise. The signal is what we are trying to determine, and the noise is what limits how accurately we can determine the signal. The probability of obtaining a measurement within a window of accuracy can be determined using SNR. For example, if we have a 1V RMS signal and 1mV RMS Gaussian noise, we can quickly determine that a measurement will be within 1mV (i.e. within one standard deviation) of the true answer 68.3% of the time; within 2mV of the true signal 95.4% of the time; within 3mV 99.7% of the time, etc. This is a simple application of probability with noise being a random variable with a Gaussian distribution.

SNR is also used to produce a parameter named effective number of bits (ENOB):

ENOB =

$$\frac{\text{SNR} - 1.76}{6.02}$$

. (3)

The units for SNR and ENOB in this equation are dB and bits respectively. For most ADC applications the "noise" in the SNR value includes harmonics from distortion, with the resulting modified SNR being referred to as SNDR (Signal to Noise + Distortion Ratio) or SINAD (SIgnal to Noise And Distortion). To keep things simple we neglect distortion for this example.

An ENOB of 10 bits implies an SNR of ~62dB (1259 to 1). It is based on the SNR obtained if we assume the noise is quantization noise. For this equation the quantization noise is assumed to be uniformly distributed across the quantization window. In other words the "noise" is bounded. But real noise is Gaussian distributed so it does not have such bounds. For example, an SNR of 62dB does not mean that the signal can be measured to 10 bit accuracy (1 part in 1024) with certainty. It means a measurement of the signal can be measured to 1 part in 1259 (~10 bits) 68.3% of the time, 2 parts in 1259 (~9 bits) 95.4% of the time, etc. Nonetheless, ENOB is a common and useful way of characterizing A/D converters.

## 1.6 Effects of limited opamp output swing

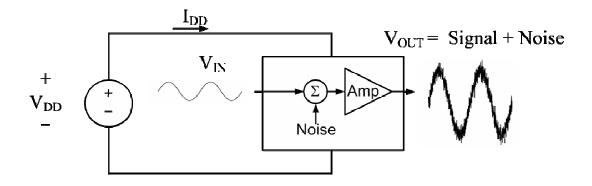

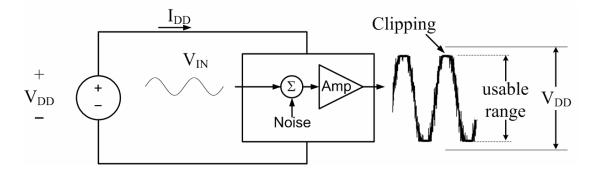

The cost of the inability to use the whole supply is the subject of this section. Fig. 3 shows a circuit that models noise in an amplifier by adding the noise to a signal before amplification. The output is visibly "noisy" (noise amplitude is exaggerated to illustrate the point). As mentioned earlier, reducing noise requires a significant increase in power. A power-efficient alternative is to increase the signal. However, as shown in Fig. 4, the opamp starts distorting (clipping) the signal well before it reaches the supply rail.

It was shown in sections 1.3 and 1.4 that reducing noise requires quadratically increasing the bias current: reducing the noise by a factor of two requires quadrupling the current – under the best of circumstances. Section 1.5 showed how the ratio of signal to noise determines how accurately a signal can be measured. The conclusion is that there are only two ways to increase how precise we can measure a signal: increase the signal amplitude or decrease the noise added to it. This section will discuss how opamp imperfections limit how much we can increase the signal amplitude.

Fig. 3. Simplified circuit with noisy signal at output.

Fig. 4. Distortion (clipping) caused by increasing the input signal beyond the linear range of the opamp.

The output voltage of most modern opamps is advertised as being able to swing "rail-to-rail." Truthfully, the output voltage of these opamps cannot literally swing rail-to-rail without significant distortion; a practical "rail-to-rail" opamp output voltage needs to be at least 150mV from both of the supplies to remain relatively distortion free – i.e. the maximum swing is reduced by a total of 300mV. Realistically, the signal needs to be reduced by more than 300mV to maintain performance, but 300mV will be used to demonstrate that the penalty is large even with this optimistic assumption.

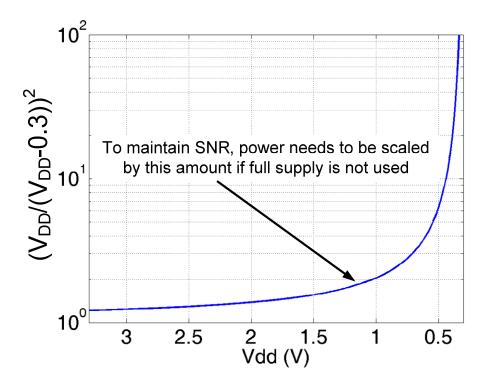

To take advantage of modern and future smaller geometry's inherently faster speeds, one needs to reduce the supply to accommodate the limitations of the process. The 300mV loss of swing becomes especially detrimental with smaller supplies. For example, to maintain SNR with this loss of swing the noise must be decreased by a factor of  $(V_{DD} - 0.3)/V_{DD}$  because we do not have the option of increasing the signal amplitude. To decrease noise by this amount, the current must be scaled by a factor of  $V_{DD}^2/(V_{DD} - 0.3)^2$ . So, to maintain SNR with a 1V supply the current needs to be doubled! Even with modern "large" 3.3V and 1.8V power supply voltages, the required power increases are 20% and 44% respectively. If future reductions in geometry size cause supplies to approach 300mV, the swing that can be realized while maintaining opamp performance approaches zero; therefore, no amount of power scaling will achieve the SNR that could be obtained if the full supply was used. A graph showing how much the power needs to be scaled to overcome a 300mV loss in swing is shown in Fig. 5.

Fig. 5. Amount that the power needs to be scaled to maintain constant SNR with a 300mV loss in swing. The graph shows that if one could use the full supply when operating at 1V the required power would be cut in half compared to opamps available today.

Use of the full supply range (or even beyond the supply if the process can tolerate it) is one of the features of correlated level shifting (CLS), which is the main contribution of the research presented in this thesis.

In summary, the amount that the power needs to be scaled to accommodate a 300mV loss in swing is significant: a factor of 2 with a 1V supply, 44% with a 1.8V supply. Furthermore, a 300mV loss is swing is optimistic – most opamps will have reduced performance at levels less than 300mV. CLS allows the full use of the supply and thus saves significant power.

### **1.7** The effect of low DC gain on pipelined ADC performance

The previous sections discussed how noise limits performance. The next two sections will discuss how finite opamp gain limits performance in pipelined ADCs.

A pipelined ADC is a topology that allows a low resolution A/D converter to achieve much higher resolution. In order to do this the input signal needs to be gained up. For example, 1mV resolution can be achieved by using a 128mV resolution ADC if the signal in amplified by a factor of 128. There are obvious limitations to this: if the power supply is 1.28v, an ADC with 128mV resolution cannot have more than 10 levels. To achieve more than 10 levels it would need to process inputs greater than the supply.

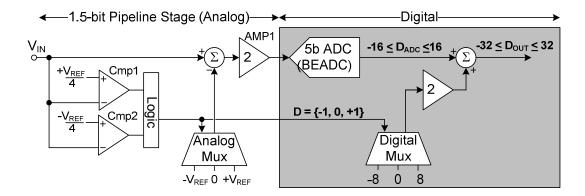

Pipelined ADCs take a different approach: they remove known amounts from the signal so when the signal is amplified it remains within the range of the course-resolution ADC. As long as these analog operations are perfectly replicated in the digital domain the signal will be properly converted to a digital value (Fig. 6). Multiplying (amplifying) by two in the digital domain is trivial: shift the digital word one bit left. The challenge lies in accurately amplifying in the analog domain. The amplification of the signal must be at least as accurate as the resolution to be achieved.

Fig. 6. A simple pipelined ADC with one pipeline stage with a gain of 2 to increase the resolution of the BEACD by 1 bit. The analog operations of adding –VREF, 0, or +VREF and amplifying by two are mimicked in the digital domain.

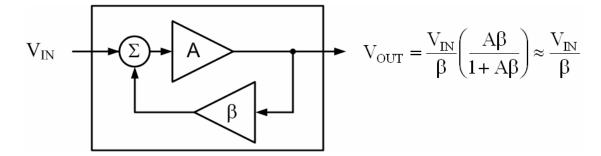

For accuracy, feedback topologies are used to amplify the signal. The well known feedback system block diagram is shown in Fig. 7. The signal  $V_{IN}$  is amplified by approximately  $1/\beta$  and the error is dependent on the loop gain A $\beta$ . For example, to achieve 10-bit accuracy (1 part in 1024), A $\beta$  must be greater than 1024.  $\beta$  is the inverse of the desired gain (1/2, 1/4, etc) so it is fixed; thus the burden is to increase A, which is the open-loop gain.

Fig. 7. The classic block diagram of a feedback system showing the loss in accuracy due to finite A.

### **1.8** Accuracy/power tradeoffs

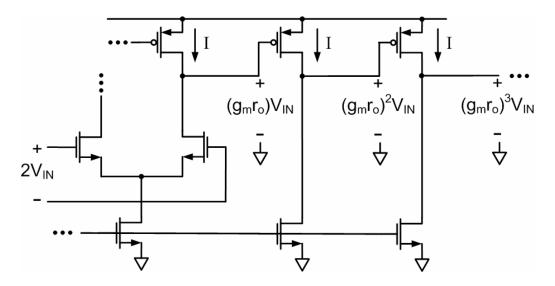

As mentioned previously, high accuracy requires a large open-loop gain. This gain is realized with a multi-stage opamp such as the one shown in Fig. 8. Each stage increases the gain by a factor of  $g_m r_o$ , where  $r_o$  represents the equivalent impedance at the point where the gain is taken. For this example we have assumed  $g_m r_o$  is the same for each stage. While not strictly true,  $g_m r_o$  will not vary significantly in an amplifier where gain and bandwidth are maximized.

As a reference point, an amplifier using a  $0.18\mu$  CMOS process with the transistors biased with 1mA current can achieve a value of  $g_m r_o$  of about 8. Four amplifier stages will be required to achieve an open-loop gain adequate enough for accuracy in the 10 – 11 bit range.

As mentioned earlier, this structure needs about 300mV of "headroom" to operate, thus one has to increase the power by a factor of  $(V_{DD})^2/(V_{DD} - 0.3)^2$  to maintain the

Fig. 8. A simplified schematic of a multi-stage opamp. Each stage increases the open loop gain by a factor of  $g_m r_o$  where  $r_o$  represents the equivalent impedance at the point where the gain is taken.

same SNR of an amplifier that can operate in a true rail-to-rail fashion. For a 0.9V supply the current needs to be increased by a factor of 2.25 to compensate for the lack of swing.

Longer channel length can be used to increase output impedance, but the cost in bandwidth is substantial: bandwidth is inversely proportional to the square of the channel length.

Cascaded amplifiers of more than two stages are difficult to compensate and are bandwidth inefficient, so cascode transistors are often used to achieve gain beyond what is possible with two stages. The phase loss through a cascode device is less than through an additional stage, so cascoded amplifiers achieve higher gain with less current.

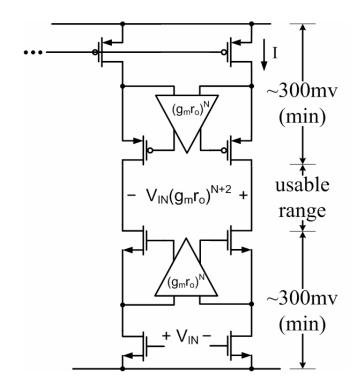

The effectiveness of the cascode transistors can be increased by using "active" cascode devices (aka regulated cascode devices) [5], which use active circuitry to amplify the effective output resistance. This can be done in many ways, but a very efficient "telescopic" implementation is shown in Fig. 9 [6]. The "active" cascode is

Fig. 9. A simplified schematic of a telescopic cascode amplifier.

produced by the parallel opamps. The parallel opamps increase the effective output impedance of the cascode devices by an amount proportional to the parallel opamp loop-gain. The phase loss due to these cascoded stages is less than a cascaded stage. In addition, the parallel opamps usually consume less power than a cascaded stage.

At first glance this telescopic amplifier structure looks to be a very power-efficient way to increase DC gain, but, as the figure illustrates, it needs 600mV of headroom. To maintain the same SNR as a true rail-to-rail opamp the power would have to be scaled by a factor of  $(V_{DD})^2/(V_{DD} - 0.6)^2$ . For a 0.9V supply one needs to increase the current by a factor of 9! The lost swing will be even greater if a tail current source is used to bias the differential pair for increased common mode rejection.

The swing can be increased by adding a second stage to the opamp, but as geometries shrink the threshold voltage decreases to accommodate lower supply voltages. This in turn forces the second stage transistors to have more overdrive ( $V_{GS} - V_T$ ) to give the cascode devices enough headroom to remain saturated. The increased overdrive limits the headroom as the output voltage cannot get closer to the

rail than the larger of  $(V_{GS} - V_T)$  or a few thermal voltages (kT/q). The increased overdrive also decreases the  $g_m$  unless the current is increased proportionally. In conclusion, the use of cascode (active or passive) increases the DC gain of an amplifier, but it also reduces the amount of swing so they may not be a power-efficient solution if noise is a limiting factor in a design.

### **1.9** The effects of capacitor mismatch on ADC performance

Power must also increase to eliminate the effect of component mismatches. Component mismatches, especially the feedback capacitors, decrease the accuracy of the gain. The negative effects of the decreased accuracy are the same as those caused by low loop-gain (section 1.7). Just as is the case for DC gain and noise errors, power must be increased quadratically if one needs to reduce the effects of capacitor mismatch. This is because mismatch can only be reduced by increasing the size of the capacitors [68], and to reduce mismatch by a factor of two the size of the capacitors needs to be increased by a factor of four, and the current must be scaled proportionately to drive the increased capacitance. Once again we see that increased precision requires a quadratic increase in current.

Section 3 describes how mismatch can be reduced using digital calibration. Section 4 describes a method to reduce mismatch effects by ordering the capacitors based on their relative size.

## 1.10 Using correlated level shifting to reduce power

The previous sections have highlighted two major issues that increase power: 1) the output signal of an opamp cannot utilize the entire power supply because opamps require at least 300mV of headroom. 2) High DC gain requires increased power because multiple stages are required. Cascode topologies require fewer stages, but suffer from increased headroom requirements; thus they still require increased power.

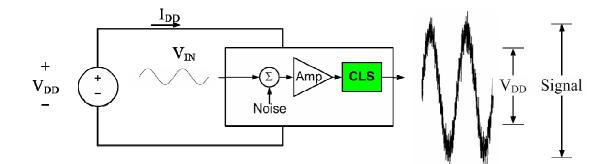

The main contribution of this thesis is a new technique named correlated level shifting (CLS). CLS significantly reduces the swing and DC gain problems associated with traditional opamps. It is a double-sampled switched-capacitor technique that

enables the output voltage of an opamp to operate true rail-to-rail. Operation beyond the rail can also be achieved.

CLS uses double sampling to achieve the DC gain of an opamp with twice the number of stages. This thesis focuses on double sampling, but triple sampling also works and achieves the gain of an opamp with 3 times the number of stages.

The reduced number of stages and the increased swing give opamps using CLS a significant power-saving advantage. The CLS network mimics an output stage (Fig. 10). However, the CLS components are passive, thus the only additional power required is to drive the switches. The double-sampling operation does not increase the settling times in most instances and can decrease it under some circumstances.

Section 2 gives a detailed description of the operation and advantages of CLS including measured results from a 20MS/s 12-bit pipelined A/D converter fabricated in a 0.18µm CMOS process.

Fig. 10. Conceptual schematic of an amplifier using CLS. The passive CLS network allows operation beyond the rail. It also achieves the gain of an N-stage amplifier with N/2 stages. These features save significant power.

# 2 An Over-60dB True Rail-to-Rail Performance Using Correlated Level Shifting and an Opamp with Only 30dB Loop Gain [1]

## 2.1 Introduction

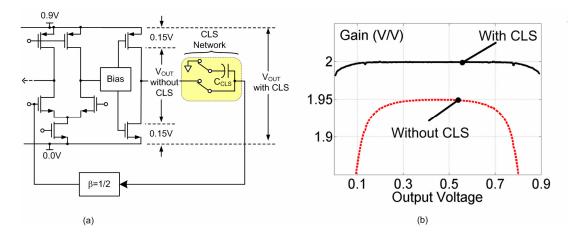

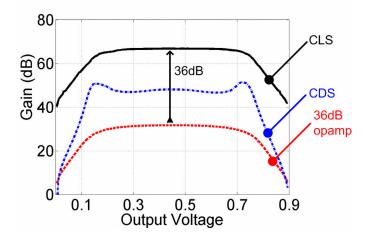

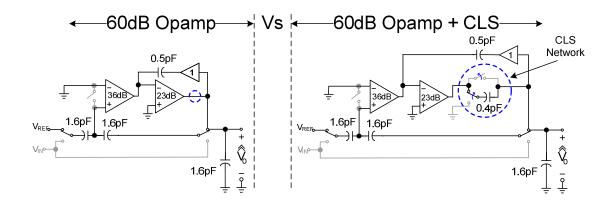

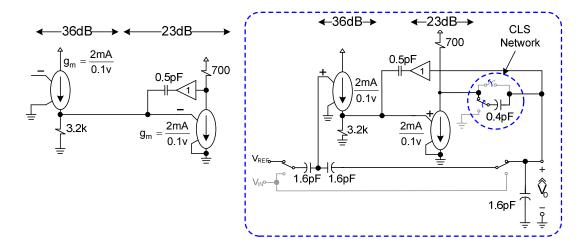

Finite opamp gain and output swing are two limitations for precision analog circuits. These limitations are especially serious at lower supply voltages where limited headroom prevents the use of cascode devices to improve gain. The magnitude of the problem is illustrated in Fig. 11 for a two-stage opamp in a 0.18µm process. Ideally, the circuit has a closed-loop gain of two, but it falls short because of the finite DC gain of the opamp. The gain of this particular opamp is about 36dB. When configured for a closed-loop gain of 2, the overall loop gain is about 30dB. This loop gain decreases dramatically when the output is near the rails as the driven second stage device enters the linear region. Fig. 11(b) shows that with a loop gain of 30dB the closed loop gain is only 1.95 V/V and this poor gain is maintained only over a small output range. At best, one could expect about 5-bit performance with a useful swing of 0.6V when configured traditionally. However, with CLS the performance is better than 10 bits over most of the supply range.

Fig. 11. a) Simplified two stage amplifier with correlated level shifting (CLS) network, b) closed loop performance of the opamp with and without CLS.

Technology scaling will not improve the situation. First, intrinsic gain  $(g_m r_o)$  will get smaller as channel lengths decrease. Second, to be in saturation, the minimum drain-to-source voltage is the larger of  $V_{GS}$ - $V_T$  or a few kT/q. These do not change with process.

Correlated double sampling (CDS) [2]-[3] can be used to decrease errors from finite opamp gain, but it adds significant noise and does not reduce errors near the rails. Similarly, replica amplifiers [4], multi-stage or regulated cascode amplifiers [5][6] can increase equivalent gain, but do not reduce errors near the rail. They also reduce phase margin and increase complexity.

This work introduces correlated level shifting (CLS), which is a new switchedcapacitor technique that simultaneously decreases the error due to finite opamp gain and allows operation to and beyond the rails (true rail-to-rail operation). An extra clock phase is needed, but, surprisingly, settling time is about the same. In addition the increased signal swing means that the same signal-to-noise ratio (SNR) can be achieved using smaller sampling capacitors. Thus, it could be argued that CLS can provide accurate results at a higher speed than the traditional approach of using high DC gain opamps. This is especially true at low power supplies.

This paper is organized as follows: Section 2.2 gives an overview of the steps and performance of the CLS technique. Section 2.3 covers some considerations required when using multi-stage opamps. Section 2.4 compares CLS to CDS. Sections 2.5 through 2.8 show how CLS can be incorporated into a pipelined A/D converter and achieve rail-to-rail performance in excess of 60dB with a 30dB opamp. Conclusions are given in section 2.9. Finally, the improvement that CLS gives is derived in the Appendix (sections 8 and 9). The Appendix also contains a discussion of the speed/accuracy tradeoffs associated with choosing the size of the level-shifting capacitance.

# 2.2 CLS overview

## 2.2.1 CLS applications

CLS is a general technique that reduces opamp errors due to finite gain and increases the distortion-free swing. Possible applications include  $\Delta$ - $\Sigma$  integrators, switched capacitor filters, and any circuit where the capacitive load is relatively constant. It cannot be used in circuits that need to drive DC loads unless the output is buffered. This paper shows that it is very well suited to improve the performance of a pipelined A/D converter.

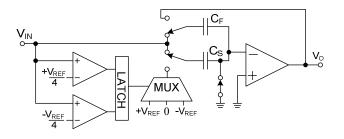

### 2.2.2 CLS operation

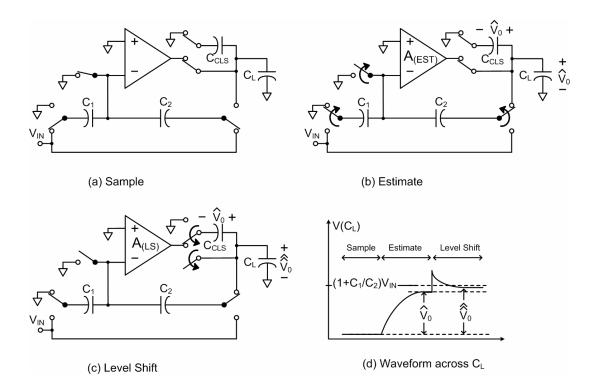

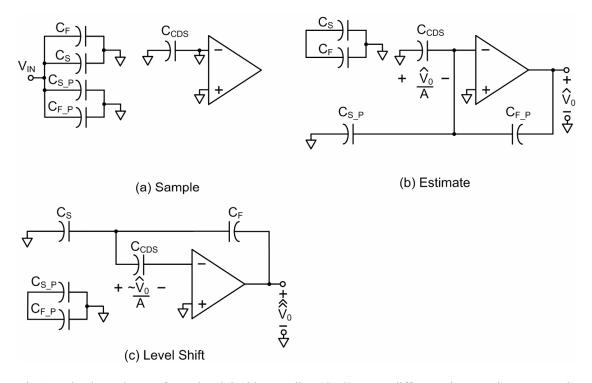

CLS can be implemented as shown in Fig. 12. Single ended is shown for simplicity. There are three phases: 1) sample input, 2) estimate output signal and store

Fig. 12. The three phases of correlated level shifting (CLS), and the waveform at the load. The opamps gains  $A_{(EST)}$  and  $A_{(LS)}$  are different because the opamp output is different in the respective phases. Single ended is shown for simplicity.

it on  $C_{CLS}$ , 3) level shift to eliminate signal from opamp. The  $C_{CLS}$  capacitor can be reset during the sample phase to eliminate memory effects. Note that the operation is identical to the two phases used in a typical MDAC [8] with a level-shifting phase added as a third step.

Fig. 15 shows that CDS has analogous steps, but the error (not the signal) is stored and eliminated from the signal (not the opamp). For the purposes of this paper, the steps for both CLS and CDS will be referred to as sample, estimate, and level shift.

### 2.2.3 Transient behavior and speed

One would expect the CLS operation to have a speed disadvantage compared to a higher gain amplifier. Surprisingly, the settling times are about the same if the amplifiers have the same phase margin and bandwidth. Furthermore, when one considers practical design constraints, CLS will generally be faster than other methods to achieve high precision.

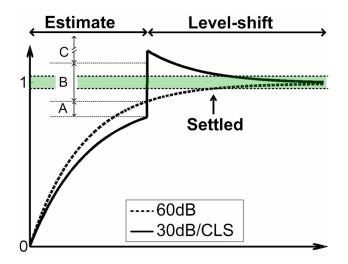

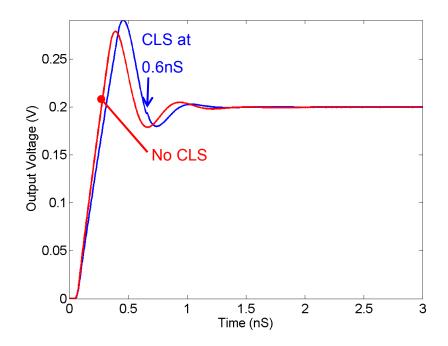

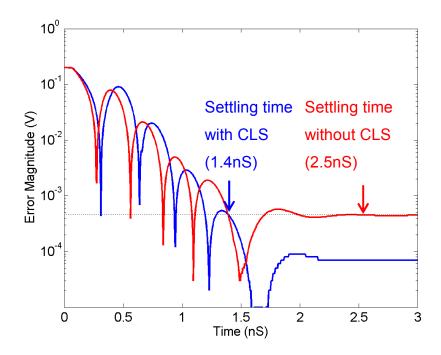

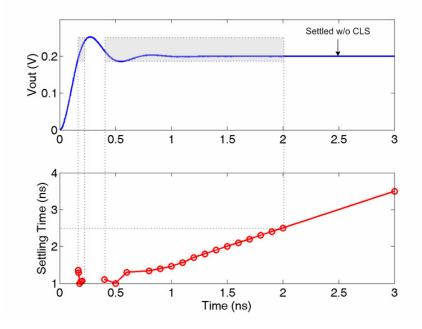

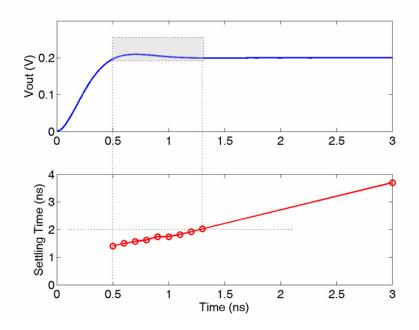

Fig. 13 is a simulation result that will be used to illustrate some general speed trends of a 30dB opamp using CLS compared to a 60dB opamp that doesn't use CLS. Both opamps have the same phase margin and bandwidth. The CLS allows the 30dB opamp to settle to the same accuracy as the 60dB opamp.

The signal using CLS has a jump at the beginning of the level-shift phase that determines if the 30dB/CLS combination is faster or slower than the 60dB opamp. This jump is caused by capacitance at the output of the opamp, and its height is determined by the relative size of the output capacitance and the load that it sees. We can make some observations about the settling times based on the size of the jump since both amplifiers have the same settling characteristics. If the output capacitance is very small compared to the load, the CLS circuit output will start the level-shift phase below the 60dB opamp curve (region A) and the settling time will be longer because it has further to settle. Similarly if the output capacitance is very large the CLS circuit will start in region C and take longer to settle. On the other hand, the CLS circuit will settle faster than the 60dB circuit if it starts the level-shift phase in region B.

Fig. 13. Transient response of a 30dB amplifier using CLS compared to a conventional 60dB opamp.

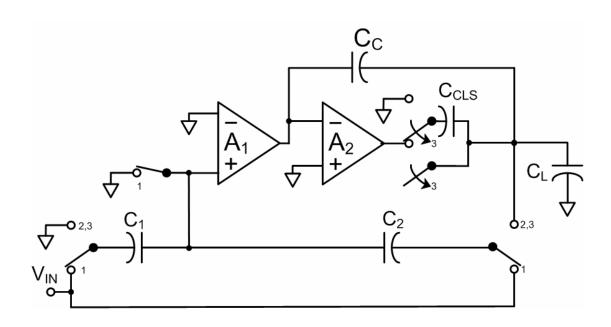

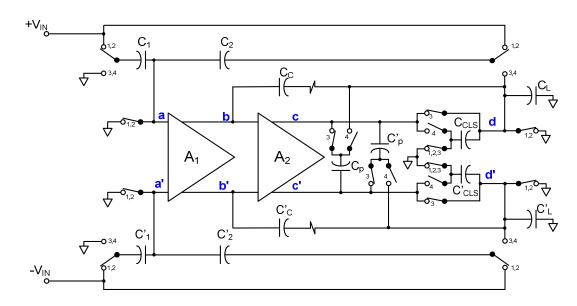

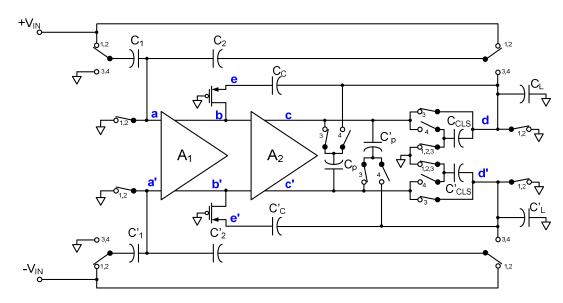

Fig. 14. CLS placement in a fully differential multi-stage amplifier with inter-stage compensation. The network should be inside the compensation loop to keep settling times the same during estimation and level-shifting phases.

Simulations show that practical circuits can start the level-shifting phase in region B, but often start in the lower part of region C and settle 10-20% slower. However, it is incorrect to infer that CLS is slower because the 30dB opamp will have fewer stages and consume roughly half the power of a 60dB opamp for the same bandwidth in a

realistic design. Since the settling times are close to begin with, the ability to use twice the power indicates that CLS would be a faster method. In addition, the CLS will increase the swing of the opamp so smaller sampling capacitors can be used to achieve the same SNR. For example, Fig. 11 shows CLS increases the opamp output range from about 0.6V to the entire 0.9V supply. As a result, the standard configuration requires a complex opamp and 2.25x larger sampling capacitors to achieve the same signal to kT/C noise ratio as CLS. Thus a high gain opamp without CLS will need to increase the power by a factor of 2.25 to maintain the speed, a factor of two to achieve the gain, and likely more to maintain the phase margin. These advantages are tempered by the digital overhead and the slightly larger current required to maintain phase margin while driving  $C_{CLS}$ . Nonetheless, it is very plausible that CLS with a simple opamp will be faster than a high gain opamp, given the nominal ~5x speed advantage of the simple opamp if the same power is used.

Even with a 3.3V supply the sampling capacitors need to be  $\sim$ 17% larger to achieve the same SNR and, when you account for the power required for the additional stages in a high gain amplifier, the CLS opamp will be  $\sim$ 2.3 times faster if the same power is used.

## 2.2.4 CLS error reduction analysis

This sub-section quantifies the amount that CLS reduces the effects of finite opamp gain. The variables are defined by Fig. 12.

The circuit in Fig. 12 can be analyzed to show that the output voltage at the end of the estimation phase is

$$\hat{V}_0 = V_{IN} \left( 1 + \frac{C_1}{C_2} \right) \left( \frac{1}{1 + 1/T} \right),$$

(4)

where  $T = \frac{A_{(EST)}C_2}{(C_1 + C_2 + C_{IN})}$  is the opamp loop gain during the estimation phase.

This first estimate  $(\hat{V}_0)$  is less than the error-free output (i.e.  $V_0 = V_{IN}(1+C_1/C_2)$ ) because the finite opamp gain produces an imperfect virtual ground so  $C_1$  doesn't completely transfer its charge to  $C_2$ . The residual voltage on  $C_1$  from the imperfect virtual ground is

$$V_{C1(EST)} = \frac{-\hat{V}_0}{A_{(EST)}}.$$

<sup>(5)</sup>

Traditionally this error is reduced by making the opamp DC gain (i.e. A) as large as possible, but notice that the error could also be reduced by making the output of the opamp small. This is what CLS does: it removes the signal from the active circuitry by storing the first estimate of the output voltage on  $C_{CLS}$  and then removing that signal from the output of the opamp in the level-shift phase (Fig. 12). Thus the residue voltage on  $C_1$  is much smaller at the end of the level-shift phase. If we neglect the charge lost from  $C_{CLS}$ , the voltage at the inverting node at the end of the level-shifting phase is:

$$V_{C1(LS)} \approx \frac{-\left(\hat{\hat{V}}_{0} - \hat{V}_{0}\right)}{A_{(LS)}},$$

(6)

where  $\hat{V}_0$  is referred to as the second estimate. This is much smaller than (5), which means that the charge from C<sub>1</sub> is closer to being completely transferred to C<sub>2</sub>.

The output voltage can be found using traditional techniques (see Appendix for details).

$$\hat{\hat{V}}_{0} = V_{IN} \left( 1 + \frac{C_{1}}{C_{2}} \right) \left( \frac{1}{1 + 1/T_{EQ}} \right),$$

(7)

where the equivalent loop gain is

$$T_{\rm EO} = T(2+T) \approx T^2. \tag{8}$$

Equation (8) neglects the charge loss from  $C_{CLS}$  and lets  $A_{(EST)} = A_{(LS)}$ . Charge transfer from  $C_{CLS}$  to the load will reduce the equivalent gain. This effect is quantified by  $\lambda$  in the Appendix (section 8).

## 2.3 Multi-stage opamp considerations

### **2.3.1** Special considerations

There are two minor special considerations when using multi-stage opamps that are compensated with inter-stage capacitance, as in the popular Miller and cascode compensated schemes [9]-[10]. First, the bandwidth will be reduced during the level-shift phase unless the circuit in Fig. 12 is slightly modified. Secondly, charge from the Miller compensation capacitor can be used offset the charge supplied by  $C_{CLS}$ , resulting in a much higher equivalent loop gain. These are discussed in the next two sub-sections.

### 2.3.2 Bandwidth considerations

If the opamp is compensated by the load (as in a single stage OTA), the bandwidth is about the same during the estimate and level-shifting phases. The bandwidth stays the same even though putting  $C_{CLS}$  in series with the load reduces the loop gain because it also reduces the load (i.e. compensation) by the same amount.

This will not happen if the compensation is inter-stage (e.g. Miller or cascode [9]-[10]). The loop gain decrease will lower the bandwidth of the configuration shown in Fig. 12, resulting in a level-shifting phase that is much slower than the estimate phase because there is no corresponding decrease in compensation. This problem is solved by putting  $C_{CLS}$  inside the compensation loop (Fig. 14). The bandwidth is the same during the estimate and level-shift phases because the lowered loop gain during the level-shift phase decreases the Miller multiplication of the compensation capacitance.

These bandwidth observations are intuitive if one realizes the amplifiers in Fig. 14 are really voltage-controlled current sources (transconductances). As such, their output currents are not affected by series capacitive elements to first order. On the other hand, it can be seen that any capacitance at the output of the last stage forms a capacitive current divider with  $C_{CLS}$  which reduces the output stage's transconductance. This reduced transconductance reduces the phase margin during the level-shift phase, requiring the output stage current to be slightly larger than what would be needed if a traditional OTA was used. The reduction is partially offset

because the opamp no longer has to drive  $C_{CLS}$ . Nonetheless the divider can place a lower bound on the size of  $C_{CLS}$  and power savings in high-speed designs where the opamp output capacitance can be comparable to the load.

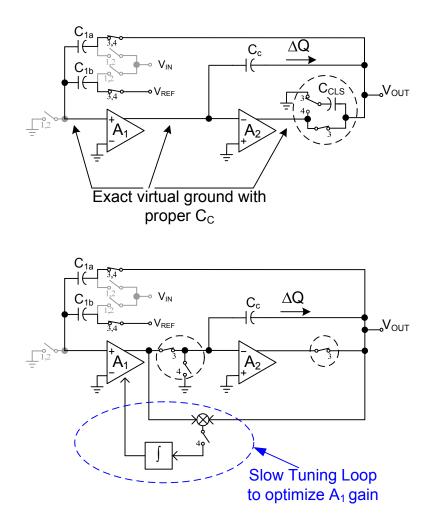

#### **2.3.3** Enhanced equivalent gain with Miller compensation

The Appendix (section 8) shows that the charge required to change the output voltage from  $\hat{V}_0$  to  $\hat{\hat{V}}_0$  comes from  $C_{CLS}$ , and this charge loss lowers the equivalent loop gain ( $T_{EQ}$ ). The effect is quantified by the term  $\lambda$  (17). This charge will be partially provided by the compensation capacitance ( $C_C$ ) if Miller compensation is used resulting in enhanced gain under some conditions.

Physically, the different equivalent gains are caused by differing amounts of level shifting. With very large  $C_{CLS}$ , the opamp output will be level shifted by  $\hat{V}_0$ , which is slightly less than the error free amount. Consequently, the second estimate is still slightly less than the error free voltage. Finite  $C_{CLS}$  results in slightly more error because the level shifting will be less than  $\hat{V}_0$  due to the charge loss. However, Miller compensation reduces the error because it adds charge to  $C_{CLS}$  and causes the level shifting to be slightly more than  $\hat{V}_0$ .

If  $C_{CLS}$  is sized so that  $\lambda = -1$ , we get a perfect estimate stored onto  $C_{CLS}$  and the equivalent opamp gain is theoretically infinite, but a ~10dB increase is a more realistic expectation over corners unless  $A_1$  is well controlled. A value of  $\lambda$  less than -1 does not indicate an unstable positive feedback condition even though  $T_{EQ}$  will be negative; rather, it means that the compensation capacitor adds more charge than necessary, which causes the magnitude of the output voltage to be slightly *larger* than the error free value. CLS works with other compensation methods such as cascode compensation. These other methods may have benefits that outweigh the gain enhancement that Miller compensation gives. In fact, very large first-stage gain will make  $\lambda < -2$  and the gain will be degraded instead of enhanced by using Miller compensation.

# 2.4 CLS compared to CDS

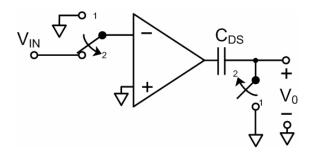

# 2.4.1 Equivalent gain of CDS

Fig. 15 shows that CDS [2], [3], [7] has steps that are similar to CLS. The output voltage after the analogous "level shift" phase is

$$\hat{\mathsf{V}}_{0} \approx \mathsf{V}_{\mathsf{IN}} \left( 1 + \frac{\mathsf{C}_{1}}{\mathsf{C}_{2}} \right) \left( \frac{1}{1 + \zeta / \mathsf{T}^{2}} \right), \tag{9}$$

where  $\zeta$  is a term analogous to  $\lambda$  in to account for charge sharing between the error storage capacitor and its load.

Like CLS, the error due to opamp loop gain is inversely proportional to loop gain squared, but there is a difference that gives CLS a large performance improvement:

Fig. 15. The three phases of correlated double sampling (CDS). Note difference in operation compared to CLS shown in Fig. 12

the level-shift phase returns the opamp output towards the mid-rail, where opamp gain will be the largest. This is especially important when the output is close to the rails because  $A_{(EST)}$  will be very small. Simulation results in Fig. 16 show the performance differences. Note how the equivalent open-loop gain for CLS is shifted up by  $A_{(LS)}$ over the entire output range. (Actually the gain is increased by +6dB more than  $A_{(LS)}$ due to Miller enhancement.) The CLS equivalent loop gain is much better than the CDS equivalent loop gain, which is just the opamp gain squared with some significant attenuation due to charge sharing ( $\zeta$ ).

Fig. 16. Simulated open loop gain versus output voltage using CLS or CDS with a 36dB opamp. The gain is lowest near the 0 and 0.9V supplies. The gain with no enhancement  $(A_{(EST)})$  is also shown for comparison.

### 2.4.2 Noise and offset

The noise power added by the CLS sampling network is

$$V_n^2 \approx \frac{(1+C_1/C_2)^2 V_{n(op)}^2 + kT/C_{CLS}}{A_{(LS)}^2},$$

(10)

where  $V_{n(op)}$  is the noise from the opamp that is sampled onto  $C_{CLS}$ , including the components that are folded down.

The noise power for CDS is

$$V_n^2 \approx (1 + (C_1 + C_{DS})/C_2)^2 V_{n(op)}^2 + (1 + C_1/C_2)^2 kT/C_{CDS}, \qquad (11)$$

where  $C_{CDS}$  is the capacitor that stores the error.

CLS has significantly better noise performance than CDS because the method removes the *signal* from the active circuitry by storing it on  $C_{CLS}$  *inside the loop between the gain block and the output*. The result is that imperfections sampled onto  $C_{CLS}$  during the estimate phase are reduced by the DC gain during the level-shift phase. These sampled imperfections include thermal noise and such things as charge injection and errors from finite swing or even incomplete settling.

CDS, on the other hand, samples the *error* and subtracts it from the signal. Thus any sampled imperfections are *directly added to the signal*. The opamp noise sampled onto  $C_{CDS}$  is very significant and limits the usefulness of CDS. In addition,  $C_{CDS}$  needs to be large or its kT/C<sub>CDS</sub> noise contribution will be significant, but large  $C_{CDS}$  lowers the loop gain (and bandwidth) during the estimate phase

The one area where CDS is better than CLS is canceling noise that does not change between the estimate and level-shifting phases (e.g. noise with frequencies much lower than the sampling frequencies including opamp offset). CDS cancels these effects, whereas CLS does not.

### 2.4.3 Complexity

CLS also has a significant advantage over CDS in terms of complexity. To boost gain effectively, CDS needs to use two different sets of matched capacitors for the estimation and level-shifting phases [7]. CLS can use a single set of capacitors without losing performance.

## 2.4.4 Output offset storage (CDS at output)

Superficially, CLS resembles output referred CDS, also referred to as output offset storage (OOS) [3]. A schematic using OOS is shown in Fig. 17. There are some key behaviors that differentiate OOS from CLS. First, OOS is a method to remove offset and low frequency noise (i.e. noise slow compared to the sample rate). CLS does not remove these DC and low frequency errors. Second, unlike CLS, OOS does not enhance gain, nor does it remove the signal from the active circuitry. Third, sampling imperfections are directly added to the output when OOS is used, whereas sampling errors are attenuated by the open loop gain with CLS. Clearly, when one considers these three differences, one must draw a distinction between OOS and CLS.

Fig. 17. Output offset storage

# 2.5 Pipelined A/D converter implementation

## 2.5.1 Prior methods to reduce low opamp gain effects in ADCs

Pipelined A/D converters require the first few stages to provide a very accurate gain. The accuracy of this gain is limited by the finite loop gain of the opamp used in the multiplying A/D converter (MDAC). For example, a 10-bit pipelined A/D converter needs the first-stage opamp to have at least 60dB DC gain. Several methods have been used to provide high DC gain opamps in pipelined ADCs. These include nested gain boosting [6] and CDS [7]. Measuring and compensating the error with a parallel A/D converter [12] is another method. CLS is simpler than these methods.

Foreground and background digital calibration [13]-[19] are very good techniques to compensate for finite opamp gain, but they cannot increase the linear range of the opamps to use the whole supply as CLS can. The ability to efficiently use the whole supply gives CLS a clear advantage because smaller sampling capacitors and lower power opamps can be used to achieve the same SNR.

Nonlinear calibration [19] can extend the range somewhat, but not nearly as much as CLS, which can go to and beyond the rails. Digital calibration also takes many cycles to respond to events such as power supply changes. On the other hand, the error reduction from CLS is updated each cycle.

Finally, CLS can be used in conjunction with calibration. The increased linear range of CLS circuits will enhance the performance of digitally calibrated circuits.

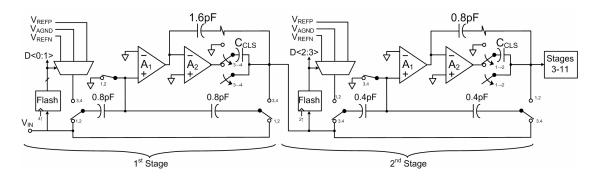

# 2.5.2 CLS pipelined A/D topology