#### AN ABSTRACT OF THE THESIS OF

<u>Sirikarn Woracheewan</u> for the degree of <u>Master of Science</u> in Electrical and Computer Engineering presented on October 26, 2010.

Title: Measurement and Characterization of Ultra-wideband Wireless Interconnects within Active Computing Systems.

| A 1                 |  |  |

|---------------------|--|--|

| Abstract approved:  |  |  |

| ribbutaco approvoa. |  |  |

#### Patrick Chiang

Ultra-wideband (UWB) radio has become an attractive alternative for wireless communications due to the robustness to multipath fading, low power transmission, mostly-digital implementation, and low cost. Furthermore, short-range, high data-rates applications are possible with UWB radios due to the wide spectral allocations at 3.1-10.6 GHz.

This thesis presents experimental measurements of UWB wireless interconnects within an operational computer system chassis. The purpose of the thesis is to analyze and verify the implementation of high-bandwidth wireless communications using an impulse-radio ultra-wideband (IR-UWB) 3.1-5 GHz transceiver within an enclosed, heavy multipath, metallic environment such as a computer server chassis. Bit-error-rate (BER) and recovered clock jitter were measured at various positions within the computer chassis. The results show a 6X improvement in BER after applying the equalizer to the noisy channel while the motherboard is fully operating.

©Copyright by Sirikarn Woracheewan October 26, 2010 All Rights Reserved

# Measurement and Characterization of Ultra-wideband Wireless Interconnects within Active Computing Systems

by

Sirikarn Woracheewan

#### A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Master of Science

Presented October 26, 2010 Commencement June 2011

| <u>Master of Science</u> thesis of <u>Sirikarn Woracheewan</u> presented on        |

|------------------------------------------------------------------------------------|

| October 26, 2010                                                                   |

|                                                                                    |

|                                                                                    |

|                                                                                    |

| APPROVED:                                                                          |

|                                                                                    |

|                                                                                    |

|                                                                                    |

| Major Professor, representing Electrical and Computer Engineering                  |

|                                                                                    |

|                                                                                    |

|                                                                                    |

| Director of the School of Electrical Engineering and Computer Science              |

|                                                                                    |

|                                                                                    |

|                                                                                    |

| Dean of the Graduate School                                                        |

|                                                                                    |

|                                                                                    |

| I understand that my thesis will become part of the permanent collection of Oregon |

| State University libraries. My signature below authorizes release of my thesis to  |

| any reader upon request.                                                           |

| any roader apon request.                                                           |

|                                                                                    |

| Sirikarn Woracheewan, Author                                                       |

|                                                                                    |

#### ACKNOWLEDGMENTS

First of all, I would like to express my sincere gratitude to my major advisor Dr. Patrick Chiang for giving me an opportunity to work in his research group. I would like to thank him for his valuable suggestions and guidance through my research work. I also would like to thank Dr. Huaping Liu for spending his time reviewing my work and giving me very helpful advice.

I would like to thank Dr. Huaping Liu and Dr. Thinh Nguyen for serving on my committee and reviewing my thesis. I would like to thank the Graduate Council Representative Dr. Brady Gibbons for being a part of my committee. My special thanks to Dr. Gabor Temes, Dr. Kartikeya Mayaram, Dr. Un-Ku Moon, and Dr. Pavan Kumar Hanumolu for their excellent analog and mixed-signal courses. I want to thank Feren Simendinger for her helpful information on program requirements and administrative assistance. I also thank Matt Brown for an orientation of using analog/mixed-signal laboratory.

I would like to thank my graduate colleagues in analog and mixed-signal group for their kindly support and friendships. My special thanks to Amr Elshazly, Saurabh Saxena, Samira Zali Asl, Saeed Pourbagheri, Ronghua Ni, and Jinzhou Cao for their willing helps and useful discussion on class projects, measurements, and thesis. I like to thank Napong Panitantum, James Ayers, and Thomas Brown for helpful advice in Cadence simulation and lab measurements. I like to thank Kangmin Hu, Tao Jiang, Divya Kesharwani, Karthik Jayaraman and the rest of VLSI research group members for their helps.

Most importantly, I would like to express my deepest love and gratitude to my parents for their love, understanding, support, advice, and encouragement during the difficult time. Without them, I would not have achieved this goal.

# TABLE OF CONTENTS

|   |      |                                                                                                                                                                                                          | Page         |

|---|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 1 | INTI | RODUCTION                                                                                                                                                                                                | 1            |

|   | 1.1  | Motivation                                                                                                                                                                                               | 2            |

|   | 1.2  | Challenges                                                                                                                                                                                               | 3            |

|   | 1.3  | Thesis Organization                                                                                                                                                                                      | 3            |

| 2 | UWI  | B COMMUNICATION                                                                                                                                                                                          | 5            |

|   | 2.1  | Introduction                                                                                                                                                                                             | 5            |

|   |      | 2.1.1 Regulation. 2.1.2 Standards                                                                                                                                                                        |              |

|   | 2.2  | Signal Characteristics                                                                                                                                                                                   | 8            |

|   | 2.3  | UWB Applications                                                                                                                                                                                         | 10           |

|   |      | <ul> <li>2.3.1 Wireless Personal Area Networks (WPANs)</li> <li>2.3.2 Wireless Sensor Networks (WSNs)</li> <li>2.3.3 Wireless Body Area Networks (WBANs)</li> <li>2.3.4 Radar/Imaging Systems</li> </ul> | . 10<br>. 11 |

|   | 2.4  | Pulse-based Transmission                                                                                                                                                                                 | 12           |

|   |      | 2.4.1 Pulse Generator                                                                                                                                                                                    |              |

|   | 2.5  | Channel Characteristics                                                                                                                                                                                  | 18           |

|   |      | 2.5.1 Path Loss                                                                                                                                                                                          | . 19         |

| 3 | MEA  | ASUREMENT SETUP                                                                                                                                                                                          | 23           |

|   | 3.1  | Experimental Setup                                                                                                                                                                                       | 23           |

|   | 3.2  | Channel Environments                                                                                                                                                                                     | 26           |

# TABLE OF CONTENTS (Continued)

|   |     |                                      | Page |

|---|-----|--------------------------------------|------|

|   | 3.3 | Channel on Top of Motherboard        | 28   |

|   |     | 3.3.1 TX1 and RX1                    |      |

|   |     | 3.3.3 TX2 and RX3                    | 32   |

|   |     | 3.3.5 TX3 and RX5                    |      |

|   | 3.4 | Channel at Bottom of Motherboard     |      |

|   |     | 3.4.1 TX1' and RX1'                  | 37   |

|   |     | 3.4.4 TX2' and RX4'                  | 39   |

|   |     | 3.4.6 TX3' and RX6'                  |      |

|   | 3.5 | IR-UWB Transceiver                   | 42   |

| 4 | MEA | ASUREMENT RESULTS                    | 44   |

|   | 4.1 | Post-Processing                      | 44   |

|   | 4.2 | Freespace                            | 45   |

|   | 4.3 | Top of Motherboard inside Chassis    | 47   |

|   |     | 4.3.1 TX1 and RX1                    | 49   |

|   |     | 4.3.4 TX2 and RX4                    | 52   |

|   |     | 4.3.6 TX3 and RX6                    |      |

|   | 4.4 | Bottom of Motherboard inside Chassis |      |

|   | 4.5 | Summary                              | 60   |

# TABLE OF CONTENTS (Continued)

|    |            |      |      | Pag | <u>ge</u> |

|----|------------|------|------|-----|-----------|

| 5  | CONCLUSION | <br> | <br> |     | 63        |

| BI | BLIOGRAPHY | <br> | <br> |     | 65        |

# LIST OF FIGURES

| Figu | $\frac{\text{Pa}}{\text{Pa}}$                                                                                           | ge |

|------|-------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | FCC spectral mask for UWB indoor and outdoor communication                                                              | 7  |

| 2.2  | A Gaussian pulse and higher-order derivative of the Gaussian pulse                                                      | 14 |

| 2.3  | Four different modulation schemes                                                                                       | 16 |

| 2.4  | An example of multipath propagation in indoor environment                                                               | 21 |

| 3.1  | Overview of the measurement setup                                                                                       | 24 |

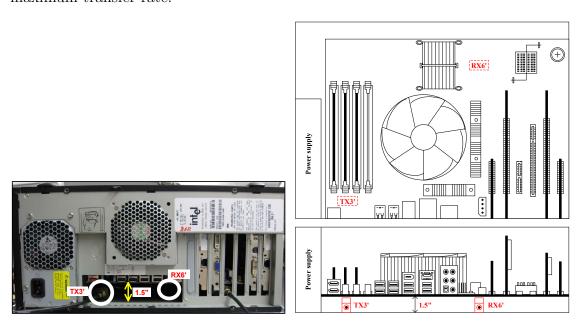

| 3.2  | Different locations of transmitting and receiving antennas on the top and bottom of the motherboard inside the computer | 25 |

| 3.3  | Top view and side view on top of the motherboard                                                                        | 28 |

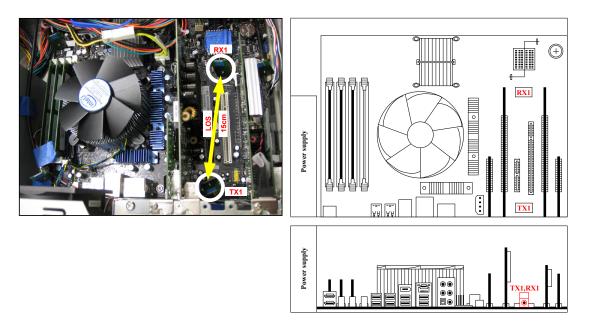

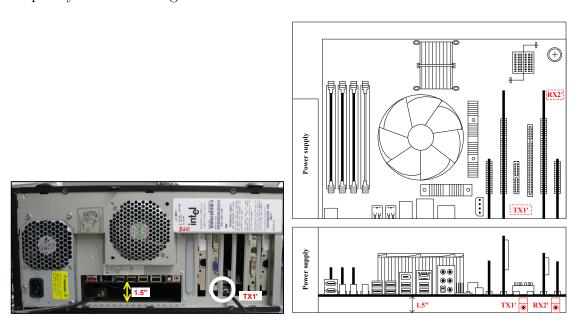

| 3.4  | Top view and side view of TX1 and RX1 on top of mother<br>board .                                                       | 29 |

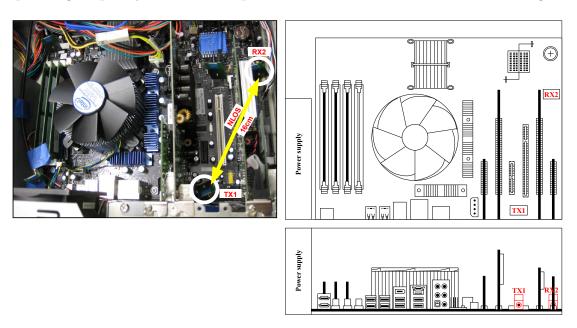

| 3.5  | Top view and side view of TX1 and RX2 on top of mother<br>board .                                                       | 30 |

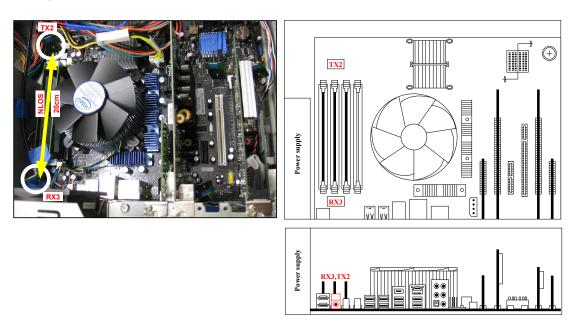

| 3.6  | Top view and side view of TX2 and RX3 on top of mother<br>board .                                                       | 31 |

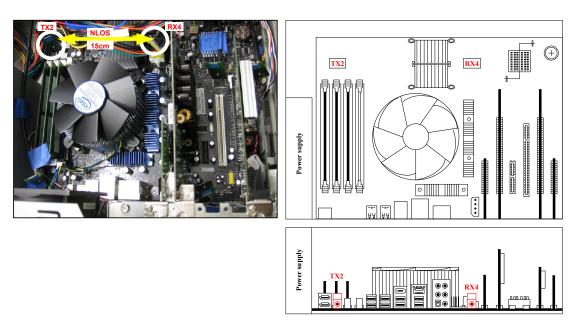

| 3.7  | Top view and side view of TX2 and RX4 on top of mother<br>board .                                                       | 32 |

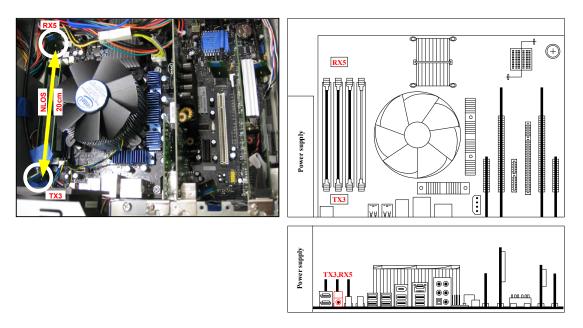

| 3.8  | Top view and side view of TX3 and RX5 on top of mother<br>board .                                                       | 33 |

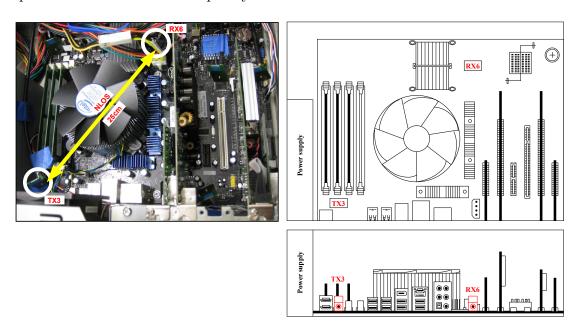

| 3.9  | Top view and side view of TX3 and RX6 on top of mother<br>board .                                                       | 34 |

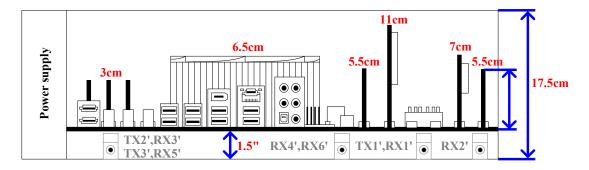

| 3.10 | Side view underneath of the motherboard                                                                                 | 35 |

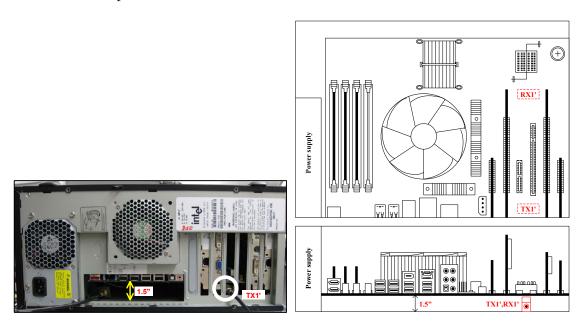

| 3.11 | Top view and side view of $\mathbf{TX1}'$ and $\mathbf{RX1}'$ under the mother<br>board                                 | 36 |

| 3.12 | Top view and side view of $TX1^{'}$ and $RX2^{'}$ under the motherboard                                                 | 37 |

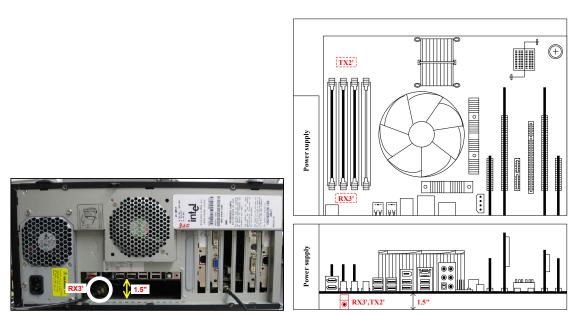

| 3.13 | Top view and side view of $TX2^{\prime}$ and $RX3^{\prime}$ under the mother<br>board                                   | 38 |

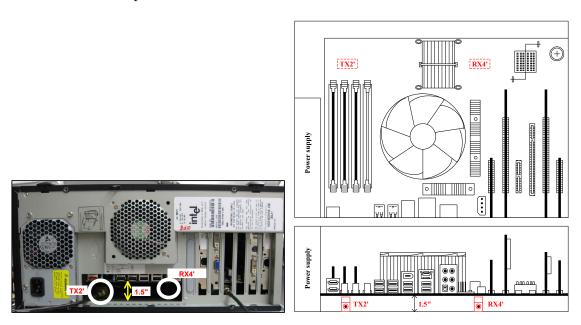

| 3.14 | Top view and side view of $TX2^{\prime}$ and $RX4^{\prime}$ under the mother<br>board                                   | 39 |

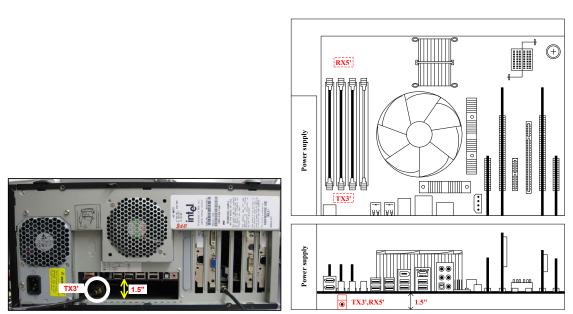

| 3.15 | Top view and side view of $\mathrm{TX3}'$ and $\mathrm{RX5}'$ under the mother<br>board                                 | 40 |

| 3.16 | Top view and side view of $TX3^{'}$ and $RX6^{'}$ under the motherboard                                                 | 41 |

| 3.17 | IR-UWB transceiver block diagram                                                                                        | 42 |

| 4.1  | Block diagram of MATLAB post-processing for BER calculation .                                                           | 45 |

# LIST OF FIGURES (Continued)

| Figu | <u>ure</u>                                            | Page |

|------|-------------------------------------------------------|------|

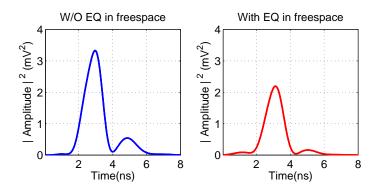

| 4.2  | Time-domain received waveform in freespace            | . 46 |

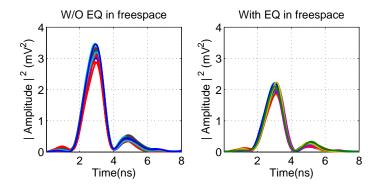

| 4.3  | Received pulse response in freespace                  | . 46 |

| 4.4  | Multiple bits of received pulse response in freespace | . 46 |

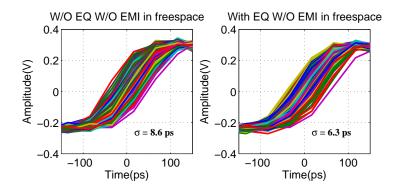

| 4.5  | Recovered ADC clock jitter in freespace               | . 47 |

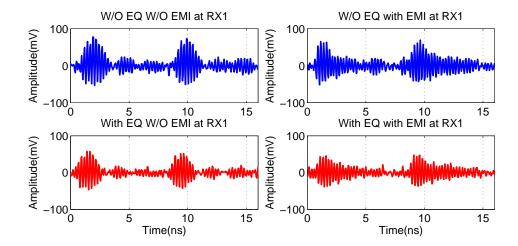

| 4.6  | Time-domain received waveform at RX1                  | . 48 |

| 4.7  | Received pulse response at RX1                        | . 48 |

| 4.8  | Recovered ADC clock jitter at RX1                     | . 49 |

| 4.9  | Time-domain received waveform at RX2                  | . 49 |

| 4.10 | Received pulse response at RX2                        | . 50 |

| 4.11 | Recovered ADC clock jitter at RX2                     | . 50 |

| 4.12 | Time-domain received waveform at RX3                  | . 51 |

| 4.13 | Received pulse response at RX3                        | . 51 |

| 4.14 | Recovered ADC clock jitter at RX3                     | . 52 |

| 4.15 | Time-domain received waveform at RX4                  | . 53 |

| 4.16 | Received pulse response at RX4                        | . 53 |

| 4.17 | Recovered ADC clock jitter at RX4                     | . 54 |

| 4.18 | Time-domain received waveform at RX5                  | . 54 |

| 4.19 | Received pulse response at RX5                        | . 55 |

| 4.20 | Recovered ADC clock jitter at RX5                     | . 55 |

| 4.21 | Time-domain received waveform at RX6                  | . 56 |

| 4.22 | Received pulse response at RX6                        | . 57 |

| 4.23 | Recovered ADC clock jitter at RX6                     | . 57 |

| 4 24 | Time-domain waveform under the motherboard            | 58   |

# LIST OF FIGURES (Continued)

| Figure                                    | Page |

|-------------------------------------------|------|

| 4.25 Pulse response under the motherboard | 58   |

# LIST OF TABLES

| Tal | <u>ole</u>                                      | Page |

|-----|-------------------------------------------------|------|

| 2.1 | FCC Spectral Mask Limits                        | 6    |

| 3.1 | Feature summary of the DX58SO motherboard       | 27   |

| 4.1 | Path loss measurements                          | 60   |

| 4.2 | Recovered ADC clock jitter for different setups | 61   |

| 4.3 | BER measurement for different setups            | 62   |

# MEASUREMENT AND CHARACTERIZATION OF ULTRA-WIDEBAND WIRELESS INTERCONNECTS WITHIN ACTIVE COMPUTING SYSTEMS

#### CHAPTER 1. INTRODUCTION

The down scaling of CMOS technology has enabled increased integration of multiple, high-frequency chips onto a single printed circuit board (PCB). For example, in embedded applications such as a cell phone, this portable device consists of the RF front-end, wireless transceiver, LCD displayer, flash memory cards, multimedia processor, power management circuits, etc. However, traditional wired interconnects for applications that connect many of these chips together such as shared busses or daisy-chained point-to-point serial interconnects degrade in performance as the number of chips increases due to larger interconnect parasitic [1] and serialization latency, respectively. One potential solution is short-range wireless interconnects, yielding an improvement by reducing latency [2], minimizing power consumption, enhancing fault tolerance, and mitigating the problem of signal dispersion in wired channels [3].

Ultra-wideband (UWB) impulse radio has become a promising alternative for these inter/intra-chip wireless communications due to a property of immunity to multipath fading, low transmit output power, fine timing resolution, mostlydigital implementation allowing circuit simplicity, and low cost [4]. Furthermore, high data rates for short-range applications are possible with UWB radios due to the large spectral allocations at 3.1 - 10.6 GHz [5]. Occupying a very wide spectrum, UWB radio system also offers the provision of increasing demand for multi-users.

#### 1.1 Motivation

Consisting of several ICs on a single motherboard, conventional computing systems incorporate many types of interconnects with various bandwidth; for example, high-speed links such a front-side bus (FSB) as CPU-main memory and processor-I/O controller, which are required a high performance operation. On the other hand, low-speed control buses such as serial Joint Test Action Group (JTAG) is likely to operate at lower performance.

These short-range wireless interconnects may be compelling for elimination of daisy-chained low-bandwidth buses whereas their use are unlikely to replace dedicated high-bandwidth front-side buses. For example, by replacing the low speed wired interfaces such as serial JTAG, wireless links can enable computing system improvements. Since the JTAG is a serial interconnect widely used for testing and debugging part defects and connectivity failures on circuit ports of microprocessors, wireless JTAG can be directly access to each JTAG port without waiting for coming serial daisy-chained registers [6], resulting in low latency and fault tolerance. Due to the reduction in latency, power optimization can be achieved. Moreover, reduced clock jitter is feasible in wireless systems [2].

# 1.2 Challenges

Several significant challenges exist for the use of wireless ultrawideband communications inside the unique computing channel such as the computer chassis. This particular channel environment is a short-distance metallic enclosure consisting of many electromagnetic-reflective materials; therefore, this computing surroundings appear to be a heavy multipath channel. Electromagnetic interference (EMI) generated by the switching noise of several ICs on the server motherboard can also limit the maximum data transfer and increase the bit-error-rate. In addition, channel characteristics [7] such as path loss, path gain, signal attenuation, reflection, and dispersion in UWB radio channels are basically different from these in conventional channels [8]. This is due to the large bandwidth, making these characteristic parameters frequency dependent. Furthermore, it is important to make sure that UWB radio system will not cause significant interferences to other useful operations in a close proximity owing to its wide spectrum. These constraints need to be investigated for the within-chassis channel environment so that the desired high-bandwidth performance can be achieved.

# 1.3 Thesis Organization

The thesis presents the measurement and characterization of ultra-wideband (UWB) wireless interconnects within active computing systems. The focus of the thesis is to analyze and verify the implementation of high-bandwidth wireless communications inside an enclosed, dense multipath, metallic environment such as a computer server chassis.

Chapter 2 provides a fundamental of UWB communications. The advantages of UWB radio and its broad applications are described. A basis of pulse transmissions is presented. Channel characteristics such as path loss and multipath propagation for UWB radio are also discussed.

Chapter 3 illustrates a measurement setup of short-range wireless interconnects within the computer chassis using an impulse-radio ultra-wideband (IR-UWB) operating in the frequency range of 3.1-5 GHz. The channel environment of an enclosed computer case on both the top and bottom of the server motherboard is described.

Chapter 4 presents measurement results at different positions of transmitters and receivers on both the top and bottom of the motherboard. Time-domain waveforms with an effect of multipath propagation are discussed. The performance of pre-transmitted equalization on mitigating multipath components is presented. Bit-error-rate and recovered clock jitter after the equalization are described.

Chapter 5 concludes the potential of implementing UWB wireless communications inside the computer server chassis.

#### CHAPTER 2. UWB COMMUNICATION

Ultra-wideband (UWB) communication has recently gained immense interest in wireless communication, networking, positioning, radar, and imaging system. Low energy levels in a large portion of spectrum makes UWB impulse radio attractive for both very high data rate and low data rate short-range applications. This chapter provides a basic understanding of UWB communications including the FCC regulated power radiation, standards in the IEEE, UWB signal characteristics, and its wide application areas. A basis of UWB pulse transmission is presented. UWB channel characteristics are also discussed.

#### 2.1 Introduction

UWB radio has become an attractive alternative for communication systems since it utilizes a very short pulse in transmission, resulting in occupying a very wide bandwidth in frequency domain. Impulse radio has been developed by the spark-gap transmission experiments of Marconi in 1901 [9]. A significant change in UWB happened when the US Federal Communication Commission (FCC) issued a regulation that allows the new band between 3.1 GHz to 10.6 GHz to be used as unlicensed communications. The enormous bandwidth of UWB impulse radio offers the potential of the increased data rate up to Gbps. However, the wide bandwidth is overlaid on other existing bands, causing interferences to these primary bands. To avoid interfering in other operating systems, the FCC set a limitation on the power emission levels of UWB pulse to be very low over the 7.5 GHz band.

# 2.1.1 Regulation

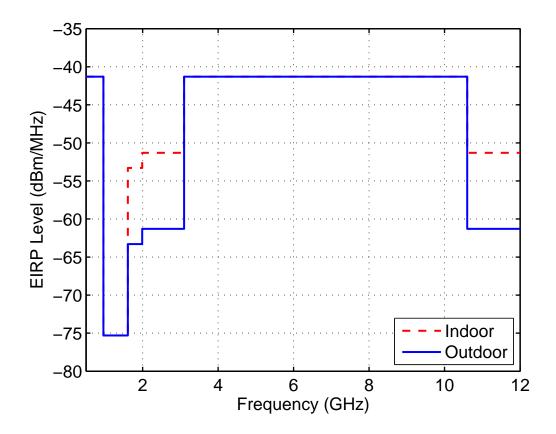

The range of operating frequency is one of the important concerns in UWB communication. Due to occupancy in very wide frequency spectrum, UWB system could potentially interfere in already available wireless services such as the Global Positioning System (GPS). In 2001, a National Telecommunications and Information Administration (NTIA) reported the effect of UWB emissions on GPS, operating at 1.2 GHz and 1.6 GHz that increases signal attenuation by 20-35 dB [10]. To ensure that license-free use of UWB radio do not cause significantly harmful interference to other useful existing systems, in February 2002 the FCC placed a requirement on UWB radiated power spectral density at a constant -41.3 dBm/MHz over the frequency range of 3.1 GHz to 10.6 GHz. The current FCC mask regulations of power emission levels for UWB indoor and outdoor communications are presented in Table 2.1 and shown in Fig. 2.1.

Table 2.1: FCC Spectral Mask Limits

| Frequency Range (MHz) | Indoor (dBm/MHz) | Outdoor (dBm/MHz) |

|-----------------------|------------------|-------------------|

| Below 960             | FCC 15.209       | FCC 15.209        |

| 960 - 1610            | -75.3            | -75.3             |

| 1610 - 1990           | -53.3            | -63.3             |

| 1990 - 3100           | -51.3            | -61.3             |

| 3100 - 10600          | -41.3            | -41.3             |

| Above 10600           | -51.3            | -61.3             |

Figure 2.1: FCC spectral mask for UWB indoor and outdoor communication

UWB signal is defined as the signal with a fractional bandwidth  $(B_f)$  greater than 20%. In other word, UWB signal occupies a bandwidth larger than 20% the center frequency. The fractional bandwidth is the ratio of the -10 dB bandwidth  $(B = f_H - f_L)$  to the center frequency  $(f_c)$  as given by

$$B_f = \frac{B}{f_c} = 2\frac{f_H - f_L}{f_H + f_L}. (2.1)$$

where  $f_H$  and  $f_L$  are the higher and lower -10 dB bandwidths, respectively. UWB signal is also characterized as the signal with an absolute bandwidths of 500 MHz or more.

#### 2.1.2 Standards

The IEEE established two work groups to examine the use of UWB radio as a new physical layer for two different application areas. One is the IEEE 802.15.3a work group, which considers using UWB as physical layer for short-range, high-data rate applications. Another is the IEEE 802.15.4a work group, which investigates the use of UWB as physical layer for short-range, low-date rate applications.

The purpose of IEEE 802.15.3a work group is to provide the high-speed physical layer applications involving imaging and multimedia such as video, multimedia links, and cable replacement [9]. The minimum data rate required for short-range, high-data rate communications is 110 Mbps at 10 m and 200 Mbps at 20 m. In addition, a data rate greater than 480 Mbps is desirable; for example, extremely high data rate at 500 Mbps for wireless USB [11].

The focus of IEEE 802.15.4a is the low data rate communications for very low power and low complexity systems such applications as sensors, RFID tags, smart badges, remote controls, interactive toys, and home automation [9]. Another application area of low data rate communications required long battery life is low-rate wireless personal area network and wireless sensor network. The range of low data rate applications is 100 kbps to 27 Mbps [12].

# 2.2 Signal Characteristics

UWB has several characteristics making UWB systems attractive to many wireless communications. Based on a carrier-less baseband transmission, UWB systems offer low complexity, low power and low cost. The fundamental character-

istic that distinguishes impulse radio from conventional narrowband is the absence of carrier frequency. A narrow transmitted pulse in time domain is generated without the need for up-conversion. Similarly, down-conversion in the receiver is not required, resulting in eliminating the need for such a power hungry block as local oscillator (LO). As a consequence, circuit simplicity, low power consumption, and low cost can be achieved.

UWB radio has robustness against severe multipath propagation due to utilizing a very short time-domain pulse of transmitted signal. Since UWB signal has a fine delay resolution, multipath components can be combined with different individual weight factors to gain higher received signal energy as the technique called rake receiver [13]. Furthermore, a very fine time-domain resolution of UWB radio can potentially provide timing precision allowing for positioning and tracking applications such as in military and radar systems, as well as in security operations.

Because of a very low power radiation regulated by the FCC, UWB radio appears as noise-like signal spectrum, making it difficult to detect. Although occupying a very large bandwidth spectrum, low-power, noise-like UWB signal transmissions do not cause significant interference to other systems operating in the vicinity [14]. However, the overlap between UWB and existing services causes the limitation on UWB communications. This main constraint is the presence of strong, in-band interference that can saturate the UWB receiver easily [12]. For example, the frequency band of 802.11a is overlapped with UWB band.

Occupancy in enormous bandwidth makes UWB radio appealing for consumer communications since it can support the growing demand for wireless data capability [10]. It reveals that UWB systems can offer both high data rate and low data rate applications. Nevertheless, most UWB radio applications are restricted to short-range or medium-range communications owing to the low energy density.

# 2.3 UWB Applications

UWB radio has many attributes, making it attractive for a wide range of applications, particularly in short-range, indoor communications. Because of a constraint of low-power emission, UWB system is restricted to very short-range, high-data rate applications or very low-data rate, moderate-range applications. Moreover, the narrow pulse width in time domain offers UWB the capability of precise ranging and high accurate positioning [15]. There are several application areas of the use of wireless UWB; for example, wireless personal area networks, wireless sensor networks, wireless body area networks, and radar system.

# 2.3.1 Wireless Personal Area Networks (WPANs)

Also known as in-home networks, WPANs provide ad-hoc connectivity in short range within 10-20 m among low-power portable home electronic and communication devices such as televisions, DVD players, and audio systems. These devices are likely to provide high-quality real-time video and audio, file exchanging among storage system, and cable replacement for home entertainment system. UWB technology has emerged as a promising candidate for WPANs since it offers high-data rate over short range with low power consumption, low cost.

# 2.3.2 Wireless Sensor Networks (WSNs)

WSNs consist of several sensor nodes that collect data around their environment, and transmit such sensory data as smoke, heat, temperature, humidity, etc.

to a central node [16]. Typically, the sensors have to operate for many years without a change of battery; thus, energy is more limited in WSNs than in WPANs. Moreover, size of sensing devices is often small [7]. UWB transmission technique has become an attractive alternative for WSNs because it provides low power and low-data rate over medium range as well as its simplicity of implementation.

# 2.3.3 Wireless Body Area Networks (WBANs)

WBAN is defined as a system of devices, which are implanted, wearable, or proximate to a human body. It is mainly used in the surgical and intensive health care or telemedicine, where medical sensors are routinely attached to the patient. This enables the continuous monitoring of the patients' health status or physical signals such as electrocardiography (ECG), electroencephalography (EEG), blood pressure, blood sugar, respiratory rate, heart rate, etc. WBAN also allows patients to move their body during the operation. Another example of WBANs is capsule endoscopy, which is a camera with a shape and size of a pill used to visualize the gastrointestinal track [17]. The features of medical sensor devices used in WBANs are small sizes, low power, energy efficiency, unharmful to human tissues, and less interfering to other medical equipments. Also, medical WBANs are used in a various range of data rates from 1 kbps to 100 Mbps [18].

According to these requirements for WBANs, UWB radio offers the potential of low power and the simplicity of design and implementation, making UWB transceiver energy efficient and smaller. Furthermore, UWB signal is less likely to cause any harm to the human body and significant interferences to other operating systems because of low spectral density of -41.3 dBm/MHz. In practical, UWB is also used in a wide range of date rates depending on distances.

# 2.3.4 Radar/Imaging Systems

Radar is an object-detection system using radio waves to identify the position, distance, direction, altitude, or velocity of both stationary and moving objects such as aircraft, spacecraft, ships, etc. For example, target coordinators are evaluated by using an estimated time of arrival corresponding to the targets and wave propagation speed. Due to the fine resolution of very short pulses, UWB technology allows a high accuracy of ranging and positioning in radar systems. Recently, the technique of radar imaging has become attractive for moving target tracking and detection; for example, medical imaging such as breast cancer/tumor [19][20], people imaging and baggage scanning [21][22] in security operation to detect threat objects such as weapons and explosive, and through-wall imaging [23]. These applications require low-cost, compact, lightweight, real-time imaging with adequate resolution, and the ability to penetrate complex materials. In addition to very precise ranging, UWB radio offers low power, the simplicity of implementation, low cost, robustness against multipath propagation, and good performance in highly cluttered environments. However, due to low power spectral density, UWB through-wall application has a drawback from loss and dispersion in materials such as brick wall and blocks; while, the previous work [24] has studies that building materials like wood, drywall, and styrofoam have small loss and dispersion effects.

#### 2.4 Pulse-based Transmission

In UWB radio systems, two possible techniques of generating the transmitted pulse-based signal are carrier-less pulse generator and carrier-based pulse generator [25]. The carrier-less pulse or baseband pulse technique is based on discontinuous transmission of very short duration pulses in order of subnanosecond. The need of frequency translation for shifting the signal to a higher frequency is not required since pulses fall directly in the UWB band. Another technique is the carrier-based pulse technique using a local oscillator to up-convert a pulse at baseband to a carrier frequency in the UWB band.

One advantage of carrier-less pulse techniques over conventional mixingbased techniques is that the high carrier frequency is inherently generated in the UWB pulse duty cycle. In addition, energy transmission is only generated during a certain period because of discrete pulse emissions. On the other hand, a drawback of this technique is that the receiver requires its own local oscillator for down-converting, which can not share with transmitter parts.

The advantage of the carrier-base pulse technique is that it offers a wide variety of controls over the frequency spectrum. Moreover, the center frequency of the pulse is well-defined by a local oscillator frequency. However, the expense of high power consumption can not be avoided since a power hungry block as a local oscillator needs to operate at the pulse carrier frequency.

#### 2.4.1 Pulse Generator

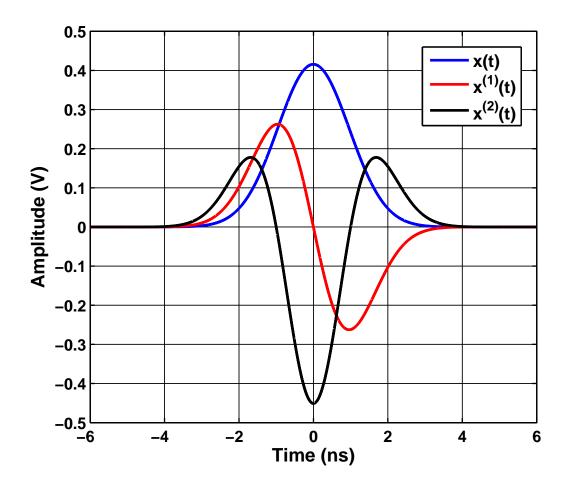

Due to low transmit output power of -41.3 dBm/MHz over the 3.1 - 10.6 GHz band, the UWB pulse waveform is required to satisfy the spectral mask regulation. There are several pulse shapes for UWB communications. The optimal choice of UWB pulse shape depends on the pulse duration, frequency spectrum, and the application. The most common pulse shape found in the literature is Gaussian pulse because its shape is easily generated [26], and it is less sensitive to inter-

Figure 2.2: A Gaussian pulse and higher-order derivative of the Gaussian pulse

symbol interference [12]. The expression of a general Gaussian pulse is given by

$$x(t) = \frac{A}{\sqrt{2\pi}\sigma} e^{\left(-\frac{t^2}{2\sigma^2}\right)} \tag{2.2}$$

The basic UWB pulse-based is easily generated by the first derivative of Gaussian pulse referred to monocycle; however, the power spectral density of the first derivative Gaussian pulse does not meet the FCC mask regulatory requirement. One solution is to modulate the monocycle pulse with the carrier to shift the center frequency and vary the value of  $\sigma$  to adjust the bandwidth. Although the transmit

power requirement in the band is met, modulation will increase complexity and power consumption.

An alternative approach is the higher-order derivatives of the Gaussian pulse [27]. In the time domain, the higher-order derivatives of the Gaussian pulse appear as sinusoidal waveforms modulated by a Gaussian pulse-shaped envelope [28]. It is clear that increasing the order of the derivatives results in the increment of the number of zero-crossing in time, corresponding to a higher carrier frequency sinusoids modulated by an equivalent Gaussian envelope as shown in Fig. 2.2. By selecting the optimal order of the derivative and a pulse width, the transmit power requirement and the maximum bandwidth can be obtained. It shows that at least the  $5^{th}$  derivative should be used for indoor systems while at least the  $7^{th}$  derivative should be used for outdoor systems [27]. Pulse shapes or the derivative operation can be implemented by the highpass filtering.

# 2.4.2 Modulation Schemes

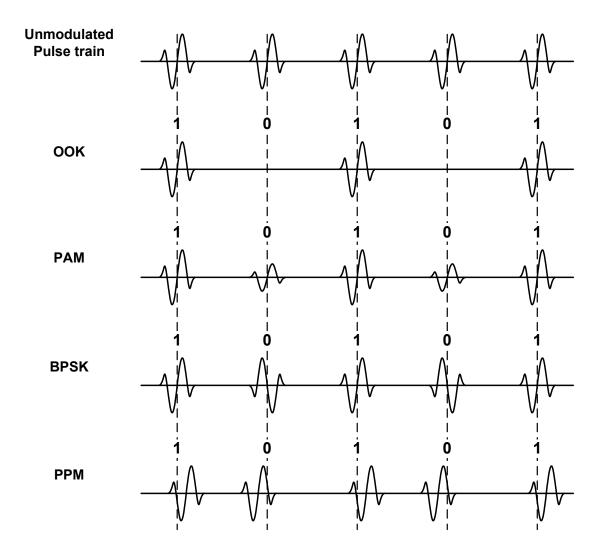

There are several well-known modulation techniques. For example, on-off keying (OOK) is a modulation scheme where the presence and absence of a pulse represents the digital data of '1' and '0', respectively. For pulse amplitude modulation (PAM), a pulse with large amplitude represents digital data of '1', and a pulse with small amplitude represents digital data of '0'. Binary phase-shift keying (BPSK) is the modulation technique where a pulse without phase shift represents digital information of '1' while a pulse with 180° phase shift represents digital information of '0'. Pulse position modulation (PPM) uses the delay of the pulse relative to time reference to signify the digital data. For instance, a pulse representing digital data '1' is delayed in time while a pulse representing digital

Figure 2.3: Four different modulation schemes

data '0' is advanced in time. Four different modulation schemes of UWB pulses for data sequence of  $\{1,0,1,0,1\}$  are shown in Fig. 2.3.

The extremely wide bandwidth is the fundamental difference between UWB systems and conventional narrowband systems. UWB systems operate in the power limited condition whereas narrowband systems operate in the bandwidth limited condition. The restriction on transmit output power in UWB systems impacts significantly on design choices of modulation. It is necessary that the modulation

scheme needs to be power efficient by having the best bit-error-rate for a given energy per bit. Another concern is that modulation schemes have a different frequency spectrum response. Thus, modulation techniques such as OOK, PAM, BPSK, and PPM affect on power efficiency and frequency spectra differently.

A general waveform of UWB signal is represented as a sequence of pulse shifted uniformly in time (t = kT) called a pulse train given by

$$s(t) = \sum_{k=-\infty}^{\infty} a_k p(t - kT)$$

(2.3)

where s(t) is the UWB signal, p(t) is the basis pulse shape, T is the pulse-spacing interval, and  $a_k$  is the amplitude of the  $k^{th}$  pulse shape. When this pulse train is transmitted with constant time interval called the pulse repetition rate, the pulse spectrum will contain peaks of power at certain frequencies. These frequencies are the inverse of pulse repetition rates. Considering the response in frequency domain, the power spectral density (PSD) of the pulse train is given [29] by

$$S(f) = \frac{\sigma_a^2}{T} |P(f)|^2 + \frac{\mu_a^2}{T^2} \sum_{k=-\infty}^{\infty} \left| P\left(\frac{k}{T}\right) \right|^2 \delta\left(f - \frac{k}{T}\right)$$

(2.4)

where S(f) is the PSD of the pulse train, P(f) is the Fourier transform of the pulse shape: p(t),  $\delta(f)$  is a unit impulse, and  $\sigma_a^2$  and  $\mu_a$  are the variance and mean of the weight sequence of p(t). As expressed in equation 2.4, the first term of the PSD is a continuous part, and the second term is a discrete part. This discrete portion causes the peak power lines in frequency spectrum called comb lines [26] or discrete spectral lines [29]. The presence of spectral lines leads to the limitation on the total transmit power in entire UWB band.

Depending on modulation schemes, the value of  $a_k$ ,  $\sigma_a^2$  and  $\mu_a$  results in different occurrence of spectral lines [29]. The frequency spectrum of UWB pulse

signal modulated by OOK, PAM, and PPM is contained spectral lines whereas the spectral lines are disappeared for BPSK modulation scheme in a condition of zero mean and random date sequence. One method to reduce the effect of spectral lines is called dither by adding a small random offset to each pulse; however, the spectral properties of each modulation scheme are a crucial consideration for UWB design to achieve maximum power efficiency.

In addition to a power efficient modulation with a smooth PSD, the efficiency of modulation techniques can be determined by the best error performance for a given energy of bit. By considering the constellation diagram of each modulation schemes [29], BPSK has a greatest distance for the same energy per bit. Thus, BPSK offers a inherent 3 dB advantage in efficiency over OOK, PAM, and PPM. In other word, for a given energy per bit, BPSK has a 3 dB improvement in BER.

#### 2.5 Channel Characteristics

Another significant challenge for UWB communication is the propagation in UWB channels. Although there is the existing conventional channel, UWB channels behave in a fundamentally different way from conventional channels. This is because UWB radio occupies the large bandwidth. Understanding the UWB propagation channel helps predicting the behavior of wireless channels in particular environments so that the desired high-bandwidth performance can be achieved. In this section, the fundamental characteristics of UWB channel including path loss and multipath propagation are discussed.

#### 2.5.1 Path Loss

The path loss is the attenuation or reduction in signal energy of an radio wave as it propagates from transmitter through the channel. Energy of the wave will decrease as a distance between transmitter and receiver increases. It is also defined as the ratio of the received signal power relative to the transmitted power. Several parameters such as free-space loss, reflection, diffraction, refraction, or absorption affect path loss. Also, path loss is influenced by channel media and environments. Let's consider the path loss in free space, which excludes the effects of reflection, diffraction, multipath, obstructing, absorbing, and transmitting/receiving antenna gains. The expression of free-space path loss is given by equation 2.5, which is a function of the distance (d) and the wavelength  $(\lambda)$  of the radiated signal.

$$PL_{FS}(\lambda, d) = \left(\frac{\lambda}{4\pi d}\right)^2$$

(2.5)

A general path loss model in presence of reflection, diffraction, multipath for both line-of-sight (LOS) and non-line-of-sight (NLOS) paths [30] is given by

$$PL(d) = PL(d_0) - 10 \cdot n \cdot \log_{10} (d/d_0)$$

(2.6)

where n is the path loss exponent (n = 2 for free-space) and  $d_0$  is a reference distance. Path loss expressed in equation 2.6 is in decibels (dB).

The distance dependence of path loss for UWB radio is expressed by equation 2.6, which n is extracted by experimental data. Another significant dependent parameter of path loss is the frequency dependence. In conventional narrowband system, the frequency dependence of the propagation parameters is negligible. However, since the bandwidth of UWB radio spread over a wide frequency range, propagation parameters in UWB system feasibly depends on frequencies. The

frequency dependence of path loss [9] is given by

$$\sqrt{PL(f)} \propto f^{-m} \tag{2.7}$$

where m is frequency decaying factor varying between 0.8 and 1.4 [9]. Therefore, the path loss for UWB propagation channel associated with distance and frequency can be expressed by the product of two independent functions of distance and frequency as given by

$$PL(f,d) = PL_f(f) \cdot PL_d(d) \tag{2.8}$$

# 2.5.2 Multipath Propagation

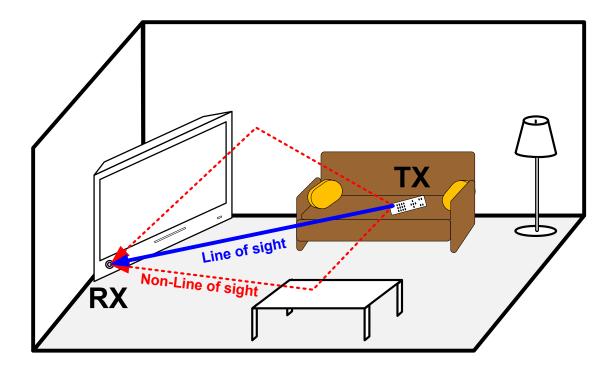

A basis of channel characteristics in wireless propagation is multipath propagation. The signal from the transmitter travels in different paths to the receiver. This transmitted signal may possibly interact with objects in the surroundings differently before arriving at the receiver. For example, the transmitted signal may reflect, diffract, or scatter with obstructing objects such as furniture, walls, doors, ceilings, and windows inside an indoor environment as shown in Fig. 2.4. Thus, each of signal components propagates in multiple paths and interacts with different objects before arriving at the receiver. Depending on the paths, multipath components have certain attenuation, delay, and direction of arrival. The conventional propagation assumed that interaction with objects in the surroundings causes only a change in attenuation and direction of the multipath components. Hence, the received signal is the sum of scaled and delayed replicas of the transmitted signal [8]. The impulse response of the conventional channel is given by

$$h(\tau) = \sum_{i=1}^{N} \alpha_i \delta(\tau - \tau_i)$$

(2.9)

Figure 2.4: An example of multipath propagation in indoor environment

where  $\alpha_i$  and  $\tau_i$  are the attenuation factor and delay of the  $i^{th}$  multipath components, respectively. N is the number of resolvable multipath components, and  $\delta(t)$  is the Dirac delta function.

However, all interactions between multipath components and objects for UWB channels are frequency dependence; thus, the conventional impulse response in equation 2.9 is not well described for UWB system. The impulse response is now a distorted version:  $\chi(\tau)$  of Dirac delta function, which the distortion relies on interactions of signals to object from the transmitter to receiver. The impulse response of the UWB channel is given by

$$h(\tau) = \sum_{i=1}^{N} \alpha_i \chi(\tau) \otimes \delta(\tau - \tau_i)$$

(2.10)

Furthermore, it is possible that multipath components sometimes add up in a constructive way, and sometimes in a destructive way depending on the arriving delay or phase of each multipath component. As mentioned earlier, UWB radio has an immunity to multipath propagation because of a very fine timing of arrivals, resulting in resolvable multipath components. If the pulse is too narrow or has a very large bandwith greater 500 MHz (large absolute bandwidth), each multipath component can be distinguished from each other by times of arrivals, which is important to determine the design of rake receiver. On the other hand, if the pulse is mild narrow or has a bandwidth equal to 20% or greater than the center frequency (large relative bandwidth), multipath components is feasibly combined with previous or post multipath components, causing distortion to the signal transmission.

#### CHAPTER 3. MEASUREMENT SETUP

This chapter describes the measurement setup of short-range wireless interconnects for active computing system like a computer chassis. An impulse-radio

ultra-wideband (IR-UWB) transceiver is experimentally implemented with off-theshelf antennas located at several positions on both the top and bottom of the motherboard. Channel environments and channel characteristics such as line-of-sight

(LOS), non-line-of-sight (NLOS), path loss, multipath propagation, and electromagnetic interference (EMI) are discussed. The setups of each pair of transmitting

and receiving antennas on the top and bottom of the motherboard are illustrated.

The IR-UWB transceiver used in the wireless measurement is presented.

# 3.1 Experimental Setup

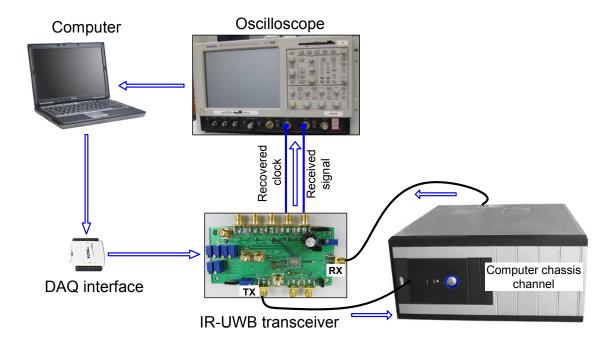

The measurement setup for UWB wireless channel consists of the IR-UWB transceiver, National Instruments Data Acquisition Device (NI-DAQ), off-the-shelf omni-directional Media+ $^{TM}$  UWB antennas, and the metallic enclosed computer chassis. Fig. 3.1 illustrates an overview of the measurement setup. The IR-UWB transceiver is controlled by LabVIEW software through the NI-DAQ interface. An oscilloscope is used to obtain a received signal and recovered ADC clock from the transceiver. The measured data is then processed in MATLAB. The post-signal processing in MATLAB is discussed more detail in the chapter 5. In the measurement, off-the-shelf omni-directional antennas are placed stationary as transmitters (TX) and receivers (RX) inside the computer case.

Figure 3.1: Overview of the measurement setup

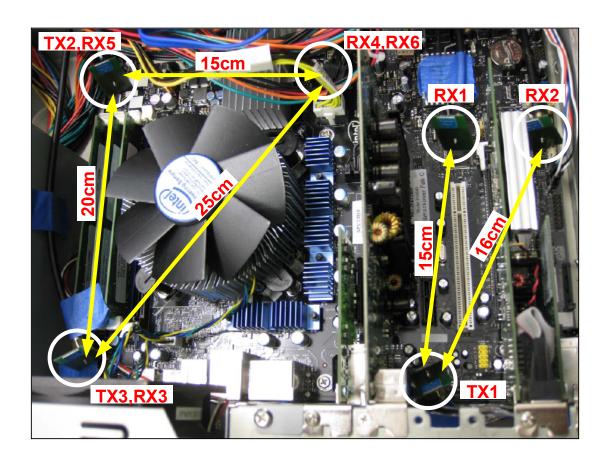

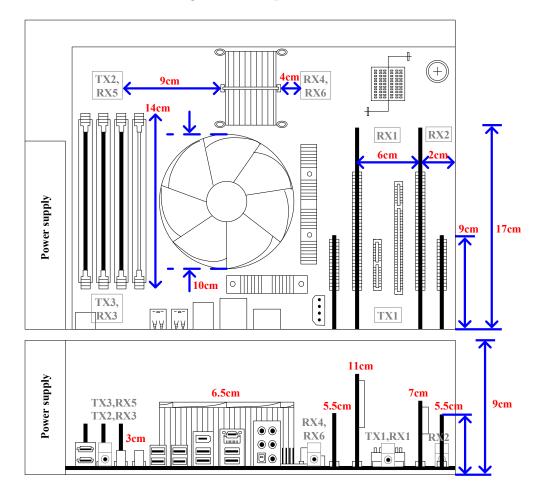

Two separate experiments are performed to observe the effect of channel characteristics on signal transmission. These experiments are performed by placing transmitting and receiving antennas on both the top and bottom of the motherboard. First, six antennas are located at several positions close to integrated circuits (ICs) on the top as its top view shown in Fig. 3.2. For example, TX1 and RX1 are in a LOS of each other located in between two PCI cards within a distance of 15 cm. Other antennas such as TX1/RX2, TX2/RX3, TX2/RX4, TX3/RX5, and TX3/RX6 are in a NLOS by having obstructing components in between. Second, the six antennas are placed underneath the motherboard at positions similar to their placement on the top-side, as its side view shown in Fig. 3.2. All of transmitters and receivers at the bottom including TX1'/RX1', TX1'/RX2', TX2'/RX3', TX2'/RX4', TX3'/RX5', and TX3'/RX6' are in a LOS of each other without having any components in between.

Figure 3.2: Different locations of transmitting and receiving antennas on the top and bottom of the motherboard inside the computer

#### 3.2 Channel Environments

A unique wireless environment of an enclosed PC case is metals surrounding and extremely short communication distance. It consists of aluminum enclosure with a size of  $45 \times 20 \times 45 \,\mathrm{cm^3}$  and electronic components inside such as CPU processor fan, heatsink, wires, PCI express card, and RAM cards. These materials and their stationary positions affect the signal transmission mainly due to the channel characteristics; for example, LOS and NLOS communication, signal attenuation, multipath reflection, and interference generated in the channel [31]. It is obvious that the NLOS communication is a common existence in this particular computing channel in addition to the LOS communication, due to many components located inside the computer obstructing the signal transmission. Depending on the distance and the frequency of transmission, the signal is attenuated along the channel. However, due to the ultra-short range channel, signal loss is not increased significantly by the incremental distance. The results of channel attenuation at each receiver are presented in the chapter 5.

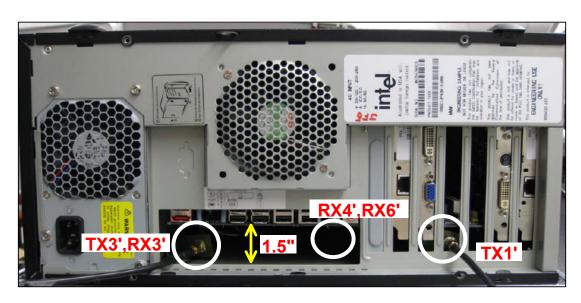

Surrounded by metallic materials causing the reflection in multiple paths, the transmitting signal tends to result in different amplitudes, phases, and times of arrived signals, thus causing an inter-symbol interference (ISI) at the receiver. Especially, within short-range communication, the transmitted signal is likely to experience a dense multipath propagation. Let's consider the channel environment at the bottom of the motherboard. Even though there are no objects underneath to cause non-line-of-sight (NLOS) communication, the signal is most likely to experience the impact of severe multipath propagation due to the limited space of 1.5 inches height from metal case to the motherboard.

Furthermore, electromagnetic interference (EMI) generated by the switching

noise of several ICs on the motherboard during the system operation [31] can limit the maximum data rate and increase the bit-error-rate (BER). All of these potential noise sources will be considered in this experimental setup. To predict these possible switching noise sources, the specifications and major features of the board [32] are summarized as shown in Table 3.1. The motherboard used in the measurement setup is Intel Desktop Board DX58SO.

Table 3.1: Feature summary of the DX58SO motherboard

| Processor    | • Intel Core i7 Processor in an LGA1366 socket             |  |  |

|--------------|------------------------------------------------------------|--|--|

| Memory       | • Four 240-pin DDR3 SDRAM Dual Inline Memory Module        |  |  |

|              | • Support for DDR3 1333MHz/1066MHz/800MHz DIMMs            |  |  |

| Peripheral   | • Two External Serial ATA (eSATA) ports on back panel with |  |  |

| Interfaces   | RAID support                                               |  |  |

|              | • Two IEEE 1394a ports                                     |  |  |

|              | • Maximum transfer rate of 3 Gbit/sec                      |  |  |

|              | • Twelve USB 2.0 ports                                     |  |  |

|              | • Six internal Serial ATA interfaces with RAID support     |  |  |

| LAN Support  | • Gigabit (10/100/1000 Mbits/sec) LAN subsystem using the  |  |  |

|              | Intel 82567LM Gigabit Ethernet Controller continued        |  |  |

| Expansion    | • One PCI Conventional bus add-in card connector (SMBus    |  |  |

| Capabilities | routed to PCI Conventional bus add-in card connector)      |  |  |

|              | • Two PCI Express 2.0 x16 bus add-in card connectors       |  |  |

|              | • One PCI Express 2.0 x4 bus add-in card connector         |  |  |

|              | • Two PCI Express 1.1 x1 bus add-in card connectors        |  |  |

### 3.3 Channel on Top of Motherboard

Channel on the top of the motherboard is illustrated in Fig. 3.3 showing positions of transmitters and receivers along with their distances to obstructing objects around. It also shows the dimension of components, which block the transmission signal such as RAM, CPU processor fan, and PCI express cards. For example, RX2 is located in between the 7 cm-high, 17 cm-long PCI card and metal case with a very short space of 2 cm. In this section, each position of transmitters and receivers is described showing both its top view and side view.

Figure 3.3: Top view and side view on top of the motherboard

### 3.3.1 TX1 and RX1

TX1 and RX1 are located 15 cm apart in a line-of-sight (LOS) of each other between the two PCI cards as shown in Fig. 3.4. Due to the shortest distance and LOS communication, the received signal at RX1 is less attenuated. However, transmitting signals from TX1 are reflected mostly in 6 cm between these two PCI cards as well as in between components such as electrolytic capacitors or card slots on the motherboard and metallic case before arriving at RX1, causing multipath propagation. During powering on the motherboard, signal transmission between TX1 and RX1 is potentially interfered by the operating frequency of the two PCI cards, which have their clock speed of 2.5 GHz and their maximum transfer rate of 2 GHz. Therefore, the main sources of interferences between TX1 and RX1 are from these two PCI express cards.

Figure 3.4: Top view and side view of TX1 and RX1 on top of motherboard

### 3.3.2 TX1 and RX2

TX1 and RX2 are located 16 cm apart in a non-line-of-sight (NLOS) of each other obstructed by the PCI express card in between as shown in Fig. 3.5. In spite of a short distance, the received signal at RX2 is likely to attenuate more than that at RX1 because of the NLOS communication. Located in between the metallic case and the PCI express card with a very short distance of 2 cm, RX2 is affected severely by multipath signals. It is possible that a second coming signal arrives closer to a main signal because of a short reflecting time from the PCI express card and the case. Similarly to RX1, the received signal at RX2 is interfered by the operating frequency of the PCI express card when the motherboard is running.

Figure 3.5: Top view and side view of TX1 and RX2 on top of motherboard

#### 3.3.3 TX2 and RX3

TX2 and RX3 are located 20 cm apart in a non-line-of-sight (NLOS) of each other blocked by RAM cards in between as shown in Fig. 3.6. Due to the farther distance and NLOS communication, signal attenuation between TX2 and RX3 is expectantly increased. Multipath distortion at RX3 is mainly caused by reflecting signals in RAM cards, CPU processor fan, and metal case. During the operation of the motherboard, signal between TX2 and RX3 is interfered by the speed of processor and memories. For the DX58SO motherboard model, the clock speed of i7 processor is 3.2 GHz, which occurs in the operating frequency range of transceiver. The speed of memories is 1333 MHz, 1066 MHz, and 800 MHz.

Figure 3.6: Top view and side view of TX2 and RX3 on top of motherboard

#### 3.3.4 TX2 and RX4

TX2 and RX4 are located 15 cm apart in a non-line-of-sight (NLOS) of each other by having a heatsink and wires in between as shown in Fig. 3.7. Although TX2 and RX4 are separated by a short distance, the received signal at RX4 is still affected by the NLOS attenuation. For example, having heatsink 9 cm apart from TX2 causes signal attenuation at RX4. Furthermore, different amplitudes, phases, and times of arrivals at RX4 caused by the reflection in CPU processor fan, heatsink, hard drives, wires, PCI express cards, and metallic cover result in the multipath propagation. Because of located near to chip processor, the signal at RX4 is interfered by the 3.2 GHz operating frequency of i7 processor during powering on the motherboard. Other sources of interferences come from speed of PCI express cards and hard drives, which are close to RX4. PCI express cards operate at clock rate of 2.5 GHz and maximum data rate of 2 GHz.

Figure 3.7: Top view and side view of TX2 and RX4 on top of motherboard

#### 3.3.5 TX3 and RX5

TX3 and RX5 are located 20 cm apart in a non-line-of-sight (NLOS) of each other obstructed by RAM cards as shown in Fig. 3.8. The position of TX3 and RX5 is the same as the position of TX2 and RX3 by swapping between the transmitter and receiver, so signal loss at RX5 is similar to that at RX3. However, multipath distortion at RX5 and RX3 may occur differently because of different position of the receiver and obstructing components around. Caused by the reflection in RAM cards, CPU processor fan, metal case, wires, and hard drives, multiple paths of transmitted signals result in inter-symbol interference (ISI) at the receiver. When the motherboard is operating, the main sources of interferences at RX5 are from the speed of Intel core i7 processor, running at 3.2 GHz. Another interference comes from memories, operating at 1333 MHz, 1066 MHz, 800 MHz.

Figure 3.8: Top view and side view of TX3 and RX5 on top of motherboard

#### 3.3.6 TX3 and RX6

TX3 and RX6 are located within the longest distance of 25 cm in a non-line-of-sight (NLOS) of each other blocked by a huge CPU processor fan in between as shown in Fig. 3.9. Obviously, due to the longest distance and NLOS communication, the received signal at RX6 is most attenuated among other receivers. The transmitted signal is reflected in CPU processor fan, hard drives, metallic lid, and PCI express cards, causing multipath propagation at the receiver. Located near to processor and PCI express cards, signal transmission is interfered mainly by the operating frequency of processor and these PCI express cards during powering on the motherboard. Intel core i7 processor runs at 3.2 GHz while PCI express cards operate at 2.5 GHz clock frequency and 2 GHz maximum transfer rate.

Figure 3.9: Top view and side view of TX3 and RX6 on top of motherboard

#### 3.4 Channel at Bottom of Motherboard

Channel at the bottom of the motherboard is illustrated in Fig. 3.10 showing six pairs of transmitters and receivers underneath the motherboard with a height of 1.5 inches. Due to an empty space under, all TXs and RXs are located in line-of-sight (LOS) of each other with different distances. Unlikely to channel on the top of the motherboard, multipath propagation at the bottom of the motherboard is mainly caused by the reflection in limited empty areas between the upper motherboard and metallic enclosure. Although the communication happens underneath, signal transmission is still interfered by the operating frequency of electronic components on the top of the motherboard such as PCI express cards, RAM cards, and processor. Depending on the position of transmitters/receivers under these active components, the received signal is interfered differently. Each location of transmitters and receivers under the motherboard is described showing its top view and side view.

Figure 3.10: Side view underneath of the motherboard

# $3.4.1 \quad TX1' \text{ and } RX1'$

TX1' and RX1' are located 15 cm apart in a line-of-sight (LOS) of each other as shown in Fig. 3.11. Multipath signals at RX1' mostly cause by the reflection in between the metal case and upper motherboard. By having two PCI express cards on the top, both transmitted and received signal during powering on the motherboard are interfered by the operating frequency of PCI express cards, running at 2.5 GHz clock speed and 2 GHz maximum transfer rate.

Figure 3.11: Top view and side view of TX1' and RX1' under the motherboard

# $3.4.2 \quad TX1' \text{ and } RX2'$

TX1' and RX2' are located 16 cm apart in a line-of-sight (LOS) of each other as shown in Fig. 3.12. Located too close to a metallic case, arriving signals at RX2' are reflected densely in the side of metallic case and upper motherboard. Similarly to RX1', during the operation of the motherboard, the operating frequency of PCI express cards on the top distributes interferences to RX2' at 2.5 GHz clock frequency and 2 GHz highest data rate.

Figure 3.12: Top view and side view of  $TX1^{'}$  and  $RX2^{'}$  under the motherboard

# $3.4.3 \quad TX2' \text{ and } RX3'$

TX2′ and RX3′ are located 20 cm apart in a line-of-sight (LOS) of each other as shown in Fig. 3.13. During powering on the motherboard, the operating frequency of active components on the top such as RAM cards and processor will interfere the received signal at RX3′. For example, RX3′ is interfered by the speed of memories at 1333 MHz, 1066 MHz, and 800 MHz. Speed of i7 processor running at 3.2 GHz also interferes the received signal. Another source of interferences is from the switching frequency of power supply located next to RX3′ on the left side.

Figure 3.13: Top view and side view of TX2' and RX3' under the motherboard

# 3.4.4 TX2' and RX4'

TX2' and RX4' are located 15 cm apart in a line-of-sight (LOS) of each other as shown in Fig. 3.14. During powering on the motherboard, the received signal at RX4' is mainly interfered by the operating frequency of processor, running at 3.2 GHz. Speed of hard drives also interferes both transmitted and received signal. Another interference is from the operating frequency of PCI express cards, running at 2.5 GHz clock speed and 2 GHz maximum transfer rate.

Figure 3.14: Top view and side view of TX2' and RX4' under the motherboard

# $3.4.5 \quad TX3' \text{ and } RX5'$

TX3′ and RX5′ are located 20 cm apart in a line-of-sight (LOS) of each other as shown in Fig. 3.15. The position of TX3′ and RX5′ is the same as the location of TX2′ and RX3′ by switching between the transmitter and receiver. In addition to the reflection inside metallic enclosure under the motherboard, the received signal at RX5′ is impacted by the reflection in wires around it. During the operation of the motherboard, signal transmission is interfered by speed of processor at 3.2 GHz as well as memories at 1333 MHz, 1066 MHz, and 800 MHz.

Figure 3.15: Top view and side view of TX3' and RX5' under the motherboard

# 3.4.6 TX3' and RX6'

TX3′ and RX6′ are located within the longest distance of 25 cm apart in a line-of-sight (LOS) of each other as shown in Fig. 3.16. During powering on the motherboard, the received signal at RX6′ is interfered by the operating frequency of i7 processor and PCI express cards on the top. Intel core i7 processor runs at 3.2 GHz while PCI express cards run at 2.5 GHz clock frequency and 2 GHz maximum transfer rate.

Figure 3.16: Top view and side view of TX3' and RX6' under the motherboard

#### 3.5 IR-UWB Transceiver

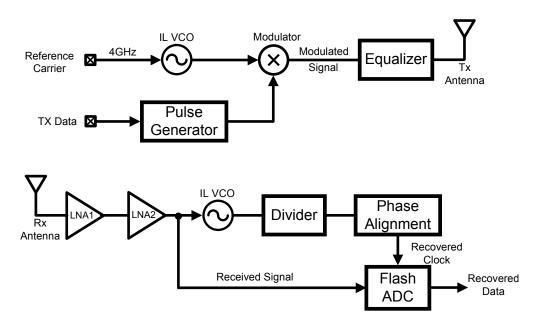

This work utilized an IR-UWB transceiver [33][34] to transmit and receive an UWB pulse signal over the frequency range of 3.1-5 GHz at a data rate of 125 Mbps. The block diagram of the IR-UWB transceiver is shown in Fig. 3.17.

Figure 3.17: IR-UWB transceiver block diagram

The transmitter includes an injection locking VCO, pulse generator, mixer, and equalizer. The receiver consists of a 2-stage low noise amplifier (LNA), injection locking VCO, divider, phase alignment block, and flash ADC. Due to the dense multipath for the short distance inside the computer case, the technique of preemphasis equalization is implemented at the transmitter to mitigate inter-symbol interference (ISI). The equalizer incorporates 2-tap pre-distortion where each tap, delay, and sign is adjustable [33]. In the receiver, the technique of pulse injection-locking for phase synchronization with the transmitted data is implemented to recover data and clock [34]. This technique in the receiver also minimize the

power consumption because the need for conventional clock and data recovery is not required.

#### CHAPTER 4. MEASUREMENT RESULTS

In this chapter, measurement results at six different positions of transmitters and receivers on the top and bottom of the motherboard inside the computer chassis are discussed. Signal attenuation across these six pairs of transmitters and receivers is presented. Time-domain received waveforms are observed to characterize the effect of multipath propagation by using post-processing in matlab, which gives the pulse response. Moreover, the technique of pre-distorted equalization (EQ) is performed to reduce the inter-symbol interference (ISI) caused by an existence of multipath reflections. In the measurement setup, all antennas are stationary, resulting in a fixed amplitude and time-delay of multipath components arriving at each receiver. Hence, 2-tap coefficient, delay, and sign of the equalizer are calibrated differently to alleviate multipath signals.

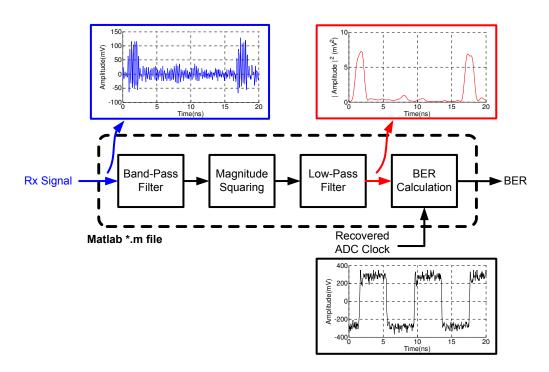

### 4.1 Post-Processing

The primary performance of wireless links is evaluated using BER. The BER was calculated in MATLAB by taking the received signal after second-stage LNA and recovered ADC clock after the phase alignment from the oscilloscope. Block diagram of the post-processing in MATLAB for BER calculation is shown in Fig. 4.1. The post-processing includes bandpass filter with cutoff frequencies of 3 GHz and 5 GHz, magnitude squaring, and lowpass filter of 1 GHz bandwidth. Only 3,000 bits of data were taken because of the limitation on the oscilloscope. The received signal was processed to obtain the baseband signal. In the post-processing, low-

Figure 4.1: Block diagram of MATLAB post-processing for BER calculation

pass filtering the amplitude square of received signals provides a pulse signal at the same frequency as a transmitted signal. Consequently, the BER was computed by the pulse signal and the recovered ADC clock. In addition to BER, the recovered ADC clock jitter was measured after the equalization was applied during the fully operating motherboard along with electromagnetic interference (EMI).

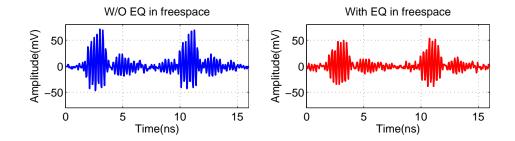

## 4.2 Freespace

In freespace, the transmitter and receiver are located through the line-of-sight distance of 10 cm. A path loss of 10 cm freespace wireless is -23.74 dB. Without applying an equalizer, the amplitude of a received signal after LNA is  $120 \,\mathrm{mV}_{pk-pk}$  with the first multipath component of  $40 \,\mathrm{mV}_{pk-pk}$ . Time-domain waveform of

Figure 4.2: Time-domain received waveform in freespace

Figure 4.3: Received pulse response in freespace

Figure 4.4: Multiple bits of received pulse response in freespace

the received signal in freespace is shown in Fig. 4.2. When the equalization was performed, the amplitude of multipath components was decreased as shown in Fig. 4.3. The results reveal that the equalizer improved the reduction of post-cursor ISI by 2.1 dB. Fig. 4.4 shows multiple bits of the received pulse plotted

Figure 4.5: Recovered ADC clock jitter in freespace

repetitively during 1-bit period (8 ns). Moreover, the recovered ADC clock jitter was slightly reduced from 8.6 ps to 6.3 ps when applying the equalization as shown in Fig. 4.5. The BER for the wireless in 10 cm freespace is less than  $3.3 \times 10^{-4}$  when applying EQ, while it is  $3.3 \times 10^{-4}$  without applying EQ.

## 4.3 Top of Motherboard inside Chassis

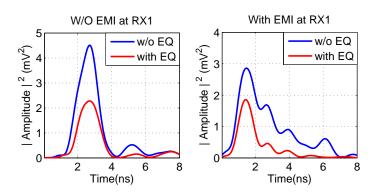

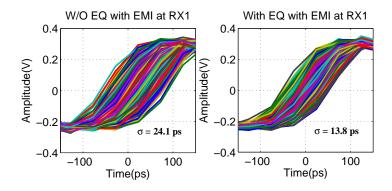

#### 4.3.1 TX1 and RX1

TX1 and RX1 are in a line-of-sight (LOS) of each other within a distance of 15 cm located in between two PCI cards. Transmitted signal was attenuated by -23.05 dB at the receiver. The amplitude of a main signal is  $130 \,\mathrm{mV}_{pk-pk}$  with  $45 \,\mathrm{mV}_{pk-pk}$  of the first multipath signal. Unlike in freespace, the amplitude of multipath distortion is larger inside the computer chassis. Moreover, in case of an active computing channel scenario, signal from multiple paths arrives close to the main signal as well as some of next arrivals are added up to the main signal, resulting in signal distortion shown in Fig. 4.6. However, Fig. 4.7 shows that

Figure 4.6: Time-domain received waveform at RX1

Figure 4.7: Received pulse response at RX1

adjustable tap coefficients of the pre-distort equalization lowered the post-cursor ISI by  $5.6\,\mathrm{dB}$  and increased the ratio of main cursor to post-cursor ISI by  $3.7\,\mathrm{dB}$  when the motherboard is operating. Without the active motherboard, the post-cursor ISI was reduced by  $5.3\,\mathrm{dB}$ , and main cursor to post-cursor ISI ratio was improved by  $2\,\mathrm{dB}$ . In addition, after the equalization was performed, recovered ADC clock jitter was enhanced by  $42.7\,\%$  during the operating motherboard as shown in Fig. 4.8. In the presence of EMI in the channel, the BER was decreased from  $2\times10^{-3}$  to  $3.3\times10^{-4}$  after the equalization showing  $5\mathrm{X}$  improvement.

Figure 4.8: Recovered ADC clock jitter at RX1

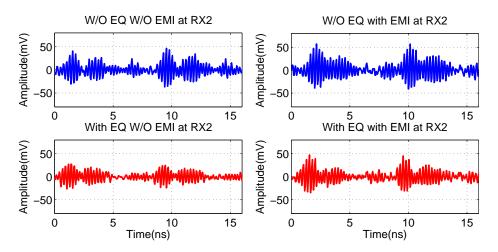

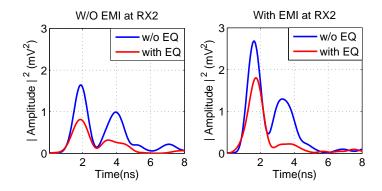

## 4.3.2 TX1 and RX2

TX1 and RX2 are in non-line-of-sight (NLOS) by having PCI card separating each other, resulting in signal attenuation and dense multipath reflections at the receiver. The signal loss between TX1 and RX2 is -26.24 dB through the channel distance of 16 cm. As shown in Fig. 4.9, main signal is attenuated to  $85 \,\mathrm{mV}_{pk-pk}$  while the impact of the multipath signals is stronger than that at RX1 showing the second arrived pulse as  $55 \,\mathrm{mV}_{pk-pk}$ . Fig. 4.10 presents the pulse response at

Figure 4.9: Time-domain received waveform at RX2

Figure 4.10: Received pulse response at RX2

Figure 4.11: Recovered ADC clock jitter at RX2

RX2 showing the reduction of post-cursor ISI when applying EQ. The ratio of main cursor to post-cursor ISI is increased by 6 dB, and the post-cursor ISI is decreased by 7.7 dB when the computer is running. On the other hand, the ratio of main cursor to post-cursor ISI is merely improved by 1.8 dB, and the post-cursor ISI is reduced by 4.9 dB when the computer is not running. As shown in Fig. 4.11, recovered ADC clock jitter is slightly changed when applying EQ. Due to the NLOS position of TX1 and RX2 causing worse multipath propagation and no improvement in clock jitter, the BER is slightly enhanced from  $2.7 \times 10^{-3}$  to  $3 \times 10^{-3}$ . However, without activities running on the motherboard, the BER shows 2.5X improvement from  $1.7 \times 10^{-3}$  to  $6.7 \times 10^{-4}$  after the equalization.

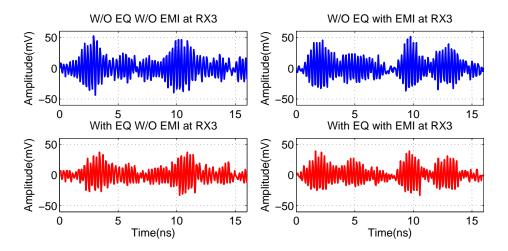

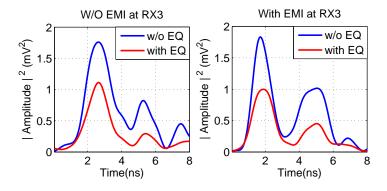

#### 4.3.3 TX2 and RX3

TX2 and RX3 are also in non-line-of-sight (NLOS) communication with the channel distance of 20 cm. The path loss of TX2 and RX3 is -25.33 dB. The amplitude of a main signal and multipath signal is  $90 \,\mathrm{mV}_{pk-pk}$  and  $50 \,\mathrm{mV}_{pk-pk}$ , respectively. Fig. 4.12 shows that next arrived signals are combined with a main signal, making width of the main signal wider. Considering the impact of EMI generated by the operating motherboard, multipath components are severe because of wide dispersing distortion and comparable large amplitude as shown in Fig. 4.13.

Figure 4.12: Time-domain received waveform at RX3

Figure 4.13: Received pulse response at RX3

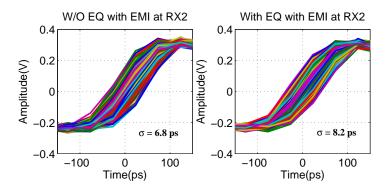

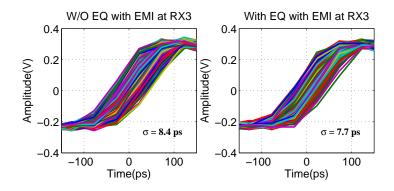

Hence, the pulse response shows  $3.52\,\mathrm{dB}$  improvement in reduction of post-cursor ISI, and only  $0.9\,\mathrm{dB}$  increase of main cursor to post-cursor ISI ratio after the equalization while the motherboard is operating. Recovered ADC clock jitter is slightly reduced from  $8.4\,\mathrm{ps}$  to  $7.7\,\mathrm{ps}$  when EQ is performed as shown in Fig. 4.14. The BER after applying EQ is also improved by  $2.5\mathrm{X}$  from  $1.7\times10^{-3}$  to  $6.7\times10^{-4}$  with the existence of EMI, and by  $3\mathrm{X}$  from  $2\times10^{-3}$  to  $6.7\times10^{-4}$  in case of an inactive computing channel environment.

Figure 4.14: Recovered ADC clock jitter at RX3

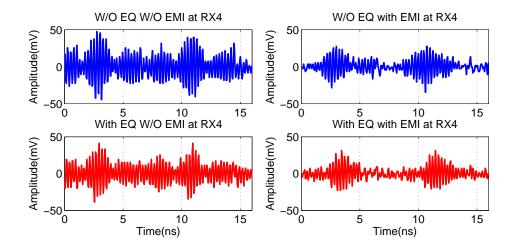

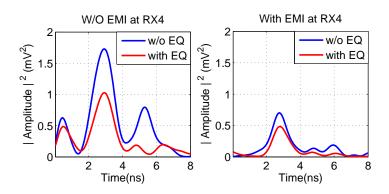

#### 4.3.4 TX2 and RX4

TX2 and RX4 are in non-line-of-sight (NLOS) position with 15 cm apart from each other. The signal attenuation between TX2 and RX4 is -25.77 dB. The time-domain waveform shown in Fig. 4.15 indicates that multipath components are comparable to a main signal with the amplitude of  $50 \,\mathrm{mV}_{pk-pk}$  and  $55 \,\mathrm{mV}_{pk-pk}$  for a pre-arrival and post-arrival, respectively while the amplitude of the main signal is  $95 \,\mathrm{mV}_{pk-pk}$ . The technique of equalization was applied to reduce pre-cursor and post-cursor ISI as shown in Fig. 4.16. In the absence of EMI, the results shows  $6.3 \,\mathrm{dB}$  and only  $1.1 \,\mathrm{dB}$  decrease in post-cursor and pre-cursor ISI, respectively. The

Figure 4.15: Time-domain received waveform at RX4

Figure 4.16: Received pulse response at RX4

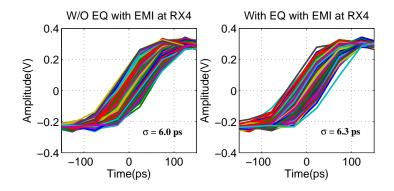

ratio of main cursor to post-cursor ISI is increased by 4 dB. Nevertheless, there is no improvement in the main cursor to pre-cursor ISI ratio. On the other hand, in the presence of EMI inside the computer, the ratio of main cursor to post-cursor ISI is increased by 1.1 dB, and post-cursor ISI is decreased by 2.7 dB. Recovered ADC clock jitter remains constant as 6.0-6.3 ps after the equalization as shown in Fig. 4.17. The existence of large amplitudes in pre-cursor ISI and post-cursor ISI causes severe multipath distortions, resulting in higher BER of  $1 \times 10^{-3}$  even after the technique of equalization is performed.

Figure 4.17: Recovered ADC clock jitter at RX4

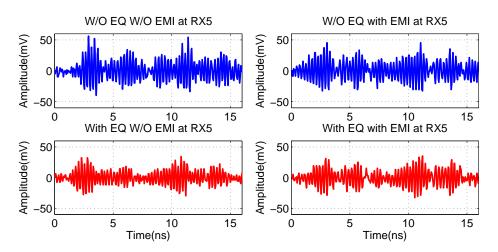

## 4.3.5 TX3 and RX5

TX3 and RX5 is located the same position as TX2 and RX3 by interchanging between the transmitter and receiver. The path loss between TX3 and RX5 is also -25.33 dB equal to the loss between TX2 and RX3. As shown in Fig. 4.18, the amplitude of a main signal is  $90 \,\mathrm{mV}_{pk-pk}$  along with the comparable amplitude of the second arrival of  $55 \,\mathrm{mV}_{pk-pk}$ . Due to different surroundings at RX5 and RX3 causing different amplitudes, phases, and times of arrivals, the pulse response

Figure 4.18: Time-domain received waveform at RX5

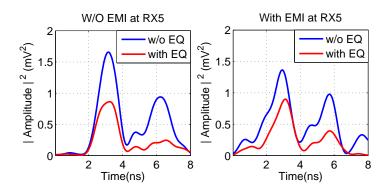

shows that the post-cursor ISI arrives to the main cursor later at RX5 than that at RX3 by 1.5 ns as shown in Fig. 4.19. After performing the equalization, the post-cursor ISI is degraded by 5.8 dB, and the main cursor to post-cursor ISI ratio is enhanced by 3 dB without any operation on the motherboard. During the operation of motherboard, it shows 3.9 dB reduction of the post-cursor ISI, and 2.1 dB increment of the main cursor to post-cursor ISI ratio.

Figure 4.19: Received pulse response at RX5

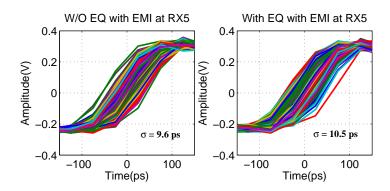

Fig. 4.20 shows an slight increase in recovered ADC clock jitter after the equalization from 9.6 ps to 10.5 ps. However, due to the late arrival of the post-cursor ISI to main cursor, the BER shows 4X enhancement from  $1.3 \times 10^{-3}$  to  $3.3 \times 10^{-4}$  when using the equalizer.

Figure 4.20: Recovered ADC clock jitter at RX5

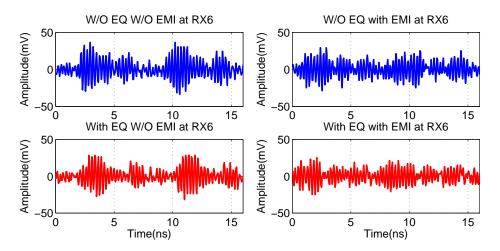

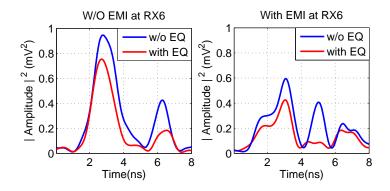

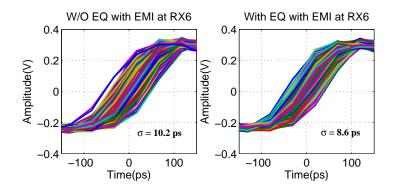

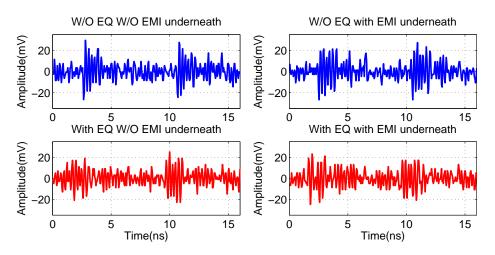

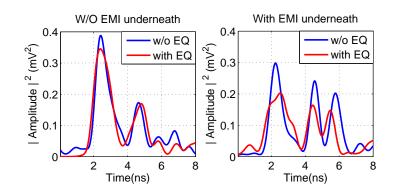

#### 4.3.6 TX3 and RX6