### AN ABSTRACT OF THE THESIS OF

<u>Vikrant P Arumugam</u> for the degree of <u>Master of Science</u> in <u>Electrical and Computer Engineering</u> presented on <u>December 14, 2009</u>. Title: <u>Efficient RF Energy Scavenging and Ultra-Low Power Management for</u> <u>Powering Wireless Sensor Nodes</u>

Abstract approved: \_

Terri Fiez

Kartikeya Mayaram

As the demand for real-time information in engineering and health care systems keeps increasing, the need for wireless sensor nodes is also continuously increasing. As a result, the cost and effort involved in installing and maintaining batteries to power the numerous sensor nodes is growing exponentially. Providing a cost effective and maintenance free alternate energy source is the motivation behind the development of energy scavenging solutions for self-powered sensor networks.

In this research, an energy scavenging system that extracts energy from ambient radio-frequency waves transmitted in the 2.4 GHz ISM band is designed. The harvested energy is efficiently managed with an ultra low-power switched capacitor buck-boost DC-DC converter to wirelessly power the nodes in a wireless sensor network.

Analysis and optimization of the number of rectifier stages required to achieve efficient power conversion is carried out. To improve far field conversion efficiency and extend the scavenger sensitivity, the threshold voltage of the diodes in the rectifiers are reduced to about 50 mV by using the floating-gate programming technique. The active power consumption of the switched-capacitor DC-DC converter is around 1.2  $\mu$ W. A micro-power analog to digital converter for variable gain selection and a sub-threshold linear voltage regulator for providing the start-up, are designed. The integrated system provides a fully autonomous micro-energy scavenging solution for the sensor nodes.

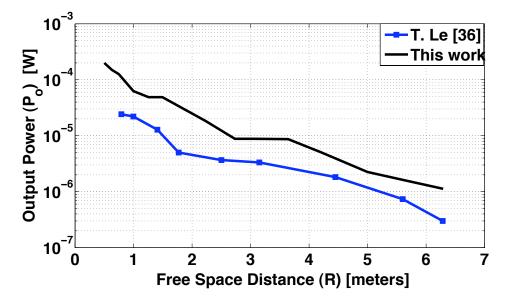

The simulated results suggest that the scavenger achieves a 10% higher conversion efficiency than the most recently reported work. The operational distance of this improved energy scavenging solution is 6 meters (in free space) from an intentional RF transmitter operating under FCC specifications at 2.4 GHz. The targeted application of this research is to provide an alternate energy solution for low power devices, including wireless sensor nodes and bio-medical applications. ©Copyright by Vikrant P Arumugam December 14, 2009 All Rights Reserved

## Efficient RF Energy Scavenging and Ultra-Low Power Management for Powering Wireless Sensor Nodes

by

Vikrant P Arumugam

# A THESIS

### submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Master of Science

Presented December 14, 2009 Commencement June 2010 Master of Science thesis of Vikrant P Arumugam presented on December 14, 2009

APPROVED:

Major Professor, representing Electrical and Computer Engineering

Director of the School of Electrical Engineering and Computer Science

Dean of the Graduate School

I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my thesis to any reader upon request.

#### ACKNOWLEDGEMENTS

I would like to express my sincere gratitude to my major advisors Dr. Kartikeya Mayaram and Dr. Terri Fiez for giving me an opportunity to be part of their research group.

I would like to thank Dr. Kartikeya Mayaram, Dr. Terri Fiez and Dr. Ted Brekken for serving on my committee and reviewing my thesis. Special thanks to the Graduate council representative Dr. Abi T. Farsoni for being a part of my defense committee.

I am very thankful to Dr. Pavan Kumar Hanumolu for the fascinating courses he offered during my time at Oregon State University. I would like to thank Dr. Gabor Temes for his courses which helped me greatly during my research work. I would also like to thank NSF (National Science Foundation) for providing financial support for this project.

I would like to thank my colleagues, in particular, James Ayers and Thomas Brown for spending their valuable time in reviewing my thesis. I thank my lab mates Triet Le, Napong Panitantum, Robert Batten, Ramin Zanbaghi, Saeed Pourbagheri among others for sharing their thoughts on my work. My sincere thanks to Qadeer Khan for the insightful discussions and giving me guidance on the switching converter design. I would also like to thank my other friends Karthik Jayaraman, Sarvesh Bang, Vikas Shilimkar, Madan Thangavelu and others for providing me a refreshing break from work whenever I needed it.

Finally, I would like to express my sincere thanks to my parents, my sister, my brothers and my friends for giving me valuable suggestions, both personal and professional. I thank the almighty for showering blessings upon me.

# TABLE OF CONTENTS

|    |      |                                                                                                                                                                       | Page           |

|----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 1. | INTI | RODUCTION                                                                                                                                                             | 1              |

|    | 1.1. | Motivation for Energy Scavenging                                                                                                                                      | 1              |

|    | 1.2. | Types of Energy Scavengers                                                                                                                                            | 1              |

|    | 1.3. | Generic Block Diagram of an Energy Scavenger                                                                                                                          | 2              |

|    | 1.4. | Motivation for Radio Frequency Energy Scavenging                                                                                                                      | 3              |

|    | 1.5. | Organization of the Thesis                                                                                                                                            | 4              |

| 2. | SYS  | TEM LEVEL OVERVIEW AND LITERATURE REVIEW                                                                                                                              | 6              |

|    | 2.1. | Introduction                                                                                                                                                          | 6              |

|    | 2.2. | RF Power Transmission - Regulations and Limitations                                                                                                                   | 6              |

|    | 2.3. | Components in a RF Energy Scavenging System                                                                                                                           | 8              |

|    | 2.4. | RF-to-DC Conversion - Rectification                                                                                                                                   | 11             |

|    |      | <ul><li>2.4.1. Comparison of energy efficient rectifier architectures</li><li>2.4.2. RF rectification design challenges</li></ul>                                     | 11<br>13       |

|    | 2.5. | DC-to-DC Conversion - Regulation                                                                                                                                      | 13             |

|    |      | <ul><li>2.5.1. Prior work on efficient regulator topologies</li><li>2.5.2. Regulation design challenges</li></ul>                                                     | 14<br>15       |

| 3. | EFF  | ICIENT FAR FIELD RF RECTIFICATION                                                                                                                                     | 16             |

|    | 3.1. | Introduction                                                                                                                                                          | 16             |

|    | 3.2. | Critical Parameters in a RF Energy Scavenging System                                                                                                                  | 16             |

|    |      | <ul><li>3.2.1. Power-up threshold of the Scavenger</li><li>3.2.2. Passive voltage amplification</li><li>3.2.3. Power Conversion Efficiency of the Scavenger</li></ul> | 18<br>19<br>24 |

# TABLE OF CONTENTS (Continued)

|    |      |                                                                                                                                                                                                                                                                        | Page                                                                                           |

|----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|    | 3.3. | Single-Poly Floating-Gate Technique                                                                                                                                                                                                                                    | 25                                                                                             |

|    |      | 3.3.1. Fowler Nordheim programming                                                                                                                                                                                                                                     | 27                                                                                             |

|    | 3.4. | Analysis and Optimization of a N-Stage Rectifier                                                                                                                                                                                                                       | 27                                                                                             |

|    |      | <ul><li>3.4.1. Optimization for maximizing the rectified DC output voltage</li><li>3.4.2. Optimization for maximizing the conversion efficiency</li><li>3.4.3. Optimization for maximizing the passive voltage amplification</li><li>3.4.4. Rectifier design</li></ul> | 28<br>29<br>29<br>31                                                                           |

| 4. | DES  | IGN OF THE POWER MANAGEMENT UNIT                                                                                                                                                                                                                                       | 33                                                                                             |

|    | 4.1. | Introduction                                                                                                                                                                                                                                                           | 33                                                                                             |

|    | 4.2. | Linear Regulator vs Switching Converter                                                                                                                                                                                                                                | 33                                                                                             |

|    |      | <ul><li>4.2.1. Linear regulator</li><li>4.2.2. Switching regulators - DC-DC converters</li></ul>                                                                                                                                                                       | 34<br>35                                                                                       |

|    | 4.3. | Inductor Based vs Switched Capacitor Based Switching Converter                                                                                                                                                                                                         | 36                                                                                             |

|    |      | <ul><li>4.3.1. Inductor based switching converters</li><li>4.3.2. Switched capacitor based switching converters</li></ul>                                                                                                                                              | $\frac{37}{37}$                                                                                |

|    | 4.4. | Analysis and Optimization of Switched Capacitor Buck-Boost Con-                                                                                                                                                                                                        | 20                                                                                             |

|    |      | <ul> <li>verter</li></ul>                                                                                                                                                                                                                                              | <ol> <li>39</li> <li>39</li> <li>40</li> <li>43</li> <li>44</li> <li>45</li> <li>48</li> </ol> |

|    | 4.5. | Proposed RF Energy Scavenging System                                                                                                                                                                                                                                   | 48                                                                                             |

|    | 4.6. | Circuit design of Switched Capacitor Buck-Boost Converter                                                                                                                                                                                                              | 50                                                                                             |

# TABLE OF CONTENTS (Continued)

|    |                                                               |                                                                                                                                                                             | Pa |

|----|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    | 4.7.                                                          | Hysteretic Mode Controller                                                                                                                                                  | ļ  |

|    |                                                               | <ul><li>4.7.1. Hysteretic comparator</li></ul>                                                                                                                              | !  |

|    | 4.8.                                                          | Gain Select Logic and Digital Encoder                                                                                                                                       | ļ  |

|    |                                                               | <ul><li>4.8.1. 3-bit Successive approximation ADC</li><li>4.8.2. Digital phase encoder</li></ul>                                                                            |    |

|    | 4.9.                                                          | Start-up circuit                                                                                                                                                            |    |

|    | 4.10.                                                         | Simulated Efficiency of the DC-DC Converter                                                                                                                                 |    |

|    | 4.11.                                                         | Performance Summary of the Light-Load Switching Converter                                                                                                                   |    |

|    |                                                               |                                                                                                                                                                             |    |

| 5. | SIMU                                                          | JLATED RESULTS OF THE RF ENERGY SCAVENGER                                                                                                                                   |    |

| 5. | SIMU<br>5.1.                                                  | JLATED RESULTS OF THE RF ENERGY SCAVENGER                                                                                                                                   |    |

| 5. |                                                               |                                                                                                                                                                             |    |

| 5. | 5.1.                                                          | Introduction                                                                                                                                                                |    |

| 5. | 5.1.<br>5.2.                                                  | Introduction Power Conversion Efficiency of Energy Scavenger                                                                                                                |    |

| 5. | <ul><li>5.1.</li><li>5.2.</li><li>5.3.</li><li>5.4.</li></ul> | Introduction       Power Conversion Efficiency of Energy Scavenger         Harvested Power of the RF Energy Scavenger       Power Conversion Efficiency of Energy Scavenger |    |

# LIST OF FIGURES

| Figure |                                                                                                               |      |

|--------|---------------------------------------------------------------------------------------------------------------|------|

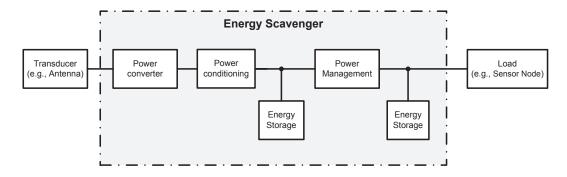

| 1.1    | Block diagram of a typical energy scavenging system                                                           | . 3  |

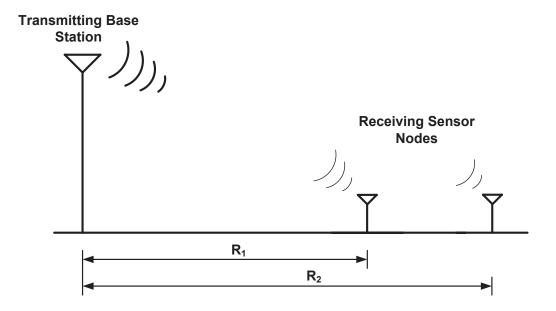

| 2.1    | Wireless power transmission and communication network with sensor nodes.                                      | . 7  |

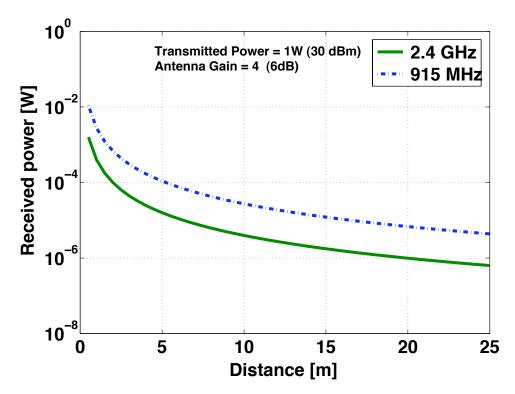

| 2.2    | Received power as a function of free space distance from a 1 W RF source.                                     | . 8  |

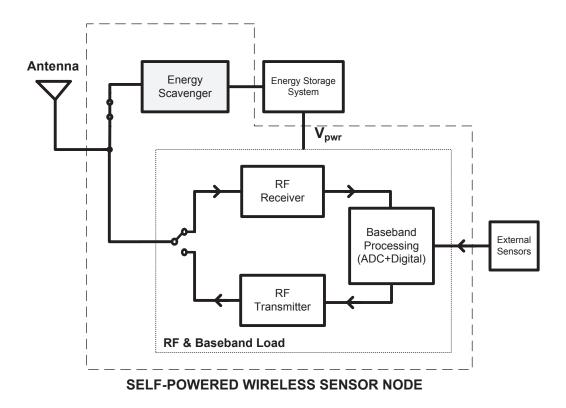

| 2.3    | RF energy scavenger in a passively powered wireless sensor node                                               | . 9  |

| 2.4    | Block diagram of a typical RF energy scavenging system                                                        | . 10 |

| 3.1    | Peak voltage across a 50 $\Omega$ terminated system from a 1 W Source.                                        | . 17 |

| 3.2    | Impedance model of the RF energy scavenging circuit                                                           | . 20 |

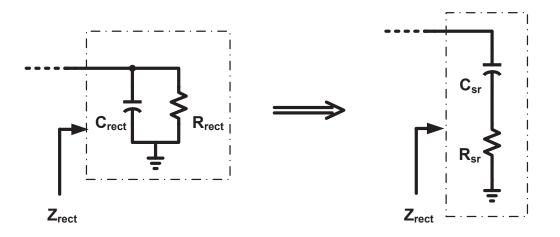

| 3.3    | Impedance modeling of the full-wave rectifier                                                                 | . 21 |

| 3.4    | Parallel to series transformation of the full-wave rectifier impedance model                                  | . 22 |

| 3.5    | Model of the passive voltage amplification network                                                            | . 22 |

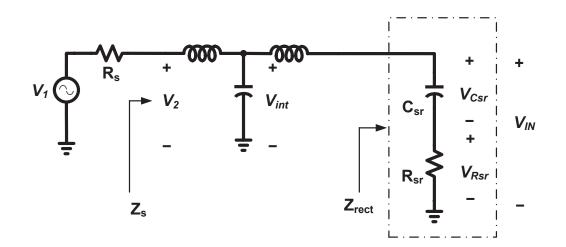

| 3.6    | Block diagram showing the received, available and output power<br>in the system                               | . 24 |

| 3.7    | Single-poly floating-gate programming of a NMOS device                                                        | . 26 |

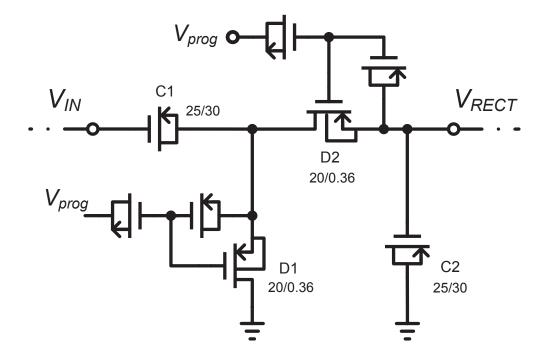

| 3.8    | PMOS rectifier design in the 180 nm CMOS process                                                              | . 31 |

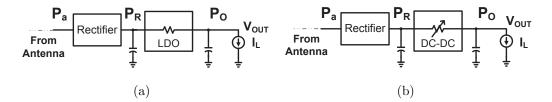

| 4.1    | Energy scavenger with the power management unit. (a) Linear LDO regulator. (b) Switching DC-DC regulator      | . 35 |

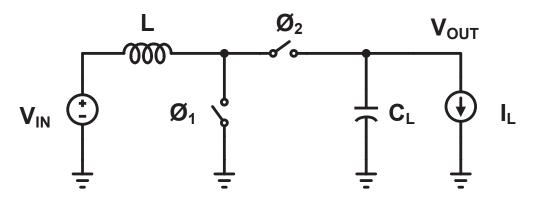

| 4.2    | Inductor based switching converter.                                                                           | . 38 |

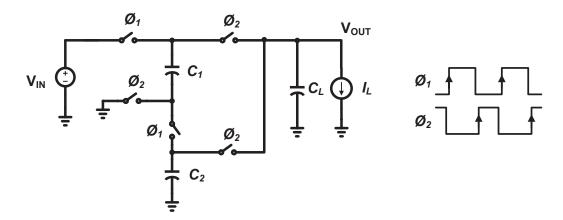

| 4.3    | Schematic of a buck-mode switched capacitor converter                                                         | . 38 |

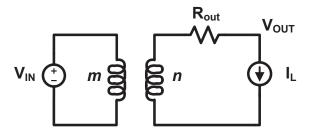

| 4.4    | General model of a switching converter with losses modeled in $R_{out}$                                       | . 40 |

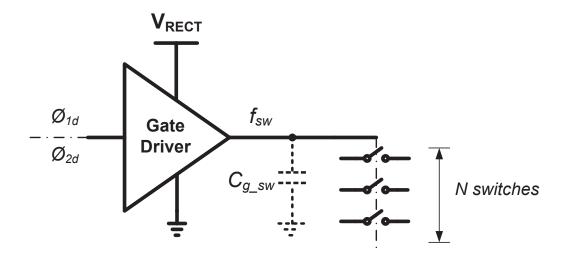

| 4.5    | Gate driver block driving the gate capacitances                                                               | . 42 |

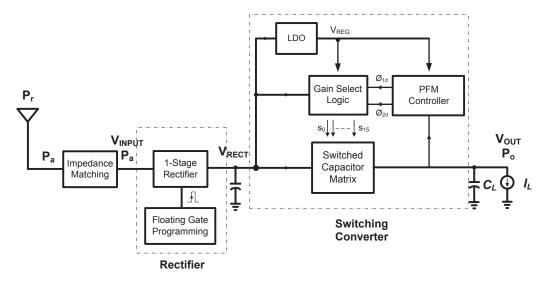

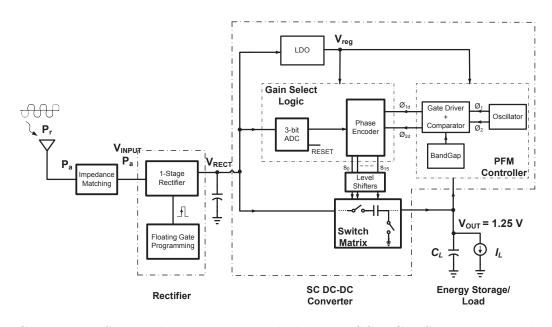

| 4.6    | Architecture of the proposed RF energy scavenging system                                                      | . 49 |

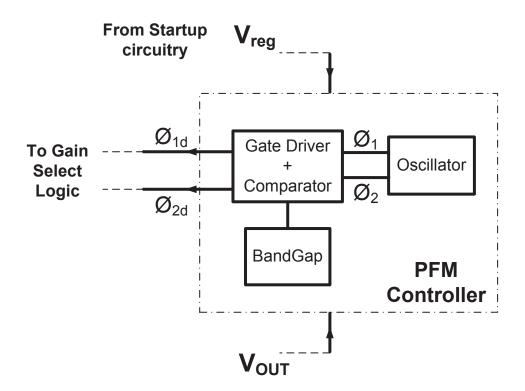

| 4.7    | Hysteretic PFM mode controller block diagram.                                                                 | . 52 |

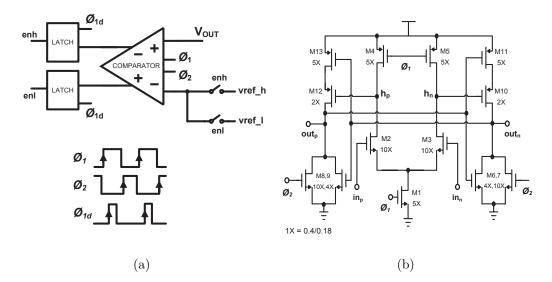

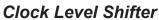

| 4.8    | Hysteretic comparator design. (a) Schematic of the hysteretic com-<br>parator. (b) Dynamic comparator circuit | . 53 |

# LIST OF FIGURES (Continued)

| Figu | Figure     P                                                                                                                        |      |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------|------|--|

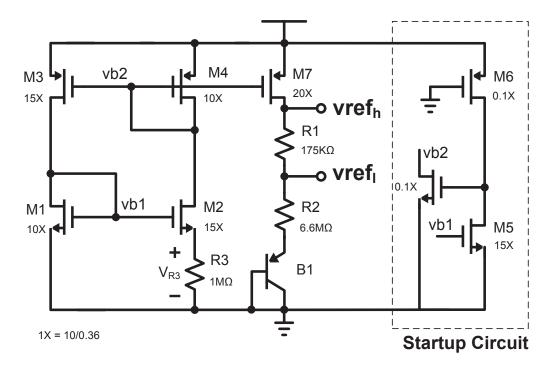

| 4.9  | Bandgap reference with a start-up circuit.                                                                                          | 55   |  |

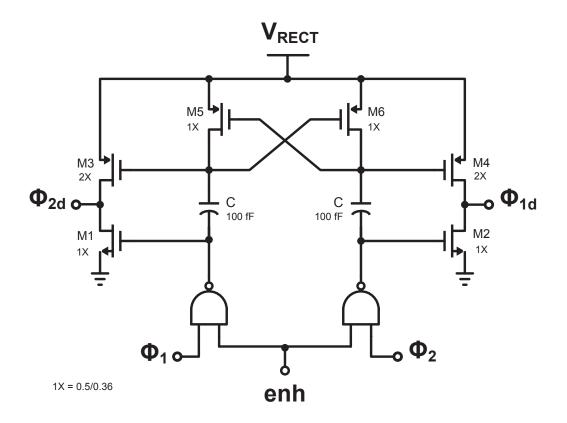

| 4.10 | Gate driver circuitry in the PFM controller                                                                                         | 56   |  |

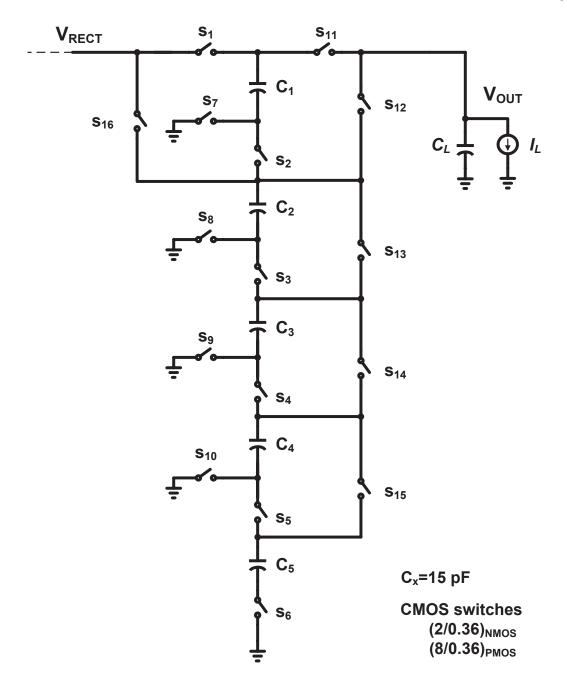

| 4.11 | Switch matrix design with 5 capacitors and 16 CMOS switches                                                                         | 58   |  |

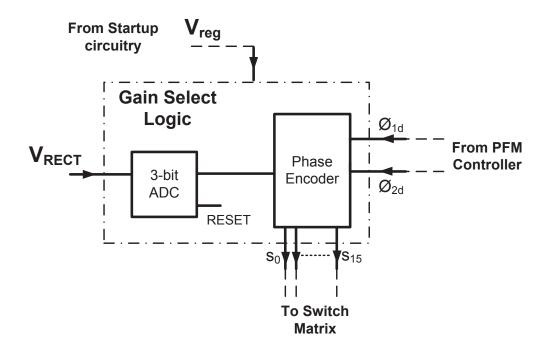

| 4.12 | Block diagram of gain select logic and digital controller                                                                           | 59   |  |

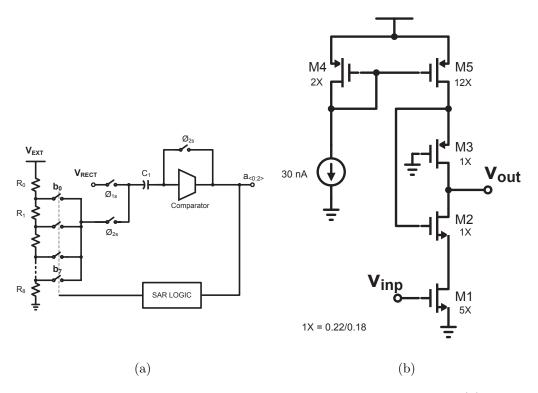

| 4.13 | Successive approximation analog to digital converter. (a) SAR ADC block diagram. (b) Inverter based comparator                      | 60   |  |

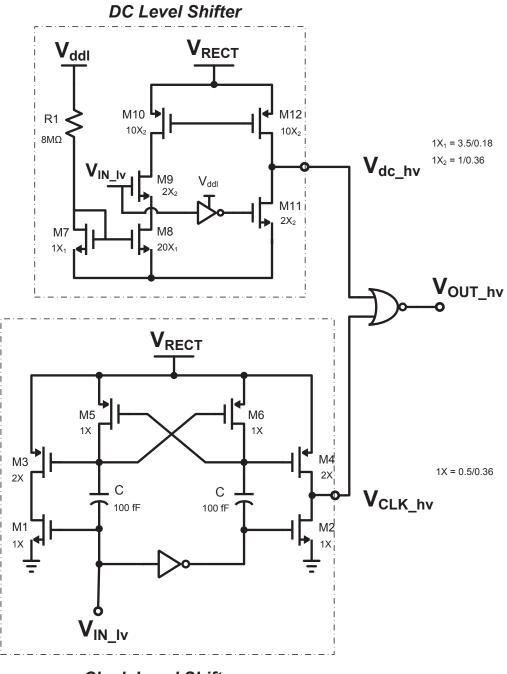

| 4.14 | Hybrid level shifter for clock and DC level shifting                                                                                | 65   |  |

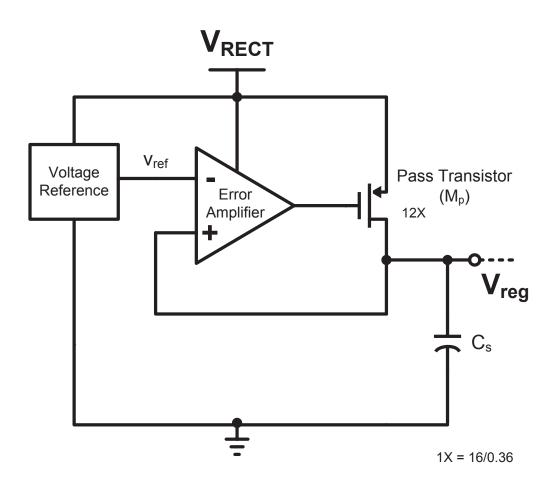

| 4.15 | Linear LDO regulator as a startup circuit                                                                                           | 66   |  |

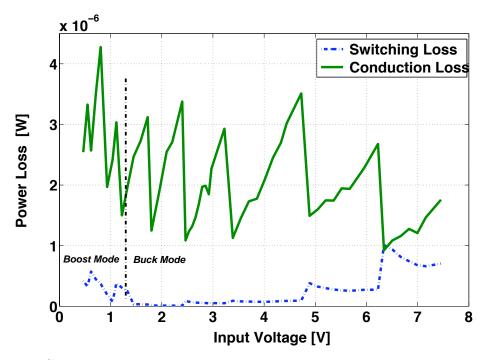

| 4.16 | Losses in the switching converter under light loads                                                                                 | 67   |  |

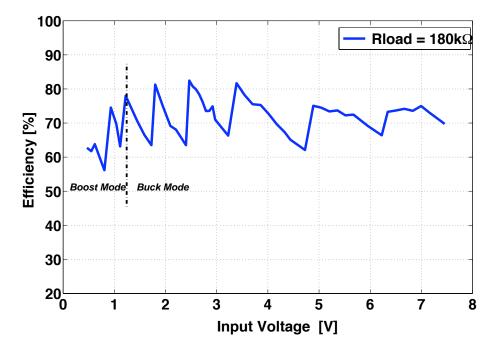

| 4.17 | Power efficiency of the switching converter under light loads                                                                       | 67   |  |

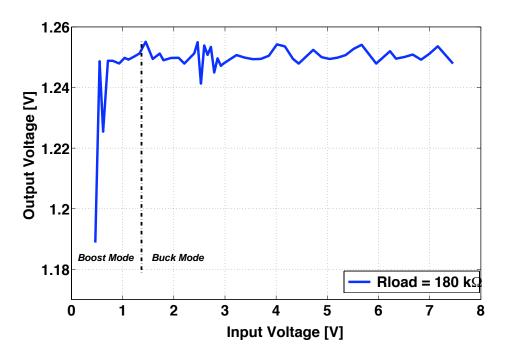

| 4.18 | Output voltage of the switching converter under light loads                                                                         | 68   |  |

| 5.1  | System level diagram including the SC DC-DC converter with the switch matrix, PFM controller, gain select logic, startup interface. | 70   |  |

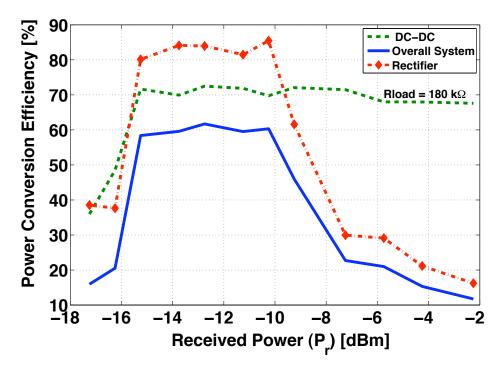

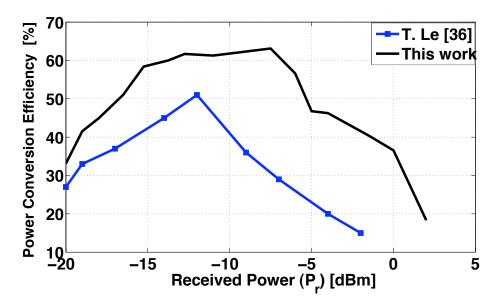

| 5.2  | Conversion efficiency of the scavenger with 8.7 $\mu \rm W$ load at 1.25 V                                                          | 71   |  |

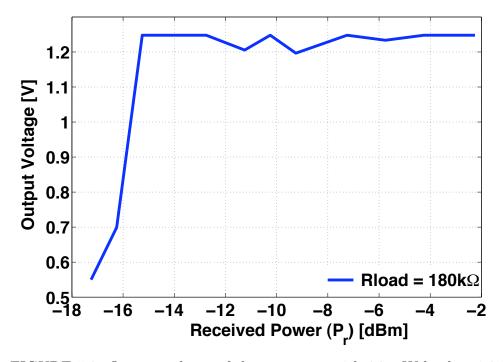

| 5.3  | Output voltage of the scavenger with 8.7 $\mu$ W load at 1.25 V                                                                     | 72   |  |

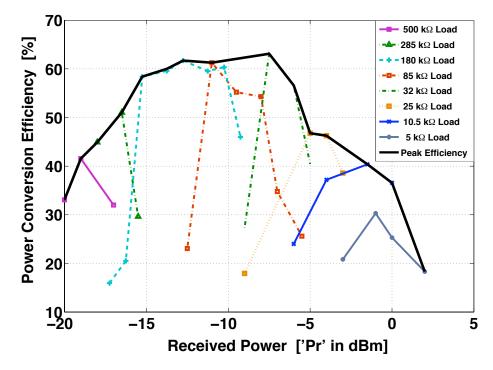

| 5.4  | Peak conversion efficiency of the converter across various load power                                                               | . 73 |  |

| 5.5  | Efficiency performance of RF energy scavenging system                                                                               | 74   |  |

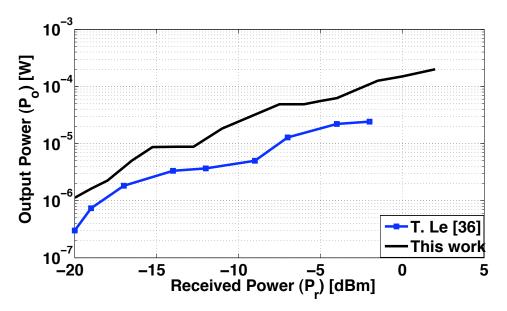

| 5.6  | Harvested output power at an output voltage of 1.25 V                                                                               | 75   |  |

| 5.7  | Harvested output power as a function of the free-space distance                                                                     | 75   |  |

# LIST OF TABLES

| Tab | ble                                                            |    |  |

|-----|----------------------------------------------------------------|----|--|

| 1.1 | Most commonly available ambient energy sources. [5]            | 2  |  |

| 4.1 | Power consumption of the low power switching converter circuit | 62 |  |

# 1. INTRODUCTION

# 1.1. Motivation for Energy Scavenging

As the wireless technology continues to evolve, the proliferation of sensor nodes in a wireless sensor network (WSN) also continues to increase. The primary source of power for the wireless sensor nodes is a battery. As the cost and effort involved in maintaining and replacing the batteries in these sensor nodes keeps increasing with the increase in the number of sensor nodes [1], the key focus shifts to finding alternate sources of energy.

Ambient sources of energy such as light, kinetic and heat have been harnessed for powering devices over a period of time dating back to a few decades. The process of harnessing energy from the ambient, or otherwise unused energy sources in the environment is referred to as *energy scavenging*. Energy scavengers can either eliminate the batteries by replacing them or increase the lifetime of the battery by replenishing the lost charge.

### **1.2.** Types of Energy Scavengers

Typical energy scavengers are photoelectric (light) [2, 3], piezoelectric (vibration) [4, 5], thermoelectric (heat) [8, 9] and electromagnetic (radio-frequency). Electrical energy converted from these sources can be stored and used to power analog or digital circuitry. Table 1.1 shows the various ambient energy sources and the power density available for extraction [5].

| Energy Sources                              | Power density $(\mu W/cm^3)$            |

|---------------------------------------------|-----------------------------------------|

| Solar/Light (Photovoltaic)                  | $15000_{sunny}$ - $150_{cloudy}$        |

| Heat (Thermoelectric)                       | $100 @ 1^{\circ}C \text{ gradient} [7]$ |

| Vibration (Piezoelectric)                   | 200 [5]                                 |

| Electromagnetic (Radio Frequency @ 2.4 GHz) | 400 @ 1 m - 15.8 @ 5 m [35]             |

TABLE 1.1: Most commonly available ambient energy sources. [5]

## **1.3.** Generic Block Diagram of an Energy Scavenger

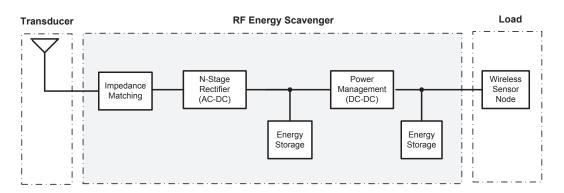

A generic block diagram of the scavenger circuit in an integrated system is shown in Figure 1.1. The system comprises of an energy capture (transducer) and convert circuit (power converter). The transducer transforms the input energy into an electrical output.

In many cases, the transducer is followed by an input matching network which ensures maximum power transfer into the system. The power converter circuit, depending on the energy source, can be a rectifier (AC-DC) or a DC-DC converter. The power converter is followed by a power conditioning circuit which provides current limitation and over voltage protection functionalities. The energy storage system (ESS) can be a rechargeable battery, a super capacitor or any other storage medium.

The output of the power conditioning circuit can vary depending on the power density available for havesting. This stored power needs to supply a device or load at a particular output voltage. The block implementing this power management

FIGURE 1.1: Block diagram of a typical energy scavenging system.

functionality can be a linear regulator or a switching converter, which converts a varying DC input to a constant DC output voltage. The extracted energy is stored in a charge storage element for future use.

# 1.4. Motivation for Radio Frequency Energy Scavenging

RF energy scavenging can play a significant role in powering and sustaining the numerous sensor nodes which are installed in harsh inaccessible environments. For wireless sensor networks powered by radio frequency (RF) waves [10, 14], a base station transmits the RF energy. The antenna acts as a transducer by capturing the incoming electromagnetic RF waves and converting them into electric current.

The primary advantage of harvesting RF energy over other energy sources is the availability of a controllable source in the form of an intentional radiator transmitting RF energy. Other sources are not always dependable for continuous supply of energy, such as solar energy where the energy available depends on the illuminated condition of the sensor location at a particular time. RF energy can be extracted from the energy available during the transmission by public RF telecommunication networks, such as mobile phones and wireless routers.

The main challenge in RF energy scavenging is the efficient scavenging of the relatively low levels of available harvestable energy. It can be seen from Table 1.1, that depending upon the distance from the transmitter, the available RF energy is very limited. This makes it difficult to continuously drive loads requiring power on the order of a few hundred micro watts. In such cases, the extracted energy is stored in an energy storage element over a period of time. The loads can then be supplied energy for short time intervals. This is referred as the *burst mode* of operation for the scavenger.

### **1.5.** Organization of the Thesis

This thesis discusses the design of an efficient RF energy scavenger circuit. Chapter 2 provides an overview of the various energy efficient techniques to harvest and store the ambient RF power. The details of the most recent work done in the area of efficient rectification and power conversion and the significant results obtained are compared and discussed.

Chapter 3 discusses the details of achieving an efficient RF rectification system. The regulations limiting RF energy transmission and the various definitions in a RF energy scavenging system are discussed. The analysis, optimization and design techniques for realizing an efficient power conversion circuit are presented.

Chapter 4 elaborates upon the system level description and component value optimization of the power management unit. The circuit details and the simulated performance of the switching power converter are presented and analyzed. Chapter 5 investigates the simulated results on the performance of the overall RF energy scavenging circuit. It concludes with a comparison of results of the current design with other prior work.

Chapter 6 provides the conclusions of this work and future research problems in the area of energy scavenging.

# 2. SYSTEM LEVEL OVERVIEW AND LITERATURE REVIEW

### 2.1. Introduction

The previous chapter introduced the concept of energy scavenging from ambient energy sources. To extract radio frequency energy, a dedicated signal source is required that satisfies the FCC rules for transmission in certain ISM bands. The strength of the transmitted RF energy decreases rapidly as the distance from the RF source increases. In order to maximize the extracted energy from these low strength RF waves, design of ultra-low power circuits, which consume power in the order of nano or pico watts, is critical. In this chapter, prior work published in the area of RF energy harvesting is presented describing their key contributions and their shortcomings. Finally, a new architecture which overcomes these shortcomings is presented.

### 2.2. **RF** Power Transmission - Regulations and Limitations

The concept of wireless transmission and reception is shown in Figure 2.1. A transmitting station transmiting high power RF energy in the ISM (Industrial, Scientific, Medical) bands is chosen.

The maximum transmitter power is 4 Watts (30 dBm transmission + 6 dB antenna gain) of EIRP (Effective Isotropic Radiated Power) at 2.4 GHz, according to the Federal Communications Commission (FCC) specifications [11]. The strength of the transmitted signal decreases quadratically as the distance from the transmit-

FIGURE 2.1: Wireless power transmission and communication network with sensor nodes.

ter increases. The power loss in free space is governed by the Friis transmission equation [35]. Equation (2.1) gives an ideal estimate of the received power given the transmitted power and the distance from the source.

$$P_r = P_t G_t G_r \left(\frac{\lambda}{4\pi R}\right)^2 \tag{2.1}$$

where  $P_r$  and  $P_t$  are the received power and transmitted power in Watts at the antenna terminals, respectively.  $G_r$  and  $G_t$  are the antenna gain of the receiving and transmitting antennas, respectively,  $\lambda$  is the wavelength of the transmitted signal in meters and R is the distance in meters between the transmit and receive antennas.

Figure 2.2 shows that the received power for signals transmitted in a higher

FIGURE 2.2: Received power as a function of free space distance from a 1 W RF source.

frequency ISM band (2.4 GHz - 2.4835 GHz) is smaller than that for signals transmitted in a lower frequency ISM band (905 MHz - 928 MHz).

# 2.3. Components in a RF Energy Scavenging System

An RF energy scavenging system in a passively powered wireless sensor node application is shown in Figure 2.3. The energy scavenger harvests the ambient RF energy, stores it across an energy storage element, and powers the RF and baseband signal processing circuitry.

FIGURE 2.3: RF energy scavenger in a passively powered wireless sensor node.

The components of the RF energy scavenging system can be explained with the help of the block diagram shown in Figure 2.4. The system has four critical blocks to convert the RF energy to usable DC power.

- 1. An input matching network which provides lossless matching between the antenna source impedance and the input impedance of the circuit.

- 2. A full wave rectification stage which provides sinusoidal RF to DC signal conversion with programmable threshold voltage MOSFET diodes to achieve high efficiency rectification.

FIGURE 2.4: Block diagram of a typical RF energy scavenging system.

- 3. A power-efficient output voltage regulation scheme capable of driving a wide range of output loads. The output voltage of the rectifier can vary between a few hundred milli-volts to more than 5 volts, depending upon the incoming power. The regulator provides a stable supply voltage.

- 4. An energy storage unit which can either be a super-capacitor or a rechargeable battery.

From Figure 2.4 it can be observed that the efficiency of a RF energy scavenger is a function of two cascaded systems: a RF-to-DC conversion system (rectifier) and a DC-to-DC conversion system (regulator). In order to realize a highly efficient scavenger, the internal loss components in both functional blocks are identified and techniques to minimize the loss are found.

# 2.4. RF-to-DC Conversion - Rectification

The input signal received by the antenna of the energy harvester, as shown in Figure 2.4, is sinusoidal in nature. This sinusoidal RF input signal is converted into a DC voltage by a rectifier. The critical loss component in a rectifier is the on-resistance of the MOS diodes. In other words, the power lost in an active rectifier is defined as the amount of power required to overcome the threshold voltage of the diodes in the rectifier.

Earlier work on highly efficient rectifiers for RF energy scavengers focused on various techniques to reduce the threshold voltage of the MOS diodes. Apart from using Schottky diodes, native and low threshold voltage devices, the threshold voltage can be reduced by other techniques as proposed in [12, 13, 14].

#### 2.4.1. Comparison of energy efficient rectifier architectures

The work done by Umeda in [12], presents an active switched capacitor circuit and an external gate-source bias voltage to bias the MOS diodes in the rectifier circuit. The extra circuitry required for the bias voltage generation and the requirement for secondary battery storage makes this three stage rectifier solution not feasible for autonomous energy scavenging operation.

A RFID tag described in [13] shows a double stacked one-stage rectifier performing the RF-to-DC conversion. The current sensing scheme used in this configuration helps reduce the threshold voltage of the PMOS diodes used in the rectifiers. But the reduction in the threshold voltage achieved using this scheme is not significant and the scheme dissipates some static power while using huge resistors occupying a larger area. The work done in [14] shows 36 stages of rectifiers cascaded to realize a higher output voltage. The threshold voltage of the MOS diodes is reduced by using a single-poly floating gate programming technique as described in [16]. This solution is shown to generate a higher output DC voltage compared to the previous work under similar load conditions. The fundamental problem of achieving maximum rectification efficiency is not addressed by this solution since a larger number of stacked rectifier stages consume higher quiescent power for operation. In other words, the higher the number of active components in the system, the higher the internal loss and hence the lower conversion efficiency.

Shameli proposed a power harvester with an increased operating range. In [18], he claims that this increase is achieved by a passive voltage amplification of the incoming input signal with the help of a high Q impedance matching circuitry. The published results indicate that the minimum power required to achieve a 2  $\mu$ W output power at 1 V output is about -14.1 dBm with a four-stage standard CMOS rectifier. The threshold voltage of the CMOS diodes remains unaffected and hence the dead zone for rectification is significant.

The power extraction system built for RFID applications by Mandal [20, 21] derives an optimization metric for realizing rectifiers with optimal performance. The number of rectifier stages and the sizing of the MOS diode tied transistors in the rectifiers are found by fixing the output voltage needed for a particular load current drive. The availability of low threshold voltage transistors in the process helps this design achieve a better power conversion efficiency than conventional rectifiers.

Recent work on energy scavenging by Salter [22], proposes an RF energy scavenging system implemented with a rectifier followed by a switched capacitor DC-DC converter. The rectifier circuit used in this design is a Villard voltage doubler in a standard CMOS process. The rectifier outputs a DC voltage of 1 V driving a 200 nA load at a input power of -16 dBm. Hence, the operating range of this harvester at 2.2 GHz is restricted to 4 meters in free space.

#### 2.4.2. RF rectification design challenges

A comparison of all the different rectifier configurations discussed earlier shows the need for an optimized rectifier configuration with a high far field RF rectification efficiency. A RF harvester with an efficient far field rectifier can operate at a longer distance from the transmitting source.

A study and design comparison of different rectifier configurations is done from [12, 13, 23, 21] and the voltage doubler configuration in [14] is chosen for the rectifier. The threshold voltage of the CMOS diodes is reduced by the floating gate programming technique proposed in [16, 17]. In this research the number of rectifier stages are optimized considering high RF rectification efficiency and high output voltage. Passive voltage amplification using a high-Q impedance matching network is achieved to increase the useful range of power harvesting.

### 2.5. DC-to-DC Conversion - Regulation

The input RF sinusoidal signal is converted to a DC output voltage by a rectifier circuitry. The output of the rectifier can vary between low to high DC voltages depending upon the distance of the scavenger from the transmitting base station. The load on the rectifier also defines the output voltage of the system. The DC output voltage is needed to power up devices having a supply voltage compliance range that is typically within +/-5% of the nominal operating voltage.

Since the RF power available for extraction is in the range of micro-watts, the best choice for a voltage regulator is a switched capacitor DC-DC converter [24]. The switched capacitor converter, also called a charge-pump based converter, works on the principle of charge sharing between the input and output capacitors during non-overlapping clock phases. The losses related to this process are due to the non-ideal nature of the switches transferring the charge, the non-ideal capacitors, and the circuitry driving the switches. Several switched capacitor converter designs are available in the literature, but only a few of them are targeted to operating efficiently in ultra-light load conditions. A good converter design should have a high power efficiency across a wide range of DC input voltages. The typical efficiency of the converter for ultra-light loads in range of 20  $\mu$ W is above 60% [25, 29].

#### 2.5.1. Prior work on efficient regulator topologies

The analysis and optimization of components of a switched capacitor DC-DC converter for efficient conversion and output regulation is provided in [29, 30]. The converter conduction losses are modeled as a resistive output impedance which is derived for both the slow switching limit (SSL) [31] and the fast switching limit (FSL) conditions [32]. The optimization of the switching frequency, the size of the transfer capacitance and the on-state switch resistance is carried out for a particular load current drive at fixed output. In [27], a DC-DC converter for a wireless tire pressure sensor load which could regulate the output at load power levels as low as 20  $\mu$ W with an efficiency of above 60% was presented. The primary reason for the lower efficiency at these light-loads is the active circuit power consumption of the converter.

In [25, 26], an output voltage scalable switched capacitor DC-DC converter

capable of driving loads in the range of 10  $\mu$ W to 250  $\mu$ W is presented. An output load voltage is regulated between 300 mV to 1.1 V with a constant input voltage of 1.2 V. The efficiency of the converter in the load range specified above is 75%. The converter operates in the pulse frequency modulation (PFM) mode, which is crucial in achieving high efficiency for a low power system such as an energy scavenger. The efficiency becomes less than 75% at very low load powers of about 4  $\mu$ W, as the leakage in the PFM control circuitry dominates the losses.

The design of a resistor emulated switching converter for RF energy scavenging is presented in [28]. The converter is capable of driving ultra-light loads as low as  $0.5 \ \mu\text{W}$  with an efficiency of 35%. The RF energy is scavenged by a RF rectifying antenna source with an rectification efficiency of 10 %. Hence the overall conversion efficiency of the entire RF harvesting solution is around 7% at received power levels of -18.2 dBm. The inductor based switching converter has a 300  $\mu$ H off chip inductor which is not integrable for the sensor node applications.

#### 2.5.2. Regulation design challenges

Highly efficient power management units in a RF energy scavenging application are needed that address the shortcomings of the previous published work. The power management solution should be capable of driving a light load at a constant DC output at low received power levels. A switched capacitor based converter solution is selected to achieve an integrated on-chip solution. The system and circuit level design of the power management unit is discussed in Chapters 4 and 5, respectively.

# 3. EFFICIENT FAR FIELD RF RECTIFICATION

### **3.1.** Introduction

A system which harvests ambient RF energy would ideally transfer all the incoming input power to the output load. From the analysis of maximum power transfer, half the incoming power is lost across the source impedance of the receiving antenna. Hence the challenge is to deliver the maximum of remaining 50% of the input power to the output load. Building low power harvesters is the key challenge in realizing highly efficient energy scavenging systems.

#### 3.2. Critical Parameters in a RF Energy Scavenging System

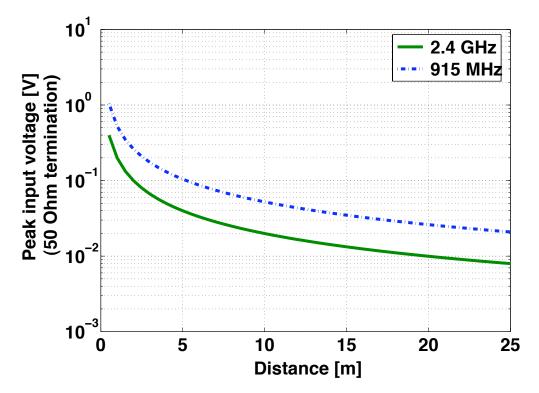

In this work, a RF-DC conversion circuit which converts the 2.4 GHz RF input signal to a DC output voltage under different load conditions is designed. The 2.4 GHz band is chosen over the 915 MHz band because of the feasibility of realizing smaller external on-board components such as the antenna and other passive impedance matching elements. However, the received power decreases by a factor of 6.8  $\left(\frac{2.4 \text{ GHz}}{0.915 \text{ GHz}}\right)^2 \approx 2.6^2$  when operating in the higher frequency band.

The approach taken to realize higher power conversion efficiency is to decrease the number of active components in the design. Fewer active components in the system lowers the active power loss, thereby increasing the efficiency. An increase in the far field power conversion efficiency also implies a lower power-up range or an increase of the sensitivity of the harvester to lower input received power levels.

FIGURE 3.1: Peak voltage across a 50  $\Omega$  terminated system from a 1 W Source.

The incoming signal strength to the harvester depends on a number of factors, the first and foremost being the distance from the transmitting source. From Friis transmission equation, the power received at 5 meters away from the transmitter at 2.4 GHz is 15.8  $\mu$ W. The corresponding peak input sinusoidal amplitude for a 50  $\Omega$ matched system is 40 mV (peak), as shown in Figure 3.1. This low input voltage level seen at the far field distance is below the threshold of the MOSFET diodes in the rectifier.

In practice, other interference phenomena like multi-path fading, reflection and absorption, can also significantly affect the input signal power reaching the harvester at a particular distance from the source. Since, these effects are not modeled in the Friis transmission equation and most other designs have used the free-space assumption for received power calculations, the interference effects are not considered for comparison and evaluation.

#### 3.2.1. Power-up threshold of the Scavenger

The threshold voltage of a typical CMOS diode is about 600 mV [41] and the input power required to overcome this threshold voltage in a typical 50  $\Omega$  input terminated system is given by:

Input Power

$$(P_{in}) = \frac{V_{rms}^2}{R_s} = \frac{V_{pk}^2}{2R_s} = \frac{0.6^2}{100} = 3.6 \text{ mW}$$

(3.1)

where  $R_s$  is the characteristic impedance of the antenna and is typically 50  $\Omega$ .

Hence, the input power required by the energy harvesting system to build any significant voltage at the output of a single stage rectifier voltage is about 5.56 dBm (3.6 mW). This causes a *dead-zone* for the rectifier. The minimum power required to overcome the rectification dead zone is called the *power-up threshold* of the harvester [20].

From Friis equation, to extract 3.6 mW of received power, the scavenger needs to operate as close as 0.5 meters from the source. This distance is considered near field. In the interest of achieving efficient far field operation, the power-up threshold of the system needs to be minimized.

By reducing the threshold voltage of the rectifying diodes, the power-up threshold of the system can be minimized. A technique called as *single-poly floating-gate programming* has been used in [16] to reduce the threshold voltage of the CMOS devices. This technique gives a programmability option for the power-up threshold. The second technique to increase the operating range or scavenger sensitivity is to overcome the power-up threshold of the scavenger for lower input power levels. Passive amplification of the voltage level of the ultra-low power signals reaching the harvester helps in overcoming the threshold. The matching network present at the input of the system, shown in Figure 2.4, provides passive voltage boosting. The following section analyzes the passive amplification of the incoming signal by choosing an appropriate input matching network.

#### **3.2.2.** Passive voltage amplification

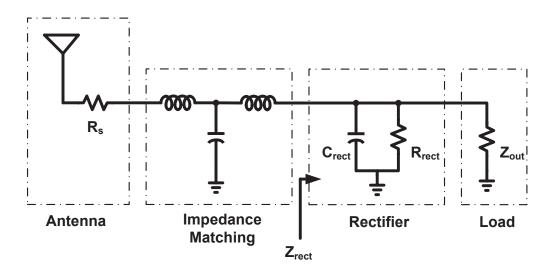

The transmitted RF signal is received by a wireless node in a sensor network with the help of an antenna. The antenna used in a typical sensor network has certain characteristic impedance,  $R_s$ , typically 50  $\Omega$ , and is impedance matched to the rectifier through a passive lossless matching network. The impedance modeling of a RF energy scavenging circuit is shown in the Figure 3.2.

The input impedance of the rectifier circuit,  $Z_{rect}$ , is predominantly capacitive  $(C_{rect})$  and resistive  $(R_{rect})$ .

$$Z_{rect} = R_{rect} \parallel \frac{1}{sC_{rect}} \tag{3.2}$$

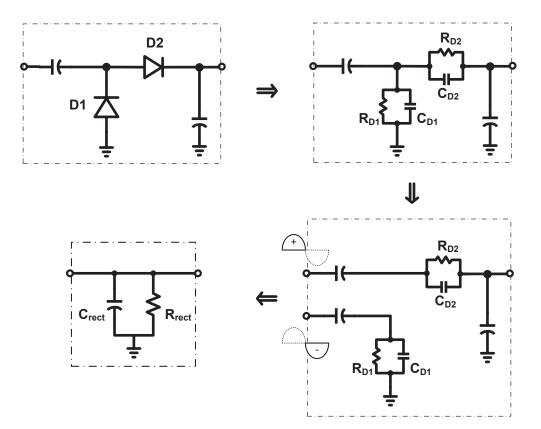

The operation of the full-wave rectifier can be explained by two half cycle operations of the input AC sinusoid as shown in Figure 3.3. During the negative half of the input sinusoid, the diode D1 gets forward biased and the DC voltage across D1 is clamped to  $(V_{inputpk} - V_{th})$ . During the positive half input sinusoid the diode D2 gets forward biased and the output capacitor C2 is charged to  $2(V_{inputpk} - V_{th})$ . The rectified output voltage needs to be regulated over the entire operational range of the harvester.

FIGURE 3.2: Impedance model of the RF energy scavenging circuit.

Cascading a number of rectifier stages affects the input impedance of the rectifier. Consider a full-wave rectifier model built from a simple diode model and, the input bypass and output storage capacitors. The addition of an extra rectifier stage decreases the reactive component by adding capacitances in parallel and reduces the resistive component by adding resistances in parallel to the existing network.

The passive impedance transformation network built using inductors and capacitors has a particular quality factor, Q, associated with it. At resonance, the resistive and capacitive components of the rectifier network can be transformed into a series  $R_{sr}$  and  $C_{sr}$  network, as shown in Figure 3.4.

At resonance [15],

$$R_{sr} = R_{rect} \cdot \left(\frac{1}{1+Q_{rect}^2}\right) \tag{3.3}$$

$$C_{sr} = C_{rect} \left( \frac{1 + Q_{rect}^2}{Q_{rect}^2} \right) \tag{3.4}$$

FIGURE 3.3: Impedance modeling of the full-wave rectifier.

where  $Q_{rect}$  is the quality factor of the rectifier circuit given by,

$$Q_{rect} = \omega_0 \cdot R_{rect} \cdot C_{rect} \tag{3.5}$$

with  $\omega_0$  being the resonant frequency of the matching network.

The model of a passive voltage amplification network is shown in Figure 3.5. When the received input signal strength is very low, the input voltage amplitude of the signal,  $V_1$ , is very low. The presence of the matching network can provide a passive input voltage amplification to  $V_1$  with the loaded Q factor of the rectifier. The amplified input signal can overcome the threshold voltage of the MOSFET

FIGURE 3.4: Parallel to series transformation of the full-wave rectifier impedance model.

FIGURE 3.5: Model of the passive voltage amplification network.

diodes in the full-wave rectifier. The matching network being lossless also provides the rectifier circuit with a proportionally reduced drive current, by the same factor  $Q_{rect}$ . The analysis for passive voltage amplification follows. At resonance,

$$Z_s = R_s \tag{3.6}$$

$$V_2 = 0.5 * V_1 \tag{3.7}$$

The power dissipated across the antenna characteristic impedance  $R_s$  is equal to the power dissipated across the only resistive component in the rectifier model,  $R_{sr}$ . The relationship between the voltages across  $R_s$  and  $R_{sr}$  is given by:

$$\frac{V_{Rsr}}{V_2} = \sqrt{\frac{R_{sr}}{R_s}} \tag{3.8}$$

At resonance, the voltage across the effective capacitance  $C_{sr}$  is  $Q_{sr}$  times the voltage across the effective resistance  $R_{sr}$ . Thus, the voltage at the rectifier input terminals  $V_{IN}$  is given by,

$$|V_{IN}| = |V_{Csr} + V_{Rsr}| \approx V_{Rsr}.Q_{sr}$$

$$(3.9)$$

Substituting (3.8) in (3.9),

Passive Voltage Gain:

$$\frac{V_{IN}}{V_2} = Q_{sr} \sqrt{\frac{R_{sr}}{R_s}}$$

(3.10)

The above relationship between the passive voltage amplification and the Q factor of the rectifier, explains the significance of a high-Q matching network in energy harvesting applications. The amplification helps in increasing the sensitivity of the scavenger to lower received input power levels.

Under loaded conditions, the rectifier MOSFET diodes need to drive load currents at a fixed output voltage with the available incoming input power. Though the input voltage of the rectifier is amplified, the reduced input current drive to the rectifier is incapable of meeting the load current requirements and hence yields a lower rectified output DC voltage when loaded.

FIGURE 3.6: Block diagram showing the received, available and output power in the system.

#### 3.2.3. Power Conversion Efficiency of the Scavenger

A critical metric which defines the performance of an energy harvesting circuit is the *power conversion efficiency* (*PCE*). The conversion efficiency is defined as the ratio of output power available for driving the load, to the input power available at the rectifier input terminals. Figure 3.6 shows the components in an energy harvesting system and the power available at the input and output terminals.

Power Conversion Efficiency (PCE) =

$$\frac{P_o}{P_a}$$

(3.11)

where  $P_o$  and  $P_a$  are the output power driving the load and the power available at the rectifier input terminals, respectively.

According to maximum power transfer, under ideal input matched conditions, only one half of the input received power  $(P_r)$  is available at the rectifier input terminals for harvesting. The *power harvesting efficiency (PHE)* is defined as the ratio of input received power to the output harvested power.

Power Harvesting Efficiency (PHE) =

$$\frac{P_o}{P_r}$$

(3.12)

where  $P_r$  is the power received at the antenna input terminals.

Under matched input conditions, the relation between PCE and PHE is,

$$PHE = 0.5 * PCE \tag{3.13}$$

In a conventional RF circuit, such as a low noise amplifier, the input matching is not dependent on the strength of the input signal. In a RF energy scavenging system, the resistive component of the rectifier,  $R_{rect}$ , reduces as the input signal level increases. The  $R_{rect}$  is a function of the diode on-resistance, which decreases with the increase in input current drive at higher power levels. Therefore, the input impedance,  $Z_{rect}$ , depends on the input signal level. However, in this work the problem is simplified by assuming a constant input impedance. This is a reasonable approximation at ultra-low input power levels closer to the power-up threshold of the harvester.

## 3.3. Single-Poly Floating-Gate Technique

The threshold voltage of the NMOS and the PMOS devices in the 180 nm process are 450 mV and 550 mV, respectively. In order to reduce the threshold voltage of these devices, several techniques can be used which require special processing in a standard CMOS process. The concept of achieving low threshold devices is derived from the EEPROM cells, where lower threshold voltages are required to

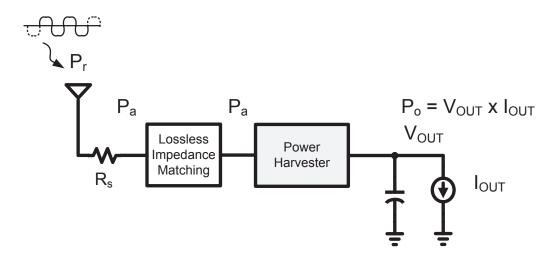

FIGURE 3.7: Single-poly floating-gate programming of a NMOS device.

have higher data retention over time. This is typically achieved by using special multi-polysilicon CMOS processes.

Earlier work on EEPROM by Ohsaki in [16] discusses the development of a single-poly pure CMOS *(SIPPOS)* cell, with options of high voltage electron tunneling on the polysilicon gates to reduce the threshold voltage of the MOS device. This tunneling process, referred to as Fowler-Nordheim tunneling, helps in injecting charge on the high-impedance gate oxide of the MOS device. The injected gate charge reduces the effective threshold voltage required to turn on the MOSFET device.

Figure 3.7 shows the structural arrangement of a typical NMOS SIPPOS cell. It consists of a NMOS and PMOS transistor with a common gate terminal, which is the *floating gate* of this SIPPOS cell. The *control gate* is a combination of the p+ diffusion and the inversion layer under the PMOS gate. Depending upon the gate capacitance ratio  $\frac{C_P}{C_N}$ , a high voltage pulse applied on this control node writes or erases charges on the floating gate of the cell.

#### 3.3.1. Fowler Nordheim programming

The NMOS gate tunneling is achieved by programming the gate and the n+ diffusion. The n+ regions are grounded and the high voltage pulse  $V_{prog}$  is applied to the control gate. The gate capacitance ratio should be higher than 3.0 to induce tunneling [16]. A higher gate capacitance ratio gives more threshold voltage shift. The amplitude and duration of  $V_{prog}$  is critical to achieve tunneling. Typical amplitudes and durations vary between 9-15 volts and 100 ms, respectively.

The charge retentivity rate of the floating gate in a SIPPOS cell is lower when compared to the multi-polysilicon floating gate technique. A single-poly programmed cell holds the tunneled charge for 31 days [36], whereas the conventional multi-polysilicon floating gate technique retains the charge for ten years or more. The presence of both n-channel and p-channel devices to realize a floating gate MOS transistor makes the single-poly floating gate programming technique more area intensive.

Floating gate programming reduces the threshold voltage of the CMOS diodes used in the rectifiers. The threshold voltage reduction ensures lower power-up threshold requirements of the harvester and increases the overall conversion efficiency of the rectifier.

### 3.4. Analysis and Optimization of a N-Stage Rectifier

The top level system diagram in Figure 2.4, shows the input AC-DC rectification is successfully carried out by a N-stage rectifier. The number of rectifier stages affects the power conversion efficiency of the RF energy scavenging system. The maximum achievable rectified output voltage also depends on the number of rectifier stages. Optimization techniques for the N-stage rectifier involve maximizing both the rectifier conversion efficiency and the rectifier output voltage.

#### 3.4.1. Optimization for maximizing the rectified DC output voltage

Cascading a number of rectifier stages in series provides a higher output voltage, provided the scavenger system receives unconstrained levels of input power. The received RF signal power level is limited by the operational distance from the transmitter. To maximize the DC output voltage in a RF rectification block, the output power needs to be maximized. The analysis is given by (3.14) and (3.15).

If  $P_a$  is the power available at the rectifier input terminals and  $P_l$  is the power loss in a single stage of a N-Stage rectifier, then the output power of the rectifier  $P_{RECT}$ is given by:

$$P_{RECT} = P_a - N.P_l = \frac{V_{RECT}^2}{R_{oRECT}}$$

$$(3.14)$$

where  $V_{RECT}$  and  $R_{oRECT}$  are the output voltage and resistive load of the rectifier, respectively.

For a fixed resistive load at the output,

$$P_{RECT} \propto V_{RECT}^2 \tag{3.15}$$

From (3.14) it follows that reducing the number of rectifying stages (N), increases the rectifier output power ( $P_{RECT}$ ). Hence, a single stage rectifier gives the maximum output power across a fixed resistive load. From (3.15) it can be concluded that the maximum output power produces the maximum output voltage in a RF rectification system. The upper bound on the rectified output voltage is set by the rectifier configuration. The most commonly used rectifier structure is a voltage doubler configuration, where the output voltage is given by,

$$V_{out} = 2 * (V_{inputpk} - V_{th}) \tag{3.16}$$

where  $V_{th}$  is the threshold voltage of the rectifying diodes, and  $V_{inputpk}$  is the peak voltage at the input of the rectifier.

#### 3.4.2. Optimization for maximizing the conversion efficiency

The power conversion efficiency of the rectifier  $(PCE_{RECT})$  is defined as the ratio of the rectifier output power  $(P_{RECT})$  to the power available at the rectifier input terminals  $(P_a)$ . Selecting the number of stages for achieving maximum rectifier power conversion efficiency is done by relating efficiency to the number of rectifier stages (N).

$$PCE_{RECT} = \frac{P_{RECT}}{P_a} = 1 - N.\frac{P_l}{P_a}$$

(3.17)

The expression for  $PCE_{RECT}$  shows that selecting a single stage rectifier helps achieving maximum power rectification efficiency.

The forward on-channel resistance  $(R_{on})$  of the MOSFET diodes and the diode reverse leakage component  $(I_{rl})$  are the primary sources of power loss in a full-wave rectifier. Hence, the smaller the number of active components used in the design the less is the power loss in the rectification system.

#### 3.4.3. Optimization for maximizing the passive voltage amplification

Another reason for selecting a single stage rectifier is to maximize the sensitivity of the scavenger to low amplitude input received signals. As the number of rectifier stages increases, the effective capacitance  $C_{rect}$  increases and the effective resistance  $R_{rect}$  decreases, as shown in the Figure 3.3. The maximum passive voltage amplification is related to the number of stages as given in (3.18) through (3.20).

Passive Voltage Gain =

$$Q_{sr}\sqrt{\frac{R_{sr}}{R_s}}$$

(3.18)

$$=\frac{1}{\omega_0.C_{sr}.\sqrt{R_{sr}}.\sqrt{R_s}}\tag{3.19}$$

$$\approx \frac{\sqrt{R_{rect}}}{\sqrt{R_s}} \tag{3.20}$$

An increase in the number of stages decreases  $R_{rect}$ , thereby reducing the maximum achievable passive voltage amplification. The passive voltage gain is proportional to  $\sqrt{R_{rect}}$  and is maximized by selecting the least number (N=1) of rectifier stages.

The quality factor of the matching network is determined by the ratio of the input impedance and the source impedance of the antenna. The quality factor for the single stage rectifier circuit is calculated to be around 30. The value closely matches with the maximum achievable quality factor for the 2.45 GHz band, which is given by the ratio of center frequency to the bandwidth occupied by the 2.45 GHz spectrum between 2.4 GHz and 2.5 GHz,  $\frac{2.45 GHz}{100 MHz} = 24.5$ . The component Q of the inductors and capacitors which realize the matching network is typically higher than 50. Passive components with self-resonant frequency above 3 GHz are chosen for the design. Thus the maximum achievable Q of the system for the single stage is not limited by the quality of the passive elements used in the matching.

The analysis and optimization of the N-stage rectification block in a RF energy scavenging system shows that to achieve a high rectified DC output voltage, maximum conversion efficiency, and increased harvester sensitivity, a single stage rectifier is desirable.

FIGURE 3.8: PMOS rectifier design in the 180 nm CMOS process.

## 3.4.4. Rectifier design

The design of a full-wave CMOS rectifier is implemented in a 180 nm process. The PMOS rectifier design with floating gate transistors is shown in Figure 3.8. The PMOS device is chosen for a MOS diode over a NMOS device because it reduces the number of body diodes connected to the high frequency nodes in the design. The junction capacitance of the body diodes provides a capacitive leakage component at higher frequencies. This loss component is less than 2% of the total power lost in rectification and is considered negligible.

The floating gate programming technique discussed in Section 3.5, helps in reducing the threshold voltage for the PMOS diodes in the rectifier to about 50 mV [36]. The lower threshold voltage devices have reduced turn-on voltages for

rectification and help increase the operating range of the RF energy harvester. Ultralight load circuits which operate on a lower supply voltage ( $\leq 500 \text{ mV}$ ) [37] can be operated by the RF energy harvester at the far-field (about 7 meters in free space).

Thick oxide devices with a higher gate voltage breakdown are chosen for the design. The minimum channel length of these devices is 360 nm. The device sizing of (20  $\mu$ m/0.36  $\mu$ m) is chosen for the MOS diode transistors (D1, D2) and (25  $\mu$ m/30  $\mu$ m) is chosen for the input (C1) and output (C2) PMOS capacitors. The devices are sized considering a fixed light-load current representing the far-field operation. The effective channel resistance,  $r_{ds}$ , of the MOS device is minimized, assuming a minimum dropout voltage across the diode transistors. The reduced channel resistance helps in maximizing the rectified output voltage ( $V_{RECT}$ ) of the rectifier configuration.

## 4. DESIGN OF THE POWER MANAGEMENT UNIT

## 4.1. Introduction

The design of an efficient RF energy scavenging solution poses two different design challenges. The first step is to efficiently convert the incoming input RF signal into a DC voltage. The previous chapter described the optimization techniques required to achieve energy efficient rectification using a single-stage single-poly floating gate programmed full-wave PMOS rectifier.

The challenge in providing a stable supply voltage to the devices operating on the harvested DC power is discussed and solutions are presented in this chapter. A *power management circuit* which regulates the varying rectifier output voltage to a constant DC supply is necessary. Building an efficient power management unit is the key to achieving an efficient energy scavenging circuit.

## 4.2. Linear Regulator vs Switching Converter

There are two types of voltage regulation schemes to ensure a constant DC supply from a variable DC input voltage: linear regulation and switching regulation. The linear regulation scheme regulates voltage with a high supply noise sensitivity. The switching regulation scheme maintains the output voltage with high power efficiency.

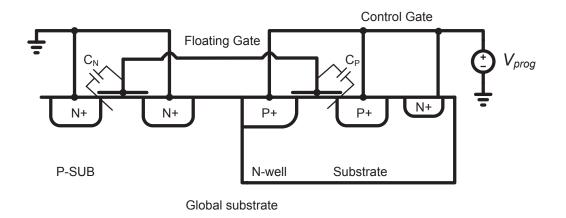

#### 4.2.1. Linear regulator

The simplest available DC-DC converter is a linear voltage regulator, which regulates any input voltage higher than the required output voltage to a targeted stable DC output voltage. The voltage difference between the input and the output, referred to as the *dropout voltage*, is dissipated as heat across a pass transistor in the output signal path as shown in Figure 4.1(a). This internal power loss makes the linear regulator the most inefficient power converter when used in a system where the required output voltage is significantly lower than the input voltage. The voltage gain of the linear regulator,  $VG_{LDO}$  is given by,

$$VG_{LDO} = \frac{V_{out}}{V_{in}} = \frac{V_{out}}{V_{out} + V_{do}}$$

$$< 1 \Longrightarrow LDO \ always \ operates \ in \ step-down \ mode$$

$$(4.1)$$

where  $V_{out}$ ,  $V_{in}$  and  $V_{do}$  are the output, input and dropout voltages of the converter, respectively.

If  $I_{out}$  is the output load current and  $I_q$  is the internal circuitry loss, then the efficiency of the LDO is given as,

$$LDO \ Efficiency: \eta_{LDO} = \frac{P_{out}}{P_{in}} = \frac{V_{out}.I_{out}}{V_{in}.(I_{out} + I_q)}$$

(4.2)

Assuming negligible losses in the regulator circuitry  $(I_q)$ ,

$$\eta_{LDO} \approx \frac{V_{out}}{V_{in}} \tag{4.3}$$

Equation (4.3) suggests that linear regulators are power efficient only when the output voltage is close to the input voltage. The efficiency of the LDO peaks

FIGURE 4.1: Energy scavenger with the power management unit. (a) Linear LDO regulator. (b) Switching DC-DC regulator.

only when the dropout voltage is small. Earlier work done on energy harvesting using linear regulators in [36] suffers from low overall conversion efficiencies because of the larger difference between  $V_{in}$  and  $V_{out}$ .

#### 4.2.2. Switching regulators - DC-DC converters

The second category of power converters are called *switching converters*. The output voltage is regulated by modulating the input received power levels, across varying loads. To maintain the high power efficiency at a fixed output voltage, the effective input impedance of the switching converter changes with respect to the incoming input power levels as shown in Figure 4.1(b). Another desirable feature with the switching converters is the input voltage to the converter can be higher or lower than the required output voltage. In other words, the switching regulators are capable of operating in the *step-up (boost)* or *step-down (buck)* modes. The voltage gain of the switching converter,  $VG_{DCDC}$  is given by,

$$VG_{DCDC} = \frac{V_{out}}{V_{in}} \tag{4.4}$$

$$< 1: if V_{in} > V_{out} \Longrightarrow buck mode$$

(4.5)

$$> 1: if V_{in} < V_{out} \Longrightarrow boost mode$$

If  $I_{mod}$  is the average frequency modulated input current from the rectified and stored output, then the efficiency of the switching converter is given as,

$$DC\text{-}DC \ Efficiency: \eta_{DCDC} = \frac{P_{out}}{P_{in}} \approx \frac{V_{out}.I_{out}}{V_{in}.I_{mod}}$$

(4.6)

When the system receives low input power, the rectifier output voltage is lower than the required output voltage. The boost mode of operation in the switching converter helps in pumping up this low rectified voltage to a higher output regulated voltage. During this mode the input charge is more frequently transferred to the output capacitor, thereby leading to a higher input current drive  $(I_{mod})$  from the rectified and stored output. This increased  $I_{mod}$  leads to a higher conduction loss in the boost mode.

The high power efficiency and the boost mode operation in switching converters make it an ideal choice for power management units in energy harvesting solutions. The next section details the type of switching converter chosen for the RF energy scavenging circuitry.

# 4.3. Inductor Based vs Switched Capacitor Based Switching Converter

Switching converters can be widely categorized into inductive based and capacitive based converters. The inductive based converters regulate the output voltage by low pass filtering a pulse width modulated input signal with a LC network. Controlling the charge transfer between the capacitors helps in regulating the output voltage in switched capacitor based converters.

#### 4.3.1. Inductor based switching converters

The inductor based converter solution operates on the input voltage using a *Pulse Width Modulation (PWM)* technique to regulate the output voltage, is shown in Figure 4.2.

The voltage boosting operation of the inductive converter can be explained in two phases; the charging phase ( $\phi_1$ ) and the discharge phase ( $\phi_2$ ). During the charging phase, a DC input voltage causes the current through the inductor, L, to increase linearly with time. During the discharge phase the inductor current charges the output capacitor, C, until the steady state is reached. At steady state, the output voltage is given by  $V_{OUT} = \frac{V_{IN}}{1-D}$ , where D is the duty cycle of the PWM control signal.

The converter is capable of efficiently driving load currents in the range of a few hundred micro-amperes to amperes. The most common application is in high current LED flash drivers. The inductor size required to realize a highly efficient LC based converter at light loads is too large (typically in the range of 100 nH to 1 uH) to have an integrated on-chip solution.

#### 4.3.2. Switched capacitor based switching converters

The switched capacitor based solution, operates on the principle of charge transfer between capacitors to build the required output voltage. The output is regulated using a *Pulse Frequency Modulation (PFM)* technique, which helps in maintaining the high efficiency over a wide range of input voltages. This converter

FIGURE 4.2: Inductor based switching converter.

FIGURE 4.3: Schematic of a buck-mode switched capacitor converter.

is mainly used in applications requiring a lower load current which is within the range of tens of micro-amperes to a few hundred milli-amperes.

Typically, RF energy scavenging solutions, harvest power in micro-watts and a switched capacitor based switching converter is chosen for the micro-power harvesting. Another advantage of using a capacitor based solution is on-chip integration. Furthermore, electro-magnetic interference (EMI) issues are not as important as in inductor based solutions.

# 4.4. Analysis and Optimization of Switched Capacitor Buck-Boost Converter

The switched capacitor DC-DC converter provides an output voltage which can be lower or higher than the input rectified voltage depending on the selected conversion ratio setting. The input voltage conversion range can be extended by having many different conversion ratios depending on the number of capacitors and the number of switches available in the converter. Maksimovic's work in [31, 33] identifies the maximum conversion ratio feasible with a given number of capacitors in a converter topology.

## 4.4.1. Choosing the right SC based topology

Five different networks are considered for realizing a switched capacitor converter: Ladder, Dickson, Fibonacci, Doubler and the Series-Parallel network. Extensive analysis and comparison of these different topologies is done in [29]. An optimization technique using cost metrics involving optimal area and total capacitively stored energy is also presented. In this work, the series-parallel topology is chosen among the five networks, primarily due to the simpler structure for realizing various non-integer conversion ratios for DC-DC conversion. The series-parallel network has the best metric with the optimization constrained on the total available energy storage in the system. This metric suggests that the capacitors are more efficiently utilized in a series-parallel network than any other network-based converters.

FIGURE 4.4: General model of a switching converter with losses modeled in  $R_{out}$ .

#### 4.4.2. Losses in the switched capacitor DC-DC converter

The model of the converter with all the losses modeled as a resistive component in  $R_{out}$  is shown in Figure 4.4 [33]. An ideal transformer represents the voltage conversion gain,  $V_g$ , given by the turns ratio  $\frac{n}{m}$ . The different losses in switched capacitor DC-DC converters are discussed below.

#### 4.4.2.1 Conduction loss

The switches in the switched capacitor converter are non-ideal with a finite on-resistance. The on-resistance leads to conduction losses in the switch network. The conduction loss  $(P_{cond})$  is also dependent on the output load current  $(I_L)$  of the converter.

In an ideal dc-dc converter with zero switch on-resistance, the expected output voltage under loaded conditions is denoted as  $V_{ideal}$ . In the presence of non-ideal switches, the output voltage with loading becomes  $V_{OUT}$ . The difference between both the output voltage conditions is given by,

$$\delta V_{OUT} = V_{OUT} - V_{ideal} \tag{4.7}$$

In the interest of simplifying the conduction loss analysis, the resistive output impedance,  $R_{out}$ , is considered to account for the resistive conduction losses. Hence the conduction loss is given by,

$$P_{cond} = \delta V_{OUT} I_L \tag{4.8}$$

where  $\delta V_{OUT}$  is the effective voltage drop across the resistance  $R_{out}$ . From the relation in (4.8), for a selected conversion gain, the conduction loss is the least when the loaded output voltage  $(V_{OUT})$  is close to the corresponding ideal switch loaded output voltage  $(V_{ideal})$ .

### 4.4.2.2 Switching loss

The switches in the switching converter are controlled by the non-overlapping clock phases. The number of switches being switched simultaneously depends on the selected voltage gain configuration  $(V_g)$ . The effective gate capacitance driven by the non-overlapping clocks from the gate driver circuit increases linearly with the number of active switches (N). Figure 4.5 shows a gate driver block driving an effective gate capacitance  $(C_{g_{-sw}} = N.C_{gg})$  of the switches.

The switching losses or gate-driving losses in the converter are given by,

$$P_{swit} = N.C_{gg}.V_{RECT}^2.f_{sw}$$

$$\tag{4.9}$$

where  $C_{gg}$  is the effective gate capacitance offered by a single switch,  $f_{sw}$  is the effective switching frequency of the circuit and  $V_{RECT}$  is the rectified DC output voltage, supplying power to the gate driver circuit.

The switching loss,  $P_{swit}$ , is linearly proportional to the effective frequency  $(f_{sw})$  of the circuit. The number of active switches, N, depends on the gain con-

FIGURE 4.5: Gate driver block driving the gate capacitances.

figuration selected. The switching loss also increases quadratically as the output voltage of the rectifier  $(V_{RECT})$  increases.

## 4.4.2.3 Bottom-plate capacitance loss