#### AN ABSTRACT OF THE DISSERTATION OF

<u>Skyler Weaver</u> for the degree of <u>Doctor of Philosophy</u> in <u>Electrical and Computer Engineering</u> presented on <u>September 15, 2010</u>. Title: Automated Synthesis of Analog to Digital Conversion.

Abstract approved: \_\_\_\_\_

Un-Ku Moon

This thesis describes circuit architectures and techniques that facilitate the automatic synthesis and fabrication of analog-to-digital converters (ADCs). Since automated synthesis already exists for digital circuits and is part of the digital circuit design flow, this work demonstrates the feasibility of ADC synthesis with little or no modification to presently existing software tools. In the end, it is demonstrated that an ADC can be implemented from synthesizable Verilog code, making it highly portable from one process technology to another. Moreover, by demonstrating how to use existing standard digital gates to generate analog functions (e.g. an analog comparator), the physical implementation of an ADC can be as automatic and straightforward as a standard digital circuit.

<sup>©</sup>Copyright by Skyler Weaver September 15, 2010 All Rights Reserved

## Automated Synthesis of Analog to Digital Conversion

by

Skyler Weaver

#### A DISSERTATION

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented September 15, 2010 Commencement June 2011 Doctor of Philosophy dissertation of <u>Skyler Weaver</u> presented on September 15, 2010

APPROVED:

Major Professor, representing Electrical and Computer Engineering

Director of the School of Electrical Engineering and Computer Science

Dean of the Graduate School

I understand that my dissertation will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my dissertation to any reader upon request.

Skyler Weaver, Author

#### ACKNOWLEDGMENTS

First of all, I would like to thank Professor Un-Ku Moon for being my advisor and helping me become a circuit master. His guidance and wisdom in the realm of analog circuits and life in general is forever appreciated. As I embark into my future career, it feels good to know that I have been equipped with the tools I will need on my journey, and I acknowledge that it was Dr. Moon that helped me discover my own stoneshiner.

I would also like to thank Professors Pavan Kumar Hanumolu, Karti Mayaram, and Gabor Temes for their advice and instruction. Their expert council have kept me thinking in the right direction regarding research. My success is in part their responsibility.

My fellow group members have all been good friends and colleagues, especially Benjamin Hershberg, Peter Kurahashi, and Nima Maghari. Being able to bounce ideas off each other and share a laugh has been a wonderful support. Our lunchtime brainstorming sessions were always enjoyable, even if we spent most of our time coming up with clever acronyms and ways to get to the moon.

My parents and family have always given me their love and have always supported and encouraged me in my passion for knowledge. I know they are proud of me for adding this work to human knowledge and unlocking some of the secrets of the Universe.

Lastly, I am grateful for Shauna, my wife. Her unquestioning support and love is always there: whether bringing me snacks and energy drinks for late nights in the lab, or accompanying me on transcontinental trips to conferences. I am truly lucky to have found someone whose companionship I cherish and whom I love so much.

## TABLE OF CONTENTS

Page

|   |      |                  | ———————————————————————————————————————                                                                                                                   |                            |

|---|------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 1 | INTF | RODU             | CTION                                                                                                                                                     | 1                          |

| 2 |      |                  | CIRCUIT SYNTHESIS USING STANDARD DIGITAL SYN-<br>DOLS                                                                                                     | 3                          |

|   | 2.1  | Using            | Custom Analog Cells                                                                                                                                       | 6                          |

|   | 2.2  | Using            | Standard Cells for Analog Circuits                                                                                                                        | 9                          |

|   | 2.3  | Summ             | nary                                                                                                                                                      | 13                         |

| 3 | STO  | CHAST            | ГІС FLASH ADC                                                                                                                                             | 14                         |

|   | 3.1  | Statis           | tical Analysis of a Uniform Distribution Stochastic Flash ADC                                                                                             | 17                         |

|   |      | $3.1.1 \\ 3.1.2$ | Number of Comparators Required<br>Calculating ENOB from SNDR of a Sine-Wave Test                                                                          | 18<br>25                   |

|   | 3.2  | Many             | -Group Stochastic Flash ADC                                                                                                                               | 30                         |

|   | 3.3  | Two-0            | Group Stochastic Flash ADC                                                                                                                                | 33                         |

|   |      | 3.3.1<br>3.3.2   | PDF FoldingTwo-Group Prototype IC3.3.2.1 Implementation details3.3.2.2 Measurement Results3.3.2.3 Summary                                                 | 37<br>42<br>42<br>47<br>51 |

|   | 3.4  | Single           | -Group Stochastic Flash ADC                                                                                                                               | 51                         |

|   |      |                  | Gaussian Distribution Mapped to a Uniform Distribution .Single-Group Prototype IC3.4.2.1 Implementation Details3.4.2.2 Measurement Results3.4.2.3 Summary | 52<br>55<br>55<br>58<br>62 |

| 4 | DOM  | IINO L           | LOGIC BASED ADC                                                                                                                                           | 65                         |

## TABLE OF CONTENTS (Continued)

Page

|    | 4.1  | Principle of Operation                                                        | 65 |

|----|------|-------------------------------------------------------------------------------|----|

|    | 4.2  | Implementation Details                                                        | 66 |

|    | 4.3  | Measurement Results                                                           | 71 |

|    | 4.4  | Summary                                                                       | 72 |

| 5  |      | TALLY IMPLEMENTED NAND-ONLY SUCCESSIVE APPROX-<br>TION REGISTER (DINOSAR) ADC | 75 |

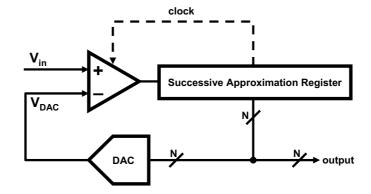

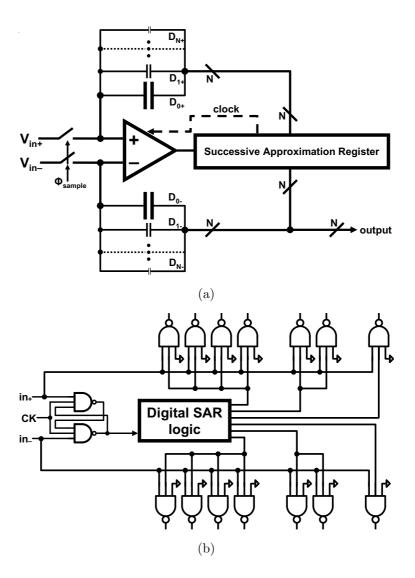

|    | 5.1  | Principle of Operation                                                        | 76 |

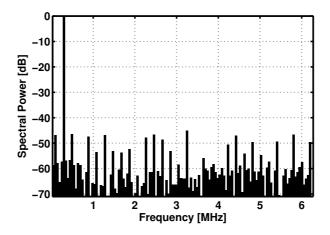

|    | 5.2  | Simulation Results                                                            | 78 |

|    | 5.3  | Summary                                                                       | 79 |

| 6  | CON  | CLUSION                                                                       | 81 |

| BI | BLIO | GRAPHY                                                                        | 83 |

## LIST OF FIGURES

| Fig | ure                                                                                                                                                                                                                                                                   | Page |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1 | The digital circuit synthesis design flow                                                                                                                                                                                                                             | 4    |

| 2.2 | RTL Verilog code.                                                                                                                                                                                                                                                     | 5    |

| 2.3 | Gate-level Verilog code of two functionally equivalent digital circuits.                                                                                                                                                                                              |      |

| 2.4 | Example instantiation of a custom cell 'customCell' into a Verilog module 'myCell.'                                                                                                                                                                                   |      |

| 2.5 | A standard digital CMOS NAND3 gate and its internal transistor schematic.                                                                                                                                                                                             |      |

| 2.6 | a) An analog comparator made from standard digital NAND3 cells. b) A analog voltage controlled delay cell with asynchronous reset using a standard digital NAND3 cell. c) A standard digital NAND3 cell used as a DAC cell.                                           | 5    |

| 2.7 | a) Verilog module 'comparator' which implements a NAND3 based comparator (lines 6-11). b) Gate-level schematic representation of the code                                                                                                                             | L    |

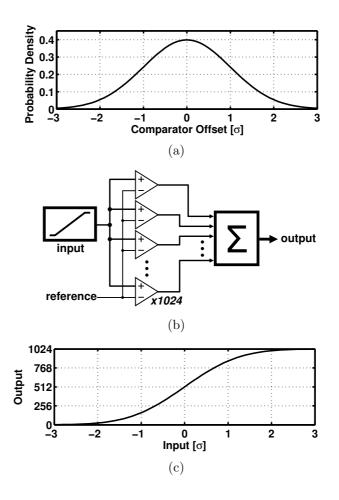

| 3.1 | a) Probability density function of comparator offset in terms of standard deviation, $\sigma$ , assuming Gaussian distribution. b) This is the basic stochastic flash ADC. c) Idealized output of the basic stochastic flash ADC with ramp input in terms of $\sigma$ | 3    |

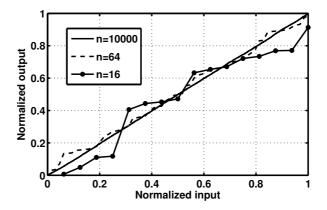

| 3.2 | Normalized transfer function of a basic stochastic flash ADC with<br>uniformly distributed comparator offsets for three cases where $n$<br>is the number of comparators                                                                                               | ,    |

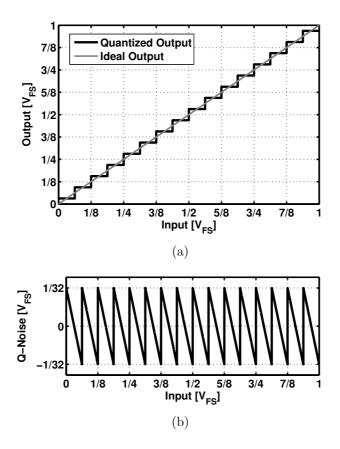

| 3.3 | a) An ideal 4-bit ideal ADC. b) The quantization noise voltage<br>of an ideal 4-bit ADC, where quantization noise is the input sub-<br>tracted from the output.                                                                                                       |      |

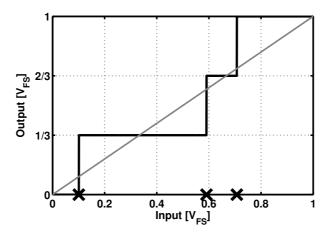

| 3.4 | A 3-comparator ADC with random comparator placement. The marks along the x-axis represent the comparator thresholds                                                                                                                                                   |      |

| 3.5 | Graphical representation of a binomial random variable $k$ – the number of $n$ comparators between 0 and $v$                                                                                                                                                          |      |

## Figure

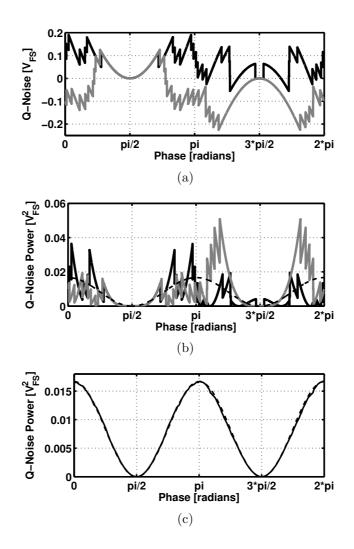

| 3.6  | a) The quantization noise of two random 15-comparator ADCs with uniformly distributed comparator thresholds $(1LSB=1/15)$ .<br>b) The square of quantization noise of the same two random ADCs. The dashed line is a plot of (3.13). c) The square of quantization noise of 5000 random ADCs averaged together. The dashed line is a plot of (3.13)                                                                                           | 23 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.7  | Effective number of bits as a function of number of comparators, where comparator thresholds are uniformly distributed across the input range.                                                                                                                                                                                                                                                                                                | 24 |

| 3.8  | a) A full-scale sine-wave input. b) The associated quantization noise voltage for an ideal 4-bit ADC.                                                                                                                                                                                                                                                                                                                                         | 26 |

| 3.9  | a) The quantization noise due to the sine-wave input in Fig. 3.8(a) for the same two random ADCs as in Fig. 3.6. b) The square of quantization noise of the same two random ADCs. The dashed line is a plot of (3.13) with $v = (1/2)\sin(x) + 1/2$ and $x = 02\pi$ .<br>c) The square of quantization noise of 5000 random ADCs averaged together. The dashed line is again a plot of (3.13) with $v = (1/2)\sin(x) + 1/2$ and $x = 02\pi$ . | 29 |

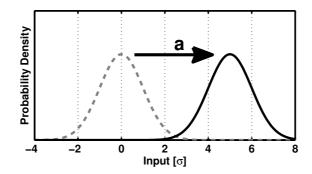

| 3.10 | Providing a global reference $a$ to a group of comparators effec-<br>tively shifts the PDF to be centered about $a$ $(a = 5\sigma)$                                                                                                                                                                                                                                                                                                           | 31 |

| 3.11 | Spacing many Gaussian distributions by $1.5\sigma$ creates an effective uniform PDF.                                                                                                                                                                                                                                                                                                                                                          | 31 |

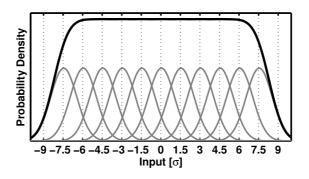

| 3.12 | Spacing 11 Gaussian distributions by $1\sigma$ , $1.5\sigma$ , and $2\sigma$ , (as in Fig. 3.11) is a trade-off between signal range and a ripple on the effective uniform PDF                                                                                                                                                                                                                                                                | 32 |

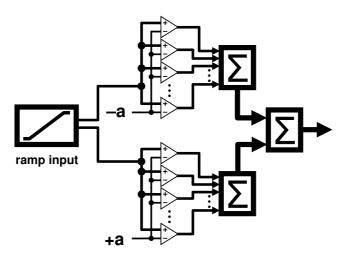

| 3.13 | A two-group stochastic flash ADC. One group is given an offset of $+a$ , the other $-a$ .                                                                                                                                                                                                                                                                                                                                                     | 33 |

| 3.14 | <ul><li>a) The resulting overall transfer function for a two-group stochastic flash ADC. (the circles correspond to the mean of each PDF).</li><li>b) The transfer function of each group before being combined into the overall transfer function. c) The resulting PDFs of each comparator group after global offset is applied</li></ul>                                                                                                   | 34 |

| Figu | ire                                                                                                                                                                                                                               | Page   |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

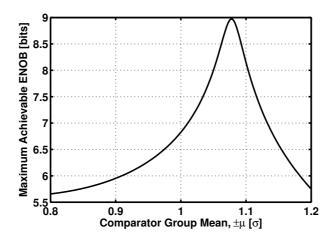

|      | Maximum achievable linearity as number of bits for a two-group<br>stochastic flash ADC with comparator group offsets of $\pm a$ and<br>the input is also set to the range $\pm a$                                                 | 1      |

|      | This is the combined probability density function (PDF) of com-<br>parator offset for a two-group stochastic flash ADC. Over half o<br>the comparators fall outside of the virtual uniform distribution<br>and are not used.      | f      |

|      | For clarity, only the left PDF is shown. The two circles indicate<br>two random comparator offsets that are equal in magnitude but<br>have opposite polarity                                                                      | t      |

|      | This circuit implements the comparator offset polarity inversion<br>seen in Fig. 3.17. The circuit causes the analog inputs to be<br>swapped and the digital output to be inverted each clock cycle<br>until "locked."            | е      |

|      | a) A histogram of 512 Gaussian comparator offsets. b) A histogram of the same 512 offsets after PDF folding has been ap plied. c) A histogram of the 512 offsets after PDF folding has been applied but in the presence of noise. | -<br>S |

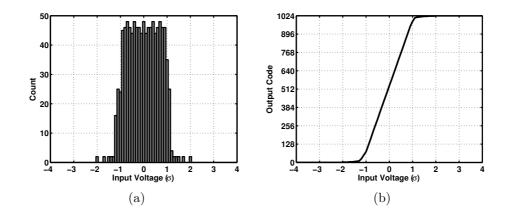

|      | a) A histogram of 1024 Gaussian comparator offsets in two groups<br>of 512 and separated with global offsets as in Fig. 3.16. b) The<br>corresponding transfer function for this set of comparator offsets                        | e      |

|      | a) A histogram of the same offsets as in Fig. 3.20(a) after PDF folding has been applied. b) The corresponding transfer function for this set of comparator offsets                                                               | 1      |

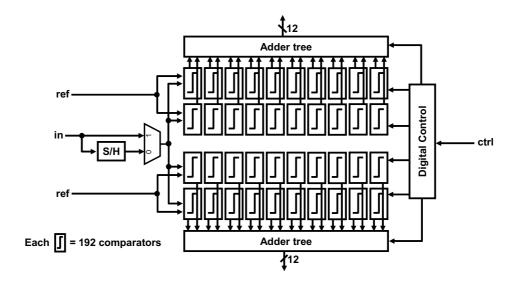

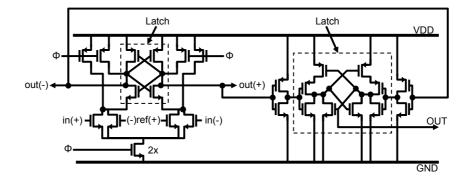

| 3.22 | Block diagram of the prototype two-group stochastic flash ADC                                                                                                                                                                     | 43     |

|      | Schematic of the comparator with a secondary latch to maintain<br>digital output when the comparator is reset                                                                                                                     |        |

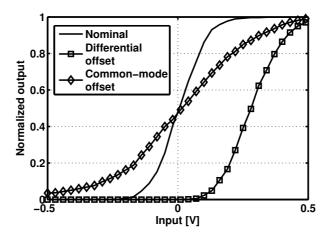

|      | Measured change in the transfer function of a basic stochastic<br>flash ADC by changing the global comparator reference differen-<br>tially and by changing the common-mode                                                       | -      |

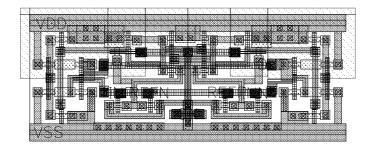

|      | Layout of comparator and secondary latch. Cell dimensions are $14.55\mu$ m by $5.84\mu$ m                                                                                                                                         |        |

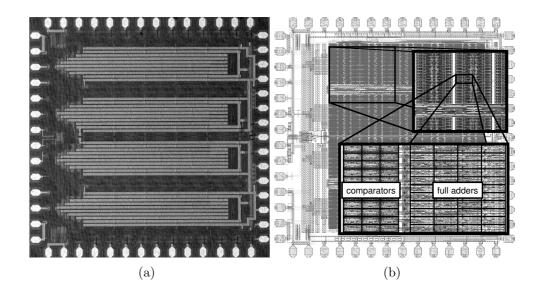

| 3.26 | a) Die photo. Die dimensions are 2.4mm by 2.4mm. b) Layout screen capture showing detail of functional blocks                                                                                                                                                                                                                                                                                                                                                                                            | 45 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

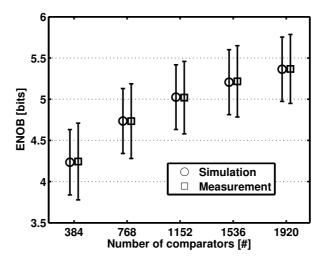

| 3.27 | Measured ENOB plotted against number of comparators activated. For comparison, numerically simulated results for the same setup are plotted. Error bars indicate $\pm \sigma$ of ENOB                                                                                                                                                                                                                                                                                                                    | 45 |

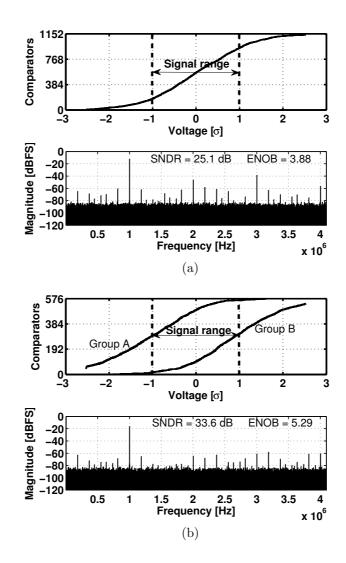

| 3.28 | a) Measured transfer function of a single group of 1152 paral-<br>lel comparators ( $\sigma \approx 140 \text{ mV}$ ) and FFT of 1 MHz sine input.<br>$f_S = 8 \text{ MHz}$ . b) Measured transfer function of the same parallel<br>comparators as two groups of 576 with differing fixed references<br>set to $\approx -1.078\sigma$ and $\approx +1.078\sigma$ for groups A and B, respec-<br>tively. Also, FFT of output from the sum of groups A and B of<br>1 MHz sine input. $f_S = 8 \text{ MHz}$ | 46 |

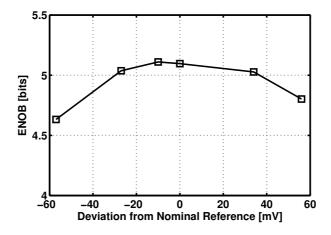

| 3.29 | Measured ENOB for the two-group stochastic flash ADC (576 comparators per group) as a function of deviation from the nomi-<br>nal differential references, $\pm 1.078\sigma$ . The range -60mV to +60mV is equivalent to $\pm 0.8\sigma$ and $\pm 1.2\sigma$ , respectively                                                                                                                                                                                                                              | 47 |

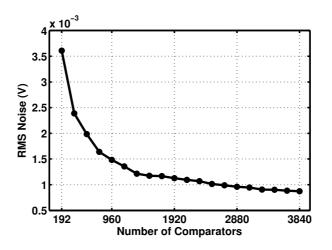

| 3.30 | Measured input-referred noise as a function of total number of comparators.                                                                                                                                                                                                                                                                                                                                                                                                                              | 47 |

| 3.31 | Block level diagram of a single-group stochastic flash ADC                                                                                                                                                                                                                                                                                                                                                                                                                                               | 52 |

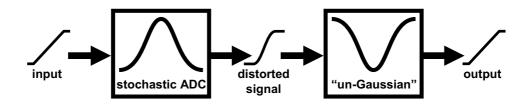

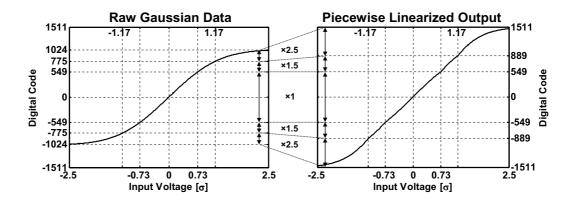

| 3.32 | A piecewise linear approximation of an inverse Gaussian CDF give<br>a more linear transfer function.                                                                                                                                                                                                                                                                                                                                                                                                     | 53 |

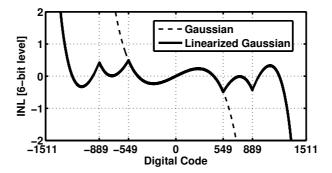

| 3.33 | A plot of the integral nonlinearity for a 2047-comparator single-<br>group stochastic flash ADC with and without piecewise linear<br>approximation                                                                                                                                                                                                                                                                                                                                                       | 54 |

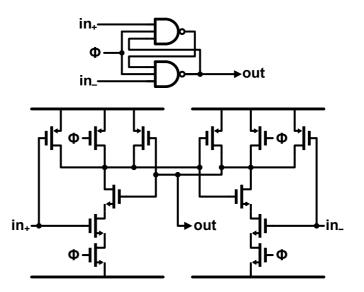

| 3.34 | An analog comparator realized using standard digital 3-input<br>NAND gates                                                                                                                                                                                                                                                                                                                                                                                                                               | 55 |

| 3.35 | Verilog module 'adc' which creates an ADC and includes a deci-<br>mate by 8 option (lines 20-28)                                                                                                                                                                                                                                                                                                                                                                                                         | 56 |

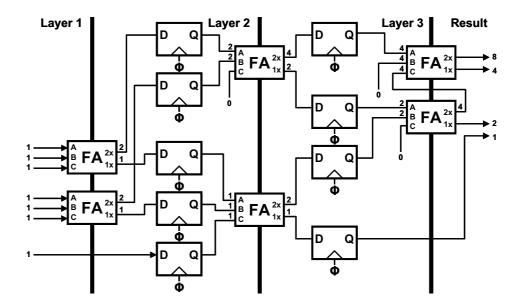

| 3.36 | Diagram of a pipelined Wallace tree ones adder for 7 inputs                                                                                                                                                                                                                                                                                                                                                                                                                                              | 57 |

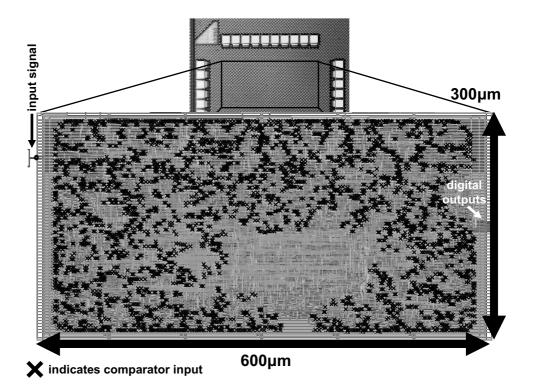

| 3.37 | Screen capture of the prototype IC with the comparator inputs<br>each marked as a black x. Dimensions are $300\mu$ m by $600\mu$ m                                                                                                                                                                                                                                                                                                                                                                       | 59 |

Figure

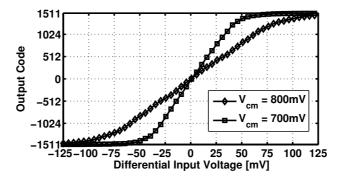

| 3.38 | Measured output transfer function of the ADC for different input<br>common mode voltages                                              | 60 |

|------|---------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.39 | Simulated and measured INL. The effect of the piecewise un-Gaussian function can be seen                                              | 60 |

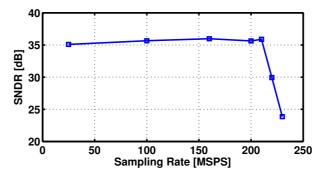

| 3.40 | SNDR from a sine-wave test as function of sampling rate                                                                               | 61 |

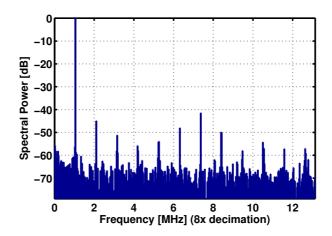

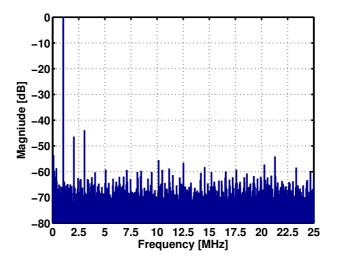

| 3.41 | Spectral plot of 1MHz input sine-wave at 210MSPS achieving 35.9dB SNDR. 8x decimation was used.                                       | 61 |

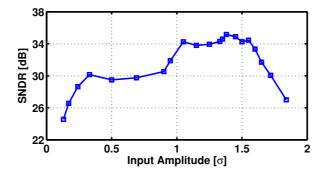

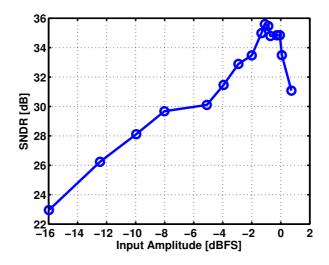

| 3.42 | SNDR from a sine-wave test as a function of input amplitude. $\dots$                                                                  | 62 |

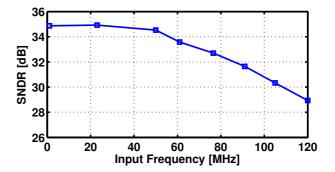

| 3.43 | SNDR from a sine-wave test as a function of input frequency                                                                           | 63 |

| 3.44 | Verilog module 'dsp' which implements the pipelined Wallace ones adder (lines 21-29) and piecewise Gaussian-to-uniform (lines 33-42). | 64 |

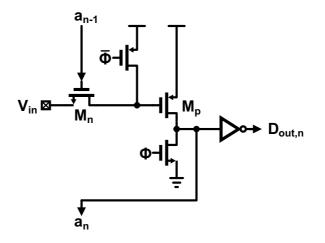

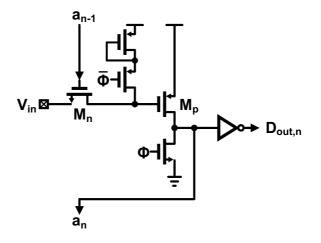

| 4.1  | A single "domino" cell                                                                                                                | 66 |

| 4.2  | A single "domino" cell with a shorter delay                                                                                           | 67 |

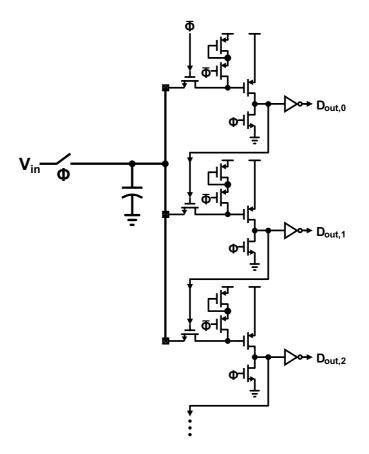

| 4.3  | Example of multiple domino delay cells combined to form an ADC.                                                                       | 68 |

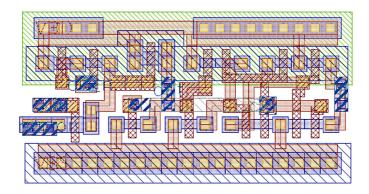

| 4.4  | Screen capture of the physical layout of a single domino cell                                                                         | 69 |

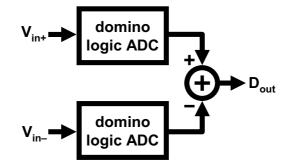

| 4.5  | Pseudo-differential domino logic ADC.                                                                                                 | 69 |

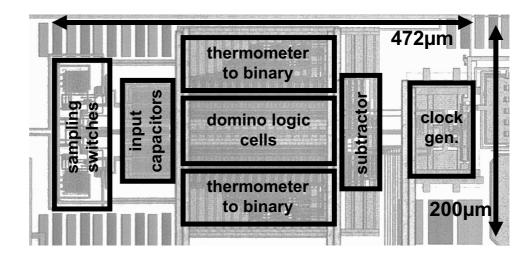

| 4.6  | Detailed die micrograph                                                                                                               | 70 |

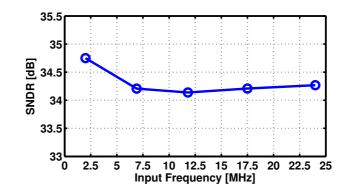

| 4.7  | SNDR is well behaved over the Nyquist range of the converter. $(f_S=50MS/s)$ .                                                        | 70 |

| 4.8  | SNDR increases proportionally with the input amplitude                                                                                | 71 |

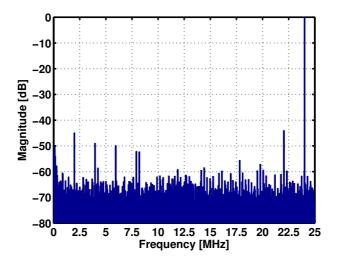

| 4.9  | Spectral FFT plot normalized to the input with an input of 1-MHz taken at 50MS/s                                                      | 72 |

| 4.10 | Spectral FFT plot normalized to the input with an input of 24-MHz taken at 50MS/s                                                     | 73 |

| 5.1  | A block diagram of the basic SAR ADC                                                                                                  | 76 |

| 5.2  | a) A block diagram of a charge redistribution SAR ADC. b) 3-bit DINOSAR example.                                                      | 77 |

| Fig | <u>gure</u> <u>F</u>                                                                                                                                                                                                                     | Page |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

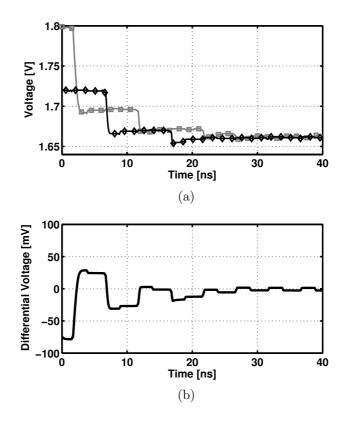

| 5.3 | a) A simulated example of the differential voltage at the input of<br>the comparator during a DINOSAR conversion. b) A simulated<br>example of the single-ended voltages at the input of the compara-<br>tor during a DINOSAR conversion | 78   |

| 5.4 | Simulated spectral plot of a 6-bit DINOSAR                                                                                                                                                                                               | 79   |

## LIST OF TABLES

| Tał | ble                 | Pag | ge |

|-----|---------------------|-----|----|

| 3.1 | Performance Summary |     | 49 |

| 3.2 | Performance Summary | ••  | 63 |

| 4.1 | Performance Summary |     | 74 |

To myself.

I really couldn't have done it without me.

# AUTOMATED SYNTHESIS OF ANALOG TO DIGITAL CONVERSION

### CHAPTER 1. INTRODUCTION

The invention of CMOS integrated circuits has led to the creation of technology only dreamed of a few decades ago. Consider the technology found on the original series of *Star Trek*, which at the time represented what was imagined to eventually be the pinnacle of human achievement. Today much of this technology has been surpassed and considered commonplace. For example, Captain Kirk would gladly trade his bulky communicator in for an iPhone, and Uhura's earpiece looks clunky next to an off-the-shelf Bluetooth headset. Integrated circuits make this technology possible; device scaling and synthesis that makes each generation of technology better and cheaper.

In digital circuit design there is a fairly straightforward trade-off between power and speed. For a digital gate to switch faster, it must source more current to its output load, i.e. the MOS gates of the successive digital block. Thus, the power-delay product is a good metric to compare digital circuits. By scaling the physical dimensions of transistors to smaller geometries, there is a innate reduction in the power-delay product in addition to an overall area reduction for a given digital design [1]. By merely shrinking the size of transistors, a circuit consumes less power for the same speed or it can achieve higher speed for the same power. In effect, scaling digital circuits is a win-win situation. There are certain reliability issues with scaled transistors that can cause transistors to fail [2]–[4], but these issues can be remedied by changing process parameters and innovative device engineering [5][6].

Since there are practically only benefits to porting a digital design to a scaleddown process, we can expect this trend to continue [7][8]. Due to the low sensitivity of digital circuits to their physical layout, they are usually synthesized: that is, their physical layout is automatically generated. This is a huge benefit in the form of dramatically reduced design cost. Digital synthesis allows designers to describe digital circuits by writing code in either VHDL or Verilog programming languages and processing it through automation tools. The digital design can then be effortlessly ported to the next generation process by simply reprocessing already existing VHDL or Verilog code.

So far this is nothing but good news. All digital circuits must eventually interface to our analog world by the use of analog-to-digital conversion (ADC) and digital-to-analog conversion (DAC) circuits. To get the most out of higher performing digital circuits, there is a need for ADCs and DACs that can be easily integrated on scaled technology. Although scaling inherently improves digital circuits, scaling analog circuits tends to gives increased speed yet decreased gain and not necessarily lower power or area [9]. This means that every time an analog circuit is ported to a new process it must be meticulously and expensively redesigned. Moreover, classic analog circuits are very sensitive to their physical layout making synthesis practically impossible. Because of this, as scaling trends continue, the analog portion of mixed-signal systems tend to consume proportionally more power, area, and have a higher design cost than the digital counterparts. This thesis will address how to use existing digital synthesis tools to synthesize analog circuits and describe new ADC architectures that are synthesizable and portable to future processes.

# CHAPTER 2. ANALOG CIRCUIT SYNTHESIS USING STANDARD DIGITAL SYNTHESIS TOOLS

Large digital circuits can be very complex, so they are frequently synthesized; that is, many of the circuit specifics and the physical layout are automatically generated by computer software. This allows the digital circuit to be designed and simulated in a very high-level way. Imagine trying to give driving directions to your house to a robot that only understands simple commands such as "turn the steering wheel to the left six degrees," and "increase the pressure on the accelerator by two percent." Trying to describe "drive down the interstate for 56 miles and take exit 231" using only these simple commands would be very tedious and it would be very easy to make a catastrophic mistake; however, if there is a deterministic way to convert a complex command into simple commands, software can be created that does the conversion. This the idea behind digital synthesis: it frees a designer from coding each individual digital logic gate to describe a circuit in a human-readable way.

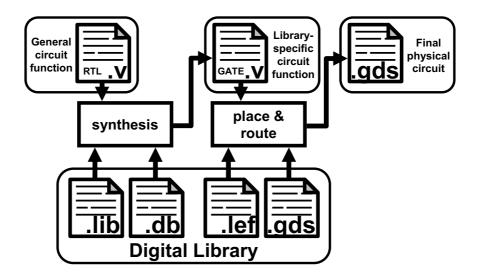

A diagram of the standard digital circuit design flow can be seen in Fig. 2.1. A digital circuit is first described at register transfer level (RTL) in a hardware description language such as Verilog or VHDL. At this high level, the code very much resembles the C programming language. Once the digital circuit is described in RTL Verilog, it can be simulated to verify its functionality. The semiconductor foundry that will fabricate the physical circuit will provide a digital library of the standard digital cells. All digital libraries tend to have the same functional blocks, but the size, speed, and area of each block depends on the fabrication process. Once

Figure 2.1: The digital circuit synthesis design flow.

the digital library has been obtained, the synthesis tool will take the RTL code and translate it into gate-level code that is optimized and specific to the process. The gate-level code can also be simulated to verify that the functionality is still correct. The final step to run the gate-level code through the place-and-route tool, which optimally places the digital blocks, physically, and generates the wiring to connect all of the blocks. This final output file from the place-and-route tool can also be simulated and will ultimately be constructed into a physical circuit.

As an example, see Fig. 2.2. This is a piece of RTL Verilog that is humanreadable and takes in three inputs, A, B, and C. The output Z is true when two or more of the inputs are true (i.e. Z = (A&B)|(B&C)|(A&C))). There is no standard digital cell that performs this function, so the synthesizer will need to create the same digital function out of simpler logic gates that are available in the digital library. Typically there are two types of files in the digital library: timing information (.lib, .tlf, or .db files) and physical information (.lef and .gds files). The synthesizer is only interested in the timing information which will have

| 1 | module circuit(A, B, C, Z);   |

|---|-------------------------------|

| 2 | output Z;                     |

| 3 | output Z;<br>input A, B, C;   |

| 4 |                               |

| 5 | assign Z = (A&B) (B&C) (A&C); |

| 6 |                               |

| 7 | endmodule                     |

Figure 2.2: RTL Verilog code.

| 1  | module circuit(A, B, C, Z);                         |

|----|-----------------------------------------------------|

| 2  | output Z;                                           |

| 3  | input A, B, C;                                      |

| 4  |                                                     |

| 5  | <b>wire</b> n1, n2, n3;                             |

| 6  | nand2x2 U1( .A(A), .B(B), .Y(n1) );                 |

| 7  | nand2x2 U2( .A(B), .B(C), .Y(n2) );                 |

| 8  | nand2x2 U3( .A(A), .B(C), .Y(n3) );                 |

| 9  | nand $3x2$ U4( .A(A), .B(B), .C(C), .Y(Z) );        |

| 10 |                                                     |

| 11 | endmodule                                           |

| 1  | module circuit(A, B, C, Z);                         |

| 2  | output Z;                                           |

| 3  | input A, B, C;                                      |

| 4  |                                                     |

| 5  | <b>wire</b> n1, n2;                                 |

| 6  | nand2x2 U1( .A(A), .B(B), .Y(n1) );                 |

| 7  | nor2x2 U2( .A(A), .B(B), .Y(n2) );                  |

| 8  | muxix2 U3( .IN0(n1), .IN1(n2), .SELECT(C), .Y(Z) ); |

| 9  |                                                     |

| 10 | endmodule                                           |

Figure 2.3: Gate-level Verilog code of two functionally equivalent digital circuits.

a list of all of the digital cells and their associated power, area, and speed. The designer can instruct the synthesizer to minimize any of these or to try and meet specific goals regarding the power, area, and speed. Fig. 2.3 is an example of two possible gate-level Verilog code outputs from the synthesizer. Both have the same digital function, so the synthesizer would choose a solution that optimally meets the targeted requirements.

There are two main advantages of synthesizing a digital circuit. First, synthesis allows a designer to spend more time on designing the function of the circuit instead of tediously optimizing the circuit at the gate level. Second, the RTL code can be re-synthesized onto a different process with relative ease, allowing a quick turnaround time when porting a circuit to a new technology.

Currently there are no automatic synthesis tools for analog circuits that are as proven and ubiquitous as conventional synthesis is for digital circuits. This is due to the fact that digital circuits are not very sensitive to their physical layout. Digital circuits are generally only sensitive to their timing. Many people have claimed to have created an "all-digital" ADC [10]–[13], but at the time of writing this thesis there has been no successful attempt at synthesizing an ADC using standard digital synthesis tools. The key limiting factor is that an ADC requires a circuit block that has an analog input and a digital output, and incorporating this into the constraints of the standard digital cell design space is nontrival.

#### 2.1 Using Custom Analog Cells

One way to incorporate analog functionality into a digitally synthesized circuit is to create a custom "digital" cell and add it to the standard cell library. There is no way for the synthesis and place-and-route tools to distinguish between a custom analog cell and a standard digital cell. In order for a custom cell to be placed into the final circuit it must be added to the library (timing and physical) and then instantiated explicitly.

In order to add the physical layout of a custom analog cell to the digital library, the cell must first be designed and simulated and laid out in such a way that it matches certain characteristics of the other cells in the library. All digital cells in the library have the same supply pitch and usually have all routing on a single metal layer, the closest to the substrate. In effect, all of the cells have the same height (set by the supply pitch) but can have varying widths. In order to make a custom cell match, it is easiest to start with the physical layout of a cell that is already in the library and alter it to make a custom cell. Once the physical layout is complete it can be added to the library. One section of the .lef file lists the input and output pin names, their location, and size with respect to the cell origin. If this is not set properly, the tool will not route to the cell correctly.

Once the physical layout has been added, the timing information needs to be added to the timing files as well or it will not be recognized by the synthesizer. Precaution must be taken when using a custom cell, because it requires "tricking" the synthesizer. In the library timing file, for each cell there is a description of its digital function and a list of the time delays from each of its inputs to each of its outputs. In the case of an analog cell where the input is analog, there is no way to describe the function in a way that the synthesizer will understand. It would be acceptable to use dummy data copied from another standard cell to make an entry into the library to at least make the custom cell valid; however, it is paramount that the function and timing entries make the cell appear to be a poor choice in implementing any digital circuit. For example, if a custom analog cell was created with two inputs and one output and the timing information was copied from a NAND gate cell, there is a risk that the synthesizer may instantiate the custom cell in a place where it needs to use a NAND gate in the digital portion of the circuit. Since the custom analog cell is not actually a NAND gate, the result will not work; however, the gate-level Verilog simulation would verify that the circuit works. This is because the digital simulation would use the timing and functional information from the copied NAND gate in order to simulate. To be safe, it is

| 1 | module myCell(A, B, Z);                                  |

|---|----------------------------------------------------------|

| 2 | output Z;                                                |

| 3 | <pre>module myCell(A, B, Z); output Z; input A, B;</pre> |

| 4 |                                                          |

| 5 | customCell U1( $.A(A)$ , $.B(B)$ , $.Z(Z)$ );            |

| 6 |                                                          |

| 7 | endmodule                                                |

Figure 2.4: Example instantiation of a custom cell 'customCell' into a Verilog module 'myCell.'

wise to use the set\_dont\_use *cell\_name* command. This synthesizer directive will inform the synthesis tool that it should not select the cell *cell\_name* from the library while synthesizing. This command will not remove the cell from the entire design if the cell is already part of a module that the tool will not synthesize (e.g. it was already synthesized or hand-designed).

With a custom analog cell added to the library physically, and functionally designed to prevent the synthesizer from choosing it automatically, the final step is to explicitly instantiate the cell and force the synthesizer to allow the cell to remain into the final circuit. This is done by calling the custom library cell by name in the RTL Verilog exactly how it will appear in the gate-level Verilog code. An example of this can be seen in Fig. 2.4. The example is of a custom cell that has been added to the library named *customCell* and is placed inside a module called *myCell* with the same number of inputs and outputs. The reason this is done is that when the synthesizer attempts to synthesize the circuit it will try and replace *customCell* with a cell that the synthesizer decides is "more optimum" based off of what is listed in the timing file. To avoid this, the command set\_dont\_touch *myCell* in any way. This command must be given to both the synthesizer and the place-and-route tool. Note that set\_dont\_touch supersedes set\_dont\_use.

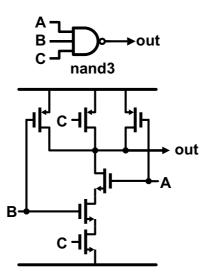

Figure 2.5: A standard digital CMOS NAND3 gate and its internal transistor schematic.

The final important detail about using a custom analog cell is that since some or all of the input and output nets are analog, the synthesizer command dont\_touch\_network netname, where netname is the name of the analog net, is required. Without this command the software tool may decide that the net has too high of a fanout or fanin and place digital buffers between the signal and the load. As digital buffers block analog signals, this command is important and must be given to both the synthesizer and the place-and-route tool.

#### 2.2 Using Standard Cells for Analog Circuits

An even more elegant solution to using custom analog cells is to use the standard digital cells that come with the library to generate analog functions. In order to see how this is possible, look at the internal transistor implementation of a standard 3-input NAND (or NAND3) digital gate (Fig. 2.5). This circuit is a

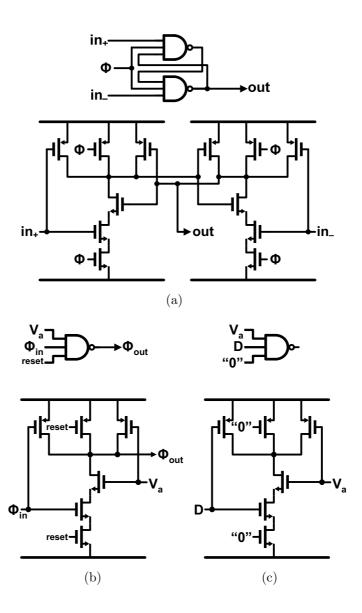

Figure 2.6: a) An analog comparator made from standard digital NAND3 cells. b) A analog voltage controlled delay cell with asynchronous reset using a standard digital NAND3 cell. c) A standard digital NAND3 cell used as a DAC cell.

digital logic gate performing a NAND function for three inputs, or  $out = \overline{A\&B\&C}$ , when the inputs are digital rail-to-rail inputs.

Upon observation, the schematic of the transistors inside a CMOS NAND3 gate closely resembles half of a clocked analog comparator. By cleverly connecting

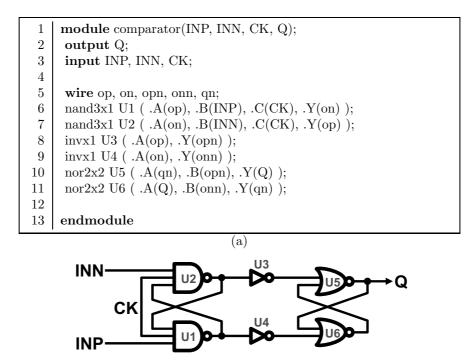

Figure 2.7: a) Verilog module 'comparator' which implements a NAND3 based comparator (lines 6-11). b) Gate-level schematic representation of the code.

(b)

two NAND3 gates together as in Fig. 2.6(a), an analog-input comparator is created if the common-mode of the input is high enough to ensure that the PMOS transistors connected to the input are in the cutoff region of operation. When the clock  $\Phi$  is low, both outputs are reset to the positive supply rail. When the clock goes high, the outputs will begin to discharge through the three series NMOS devices. The discharge rate depends on the capacitance on the output node and the current through the three series devices. Since one of the series devices is connected to the analog input, the discharging current is related to the input. Once an output discharges to below a PMOS threshold voltage, the cross-coupled connection creates positive feedback that causes the comparator to force the outputs all the way to the supply rails. Implementing such a comparator can be done by explicitly referencing the standard library cells in the RTL Verilog code as in Fig. 2.7(a). In this example, a static SR-latch is added to the output of the comparator. The SR-latch holds the output data valid while the comparator is reset. The SR-latch input is buffered with inverters to reduce a memory-effect on the comparator due to the SR-latch. Although this circuit is inherently compatible with digital synthesis, the synthesizer will assume that the circuit is actually a digital one, and will try and optimize it by replacing some of the gates or changing the circuit entirely while maintaining the same digital function. This digital optimization may render the circuit nonfunctional from an analog perspective, so here the command set\_dont\_touch comparator would prevent the synthesizer from altering the comparator module.

In the NAND3 comparator, the capacitance at the output nodes discharges as a rate that is dependent on an analog input. Using the same input-dependent discharging function, an analog voltage controlled delay cell can be created as seen in Fig. 2.6(b). When the clock input  $\Phi$  goes high, the output is discharged to low at a rate that is dependent on the analog input  $V_a$ . The analog input voltage should be high enough as to keep the connected PMOS in the cutoff region of operation. In the figure, a NAND3 is used because this allows one input to be an asynchronous reset for the cell. Creating a large chain of delay cells can be used to create an voltage controlled delay line and can also be used to make an ADC as will be discussed in Section 4.

Finally, a NAND3 cell can also be used to implement a digital-to-analog (DAC) cell when used as in Fig. 2.6(c). Parasitic overlap capacitance creates a coupling effect between the input of one device and the input of an adjacent device. First, sample an analog voltage  $V_a$  onto the parasitic capacitance of a NAND3 gate input and hold it there at high-impedance. Changing the digital voltage D will then cause a small voltage step on  $V_a$  due to the coupling capacitance and charge injection. This same DAC cell can be created out of a 2-input NAND gate, but a NAND3 gives better performance since an input can be held at digital zero to cause the NAND3 output to never change, saving power.

#### 2.3 Summary

Analog circuit components can be integrated into standard digital circuit design if certain precautions are taken. A good candidate architecture for synthesis is one that is based on repeated and modular blocks that are not very sensitive to their physical location and routing. Designing and creating custom analog cells gives a designer a great deal of flexibility, but requires being very careful in integrating the custom cell into the standard cell library. Using standard cells to create analog circuits removes one layer of complexity by eliminating the need to integrate a custom cell into the library, but the design is less flexible since the design is limited to using already existing cells. All comparators have some input-referred offset due to random device mismatch. In a flash ADC, minimizing comparator offset is critical to the overall accuracy of the converter. This requires that each comparator consume a large area footprint in an effort to reduce device mismatch, or offset-canceling circuit techniques such as autozeroing or output offset storage must be implemented as described in [14]. The latter technique requires storing offset values on capacitors at the output of gain stages. Due to low intrinsic device gain multiple cascaded gain stages are typically used [15]–[17]. Instead of suppressing comparator offset, it is possible to use the random nature of the offset as part of a stochastic ADC.

Flash ADCs typically use a reference ladder to generate the comparator trip points that correspond to each digital code. First proposed in [18], a stochastic ADC uses comparators' inherent input-referred offset due to device mismatch as the trip-points. It has been proposed in [19] that by determining the offset of each comparator, it is possible to choose comparators with offsets that correspond to a desired transfer function. Choosing only the best of redundant comparators was also performed in the past in [20]. This solution requires a computationally expensive foreground calibration to generate a transfer function. In [19], the calibration logic consumed more area than the rest of the ADC combined; not including the computation engine which was off-chip. If comparator offset follows a distribution that is nearly linear, then the resulting comparator offsets can be used as the transfer function and none of this calibration hardware is required.

In a basic flash ADC, an input signal is connected to the inputs of a group

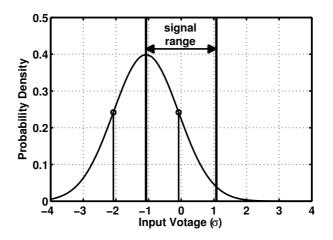

Figure 3.1: a) Probability density function of comparator offset in terms of standard deviation,  $\sigma$ , assuming Gaussian distribution. b) This is the basic stochastic flash ADC. c) Idealized output of the basic stochastic flash ADC with ramp input in terms of  $\sigma$ .

of comparators. The threshold of each comparator is set precisely, usually by a resistor string, such that all comparator thresholds are equally spaced by 1 LSB. In reality there is also a random offset in each comparator that, in effect, readjusts each comparator threshold by a random amount. This random offset, due to device mismatches will be assumed to be a Gaussian distribution with a mean ( $\mu$ ) of zero and variance ( $\sigma^2$ ) inversely proportional to comparator area.

In a stochastic flash ADC, an input signal is also connected to the inputs of

a group of comparators. However, the comparator thresholds are not precisely set by design, but rather are allowed to be random. In the case of a standard flash, the comparator outputs after a conversion can be expected to be a thermometer code since the comparator thresholds are monotonically increasing by design. If each comparator threshold is random, however, then comparator outputs can not be expected to have any order. The total number of comparators that evaluate high will still be monotonically increasing with an increase in the input, so a ones adder is required to decode the output. This basic architecture with a group of comparators with random offsets followed by a ones adder is the basic stochastic flash ADC (Fig 3.1(b)).

The probability density function (PDF) of random comparator offset is influenced by many factors such as random variation of threshold voltage and current factor [21]. The Central Limit Theorem [22] indicates that since comparator offset is a sum of independent random variables with finite mean and variance the PDF will be approximately Gaussian (Fig. 3.1(a)). When a ramp signal is applied to the input of a basic stochastic flash ADC, the output will follow the cumulative distribution function (CDF) of comparator offset; therefore, the voltage transfer function of a basic stochastic flash ADC is the CDF of the random comparator offset (Fig. 3.1(c)). The number of comparators in the stochastic flash ADC must be enough such that the actual transfer function resembles the comparator offset CDF to the desired degree.

What make a stochastic flash ADC very interesting is that if the comparators are made to be digital cells, then the entire design can be synthesized like a digital circuit, as no analog references are required.

Figure 3.2: Normalized transfer function of a basic stochastic flash ADC with uniformly distributed comparator offsets for three cases where n is the number of comparators.

## 3.1 Statistical Analysis of a Uniform Distribution Stochastic Flash ADC

In a standard flash ADC, the number of comparators required to obtain N bits of quantization is  $2^N - 1$ . Since in a stochastic flash ADC the comparator levels are not set deliberately, but allowed to be random, a designer needs to know how many random comparator levels are required to obtain a desired accuracy. To analyze this, this section will only consider the case where comparator offset is random with a uniform PDF. The transfer function for a near infinite number of comparators will merely be the CDF of this random offset, which is a perfect line. Due to the random placement of each comparator level, a typical set of a smaller number of comparators will not give perfect linearity (Fig. 3.2). Actual comparator offset has a Gaussian PDF, but it will be demonstrated later that it is possible to approximate a uniform distribution, so this analysis is valid.

#### 3.1.1 Number of Comparators Required

Before analyzing a stochastic flash ADC, let us first revisit how to obtain that for a conventional flash ADC,  $2^N - 1$  comparators are required for N bits. The number of bits N can be calculated by determining the signal-to-quantization-noise ratio (SQNR) by the relationship,

$$N = \log_2(SQNR), \tag{3.1}$$

or when SQNR is expressed in decibels,

$$N = \frac{SQNR}{20\log_{10}(2)} \approx \frac{SQNR}{6.02}.$$

(3.2)

To calculate SQNR, the signal power and quantization noise power must be determined. First, consider the signal as being uniformly distributed between 0 and 1, the normalized range of the theoretical ideal ADC in Fig. 3.3(a). This signal can be described as a random variable with a uniform (PDF). The variance of a random variable is equivalent to its mean-square power, and since the variance of a uniform PDF is found to be

$$\operatorname{Var}(PDF_{uniform}) = \frac{\Delta^2}{12},\tag{3.3}$$

where  $\Delta$  is the full range of the PDF. In the case of the signal,  $\Delta=1$  thus signal power is

$$P_{signal} = \frac{1}{12}.\tag{3.4}$$

To calculate quantization noise power, it must first be observed from Fig. 3.3(b)

Figure 3.3: a) An ideal 4-bit ideal ADC. b) The quantization noise voltage of an ideal 4-bit ADC, where quantization noise is the input subtracted from the output.

that quantization noise is uniformly distributed between  $\pm 1/2$  LSB where

$$LSB = \Delta = \frac{1}{n+1},\tag{3.5}$$

and n is number of comparators. Therefore,

$$P_{noise} = \frac{\left(\frac{1}{n+1}\right)^2}{12}.$$

(3.6)

Now that signal and quantization noise power (mean-square) are known, SQNR in terms of voltage can be found by taking the ratio of the rms values of each, i.e.

$$SQNR_{ideal} = \frac{\sqrt{P_{signal}}}{\sqrt{P_{noise}}}$$

$$SQNR_{ideal} = \frac{\sqrt{\frac{1}{12}}}{\sqrt{\frac{(\frac{1}{n+1})^2}{12}}}$$

$$SQNR_{ideal} = n + 1,$$

(3.7)

or in decibels,

$$SQNR_{ideal,dB} = 20\log(SQNR_{ideal}).$$

(3.8)

From (3.1) and (3.7) the resulting number of comparators n required for a given number of bits N is

$$N = \log_2(n+1)$$

$n = 2^N - 1,$

(3.9)

which is the expected result.

Now consider an ADC whose comparator thresholds are randomly and uniformly distributed along full-scale from 0 to 1. A possible example of a 3-comparator ADC of this type is shown in Fig. 3.4. Calling this a 2-bit ADC would be a misnomer, since quantization noise is actually much higher than an ideal 2-bit ADC, as will be demonstrated in this section. In order to bound quantization noise to zero at the extremes of the input (as in Fig. 3.4), let

$$LSB = \frac{1}{n}.$$

(3.10)

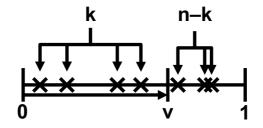

Fig. 3.5 is a visualization of how to describe the random comparator placement as a random variable. If it is known that there are n comparator thresholds

Figure 3.4: A 3-comparator ADC with random comparator placement. The marks along the x-axis represent the comparator thresholds.

Figure 3.5: Graphical representation of a binomial random variable k – the number of n comparators between 0 and v.

within the range 0 to 1, and the number of thresholds between 0 and an arbitrary point v is called k, then the remaining thresholds (n - k) must exist between vand 1. Since these comparator thresholds are uniformly distributed, the random variable k is a binomial distribution [23] with a probability mass function (PMF) of

$$PMF_k(n,v) = \binom{n}{k} (v)^k (1-v)^{n-k}.$$

(3.11)

For any given value of input v, the output is merely k/n since 1LSB was

defined as 1/n. The mean of the output k/n as a function of v is calculated to be

$$\operatorname{Mean}(\frac{k}{n}(v)) = \sum_{k=0}^{n} \left(\frac{k}{n}\right) \binom{n}{k} (v)^{k} (1-v)^{n-k}$$

$$\operatorname{Mean}(\frac{k}{n}(v)) = v.$$

(3.12)

This result means that, for example, in the range 0 to 30% of full-scale there will on average be 30% of the total comparator thresholds. Any variation from this mean value results in quantization noise, therefore the variance of k/nis quantization noise power as a function of the input v, and is calculated to be

$$\operatorname{Var}(\frac{k}{n}(v)) = \sum_{k=0}^{n} \left(\frac{k}{n} - v\right)^{2} {\binom{n}{k}} (v)^{k} (1 - v)^{n-k}$$

$$\operatorname{Var}(\frac{k}{n}(v)) = \frac{v - v^{2}}{n}.$$

(3.13)

Now to calculate SQNR for the uniform stochastic ADC, the signal power for a uniformly distributed input is the same as in the ideal case, only the quantization noise will be different, i.e.

$$P_{signal} = \frac{1}{12}.\tag{3.14}$$

Quantization noise power as a function of input was found in (3.13), and integrating this function over the signal range gives total quantization noise power;

$$P_{noise} = \int_0^1 \frac{v - v^2}{n} dv = \frac{1}{6n}.$$

(3.15)

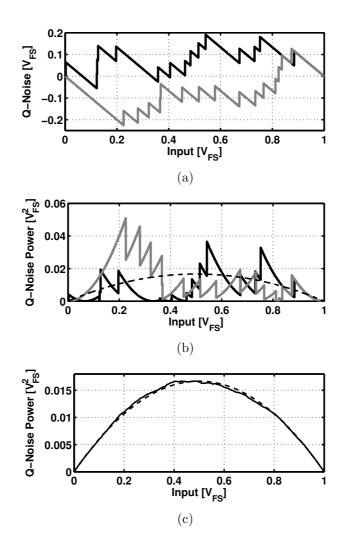

This result can be verified numerically as shown in the example in Fig. 3.6.

Figure 3.6: a) The quantization noise of two random 15-comparator ADCs with uniformly distributed comparator thresholds (1LSB=1/15). b) The square of quantization noise of the same two random ADCs. The dashed line is a plot of (3.13). c) The square of quantization noise of 5000 random ADCs averaged together. The dashed line is a plot of (3.13).

SQNR is finally calculated to be

$$SQNR_{stochastic} = \frac{\sqrt{P_{signal}}}{\sqrt{P_{noise}}}$$

$$SQNR_{stochastic} = \frac{\sqrt{\frac{1}{12}}}{\sqrt{\frac{1}{6n}}}$$

$$SQNR_{stochastic} = \sqrt{\frac{n}{2}}.$$

(3.16)

Figure 3.7: Effective number of bits as a function of number of comparators, where comparator thresholds are uniformly distributed across the input range.

From (3.1) and (3.16) the resulting number of comparators n required for a given number of bits N is

$$N = \log_2(\sqrt{\frac{n}{2}})$$

$$n = 2 \cdot 4^N.$$

(3.17)

This analysis assumes not canceling any DC offset of the ADC; if this offset is removed (as is usually the case) rms quantization noise will be decreased by 3dB [24], finally yielding,

$$n = 4^N. (3.18)$$

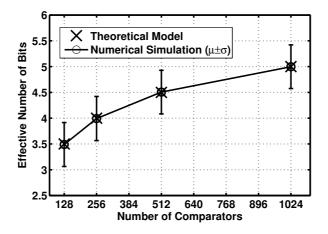

This result can be easily verified with numerical simulation by taking n samples of a uniform random variable and using these values as the references for an simulated flash ADC. After applying a full-scale ramp input, the rms quantization noise can be calculated empirically, finally giving the resulting number of bits N. Repeating this test many times, as to satisfy the Law of Large Numbers [25],

allows us to find the average number of bits N and its standard deviation for a given number of comparators n. Plots of both the theoretical result from (3.18) and the numerical simulation result can be seen in Fig. 3.7. It is also relevant to note that the standard deviation of the number of bits N is approximately 0.42 bits regardless of the number of comparators.

To compare to a conventional flash ADC, the number of comparators must be increased by a factor of 2 to obtain 1 additional bit of accuracy. This analysis shows that to increase the accuracy of a uniformly random stochastic ADC by 1 bit, the number of comparators must be increased by a factor of 4.

## 3.1.2 Calculating ENOB from SNDR of a Sine-Wave Test

The value of the effective number of bits (ENOB) describes the overall accuracy of an ADC. The most widely used method to determine ENOB is to apply a sine-wave input and create a coherent FFT-plot. Signal-to-noise-and-distortion ratio (SNDR) is easily calculated by taking the power from the signal histogram bin and comparing it the the total remaining power from the remaining bins (after removing the DC bin). Creating an accurate, low-noise (through the use of bandpass filters) sine-wave input is very easy, making this method popular. Moreover, this method captures both static and dynamic sources of error. The accepted conversion to ENOB from SNDR from this sine-wave test is defined as

$$ENOB = \frac{SNDR - 1.76}{6.02},\tag{3.19}$$

where SNDR has units of dB and ENOB is measured in bits. In this section it will be demonstrated that while (3.19) holds true for ADCs with quantization noise

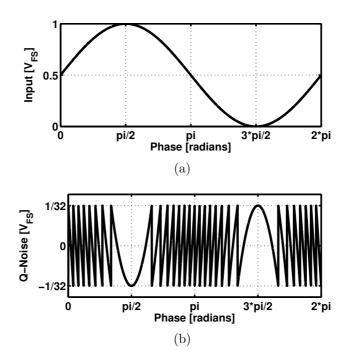

Figure 3.8: a) A full-scale sine-wave input. b) The associated quantization noise voltage for an ideal 4-bit ADC.

that is mostly uncorrelated to the input, if quantization noise is correlated to the input a different conversion of SNDR to ENOB should be considered.

To see where (3.19) comes from, first consider the ideal ADC from Section 3.1.1, and calculate the SQNR for when the input is a sine-wave. For a sine-wave input such as the waveform seen in Fig. 3.8(a), the observed quantization noise (Fig. 3.8(b)) still appears to be roughly uniformly distributed and, for the most part, uncorrelated to the input signal. Therefore the noise power in the sine-wave input case is identical to (3.6),

$$P_{noise,sine} = \frac{\left(\frac{1}{n+1}\right)^2}{12}.$$

(3.20)

The signal, however, is no longer a uniform distribution, but a sine-wave

distribution whose PDF is

$$PDF_{sine}(v) = \frac{1}{\pi\sqrt{\frac{1}{4} - (v - \frac{1}{2})^2}}$$

(3.21)

over the full-scale range from 0 to 1. The variance of (3.21) is

$$\operatorname{Var}(PDF_{sine}) = \frac{1}{8},\tag{3.22}$$

and thus the signal power is

$$P_{signal,sine} = \frac{1}{8}.$$

(3.23)

Calculating SQNR yields

$$SQNR_{ideal,sine} = \frac{\sqrt{P_{signal,sine}}}{\sqrt{P_{noise,sine}}}$$

$$SQNR_{ideal,sine} = \frac{\sqrt{\frac{1}{8}}}{\sqrt{\frac{(\frac{1}{n+1})^2}{12}}}$$

$$SQNR_{ideal,sine} = \sqrt{\frac{3}{2}}(n+1).$$

(3.24)

The result from (3.24) is not the same as (3.7), but the relationship between the two is

$$SQNR_{ideal} = \sqrt{\frac{2}{3}}SQNR_{ideal,sine},$$

(3.25)

or in decibels,

$$SQNR_{ideal,dB} = SQNR_{ideal,sine,dB} + 20\log(\sqrt{\frac{2}{3}})$$

$$SQNR_{ideal,dB} = SQNR_{ideal,sine,dB} - 1.76.$$

(3.26)

It is from (3.26) and (3.2) that we derive (3.19) to make sure that ENOB is

in terms of a uniformly distributed input, repeated here,

$$ENOB = \frac{SQNR_{ideal,sine,dB} - 1.76}{6.02}.$$

(3.27)

Following the same procedure for the uniform distribution stochastic flash ADC, the difference between SQNR from a uniform input and a sine-wave input can be obtained. As in the case of an ideal ADC, the signal power of a sine-wave input is

$$P_{signal,sine} = \frac{1}{8}.$$

(3.28)

The quantization noise power, however, changes due to the input. Recall that from (3.13) (shown graphically in Fig. 3.6(c)), quantization power is smaller toward the extremes of the input range, and that a sine-wave spends more of its time at these regions. Integrating (3.13) multiplied by the PDF of a sine-wave weights the quantization noise power by the non-uniform distribution of the input and yields

$$P_{noise,sine} = \int_0^1 \left(\frac{v - v^2}{n}\right) \left(\frac{1}{\pi\sqrt{\frac{1}{4} - (v - \frac{1}{2})^2}}\right) dv = \frac{1}{8n}.$$

(3.29)

Another way of finding the same result is to substitute the actual sine-wave signal for v in (3.13) and integrate over the time period of the signal, yielding

$$P_{noise,sine} = \frac{1}{2\pi} \int_{0}^{2\pi} \frac{\left(\frac{1}{2}\sin(t) + \frac{1}{2}\right) - \left(\frac{1}{2}\sin(t) + \frac{1}{2}\right)^{2}}{n} dt$$

$$P_{noise,sine} = \frac{1}{8n}.$$

(3.30)

This result can also be verified numerically as in the example in Fig. 3.9.

Figure 3.9: a) The quantization noise due to the sine-wave input in Fig. 3.8(a) for the same two random ADCs as in Fig. 3.6. b) The square of quantization noise of the same two random ADCs. The dashed line is a plot of (3.13) with  $v = (1/2)\sin(x) + 1/2$  and  $x = 0...2\pi$ . c) The square of quantization noise of 5000 random ADCs averaged together. The dashed line is again a plot of (3.13) with  $v = (1/2)\sin(x) + 1/2$  and  $x = 0...2\pi$ .

SQNR for sine-input is finally calculated to be

$$SQNR_{stochastic,sine} = \frac{\sqrt{P_{signal,sine}}}{\sqrt{P_{noise,sine}}}$$

$$SQNR_{stochastic,sine} = \frac{\sqrt{\frac{1}{8}}}{\sqrt{\frac{1}{8n}}}$$

$$SQNR_{stochastic,sine} = \sqrt{n}.$$

(3.31)

The result from (3.31) is not the same as what was found in Section 3.1.1 as (3.16). As in the ideal ADC case, SQNR should be in terms of a uniformly distributed input, thus a conversion factor must be applied,

$$SQNR_{stochastic} = \sqrt{2}SQNR_{stochastic,sine},$$

(3.32)

or in decibels,

$$SQNR_{stochastic,dB} = SQNR_{stochastic,sine,dB} + 20\log(\sqrt{2})$$

$$SQNR_{stochastic,dB} = SQNR_{stochastic,sine,dB} - 3.01.$$

(3.33)

This result implies that for an ADC such as described here, ENOB calculation from a sine-wave input should actually be

$$ENOB = \frac{SQNR_{sine} - 3.01}{6.02}.$$

(3.34)

## 3.2 Many-Group Stochastic Flash ADC

The actual distribution of comparator thresholds is not uniform, but rather a Gaussian distribution. This section will discuss how to effectively create a uniform distribution of comparator thresholds using multiple groups of comparators. The transfer function of a stochastic flash ADC is the integral of the PDF of its comparator thresholds. The integral of a Gaussian PDF is not linear (Fig. 3.1(c)), but the sum of many Gaussian PDFs can be. Fig. 3.1(b) depicts the basic stochastic flash ADC, which has a Gaussian PDF. Setting the global reference *a* to this comparator group effectively shifts the PDF to have a mean of *a* instead of zero (Fig. 3.10). The result of this is that it grants the ability to construct, effectively,

Figure 3.10: Providing a global reference a to a group of comparators effectively shifts the PDF to be centered about a ( $a = 5\sigma$ ).

Figure 3.11: Spacing many Gaussian distributions by  $1.5\sigma$  creates an effective uniform PDF.

a new PDF by using many Gaussian PDFs, each with a different mean.

Using a basic stochastic flash ADC (i.e. one group) by itself will obtain less than 3 bit linearity performance for a signal with range  $\pm 2\sigma$ , even if the number of comparators approaches infinity. Using multiple groups of comparators with the correct spacing of their means will yield as high of performance as desired. For example, Fig. 3.11 shows 11 Gaussian PDFs with their means spaced every  $1.5\sigma$ . The resulting effective PDF is much more linear, in fact a signal of range  $\pm 5\sigma$ would achieve almost 16 bit linearity. The total number of comparators required would be quite large to achieve this result from a stochastic quantization noise

Figure 3.12: Spacing 11 Gaussian distributions by  $1\sigma$ ,  $1.5\sigma$ , and  $2\sigma$ , (as in Fig. 3.11) is a trade-off between signal range and a ripple on the effective uniform PDF.

point of view, but the inherent linearity of the distribution is such that the result is effectively a uniform PDF over a certain range.

There is a simple trade-off between signal range and linearity when it comes to setting the spacing of multiple comparator groups. The example in Fig. 3.12 shows 11 Gaussian PDFs with three difference spacing values. The larger the spacing value, the larger the linear region in terms of  $\sigma$  (which is in terms of volts); however, a spacing value larger than  $1\sigma$  will cause a ripple to appear in this linear region. This ripple needs to be small enough as to not dominate in limiting the accuracy of the converter.

By effectively creating a uniform comparator offset distribution, the analysis of Section 3.1.1 is valid for this type of stochastic flash ADC.

Figure 3.13: A two-group stochastic flash ADC. One group is given an offset of +a, the other -a.

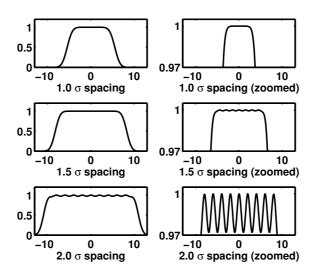

## 3.3 Two-Group Stochastic Flash ADC

Again, the actual distribution of comparator thresholds is not uniform, but rather a Gaussian distribution, so this section will demonstrate how to effectively realize a uniform distribution of comparator thresholds using only two groups of comparators. The transfer function of the basic stochastic flash ADC is the CDF of a Gaussian distribution. A Gaussian CDF is not linear (Fig. 3.1(c)), so linearization must be implemented in order to achieve a desirable linear transfer characteristic. Here we will consider using two basic stochastic flash ADCs, each with a Gaussian CDF transfer function but with a different mean (Fig. 3.13). This can be implemented by adding a constant, intentional offset to a group of comparators.

Changing the mean of comparator thresholds merely shifts the input-tooutput transfer function along the input axis by applying a constant offset to

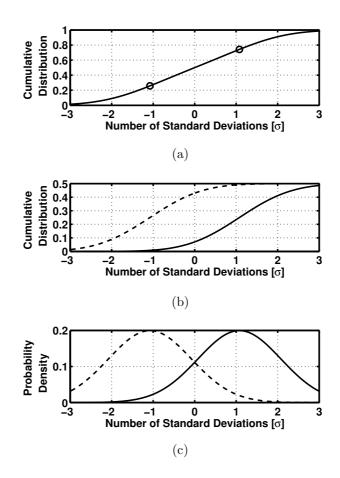

Figure 3.14: a) The resulting overall transfer function for a two-group stochastic flash ADC. (the circles correspond to the mean of each PDF). b) The transfer function of each group before being combined into the overall transfer function. c) The resulting PDFs of each comparator group after global offset is applied.

all comparators in that ADC. The outputs of each ADC are summed to obtain the overall output of this two-group stochastic flash ADC. As the two PDFs are shifted such that the difference of their means increases, a somewhat linear region appears when the input is bounded between the means of the two PDFs (Fig. 3.14). The equation for a Gaussian CDF is

$$f(x) = \frac{1}{2} \left( 1 + \operatorname{erf}\left(\frac{x-\mu}{\sigma\sqrt{2}}\right) \right), \qquad (3.35)$$

Figure 3.15: Maximum achievable linearity as number of bits for a two-group stochastic flash ADC with comparator group offsets of  $\pm a$  and the input is also set to the range  $\pm a$ .

where

$$\operatorname{erf}(x) = \int_{-\infty}^{x} \frac{1}{\sigma\sqrt{2\pi}} e^{\frac{-(u-\mu)^2}{2\sigma^2}} du.$$

(3.36)

Since the transfer function in which we are interested is for a two-group stochastic flash ADC, we will let  $\mu = \pm a$  where an offset of a is applied to one ADC and an offset of -a is applied to the other. We can let  $\sigma = 1$ , causing a to be in units of *number of standard deviations*, for simplicity without loss of generality. Therefore, the transfer function of a two-group stochastic flash ADC can be described by

$$g(x) = \frac{1}{4} \left( 2 + \operatorname{erf}\left(\frac{x-a}{\sqrt{2}}\right) + \operatorname{erf}\left(\frac{x+a}{\sqrt{2}}\right) \right).$$

(3.37)

Since we are interested in when the input is bounded between -a and a, we can find the integral-nonlinearity (INL) by removing the constant linear portion and the overall offset of the transfer function by

$$INL(x) = g(x) - x \frac{g(a) - g(-a)}{2a} - \frac{1}{2}.$$

(3.38)

The rms value of this INL as a function of a is then

$$V_{rms,INL}(a) = \sqrt{\frac{\int_{-a}^{a} (INL(x))^{2} dx}{2a}}.$$

(3.39)

By relating this rms value of INL to LSB voltage,

$$V_{rms,INL}(a) = \frac{V_{LSB}}{\sqrt{12}} = \frac{\frac{1}{2^N}}{\sqrt{12}},$$

(3.40)

we are able to obtain the optimal value for a, and what the maximum achievable number of bits (MANOB) is for a two-group stochastic flash ADC,

$$MANOB(a) = \log_2 \left( \frac{g(a) - g(-a)}{\sqrt{12} V_{rms,INL}(a)} \right).$$

(3.41)

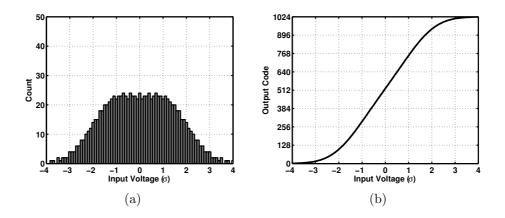

The closed-form solution of (3.41) is rather cumbersome and we would gain no additional insight by writing it out here, thus a plot of (3.41) can be seen in Fig. 3.15. There is a maximum of approximately 8.97 bits when *a* is approximately 1.078 standard deviations. This result means that the linear region between two offset Gaussian distributions, even if the number of comparator levels were infinite, is inherently limited to 8.97 bits. More importantly, if the targeted resolution is significantly less than 8.97 bits, then the comparators levels in the linear region between two offset Gaussian distributions is effectively uniformly distributed. Therefore, (3.18) can be applied if scaled by the inverse of the fraction of the comparator levels that will exist within the useful range.

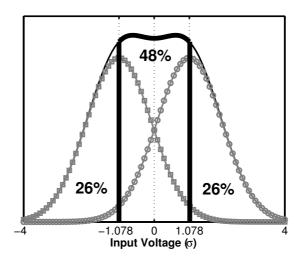

Figure 3.16: This is the combined probability density function (PDF) of comparator offset for a two-group stochastic flash ADC. Over half of the comparators fall outside of the virtual uniform distribution and are not used.

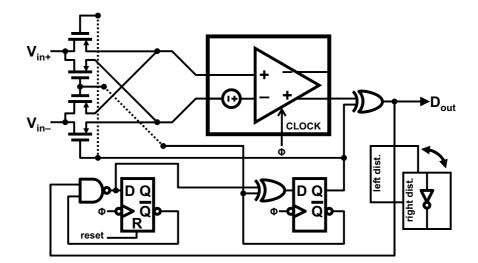

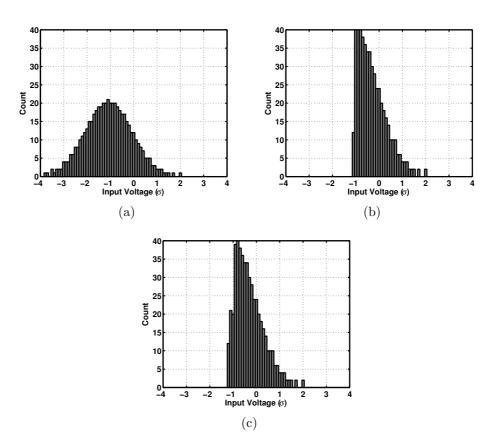

# 3.3.1 PDF Folding

One disadvantage of the two-group stochastic flash technique is that although a near uniform distribution (Fig. 3.14) is generated between the two means of the Gaussian distributions, it comes at a cost of wasted comparators. On average, 48% of comparator thresholds will reside in the useful region. This leaves 52% of comparators outside the range of the signal. These comparators continue to function and consume power, yet provide no additional information since they will always evaluate "high" or "low" whether they are in the left PDF or right PDF, respectively. This section describes a technique that folds each Gaussian PDF about its center to bring almost all of the comparators into the useful region.

Consider a comparator that has a +100mV input-referred offset. If this comparator lies in the "left" group of comparators, as defined in Fig. 3.16, then its output will always be "high" since the lowest differential voltage input in the

Figure 3.17: For clarity, only the left PDF is shown. The two circles indicate two random comparator offsets that are equal in magnitude but have opposite polarity.