### AN ABSTRACT OF THE THESIS OF

Mahmoud A. Abu-Dayeh for the degree of Master of Science in Electrical and Computer Engineering presented on October 4, 1988.

Title: <u>A Fast-Settling Folded-Cascode CMOS Operational</u>

Amplifier.

Abstract approved: Redacted for Privacy\_

David J. Allstot

A fast-settling CMOS operational amplifier using the folded-cascode topology has been designed. The design is based on a theory developed by Yang et al for the optimum settling time of two-pole systems for switched-capacitor applications. The theory states that the two poles are separated by a given factor in order to obtain a minimum small-signal settling time. The design is achieved by performing a complete small-signal analysis to gain a better understanding of the frequency and time responses of the folded-cascode op-amp. SPICE simulation results are in good agreement with the theoretical predictions.

## A Fast-Settling Folded-Cascode CMOS Operational Amplifier

by

Mahmoud A. Abu-Dayeh

A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Master of Science

Completed October 4, 1988

Commencement June 1989

### APPROVED:

## Redacted for Privacy

Associate Professor of Electrical & Computer Engineering Department in charge of major

Head of Department of Electrical & Computer Engineering

| R       | edacte | асу |  |  |

|---------|--------|-----|--|--|

| Dean o: | ()     | V   |  |  |

Date thesis is presented \_\_\_\_\_October 4, 1988

### ACKNOWLEDEMENT

The author wishes to thank his graduate committee members for their important contributions; Dr. David Allstot, Dr. Thomas Plant, Dr. Sayfe Kiaei and Dr. Robert Stalley. Special appreciation to Dr. Allstot for his patience, advice and unlimited support and encouragement. Also, the author would like to thank Magnavox Government and Industrial Electronics Company for providing partial support to realize this project.

## TABLE OF CONTENTS

| I      | INTRODUCTION                                                                      | 1      |

|--------|-----------------------------------------------------------------------------------|--------|

| II     | BASIC CIRCUITS ANALYSIS 2.1 Introduction 2.2 Common-source amplifier with passive | 6<br>6 |

|        | load                                                                              | 6      |

|        | 2.3 Cascode common-source amplifier with passive load                             | 9      |

|        | 2.4 Cascode common-source amplifier with                                          |        |

|        | cascode active load                                                               | 12     |

| III    | FREQUENCY AND STEP RESPONSES                                                      | 14     |

| IV     | SETTLING BEHAVIOR                                                                 | 19     |

| V      | ACTUAL IMPLEMENTATION                                                             | 21     |

| VI     | FURTHER IMPROVEMENT                                                               | 23     |

| VII    | CONCLUSION                                                                        | 24     |

| VIII   | BIBLIOGRAPHY                                                                      | 53     |

| Y DDEN | NTY                                                                               | 55     |

## LIST OF FIGURES

| Figu: | <u>re</u>                                                                                                                     | <u>Page</u> |

|-------|-------------------------------------------------------------------------------------------------------------------------------|-------------|

| 1.    | An ideal operational amplifier schematic diagram.                                                                             | 28          |

| 2.    | A two-stage CMOS operational amplifier.                                                                                       | 29          |

| 3.    | A class-AB CMOS operational amplifier.                                                                                        | 30          |

| 4.    | A folded-cascode CMOS operational amplifier.                                                                                  | 31          |

| 5.    | A cross section of an n-well CMOS process.                                                                                    | 32          |

| 6.    | (a) A common-source amplifier with passive load, (b) the AC equivalent circuit of the amplifier.                              | 33          |

| 7.    | The small-signal model of a MOS transistor.                                                                                   | 34          |

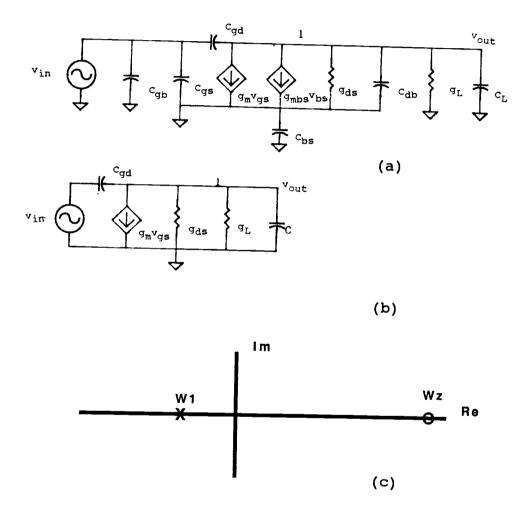

| 8.    | (a) The small-signal model of the amplifier in fig. 6a; (b) a simplified model; (c) the pole-zero locations of the amplifier. | 35          |

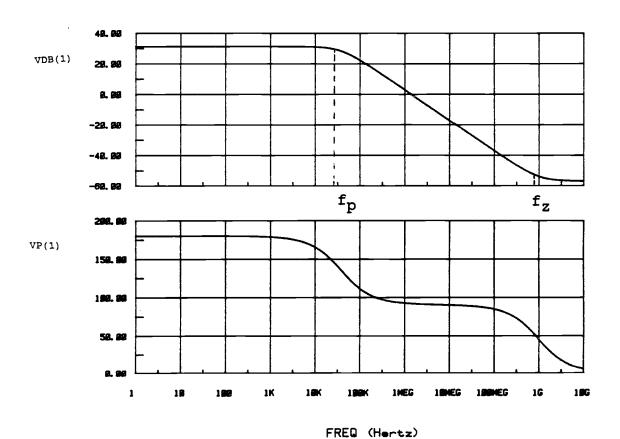

| 9.    | The simulated frequency response of the amplifier in fig. 6a.                                                                 | 36          |

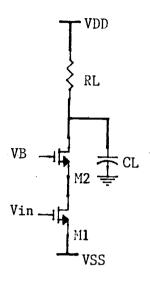

| 10.   | (a) A cascode common-source amplifier with passive load, (b) the small-signal model of the amplifier.                         | 37          |

| 10.   | c) The small-signal model of the cascode transistors, M1, and M2.                                                             | 38          |

| 11.   | The simulated frequency response of the amplifier in fig. 10a.                                                                | 39          |

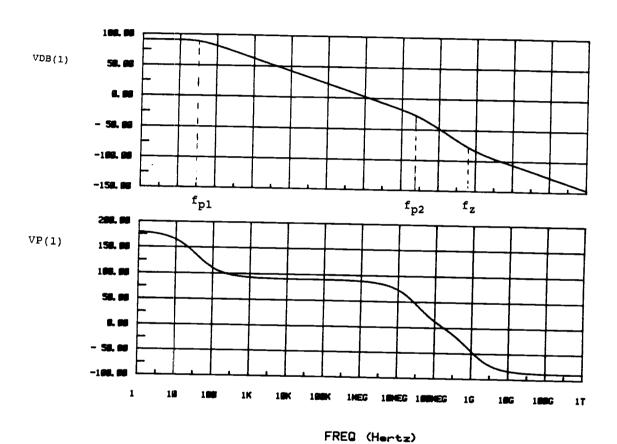

| 12.   | (a) A cascode common-source amplifier with cascode active load.                                                               | 40          |

| 12.   | <ul><li>(b) The small-signal model of the amplifier;</li><li>(c) the poles and zeros locations of the amplifier.</li></ul>    | 41          |

| 13.   | The simulated frequency response of the                                                                                       | 42          |

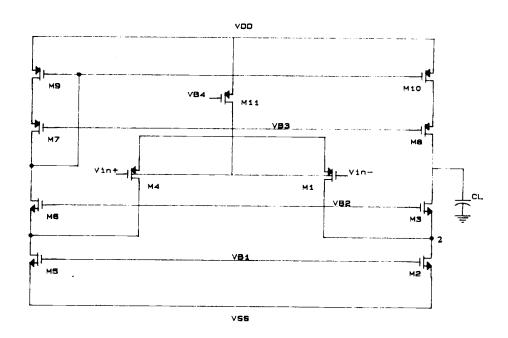

| 14. | A folded-cascode operational amplifier.                                                     | 43 |

|-----|---------------------------------------------------------------------------------------------|----|

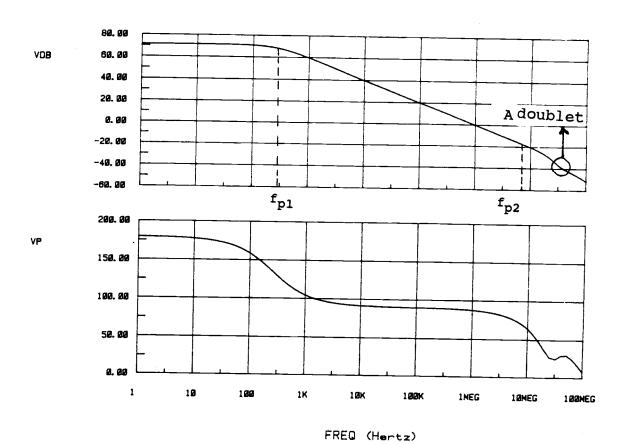

| 15. | The simulated frequency response of the amplifier in fig. 14.                               | 44 |

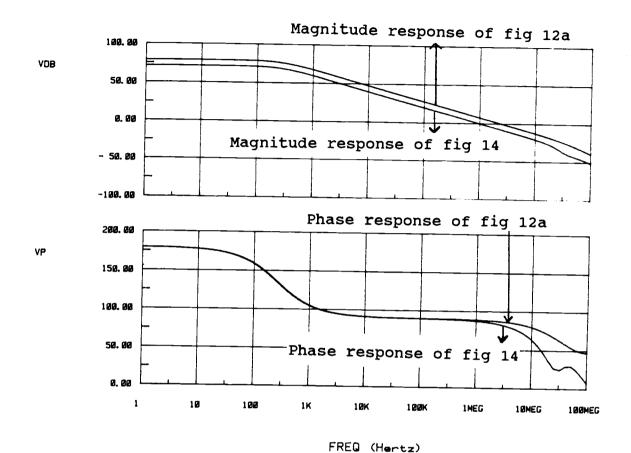

| 16. | The simulated frequency responses of the circuits in figures 12a and 14.                    | 45 |

| 17. | An op-amp in unity-gain closed-loop configuration.                                          | 46 |

| 18. | An underdamped response with an error bound, D. The settling time is $t_s$ .                | 47 |

| 19. | An underdamped response just intersecting the upper error bound and an overdamped response. | 48 |

| 20. | The optimized folded-cascode op-amp with bias circuitry.                                    | 40 |

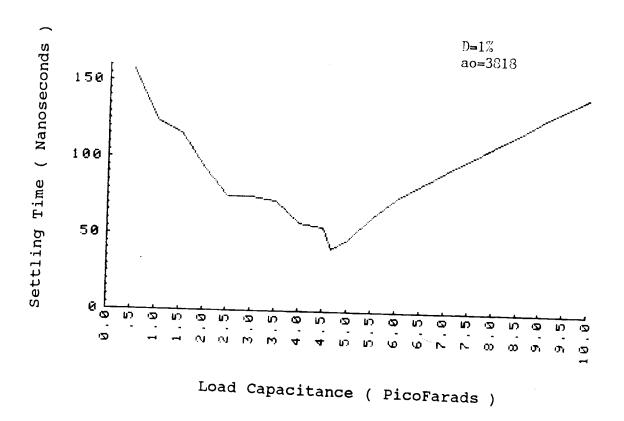

| 21. | A plot of the settling time vs. the load capacitance.                                       | 50 |

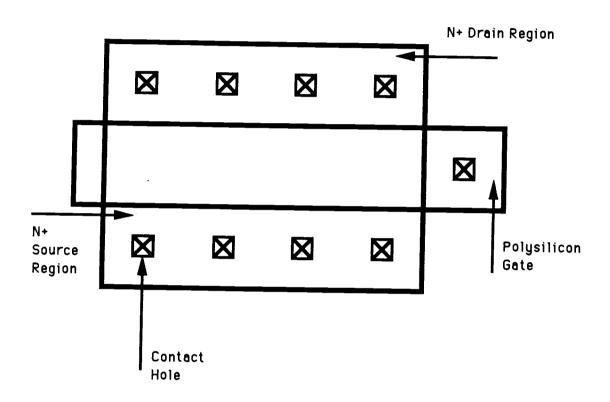

| 22. | A rectangular layout of a MOS transistor.                                                   | 51 |

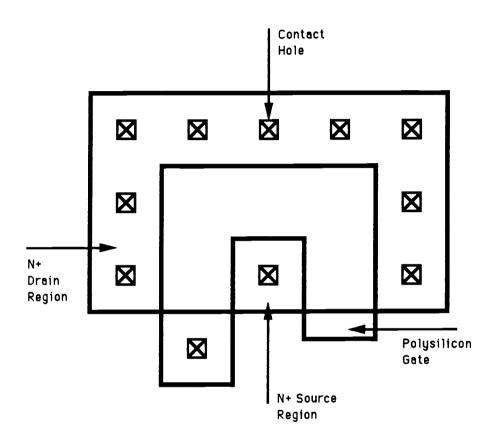

| 23. | A horseshoe layout of a MOS transistor.                                                     | 52 |

## LIST OF TABLES

| Table | <u>e</u>                                                                                                                                                                                                          | Page |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.    | A comparison between hand calculation and SPICE results for the (a) common-source amplifier, (b) cascode common-source amplifier with passive load, (c) cascode common-source amplifier with cascode active load. | 25   |

| 2.    | The optimized folded-cascode operational amplifier device sizes.                                                                                                                                                  | 26   |

| 3.    | The optimized folded-cascode operational amplifier specifications.                                                                                                                                                | 27   |

#### 1 INTRODUCTION

The electronic component known as the operational amplifier (op-amp) is a basic building block in analog In the past before the development systems. integrated circuit technology, the operational amplifier was used primarily in analog computers to implement the mathematical operations of addition, integration differentiation. However, in recent years, and after the progress that has been made in the monolithic circuit technology, a great number of op-amps may be fabricated greatly reducing chip thus on single Consequently, the range of applications has broadened enough to make the op-amp the most well-known device used in signal conditioning.

In one form, the op-amp consists of a differential input stage, a single-ended output stage, and has the following ideal characteristics [1]:

- 1) Infinite input impedance,

- 2) zero output impedance, and

- 3) infinite gain.

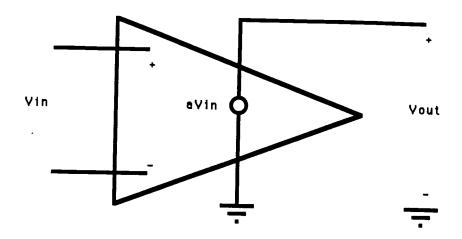

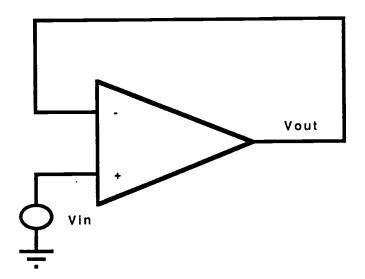

A schematic diagram of such an ideal op-amp is shown in figure 1. In practice, op-amps do not behave ideally,

but their performance can be approximated by the ideal op-amps.

In the past few years, the technology of metal-oxide-semiconductor (MOS) has been established as an efficient fabrication process. The MOS technology, when compared with the bipolar technology, is more desirable. The MOS technology uses relatively simple fabrication techniques, providing high-packing density and low power consumption. These features make the MOS technology attractive for large-scale integrated digital circuits. Recently, there was a need to use MOS technology in analog circuits where bipolar technology was previously dominating. This was necessary to realize analog-digital subsystems on the same integrated circuit using the same technology.

The performance of the MOS op-amp does not challenge that of the bipolar op-amp [2]. MOS op-amps have higher offset voltage, higher input noise, especially the 1/f component, and lower transconductance per stage. However, improvements in the control of the MOS process have lowered the offset voltage. Also, higher gain is obtained by using cascode stages, depletion load devices and the complementary MOS (CMOS) process.

CMOS op-amps can be implemented in different topologies. The two-stage topology shown in figure 2 [3] is widely used. The two-stage op-amp performance is well understood. It provides high voltage gain, wide output swing, high CMRR, and wide input common-mode range.

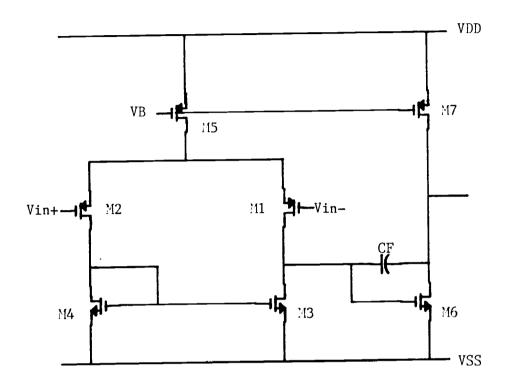

A second topology is the class-AB op-amp as shown in figure 3 [1]. The quiescent currents in the input transistors are determined by the bias voltages  $V_{B1}$  and  $V_{B2}$ . The class-AB op-amps do not show any slew-rate limiting since they can deliver to and source from a load, a current that is much larger than the quiescent current.

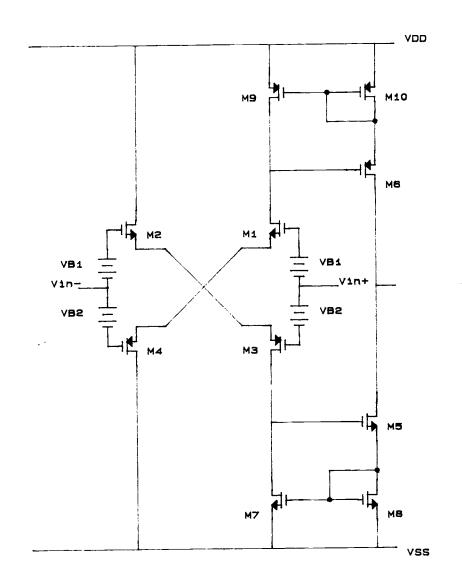

Another topology is the common-source common-gate or the folded-cascode op-amp shown in figure 4 [3]. It is a cascade of a common-source stage and a common-gate stage, whereas the two stage op-amp is a cascade of two common-source stages. The folded-cascode op-amp consists of a p-channel source-coupled pair M1 and M4 with the drains connected to the sources of the n-channel cascode devices M3 and M6. This technique is known as the current folding circuit technique [4]. The folded-cascode op-amp has a small-signal voltage gain comparable to that of the two-stage op-amp due to the cascode transistors at the output. One of the advantages of the folded-cascode topology is that the dominant pole is determined by the

load capacitance. Thus, no compensation capacitor needs be added since the load and the compensation capacitors are the same. This leads to improved frequency response and to large phase margin (compared to two-stage topology) since increasing capacitance reduces the bandwidth and increases the phase margin.

In this thesis, the folded-cascode topology is used to design a minimum settling time op-amp to be used in high-frequency switched-capacitor (SC) circuits, thus increasing the maximum operating frequency of SC filters and other SC circuits.

The settling time consists of two distinct periods [5]. The first is the slewing period which is determined by the amount of current available to charge or discharge the load capacitor. During that period, the op-amp behaves nonlinearly and the output makes the transition from the original output voltage to the vicinity of the new value. The second part is the settling period or the small-signal settling time. In this period, the op-amp behaves quasi-linearly and settles to the final value. The small-signal settling time is the significant part when working with SC circuits and will be thoroughly discussed in this thesis.

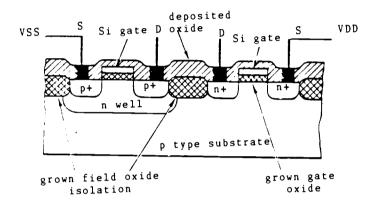

A simplified cross section of the silicon-gate 3-um n-well CMOS process used in this thesis is shown in figure 5.

The design is initiated by providing background material in chapter II.

Chapter III gives the frequency and time responses of the folded-cascode op-amp.

Chapter IV presents the small-signal settling behavior of the op-amp.

Chapter V describes the actual implementation of the design.

Chapter VI gives further improvements on the design.

Chapter VII provides summary and conclusions.

### 2 BASIC CIRCUITS ANALYSIS

## 2.1 Introduction

Although the folded-cascode op-amp is widely used, apparently it has never been fully analyzed. The architecture of the op-amp is complex, so to understand better the operation and the structure of the op-amp, some basic circuits which constitute the building blocks of the op-amp are analyzed. These circuits include:

- 1) Common-source amplifier with passive load.

- Cascode common-source amplifier with passive load.

- 3) Cascode common-source amplifier with cascode active load.

The presentation includes small-signal analysis and computer verification.

##

## A. AC equivalent circuit

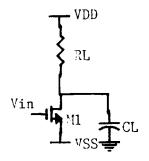

The AC equivalent circuit shown in figure 6b is obtained by [7]:

replacing all DC current sources with open circuits, and 2) replacing all DC voltage sources with short circuits.

## B. Small-signal model

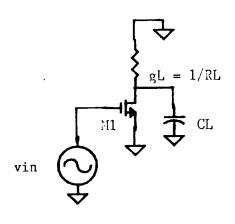

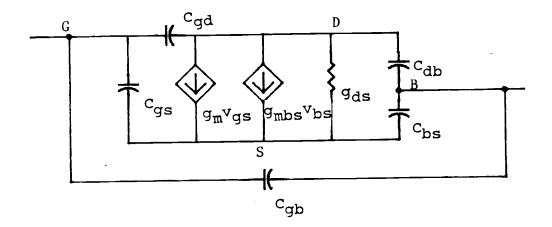

The small-signal model of a MOS transistor is shown in figure 7 [7]. Replacing the active device of the circuit in figure 6b with the small-signal model, the circuit becomes as shown in figure 8a. With  $v_{\rm bs}=0$ , and with  $c_{\rm gs}$  directly loading the input source,  $v_{\rm in}$ , this circuit can be simplified as shown in figure 8b,

where

$$C = C_{I_i} + C_{db}, \tag{1}$$

$$g_{L} = g_{ds'} \tag{2}$$

and

or

$$g_{L} = 1/R_L. \tag{3}$$

Ċ.

## C. Transfer function

The voltage transfer function is obtained by applying Kirchoff's Current Law (KCL) at node 1 in figure 8b:

$$v_{out}[s(C_{gd1}+C)(g_{L}+g_{L})]+v_{in}(g_{m}-sC_{gd1}) = 0,$$

(4)

$$\frac{v_{\text{out}}}{v_{\text{in}}} = \frac{-(g_{\text{m}} - sC_{\text{gd}})}{s(C_{\text{gd}} + C) + g_{\text{L}} + g_{\text{L}}}.$$

(5)

As shown in figure 8c, the transfer function has a righthalf plane (RHP) zero at a radian frequency of

$$W_{Z} = \frac{g_{m}}{c_{qd}}, \tag{6}$$

and a left-half plane (LHP) pole at

$$W_1 = \frac{-(g_L + g_L )}{c + c_{qd}}, \qquad (7)$$

or approximately,

$$W_1 = \frac{-(g_{L\downarrow} + g_{L\uparrow})}{c_{L\downarrow}}, \tag{8}$$

with  $C_L >> C_{gd} + C_{db}$ .

Equation (7) shows the fundamental principle that the pole frequency at a node is determined by the inverse of the RC product at that node, or

LHP pole =

$$\frac{g_{out}}{c_{out}} = \frac{1}{r_{out}c_{out}}$$

(9)

The small-signal low-frequency voltage gain,  $a_0$ , is obtained from equation (5) with s  $--\rightarrow$  0, and is given by:

$$a_{O} = \frac{-g_{m}}{g_{L} + g_{L}}.$$

(10)

## D. Computer simulation

The circuit of figure 8a was simulated using SPICE2

[8] with the resulting frequency response shown in figure

9.

## E. Summary of results

Table 1a shows a comparison between hand analysis and SPICE results. As shown, the error percentages are very small, indicating that hand calculations are in good agreement with SPICE results.

# 2.3 Cascode common-source amplifier with passive load (figure 10a.)

Following the same procedure as in section 2.2, the simplified small-signal model of the amplifier is shown in figure 10b,

where

$$c_1 = c_{db2} + c_{qd2} + c_{L'}$$

(11)

and

$$c_2 = c_{db1} + c_{qs2} + c_{bs2}.$$

(12)

Applying KCL at nodes 1 and 2, the following voltage transfer function is obtained:

$$\frac{v_{\text{out}}}{v_{\text{in}}} = \frac{-g_{\text{s2}}(g_{\text{m1}} - sC_{\text{gd1}})}{As^2 + Bs + D},$$

(13)

where

$$A = C_2(C_1 + C_{qd1}), (14)$$

$$B = (C_{qd1} + C_1) (g_{ds2} + g_{L\uparrow}) + C_2 (g_{s2} + g_{ds1} - g_{ds2}g_{s2}), \quad (15)$$

$$D = (g_{ds2} + g_{L\uparrow}) (g_{s2} + g_{ds1} - g_{ds2}g_{s2}), \tag{16}$$

and

$$g_{s2} = g_{m2} + g_{mbs2} + g_{ds2}.$$

(17)

$G_{L}\downarrow$  and  $g_{L\uparrow}$  are the conductances at the output node and are given by:

$$g_{L\downarrow} = \frac{g_{ds1}g_{ds2}}{g_{s2}+g_{ds1}},\tag{18}$$

and

$$g_{L\uparrow} = 1/R_{L}. \tag{19}$$

The transfer function shows a RHP zero given by :

$$W_{z} = \frac{g_{m1}}{c_{ad1}}, \qquad (20)$$

and using the results from section 2.2, the two LHP poles are:

$$W_1 = \frac{-\left(g_L \downarrow + g_L \uparrow\right)}{c_1},\tag{21}$$

or

$$W_1 = \frac{-\left(g_L \downarrow + g_L \uparrow\right)}{C_L}, \tag{22}$$

for

$$c_L >> c_{db2} + c_{qd2}$$

and

$$W_2 = \frac{-(g_{s2} + g_{ds1})}{c_2}, \tag{23}$$

or

$$W_2 = \frac{-g_{m2}}{c_2}, \tag{24}$$

for

$g_{m2} >> g_{ds1} + g_{mbs2} + g_{ds2}$

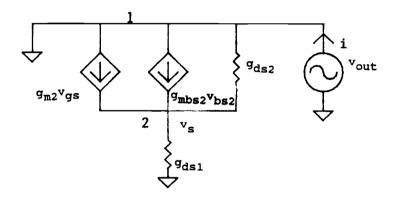

The  $g_{L}$  expression is obtained by carrying-out the following derivation: The small-signal model of the cascode devices is shown in figure 10c. Applying KCL at nodes 1 and 2, the following equations are obtained:

$$v_{s} = \frac{i}{g_{ds1}}, \tag{25}$$

and

$$i = g_{ds2}v_{out}-g_{s2}v_{s}. \tag{26}$$

Substituting equation (25) into (26),

$$g_{LL} = \frac{i}{v_{out}} = \frac{g_{ds1}g_{ds2}}{g_{s2} + g_{ds2}}.$$

(27)

The small-signal low frequency voltage gain is given by :

$$a_{o} = \frac{-g_{m1}g_{s2}}{(g_{L} + g_{L})(g_{s2} + g_{ds1} - g_{ds2}g_{s2})},$$

(28)

or

$$a_{o} = \frac{-g_{m1}}{g_{L} + g_{L}}, \qquad (29)$$

for  $g_{s2} \gg g_{ds1} - g_{ds2}g_{s2}$ .

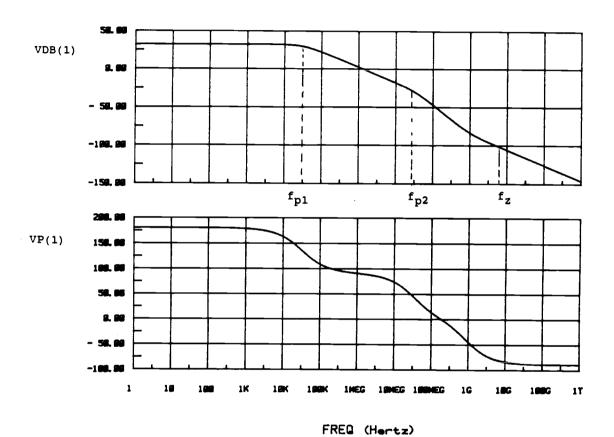

The frequency response of the amplifier obtained by computer simulation is shown in figure 11. Also, table 1b shows a comparison between hand analysis and SPICE results. As shown, the error percentages are small,

indicating that hand calculations are in good agreement with SPICE results.

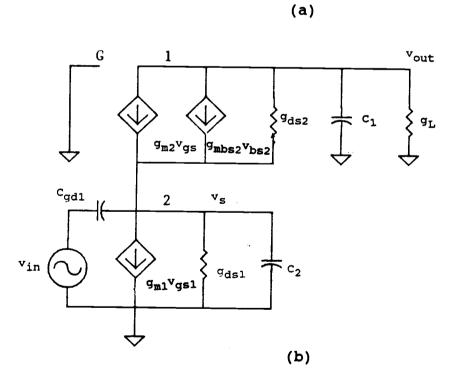

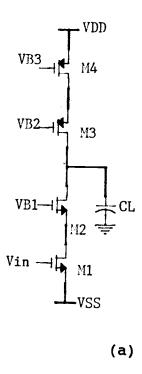

# 2.4 Cascode common-source amplifier with cascode active load (figure 12a.)

Using nodal analysis, the voltage transfer function of the cascode common-source circuit in figure 12b is:

$$\frac{v_{\text{out}}}{v_{\text{in}}} = \frac{-g_{\text{s2}}(g_{\text{s3}} + \text{sC}_3 + g_{\text{ds4}})(g_{\text{m1}} - \text{sC}_{\text{gd1}})}{K_1 s^3 + K_2 s^2 + K_3 s + K_4},$$

(30)

where

$$K_1 = (C_1 + C_{qd1}) C_2 C_3, (31)$$

$$K_{2} = C_{3}(C_{gd1}+C_{1})g_{ds2}+C_{3}C_{2}(2g_{s2}+g_{ds1}) + C_{2}(C_{dq1}+C_{1})(g_{s3}+g_{ds4}),$$

(32)

$$K_{3} = g_{s2}(g_{s3}+2g_{ds2})C_{3}+g_{ds2}(g_{s3}+g_{ds4})(C_{gd1}+C_{1})$$

$$+g_{ds2}(2g_{s2}+g_{ds1})C_{3}, \qquad (33)$$

and

$$K_4 = g_{ds2}(g_{s3} + g_{ds4})(2g_{s2} + g_{ds1}) + g_{ds3}g_{s3}g_{s2}$$

$$-g_{s2}(g_{ds3} + 2g_{ds2})(g_{s3} + g_{ds4}). \tag{34}$$

As expected, the transfer function has three LHP poles, with one pole at each node :

$$W_1 = \frac{-g_{L} + g_{L}}{c_1}, \qquad (35)$$

$$W_2 = \frac{-g_{s2} + g_{ds1}}{c_2}, \tag{36}$$

$$W_3 = \frac{-g_{s3} + g_{ds4}}{c_3}, \tag{37}$$

and a RHP zero :

$$W_{z1} = \frac{g_{m1}}{c_{gd1}}, \tag{38}$$

and a LHP zero:

$$W_{z2} = \frac{-(g_{s3} + g_{ds4})}{c_3}. (39)$$

As shown in figure 12c, there is (fortunately) a polezero cancellation;

$$W_{22} = W_3. \tag{40}$$

Using the results from the previous sections, the smallsignal gain can be approximated by :

$$a_{0} = \frac{-g_{m1}}{g_{L}\downarrow + g_{L}\uparrow}, \tag{41}$$

where

$$g_{L\downarrow} = \frac{g_{ds1}g_{ds2}}{g_{s2}+g_{ds1}},$$

(42)

and

$$g_{L} \uparrow = \frac{g_{ds3}g_{ds4}}{g_{s3}+g_{ds4}}.$$

(43)

The frequency response of the amplifier is shown in figure 13. Also, table 1c shows a comparison between hand analysis and SPICE results. As shown, the error percentages are small, indicating that hand calculations are in good agreement with SPICE results.

## 3 FREQUENCY AND STEP RESPONSES

The folded-cascode op-amp has been used in a wide range of applications, mainly high-frequency SC circuits. One advantage of this op-amp, as mentioned before, is that the dominant pole is contributed by the load capacitor. Thus, no compensation capacitor is needed providing a good phase margin and a fast settling time [9].

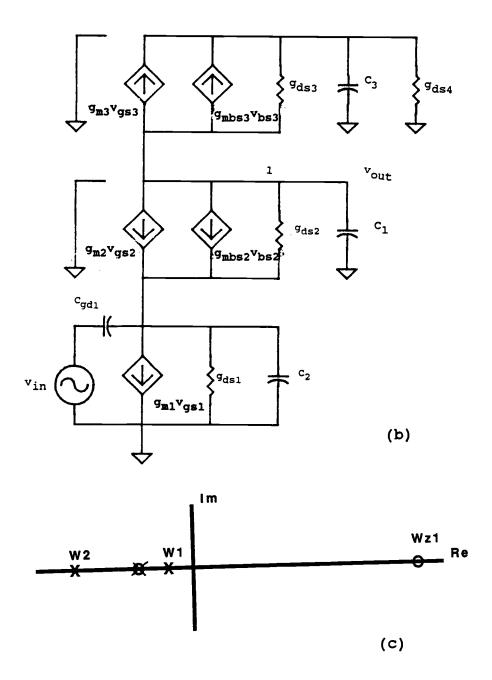

In this chapter, the folded-cascode op-amp is analyzed. The small-signal analysis is necessary to realize expressions for the most dominant poles and to develop an optimum two-pole model. Then applying the theory developed in [10], an optimum design is realized to obtain small-signal settling time for a given load capacitance.

The op-amp shown in figure 14 is computer simulated to obtain the frequency response which shows that the opamp has two poles and a pole-zero doublet (a doublet occurs when a pole and a zero do not cancel exactly) as shown in figure 15. The doublet is located far from the unity-gain frequency so it has a negligible effect on the transfer function. The op-amp can then be well-approximated by a simple two-pole model. The open-loop

transfer function of the model for small-signal analysis can be approximated by a second-order system,

$$a(s) = \frac{a_0}{(1+s/W_1)(1+s/W_2)},$$

(44)

where  $\mathbf{a}_0$  is the DC gain of the op-amp,  $\mathbf{W}_1$  and  $\mathbf{W}_2$  are the frequencies of the LHP poles.

To determine  $W_1$  and  $W_2$ , the cascode common-source circuit in figure 12a is used. The frequency responses of both circuits 12a and 14 are shown in figure 16. As shown, except at very high frequencies not of interest, the phase responses are in good agreement with each other ( the unity-gain phase margins of the op-amp and the cascode common-source amplifier are  $87.6^{\circ}$  and  $87.4^{\circ}$  respectively.) For the magnitude responses, the response of the op-amp is shifted down because it has a lower DC gain. However, the locations of the poles will not be affected. Then, the frequency response of the op-amp can be well-approximated by that of the cascode common-source amplifier in figure 12a. Thus  $W_1$  and  $W_2$  can be determined by the equations derived in chapter 2:

$$W_2 = \frac{-(g_{s3} + g_{ds1} + g_{ds2})}{c_2}, \tag{45}$$

or

$$W_2 = \frac{-g_{s3}}{c_2}, \tag{46}$$

for

and

$$W_{1} = \frac{-(g_{L} + g_{L})}{c_{1}}, \tag{47}$$

or

$$W_1 = \frac{-\left(g_L \downarrow + g_L \chi\right)}{C_L},\tag{48}$$

for

$$c_L >> c_{db3} + c_{gd3} + c_{db8} + c_{gd8}$$

where

$$C_2 = C_{gd1} + C_{gs1} + C_{gb1} + C_{db1} + C_{gd2} + C_{db2} + C_{gs3} + C_{bs3},$$

(49)

$$C_1 = C_L + C_{gd3} + C_{db3} + C_{gd8} + C_{db8},$$

(50)

$$g_{L} = \frac{g_{ds10} g_{ds8}}{g_{ds10} + g_{s8}}, \tag{51}$$

and

$$g_{L} \downarrow = \frac{(g_{ds1} + g_{ds2})g_{ds3}}{g_{ds1} + g_{ds2} + g_{s3}}.$$

(52)

The transfer function in the unity-gain closed-loop configuration (figure 17) is given by:

$$A(s) = \frac{A_0}{(s/W_0)^2 + 2k(s/W_0) + 1},$$

(53)

where

$$A_{O} = \frac{a_{O}}{1+a_{O}}, \tag{54}$$

$$W_{O} = (W_{1}W_{2}(1+a_{O}))^{1/2}, (55)$$

and k, the damping factor, is given by :

$$k = \frac{W_1 + W_2}{2W_0}.$$

(56)

Defining the pole separation factor as

$$\beta = W_2/W_1, \tag{57}$$

equation (56) becomes:

$$k = \frac{1+\beta}{2((1+a_0))^{1/2}}.$$

(58)

It is well-stated [11] that the second-order system possessing two poles in the LHP has three possible responses to a step input. Each response is directly related to the damping factor k. Equation (53) is solved for the inverse Laplace transform to obtain the following analytical expressions for the normalized responses [10]:

1) k > 1, overdamped (exponentially approaching the steady-state value):

$$v_{o}(t) = 1 - \frac{1}{2(k^{2}-1)^{1/2}} [1/k_{1}exp(-k_{1}W_{o}t) - 1/k_{2}exp(-k_{2}W_{o}t)],$$

(59)

where

$$k_1 = k - (k^2 - 1)^{1/2},$$

(60)

and

$$k_2 = k + (k^2 - 1)^{1/2}$$

(61)

2) k = 1, critically damped (exponentially

approaching the steady-state value):

$$v_o(t) = 1 - (1+W_ot) \exp(-W_ot)$$

. (62)

3) k < 1, underdamped (overshoot followed by damped response):

$$v_o(t) = 1 - [k/(1-k^2)^{1/2} \sin((1-k^2)^{1/2} W_o t) + \cos((1-k^2)^{1/2} W_o t)] \exp(-kW_o t).$$

(63)

### 4 SETTLING BEHAVIOR

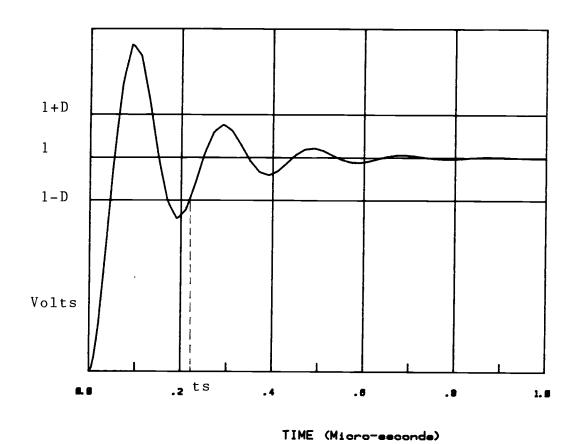

Settling time is a very important characteristic in analog sampled-data system applications, especially in high-frequency SC circuits. The settling time affects the speed of analog signal processing, since the amplifier has to settle within a predetermined error bound of the final value of the applied signal to avoid errors in processing that signal. Thus the settling time, t<sub>s</sub>, can be defined [12] as the time required for the output voltage to settle within a specified input step excitation region as shown in figure 18.

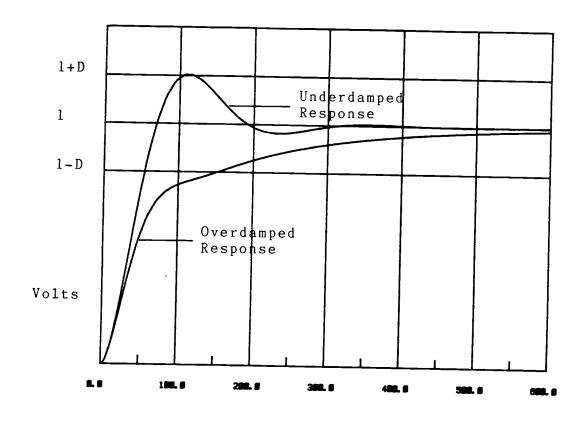

The minimum settling time is obtained when the system response is underdamped. This is illustrated in figure 19. As shown, the overdamped response takes longer time to rise and intersect the lower error bound. In the case of the underdamped response, the minimum settling time is obtained when the first peak of the response just intersects the upper error bound. The position of the first peak is obtained by differentiating equation (63) with respect to Wot, and the derivative is set equal to zero. The first peak is found to occur at

$$W_{o}t = \frac{\pi}{(1-k^2)^{1/2}}.$$

(64)

The value of the first peak is obtained when equation (64) is substituted into (63),

$$v_0 = 1 + \exp(-k \pi/(1-k^2)^{1/2}).$$

(65)

Setting that value equal to the upper error bound, 1+D, equation (65) becomes:

$$1+D = 1+\exp(-k\pi/(1-k^2)^{1/2}). \tag{66}$$

Substituting equation (58) into (66) gives [10]:

$$\beta = \frac{4 (1+a_0)}{1+(\pi/\ln D)^2},$$

(67)

where  $oldsymbol{eta}$  is the pole separation factor.

#### 5 ACTUAL IMPLEMENTATION

The frequency and time responses of the folded-cascode op-amp are now well understood. The theory established in [10] is applicable to the folded-cascode op-amp after it was well-approximated by a two-pole system. The theory states that for any two-pole system, a minimum settling time is obtained when the two poles are separated such that equation (67) is satisfied for given a and D, or

$$\mathbf{w}_2 = \boldsymbol{\beta} \, \mathbf{w}_1 \,, \tag{68}$$

or equivalently from equations (46) and (48),

$$\frac{g_{s3}}{c_2} = \frac{(g_{L\downarrow} + g_{L\uparrow})}{c_L}.$$

(69)

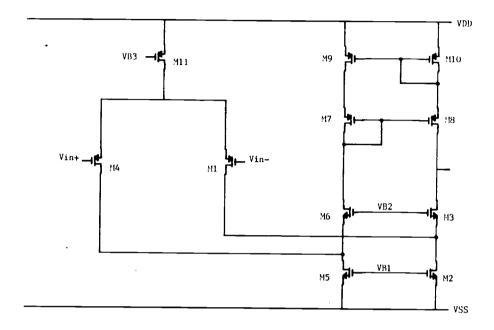

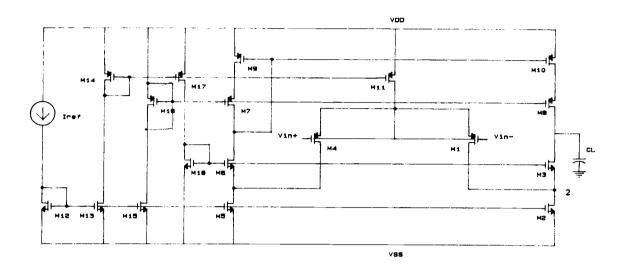

The folded-cascode topology is used to design an op-amp optimized for a given specific load capacitor value to obtain a minimum small-signal settling time. The biasing currents and device sizes are determined by satisfying equation (69) for a given load capacitance ( $C_L$  = 5 pF). The circuit schematic and device sizes are shown in figure 20 and table 2 respectively.

It is clearly evident from the previous analysis that the small-signal settling time of the op-amp is a strong function of the load capacitance. This is demonstrated by the graph in figure 21. The graph is

obtained by applying a small-signal step (20 mV) to the op-amp in the unity-gain configuration. Also, it is clearly evident from the graph that increasing or decreasing  $C_L$  beyond the optimum value ( $C_L = 5$  pF) would slow the response speed of the op-amp. This is in agreement with the discussion in chapter 4 about the settling time and the type of response. The minimum settling time occurs when the response is underdamped and the first peak of the response just intersects the upper error bound.

### 6 FURTHER IMPROVEMENT

The type of layout technique has a significant effect on the small-signal settling time and the load capacitance plot. This can be easily observed when equation (69) is rewritten as:

$$c_{L} = \frac{(g_{L\downarrow} + g_{L\uparrow})c_{2}}{g_{s3}}, \tag{70}$$

where  $C_2$  is the parasitic capacitance at node 2.  $C_2$  depends among other things on the layout technique. The plot in figure 21 was obtained by assuming the typical rectangular layout shown in figure 22. By selecting a layout technique that reduces  $C_2$ , the plot can be shifted to the right, driving larger load, thus further improving the previous optimized design. One technique is the horseshoe layout shown in figure 23. Transistors M1, M2, and M3 are laid out using that technique.  $C_2$  was reduced by 5%, indicating that some improvement on the plot is possible.

### 7 CONCLUSION

small-signal analysis of the folded-cascode operational amplifier is complete. The op-amp possessed several poles and zeros but an optimum two-pole model was realized representing the two most dominant left-halfplane poles. Using this model, a fast settling op-amp, to be used in high-frequency switched-capacitor circuits, designed. The design was based on a relationship that specifies the separation between the two poles. By satisfying that relationship, a minimum small-signal time is obtained for an optimum load capacitance  $(C_{T_i} = 5 pF)$ . The specifications of the optimized op-amp are shown in table 3.

| Parameter      | SPICE<br>Results | Hand<br>Calculation | Error<br>Percentage |

|----------------|------------------|---------------------|---------------------|

| a <sub>O</sub> | -35.91           | -35.89              | 0.06                |

| fp             | 38.02E3 Hz       | 37.97E3 Hz          | 0.13                |

| f <sub>z</sub> | 97.72E7 Hz       | 98.89E7 Hz          | 1.20                |

(a)

| Parameter       | SPICE<br>Results | Hand<br>Calculation | Error<br>Percentage |

|-----------------|------------------|---------------------|---------------------|

| a <sub>O</sub>  | -38.08           | -39.05              | 2.55                |

| f <sub>p1</sub> | 31.80E3 Hz       | 32.98E3 Hz          | 3.71                |

| f <sub>p2</sub> | 32.50E6 Hz       | 33.60E6 Hz          | 3.38                |

| f <sub>z</sub>  | 96.72E7 Hz       | 90.16E7 Hz          | 6.78                |

(b)

| Parameter       | SPICE<br>Results | Hand<br>Calculation | Error<br>Percentage |

|-----------------|------------------|---------------------|---------------------|

| a <sub>o</sub>  | -33.74E3         | -34.07E3            | 0.98                |

| f <sub>p1</sub> | 34.67 Hz         | 33.66 Hz            | 2.91                |

| f <sub>p2</sub> | 30.60E6 Hz       | 31.70E6 Hz          | 3.60                |

| f <sub>z</sub>  | 90.10E7 Hz       | 85.01E7 Hz          | 5.55                |

(c)

Table 1 A comparison between hand calculation and SPICE results for the (a) common-source amplifier, (b) cascode common-source amplifier with passive load, (c) cascode common-source amplifier with cascode active load.

| Ml | 280/6  | M10 | 280/6  |

|----|--------|-----|--------|

| M2 | 280/10 | M11 | 280/6  |

| МЗ | 140/10 | M12 | 279/10 |

| M4 | 280/6  | M13 | 558/10 |

| M5 | 280/10 | M14 | 1645/6 |

| M6 | 140/10 | M15 | 140/10 |

| M7 | 280/6  | M16 | 95/6   |

| M8 | 280/6  | M17 | 410/6  |

| M9 | 280/6  | M18 | 63/10  |

|    |        |     |        |

Table 2 The optimized folded-cascode operational amplifier device sizes ( um. )

| AC gain              | 71.6 dB         |

|----------------------|-----------------|

| Load capacitance     | 5 pF            |

| Unity-gain bandwidth | 8 MHz           |

| Phase margin         | 69 <sup>O</sup> |

| Gain margin          | 40 dB           |

| Slew rate            | 18 V/uS         |

| Settling time        | 41 ns +5 15?    |

| DC offset voltage    | 1 mV            |

| Power dissipation    | 8.85 mW         |

| Power Supplies       | ± 5 V           |

|                      |                 |

Table 3 The optimized folded-cascode operational amplifier specifications.

Fig. 1 An ideal operational amplifier schematic diagram.

Fig. 2 A two-stage CMOS operational amplifier.

Fig. 3 A class-AB CMOS operational amplifier.

Fig. 4 A folded-cascode CMOS operational amplifier.

Fig. 5 A cross section of an n-well CMOS process [6].

(a)

(b)

Fig. 6 (a) A common-source amplifier with passive load, (b) The AC equivalent circuit of the amplifier.

Fig. 7 The small-signal model of a MOS transistor.

Fig. 8 (a) The small-signal model of the amplifier in fig. 6a; (b) a simplified model; (c) the polezero locations of the amplifier.

Fig. 9 The simulated frequency response of the amplifier in fig. 6a.

Fig. 10 (a) A cascode common-source amplifier with passive load, (b) the small-signal model of the amplifier.

(c)

Fig. 10 A (c) The small-signal model of the cascode transistors, M1, M2.

Fig. 11 The simulated frequency response of the amplifier in fig. 10a.

Fig. 12 (a) A cascode common-source amplifier with cascode active load.

$$C1 = CL + Cgd2 + Cdb2 + Cgd3 + Cdb3$$

$C2 = Cdb1 + Cbs2 + Cgs2$

$C3 = Cgs3 + Cbs3 + Cgd4 + Cdb4$

Fig. 12 A (b) The small-signal model of the amplifier, (c) the poles and zeros locations of the amplifier.

Fig. 13 The simulated frequency response of the amplifier in fig. 12a.

Fig. 14 A folded-cascode operational amplifier.

Fig. 15 The simulated frequency response of the amplifier in fig. 14.

Fig. 16 The simulated frequency responses of the circuits in figures 12a and 14.

Fig. 17 An op-amp in unity-gain closed-loop configuration.

Fig. 18 An underdamped response with an error bound, D. The settling time is  $t_{\rm s}$ .

TIME (Nano-econde)

Fig. 19 An underdamped response just intersecting the upper error bound and an overdamped response.

Fig. 20 The optimized folded-cascode op-amp with bias circuitry.

Fig. 21 A plot of the settling time vs. the load capacitance.

Fig. 22 A rectangular layout of a MOS transistor.

Fig. 23 A horseshoe layout of a MOS transistor.

## VIII BIBLIOGRAPHY

- [1] P. R. Gray and R. G. Meyer, <u>Analysis and Design of</u>

<u>Analog Integrated Circuits</u>, 2nd edition, New York: Wiley

1982.

- [2] D. A. Hodges, P. R. Gray and R. W. Brodersen, "Potential of MOS technologies for analog integrated circuits," IEEE J. Solid-State Circuits, vol. sc-13, no. 3, pp. 285-293, June 1978.

- [3] P. R. Gray and R. G. Meyer, "MOS operational amplifier design A tutorial overview," IEEE J. Solid-State Circuits, vol. sc-17, no. 6, pp. 969-982, December 1982.

- [4] D. B. Ribner and M. A. Copeland, "Design techniques for cascoded CMOS op-amps with improved PSRR and common-mode input range," IEEE J. Solid-State Circuits, vol. sc-19, no. 6, pp. 919-925, December 1984.

- [5] C. T. Chuang, "Analysis of the settling behavior of an operational amplifier," IEEE J. Solid-State Circuits, vol. sc-17, no.1, pp. 74-80, February 1982.

- [6] S. L. Hurst, <u>Custom-Specific Integrated Circuits--</u>

<u>Design and Fabrication</u>, 1st edition, New York, Marcell

Dekker, 1985.

- [7] D. J. Allstot, <u>CMOS Analog Circuit Design</u>, EE519 Course Notes, Oregon State University, Spring 1987.

- [8] A. Vladimirescu and S. Liu, "The simulation of MOS integrated circuits using SPICE2," ERL Memo ERL M80/7, Eletron. Res. Lab., Univ. of California, Berkeley, October 1980.

- [9] P. E. Allen and D. Holberg, <u>CMOS Analog Circuit</u>

<u>Design</u>, Holt, Rinehart and Winston, The Dryden Press,

Saunders College Publishing, 1987.

- [10] H. C. Yang, J. R. Ireland and D. J. Allstot,

"Improved Operational Amplifier Compensation Techniques

for High-Frequency Switched-Capacitor Circuits,"

Proceedings of the 30th Midwest Symposium on Circuits and

Systems, New York, pp. 952-955, August 1987.

- [11] S. Rosenstark, <u>Feedback Amplifier Principles</u>, New York: Macmillan, 1986.

- [12] J. Dostal, <u>Operational Amplifiers</u>, Elsevier Scientific Publishing Company, 1981.

## APPENDIX

## Appendix A. Simulation programs SPICE input file for the circuit in Fig. 6a.

SPICE input file for the circuit in Fig. 10a.

```

CASCODE COMM-SOUR AMP ( RESISTIVE LOAD )

**

.MODEL NIO NMOS LEVEL=2 VTO=0.75 KP=40U GAMMA=0.17 PHI=0.52

+TOX=60N UCRIT=4000 DEXP=0.1 XJ=0.5U LD=0.3U PB=0.82

+CJSW=0.3N CGD0=0.173N CGSD=0.173N CGBD=0.1N JS=18U AF=1.25

+KF=1E-27 MJ=0.5 MJSW=0.5 LAMBDA=0.033 CJ=0.055M

**

.OPTIONS NOMOD

**

M1 2 1 5 5 N10 W=40U L=10U AS=360P AD=360P PS=58U PD=58U

**

VDD 10 0 GC 5

VSS 5 0 DC -5

VSS 5 0 DC -5

VSS 5 0 DC -3.75

**

CL 4 0 5P

R 10 4 1MEG

**

.TF V(4) VIN

.AC DEC 10 1 1T

**

.PRINT AC VDB(4) VP(4)

.PLOT AC VDB(4) VP(4)

.PLOT AC VDB(4) VP(4)

.CRAPH AC VDB(4) VP(4)

.END

```

SPICE input file for the circuit in Fig. 12a.