#### AN ABSTRACT OF THE DISSERTATION OF

<u>Xuefeng Chen</u> for the degree of <u>Doctor of Philosophy</u> in <u>Electrical and Computer Engineering</u> presented on <u>March 15, 2007</u>.

Title: <u>A Wideband Low-Power Continuous-Time Delta-Sigma Modulator for Next Generation</u> Wireless Applications.

Abstract approved:

#### Gábor C. Temes

Delta-Sigma ( $\Delta\Sigma$ ) analog-to-digital converters (ADCs) are widely used in wireless transceivers. Recently, continuous-time (CT)  $\Delta\Sigma$  ADCs gain growing interest in wireless applications for their lower power consumption and wider input bandwidth as compared with the discrete-time (DT) counterparts.

In this thesis, a wideband low-power CT  $\Delta\Sigma$  modulator for next generation wireless applications is proposed to achieve 10-bit dynamic range within a 25 MHz signal bandwidth. On the system level, a low-power, mainly feed-forward architecture is used to realize the loop filter. Feed-in branches are added and optimized to eliminate the out-of-band peaking in the signal transfer function. On the circuit level, two-stage operational amplifiers with class-AB output stages are used to implement low-power active RC integrators. Capacitor tuning is used to compensate the variation of RC time constants. In addition, a fast current adder, an 11-level internal flash ADC and three current feedback DACs are also integrated on the chip which was manufactured in TSMC 0.18  $\mu$ m CMOS technology. The test results show that the modulator draws less than 10 mA from the 1.8 V supply voltage. © Copyright by Xuefeng Chen

March 15, 2007

All Rights Reserved

### A Wideband Low-Power Continuous-Time Delta-Sigma Modulator for Next Generation Wireless Applications

by Xuefeng Chen

### A DISSERTATION

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented March 15, 2007

Commencement June 2007

Doctor of Philosophy dissertation of Xuefeng Chen presented on March 15, 2007.

APPROVED:

Major Professor, representing Electrical and Computer Engineering

Director of the School of Electrical Engineering and Computer Science

Dean of the Graduate School

I understand that my dissertation will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my dissertation to any reader upon request.

Xuefeng Chen, Author

#### ACKNOWLEDGEMENTS

I wish to express my sincere gratitude to my major professor, Dr. Gábor C. Temes. I feel very honored and privileged to have worked under his supervision. I greatly benefited from his deep intuition and extensive knowledge of system and circuit design, from his invaluable teaching and research skills, and from his guidance in writing papers/thesis and making presentations.

I would like to thank Prof. Un-Ku Moon, Prof. Huaping Liu, Prof. Zhongfeng Wang, Prof. Pavan Kumar Hanumolu and Prof. Jack Higginbotham for serving on my committee.

I am grateful to my close friends Zhenyong Zhang, Qingdong Meng and Yan Wang, for their generous help in both the research and personal life. In particular, I cherish the days living with Zhenyong who is such a nice roommate. Qingdong is always a good elder brother. Yan greatly helped me in designing some circuit blocks of this work.

I also want to express my appreciation to all my colleagues and ex-colleagues in the analog and mixed-signal group. My earliest days in the U.S. could have been much tougher if there was no generous and thoughtful help from Jipeng Li and Xuesheng Wang. It was Jose Silva who helped me a lot to gain the background knowledge on the Delta-Sigma data converters. I have also benefited much from the discussion with Zhimin Li.

I would like to thank Dr. Mustafa Keskin at Qualcomm for a fruitful summer internship. I had a special appreciation for Paul Ferguson at Analog Devices, for giving me the opportunity to do the internship at ADI and opening the door to the continuous-time Delta-Sigma ADCs to me.

For their important contributions to this work, I wish to thank Yan Wang, Yoshihisa Fujimoto, Yusuke Kanazawa and Pascal Lo Re. I am indebted to Dr. Jesper Steensgaard and Dr. Richard Schreier for their help with system-level design. I am thankful to Paul Ferguson,

Jose Silva and Jeff Gealow for their invaluable feedback on testing issues. I appreciate George Corrigan and Keith Moore at Hewlett Packard, for their assistance with FIB modifications. This work would not have been possible without the generous financial support provided by Sharp Corporation.

I am very grateful to my parents and sister, who demonstrated in so many admirable ways their unconditional love and support throughout my life. I also sincerely appreciate my parents-in-law, for their great help during their staying with us in the U.S.

Finally, I want to express my deepest gratitude to my wife, for her genuine care, understanding and love throughout my 42-month Ph.D. candidate life.

# TABLE OF CONTENTS

|    |                                                           | Page |

|----|-----------------------------------------------------------|------|

| 1. | INTRODUCTION                                              | 1    |

|    | 1.1. Motivation                                           | 1    |

|    | 1.2. Thesis Organization                                  | 4    |

| 2. | OVERVIEW OF OVERSAMPLING $\Delta\Sigma$ ADC               | 5    |

|    | 2.1. Sampling and Quantization                            | 5    |

|    | 2.2. Oversampling                                         | 8    |

|    | 2.3. Noise Shaping                                        | 9    |

|    | 2.4. Multi-Stage Noise Shaping                            | 13   |

| 3. | SYNTHESIS OF CONTINUOUS-TIME $\Delta\Sigma$ MODULATOR     | 16   |

|    | 3.1. Impulse Invariant Transformation                     | 16   |

|    | 3.2. Simulation-Based Synthesis of a CT Loop Filter       | 18   |

|    | 3.3. Signal Transfer Function (STF)                       | 23   |

| 4. | DESIGN ISSUES OF CONTINUOUS-TIME $\Delta\Sigma$ MODULATOR | 28   |

|    | 4.1. Non-Idealities of CT Integrators                     | 28   |

|    | 4.1.1. Finite Gain Bandwidth of Opamp                     | 29   |

|    | 4.1.2. Variation of RC Time Constant                      | 32   |

|    | 4.2. Non-Idealities of Quantizer                          | 34   |

|    | 4.2.1. Quantizer Delay (Excess Loop Delay)                | 35   |

|    | 4.2.2. Real Characteristics of Comparator                 |      |

|    | 4.3. Clock Jitter                                         | 41   |

|    | 4.3.1. Jitter Noise in NRZ DAC                            | 42   |

|    | 4.3.2. Jitter Noise in RZ DAC                             | 46   |

|    | 4.4. Element Mismatch Effects in a Multi-Bit DAC          |      |

# TABLE OF CONTENTS (Continued)

| 5. | SYSTEM LEVEL DESIGN                                |

|----|----------------------------------------------------|

|    | 5.1. System Level Parameters                       |

|    | 5.2. Architecture of the Loop Filter               |

|    | 5.3. Noise Budget                                  |

|    | 5.4. System Level Simulation                       |

| 6. | CIRCUIT AND LAYOUT LEVEL DESIGN                    |

|    | 6.1. Loop Filter                                   |

|    | 6.2. Front-End Circuits63                          |

|    | 6.2.1. Noise Analysis64                            |

|    | 6.2.2. Opamp Design                                |

|    | 6.2.3. Current DAC Design                          |

|    | 6.3. Summation Circuits77                          |

|    | 6.4. Quantizer                                     |

|    | 6.5. Clock Generator                               |

|    | 6.6. Interface Circuit                             |

|    | 6.7. Time Constant Tuning                          |

|    | 6.8. Layout Considerations for High Speed Circuits |

| 7. | CHIP EVALUATION                                    |

|    | 7.1. Test Board Design                             |

|    | 7.2. Test Environment                              |

|    | 7.3. Measurement Results                           |

|    | 7.3.1. Problem of the Interface Circuits           |

|    | 7.3.2. Evaluation of MOD295                        |

|    | 7.3.3. Measurement Results                         |

# TABLE OF CONTENTS (Continued)

|     |                                                                | Page |

|-----|----------------------------------------------------------------|------|

|     | 7.4. Comparison Between This Work and Earlier Reported Designs | 101  |

| 8.  | CONCLUSIONS                                                    | 103  |

|     | 8.1. Summary                                                   | 103  |

|     | 8.2. Future Work                                               | 104  |

| Bil | bliography                                                     | 106  |

# LIST OF FIGURES

| Figure                                                                                                                         | <u>Page</u> |

|--------------------------------------------------------------------------------------------------------------------------------|-------------|

| 1.1 Basic diagram of a direct conversion wireless receiver                                                                     | 2           |

| 1.2 Performance of $\Delta\Sigma$ ADCs in some wireless applications                                                           | 3           |

| 2.1 Analog-to-digital conversion                                                                                               | 5           |

| 2.2 (a) Transfer curve and (b) error function of a 4-level quantizer                                                           | 6           |

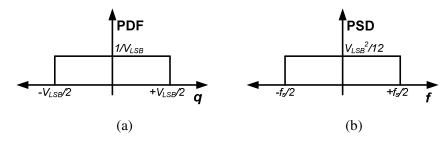

| 2.3 Probability density function and power spectral density of quantization noise                                              | 7           |

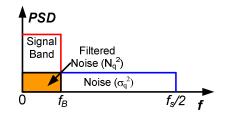

| 2.4 Oversampling                                                                                                               | 8           |

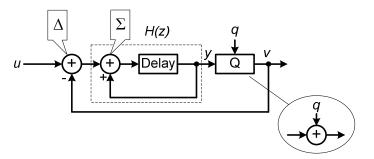

| 2.5 First-order $\Delta\Sigma$ modulator                                                                                       | 9           |

| 2.6 Output spectrum of a first-order $\Delta\Sigma$ modulator                                                                  | 11          |

| 2.7 General structure of a single-quantizer $\Delta\Sigma$ modulator                                                           | 12          |

| 2.8 A general structure of MASH                                                                                                | 14          |

| 2.9 2-2 MASH $\Delta\Sigma$ modulator                                                                                          | 15          |

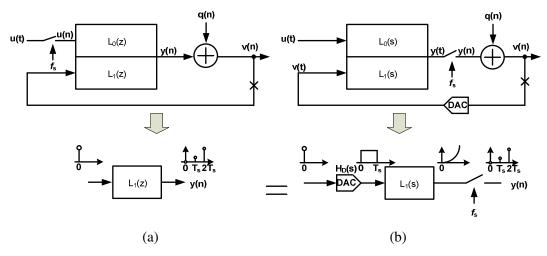

| 3.1 General structures of (a) DT and (b) CT $\Delta\Sigma$ modulator                                                           | 17          |

| 3.2 Linearized (a) DT and (b) CT $\Delta\Sigma$ modulator and their open loop equivalence                                      | 17          |

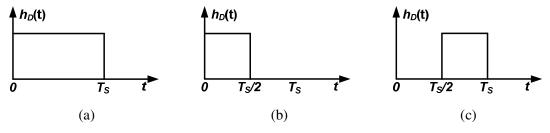

| 3.3 Impulse response of rectangular DAC pulses: (a) NRZ; (b) RZ; (c) HRZ                                                       | 19          |

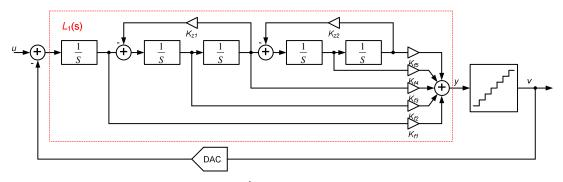

| 3.4 Diagram of a 5 <sup>th</sup> -order feed-forward CT $\Delta\Sigma$ modulator                                               |             |

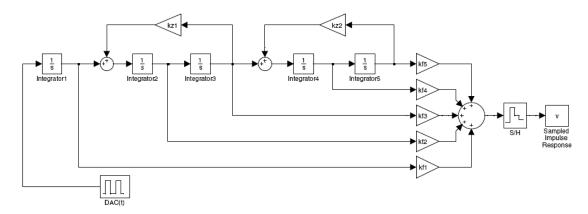

| 3.5 Simulation diagram used to determine the feed-forward coefficients                                                         | 22          |

| 3.6 Diagram of a 5 <sup>th</sup> -order feedback CT $\Delta\Sigma$ modulator                                                   | 24          |

| 3.7 Magnitude response of $L_0(s)$ , NTF(z) and STF(s) of a 5 <sup>th</sup> -order feedback<br>CT $\Delta\Sigma$ modulator     | 25          |

| 3.8 Magnitude response of $L_0(s)$ , NTF (z) and STF(s) of a 5 <sup>th</sup> -order feed- forward CT $\Delta\Sigma$ modulator. | 25          |

| 3.9 Three feed-forward CT $\Delta\Sigma$ modulators with filtering STF                                                         | 27          |

| 4.1 (a) RC and (b) G <sub>m</sub> C integrators                                                                                |             |

# LIST OF FIGURES (Continued)

| Figure                                                                                                                               | Page |

|--------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.2 An n-input RC integrator                                                                                                         | 31   |

| 4.3 The first stage of CT modulator with finite GBW opamp                                                                            | 32   |

| 4.4 The effect of RC time constant variation on the CT modulator                                                                     | 33   |

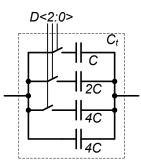

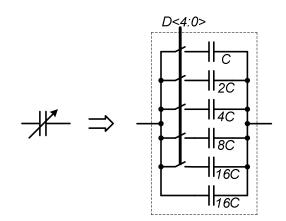

| 4.5 A 3-bit binary-weighted tunable capacitor                                                                                        | 34   |

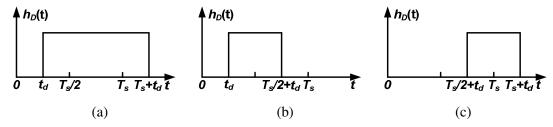

| <ul><li>4.6 Impulse responses of the rectangular DAC pulses including excess loop delay:</li><li>(a) NRZ; (b) RZ; (c) HRZ.</li></ul> | 35   |

| 4.7 The effect of the excess loop delay on the CT modulator                                                                          |      |

| 4.8 The feed-forward CT $\Delta\Sigma$ modulator with excess loop delay compensation                                                 |      |

| 4.9 Impulse-invariant transformation with the compensation for excess loop delay                                                     |      |

| 4.10 Diagram of the quantizer (flash ADC)                                                                                            | 39   |

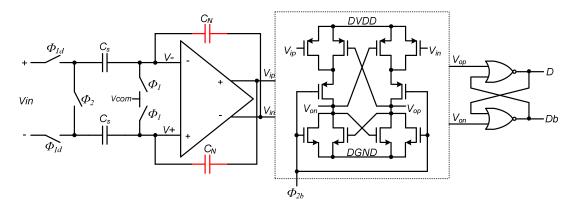

| 4.11 Input offset cancellation of a comparator                                                                                       | 40   |

| 4.12 Real characteristics of a comparator                                                                                            | 41   |

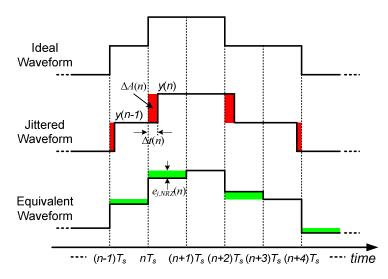

| 4.13 Model of the jitter-induced noise for NRZ DAC                                                                                   | 42   |

| 4.14 Model of the jitter-induced noise for RZ DAC                                                                                    | 47   |

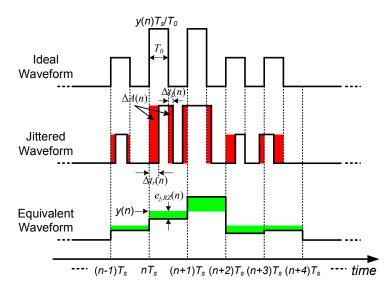

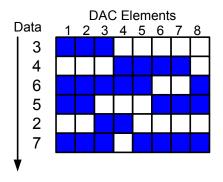

| 4.15 DAC error in the $\Delta\Sigma$ modulator                                                                                       | 48   |

| 4.16 Illustration of DWA                                                                                                             | 49   |

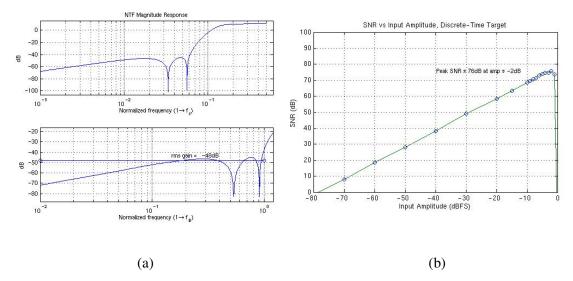

| 5.1 (a) NTF magnitude response; (b) Input-SQNR relationship of the DT target                                                         | 53   |

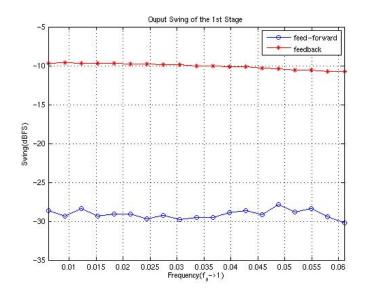

| 5.2 The 1 <sup>st</sup> -stage output swings of the feed-forward and feedback loop filters                                           | 54   |

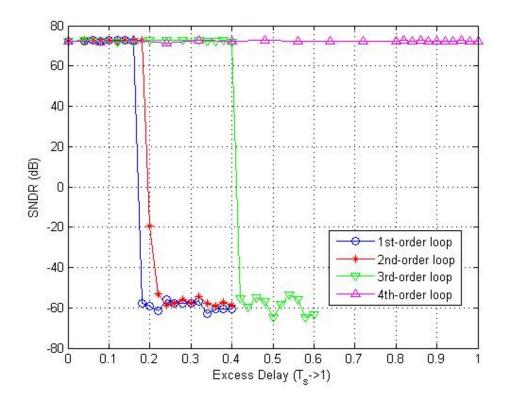

| 5.3 The effect of the excess delay in different order loops on the stability                                                         |      |

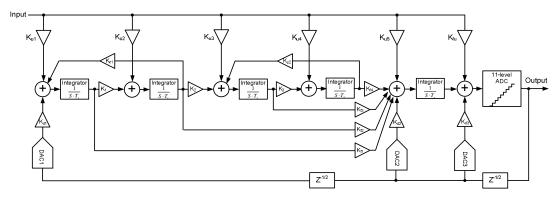

| 5.4 The architecture of the prototype CT $\Delta\Sigma$ modulator                                                                    | 56   |

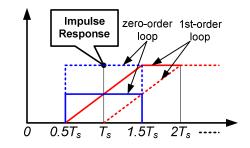

| 5.5 Impulse response of the zero-order and 1 <sup>st</sup> -order loops                                                              | 57   |

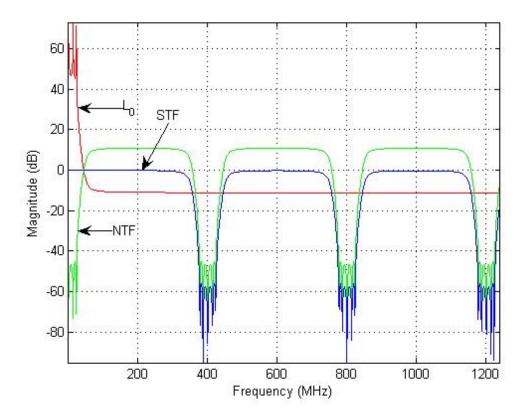

| 5.6 Magnitude responses of L <sub>0</sub> (s), NTF(z) and STF(s)                                                                     | 58   |

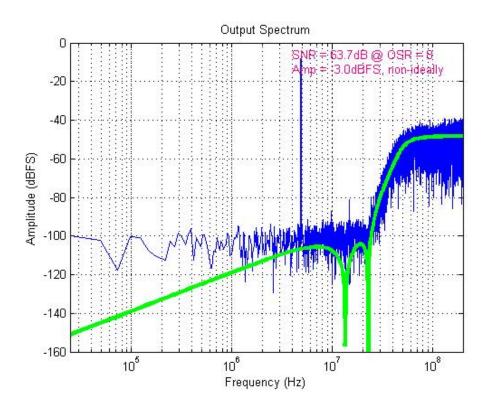

| 5.7 Output spectrum of the system level simulation                                                                                   | 61   |

# LIST OF FIGURES (Continued)

| <u>Figure</u> <u>Pag</u>                                                         | e |

|----------------------------------------------------------------------------------|---|

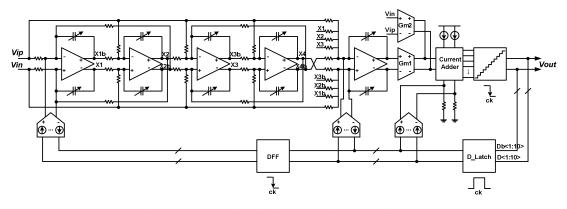

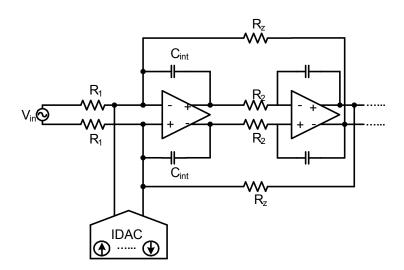

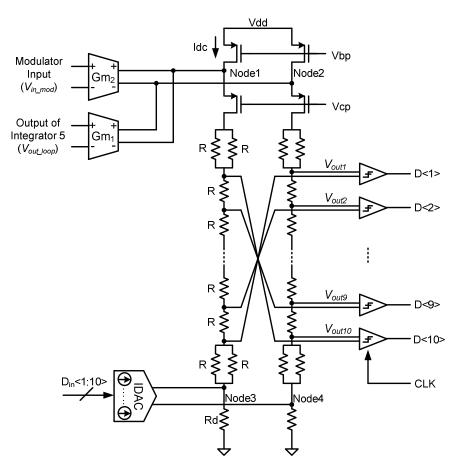

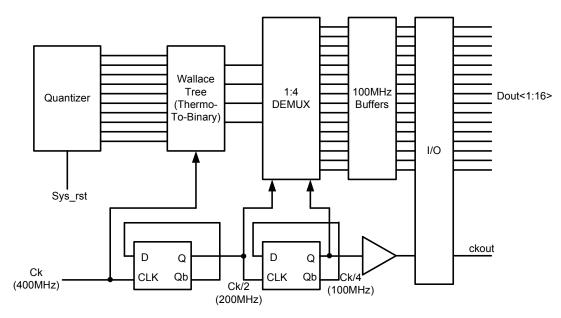

| 6.1 Top level circuit diagram of the CT $\Delta\Sigma$ modulator                 | 2 |

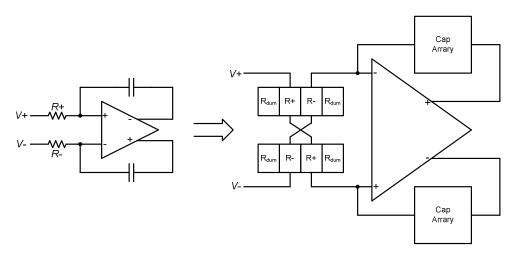

| 6.2 Diagram of the front-end circuits                                            | 3 |

| 6.3 Noise sources in the simplified diagram of the current DAC                   | 4 |

| 6.4 Noise sources in the differential-pair                                       | 7 |

| 6.5 A large output swing class-AB CMOS output stage with CM transistor coupling7 | 0 |

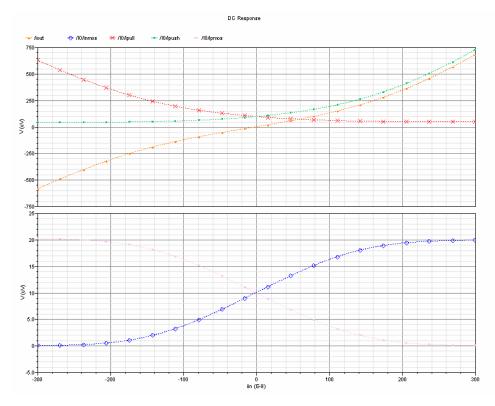

| 6.6 Input-output current characteristics of the class-AB output stage7           | 2 |

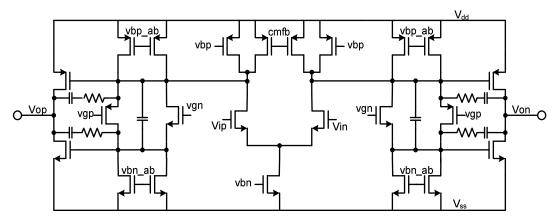

| 6.7 Schematic of the two-stage opamp7                                            | 2 |

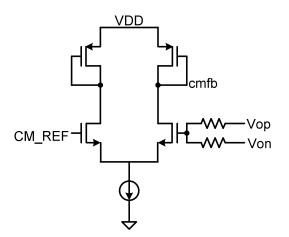

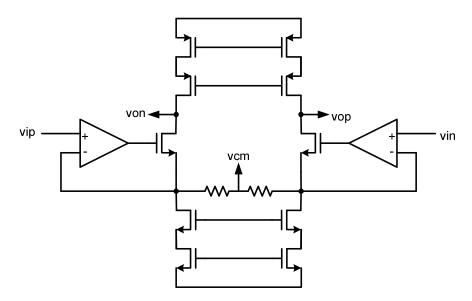

| 6.8 Schematic of the CMFB circuit                                                | 4 |

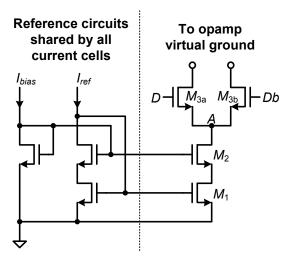

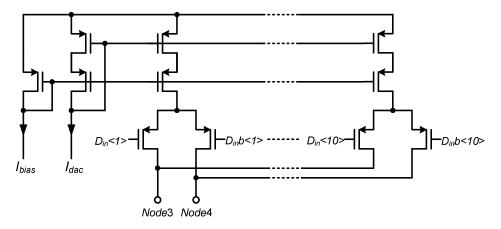

| 6.9 Schematic of the unit current cell                                           | 4 |

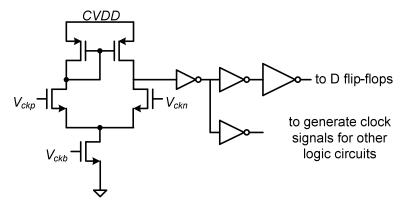

| 6.10 Low-jitter clock generation                                                 | 6 |

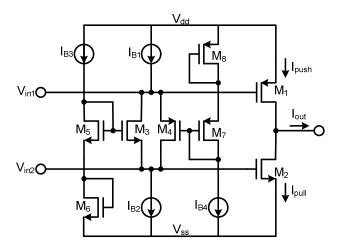

| 6.11 Schematic of the summation circuit                                          | 7 |

| 6.12 Schematic of the $G_m$ cell                                                 | 8 |

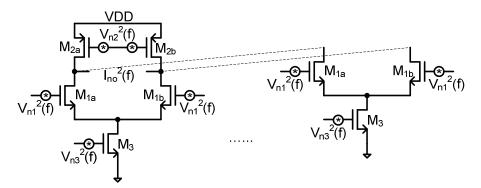

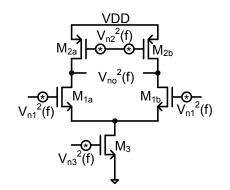

| 6.13 Schematic of the direct feedback DAC7                                       | 9 |

| 6.14 Schematic of the comparator                                                 | 0 |

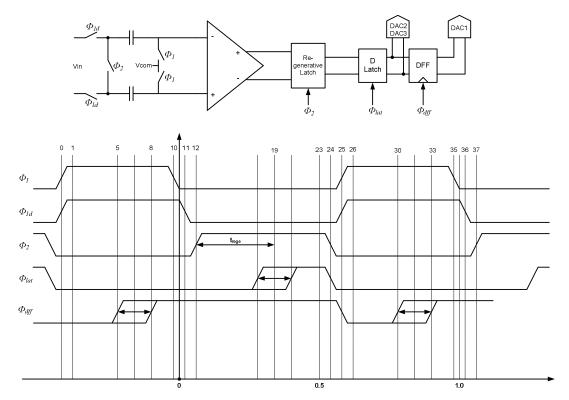

| 6.15 Timing relationship between different clock signals                         | 3 |

| 6.16 Schematic of the multi-phase clock generator                                | 3 |

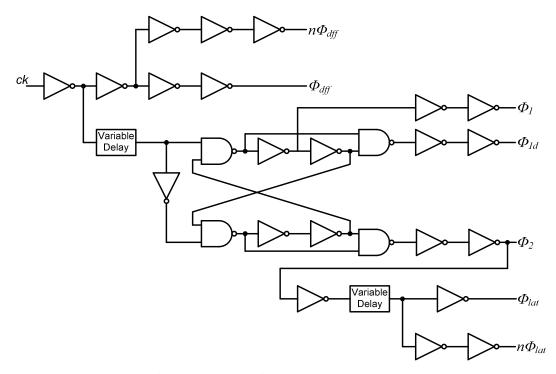

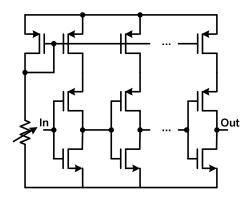

| 6.17 Schematic of the variable delay cell                                        | 4 |

| 6.18 Diagram of the interface circuit                                            | 5 |

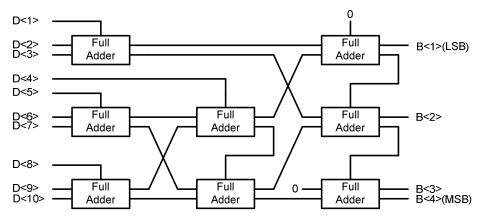

| 6.19 Diagram of the Wallace-Tree thermometer-to-binary encoder                   | 5 |

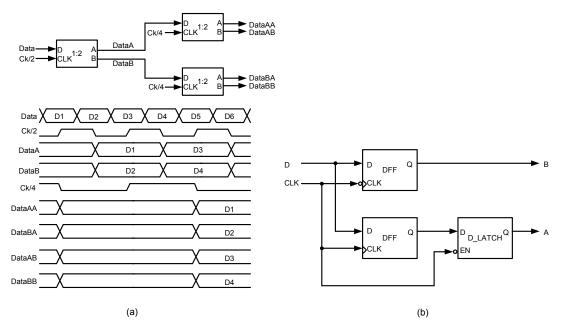

| 6.20 (a) 1:4 DEMUX and its timing; (2) 1:2 DEMUX cell                            | 6 |

| 6.21 Tunable capacitor array                                                     | 6 |

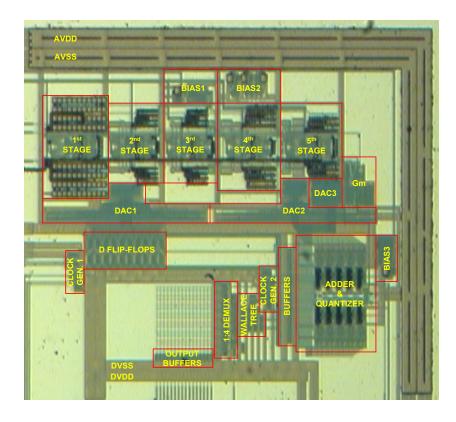

| 6.22 Die photo of the CT $\Delta\Sigma$ modulator                                | 8 |

| 6.23 The fully differential layout scheme                                        | 9 |

# LIST OF FIGURES (Continued)

| <u>Figure</u> <u>P</u>                                                              | Page |

|-------------------------------------------------------------------------------------|------|

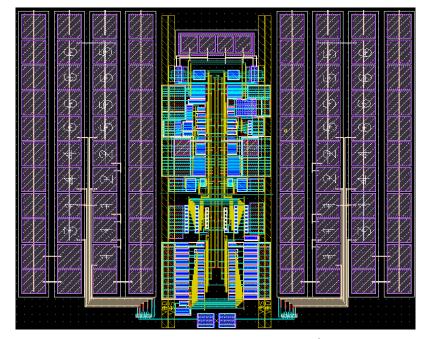

| 6.24 Fully differential layout of the 1 <sup>st</sup> integrator                    | 89   |

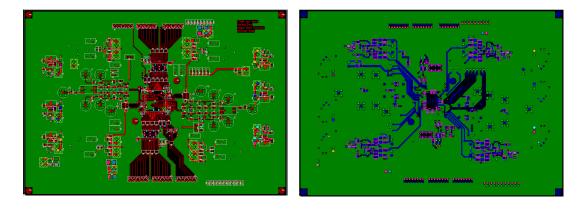

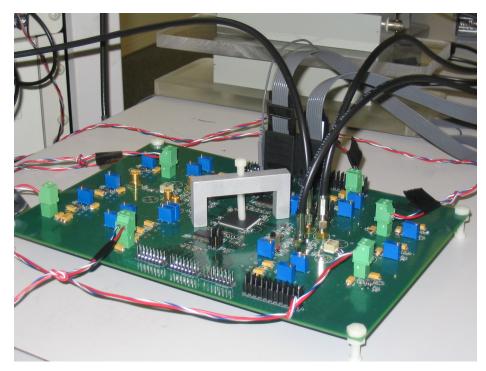

| 7.1 (a) Top layer and (b) bottom layer of the test board                            | 90   |

| 7.2 Test setup photo                                                                | 91   |

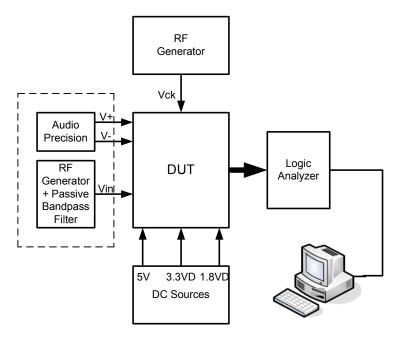

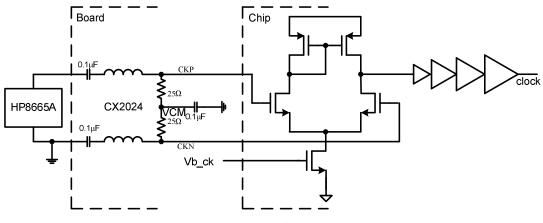

| 7.3 Test environment                                                                | 93   |

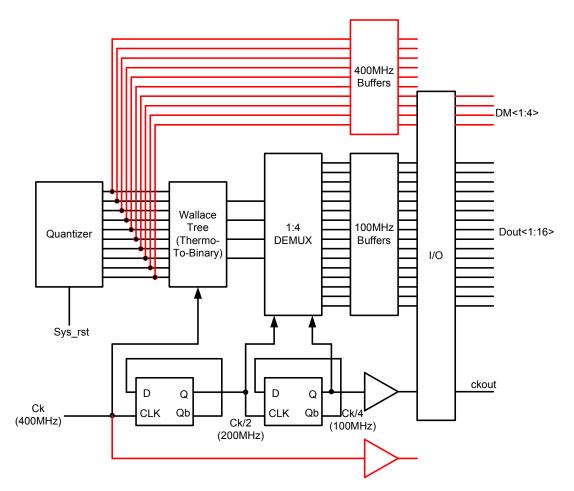

| 7.4 Diagram of the interface circuit (the buffers in red are only included in MOD1) | 94   |

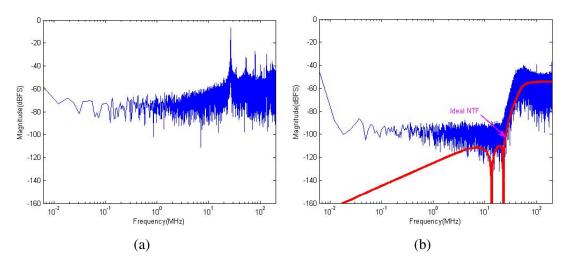

| 7.5 Output spectrum of the MOD2 with (a) normal and (b) increased RC time constant  | 95   |

| 7.6 Diagram of the clock generator                                                  | 96   |

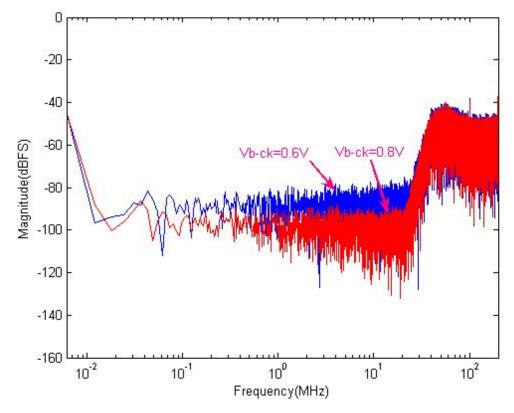

| 7.7 The effect of the clock jitter                                                  | 97   |

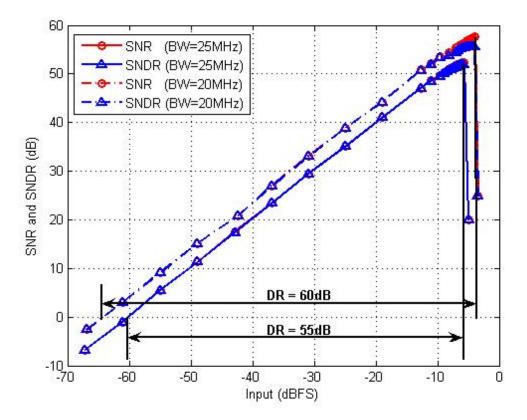

| 7.8 SNR and SNDR versus input amplitude with 2 MHz input                            | 98   |

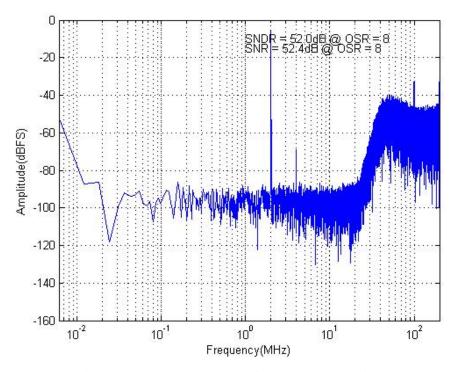

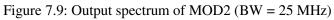

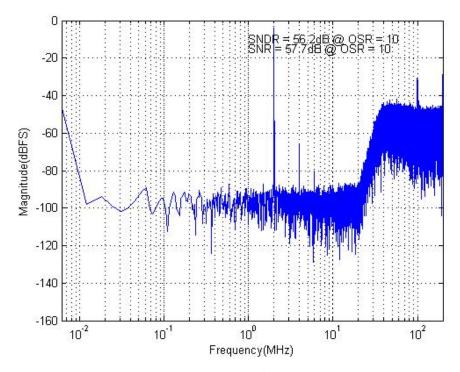

| 7.9 Output spectrum of MOD2 (BW = 25 MHz)                                           | 99   |

| 7.10 Output spectrum of MOD2 (BW = 20 MHz)                                          | 99   |

# LIST OF TABLES

| Table                                                             | Page |

|-------------------------------------------------------------------|------|

| 5.1 Three combinations of the system level parameters             | 53   |

| 5.2 Noise budget of the modulator                                 | 60   |

| 7.1 Test results with different input frequencies                 | 100  |

| 7.2. Summary of the measured chip results                         | 101  |

| 7.3 Performance comparison between reported designs and this work | 102  |

To my beloved parents and family

# A Wideband Low-Power Continuous-Time Delta-Sigma Modulator for Next Generation Wireless Applications

### **CHAPTER 1. INTRODUCTION**

Delta-Sigma ( $\Delta\Sigma$ ) analog-to-digital converters (ADCs) are widely used in wireless applications due to their oversampling, high dynamic range, and low power consumption characteristics. Compared with the traditional discrete-time (DT) counterparts, the  $\Delta\Sigma$  ADCs that employ continuous-time (CT) technique behave even better in terms of power consumption and allowable input bandwidth. This thesis describes a new synthesis method of the CT loop filter from a DT target and discusses several design challenges of the CT  $\Delta\Sigma$ modulators as well as the solutions. After that, the detailed design of a wideband (25 MHz) CT  $\Delta\Sigma$  modulator which utilizes several low-power techniques at both the system level and circuit level is described.

### **1.1. Motivation**

$\Delta\Sigma$  ADCs are very popular in wireless applications [1, 2, 3, 4] due to the following three reasons. First, thanks to the advance of both the semiconductor technology and the design techniques, the input signal bandwidth which the  $\Delta\Sigma$  ADCs can handle is extended to the MHz range. Second,  $\Delta\Sigma$  ADCs are more suitable for low-power design which is one of the most important concerns in the battery-powered wireless equipments (e.g., mobile phones) because the over-sampling characteristics of the  $\Delta\Sigma$  ADCs greatly reduce the performance requirement of the anti-aliasing filters which are power hungry blocks in the wireless transceiver. Last but not least,  $\Delta\Sigma$  ADCs spectrally shape most of the analog circuit error away from the band of interest to achieve high accuracy only in a narrow band, which matches the usual case that the bandwidth of an analog signal of interest in a wireless transceiver is much narrower compared with practical data-converter sample-rates and digital filter clock rates.

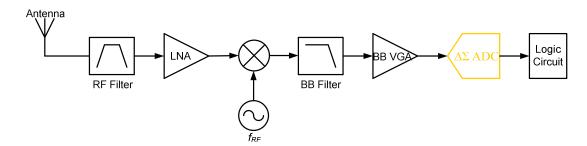

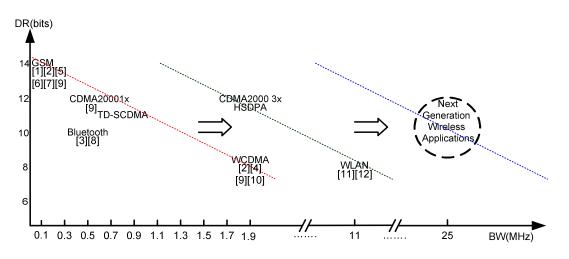

Fig. 1.1 shows the basic diagram of a popular direct conversion wireless receiver which employs a  $\Delta\Sigma$  ADC. Fig. 1.2 describes the relationship between the bandwidth (BW) and the dynamic range (DR) of the  $\Delta\Sigma$  ADCs used in several most popular wireless applications. From this plot, we can see that both the 2<sup>nd</sup>-generation (e.g., GSM, GPRS and EDGE) and the 3<sup>rd</sup>-generation (e.g., WCDMA, CDMA2000 and TD-SCDMA) cellular systems widely used  $\Delta\Sigma$  ADCs in their receivers of the mobile phones. In addition, the  $\Delta\Sigma$ ADCs are also suitable for wireless connection (e.g., Bluetooth) and wireless internet access (e.g., WLAN) applications.

Figure 1.1: Basic diagram of a direct conversion wireless receiver

While most of current commercial  $\Delta\Sigma$  ADCs for wireless applications were implemented by using switched-capacitor techniques [1, 2] which are also known as discretetime (DT)  $\Delta\Sigma$  ADCs mainly due to mature design methodologies and robustness, more and more continuous-time (CT)  $\Delta\Sigma$  ADCs were reported [3~11] and showed impressive performance. Compared with DT counterparts, the CT  $\Delta\Sigma$  ADCs have two main advantages. First, the inherent anti-aliasing characteristics of the CT  $\Delta\Sigma$  ADCs reduce the performance requirement of the anti-aliasing filter further and hence reduce the power consumption of the transceiver. Second, the bandwidth requirement of the operational amplifiers (opamps) in CT  $\Delta\Sigma$  ADCs is much lower than that of the opamps in DT ones for a given sampling-rate, so the CT  $\Delta\Sigma$  ADCs are more suitable for wideband applications.

Figure 1.2: Performance of  $\Delta\Sigma$  ADCs in some wireless applications

It is reasonable to believe that the signal bandwidth of the next generation wireless applications (e.g., the 4<sup>th</sup>-generation cellular system) will be much higher (e.g., 10x) than for the current one. Assuming that other specifications of the receiver are similar to those of the  $3^{rd}$ -generation cellular system [13], the dynamic range requirement of the  $\Delta\Sigma$  ADCs will be around 60 dB. So, CT  $\Delta\Sigma$  ADCs are more suitable than DT ones for next generation wireless applications.

The target of this research is to design a low-pass real CT  $\Delta\Sigma$  modulator with the widest bandwidth to date (25 MHz) to achieve 60 dB dynamic range by consuming very low power (less than 20 mW). This CT  $\Delta\Sigma$  modulator will be a very good candidate for the next generation wireless applications.

#### **1.2.** Thesis Organization

This thesis covers theoretical analysis of the CT  $\Delta\Sigma$  modulator and a novel synthesis method of the CT loop filter from its DT target. After describing the design issues of the CT  $\Delta\Sigma$  modulator as well as the solutions, the detailed design procedure of the prototype modulator as well as the chip evaluation work are presented. The thesis is organized as following:

Chapter 2 provides some basic background knowledge about  $\Delta\Sigma$  ADCs to help understand the rest of the thesis.

Chapter 3 describes the equivalence between the DT and CT loop filters in terms of impulse-invariant transformation (IIT) and proposes a novel synthesis method of the CT loop filter from its DT target based on simulation.

Chapter 4 covers some main design issues of the CT  $\Delta\Sigma$  modulators, which include excess loop delay, clock jitter, and RC time constant variation, as well as the solutions to those issues.

Chapter 5 proposes a system level design procedure which combines many aspects of the design considerations of the wideband low-power CT  $\Delta\Sigma$  modulator.

Chapter 6 presents detailed circuit level and layout level design of this wideband modulator.

Chapter 7 covers the issues of high speed test board design as well as the chip evaluation work.

Chapter 8 concludes the thesis and discusses some future work.

### CHAPTER 2. OVERVIEW OF OVERSAMPLING $\Delta\Sigma$ ADC

This chapter provides some basic background knowledge about  $\Delta\Sigma$  ADCs to help understand the rest of the thesis. The concepts of quantization, oversampling and noiseshaping are introduced and illustrated with examples. Two common architectures of the  $\Delta\Sigma$ modulators, single-loop and multi-stage (cascaded, MASH), are compared.

### 2.1. Sampling and Quantization

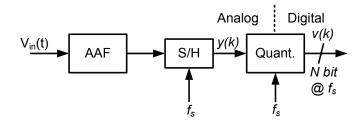

In order to properly interface the real analog world which is composed of continuoustime and continuous-amplitude analog signals (e.g., voice, audio or video) with the digital signal processor which can only process discrete-time and discrete-amplitude signals, analogto-digital conversion is required (see Fig. 2.1). The AAF block stands for the anti-aliasing filter which is used to limit the bandwidth of the input signal to half of the sampling rate (Nyquist theorem). Otherwise, the undesired higher frequency components will alias into the band of interest and interrupt the desired signal while sampling which changes the input signal from continuous form to discrete form in the time domain. The sampled signal should be "frozen" for a sufficient time to be determined and represented by one of some discrete levels, which is known as quantization. For this reason, the quantizer that carries out the quantization should be preceded by a sample-and-hold (S/H) or track-and-hold (T/H) block.

Figure 2.1: Analog-to-digital conversion

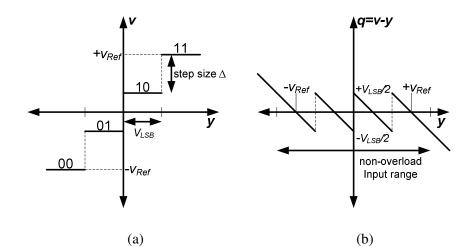

The quantizer is assumed to be a memoryless nonlinear device completely defined by its static input-output characteristics, i.e., by its *y*-*v* transfer curve. An example of such a curve is shown in Fig. 2.2a, where the number of quantization level is 4 which can be represented by a 2-digit binary code, and the difference of two adjacent quantized values,  $\Delta$ , is the same as the difference between input thresholds, also known as least-significant bit size or LSB size, given by  $V_{LSB}$ . The difference between the lowest and highest levels is called the full-scale (FS) of the quantizer, given by  $2V_{Ref}$ . The deviation between the sampled input and the quantized output is called the quantization error, or the quantization noise. Fig. 2.2b shows the relationship between the quantization noise *q* and the input *y*. From this figure, it can be seen that as long as *y* is between - $(V_{Ref}+V_{LSB}/2)$  and + $(V_{Ref}+V_{LSB}/2)$ , the error *q* is between - $V_{LSB}/2$ and + $V_{LSB}/2$ . The range of *y* where this condition is satisfied is called the non-overload input range. For a *N* bit ADC, the quantization step as well as the LSB size is given by  $\Delta = V_{LSB} =$ *FS*/(2<sup>*N*</sup>-1), which is, in this case, 2*V<sub>Ref</sub>*/3.

Figure 2.2: (a) Transfer curve and (b) error function of a 4-level quantizer

The ideal quantizer is a deterministic device. The output v and hence the error q are fully determined by the input y. However, under certain circumstances, for example, if the

input *y* stays within the non-overload input range of the quantizer, and changes by sufficiently large amounts from sample to sample so that its position within a quantization interval is essentially random, then it is permissible to assume that *q* is a white noise process with samples uniformly distributed between  $-V_{LSB}/2$  and  $+V_{LSB}/2$ . The probability density function (PDF) and power spectral density (PSD) of the quantization noise are shown in Fig. 2.3.

Figure 2.3: Probability density function and power spectral density of quantization noise

The impact of the quantization noise on the ADC's performance can be found by calculating its maximum signal-to-quantization-noise ratio (SQNR<sub>max</sub>). This parameter is obtained by dividing the power of a sinusoidal input signal by the power of the quantization noise. The power of a sinusoidal signal is given by  $A_u^2/2$ , where  $A_u$  is the amplitude of the signal. The power of the quantization noise is given in Eq. 2.1.

$$\sigma_q^2 = \frac{1}{V_{LSB}} \int_{-V_{LSB}/2}^{V_{LSB}/2} dq = \frac{V_{LSB}^2}{12}$$

(2.1)

To get the SQNR<sub>max</sub>,  $A_u$  should be equal to half of the non-overload input range of the quantizer, which is  $V_{Ref} + V_{LSB}/2$ .

$$SQNR_{\text{max}} = \frac{\left(\frac{V_{\text{Re}f} + \frac{V_{LSB}}{2}\right)^2}{V_{LSB}^2/12} = \frac{\left(\frac{2^{N-1}V_{LSB}}{V_{LSB}^2}\right)^2/2}{V_{LSB}^2/12} = \frac{3}{2}2^{2N}$$

(2.2)

Expressed in dB, this becomes Eq. 2.3, which is widely used to assess the performance of the data converter.

$$SQNR_{\max}[dB] = 10\log_{10}(SQNR_{\max}) = 6.02N + 1.76$$

(2.3)

# 2.2. Oversampling

An alternative way to calculate the power of the quantization noise is to integrate its power spectral density over the full bandwidth of operation of the ADC:

$$\sigma_q^2 = \frac{1}{f_s} \int_{-f_s/2}^{f_s/2} \frac{V_{LSB}^2}{12} df = \frac{V_{LSB}^2}{12}$$

(2.4)

From above equation, it is obvious that if the bandwidth of interest is much lower than the bandwidth of operation, the resolution of the ADC can be improved by filtering the output to the desired bandwidth which reduces the total power of the quantization noise. This technique, illustrated in Fig. 2.4, is called oversampling.

Figure 2.4: Oversampling

Now, the power of the in-band quantization noise is given in Eq. 2.5.

$$N_{q}^{2} = \frac{1}{f_{s}} \int_{-f_{B}}^{f_{B}} \sigma_{q}^{2} df = \sigma_{q}^{2} \frac{2f_{B}}{f_{s}} = \frac{\sigma_{q}^{2}}{OSR}$$

(2.5)

where OSR, defined as  $f_s/2f_B$ , is called oversampling ratio which is one of the most important parameters used to characterize the oversampling data converters. The power of input signal is

not modified since it is assumed that it has no frequency content above  $f_B$ . Therefore, the maximum SQNR is given by:

$$SQNR_{\max}[dB] = 6.02N + 1.76 + 10\log_{10}OSR$$

(2.6)

It is obvious that if the sampling rate is equal to twice the Nyquist rate (OSR = 2), the SQNR is improved by 3 dB. Eq. 2.6 shows that oversampling can improve the SQNR with the OSR at a rate of 3 dB/octave, or 0.5 bit/octave.

#### 2.3. Noise Shaping

The previous section shows that oversamping can be used to trade speed for resolution of ADC. However, the rate of this trading is only 3 dB/octave with plain oversamping.

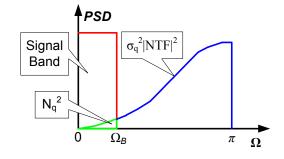

It is noticed that the quantization noise in previous section has a flat power spectral density over the full bandwidth  $(-f_s/2 - f_s/2)$ . A more efficient way to use oversampling is to shape the spectral density such that most of the quantization noise power is outside the band of interest.  $\Delta\Sigma$  or  $\Sigma\Delta$  modulators can be used to do this noise shaping without affecting the desired signal band. Fig. 2.5 shows a  $\Delta\Sigma$  modulator that can shape the quantization noise with a first-order high-pass transfer function.

Figure 2.5: First-order  $\Delta\Sigma$  modulator

Again, it is assumed that the quantization noise is uniformly distributed and not dependent on the input signal u. The modulator can be completely linearized by replacing the

quantizer with a summation block. This system has two inputs, u and q, and one output, v. The transfer function from u to v, which is called signal transfer function (STF), is given by:

$$STF(z) = \frac{V(z)}{U(z)} = \frac{H(z)}{1 + H(z)} = z^{-1}$$

(2.7)

This means that the input signal u is delayed and appears unaltered at the output v. As for the noise transfer function (NTF) which is defined as the transfer function from q to v, it is given out by:

$$NTF(z) = \frac{V(z)}{Q(z)} = \frac{1}{1 + H(z)} = 1 - z^{-1}$$

(2.8)

This equation shows that the quantization noise is shaped by a first-order high-pass transfer function. The order of noise shaping is associated with the order of the NTF.

To calculate the SQNR of the output v, it is necessary to find the squared magnitudes of the transfer functions which are given out as followings:

$$\left|STF(e^{j\Omega})\right|^2 = \left|e^{-j\Omega}\right|^2 = 1$$

(2.9)

$$\left| NTF(e^{j\Omega}) \right|^{2} = \left| 1 - e^{-j\Omega} \right|^{2} = \left| 1 - \cos \Omega + j \sin \Omega \right|^{2} = 2 - 2 \cos \Omega = \left( 2 \sin \left( \frac{\Omega}{2} \right) \right)^{2}$$

(2.10)

where  $\Omega$ , defined as  $\Omega = 2\pi f/f_s$ , is the normalized angular frequency.

The power spectral density of the quantization noise at output v can be calculated by multiplying that of q with the squared magnitude of the NTF (see Fig. 2.6). So, the power of the quantization noise within the band of interest is given by:

$$N_{q}^{2} = \frac{1}{2\pi} \int_{-\Omega_{B}}^{\Omega_{B}} \sigma_{q}^{2} |NTF|^{2} d\Omega = \frac{\sigma_{q}^{2}}{\pi} \int_{0}^{\pi/OSR} (2\sin(\Omega/2))^{2} d\Omega$$

(2.11)

If the oversampling ratio is very large, which is a common case for  $\Delta\Sigma$  data converters,  $\Omega_B = \pi/OSR$  is much less than 1. Then, the following approximation is valid in the signal band.

11

$$2\sin\left(\frac{\Omega}{2}\right) \approx 2 \cdot \frac{\Omega}{2} = \Omega$$

(2.12)

Therefore, the result of Eq. 2.11 can be as simple as:

$$N_q^2 \approx \frac{\sigma_q^2}{\pi} \int_0^{\pi/OSR} \Omega^2 d\Omega = \frac{\sigma_q^2 \pi^2}{3OSR^3}$$

(2.13)

Use this result to calculate the maximum SQNR in dB, following expression can be obtained:

$$SQNR_{\max}[dB] = 6.02N + 1.76 + 30\log_{10}OSR - 10\log_{10}\frac{\pi^2}{3}$$

(2.14)

Compared with Eq. 2.6, it is obvious that the trading rate of speed and resolution with this 1<sup>st</sup>-order noise shaping is triple that of plain oversampling, which is 9 dB/octave, or equivalently, 1.5 bit/octave. However, the total noise power at the output (for full bandwidth) is higher than that of a Nyquist rate data converter. Thus, there is a lower limit of OSR, below which  $\Delta\Sigma$  converters don't provide any benefits.

Figure 2.6: Output spectrum of a first-order  $\Delta\Sigma$  modulator

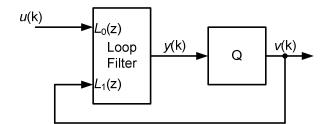

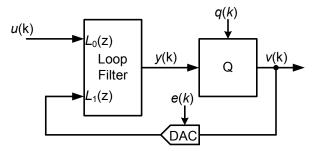

A general structure of  $\Delta\Sigma$  modulator is shown in Fig. 2.7 [14]. In this diagram, the modulator is divided into two parts: a linear part (the loop filter) containing memory elements and a memoryless nonlinear part (the quantizer). The loop filter is a two-input system whose output *y* can be expressed as a linear combination of inputs *u* and *v*. In *Z* domain, this is:

$$Y(z) = L_0(z)U(z) + L_1(z)V(z)$$

(2.15)

So, the first-order  $\Delta\Sigma$  modulator shown in Fig. 2.5 is just a special case of the general structure, in which  $L_0(z) = -L_1(z) = H(z)$ .

Figure 2.7: General structure of a single-quantizer  $\Delta\Sigma$  modulator

The operation of the quantizer is, as usual, described as the addition of an error signal:

$$V(z) = Y(z) + Q(z)$$

(2.16)

Using Eq. 2.15 and 2.16, the modulator output v can be written as the linear combination of two signals, namely the modulator input u and the quantization error q, in Z domain:

$$V(z) = STF(z)U(z) + NTF(z)Q(z)$$

(2.17)

where

$$STF(z) = \frac{L_0(z)}{1 - L_1(z)}$$

and  $NTF(z) = \frac{1}{1 - L_1(z)}$  (2.18)

Conversely, given the desired STF(z) and NTF(z), one can computer the loop filter's transfer functions which are required to implement them.

$$L_0(z) = \frac{STF(z)}{NTF(z)}$$

and  $L_1(z) = 1 - \frac{1}{NTF(z)}$  (2.19)

By properly designing  $L_0(z)$  and  $L_1(z)$ , higher order NTF can be realized while keeping the STF just a few delays. A simple example of the  $L^{th}$ -order high pass NTF is given by:

$$NTF(z) = \left(1 - z^{-1}\right)^L$$

(2.20)

Following the same analysis as that used in the first-order modulator, if  $OSR \gg 1$ , the in-band integrated noise power will be given by:

$$N_q^2 = \frac{\sigma_q^2 \pi^{2L}}{(2L+1)OSR^{2L+1}}$$

(2.21)

and the maximum SQNR in dB can be expressed as following:

$$SQNR_{\max}[dB] = 6.02N + 1.76 + (20L + 10)\log_{10}OSR - 10\log_{10}\frac{\pi^{2L}}{2L + 1}$$

(2.22)

In general, the SQNR will improve with the OSR at a rate of 6L+3 dB/octave, or equivalently, L+0.5 bit/octave with the  $L^{th}$ -order noise shaping.

# 2.4. Multi-Stage Noise Shaping

According to Eq. 2.22, the SQNR of a  $\Delta\Sigma$  modulator can be improved by increasing the resolution of the quantizer, oversampling ratio and the order of noise shaping. However, the resolution of the quantizer is usually no more than 6 bits. Otherwise, both the circuit complexity and the power consumption of the modulator will be too high. In addition, the sampling rate and hence the OSR is limited by both the semiconductor technology and power consumption. Compared with other two ways, increasing the order of noise shaping is relatively cheap. However, in a single-loop  $\Delta\Sigma$  modulator, the order of the loop filter is severely limited by the stability issue [14].

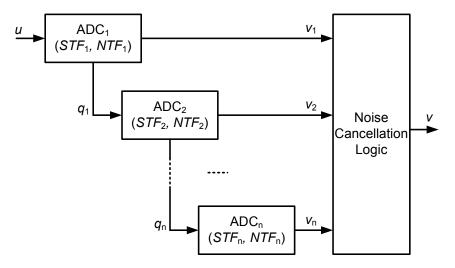

One way to avoid the stability problem in a high-order  $\Delta\Sigma$  modulator is to implement it with a cascade of multiple stable low-order loops. This type of noise shaping is called MultistAge noise SHaping, or MASH. Fig. 2.8 gives out a general MASH structure. The first stage  $(ADC_1)$  is a low-order  $\Delta\Sigma$  modulator. Each of the remaining stages  $(ADC_2 \text{ to } ADC_n)$  can be a  $\Delta\Sigma$  modulator as well or a plain Nyquist-rate ADC. If the quantization error q of each stage is acquired and converted to digital format by a subsequent stage, all errors except that of the last stage can be cancelled out at the MASH output v in the digital domain. Proper design of the noise cancellation logic will make the output of the modulator v equal to:

$$V = U \cdot STF_1 \cdot STF_2 \cdots STF_n + Q_n \cdot NTF_1 \cdot NTF_2 \cdots NTF_n$$

(2.23)

where the order of the noise transfer function is the summation of the individual orders,  $L_1$  to  $L_{n.}$ .

Figure 2.8: A general structure of MASH

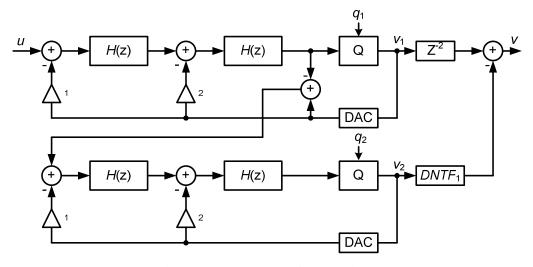

When referring to a MASH ADC, it is usual to indicate the number of stages and the order of each stage. For example, a 2-2 MASH (see Fig. 2.9) has two stages, and both stages are second-order  $\Delta\Sigma$  modulators.

The quantization noise of the first stage,  $q_1$ , is obtained by subtracting the input of the quantizer from its output. For this example, the output *v* of the modulator is given by:

$$V = U \cdot z^{-4} + Q_1 (ANTF_1 - DNTF_1) z^{-2} - Q_2 \cdot ANTF_2 \cdot DNTF_1$$

(2.24)

where  $ANTF_1$  and  $ANTF_2$  refer to the noise transfer functions of the first and second stages, which are implemented in the analog domain.  $DNTF_1$  is the noise transfer function following the second stage, which is implemented in digital domain. Assuming that everything is ideal, i.e., that  $ANTF_1 = DNTF_1$ , the quantization noise  $q_1$  is cancelled, and only the second-stage's quantization noise  $q_2$ , shaped by the product of the two NTFs, will appear at the output:

$$V = U \cdot z^{-4} - Q_2 \cdot ANTF_1 \cdot ANTF_2 \tag{2.25}$$

Figure 2.9: 2-2 MASH  $\Delta\Sigma$  modulator

However, if the analog and digital transfer functions don't match exactly, a problem known as quantization noise leakage will occur. If noise leakage happens, the quantization noise  $q_1$ , shaped only by a low-order NTF, will appear at the output and greatly degrade the accuracy of the MASH  $\Delta\Sigma$  modulators. The problem of noise leakage is more serious in the continuous-time MASH modulators than in the discrete-time counterparts because the accuracy of the CT analog transfer function is dependent on the absolute RC time constant which is much more inaccurate than the ratio of the capacitors in modern semiconductor process. So, single-loop structure is more popular in the CT  $\Delta\Sigma$  modulators.

# CHAPTER 3. SYNTHESIS OF CONTINUOUS-TIME ΔΣ MODULATOR

$\Delta\Sigma$  modulators are usually thought of mathematically in the discrete-time (DT) domain as we did in the Chapter 2 because the majority of published designs are built with DT, e.g., switched-capacitor [1, 2] or switched-current [15] circuitry. However, for a continuoustime (CT)  $\Delta\Sigma$  modulator, there are two ways to synthesize its loop filter, direct synthesis in the CT domain [16, 17] or equivalently transformation from DT origin [18, 19]. Since the design methodologies of the DT  $\Delta\Sigma$  modulators have been thoroughly studied during the past decades, many good design tools, e.g., the  $\Delta\Sigma$  MATLAB toolbox written by Richard Schreier [20], are available on hand. In addition, it is easier to simulate a DT  $\Delta\Sigma$  modulator with computer. So, it is more popular to synthesize the CT loop filter by equivalently transforming from its DT target.

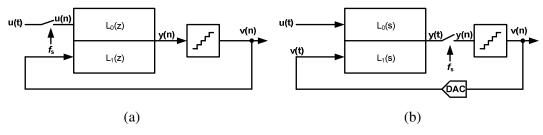

# 3.1. Impulse-Invariant Transformation

The quantizer in a CT  $\Delta\Sigma$  modulator is clocked, which means there is an implicit sampling action inside the modulator, and sampled circuits are DT circuits, so we can make the sampling explicit by placing the sampler immediately prior to the quantizer (see Fig. 3.1b) without changing the behavior of the modulator. For comparison, the general structure of a DT  $\Delta\Sigma$  modulator which was shown in Fig. 2.7 is redrawn in Fig. 3.1a.

As we mentioned in the section 2.3, if the quantization is described as the addition of an error signal, a  $\Delta\Sigma$  modulator can be treated as a two-input system (see Fig. 3.2) whose output v can be expressed as the linear combination of modulator input u and quantization noise q.

$$V = STF \cdot U + NTF \cdot Q \tag{3.1}$$

Figure 3.1: General structures of (a) DT and (b) CT  $\Delta\Sigma$  modulator

From Fig. 3.2b, it can be seen that, in a CT  $\Delta\Sigma$  modulator, both the quantization noise q and modulator output v are discrete-time signals, so it is reasonable to believe that a CT  $\Delta\Sigma$  modulator can find its equivalent DT counterpart in terms of the noise transfer function. How to find this equivalence?

Figure 3.2: Linearized (a) DT and (b) CT  $\Delta\Sigma$  modulator and their open loop equivalence

It is well known that the NTF is given by:

$$NTF = \frac{1}{1 - LTF},\tag{3.2}$$

where LTF stands for the loop transfer function which is the same as  $L_1(z)$  in DT modulator, so the NTFs will be the same as long as both modulators have the same LTFs. To find the equivalent LTFs, it is instructive to zero both inputs of the modulators and open both loops around the quantizers, which leads to bottom two diagrams of Fig. 3.2. In the CT open-loop diagram, the DAC can be thought of as a "discrete-to-continuous converter" which makes a CT pulse v(t) from the quantizer output v(n) which is a discrete-time quantity. This pulse is filtered by  $L_1(s)$  (the CT loop filter) to produce y(t) at the quantizer input, which is then sampled to produce the DT quantizer input y(n). If this quantizer input is equal to that of the DT modulator at each sampling instant (Eq. 3.3), then both modulators will produce the same output sequences v(n) and hence the same LTFs:

$$y(n) = y(t)\Big|_{t=nT}$$

(3.3)

Above equation can be satisfied if the impulse response of the open-loop diagrams in Fig. 3.2 are equal at the sampling instants, leading to the condition:

$$Z^{-1}\{L_1(z)\} = L^{-1}\{H_D(s)L_1(s)\}\Big|_{t=nT_s}$$

(3.4)

or, in the time domain:

$$l_{1}(n) = \left\{ h_{D}(t) * l_{1}(t) \right\}_{t=nT_{S}} = \int_{-\infty}^{+\infty} h_{D}(\tau) l_{1}(t-\tau) d\tau \bigg|_{t=nT_{S}}$$

(3.5)

where  $H_D(s)$  and  $h_D(t)$  are the transfer function and impulse response of the DAC. Since this equivalence requires the DT and CT impulse responses to be the same, this transformation between them is called impulse-invariant transformation (IIT).

# 3.2. Simulation-Based Synthesis of a CT Loop Filter

To synthesize a CT loop filter from a DT target based on IIT in a practical design, it is necessary to determine the shape of the feedback DAC waveform first because different DAC pulses will result in different CT loop filters for a given DT origin according to Eq.3.4 or 3.5.

The most commonly used DAC waveform is the rectangular pulse which includes non-return-to-zero (NRZ), return-to-zero (RZ) and half-delay-return-to-zero (HRZ) pulses [18]. The impulse responses of those DAC waveforms are shown in Fig. 3.3.

Figure 3.3: Impulse response of rectangular DAC pulses: (a) NRZ; (b) RZ; (c) HRZ

Besides the rectangular DAC waveform, some other waveforms are proposed to reduce the clock jitter sensitivity of the modulator [21, 22]. The research on the DAC jitter sensitivity will be presented in detail in the Chapter 4.

After determining the feedback DAC waveform, the CT loop filter  $L_1(s)$  can be calculated manually based on the tables and steps described in reference [18]. To realize the  $L_1(s)$  with a given loop filter architecture, e.g., feedback or feed-forward, the symbolic expression of the transfer function has to be obtained. After that, the coefficients of the expression can be calculated by solving an equation set that is acquired by mapping  $L_1(s)$  to the symbolic expression (see Appendix A of [23]).

The synthesis method described above needs too much manual calculation, which makes this process very complex, especially for a high-order loop filter. In addition, this method is difficult to use while the non-rectangular DACs are employed in the feedback loop because the equivalence between the S-domain and the Z-domain becomes much more complex while using other shaped DACs, e.g., the exponential decaying DAC pulse [24].

A novel synthesis methodology that combines the impulse-invariant transformation and the mapping between  $L_1(s)$  and a given loop filter structure was developed in this work. In this methodology, most of the transformation-domain calculation is replaced by the timedomain simulations, which greatly simplifies the synthesis process. In addition, it can be used to synthesize the loop filter with different DAC waveforms.

In a linear time invariant (LTI) system described by linear equation:

$$Q(D)y(t) = P(D)f(t),$$

(3.6)

where Q(D) and P(D) are polynomials of D-operators (Differentiation), the output response can be divided into two parts: natural response and forced response. The former is usually given by the following equation:

$$y_{n}(t) = \sum_{j=1}^{n} c_{j} e^{\lambda_{j} t}$$

(3.7)

where the  $\lambda_i$  are the roots of the characteristic equation  $Q(\lambda) = 0$ .

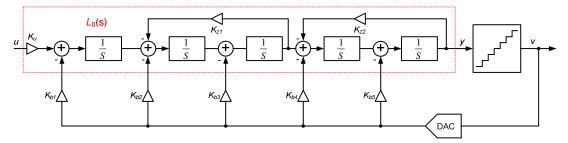

Fig. 3.4 shows the diagram of a 5<sup>th</sup>-order feed-forward CT  $\Delta\Sigma$  modulator. In this LTI system  $L_1(s)$ , the natural response is determined by those two local loops which form the non-DC poles of the transfer function. On the other hand, the forced response is related to all those feed-forward paths.

Figure 3.4: Diagram of a 5<sup>th</sup>-order feed-forward CT  $\Delta\Sigma$  modulator

The impulse-invariant transformation described in the section 3.1 will map the poles in S-domain to those in Z-domain with following equation while keeping the multiplicity [18].

$$Z_P = e^{S_P} \tag{3.8}$$

In addition, the non-DC poles of the  $L_1(s)$  in Fig. 3.4 have the following relationship with the coefficients of the local feedback branches, namely  $K_{Z1}$  and  $K_{Z2}$ :

$$S_{P_{1,2}} = \pm j\sqrt{K_{Z1}}$$

and  $S_{P_{3,4}} = \pm j\sqrt{K_{Z2}}$  (3.9)

Using these two equations, we can easily get the relationship between the non-DC poles of the  $L_1(z)$ , which are also the non-DC zeros of the NTF, and the coefficients of  $K_{Z1}$  and  $K_{Z2}$  in the CT loop filter:

$$K_{Z1} = (angle(Z_{P_{1,2}}))^2$$

and  $K_{Z2} = (angle(Z_{P_{3,4}}))^2$  (3.10)

After determining the natural response of the CT loop filter, we have to identify a set of coefficients that can be used to adjust the gain of each loop independently. In this example, those feed-forward paths ( $K_{f1} \sim K_{f5}$ ) are just the independent path gain factors that we need to find. For example, the gain of the first-order loop that only contains one integrator can be adjusted arbitrarily by the coefficient  $K_{f1}$  without affecting the gains of other loops.

To determine those independent coefficients, we have to "ping" the loop filter for each coefficient by setting it to be one and the others zero, which can be performed with the time-domain simulation in some commercial simulators, e.g., SIMULINK. Fig. 3.5 shows the simulation diagram of the open-loop CT modulator. The block DAC(t) is used to generate a specific DAC impulse response. For each feed-forward coefficient, we can get a sampled impulse response at the output v. Because those coefficients are independent of each other, the total impulse response should be the linear combination of those individual impulse responses:

$$h(k) = \sum_{i=1}^{5} \alpha_{i} \cdot h_{i}(k)$$

(3.11)

Figure 3.5: Simulation diagram used to determine the feed-forward coefficients

We can build up an equation set by equating the above impulse response with that of the  $L_1(z)$ , which is also easily obtained by simulation, at several first time instants, e.g., h(1), h(2), ..., and h(5).

$$h_{1}(1)\alpha_{1} + h_{2}(1)\alpha_{2} + h_{3}(1)\alpha_{3} + h_{4}(1)\alpha_{4} + h_{5}(1)\alpha_{5} = h_{d}(1)$$

$$h_{1}(2)\alpha_{1} + h_{2}(2)\alpha_{2} + h_{3}(2)\alpha_{3} + h_{4}(2)\alpha_{4} + h_{5}(2)\alpha_{5} = h_{d}(2)$$

$$h_{1}(3)\alpha_{1} + h_{2}(3)\alpha_{2} + h_{3}(3)\alpha_{3} + h_{4}(3)\alpha_{4} + h_{5}(3)\alpha_{5} = h_{d}(3)$$

$$h_{1}(4)\alpha_{1} + h_{2}(4)\alpha_{2} + h_{3}(4)\alpha_{3} + h_{4}(4)\alpha_{4} + h_{5}(4)\alpha_{5} = h_{d}(4)$$

$$h_{1}(5)\alpha_{1} + h_{2}(5)\alpha_{2} + h_{3}(5)\alpha_{3} + h_{4}(5)\alpha_{4} + h_{5}(5)\alpha_{5} = h_{d}(5)$$

(3.12)

where  $h_d(k)$  is the impulse response of DT loop filter  $L_1(z)$ . It is easy to solve the above equation set in MATLAB and get the answer of  $\alpha_i$ .

$$\begin{bmatrix} \alpha_{1} \\ \alpha_{2} \\ \alpha_{3} \\ \alpha_{4} \\ \alpha_{5} \end{bmatrix} = \begin{bmatrix} h_{1}(1) & h_{2}(1) & h_{3}(1) & h_{4}(1) & h_{5}(1) \\ h_{1}(2) & h_{2}(2) & h_{3}(2) & h_{4}(2) & h_{5}(2) \\ h_{1}(3) & h_{2}(3) & h_{3}(3) & h_{4}(3) & h_{5}(3) \\ h_{1}(4) & h_{2}(4) & h_{3}(4) & h_{4}(4) & h_{5}(4) \\ h_{1}(5) & h_{2}(5) & h_{3}(5) & h_{4}(5) & h_{5}(5) \end{bmatrix}^{-1} \begin{bmatrix} h_{d}(1) \\ h_{d}(2) \\ h_{d}(3) \\ h_{d}(4) \\ h_{d}(5) \end{bmatrix}$$

(3.13)

By making the feed-forward coefficients equal to corresponding  $\alpha_i$ , the total impulse response of the open-loop CT modulator (DAC(t) \* h(t)) at the sampling instants will be the same as that of DT loop filter  $L_1(z)$ .

This novel synthesis methodology of the CT  $\Delta\Sigma$  loop filter realizes the impulseinvariant transformation (IIT) and the mapping of the CT transfer function for a given loop filter topology at the same time. The procedure is summarized as following:

Step 1: Synthesize the target DT NTF and hence the  $L_1(z)$  based on the specification of the ADC by using  $\Delta\Sigma$  toolbox [20]. Get the impulse response of  $L_1(z)$  by simulation.

Step 2: Determine the DAC waveform and the structure of the CT  $\Delta\Sigma$  modulator. Build the simulation diagram in SIMULINK.

Step 3: Calculate the coefficients of the local feedback loops in the CT modulator by substituting the non-DC zeros of the DT NTF to Eq. 3.10.

Step 4: Identify a set of coefficients that can adjust the gain of each loop in the CT modulator independently.

Step 5: Simulate the impulse response of each loop by setting the corresponding coefficient to be one and the others to be zero. The expression of the total sampled impulse response of the CT modulator is the linear combination of those individual responses.

Step 6: Build up an equation set for the coefficients of the linear combination by equating those two impulse response obtained in Step 1 and 5. Solve this equation set to get the coefficients.

Step 7: Calculate the coefficients of the branches in the CT loop filter based on those independent coefficients acquired in Step 6.

# **3.3. Signal Transfer Function (STF)**

The synthesis of a CT  $\Delta\Sigma$  modulator from a DT target by using IIT only considers the equivalence in terms of the noise transfer function, so this transformation cannot guarantee the

signal transfer function of the CT modulator is the same as the DT one (usually they are different).

According to the general structure shown in Fig. 3.1b, the STF of the CT modulator can be given by:

$$STF(s) = \frac{L_0(s)}{1 - LTF(z)} = L_0(s) \cdot NTF(z) \Big|_{z=e^s}$$

(3.14)

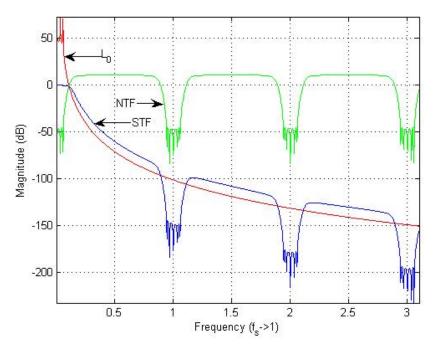

In a feedback CT  $\Delta\Sigma$  modulator (see Fig. 3.6), the transfer function of  $L_0(s)$  is an allpole system whose poles are the same as the zeros of the NTF in the band of interest. So, the magnitude of the STF in the signal band is flat and equal to one if the feed-in branch coefficient is equal to that of the first feedback branch in magnitude. In addition, outside the signal band, the STF shows low-pass characteristics. Fig. 3.7 shows the magnitude response of  $L_0(s)$ , NTF(z) and STF(s) of the modulator shown in Fig. 3.6.

Figure 3.6: Diagram of a 5<sup>th</sup>-order feedback CT  $\Delta\Sigma$  modulator

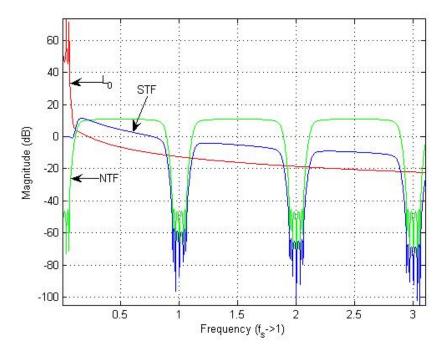

As for the feed-forward CT modulator like that shown in Fig. 3.4, the  $L_0(s)$  shares the same circuits with  $L_1(s)$ . The poles of the  $L_0(s)$  are still the same as the zeros of the NTF in the signal band. However, it also shows zeros in its transfer function, which are introduced by the feed-forward paths. Those zeros will cause the out-of-band peaking in the STF magnitude. Fig. 3.8 shows the magnitude response of  $L_0(s)$ , NTF(z) and STF(s) of this feed-forward modulator.

Figure 3.7: Magnitude response of  $L_0(s)$ , NTF(z) and STF(s) of a 5<sup>th</sup>-order feedback CT  $\Delta\Sigma$  modulator

Figure 3.8: Magnitude response of  $L_0(s)$ , NTF(z) and STF(s) of a 5<sup>th</sup>-order feed-forward CT  $\Delta\Sigma$  modulator

The same out-of-band peaking appears in the DT feed-forward  $\Delta\Sigma$  modulator, but it is easy to cancel it by adding a direct feed-in branch to the input of the quantizer [25] because the zeros of the new transfer function,  $1+L_0(z)$ , are the same as the poles of the NTF. However, in the CT case, the out-of-band peaking cannot be cancelled in the same way because the zeros of the new transfer function,  $1+L_0(s)$ , are still different from the poles of the NTF in terms of Eq. 3.8.

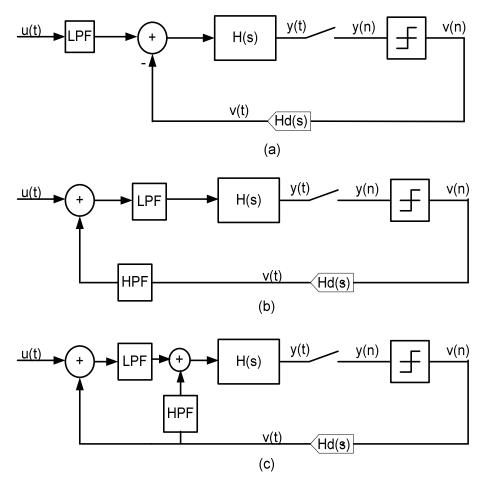

In order to compensate the out-of-band peaking in the STF of the feed-forward CT modulator, some new ideas were proposed in publications [8, 26]. One of them is to modify the STF by adding a low-pass (usually first-order) transfer function in series with the original STF. Two methods can be used to realize this idea without affecting the loop transfer function that should be the same as the DT origin in terms of impulse response. One is to directly add the low-pass filter at the front end of the CT modulator (Fig. 3.9a), and the other is to add the low-pass filter in the loop with a compensation high-pass filter. The transfer function of the high-pass filter should be 1/LPF(s) (Fig. 3.9b) or 1 - LPF(s) (Fig. 3.9c). All of those three CT modulators have a filtering STF:

$$STF(s) = LPF(s) \cdot STF(s)_{feed-forward} = LPF(s) \cdot H(s) \cdot NTF(z)|_{z=e^s}$$

(3.15)

These approaches showed good results in high OSR modulators but they are not suitable for low OSR design. Because, in a low OSR modulator, the out-of-band peaking is very close to (or even in) the signal band, the added low-pass filter will introduce attenuation around the edge of the signal band. It is difficult to find a good trade-off between the effectiveness of the filtering and the amount of the in-band attenuation. In this work, a new way is proposed to cancel the out-of-band peaking in the STF, which will be described later.

A very important characteristic that makes the CT  $\Delta\Sigma$  modulators superior to the DT counterparts is the inherent anti-aliasing. As we mentioned in the chapter 2, an anti-aliasing

filter is needed before an ADC otherwise the out-of-band signals, especially those within the frequency ranges of ( $nf_s$ - $f_B$ ,  $nf_s$ + $f_B$ ), will alias into the band of interest after sampling. However, from both Fig. 3.7 and 3.8, those obvious notches around the multiples of the sampling frequency can be seen in the magnitude response of the STF. This is known as inherent antialiasing. From Eq. 3.14, we can see that the zeros of the NTF are also the zeros of the STF except those which are cancelled by the poles of  $L_0$  within the signal band. Because the zeros of the NTF reside around the multiples of the sampling frequency, the CT  $\Delta\Sigma$  modulators can attenuate the signals in those bands and hence are inherent anti-aliasing.

Figure 3.9.Three feed-forward CT  $\Delta\Sigma$  modulators with filtering STF

# CHAPTER 4. DESIGN ISSUES OF CONTINUOUS-TIME $\Delta\Sigma$ MODULATOR

After successfully synthesizing the continuous-time (CT) loop filter from the discretetime (DT) target for a given feedback DAC waveform, we need to realize the modulator with real circuit blocks. However, the non-idealities of those circuit blocks as well as the clock source will influence the performance, even the stability, of the CT  $\Delta\Sigma$  modulator. In this chapter, some the most critical design issues are discussed in detail, which include the nonidealities of the CT integrators and the internal flash ADC, clock jitter, and element mismatch of the multi-bit feedback DAC. For each issue, detailed analysis and example simulation are presented, and then the possible solutions are discussed.

## 4.1. Non-Idealities of CT Integrators

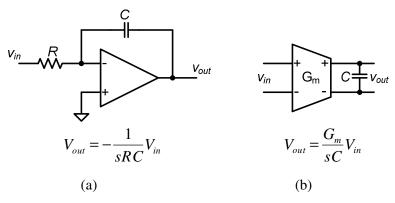

The basic circuit blocks of which a CT loop filter consists are the CT integrators. Many kinds of CT integrators are available but the most commonly used ones are RC integrators and  $G_mC$  integrators (see Fig. 4.1).

Figure 4.1: (a) RC and (b) G<sub>m</sub>C integrators

The advantages of the RC integrators over the  $G_mC$  counterparts include higher linearity and larger input signal swing. Because the RC integrators are based on the closedloop applications of the operational amplifiers (opamps), the opamps' inputs are virtual ground and only experience very small signal swing regardless of that of the integrator's input. On the contrary, the transconductor, which performs voltage-to-current (V-I) transformation with a known (or well-controlled) transconductance, operates under the open-loop condition in the  $G_mC$  integrators, so its inputs have to experience the full swing of the integrator's input, which degrades the linearity of the integrator. Due to this reason, the input signal of the  $G_mC$ integrator has to be small enough to keep a reasonable linearity.

When using RC integrators to build a CT  $\Delta\Sigma$  modulator, the virtual ground provided by the closed-loop opamp application will also greatly improve the linearity of the feedback current DAC whose outputs are connected with the inputs of the opamp. However, in a CT  $\Delta\Sigma$ modulator based on G<sub>m</sub>C integrators, the feedback DAC's outputs have to be connected with the output of the integrator and hence experience the full output swing, which degrades the linearity of the DAC.

On the other hand, due to the same open-loop working condition, the speed performance of the  $G_mC$  integrator is better than the RC counterparts. In other words, the power consumption of the  $G_mC$  integrator will be lower for a given bandwidth requirement.

According to the above analysis, the RC integrators are preferred in our prototype CT modulator, so only the non-idealities of the RC integrators will be discussed in this section.

#### 4.1.1. Finite Gain Bandwidth of Opamp

Operational amplifiers are the basic blocks of the RC integrators. An ideal opamp can be seen as a voltage-controlled voltage source whose voltage gain is infinitely large across the whole frequency domain. However, a real opamp has a finite DC gain and several poles and zeros in its transfer function. In analysis, it is popular and reasonable to approximate the real opamp's characteristics with a single-pole model given by:

$$A(s) = \frac{A_{DC}}{1 + \frac{s}{\omega_P}}$$

(4.1)

where  $A_{DC}$  and  $\omega_P$  stand for the DC gain and the pole frequency of the opamp, respectively.

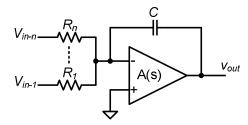

Using this opamp model in a general *n*-input RC integrator shown in Fig. 4.2, the integrator transfer function (ITF) from the  $i^{th}$  input to the output can be calculated by using the Kirchhoff Current Law (KCL) at the negative input point of the opamp.

$$ITF(s)\Big|_{V_{in-i} \sim V_{out}} = -\frac{1}{R_i} \frac{1}{\frac{C}{A_{DC}\omega_P} s^2 + \left(\frac{(A_{DC}+1)C}{A_{DC}} + \frac{1}{A_{DC}\omega_P} \left(\sum_{k=1}^n \frac{1}{R_k}\right)\right) s + \frac{1}{A_{DC}} \left(\sum_{k=1}^n \frac{1}{R_k}\right)}$$

(4.3)

If  $A_{DC} \gg 1$ , which is a common case in real opamps, the above equation can be simplified as:

$$ITF(s)\Big|_{V_{in-i} \sim V_{out}} = -\frac{1}{R_i} \frac{1}{\frac{C}{A_{DC} \omega_p}} s^2 + \left(C + \frac{1}{A_{DC} \omega_p} \left(\sum_{k=1}^n \frac{1}{R_k}\right)\right) s$$

$$= -\frac{1}{sR_iC} \cdot \frac{1 - \frac{\left(\sum_{k=1}^n \frac{1}{R_kC}\right)}{GBW + \left(\sum_{k=1}^n \frac{1}{R_kC}\right)}}{1 + \frac{s}{GBW + \left(\sum_{k=1}^n \frac{1}{R_kC}\right)}}$$

$$(4.4)$$

where  $GBW = A_{DC} \cdot \omega_P$  stands for the gain bandwidth product of the opamp.

Figure 4.2: An *n*-input RC integrator

It is convenient to normalize the RC time constants of the integrators to the sampling period,  $T_s$  or  $1/f_s$ , of the CT  $\Delta\Sigma$  modulator because the  $T_s$  is usually assumed to be one while synthesizing the CT loop filter using the IIT. So, we have following equation:

$$\frac{1}{R_k C} = \frac{K_k}{T_s} = K_k f_s \tag{4.5}$$

where  $K_k$  is the scaling coefficient.

Compared with the ideal integrator transfer function shown in Fig. 4.1a, Eq. 4.4 represents the gain error (GE) and second pole ( $\omega$ ) which are introduced by the finite gain bandwidth of the opamp:

$$GE = \frac{\sum_{k=1}^{n} K_k f_s}{GBW + \sum_{k=1}^{n} K_k f_s} \text{ and } \omega = GBW + \sum_{k=1}^{n} K_k f_s$$

(4.6)

So, the integrator transfer function can be represented as

$$ITF(s)\Big|_{V_{in-i} \sim V_{out}} = -\frac{K_i}{sT_s} \cdot \frac{1 - GE}{1 + \frac{s}{\omega}}$$

(4.7)

Fig. 4.3a shows a typical diagram of the first stage of the CT  $\Delta\Sigma$  modulator, in which the integrator block is modeled with Eq. 4.7.

Figure 4.3: The first stage of CT modulator with finite GBW opamp

To understand the effect of the gain error and the second pole of the integrator on the modulator, we redraw the diagram as Fig. 4.3b. The effect of the gain error is equivalent to that of the RC time constant variation which will be discussed in the next section. It can be compensated by adjusting the coefficient  $K_k$  with some kind of tuning techniques. The second pole of the integrator equivalently adds a low-pass filter in both the feed-in and feedback branches. For the feed-in branch, this low-pass filter has little effect because the signal frequency is usually much lower than the pole frequency  $\omega$ . However, this is not the case in the feedback branch. As discussed in [27], the low-pass filter in the feedback path equivalently introduces a delay which affects the modulator in the same as the excess loop delay introduced by the quantizer. The solution to compensate this delay will be described in the section 4.2.

## 4.1.2. Variation of RC Time Constant

As we discussed before, the accuracy of the integrator transfer function is related to that of the RC time constant. In modern semiconductor process, the absolute values of resistors and capacitors can vary as large as  $\pm 15\%$  independently due to the change of process, supply voltage and temperature (PVT), so it is reasonable to believe that the RC product and hence the integrator gain can vary  $\pm 30\%$ .

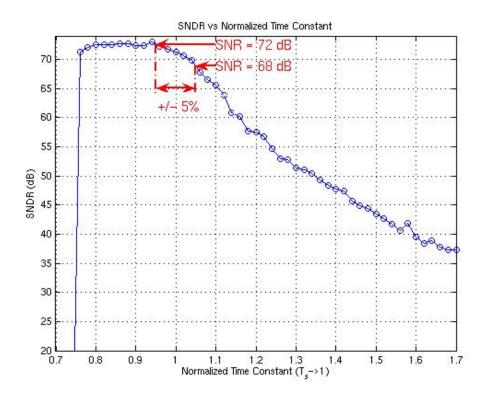

In order to see the effect of the RC time constant variation on a CT  $\Delta\Sigma$  modulator, a system-level simulation is performed on the feed-forward modulator shown in Fig. 3.4. In this simulation, the normalized time constant is swept in the range from 0.7 to 1.7.

Figure 4.4: The effect of RC time constant variation on the CT modulator

From the simulation results shown in Fig. 4.4, we find that when the time constant deviates from its nominal value  $T_s$ , the performance of the modulator will degrade. When the time constant becomes smaller, a better signal-to-noise ratio (SNR) may result due to the higher loop filter gain. However, the system becomes unstable when the normalized time constant decreases to be about 0.76. If the time constant is larger than  $T_s$ , although the modulator is more stable, the noise shaping is less efficient due to the smaller loop filter gain, and hence the in-band noise power increases. So, during the system level design, the in-band noise increasing due to the time constant variation should be considered in the whole noise

budget. If only 2-dB degradation in SNR is allowed, above simulation results show that the variation of less than  $\pm 5\%$  is necessary.

To make the RC product variation as small as  $\pm 5\%$ , some kind of tuning technique has to be used. In the past several decades, many useful tuning techniques were published for designing continuous-time filters [28 ~ 31]. In a CT  $\Delta\Sigma$  modulator based on RC integrators, it is more convenient to tune the capacitors instead of the resistors to adjust the RC product because the integration capacitor is shared by all input resistors. Fig. 4.5 shows the diagram of a tunable capacitor array which consists of binary-weighted capacitors.

Figure 4.5: A 3-bit binary-weighted tunable capacitor

The D<2:0> is a 3-bit tuning code. The nominal value of it is "100", which leads the total capacitance  $C_t$  equal to that of eight unit capacitors. The tuning range of this capacitor array is from -50% to +37.5% with the step size of 12.5%. If we want to reduce the step size to increase the tuning accuracy, the always-on capacitance should be increased. For example, if we set it to be 8C instead of 4C, then the tuning accuracy is increased to be about 8.3%. However, the tuning range is reduced, which is from -33.3% to +25%.

#### 4.2. Non-Idealities of Quantizer

In a wideband CT  $\Delta\Sigma$  modulator, a multi-bit quantizer is usually used to reduce the quantization noise as well as the clock jitter sensitivity. The non-idealities of this fast multi-bit

quantizer, which include the excess delay, comparator offset, hysteresis, and metastability, will greatly affect the performance of the whole modulator.

# 4.2.1 Quantizer Delay (Excess Loop Delay)

When we synthesize the CT loop filter  $L_1(s)$  from a DT target  $L_1(z)$  for a given feedback DAC waveform in the section 3.1, it is assumed that the delay between the sampling instant of the loop filter output and the generation of new output is zero. However, in the real circuits, this delay, known as excess loop delay, is non-zero due to the finite speed of transistors. The excess loop delay usually consists of the delays introduced by the quantizer (including the dynamic element matching (DEM) logic if necessary), DAC, and loop filter. In section 4.1.1, the delay caused by the loop filter has been analyzed and replaced with the equivalent one in the feedback path so the total excess loop delay can be modeled with a delay cell in the feedback path.

If the excess loop delay is considered, the impulse response of those three rectangular DAC pulses shown in Fig. 3.3 is changed to be that in Fig. 4.6.

Figure 4.6: Impulse responses of the rectangular DAC pulses including excess loop delay: (a) NRZ; (b) RZ; (c) HRZ

For NRZ and RZ pulses, the delay  $t_d$  includes the whole excess loop delay. However, if using HRZ DAC pulse, the quantizer delay, and even the delay introduced by the DEM logic, can be absorbed by the explicit half clock delay of the DAC pulse, so the  $t_d$  in Fig 4.6c

mainly refers to the DAC switching delay and the equivalent delay caused by the finite gain bandwidth of the integrators in the loop filter.

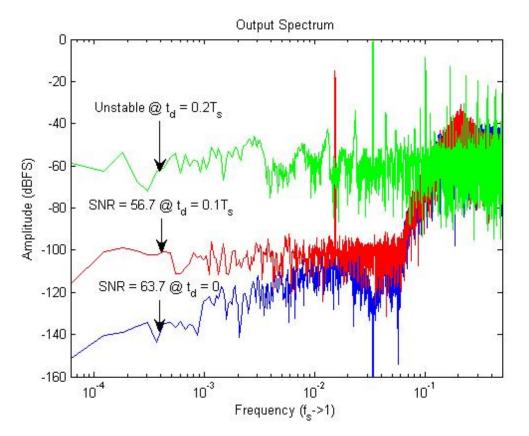

As analyzed in [18], if the falling edge of the DAC pulse exceeds the time instant  $T_s$ , the order of the equivalent DT loop filter of the CT one is higher by one than under ideal conditions, which makes the CT modulator uncontrolled. The excess loop delay degrades the dynamic range of the modulator by reducing the effectiveness of the noise shaping as well as the maximum stable input signal swing. If the excess loop delay is too large compared with the clock period, the CT modulator will be unstable. Fig. 4.7 shows the simulation results of the feed-forward CT modulator given by Fig. 3.4 with three different excess loop delays  $t_d$ .

Figure 4.7: The effect of the excess loop delay on the CT modulator

In order to compensate the excess loop delay, the RZ pulse can be used as the DAC waveform. From Fig.4.6b, it can be seen that if the excess loop delay is smaller than half clock period, then the falling edge is still within the range of  $0 \sim T_s$ , and hence the equivalent DT loop filter has the same order of the CT one. However, in most wideband CT  $\Delta\Sigma$  modulators, the NRZ DAC pulse is superior to the RZ (or HRZ) counterpart in terms of clock jitter sensitivity which will be analyzed in detail in section 4.3. In addition, because the exact value of the excess loop delay  $t_d$  is unknown while synthesizing the CT loop filter, the resulting CT modulator still cannot realize the same noise shaping as the DT target even using RZ DAC pulse.

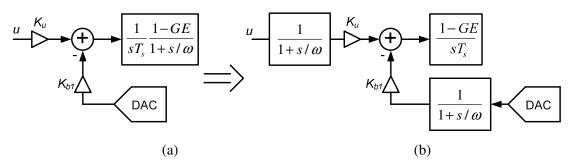

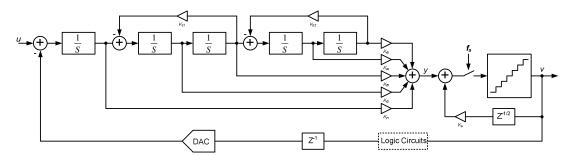

A common solution to the excess loop delay while using NRZ DAC pulse is to introduce an explicit full clock delay in the feedback path to absorb the varying quantizer delay as well as the other delays caused by the possible logic circuits (see Fig. 4.8). However, due to this full clock delay, the impulse response of the CT loop at the sampling instant  $T_s$  is zero. To compensate this response sample, an extra feedback branch is added directly to the quantizer input to make the total impulse response equivalent to the DT target [32]. Because the loop formed by the extra feedback branch doesn't include any integrator, we call this loop zero-order loop.

Figure 4.8: The feed-forward CT  $\Delta\Sigma$  modulator with excess loop delay compensation

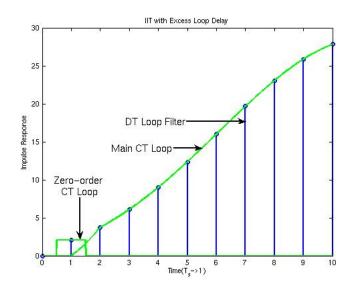

As an example, the impulse-invariant transformation with this excess loop delay compensation is performed between the above CT modulator and a DT target. The resulting impulse responses are shown in the Fig. 4.9. It is obvious that the zero-order loop doesn't affect any other samples of the impulse response which are formed by those original loops. Although a half clock delay is used in the direct feedback path to compensate the quantizer delay in this example, the real delay of the quantizer can be any value between 0 and  $T_s$ , which greatly relaxes the speed requirement of the quantizer.

Figure 4.9: Impulse-invariant transformation with the compensation for excess loop delay

It should be mentioned here that above scheme cannot compensate the DAC delay and the equivalent delay caused by the finite integrator GBW. However, compared with the quantizer delay, those two delays are much smaller which can be partially compensated by adjusting the timing relationship between the quantizer and DAC clock signals.

## 4.2.2. Real Characteristics of Comparator

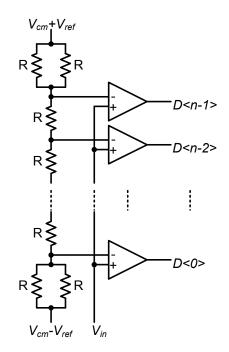

The quantizer in a  $\Delta\Sigma$  modulator is usually a flash ADC which consists of a comparator array and a resistor string to generator a thermometer-code output (see Fig. 4.10).

Figure 4.10: Diagram of the quantizer (flash ADC)

$V_{cm}$  is the common mode voltage of the input signal  $V_{in}$  and  $2V_{ref}$  is the full-scale of the quantizer.

Besides the excess loop delay, the offset, hysteresis and metastability of the comparators are three important non-idealities of the quantizer which will affect the performance of a CT  $\Delta\Sigma$  modulator.

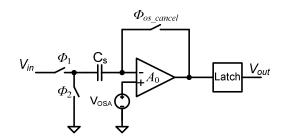

In a commonly used latched comparator, a preamplifier is usually added before the latch to reduce its input-referred offset (see Fig. 4.11). As for the offset of the preamplifier itself, some input offset storage techniques, e.g., auto-zeroing, were proposed to reduce it. So, the total input-referred offset of the comparator is given by [33]:

$$V_{OS(total)} = \frac{V_{OSA}}{1+A_0} + \frac{\Delta q}{C_s} + \frac{V_{OSL}}{A_0}$$

(4.8)

where  $V_{OSA}$  and  $V_{OSL}$  are the input offset of the preamplifier and the latch respectively,  $\Delta q$  is the error due to the charge injection, and  $A_0$  is the gain of the preamplifier. From this equation, we can see that the offset of the comparator is attenuated by  $A_0$  which is normally between 10 and 20, so the comparator offset won't become a big problem in a  $\Delta\Sigma$  modulator.

Figure 4.11: Input offset cancellation of a comparator

Hysteresis refers to the memory characteristics of a quantizer, which means the quantizer does not make a decision to change the output when it should. Like a DC offset, the hysteresis will also degrade the noise performance of the  $\Delta\Sigma$  modulators. In order to reduce the hysteresis, the comparator should be reset before entering the regeneration period. For example, the differential internal nodes in the latch can be shorted to one of the power supplies or connected together using switches in the reset phase [34].

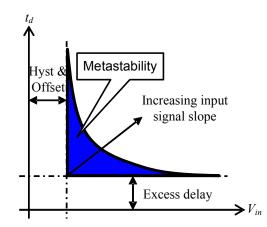

Metastability refers to the phenomenon that the regeneration time of the comparator becomes longer when the input signal is very small. Besides the signal magnitude, the slope of the input signal also affects the regeneration time. This varying delay will cause the output limit cycle behavior and variant feedback charge which folds the out-of-band noise into signal band in the same way the clock jitter does (see detail in section 4.3) Reference [35] proposed several methods to mitigate the performance loss due to the metastability, such as scaling the quantizer input to have as large as possible span; decreasing regeneration time by inserting a preamplifier stage and increasing the gain-bandwidth product of the regenerative circuits; adding additional latching stages and using improved modulator architectures. In conclusion, the real characteristics of a comparator can be that shown in Fig. 4.12.

Figure 4.12: Real characteristics of a comparator

where  $t_d$  refers to the delay of the comparator and  $V_{in}$  is the input signal amplitude.

## 4.3. Clock Jitter

In a DT  $\Delta\Sigma$  modulator, the continuous-time signal is sampled at the modulator input, so the sampling error caused by the clock jitter is directly added to the output without any attenuation. On the other hand, the sampling action in the CT modulator happens at the input of the quantizer, so the jitter-induced error is shaped by the loop filter before it appears at the output and hence may be negligible.