## AN ABSTRACT OF THE THESIS OF

<u>OnnLim Yong</u> for the degree of <u>Master of Science</u> in <u>Electrical and Computer</u> <u>Engineering</u> presented on <u>March 7, 2019</u>.

Title: <u>A Fully Integrated Bio-potential Low-noise Amplifier Utilizing Capacitor</u> <u>Multipliers.</u>

Abstract approved:

#### David J. Allstot

In any biomedical signal acquisition system, a front-end amplifier is needed to amplify low amplitude bio-signals while filtering out any unwanted low-frequency artifacts. The design of low frequency poles within the sub-Hz range implies very large time-constants which goes against system integrability. In recent years, the pseudo resistor has been used to provide very large on-chip resistance to achieve sub-Hz pole frequency. However, the pseudo resistor behaves poorly across PVT variations and is highly non-linear which makes the low-frequency pole unpredictable.

In this thesis, a bio-LNA utilizing a differential difference amplifier structure along with gm-C filters is examined. The differential topology provides high CMRR while the negative feedback through the gm-C filter provides the low-frequency pole. A capacitor multiplier is also implemented to achieve a very high value effective onchip capacitance. The functionality of the bio-LNA is validated through simulations in Cadence. ©Copyright by OnnLim Yong March 7, 2019 All Rights Reserved

## A Fully Integrated Bio-potential Low-noise Amplifier Utilizing Capacitor Multipliers

by OnnLim Yong

## A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Master of Science

Presented March 7, 2019 Commencement June 2019 Master of Science thesis of OnnLim Yong presented on March 7th 2019

APPROVED:

Major Professor, representing Electrical and Computer Engineering

Head of the School of Electrical Engineering and Computer Science

Dean of the Graduate School

I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my thesis to any reader upon request.

OnnLim Yong, Author

#### ACKNOWLEDGEMENTS

Of all the people who helped me get to where I am now, two individuals who deserve honorary recognitions are my parents. They shaped my personality and cultivated my love for knowledge since the very beginning. Their sacrifices will never be forgotten.

Next, I would like to express my immense gratitude to Professor David J. Allstot for giving me the opportunity to grow as an analog designer. Professor Allstot is a prominent figure in analog world and to have him as an advisor is a prodigious blessing. His astute guidance and perceptive teachings have deepened my appreciation for analog circuit design.

I would also like to thank Professor Un-Ku Moon and Professor Arun Natarajan for exposing the beauty and intricacies of analog design in my years as an undergraduate. Professor Moons uncanny intuitive sense followed by Professor Natarajans ability to simplify complex concepts influenced me to pursue my master's here in OSU. Also, many thanks to my committee members, Professors Un-Ku Moon, Matthew Johnston, and Len Coop for taking the time and energy to attend to my needs.

Finally, I would like to express my sincere appreciation towards my group mates Pavan and Ajmal, for helping me throughout my master's program. Their willingness to help clarify any uncertainties on my work has made my journey to graduation a lot more enjoyable and gratifying.

# TABLE OF CONTENTS

| 1 | Int | roduction1                        |

|---|-----|-----------------------------------|

|   | 1.1 | Biomedical Signals 1              |

|   | 1.2 | Biopotential Low-Noise Amplifier  |

|   | 1.3 | Pseudo Resistors                  |

| 2 | Caj | pacitor Multiplier                |

|   | 2.1 | The Miller Effect                 |

|   | 2.2 | Implementation                    |

| 3 | Dif | ferential Difference Amplifier 12 |

|   | 3.1 | Transfer Function                 |

|   | 3.2 | Design Procedure                  |

|   | 3.3 | Loop Gain 19                      |

|   | 3.4 | Implementation                    |

|   | 3.4 | .1 Two-stage OTA                  |

|   | 3.4 | .2 Gm <sub>o</sub>                |

|   | 3.4 | .3 Gm <sub>f</sub>                |

|   | 3.4 | .4 Capacitor Multiplier           |

| 4 | Sin | nulation Results                  |

|   | 4.1 | Frequency Response                |

|   | 4.2 | Noise                             |

| 4.3     | CMRR             |

|---------|------------------|

| 4.4     | PSRR             |

| 4.5     | Monte Carlo      |

| 4.5.    | 1 Pass-band Gain |

| 4.5.    | 2 Loop Gain      |

| 4.5.    | 3 DC Gain        |

| 4.5.    | 4 First Pole     |

| 4.5.    | 5 Second Pole    |

| 4.5.    | 6 CMRR           |

| 4.5.    | 7 PSRR           |

| 5 Cor   | nclusion         |

| 5.1     | Future Work      |

| Bibliog | raphy 44         |

| Append  | lices            |

# LIST OF FIGURES

| <u>Fig</u> | <u>Pag</u>                                              | <u>ge</u> |

|------------|---------------------------------------------------------|-----------|

| 1.         | Low-noise neural amplifier [13]                         | . 5       |

| 2.         | Frequency response of the low-noise neural amplifier    | . 6       |

| 3.         | Miller effect stating that $Ceff = 1 + A CF$            | . 8       |

| 4.         | Impractical implementation of a capacitor multiplier    | . 9       |

| 5.         | Current-mode Miller effect                              | . 9       |

| 6.         | Current-mirror implementation of a capacitor multiplier | 10        |

| 7.         | Equivalent circuit of the capacitor multiplier          | 11        |

| 8.         | Differential difference amplifier                       | 12        |

| 9.         | Proposed DDA configuration [31]                         | 13        |

| 10.        | High-pass characteristic of the DDA                     | 14        |

| 11.        | Plots of each stage in the DDA                          | 14        |

| 12.        | CMOS implementation of the DDA                          | 15        |

| 13.        | Small-signal behavior of the DDA                        | 17        |

| 14.        | Transfer function with different <i>rof</i> values      | 20        |

| 15.        | Two-stage DDA structure                                 | 22        |

| 16.        | Current-mirror OTA                                      | 24        |

| 17.        | Gain-boosted current-mirror OTA                         | 25        |

| 18.        | Gain-boosted capacitor multiplier                       | 26        |

| 19.        | Effect of the ESR on the transfer function              | 28        |

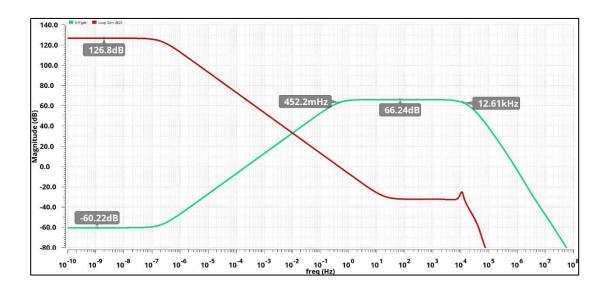

| 20.        | Magnitude and phase response of the DDA                 | 30        |

| 21.        | Magnitude and phase response of the feedback loop       | 31        |

| 22.        | DDA transfer function with loop gain                    | 31        |

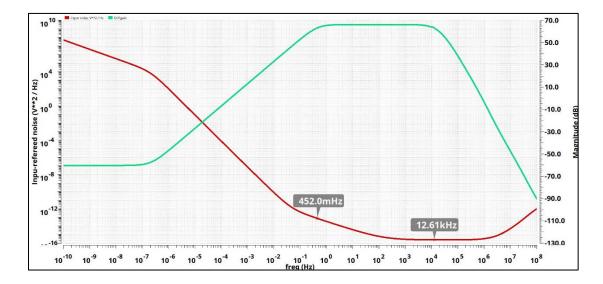

| 23. Input-referred noise with the DDA transfer function | . 33 |

|---------------------------------------------------------|------|

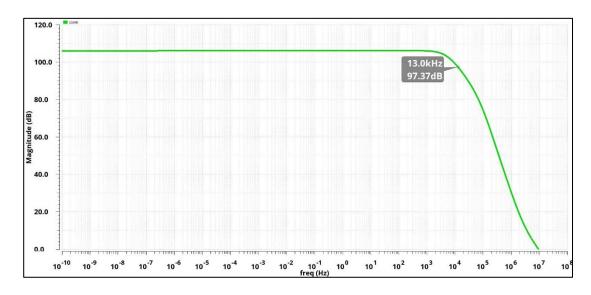

| 24. Common-mode rejection ratio of the DDA              | . 34 |

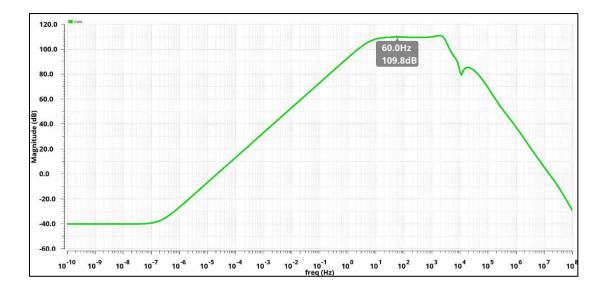

| 25. Power supply rejection ratio of the DDA             | . 35 |

| 26. Pass-band gain monte carlo plot                     | . 36 |

| 27. Loop gain monte carlo plot                          | . 37 |

| 28. DC gain monte carlo plot                            | . 38 |

| 29. First pole monte carlo plot                         | . 39 |

| 30. Zoomed version of first pole monte carlo plot       | . 39 |

| 31. Second pole monte carlo plot                        | . 40 |

| 32. Zoomed version of second pole monte carlo plot      | . 40 |

| 33. CMRR monte carlo plot                               | . 41 |

| 34. PSRR monte carlo plot                               | . 42 |

A Fully Integrated Bio-potential Low-noise Amplifier Utilizing Capacitor Multipliers

## **1** Introduction

#### **1.1 Biomedical Signals**

Biomedical signals are information-bearing signals that emanate from biological organisms. These signals shed light on the underlying biological and physiological processes that occur within the living organism. Amongst the many types of biomedical signals, the bioelectric signal can be measured through changes in electrical potential across a cell or an organ. These changes in action potential can be measured on the surface of the skin with electrodes which converts the ionic flow of currents in the biological tissue to the electronic flow of current in the amplifier. The fact that our muscles and nerves are stimulated by electrical signals makes the bioelectric signal the most widely used signal in most fields of biomedicine [1].

The three most common bioelectric signals are the electrocardiogram (ECG/EKG), the electromyogram (EMG) and the electroencephalogram (EEG). The ECG measures is the electrical activity of the cardiac muscles, the EMG measures the electrical activity of the skeletal muscles and the EEG measures the electrical activity of brain cells [2]. Each of these bioelectric signals help physicians diagnose and treat disorders related to the targeted organ.

## **1.2 Biopotential Low-Noise Amplifier**

In any biomedical recording apparatus, bioelectric signals measured by electrodes require proper amplification to allow for signal processing and digitization [3]. Due to the weak amplitudes of the measured biopotential signals, the biopotential amplifier itself must contribute very little noise to prevent signal corruption, hence the term biopotential low-noise amplifier (BPA) or (bio-LNA).

Each bioelectric signal has different amplitude and frequency characteristics as shown in Table 1. Therefore, to achieve optimum signal quality, bio-LNAs are usually designed for the specific application with appropriate gain and bandwidth. In the case where multiple bioelectric signals are of interest, the bio-LNA must provide at least 40 dB gain with a passband from 50 mHz to 10 kHz to accommodate all bioelectric signals listed in Table 1 [4, 5, 6].

| Bioelectric signal         | Frequency range (Hz) | Amplitude range (mV) |

|----------------------------|----------------------|----------------------|

| Electrocardiogram (ECG)    | 0.05 - 100           | 1 - 10               |

| Electromyogram (EMG)       | 500 - 10k            | 0.02 - 0.01          |

| Electroencephalogram (EEG) | 0.5 - 100            | 0.02 - 0.1           |

Table 1 Bioelectric signal characteristics [3]

Bio-LNAs are designed with a differential topology with high common-mode rejection ratio (CMRR) to reject common-mode noise and high power supply

rejection ratio (PSRR) to reject power line noise at 50/60 Hz. Bio-LNAs must also have high input impedance to minimize loading of the measured signal and to prevent source impedance unbalances caused by electrodes from deteriorating the overall CMRR [1, 3].

A common figure of merit that ties total noise and current consumption of bio-LNAs is the Noise Efficiency Factor (NEF) introduced by Stayaert et al. [7]. The NEF describes how many times the input-referred noise of a system is higher compared to that of an ideal bipolar transistor with the same current and bandwidth as shown in Eq. (1).

$$NEF = V_{rms,in} \sqrt{\frac{2 I_{total}}{\pi V_T 4kT BW}}$$

(1)

The NEF is a good figure of merit when comparing bio-LNAs with the same supply voltage. However, two different bio-LNAs with equal current consumption and input-referred noise will have the same NEF but different power dissipation due to the different supply voltages used. A more suitable figure of merit introduced by Muller et al. is the Power Efficiency Factor (PEF) which compares the total power consumption of the bio-LNA as shown in (2) [8].

$$PEF = NEF^2 V_{DD} = V_{rms,in}^2 \frac{2 P_{tot}}{\pi V_T 4kT BW}$$

(2)

Since most bioelectric signals are located at very low frequency, flicker noise becomes a major contributor for the total noise of the amplifier. The two most common solutions are to utilize the chopping technique or to utilize a topology with a bandpass frequency response. The chopper amplifier has been used by many to modulate flicker noise to the chopping frequency, however it requires additional circuitry which takes up a portion of the power budget [9, 10, 11]. On the other hand, utilizing a topology that provides a bandpass frequency response limits flicker noise contribution as well as filters out lower frequency artifacts [4, 5, 6, 12].

#### **1.3 Pseudo Resistors**

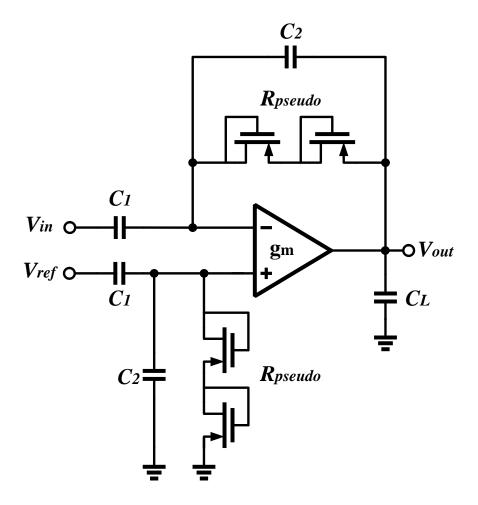

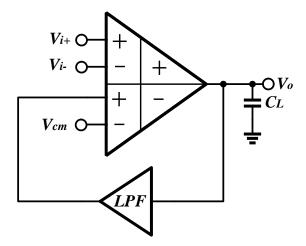

A bandpass frequency response can be obtained by introducing a zero followed by two poles. However, having a pole within the sub-Hz range implies that the circuit must have very large RC time-constants which may be achieved by off-chip components. In recent years, the focus has been to obtain a high valued on-chip resistor to achieve the sub-Hz pole frequency. Harrison et al. introduced a bio-LNA utilizing on-chip pseudo resistors to set the very low pole frequency as shown in Fig. 1 [13].

The pseudo resistor was first used in a photoreceptor circuit to adapt to different lighting conditions by providing huge effective resistance for small signals and small effective resistance for large signals [14]. When biased with positive  $V_{gs}$ , it behaves as a diode-connected pnp BJT and when biased with negative  $V_{gs}$ , it behaves as a

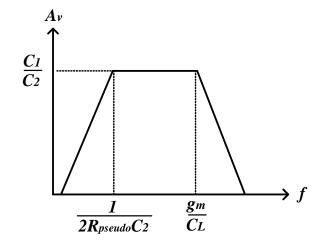

diode-connected PMOS transistor. As shown in the Fig. 2, the midband gain of the bio-LNA is given as  $C_1/C_2$  with a first pole of  $1/(2 R_{pseudo}C_2)$  and a second pole of  $g_m/C_L$ . The incremental resistance of the pseudo resistor achieved in [13] was greater than  $10T\Omega$  which resulted in a first pole of 0.025Hz.

Figure 1 Low-noise neural amplifier [13]

Figure 2 Frequency response of the low-noise neural amplifier

The prevalence of pseudo resistors in bio-LNAs, has made it possible to fabricate fully integrated biomedical acquisition systems [12, 13, 15]. However, one of the disadvantages of the pseudo resistor is that its effective resistance varies drastically across voltages [16]. The dependence of the pseudo resistor on its voltage drop coupled with PVT variations makes its effective resistance difficult to control. In essence, the variability of the pseudo resistor causes the first pole of the bio-LNA to wander across different chips.

Since its inception, multiple research groups have been investigating different approaches to solve the variability of pseudo resistors. A common theme amongst them is to make the pseudo resistor tunable so that its effective resistance can be accurately controlled manually or by means of feedback [17, 18, 19, 20, 21, 22].

Other intellectuals have moved away from pseudo resistors all together exploring other methods to achieve the sub-Hz pole frequency.

## 2 Capacitor Multiplier

Another way to achieve sub-Hz pole frequency is to utilize  $g_m C$  filters with very low transconductance and/or very large capacitors [23]. Sub-nS transconductances can be obtained by employing series-parallel current mirrors [24]. However, large capacitors are difficult to implement on-chip since its capacitance is limited by the available area. Capacitor multipliers solve this issue by producing an effective capacitance which is many times larger than the implemented capacitor negating the need of off-chip elements.

## **2.1 The Miller Effect**

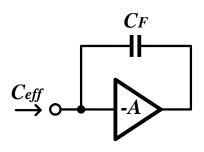

The Miller Effect indicates that the effective capacitance,  $C_{eff}$ , of a capacitor,  $C_F$ , when placed across an inverting gain stage, -A, is approximately  $(1 + A)C_F$  as shown in Fig. 3 [25]. The Miller Effect may be used to implement high-valued capacitors in  $g_mC$  filters to obtain very low pole frequency as shown in Fig. 4. However, this implementation is impractical as it limits the voltage swing at the output node and requires proper DC biasing for the amplifier [26].

Figure 3 Miller effect stating that  $C_{eff} = (1 + A) C_F$

Figure 4 Impractical implementation of a capacitor multiplier

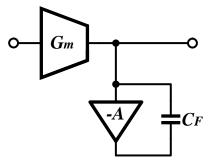

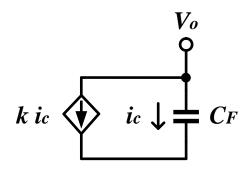

Instead of employing the Miller Effect in the voltage domain, capacitance scaling can be achieved in the current domain by sinking an amplified version of the current in the capacitor,  $k i_c$ , as shown in Fig. 5 [27]. The total current flow at the input node is  $i_c(k + 1)$  achieving an effective capacitance of  $C_F(k + 1)$ . The capacitor multiplier has been used to increase the compensation capacitance in a linear regulator as well as to increase the capacitance of the loop filter in a phase-locked loop [28, 29].

Figure 5 Current-mode Miller effect

## **2.2 Implementation**

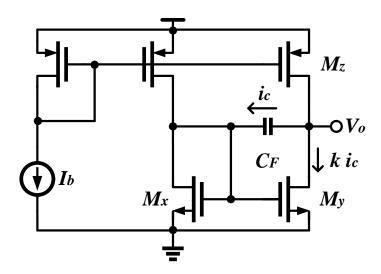

The simplest way to implement the capacitor multiplier is to utilize current mirrors as shown in Fig. 6 [28]. Devices  $M_X$  and senses the small-signal current flowing through the capacitor and scales the current to the output though  $M_Y$  which is k times larger than  $M_X$ . The effective capacitance looking in from the node  $V_o$  is  $C_F(k + 1)$ . With  $\frac{W}{L_Y} = k \frac{W}{L_X}$  the obvious disadvantage of this topology is that the current and area increases with the multiplication factor k.

Figure 6 Current-mirror implementation of a capacitor multiplier

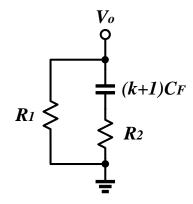

The equivalent circuit of the capacitor multiplier consist of a parallel load resistance (PLR),  $R_1$ , and an equivalent series resistance (ESR),  $R_2$ , as shown in Fig. 7. With  $R_1 = ro_x || ro_y$  and  $R_2 = 1/g_{mx}$ , the impedance looking in from  $V_o$  is now has a pole and zero at  $1/kC_F(R_1 + R_2)$  and at  $1/kC_FR_2$  respectively as shown in Eq. (3).

Figure 7 Equivalent circuit of the capacitor multiplier

$$Z_{in} \approx \frac{R_1(skC_FR_2 + 1)}{skC_F(R_1 + R_2) + 1}$$

(3)

## **3** Differential Difference Amplifier

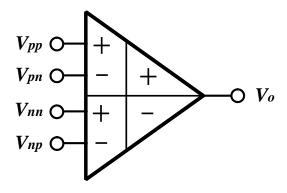

The differential difference amplifier (DDA) operates in a similar fashion as the standard op amp. The only difference is that the standard op amp amplifies a single differential input whereas the DDA amplifies the difference of two differential inputs as shown in Fig. 8 Differential difference amplifierand Eq. (4. As with the conventional op amp, various feedback arrangements are available to cater to different applications [30].

Figure 8 Differential difference amplifier

$$V_{o} = A_{v} \left[ \left( V_{pp} - V_{pn} \right) - \left( V_{nn} - V_{np} \right) \right]$$

(4)

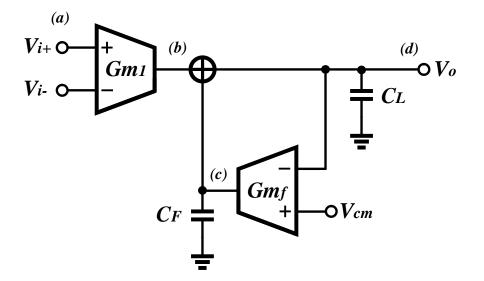

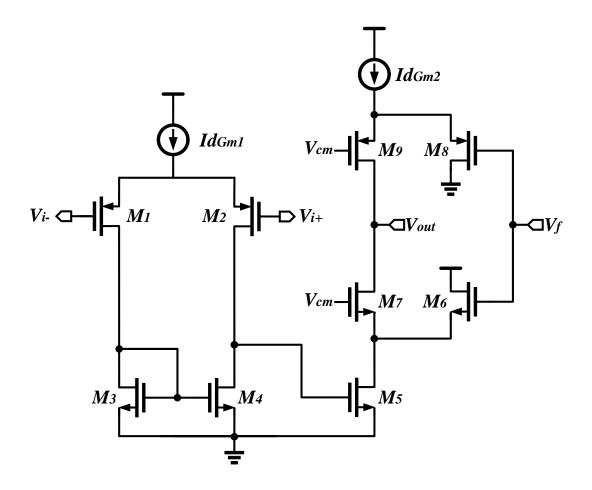

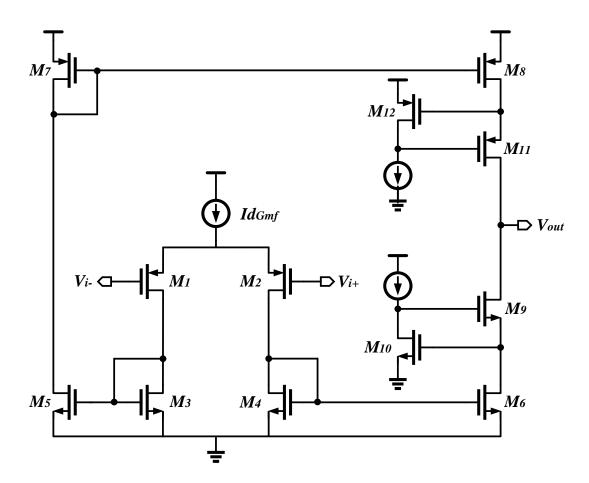

In an attempt to conceive of a design without pseudo resistors, Oreggioni et al. introduced a bio-LNA using a DDA to provide high CMRR for neural recording applications as shown in Fig. 9 Proposed DDA configuration [31] [31]. The DDA structure used is rather intriguing as it utilizes one differential input for amplification and the other for feedback to achieve the high-pass characteristic.

Figure 9 Proposed DDA configuration [31]

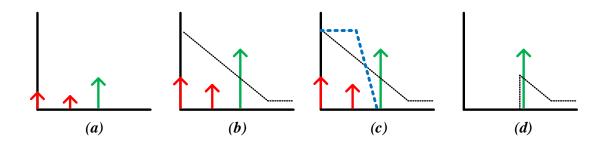

An intuitive way of understanding the high-pass characteristic of the feedback loop is shown in Fig. 10 High-pass characteristic of the DDA In Fig. 11(a), the input spectrum consist of the desired bio-signal (green) along with a DC component and lower frequency artifacts (red). As the signal passes through  $G_{m1}$ , each component is amplified but the spectrum is contaminated with flicker and thermal noise as shown in Fig. 11(b). The  $G_{mf}$  block has a low-pass response which can designed in such a way to filter out the signal of interest preserving only the DC component and lower frequency artifacts as shown in Fig. 11(c). When subtracted with the output of  $G_{m1}$ , the result will only contain the signal of interest and lower noise content as shown in Fig. 11(d). The resulting transfer function will have a bandpass nature which will be described in the next section.

Figure 10 High-pass characteristic of the DDA

Figure 11 Plots of each stage in the DDA

## **3.1 Transfer Function**

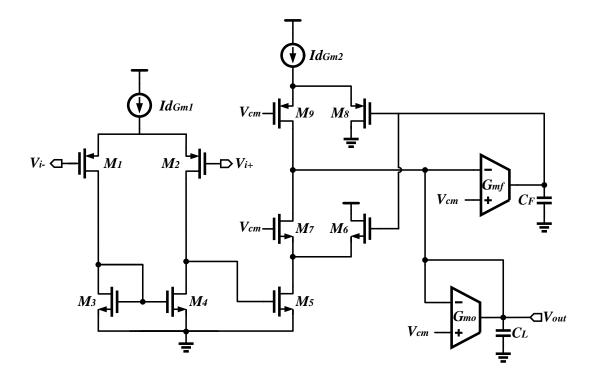

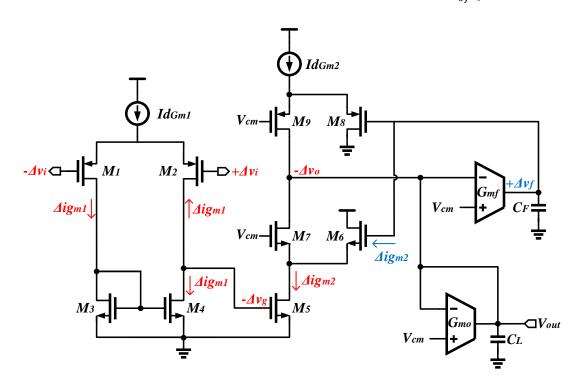

Figure 12 CMOS implementation of the DDA

The circuit in Fig. 12 features a two-stage OTA where  $G_{m1}$  and  $G_{m2}$  are the transconductance of the first and second stage respectively while  $R_{o1}$  is the output resistance of the first stage. The output of the second stage is taken into a negative feedback loop through  $G_{mf}$  and  $C_f$  which sets the first pole,  $f_{p1}$ . The ratio of  $G_{mo}$  to the transconductance of the two-stage OTA sets the midband gain, G, while the load capacitance  $C_L$  sets the second pole,  $f_{p2}$  as shown in (5)-(10). It is important to note that the zero,  $f_z$ , which is caused by the finite gain of  $G_{mf}$  affects the DC gain,  $G_{DC}$ , of the DDA and will be discussed in the next section.

$$\frac{V_{out}}{V_{in}} = \frac{\frac{G_{m1}G_{m2}R_{o1}}{C_L}\left(s + \frac{1}{r_{of}C_F}\right)}{s^2 + \frac{G_{mo}}{C_L}s + \frac{(g_{m6} + g_{m8})G_{mf}}{C_LC_F}}$$

(5)

$$G = \frac{G_{m1}G_{m2}R_{o1}}{G_{mo}}$$

(6)

$$G_{DC} = \frac{G_{m1}G_{m2}R_{o1}}{(g_{m6} + g_{m8})G_{mf}r_{of}}$$

(7)

$$f_z = \frac{1}{2\pi r_{of} C_F} \tag{8}$$

$$f_{p1} = \frac{(g_{m6} + g_{m8})G_{mf}}{2\pi C_F G_{mo}} \tag{9}$$

$$f_{p2} = \frac{G_{mo}}{2\pi C_L} \tag{10}$$

The appeal of this architecture is the implementation of the feedback loop producing the high-pass characteristic. Consider an undesirable low frequency smallsignal voltage at the input of the DDA, a small-signal current of  $\Delta i g_{m1}$  will flow through  $M_1$  and  $M_2$  as shown. This current will produce a voltage drop of  $\Delta v_g$  at the gate of  $M_5$  which in turn causes a current of  $\Delta i g_{m2}$  to flow from  $V_{out}$  to ground. Without the feedback loop, the output voltage will drop by  $\Delta v_o$  which is undesirable. With the feedback loop, the voltage drop at the output causes a voltage rise of  $\Delta v_f$  at the output of  $G_{mf}$  which increases current flow in  $M_6$ . This continues until  $I_{out} = 0$  or equivalently  $V_{out} = V_{cm}$ . This feedback loop will reject input signals from DC up to the cut-off frequency of the  $G_{mf}C_F$  block which is at  $f_{feedback} = \frac{1}{2\pi r_{of}C_F}$ .

Figure 13 Small-signal behavior of the DDA

#### **3.2 Design Procedure**

The design of the DDA starts with the gain specification which states that a high valued  $G_{m1}$  is required to provide high pass-band gain. In order to keep current consumption to the minimum,  $M_1$  and  $M_2$  are biased in weak inversion to yield a high  $g_m/I_d$  ratio. Having high  $G_{m1}$  is also crucial for lowering the input-referred noise. Depending on the choice of  $g_m/I_d$  value,  $G_{m1}$  and  $G_{m2}$  are determined from the current budget of the bio-LNA. Once  $G_{m1}$  and  $G_{m2}$  is determined,  $G_{m0}$  is chosen to meet the pass-band gain, G.

After selecting  $G_{mo}$ , the required load capacitance,  $C_L$ , is calculated to set the required low-pass cut-off frequency,  $f_{p2}$ . For the high-pass cut-off frequency,  $f_{p1}$ , the feedback capacitor,  $C_F$ , needs to be large and therefore is determined from the available area on-chip.  $G_{mf}$  along with  $g_{m6}$  are then designed to meet the required high-pass cut-off frequency.

It is important to note that  $M_6$  drains a portion of the AC signal current. To mitigate this issue,  $g_{m7}$  must be designed to be greater than  $g_{m6}$  so that the source impedance of  $M_7$  is lower than that of  $M_6$ . However,  $g_{m6}$  must not be too low as it plays a role in setting the DC gain as shown in (7. The design process is reiterated until all specifications are met.

#### 3.3 Loop Gain

The loop gain of the negative feedback loop contains two poles, one at  $1/C_F r_{of}$ and another at  $G_{mo}/C_L$  as shown in Eq. (11). The first and second pole represents the zero and the low-pass pole of the overall transfer function respectively. Therefore, a dominant single pole assumption can be made which states that the loop is stable with a phase margin of 90°. The loop gain plays an important role in setting the DC gain of the DDA,  $G_{DC}$ , because it is defined as the ratio of the pass-band gain of the DDA, G, and the loop gain,  $LG_{DC}$ , as shown in Eq. (13) which agrees with (7). Thus, achieving high loop gain is synonymous to obtaining low DC gain for the DDA.

$$LG \approx \frac{G_{mf}r_{of}(g_{m6} + g_{m8})}{G_{mo}(sC_F r_{of} + 1)(\frac{sC_L}{G_{mo}} + 1)}$$

(11)

$$LG_{DC} = \frac{G_{mf}r_{of}(g_{m6} + g_{m8})}{G_{mo}}$$

(12)

$$G_{DC} \approx \frac{G}{LG_{DC}} = \frac{G_{m1}G_{m2}R_{o1}}{(g_{m6} + g_{m8})G_{mf}r_{of}}$$

(13)

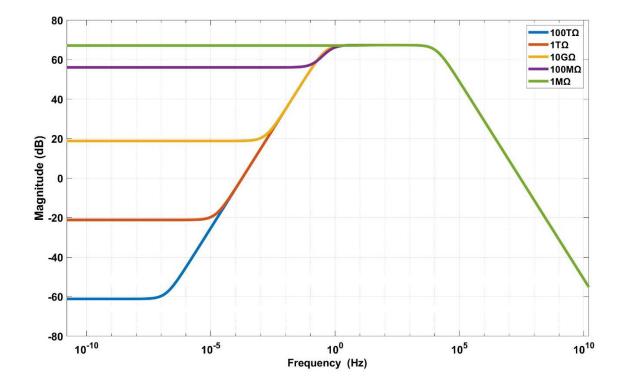

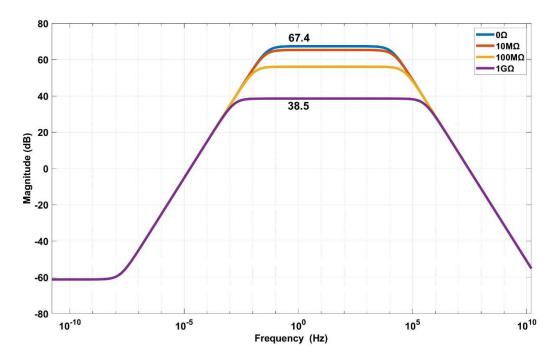

By plotting the transfer function of the DDA in Matlab (see appendix), the effect of the zero on the DC gain is observed. As the loop gain is reduced by reducing  $r_{of}$ , the DC gain increases and the DDA no longer has a band-pass characteristic as

shown in the Fig. 14. Hence, the output impedance of the  $G_{mf}$  is crucial in rejecting DC components as well as lower frequency artifacts.

Figure 14 Transfer function with different  $r_{of}$  values

## 3.4 mplementation

Iterating through the design process for the specifications in Table 2, the design parameters are obtained as shown in Table 3.

Table 2 Design specifications

| Table 2 Design specifications |       |  |

|-------------------------------|-------|--|

| Spec                          | Value |  |

| <b>G</b> ( <b>dB</b> )        | >40   |  |

| <i>G<sub>DC</sub></i> (dB)    | <-40  |  |

| $f_{p1}$ (mHz)                | <50   |  |

| $f_{p2}$ (kHz)                | >10   |  |

Table 3 Design Parameters

| Design Parameters                  | Value |

|------------------------------------|-------|

| Technology (nm)                    | 180   |

| VDD (V)                            | 1.8   |

| $G_{m1}G_{m2}R_{o1}$ (mS)          | 3.5   |

| <i>G<sub>mo</sub></i> (μS)         | 1.5   |

| $G_{mf}$ (nS)                      | 10    |

| <i>g</i> <sub>m6,8</sub> (μS)      | 2     |

| <i>C<sub>L</sub></i> (pF)          | 20    |

| <i>C<sub>F</sub></i> ( <b>pF</b> ) | 200   |

| k                                  | 50    |

| <i>Id<sub>Gm1</sub></i> (μA)       | 4     |

| <i>Id<sub>Gm2</sub></i> (μA)       | 1     |

| Id <sub>Gmo</sub> (nA)             | 100   |

| $Id_{G_{mf}}$ (nA)                 | 1     |

| I <sub>bias</sub> (nA)             | 1     |

| I <sub>total</sub> (μA)            | 5.38  |

## 3.4.1 Two-stage OTA

Figure 15 Two-stage DDA structure

The two-stage OTA was chosen primarily to provide high pass-band gain. A single stage OTA can be used as in [31] to lower current consumption. However, stacking five transistors lowers the voltage headroom for the current source which will degrade CMRR for lower supply voltages.

As mentioned in the previous section, the ratio of  $g_{m6}$  to  $g_{m7}$  determines how much pass-band gain is lost. For example, if  $g_{m6} = g_{m7}$ , half of the AC signal is lost and hence the pass-band gain is lowered by 6dB. In this design,  $g_{m6}$  is designed to be 10 times less than  $g_{m7}$ .

It is important to note that the output node of the first stage OTA contains a pole,  $f_{p3}$ , which can be less than  $f_{p2}$  if the output resistance,  $R_{o1}$ , or the parasitic capacitances at that node is too large as shown in Eq. (14. Therefore, it is important to keep that in mind when sizing the devices.

$$f_{p3} = \frac{1}{2\pi R_{o1}(C_{gs_5} + C_{gd_2} + C_{gd_4})}$$

(14)

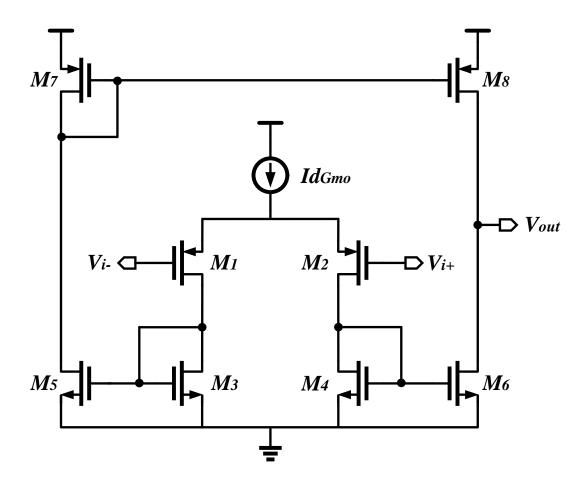

3.4.2 Gmo

Figure 16 Current-mirror OTA

A current-mirror OTA was chosen to implement the output transconductance block. As with the two-stage OTA, the  $G_{mo}$  block can be implemented with a single-stage OTA.

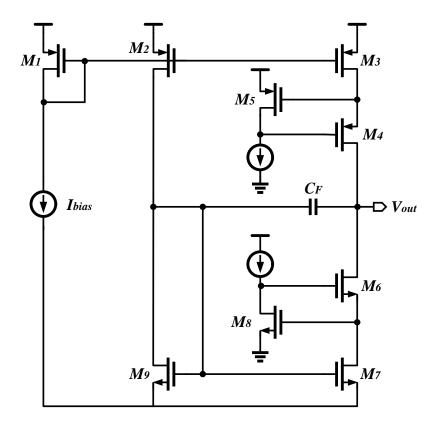

3.4.3 Gm<sub>f</sub>

Figure 17 Gain-boosted current-mirror OTA

The  $G_{mf}$  block is implemented with a current-mirror OTA with gain-boosted cascodes to increase the output impedance,  $r_{of}$ , as shown in Fig. 17. A common source configuration is used to boost the impedance of the output. In the case where output swing is limited, a folded cascode gain boost amplifier may be used.

## 3.4.4 Capacitor Multiplier

Figure 18 Gain-boosted capacitor multiplier

The capacitor multiplier is implemented with current-mirrors with gain-boosted cascodes to reduce the loading on the output node of  $G_{mf}$  as shown in Fig. 18. With a bias current of 1nA,  $gm_9$  will be in the order of a few tens of nS. As a result, the equivalent series resistance,  $R_{ESR}$ , of  $1/gm_9$  will have an effect on the overall transfer function. As  $R_{ESR}$  increases, G,  $f_{p1}$  and  $f_{p2}$  is scaled with a factor  $\alpha$  as shown in Eq. (15)-(18). Referring to the design parameters in Table 3 Design Parameters, a

$R_{ESR}$  of 1G $\Omega$  yields an  $\alpha$  of 27.67 which reduces the pass-band gain by 28.8dB and shifts the poles by the same factor as shown in Fig. 19 Effect of the ESR on the transfer function. The ESR also introduces a zero in the loop gain at  $1/R_{ESR}C_F$  as shown in Eq. (19).

$$G = \frac{1}{\alpha} \left( \frac{G_{m1} G_{m2} R_{o1}}{G_{mo}} \right) \tag{15}$$

$$f_{p1} = \frac{1}{\alpha} \left[ \frac{(g_{m6} + g_{m8})G_{mf}}{2\pi C_F G_{mo}} \right]$$

(16)

$$f_{p2} = \alpha \left(\frac{G_{mo}}{2\pi C_L}\right) \tag{17}$$

$$\alpha \approx 1 + \frac{G_{mf}(g_{m6} + g_{m8})R_{ESR}}{G_{mo}}$$

(18)

$$LG \approx \frac{G_{mf}r_{of}(g_{m6} + g_{m8})(sC_FR_{ESR} + 1)}{G_{mo}(sC_Fr_{of} + 1)(\frac{sC_L}{G_{mo}} + 1)}$$

(19)

Figure 19 Effect of the ESR on the transfer function

## **4** Simulation Results

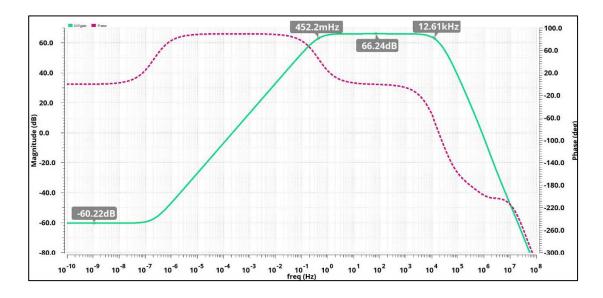

The bio-LNA was simulated with PVT variations of  $\pm 10\%$  V<sub>DD</sub> (1.62, 1.8, 1.98V), 5 process corners (tt, ss, ff, sf, fs), and temperatures of 0, 27 and 100°C. The minimum, typical and maximum simulation results are shown in Table 4.

| Spec                       | Min.   | Typical | Max.   |

|----------------------------|--------|---------|--------|

| <i>G</i> (dB)              | 65.91  | 66.24   | 69.16  |

| G <sub>DC</sub> (dB)       | -61.88 | -60.22  | -29.23 |

| $f_{p1}$ (mHz)             | 441.2  | 452.1   | 486.7  |

| $f_{p2}$ (kHz)             | 8.26   | 12.6    | 13.60  |

| I <sub>total</sub> (μA)    | 5.33   | 5.38    | 5.47   |

| <i>V<sub>ni</sub></i> (μV) | 2.99   | 3.33    | 3.72   |

| NEF                        | 2.43   | 2.65    | 3.23   |

| PEF                        | 9.58   | 12.60   | 20.59  |

| CMRR @<br>13kHz (dB)       | 94.74  | 97.37   | 98.72  |

| PSRR @<br>60Hz (dB)        | 105.8  | 109.8   | 111.2  |

Table 5 Simulation results

#### **4.1 Frequency Response**

The simulated  $f_{p1}$  was not able to achieve the desired value of less than 50mHz because the multiplication factor, k, is limited by matching as well as the loop gain. As k increases, mismatches in the current-mirror will worsen which will vary the location of  $f_{p1}$ . Furthermore, a high k lowers  $r_{of}$  which increases the DC gain of the DDA,  $G_{DC}$ . In the end, a k of 50 was used to multiply  $C_F$  to produce an effective capacitance of 10nF.

Figure 20 Magnitude and phase response of the DDA

The existance of the zero due to the ESR of the capacitor multiplier is seen in the loop gain plot in Fig. 21. Since the zero is at least a decade away from the unity gain

bandwidth, it does not affect the phase margin at all. Fig. 22 shows the relationship between the loop gain, pass-band gain and the DC gain as stated in (13).

Figure 21 Magnitude and phase response of the feedback loop

Figure 22 DDA transfer function with loop gain

#### 4.2 Noise

Fig. 23 Input-referred noise with the DDA transfer functionshows the inputreferred noise of the DDA plotted in log scale. Before the zero,  $f_z$ , the 1/f slope due to flicker noise is -10dB/dec. After  $f_z$ , the slope decreases to -30dB/dec due to the 20dB/dec slope of the transfer function. In the passband, flicker noise of -10dB/dec is observed until the corner frequency which is around 1kHz. The input-referred noise was integrated with a bandwidth from the first pole to the second pole to yield a NEF of 2.65 and a PEF of 12.6.

The devices in the first stage of the  $G_{m1}$  block dominated the overall noise contribution as shown in Table 6 Noise contribution.  $M_1$  and  $M_2$  contributed the most thermal noise followed by  $M_3$  and  $M_4$  because the noise current of  $M_{3,4}$  is divided by the transconductance of  $M_{1,2}$ . The flicker noise of  $M_{1,2}$  is lower  $M_{3,4}$  because the sizes of  $M_{1,2}$  are larger to increase the value of  $G_{m1}$ .

Figure 23 Input-referred noise with the DDA transfer function

| Device           | Noise<br>Type | Noise<br>Contribution |

|------------------|---------------|-----------------------|

| M <sub>1,2</sub> | Thermal       | 60.8%                 |

| M <sub>3,4</sub> | Thermal       | 25.8%                 |

| M <sub>3,4</sub> | Flicker       | 9.8%                  |

| M <sub>1,2</sub> | Flicker       | 3.6%                  |

Table 6 Noise contribution

## **4.3 CMRR**

The common-mode rejection ratio is taken at 13kHz as it is the location of the second pole. As shown in Fig. 24, a CMRR of 97.4dB is obtained.

Figure 24 Common-mode rejection ratio of the DDA

## **4.4 PSRR**

A power supply rejection ratio of 109.8dB is obtained at 60Hz as shown in Fig. 25.

Figure 25 Power supply rejection ratio of the DDA

#### 4.5 Monte Carlo

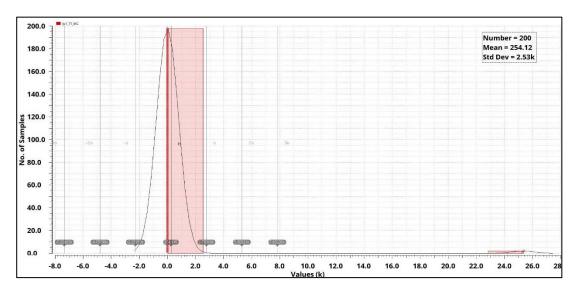

The monte carlo simulations were done with 200 samples. Out of the 200 samples 4 cases had mismatches that were too large for the feedback loop to handle which resulted in very low gain and erroneous pole locations.

#### 4.5.1 Pass-band Gain

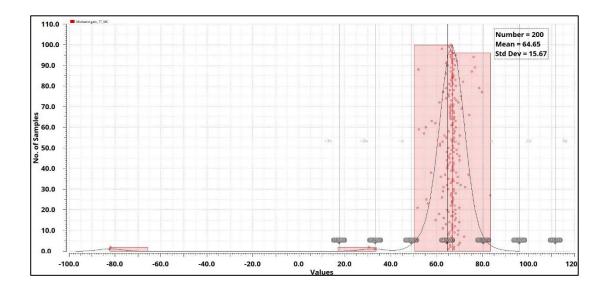

The pass-band gain has a mean of 64.65dB as shown in Fig. 26.

Figure 26 Pass-band gain monte carlo plot

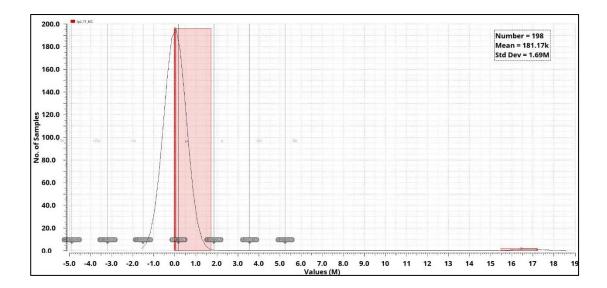

# 4.5.2 Loop Gain

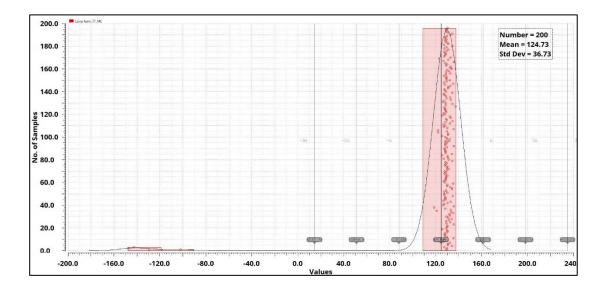

The loop gain has a mean of 124.73dB as shown in Fig. 27.

Figure 27 Loop gain monte carlo plot

### 4.5.3 DC Gain

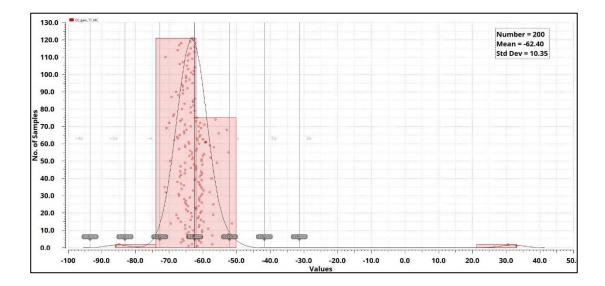

The DC gain has a mean of -62.4dB as shown in Fig. 28.

Figure 28 DC gain monte carlo plot

#### 4.5.4 First Pole

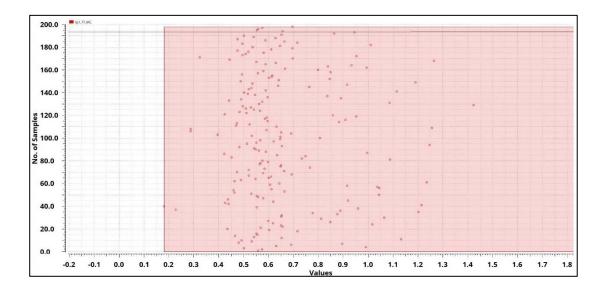

The mean and standard deviation in this case does not apply for the first pole as the circuit is not working properly under extreme mismatch cases. Shown in Fig. 30 is a zoomed version of the first pole variations. In some cases, the first pole is 3 times the designed value which is due to the mismatches in the capacitor multiplier.

Figure 29 First pole monte carlo plot

Figure 30 Zoomed version of first pole monte carlo plot

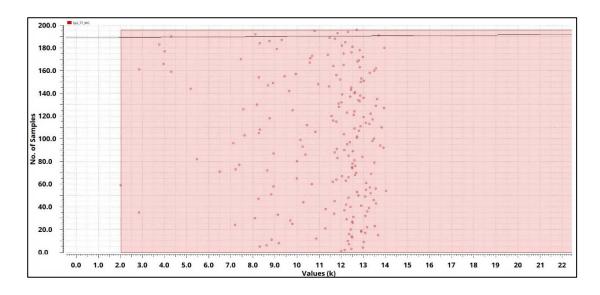

## 4.5.5 Second Pole

As with the first pole, the second pole monte carlo plot shows a few outliers due to the extremely low loop gain. The second pole varies as low as 2kHz for the worst case due to mismatches in  $G_{mo}$  as shown in Fig. 32.

Figure 31 Second pole monte carlo plot

Figure 32 Zoomed version of second pole monte carlo plot

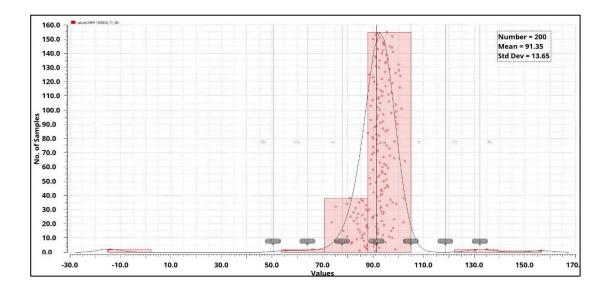

## 4.5.6 CMRR

The CMRR obtained has a mean of 91.35dB as shown in Fig. 33.

Figure 33 CMRR monte carlo plot

## 4.5.7 **PSRR**

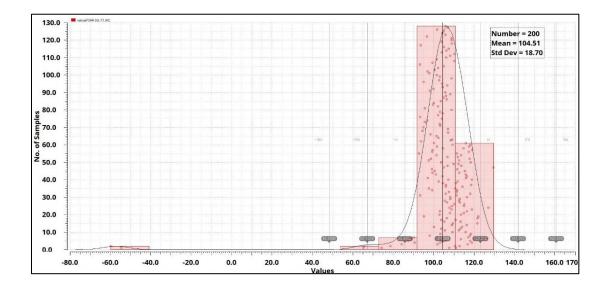

The PSRR has a mean of 104.51dB as shown in Fig. 34.

Figure 34 PSRR monte carlo plot

#### 5 Conclusion

In conclusion, a bio-LNA with a DDA structure is verified with simulations obtaining a pass-band from 452mHz to 12.6kHz with a pass-band gain of 66.24dB. The bio-LNA suppress lower frequency artifacts and DC components by 60.22dB while achieving a CMRR and PSRR of 97.37dB and 109.8dB respectively. The total current consumption is 5.28µA which resulted in a NEF of 2.65 and PEF of 12.6.

This bio-LNA is not suitable for ECG signals as the first pole is too high in frequency. However, this bio-LNA can be used to acquire EEG and EMG signals as described in Table 1 Bioelectric signal characteristics [1].

#### **5.1 Future Work**

Future works of this bio-LNA includes exploring other topologies that could take advantage of the feedback loop structure which may be beneficial to other applications. A more robust capacitor multiplier is also required to eliminate the issue of matching and the effect of the equivalent series resistance. More efficient transconductance blocks is also needed to lower power consumption and inputreferred noise which will lower the NEF and PEF.

#### **Bibliography**

- J. D. Bronzino, The Biomedical Engineering Handbook, 3rd Edition, Taylor & Francis Group, 2006.

- [2] R. M. Rangayyan, Biomedical Signal Analysis, A Case-Study Approach, John Wiley & Sons, 2002.

- [3] J. G. Webster, Medical Instrumentation, Application and Design, 4th Edition, John Wiley & Sons, 2010.

- [4] F. Zhang, J. Holleman and B. P. Otis, "Design of ultra-low power biopotential amplifiers for biosignal acquisition applications," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 6, no. 4, pp. 344-355, Aug. 2012.

- [5] T.-Y. Wang, M.-R. Lai, C. M. Twigg and S.-Y. Peng, "A fully reconfigurable low-noise biopotential sensing amplifier with 1.96 noise efficiency factor," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 8, no. 3, pp. 411-422, Jun. 2014.

- [6] T. Yang, J. Lu, M. S. Jahan, K. Griffin, J. Langford and J. Holleman, "A configurable 5.9 μW analog front-end for biosignal acquisition," in *IEEE Custom Integrated Circuits Conference*, Sept. 2015.

- [7] M. S. J. Steyaert, W. M. C. Sansen and C. Zhongyuan, "A micropower lownoise monolithic instrumentation amplifier for medical purposes," *IEEE Journal* of Solid-State Circuits, vol. 22, no. 6, pp. 1163-1168, Dec. 1987.

- [8] R. Muller, S. Gambini and J. M. Rabaey, "A 0.013 mm2, 5µW, DC-coupled neural signal acquisition IC with 0.5 V supply," *IEEE Journal of Solid-State Circuits*, vol. 47, no. 1, pp. 232-243, Jan. 2012.

- [9] Y. Tseng, Y. Ho, S. Kao and C. Su, "A 0.09 μW low power front-end biopotential amplifier for biosignal recording," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 6, no. 5, pp. 508-516, Oct. 2012.

- [10] T. Denison, K. Consoer, W. Santa, G. Molnar and K. Miesel, "A 2μW, 95nV/rtHz, chopper-stabilized instrumentation amplifier for chronic measurement of bio-potentials," *IEEE Instrumentation and Measurement Technology Conference*, pp. 1-6, May. 2007.

- [11] C. J. Mandic, D. Gangopadhyay and D. J. Allstot, "A 1.1µW 2.1µVrms input noise chopper-stabilized amplifier for bio-medical applications," *IEEE International Symposium on Circuits and Systems*, pp. 2881-2884, May. 2012.

- [12] W. Wattanapanitch, M. Fee and R. Sarpeshkar, "An energy-efficient micropower neural recording amplifier," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 1, no. 2, pp. 136-147, Jun. 2007.

- [13] R. Harrison and C. Charles, "A low-power low-noise CMOS amplifier for neural recording applications," *IEEE Journal of Solid-State Circuits*, vol. 38, no. 6, pp. 958-965, Jun. 2003.

- [14] T. Delbrück and C. A. Mead, "Analog VLSI adaptive, logarithmic widedynamic-range photoreceptor," *Proc. IEEE Int. Symp. Circuits and Systems*, vol. 4, pp. 339-342, 1994.

- [15] Y. Huang, T. Yang, S. Hsu, X. Chen and J. Chiou, "A novel pseudo resistor structure for biomedical front-end amplifiers," *37th Annual International Conference of the IEEE Engineering in Medicine and Biology Society*, pp. 2713-2716, 2015.

- [16] C. Pereira, P. L. Benko, J. C. Lucchi and R. C. Giacomini, "Teraohm pseudoresistor experimental characterization aiming at implementation of bioamplifiers," in *31st Symposium on Microelectronics Techonology and Devices*, 2016.

- [17] M.-T. Shiue, K.-W. Yao and C.-S. A. Gong, "Tunable high resistance voltagecontrolled pseudo-resistor with wide input voltage swing capability," *Electronics Letters*, vol. 47, no. 6, pp. 377-378, Mar. 2011.

- [18] R. Puddu, C. Carboni, L. Bisoni, G. Barabino, D. Pani, L. Raffo and M. Barbaro, "A precision pseudo resistor bias scheme for the design of very large time constant filters," *IEEE Transactions on CIrcuits and Systems II: Express Briefs*, vol. 64, no. 7, pp. 762-766, Jul. 2017.

- [19] H. Kassiri, K. Abdelhalim and R. Genov, "Low-distortion super-GOhm Subthreshold-MOS resistors for CMOS neural amplifiers," in *IEEE Biomedical Circuits and Systems Conference*, 2013.

- [20] Z. Kárász, R. Fiáth, P. Földesy and Á. R. Vázquez, "Tunable low noise amplifier implementation with low distortion pseudo-resistance for in vivo brain activity measurement," *IEEE Sensors Journal*, vol. 14, no. 5, pp. 1357-1363, May 2014.

- [21] X. Zou, X. Xu, L. Yao and Y. Lian, "A 1-V 450-nW fully integrated progammable biomedical sensor interface chip," *IEEE Journal of Solid-State Circuits*, vol. 44, no. 4, pp. 1067-1077, Apr. 2009.

- [22] H. Rezaee-Dehsorkh, N. Ravanshad, R. Lotfi, K. Mafinezhad and A. Sodagar, "Analysis and design of tunable amplifiers for implantable neural recording applications," *IEEE Journal on Emergin and Selected Topics in Circuits and Systems*, vol. 1, no. 4, pp. 546-556, Dec. 2011.

- [23] Y. Li, C. C. Poon and Y.-T. Zhang, "Analog integrated circuits design for processing physiological signals," *IEEE Reviews in Biomedical Engineering*, vol. 3, pp. 93-105, 2010.

- [24] A. Arnaud, R. Fiorelli and C. Galup-Montoro, "Nanowatt, sub-nS OTAs, with sub-10-mV input offset, using series-parallel current mirrors," *IEEE Journal of Solid-State Circuits*, vol. 41, no. 9, pp. 2009-2018, Sep. 2006.

- [25] P. R. Gray, P. J. Hurst, S. H. Lewis and R. G. Meyer, Analysis and Design of Analog Integrated circuits, 4th Edition, Wiley, 2001.

- [26] B. Razavi, Design of Analog CMOS Integrated Circuits, 2nd Edition, McGraw-Hill Education, 2017.

- [27] J. Silva-Martínez and A. Vázquez-González, "Impedance scalers for IC active filters," *Proc. IEEE International Symposium on Circuits and Systems*, vol. 1, pp. 151-154, 1998.

- [28] G. A. Rincon-Mora, "Active capacitor multiplier in miller-compensated circuits," *IEEE Journal of Solid-State Circuits*, vol. 35, no. 1, pp. 26-32, Jan. 2000.

- [29] J. Choi, J. Park, W. Kim, K. Lim and J. Laskar, "High multiplication factor capacitor multiplier for an on-chip PLL loop filter," *Electronics Letters*, vol. 45, no. 5, pp. 239-240, Feb. 2009.

- [30] E. Säckinger and W. Guggenbühl, "A versatile building block: The CMOS differential difference amplifier," *IEEE Journal of Solid-State Circuits*, vol. 22, no. 2, pp. 287-294, Apr. 1987.

- [31] J. Oreggioni, A. A. Caputi and F. Silveira, "Current-efficient preamplifier architecture for CMRR sensitive neural recording applications," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 12, no. 3, pp. 689-699, Jun. 2018.

- [32] P. Castro and F. Silveira, "High CMRR power efficient neural recording amplifier architecture," *Proc. IEEE International Symposium on Circuits and Systems*, pp. 1700-1703, May 2011.

## Appendices

1 clc2 clear 3 % close all 4 hold on 5 format shortEng 6 7 syms Gm1 Gmo Gmf gm8 gm6 Vi Vo Vf ZL Zf Igm1 8 9 eq\_Igm1 = Gm1\*Vi+(gm6+gm8)\*Vf; 10 11 eq\_1 = Igm1 == Vo/ZL + Vo\*Gmo; 12 13eq\_Vo = Vo == solve(eq\_1, Vo); 14 15 eq Vf = -Vo\*Gmf\*Zf ;16 17 eq\_Vo = Vo == solve(subs(eq\_Vo,Igm1,eq\_Igm1),Vo); 18 19eq\_Vo = solve(subs(eq\_Vo,Vf,eq\_Vf),Vo) 20 21 22 23 syms rof CL ro2 s Cf rgm 24 25 -ZL = ro2/(1+s\*CL\*ro2);26-Zf = rof/(1+s\*Cf\*rof);% Zf = (rof\*(1+s\*Cf\*rgm))/(1+s\*Cf\*(rof+rgm)); 27 28 29 % This equation is taken from the output of the Matlab command window 30 % (eq Vo) and removing the Vi term 31 a4 = expand((Gm1)/(((Gmf\*Zf\*(gm8 + gm6))/(Gmo + 1/ZL) + 1)\*(Gmo + 1/ZL)));32 33 disp('Vo/Vi = ') 34 pretty(collect(simplifyFraction(a4)));

```

35

36

% a4 = subs(a4,Cf,100e-9/(2*3.142));

37 -

a4 = subs(a4,Cf,100e-9);

38

% a4 = subs(a4,CL,10e-12/(2*3.142));

39-

a4 = subs(a4,CL,20e-12);

40 -

a4 = subs(a4, Gmo, 1.5e-6);

41 -

a4 = subs(a4, Gmf, 10e-9);

42

43

% a4 = subs(a4,rgm,10e6);

44 -

a4 = subs(a4,rof,100e12);

45 -

a4 = subs(a4,ro2,100e9);

46-

a4 = subs(a4, Gm1, 3.5e-3);

47 -

a4 = subs(a4, gm8, 2e-6);

48-

a4 = subs(a4, gm6, 2e-6);

49

50 -

[n4,d4] = numden(a4);%vo/vi

51

52 -

sys = tf(sym2poly(n4),sym2poly(d4));

53-

[z,p,k] = tf2zpk(sym2poly(n4),sym2poly(d4));

54

55 -

z = z/(2*pi)

56-

p = p/(2*pi)

57

58 -

opts = bodeoptions;

59-

opts.FreqUnits = 'Hz';

60 -

opts.Ylim = [-80 80];

61 -

w = logspace(-10, 11, 1e6);

62 -

bodemag(sys,w,opts);

63 -

grid on

```