#### AN ABSTRACT OF THE THESIS OF

<u>Cheng-Hsien Tsai</u> for the degree of <u>Master of Science</u> in <u>Electrical and Computer</u> <u>Engineering presented</u> on <u>August 10, 2021</u>.

Title: <u>5th-Order Elliptic LPF Using Passive Charge Compensation Technique (PCC)</u> <u>Design</u>

Abstract approved:

Gabor C. Temes

The passive charge compensation (PCC) technique was introduced for switched capacitor (SC) circuit to increase the slew rate and enhance the linearity performance, as PCC techniques are used on the Delta-Sigma modulator (DSM) in ADC circuitry. The PCC technique of the project was applied to the design of a SC filter to explore how PCC can relax the constraints in each of the stages. The filter designed in the study consisted of a conventional cascaded low-pass 5th order elliptic filter with bilinear, high-Q, low-Q sections and PCC switched cap branches, which were added at output of the first integrator of each section. When implemented in a TSMC 180nm CMOS process, this architecture showed a significant noise reduction of 12.3dB at the 3<sup>rd</sup> harmonic distortion and 13.1dB at the 5<sup>th</sup> harmonic distortion as compared to the conventional scheme. In additional, a rail-to-rail input and output operational amplifier was designed in a 180nm process with the complementary input pair and class-AB output stage.

©Copyright by Cheng-Hsien Tsai August 10, 2021 All Rights Reserved

### 5th-Order Elliptic LPF Using Passive Charge Compensation Technique (PCC) Design

by Cheng-Hsien Tsai

### A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Master of Science

Presented August 10, 2021 Commencement June 2022 Master of Science thesis of Cheng-Hsien Tsai presented on August 10, 2021.

APPROVED:

Major Professor, representing Electrical and Computer Engineering

Head of the School of Electrical Engineering and Computer Science

Dean of the Graduate School

I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my thesis to any reader upon request.

Cheng-Hsien Tsai, Author

#### ACKNOWLEDGEMENTS

It is an amazing journey to learn new knowledge and face any unknown challenges since I study at OSU. It would be impossible to complete this work without the helps and supports of my professors. I would like to express my heartfelt thanks to my advisor Professor Dr. Gabor Temes for providing me this great research opportunity under his guidance. Especially, Dr. Temes always gives pertinent comments on what I need to improve during our discussion on the progress of the research work. I could not have completed the MS degree without his guidance and support. I would also like to thank Prof. Alan Wang, Prof. Anne Trehu, and Prof. Matthew Johnston for being on committees for my final exam. I would also like to thank my colleagues and friends, Jyotindra, Manju, Jenny, Emanuel, Alex, Ray, Leo, Grace, and Wilson, for all their support during my MS study. I would like to truly thank my wife, Yi-Chun Chen, for fully supporting me in everything including raising two young kids, Ling-Rou and Cheng-Ning, at home and accompanying to the US. Finally, I do appreciate my parents for encouraging me to pursue my dream abroad.

## TABLE OF CONTENTS

| Page                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 Introduction 1                                                                                                                                            |

| 1.1. Overview1                                                                                                                                              |

| 1.2. Design Object2                                                                                                                                         |

| 1.3. Thesis Organization2                                                                                                                                   |

| 2 Filter Introduction                                                                                                                                       |

| 2.1. Background                                                                                                                                             |

| 2.2. Type of filters                                                                                                                                        |

| 2.3. Frequency Response                                                                                                                                     |

| 3 SC Circuit Introduction and Design Of a 5th-order Elliptic SC Filter7                                                                                     |

| 3.1 SC Circuits                                                                                                                                             |

| 3.1.1 Capacitors                                                                                                                                            |

| 3.2 Design of a 5 <sup>th</sup> Order SC Elliptic filter                                                                                                    |

| 3.2.1 Filter Specification       14         3.2.2 Pole and zero       16         3.2.3 Filter Design       17         3.2.4 Circuit implementation       20 |

| 3.3 PCC Technique                                                                                                                                           |

| 3.3.1 PCC Technique Design and Implementation                                                                                                               |

# TABLE OF CONTENTS (Continued)

|                              | <u>Page</u> |

|------------------------------|-------------|

| 3.3.2 Simulation Result      | 45          |

| 4 Conclusion and Future Work | 48          |

| Bibliography                 | 49          |

| Appendix I                   | 50          |

## LIST OF FIGURES

| Figure     Page                                                                                    |

|----------------------------------------------------------------------------------------------------|

| 2.1. Block diagram of a DSP system                                                                 |

| 2.2. Block diagram of a filter4                                                                    |

| 2.3. Four types of filters                                                                         |

| 2.4. Filter parameters                                                                             |

| 3.1. Capacitor for SC circuits                                                                     |

| 3.2. An SC resistor                                                                                |

| 3.3. Positive parasitic-insensitive SC resistor                                                    |

| 3.4. Negative parasitic-insensitive SC resistor10                                                  |

| 3.5. Non-ideal effects of MOS switches                                                             |

| 3.6. MOS switches                                                                                  |

| 3.7. A MOS switch with a dummy switch                                                              |

| 3.8. Bottom-plate sampling implementation in an SC integrator14                                    |

| 3.9. Z-domain pole and zero map                                                                    |

| 3.10. Z-domain frequency response                                                                  |

| 3.11. Frequency response of the elliptic filter, linear section, low-Q section, and High-Q section |

| 3.12. Frequency response of the elliptic filter with pass-band ripple                              |

| 3.13. The cascading structure of an elliptic filter21                                              |

| 3.14 A fully differential structure with even-order term cancellation filter22                     |

# LIST OF FIGURES (Continued)

| <u>Figure</u> <u>Page</u>                                                                          | 2 |

|----------------------------------------------------------------------------------------------------|---|

| 3.15. First linear stage                                                                           | 2 |

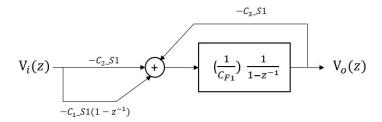

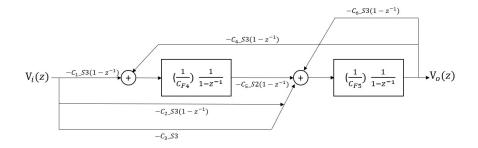

| 3.16. Signal-flow-graph of the linear section                                                      | 3 |

| 3.17. Second High- Q stage24                                                                       | 1 |

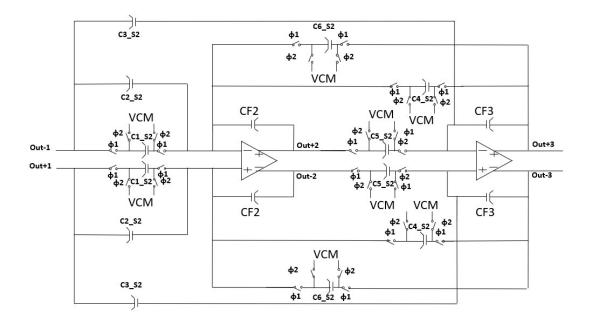

| 3.18. Signal-flow-graph of the High- Q section24                                                   | 1 |

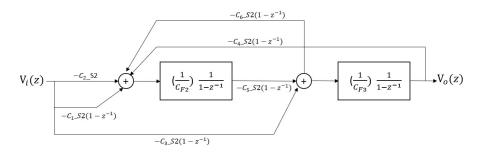

| 3.19. Third low- Q stage25                                                                         | 5 |

| 3.20. Signal-flow -graph of the low- Q section25                                                   | 5 |

| 3.21. Proposed charge injection canceling                                                          | 8 |

| 3.22. Schematic of the first stage real OPA                                                        | 0 |

| 3.23. Schematic of the second stage real OPA                                                       | l |

| 3.24. Schematic of the third stage real OPA                                                        | 2 |

| 3.25. Schematic of the fourth stage real OPA                                                       | 3 |

| 3.26. Schematic of the fifth stage real OPA                                                        | 4 |

| 3.27. Frequency response of the linear section between the ideal and transistor levels. transistor |   |

| 3.28. Frequency response of the high-Q section between the ideal and transistor level              | 5 |

| 3.29. Frequency response of the low-Q section between the ideal and transistor levels              | 6 |

| 3.30. Frequency response of the LPF between the ideal and transistor levels                        | 6 |

| 3.31. A charge-compensated integrator                                                              | 3 |

| 3.32. Linear section with a PCC path                                                               | ) |

| 3.33. Linear section with a PCC path during the $\Phi$ 2 phase operation                           | 9 |

# LIST OF FIGURES (Continued)

| Figure                                                                   | Page |

|--------------------------------------------------------------------------|------|

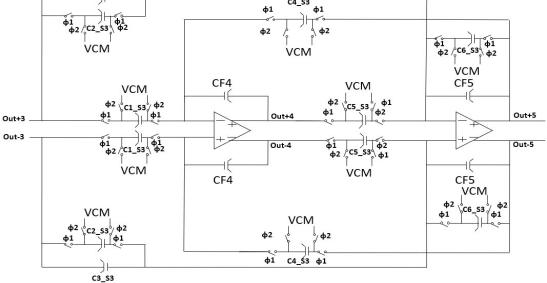

| 3.34. High-Q section with a PCC path                                     | 40   |

| 3.35. High-Q section with a PCC path during the $\Phi$ 2 phase operation | 40   |

| 3.36. Low-Q section with a PCC path                                      | 41   |

| 3.37. Low-Q section with a PCC path during the $\Phi 2$ phase operation  | 42   |

| 3.38. Complete LPF circuit with the proposed PCC technique               | 44   |

| 3.39. Distortions in the conventional LPF                                | 45   |

| 3.40. LPF transient time responses of the ideal and transistor levels    | 46   |

# LIST OF TABLES

| <u>Table</u> | Page                                                         |

|--------------|--------------------------------------------------------------|

| I.           | 5th order elliptic filter specification 15                   |

| II.          | Filter order calculation                                     |

| III.         | Poles and zeros in the s- and Z-domains 17                   |

| IV.          | First stage capacitances                                     |

| V.           | Second stage capacitances                                    |

| VI.          | Third stage capacitances                                     |

| VII.         | Specification of the first transistor                        |

| VIII.        | Sizes of the first transistor and biasing circuit            |

| IX.          | Specification of the second transistor                       |

| Х.           | Sizes of the second transistor and biasing circuit           |

| XI.          | Specification of the third transistor                        |

| XII.         | Sizes of the third transistor and biasing circuit            |

| XIII.        | Specification of the fourth transistor                       |

| XIV.         | Sizes of the fourth transistor and biasing circuit           |

| XV.          | Specification of the fifth transistor                        |

| XVI.         | Sizes of the fifth transistor and biasing circuit            |

| XVII.        | Specification for the LPF                                    |

| XVIII.       | Simulation results for the macro-module and transistor level |

# LIST OF TABLES (Continued)

| XIX. | Simulation results of dynamic power at the transistor level circuit47 |

|------|-----------------------------------------------------------------------|

| XX.  | Simulation results of the dynamic power comparison47                  |

## LIST OF APPENDICES

| Appendix       | Page |

|----------------|------|

| A. MATLAB code | 50   |

### **Chapter 1: Introduction**

#### 1.1. Overview

In recent years, the development of the transceiver system in wireless communication and biomedical equipment has motivated many design challenges, specifically in lowvoltage and high-performance integrated circuits.

Filter design is one of the most important topics in signal processing. Many techniques are available to design analog as well as digital filters. Many researchers engaged in analog filter design focus on innovative circuit designs with better performance and methods, or on developing more reliable, efficient, and convenient design algorithms. Moreover, in analog and mixed analog-digital circuits, the circuit technique used most often for analog signal processing is based on switched-capacitor (SC) stages for two main reasons. First, chip area is minimized by replacing the resistors with capacitors. Another reason is that in the proper clock operations, the performance of SC circuits is generally comparable to that of conventional RC circuits. In additional, SC circuits fan out at the different bandwidths performing tunable and flexible frequency response when their clock frequency modifies also tunable SC circuits. Thus, SC circuits are used in a wide range of applications, such as analog filters, feedback amplifiers, analog-to-digital converters, and DC-DC regulators. SC circuits mainly consist of MOS switches, OTAs, and capacitors. Hence, they should consume less power, should exhibit small die-area, and must not limit the overall performance of the system.

#### **1.2.** Design Objective

The linearity, power, and area efficiencies of a filter design are critical for wireless applications with low hardware complexity and cost. Some approaches for linearity enhancement have been introduced in SC circuits, [1,2]. Both the approaches use an active operational transconductance amplifier (OTA) to implement linearity improvement In this project, we not only used presenting the passive charge compensation (PCC) technique [3] that can improve the linearity performance of a filter with less power consumption as compared to a conventional filter without a CCT circuit, but also extended the application of the PCC technique during this evaluation.

### **1.3.** Thesis Organization

There are five chapters in this thesis. Chapter 1 mentions the background of this thesis and thesis organization. Chapter 2 introduces the fundamental theory and operation of filters. Chapter 3 describes the fundamental theory and operation of the SC circuit, how important the linearity is, and the concepts and PCC technique used in this thesis. In this chapter, the equations for low-pass filters and circuit implementation of SC filters have been derived. The implementation of such filters involved a fully differential, high bandwidth, and conventional common-mode feedback circuit (CMFB). It also discusses the simulation results demonstrating the potential of the PCC techniques for application in analog filters. Chapter 4 concludes this thesis and discusses the perspectives of the future studies on improving the linearity of SC analog filters.

#### **Chapter 2: Filter Introduction**

In this chapter, the fundamental concepts in the design of filters, and the frequency response of filters are discussed. Filters are classified according to the functions they perform. As our filters were designed for low frequency (LF) applications, we have focused on low-pass filters (LPFs) in this thesis.

#### 2.1 Background

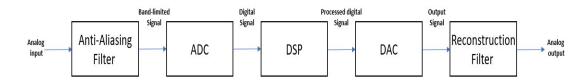

Filters are used in a wide range of applications such as data conversion, signal processing, and phase-locked loops, owing to their accurate frequency response, linearity, and dynamic range. Figure 2.1 shows the block diagram of a DSP system, filters that locate the front-end of ADC or the back-end of DAC allow the transmission of the desired electric signals within a certain frequency range and cancel out the transmission of the unwanted electric signals outside this range.

Figure 2.1. Block diagram of a DSP system.

A filter is an electrical network that alters the amplitude and/or phase characteristics of a signal with respect to frequency. The frequency-domain behavior of a filter is described mathematically in terms of its transfer function or network function. This is the ratio of the Laplace transforms of its output and input signals. The voltage transfer function H(s) of the filter shown in Figure 2.2 can be written as follows.

$$H(s) = \frac{V_{out}(s)}{V_{in}(s)}$$

(2.1)

Figure 2.2. Block diagram of a filter.

where  $V_{out}(s)$  and  $V_{in}(s)$  are the output and input signal voltages, respectively, and s is the complex frequency variable [4].

#### 2.2 Type of Filters

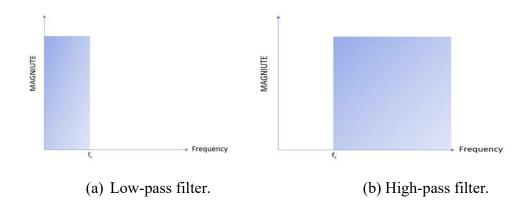

Depending on the characteristics of the filter's frequency response, filters can be classified into four types, namely, generally such as low-pass filter, high-pass filter, band-reject filters, etc. . Those are shown in Figure 2.3.

Figure 2.3 (A) shows an ideal low-pass filter. It allows the transmission of the desired electric signals at a frequency lower than the cut-off frequency,  $f_c$ . An ideal high-pass filter allows the transmission of the desired electric signals at a frequency higher than the cut-off frequency,  $f_c$  (Figure 2.3 (B)). Bandpass filters (Figure 2.3 (C)) pass only the frequencies below  $f_l$  and above  $f_h$ , and bandstop filters block only the frequencies below  $f_l$  and above  $f_h$  (Figure 2.3 (D)).

Figure 2.3. Four Types of Filters.

### 2.3 Frequency Response

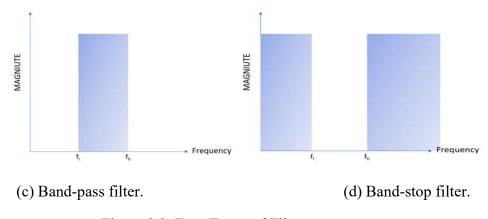

In the filter design process, first the filter type was selected. Then, the responses of the filters to the individual frequency components that constituted the input signal were defined. In practice, an LPF shows the following responses to different frequencies: pass-band, transition-band, or stop-band, as shown in Figure 2.4.

Figure 2.4. Filter parameters.

The pass-band response of a filter is its effect on the frequency components that are passed through unchanged. The frequencies within the stop-band of a filter are sharply attenuated. The transition-band represents the intermediate frequencies, which may receive some attenuation, but are not removed completely from the output signal. In practice, the magnitude may not be a constant in the passband of a filter with a small amount of ripple in the pass band known as the "passband ripple". Similarly, the filter response does not reduce to zero with a small, non-zero value in the stopband which is known as the "stop-band ripple". These ripples are shown in Figure 2.4.

The ripple in the pass-band of a filter is denoted as  $\delta_p$ , and its magnitude varies from 1-  $\delta_p$  to 1+  $\delta_p$ .  $\delta_s$  is the ripple in the stop-band [5].

### Chapter 3: SC Circuit Introduction and Design Of a 5<sup>th</sup>-order Elliptic SC Filter

In this chapter, the fundamental concepts of filter design, and the frequency response of filters are discussed. Filters are classified according to the functions they perform. As our filters were designed for LF applications, we will focus on LPFs in this chapter.

#### 3.1 SC Circuits

SC circuits can sample data efficiently and accurately and simulate continuous-time functions as a discrete-time signal processor. An SC circuit is realized with some basic function blocks including capacitors, switches, non-overlapping clocks, and OTAs. These blocks are discussed in this section.

#### 3.1.1 Capacitors

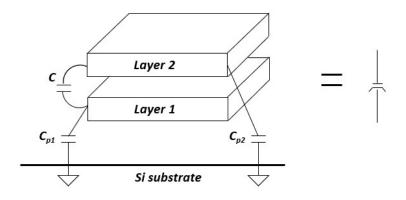

A highly linear capacitance in an integrated circuit is constructed by two silicon areas (double poly capacitors), as shown in Figure 3.1(a). The desired capacitor is formed by the intersection of the two silicon layers. By growing a thin oxide between two conductive layers, it usually is accompanied by a 20% bottom plate parasitic

capacitor, as shown in Figure 3.1(b)[6].

(a) Physical construction.

(b) Equivalent circuit.

Figure 3.1. Capacitor for SC circuits.

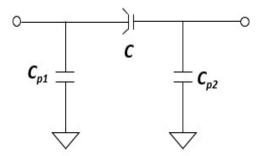

### 3.1.2 SC circuit

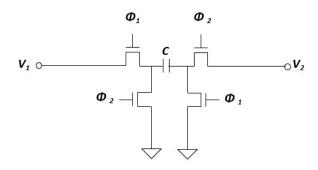

Consider the SC circuit shown in Figure 3.2. Assuming  $\phi_1$  and  $\phi_2$  are two nonoverlapping clocks. C is charged to V<sub>1</sub> and then V<sub>2</sub> during each clock period. Therefore, the change in charge over one clock period is given by

$$\Delta Q = C(V_1 - V_2) \,. \tag{3.1}$$

Then, we can also determine the equivalent average current over one clock period as follows.

$$I_{eq} = \frac{C(V_1 - V_2)}{T},$$

(3.2)

where T is the clock period. The equivalent resistor of the SC shown in Figure 3.14 over one clock period can be expressed as follows.

$$R_{eq} = \frac{V_1 - V_2}{I_{eq}} = \frac{T}{c} = \frac{1}{C * f_s},$$

(3.3)

where fs is the sampling frequency.

Figure 3.2. An SC resistor.

In Figure 3.2, we ignored the effect of the parasitic capacitors. Here,  $C_p$  represents the parasitic capacitor of the top plate of C as well as the non-linear capacitors associated with the two switches. It is in parallel with C, and therefore cause gain error of the circuit transfer function. To overcome this drawback, parasitic-insensitive structures have been developed to realize high accuracy. Figure 3.3 shows a parasitic-insensitive resistor equivalence of a positive SC. Figure 3.4 shows the same for a negative one [6].

Figure 3.3. Positive parasitic-insensitive SC resistor.

Figure 3.4. Negative parasitic-insensitive SC resistor.

#### 3.1.3 Switches

The switches used in SC filters must have a very high "off" resistance, a relatively low "on" resistance, and no offset voltage when it turns on. In the present-day CMOS technology, MOSFETs are used as switches to meet these requirements.

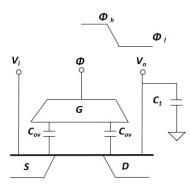

The non-ideal effects of MOS switches are the major limitation for the resolution of SC circuits. They cause errors by injecting unwanted charges into the circuit when the switches turn "off". There are two types of non-ideal effects, namely charge injection and clock feedthrough.

A. Channel Charge Injection[6]

A simple sampling circuit is shown in Figure 3.5. The channel charge is given by

$$Q_{CH} = WLC_{ox}(V_{DD} - V_{in} - V_{TH})$$

(3.4)

Figure 3.5. Non-ideal effects of MOS switches.

When the transistor turns off, this charge moves to the source and drain, which is called channel charge injection. The charge moving to the input is absorbed by the input source but the output is affected by the remaining channel charge deposited on to the capacitor. The output voltage deviation due to channel charge is

$$\Delta V = \frac{WLC_{ox}(V_{DD} - V_{in} - V_{TH})}{2C_l} \tag{3.5}$$

Assuming that the total channel charge moves on to the sampling capacitor, then the output voltage is given by

$$V_{out} \approx V_{in} - \frac{WLC_{ox}(V_{DD} - V_{in} - V_{TH})}{c_l}$$

(3.6)

and ignoring the phase shift between the input and output, the output is given by

$$V_{out} = V_{in} \left( 1 + \frac{WLC_{ox}}{C_l} \right) - \frac{WLC_{ox}(V_{DD} - V_{TH})}{C_l}$$

(3.7)

B. Clock Feedthrough

As can be observed from Figure 3.5, the overlap capacitors between the gate and junctions inject additional charge into the circuit when the switches turn "off". This effect is called clock feedthrough. The voltage error due to the clock feedthrough is given by

$$\Delta V = -(\phi_h - \phi_l) \frac{c_{ox}}{c_l + c_{ox}}$$

(3.8)

where  $\phi_h$  is V<sub>DD</sub> and  $\phi_l$  is ground.

According to equations (3.6) and (3.7), the error caused by clock feedthrough is small and signal-independent, which can be eliminated by employing a fully-differential structure. On the other hand, the error caused by charge injection is much larger. We can also divide charge injection into two parts, signal-dependent and signal-independent. Switches connected to the analog ground and virtual ground cause the signal-independent error because their turn-on voltage is constant. Just like the error caused by clock feedthrough, these errors can be eliminated by employing a fully-differential structure. Moreover, switches connected to the signal cause the signal-dependent error, which changes with the signal. This error is important because it significantly affects the resolution of the circuit. Therefore, the reduction in this error is a critical issue in SC circuits. These approaches are discussed in the following sections.

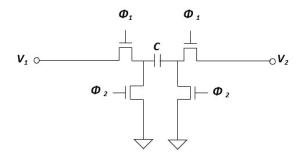

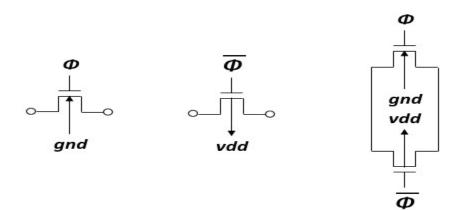

1. CMOS Switch

MOS switches includes NMOS, PMOS, and CMOS switches, as shown as Figure 3.6. NMOS switches are applicable in low-voltage ranges, and PMOS switches are applicable at high voltages. However, CMOS switches combine the advantages of both the NMOS and PMOS switches and work at all voltages.

Figure 3.6. MOS switches.

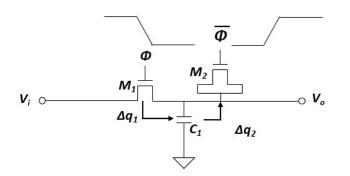

2. Dummy Switch

Figure 3.7 shows a dummy switch (M2) driven by inverse clock added to the circuit. Therefore, the charge injected by the main switch (M1) can be removed to M2 after M1 turns "off" and M2 turns "on". Note that both the source and drain of M2 are connected to the output node and the size of M2 is half of that of M1 so that  $\Delta_{q1} = -\Delta_{q2}$ .

Figure 3.7. A MOS switch with a dummy switch.

3. Bottom-plate sampling method

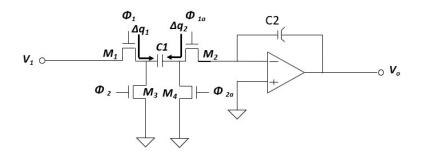

As shown in Figure 3.8, we added a pair of clocks ( $\varphi_{1a}$ , $\varphi_{2a}$ ) that were slightly advance as compared to the original clocks ( $\varphi_1$ , $\varphi_2$ ) in an SC integrator. When M1 turns "off", the injected charge 1  $\Delta q$  does not cause any change in the charge stored in Cl as M2 has already turned "off" and the right side of C1 is connected to an effective open circuit. Therefore, by this approach, the circuit is affected only by M2 and M4, which are connected to the virtual ground or analog ground. The charges injected by these transistors are signal-independent and are cancelled by the fullydifferential structure.

Figure 3.8. Bottom-plate sampling implementation in an SC integrator. The size of MOS switches is discussed in the following section.

## 3.2 Design of a 5<sup>th</sup> Order Elliptic Low Pass SC Filter

To design the low-pass switch capacitor filter, we calculated the transfer function and the capacitance of the filter using Matlab. Then the non-idealities of the operational amplifier (OPA) and sampling switches were simulated in Cadence. To reduce the effect of the chip area on the idealities of the OPA, dynamic range and impedance scaling were conducted. Finally, a folded cascade full differential OPA and transmission gate switches were designed to implement the filter.

#### 3.2.1 Filter Specification

Table I lists the filter specifications, which we aimed to design in this study. Switch capacitor filter is discrete time; and therefore it is was necessary to transfer the design parameters accordingly to discrete time domain specifications.

| Parameter              | Value      |

|------------------------|------------|

| Sampling Frequency     | 600KHz     |

| DC Gain                | 0 dB       |

| Passband               | 0-36 KHz   |

| Ripple in passband     | 0.229dB    |

| Stopband               | 72-240 KHz |

| Gain in Stopband       | - 51dB     |

| Minimum Capacitor size | 100 fF     |

| Total Capacitance      | 4560.5fF   |

Table I. 5<sup>th</sup> order Elliptic Filter Specification.

The design was implemented considering the addition of some margin on the filter. The pass-band ripple was set at 0.25 dB. The stop-band gain was selected to be -50 dB. Table II lists the orders of different types of filters. The elliptic filter requires the minimum filter order. Therefore, the LPF used in this study was designed using the elliptic filter structure.

Table II. Filter order calculation.

| Filter      | Filter Orde |  |

|-------------|-------------|--|

| Butterworth | 11          |  |

| Chebyshev   | 7           |  |

| Elliptic    | 5           |  |

#### 3.2.2 Pole and Zero

The Bilinear transform is used to design a sampled-data filter from the analog counterpart. The relationship for the transformation of the s domain to the z domain is as follows.

$$S = \frac{2}{T} \frac{z-1}{z+1}$$

(3.9)

where T is the sampling period. As

$$S = j\Omega \tag{3.0}$$

$$z = e^{j\omega} \tag{3.11}$$

$\Omega$  and  $\omega$  can be related as

$$\Omega = \frac{2}{T} \tan\left(\frac{\omega}{2}\right) \tag{3.12}$$

The transfer function, poles, and zeros can be calculated by using the MATLAB elliptic low pass filter design. This function can directly return the value in the z-domain. After getting the pole and zero result in the z-domain, equation (3.9) is used to change the poles and zeros from the z-domain to the s-domain in order to calculate the Q value of the  $2^{nd}$  order transfer function.

The quality factors (Q) of the s-domain poles are 6.748 and 0.674, respectively, to the two complex poles shown in Table III. The poles and zeros close to each other formed the biquadratic section. These poles and zeros could be obtained through the MATLAB transcript given in appendix I. The corresponding transfer function calculated by Matlab is

$$H(z) = \frac{0.0039z^5 - 0.071z^4 + 0.0044^{-3} + 0.0044z^2 - 0.0071z + 0.0039}{z^5 - 4.2348z^4 + 7.3648z^3 - 6.553^{-2} + 2.9783z - 0.5524}$$

(3.13)

The single-ended version of each of the three filter blocks is delivered in [6] and [8], along with derivations for all of the capacitor values.

| Poles & Zeros | Z-Domain       | S-Domain          | Q-factor           |

|---------------|----------------|-------------------|--------------------|

| P1, P2        | 0.884 ± 0.37i  | 0.543 ± 4.922i    | 0.674              |

| P3, P4        | 0.831 ± 0.238i | -2.968 ±5.59i     | 6.748              |

| P5            | 0.805          | 9.25641           | 0.70               |

| Z1, Z2        | 0.804 ± 0.595i | -0.000952 ± 3.03i | ( 1944)<br>( 1944) |

| Z3, Z4        | 0.595 ± 0.803i | -0.00218 ±1.984i  | 0-0                |

| Z5            | -1             | α                 | 1.42               |

Table III. Poles and zeros in the s- and Z-domains.

#### 3.2.3 Filter Design

The 5<sup>th</sup> order transfer function was designed as a cascade of a linear section and two second order sections. The poles and zeros were used to form biquadratic sections, a bilinear section, a high-quality (high-Q) factor section, and a low-quality (low-Q) factor section as follows.

a. Bilinear section

$$H_{Lear} = \frac{0.003943(z+1)}{z-0.805} \tag{3.14}$$

b. High-Q section, Q = 6.748

$$H_{High-} = \frac{z^2 - 1.0607z}{z^2 - 1.768z + 0.9184}$$

(3.15)

c. Low-Q section, Q = 0.674

$$H_{Low-} = \frac{z^2 - 1.193z +}{z^2 - 1.662z + .7472}$$

(3.16)

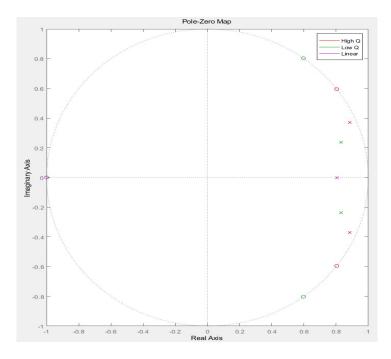

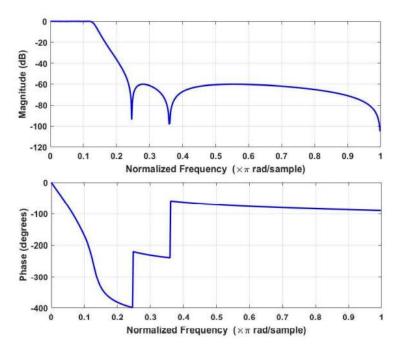

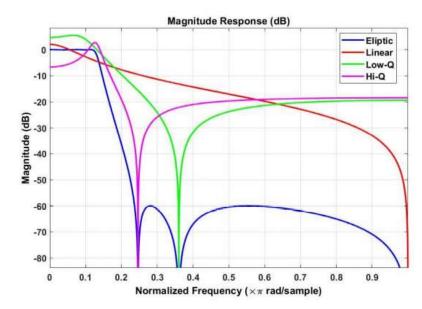

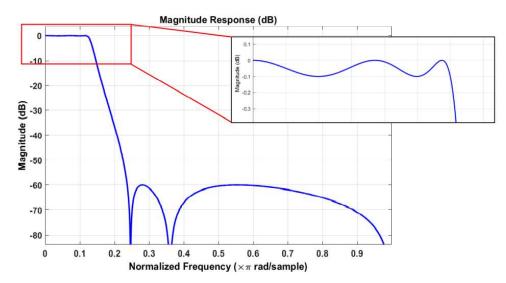

The pole location, zero location, and frequency response plots are shown in Figures 3.9, 3.10, and 3.11, respectively.

Figure 3.9. Z-domain pole and zero map.

Figure 3.10. Z-domain frequency response.

Figure 3.11. Frequency response of the elliptic filter, linear section, low-Q section, and High-Q section.

The frequency response of the elliptic filter with ripple plot, as obtained using MATLAB, is shown in Figure 3.12.

Figure 3.12. Frequency response of the elliptic filter with pass-band ripple.

#### 3.2.4 Circuit implementation

#### 1. Dynamic and chip area scaling

Dynamic range scaling is performed to optimize the output swing of each node of a filter. This can be done by measuring the output voltage of the amplifier in each stage.

Then by scaling the area of the capacitors, which occupy larger area than the other components, we built out the core die on a chip. Reducing the chip area is one of the most important considerations in circuit design. Therefore, chip area scaling is implemented in the design. This technique not only reduces the on-chip area, impedance level scaling, and chip area scaling, but also minimizes the noise. Chip area scaling is carried out by using the smallest capacitance connected to the input node of the OTA and setting it to the minimum allowable capacitance. In addition, all the other capacitances connected to the input node (for that stage) are scaled according to the ratio of the scaled factor for the smallest capacitance. Then, this procedure is repeated for all the stages, including the bilinear, high-Q, and low-Q. The output response does not change after implementing the chip area scaling. As we noticed, it multiplies all the capacitances by a scaling factor to the entire stage instead of only multiplying to the input node-connected capacitances, which do not affect the overall transfer function. Thus, the overall chip area is minimized.

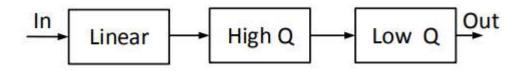

#### 2. Filter Cascade

The order of a filter is implemented to achieve high performance. The linear section is placed at the input in order to reject high-frequency noise. The high-Q section is placed in the middle to reduce the sensitivity and power supply rejection ratio. The low-Q section is placed at the end. The filter cascading structure is shown in Figure 3.13.

Figure 3.13. The cascading structure of an elliptic filter.

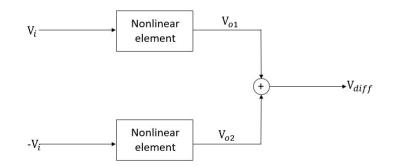

#### 3. Fully differential structure

In most of the analog applications, it is desirable to keep signals in the differential mode. Fully-differential signals imply that the difference between two lines represents the signal component. Thus, any noise that appears as a common-mode signal on those two lines does not affect the signal. Fully differential circuits should also be balanced, implying that the differential signals operate symmetrically around a DC common-mode voltage, which is called the analog ground. Fully differential circuits have another advantage that if each single-ended signal is distorted symmetrically around the common-mode voltage, the differential signal will have only odd-order distortion terms. These terms are often much smaller than the single-ended structure. Consider the block diagram shown in Figure 3.15, if two non-linear elements are identical then each of the outputs can be determined as a Taylor series expansion given by

$$V_i = k_1 V_i + k_2 V_i^2 + k_3 V_i^3 + \cdots$$

(3.17)

$$-V_i = -k_1 V_i + k_2 V_i^2 - k_3 V_i^3 + \cdots$$

(3.18)

where  $k_i$  are the constant terms. In this case, the differential output signal,  $V_{diff}$ , consists of only the odd-order terms,

$$V_{diff} = 2k_1 V_i + 2k_3 V_i^3 + 2k_5 V_i^5 + \cdots$$

(3.19)

With these two important advantages, most of the modern switched-capacitor circuits are realized using fully differential structures.

Figure 3.14. A fully differential structure with even-order term cancellation.

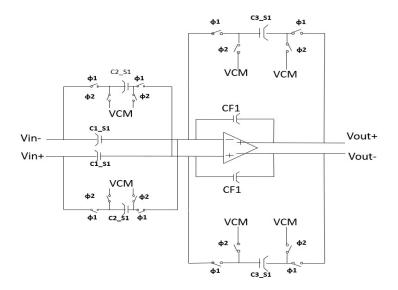

#### 4. Linear section

The schematic of a linear section is shown in Figure. 3.15. The signal-flow-graph is shown in Figure. 3.16, and the corresponding values of the capacitors are listed in Table IV. The transfer function of the linear section is given by equation (3.20), which can be derived from its signal-flow-graph. The capacitor calculation is performed using equation (3.14) to determine  $C_{1_S1}$ ,  $C_{2_S2}$ , and  $C_{3_S1}$ , when simplifying the calculation,  $C_A$  is set to 100fF.

$$H(z)_{Lear} = \frac{V_o(z)}{V_i(z)} = -\frac{\frac{C_{1\_S1}}{C_{F1}}(1-z^{-1}) + \frac{C_{2\_S1}}{C_{F1}}}{1-z^{-1} + \left(\frac{C_{3\_S1}}{C_{F1}}\right)} = -\frac{\left(\frac{C_{1\_S1} + C_{2\_S1}}{C_{F1}}\right)z - \frac{C_{1\_S1}}{C_{F1}}}{\left(1 + \frac{C_{3\_S1}}{C_{F1}}\right)z - 1}$$

(3.20)

Figure 3.15. First linear stage.

Figure. 3.16 Signal-flow-graph of the linear section.

|       | Bilinear Sect | Bilinear Section Caps value table |  |  |  |  |

|-------|---------------|-----------------------------------|--|--|--|--|

| 1     | DR Unit (fF)  | Area (fF)                         |  |  |  |  |

| CF1   | 825           | 825                               |  |  |  |  |

| C1_S1 | 100           | 100 (Unit Cap)                    |  |  |  |  |

| C2_S1 | 200           | 200                               |  |  |  |  |

| C3_S1 | 200           | 200                               |  |  |  |  |

Table IV First Stage capacitances.

## 5. High-Q section

The high-Q section, which has a pole quality factor of 6.748, is placed at the middle. The schematic of the high-Q section and the capacitances in the second stage (Table V are shown in Figure 3.17. The signal-flow-graph is shown in Figure. 3.18. The quality factor of each filter is determined from the pole frequency as follows.

$$Q = \frac{|\omega_p|}{2Re(\omega_p)} \tag{3.21}$$

The transfer function of the linear section is expressed as (3.21), which can be derived from its signal-flow-graph and equation (3.15).

$$H(z)_{High-} = \frac{V_o(z)}{V_i(z)}$$

$$= -\frac{(C_{3\_S2})z^2 + (C_{1\_S2}C_{5\_S2} + C_{2\_S2}C_{5\_S2} - 2C_{3\_S2})z + (C_{3\_S2} - C_{2\_S2}C_{5\_S2})}{z^2 + (C_{4\_S2}C_{5\_S2} + C_{6\_S2}C_{5\_S2} - 2)z + (1 - C_{6\_S2}C_{5\_S2})}$$

(3.22)

Figure. 3.17 Second high-Q stage.

Figure 3.18. Signal-flow graph of the high-Q section.

|       | High-Q Secti | ion Caps value table |

|-------|--------------|----------------------|

|       | DR Unit (fF) | Area (fF)            |

| C6_S2 | 103          | 100 (Unit Cap)       |

| CF2   | 463          | 348                  |

| CF3   | 374          | 363                  |

| C1_S2 | 133          | 100 (Unit Cap)       |

| C2_S2 | 0            | 0                    |

| C3_S2 | 100          | 97                   |

| C4_S2 | 184.5        | 179                  |

| C5_S2 | 141          | 106                  |

| C6_S2 | 103          | 100 (Unit Cap)       |

|       |              |                      |

Table V. Capacitance of the second stage.

## 6. Low-Q section

The low-Q section, which has a pole quality factor of 0.67, is placed at the end. The schematic of the low-Q section and the capacitances in the third stage (Table VI) are shown in Figure 3.19. The signal-flow-graph is shown in Figure 3.20.

The transfer function of the linear section is expressed as (3.23), which can be derived from its signal-flow graph and equation (3.16).

$$H(z)_{Low-Q} = \frac{V_0(z)}{V_i(z)}$$

$$= -\frac{(C_{2\_S3} + C_{3\_S3})z^2 + (C_{1\_S3}C_{5\_S3} - C_{2\_S3} - 2C_{3\_S3})z + (C_{3\_S3})}{(1 + C_{6\_S3})z^2 + (C_{4\_S3}C_{5\_S3} - C_{6\_S3} - 2)z + 1}$$

(3.23)

Figure 3.19. Third low-Q stage.

Figure 3.20. Signal-flow graph of the low-Q section.

|       | Low-Q Section | on Caps value table |

|-------|---------------|---------------------|

|       | DR Unit (fF)  | Area (fF)           |

| CF4   | 530.5         | 530                 |

| C1_S3 | 141.7         | 141                 |

| C2_S3 | 0             | 0                   |

| C3_S3 | 100           | 100 (Unit Cap)      |

| C4_S3 | 100           | 100 (Unit Cap)      |

| CF5   | 500           | 500                 |

| C5_S3 | 302.5         | 302                 |

| C6 S3 | 169           | 169                 |

Table VI. Third stage capacitances.

#### 7. Switches Sizing [8]

Clock feedthrough and charge injection cause setup error voltage in sampling signals. And the nonlinearity of switches introduces harmonics to the sampling signals. At the beginning, we took biquad filters as two first-order systems with a single delay around the loop because of the negative SC resistor. In addition, the output error of an ideal first-order system is given by the following equation.

$$V_e(t) = e^{-\frac{t_s}{\tau}} \tag{3.24}$$

where  $\tau$  is the RC time constant of the first-order system and t<sub>s</sub> is the settling time of the first-order system. Assuming the circuit has a resolution of N bits, then (3.16) can be rewritten as

$$e^{-\frac{t_s}{\tau}} \le \frac{1}{2^{N+1}} \tag{3.25}$$

If we set the capacitance loading to 2 pF, the settling time as the half of the clock period, and the resolution as 8 bits, then the turn-on resistance limitation is given by

$$R_{on} \le \frac{t_s}{(N+1)\ln(2)C_l} \approx 0.13 \ k\Omega \tag{3.26}$$

From equation (3.25), we can determine the size of the NMOS switches. As for the CMOS switches, we still have to consider the ratio of the sizes of the NMOS and PMOS switches.

First of all, we recall that the equation of transistor current vs. voltage in the triode region is given by

$$I_{d} = \mu C_{ox} \left(\frac{W}{L}\right) \left[ \left( V_{gs} - V_{th} \right) V_{ds} - \frac{1}{2} V_{ds}^{2} \right]$$

(3.27)

Then turn-on resistance of MOS switches is given by

$$R_{on} = \left(\frac{\partial I_d}{\partial V_{ds}}\right)^{-1} = \frac{1}{\mu C_{ox} \left(\frac{W}{L}\right) (V_{DD} - V_{in} - V_{TH})}$$

(3.28)

According to (3.19) the size of the switch transistor is

$$\frac{W}{L} = \frac{1}{\mu C_{ox} \left(\frac{W}{L}\right) (V_{DD} - V_{in} - V_{TH}) R_{on}} \approx 3$$

(3.29)

Assuming the length of the channel to be minimum i.e.,  $L = 0.18 \mu m$ , then  $W = 0.54 \mu m$ . Generally, the mobility of a PMOS switch is the one-third of that of an NMOS switch. Thus, the size of a PMOS switch should be three times larger that of an NMOS switch to provide equivalent resistance.

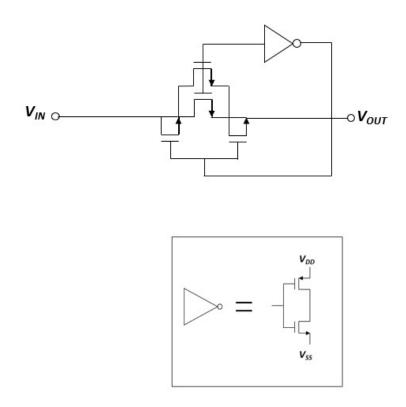

Figure 3.21 shows the switch used in our LPF. It consisted of four NMOS transistors with the W/L ratio of 0.54/0.18, and a CMOS inverter was used for providing an opposite phase clock to the dummy switches.

Figure 3.21. Proposed charge injection canceling switch.

$$\Delta V = -\frac{Q_{ch}}{2(C_l + C_{ov})} \approx -\frac{WLC_{ox}(V_{gs} - V_{th})}{2C_l}$$

(3.30)

#### 7. Design of OTA

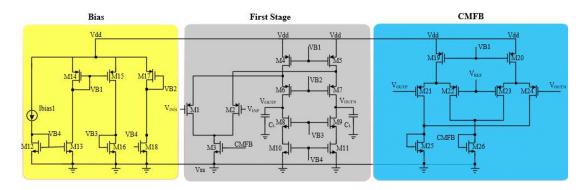

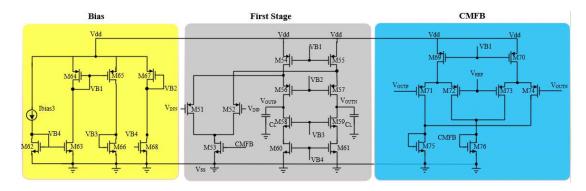

The TSMC 180nm CMOS technology was used to design the OTAs. The OTAs designed in this study are shown in Figures 3.22–3.26. The folded cascade structure was used, the minimum length of the transistors in the output path was set to 1  $\mu$ m to achieve a gain of 60 dB. The CMFB was utilized to provide an output DC operation point for the OPA, and the trans-conductance of the CMFB circuit was about the half of the input trans-conductance that could provide enough common-mode bandwidth. The size of the transistors, the bias circuit, and specification are listed in Tables VII – Table XV. The frequency response of the first stage OTA is summarized in Table VII, the DC gain was approximately 54.15 dB, the bandwidth was 6.2 MHz, and the phase margin of the OTA was 92.35°. The frequency response of the filter at each stage and the overall frequency response of the filter with the real OTA are summarized in Tables VII–XV. The pass-band ripple was approximately 0.229 dB

and the stop-band attenuation was -51dB. When the amplitude of the input sine signal was 2 Vpp and the frequency was 30 kHz, the output waveform of the filter and the FFT results are shown in Figures. 3.27–3.30. Sampling caused glitches in the output signal. The 3<sup>rd</sup> harmonic was -110.25 dB and the 5<sup>th</sup> harmonic was -124.42 dB.

Figure 3.22. Schematic of the first stage real OPA.

|              | 1st Order OPA - Folded cascode opamp |

|--------------|--------------------------------------|

|              | Pre-sim                              |

| loading (pF) | 2                                    |

| DC Gain (dB) | 54.15                                |

| Ft(KHz)      | 11.18                                |

| PM (degree)  | 92.35                                |

| SR+(us/sec)  | 2.15                                 |

| SR-(us/sec)  | 1.60                                 |

| CM(vol)      | 0.9                                  |

| CMRR (dB)    | 87.7                                 |

| power (uW)   | 225.128                              |

| UBM (MHz)    | 6.2                                  |

|              |                                      |

Table VII. Specification Of First transistor.

| Table VIII. Size Of First tran | sistor and | biasing | circuit. |

|--------------------------------|------------|---------|----------|

|--------------------------------|------------|---------|----------|

|            |          |        | Folded Ca  | scade OPA  |          |        |           |

|------------|----------|--------|------------|------------|----------|--------|-----------|

| Transistor | W/L (um) | Finger | Multiplier | Transistor | W/L (um) | Finger | Multiplie |

| M1         | 400/300  | 2      | 1          | M7         | 600/400  | 6      | 1         |

| M2         | 400/300  | 2      | 1          | M8         | 400/300  | 2      | 1         |

| M3         | 400/300  | 10     | 1          | M9         | 400/300  | 2      | 1         |

| M4         | 600/400  | 17     | 2          | M10        | 400/300  | 2      | 1         |

| M5         | 600/400  | 17     | 2          | M11        | 400/300  | 2      | 1         |

| M6         | 600/400  | 6      | 1          |            |          |        |           |

|            | Biasing Circuit |        |            |            |          |        |            |  |  |

|------------|-----------------|--------|------------|------------|----------|--------|------------|--|--|

| Transistor | W/L (um)        | Finger | Multiplier | Transistor | W/L (um) | Finger | Multiplier |  |  |

| M12        | 400/300         | 4      | 1          | M16        | 400/300  | 1      | 1          |  |  |

| M13        | 400/300         | 4      | 1          | M17        | 600/400  | 4      | 1          |  |  |

| M14        | 600/400         | 22     | 1          | M18        | 400/300  | 4      | 1          |  |  |

| M15        | 600/400         | 22     | 1          |            |          |        |            |  |  |

|            | CMFB Circuit |        |            |            |          |        |            |  |  |

|------------|--------------|--------|------------|------------|----------|--------|------------|--|--|

| Transistor | W/L (um)     | Finger | Multiplier | Transistor | W/L (um) | Finger | Multiplier |  |  |

| M19        | 600/400      | 10     | 1          | M23        | 600/400  | 4      | 1          |  |  |

| M20        | 600/400      | 10     | 1          | M24        | 600/400  | 4      | 1          |  |  |

| M21        | 600/400      | 4      | 1          | M25        | 400/300  | 2      | 1          |  |  |

| M22        | 600/400      | 4      | 1          | M26        | 400/300  | 2      | 1          |  |  |

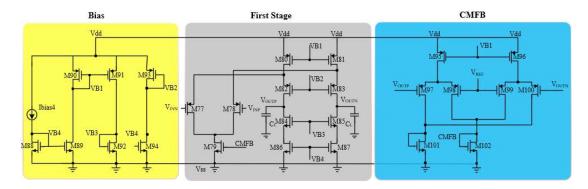

Figure 3.23 Schematic of the second stage real OPA.

|              | 2nd Order OPA - Folded cascode opamp |

|--------------|--------------------------------------|

|              | Pre-sim                              |

| loading (pF) | 2                                    |

| DC Gain (dB) | 63.77                                |

| Ft(KHz)      | 3.69                                 |

| PM (degree)  | 89.19                                |

| SR+(us/sec)  | 2.067                                |

| SR-(us/sec)  | 1.423                                |

| CM(vol)      | 0.9                                  |

| CMRR (dB)    | 95.79                                |

| power (uW)   | 247.038                              |

| UBM (MHz)    | 5.6                                  |

Table IX. Specification of the second transistor.

Table X. Size of the second transistor and biasing circuit.

| Folded Cascade OPA |          |        |            |            |          |        |           |  |

|--------------------|----------|--------|------------|------------|----------|--------|-----------|--|

| Transistor         | W/L (um) | Finger | Multiplier | Transistor | W/L (um) | Finger | Multiplie |  |

| M25                | 250/500  | 2      | 2          | M31        | 470/500  | 6      | 1         |  |

| M26                | 250/500  | 2      | 2          | M32        | 260/500  | 3      | 1         |  |

| M27                | 250/500  | 16     | 3          | M33        | 260/500  | 3      | 1         |  |

| M28                | 400/500  | 17     | 2          | M34        | 260/500  | 3      | 1         |  |

| M29                | 400/500  | 17     | 2          | M35        | 260/500  | 3      | 1         |  |

| M30                | 470/500  | 6      | 1          |            |          |        |           |  |

|            | Biasing Circuit |        |            |            |          |        |            |  |

|------------|-----------------|--------|------------|------------|----------|--------|------------|--|

| Transistor | W/L (um)        | Finger | Multiplier | Transistor | W/L (um) | Finger | Multiplier |  |

| M36        | 250/500         | 10     | 1          | M40        | 250/500  | 2      | 1          |  |

| M37        | 250/500         | 10     | 1          | M41        | 400/500  | 4      | 1          |  |

| M38        | 400/500         | 20     | 1          | M42        | 250/500  | 10     | 1          |  |

| M39        | 400/500         | 20     | 1          |            |          |        |            |  |

| CMFB Circuit |          |        |            |            |          |        |            |  |

|--------------|----------|--------|------------|------------|----------|--------|------------|--|

| Transistor   | W/L (um) | Finger | Multiplier | Transistor | W/L (um) | Finger | Multiplier |  |

| M43          | 500/500  | 9      | 1          | M47        | 400/500  | 9      | 1          |  |

| M44          | 500/500  | 9      | 1          | M48        | 400/500  | 9      | 1          |  |

| M45          | 400/500  | 9      | 1          | M49        | 250/500  | 4      | 2          |  |

| M46          | 400/500  | 9      | 1          | M50        | 250/500  | 4      | 2          |  |

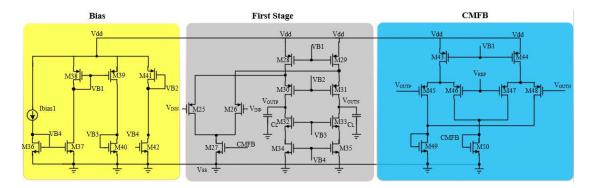

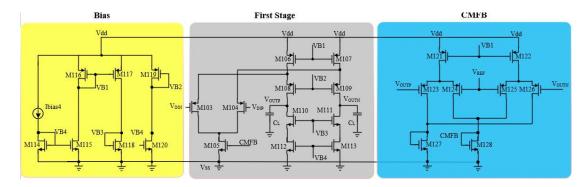

Figure 3.24. Schematic of the third stage real OPA.

|              | 3rd Order OPA - Folded cascode opamp |

|--------------|--------------------------------------|

|              | Pre-sim                              |

| loading (pF) | 2                                    |

| DC Gain (dB) | 62.63                                |

| Ft(KHz)      | 25.76                                |

| PM (degree)  | 85.89                                |

| SR+(us/sec)  | 16.06                                |

| SR-(us/sec)  | 8.458                                |

| CM(vol)      | 0.9                                  |

| CMRR (dB)    | 93.24                                |

| power (uW)   | 287.993                              |

| UBM (MHz)    | 34.05                                |

Table XI. Specification of the third transistor.

Table XII. Sizes of the third transistor and biasing circuit.

|            |          |        | Folded Ca  | scade OPA  |          |        |            |

|------------|----------|--------|------------|------------|----------|--------|------------|

| Transistor | W/L (um) | Finger | Multiplier | Transistor | W/L (um) | Finger | Multiplie  |

| M51        | 400/300  | 2      | 1          | M57        | 600/400  | 12     | 2          |

| M52        | 400/300  | 2      | 1          | M58        | 400/300  | 4      | 1          |

| M53        | 400/300  | 10     | 2          | M59        | 400/300  | 4      | 1          |

| M54        | 600/400  | 17     | 4          | M60        | 400/300  | 4      | 1          |

| M55        | 600/400  | 17     | 4          | M61        | 400/300  | 4      | 1          |

| M56        | 600/400  | 12     | 2          | о<br>      | 17       | 2      | 10.77<br>1 |

|            |          |        | Biasing    | Circuit    |          |        |            |

|------------|----------|--------|------------|------------|----------|--------|------------|

| Transistor | W/L (um) | Finger | Multiplier | Transistor | W/L (um) | Finger | Multiplier |

| M62        | 400/300  | 4      | 1          | M66        | 400/300  | 1      | 1          |

| M63        | 400/300  | 4      | 1          | M67        | 600/400  | 4      | 1          |

| M64        | 600/400  | 22     | 1          | M68        | 400/300  | 4      | 1          |

| M65        | 600/400  | 22     | 1          | о<br>о     | 29 W     | 8      | 400        |

|            |          |        | CMFB       | Circuit    |          |        |            |

|------------|----------|--------|------------|------------|----------|--------|------------|

| Transistor | W/L (um) | Finger | Multiplier | Transistor | W/L (um) | Finger | Multiplier |

| M69        | 600/400  | 10     | 1          | M73        | 600/400  | 4      | 1          |

| M70        | 600/400  | 10     | 1          | M74        | 600/400  | 4      | 1          |

| M71        | 600/400  | 4      | 1          | M75        | 400/300  | 2      | 1          |

| M72        | 600/400  | 4      | 1          | M76        | 400/300  | 2      | 1          |

Figure 3.25 Schematic of the fourth stage real OPA.

|              | 4th Order OPA - Folded cascode opamp |

|--------------|--------------------------------------|

| 2<br>1       | Pre-sim                              |

| loading (pF) | 2                                    |

| DC Gain (dB) | 72.48                                |

| Ft(KHz)      | 11.18                                |

| PM (degree)  | 80.05                                |

| SR+(us/sec)  | 18.05                                |

| SR-(us/sec)  | 4.46                                 |

| CM(vol)      | 0.9                                  |

| CMRR (dB)    | 100.81                               |

| power (uW)   | 262.893                              |

| UBM (MHz)    | 40.9                                 |

Table XIII. Specification of the fourth transistor.

| Table XIV. | Size of | the fourth | transistor  | and   | biasing   | circuit.          |

|------------|---------|------------|-------------|-------|-----------|-------------------|

| 1001011111 |         | 110 100101 | u wiibibibi | wii u | orability | • 11 • • • 11 • • |

|            |          |        | Folded Ca  | scade OPA  |          |        |           |

|------------|----------|--------|------------|------------|----------|--------|-----------|

| Transistor | W/L (um) | Finger | Multiplier | Transistor | W/L (um) | Finger | Multiplie |

| M77        | 250/500  | 30     | 1          | M83        | 470/500  | 9      | 1         |

| M78        | 250/500  | 30     | 1          | M84        | 260/500  | 3      | 1         |

| M79        | 250/500  | 16     | 3          | M85        | 260/500  | 3      | 1         |

| M80        | 400/500  | 38     | 1          | M86        | 260/500  | 3      | 1         |

| M81        | 400/500  | 38     | 1          | M87        | 260/500  | 3      | 1         |

| M82        | 470/500  | 9      | 1          |            |          |        | 1000 C    |

|            |          |        | Biasing    | Circuit    |          |        |            |

|------------|----------|--------|------------|------------|----------|--------|------------|

| Transistor | W/L (um) | Finger | Multiplier | Transistor | W/L (um) | Finger | Multiplier |

| M88        | 250/500  | 10     | 1          | M92        | 250/500  | 2      | 1          |

| M89        | 250/500  | 10     | 1          | M93        | 400/500  | 4      | 1          |

| M90        | 400/500  | 20     | 1          | M94        | 250/500  | 10     | 1          |

| M91        | 400/500  | 20     | 1          |            | · · · ·  |        | •          |

|            |          |        | CMFB       | Circuit    |          |        |            |

|------------|----------|--------|------------|------------|----------|--------|------------|

| Transistor | W/L (um) | Finger | Multiplier | Transistor | W/L (um) | Finger | Multiplier |

| M95        | 500/500  | 9      | 1          | M99        | 400/500  | 9      | 1          |

| M96        | 500/500  | 9      | 1          | M100       | 400/500  | 9      | 1          |

| M97        | 400/500  | 9      | 1          | M101       | 250/500  | 4      | 2          |

| M98        | 400/500  | 9      | 1          | M102       | 250/500  | 4      | 2          |

Figure 3.26 Schematic of the fifth stage real OPA.

|              | 5th Order OPA - Folded cascode + gain bosted opamp |

|--------------|----------------------------------------------------|

|              | Pre-sim                                            |

| loading (pF) | 2                                                  |

| DC Gain (dB) | 90.91                                              |

| Ft(KHz)      | 1.22                                               |

| PM (degree)  | 84.63                                              |

| SR+(us/sec)  | 23.56                                              |

| SR-(us/sec)  | 3.61                                               |

| CM(vol)      | 0.9                                                |

| CMRR (dB)    | 128.82                                             |

| power (uW)   | 319.103                                            |

| UBM (MHz)    | 43.52                                              |

Table XV. Specification of the fifth transistor.

Table XVI. Size of the fifth transistor and biasing circuit.

|            | Folded Cascade OPA |        |            |            |          |        |            |  |  |  |

|------------|--------------------|--------|------------|------------|----------|--------|------------|--|--|--|

| Transistor | W/L (um)           | Finger | Multiplier | Transistor | W/L (um) | Finger | Multiplier |  |  |  |

| M103       | 250/500            | 30     | 1          | M109       | 470/500  | 9      | 2          |  |  |  |

| M104       | 250/500            | 30     | 1          | M110       | 260/500  | 3      | 2          |  |  |  |

| M105       | 250/500            | 16     | 6          | M111       | 260/500  | 3      | 2          |  |  |  |

| M106       | 400/500            | 38     | 2          | M112       | 260/500  | 3      | 2          |  |  |  |

| M107       | 400/500            | 38     | 2          | M113       | 260/500  | 3      | 2          |  |  |  |

| M108       | 470/500            | 9      | 2          |            | 685      |        |            |  |  |  |

|            |          |        | Biasing    | Circuit    |          |        |            |

|------------|----------|--------|------------|------------|----------|--------|------------|

| Transistor | W/L (um) | Finger | Multiplier | Transistor | W/L (um) | Finger | Multiplier |

| M114       | 250/500  | 10     | 1          | M118       | 250/500  | 2      | 1          |

| M115       | 250/500  | 10     | 1          | M119       | 400/500  | 4      | 1          |

| M116       | 400/500  | 20     | 1          | M120       | 250/500  | 10     | 1          |

| M117       | 400/500  | 20     | 1          |            |          |        |            |

| CMFB Circuit |          |        |            |            |          |        |            |

|--------------|----------|--------|------------|------------|----------|--------|------------|

| Transistor   | W/L (um) | Finger | Multiplier | Transistor | W/L (um) | Finger | Multiplier |

| M121         | 500/500  | 9      | 2          | M125       | 400/500  | 9      | 2          |

| M122         | 500/500  | 9      | 2          | M126       | 400/500  | 9      | 2          |

| M123         | 400/500  | 9      | 2          | M127       | 250/500  | 4      | 4          |

| M124         | 400/500  | 9      | 2          | M128       | 250/500  | 4      | 4          |

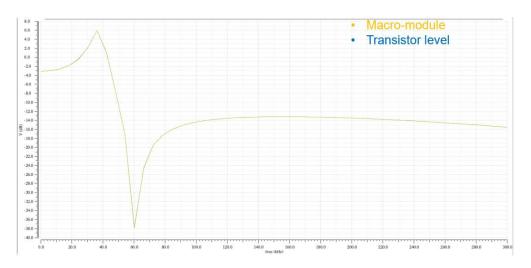

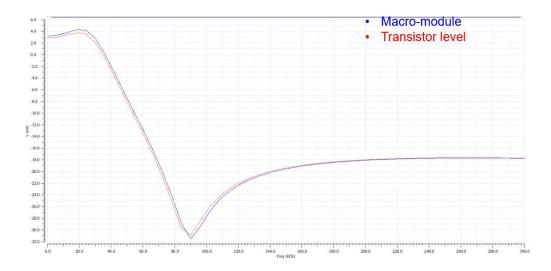

Figure 3.27 Frequency response of the linear section between the ideal and transistor levels.

Figure 3.28 Frequency response of the high-Q section between the ideal and transistor levels.

Figure 3.29. Frequency response of the low-Q section between the ideal and transistor levels.

Figure 3.30. Frequency response of the LPF between the ideal and transistor levels. In this work, a 5<sup>th</sup> order elliptic LPF was analyzed and designed. To ensure the high performance of the LPF, the non-idealities of the OPA and sampling switches were simulated. The TSMC 0.18  $\mu$ m CMOS technology was employed to verify this design. The transistor level simulation results are summarized in Table XVII.

| Parameter              | Value      |  |

|------------------------|------------|--|

| Sampling Frequency     | 600KHz     |  |

| DC Gain                | 0 dB       |  |

| Passband               | 0-36 KH    |  |

| Ripple in passband     | 0.229dB    |  |

| Stopband               | 72-240 KHz |  |

| Gain in Stopband       | - 51dB     |  |

| Minimum Capacitor size | 100 fF     |  |

| Total Capacitance      | 4560.5fF   |  |

Table XVII. Specification for the LPF.

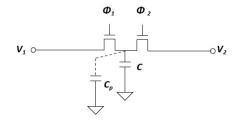

# **3.3** PCC Technique [3]

The linearity, power, and area efficiencies of a filter design are critical for wireless applications with low hardware complexity and cost. These integrators in filter application should have high linearity to achieve a high SNDR and to avoid the input referred noise, which affects the overall linearity performance [9].

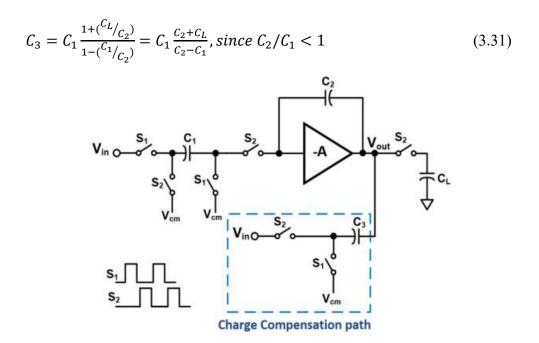

Several techniques have been proposed to improve the slew rate of OTAs in switched capacitor circuits [10][11]. These techniques involve the designing of an active component and auxiliary amplifier to share the redundant current flows, resulting in the settling down of the fully-differential OPA circuit to the common ground level with enough current flows. These approaches enhance the linearity by improving the slew rate, but at the expense of chip efficiency. This study focuses on the slew rate enhancement, which would reduce the settling time with an additional passive charge compensation path adding at the output of the OTA [3]. The proposed technique is shown in Figure 3.31. During phase S<sub>1</sub>, the input is sampled onto C<sub>1</sub>, while the charge transfer phase S<sub>2</sub>, the OTA needs to provide charge equal to C<sub>1</sub>V<sub>in</sub> to the top plate of C<sub>2</sub> in additional charge proportional to the input voltage is also provided onto the top plate of C<sub>2</sub> provided through C<sub>3</sub>. Ideally, if V<sub>in</sub> between S<sub>1</sub> and S<sub>2</sub> does not change,

and if the optimum value of  $C_3$  is chosen, the OTA does not need to provide any charge, hence power can be saved in biasing the OTA. If the input varies slowly (i.e., it is oversampled) the charge provided by the OTA can still be greatly reduced as only the charge proportional to the difference between the previous input voltage and current input voltage needs to be provided. Considering the effect of  $C_L$ ,  $C_3$  can be expressed as (3.31).

Figure 3.31. A charge-compensated integrator [3].

# **3.3.1 PCC Technique Design and Implementation**

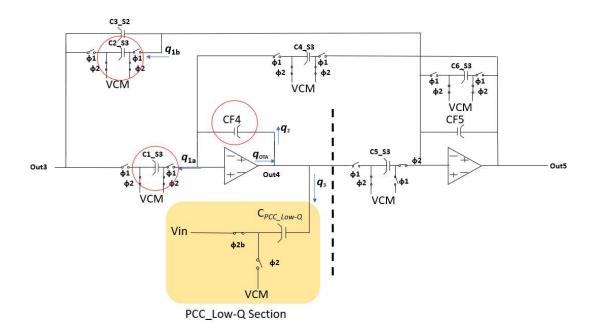

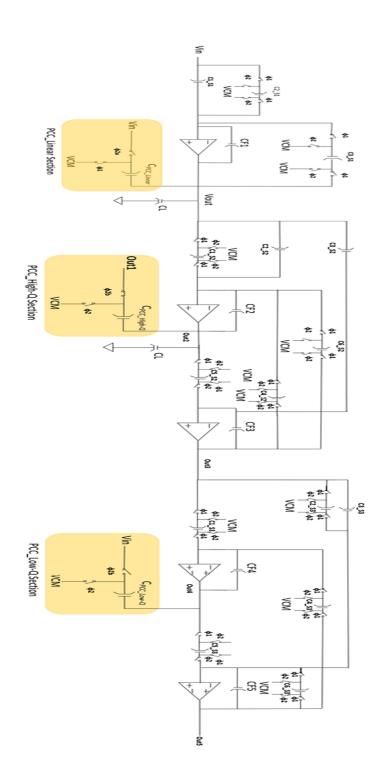

In the LPF design, the DC-gain loops of each OTA were less than 1, we derived the capacitance needed at the output of the OTA of the linear , high-Q, and low-Q sections. We added PCC paths at the output of the 1<sup>st</sup> integrator in the high-Q and low-Q sections during the evaluation because the output of the 2<sup>nd</sup> integrator connected the unknown capacitor load.

1. Designing the PCC capacitance of the linear section

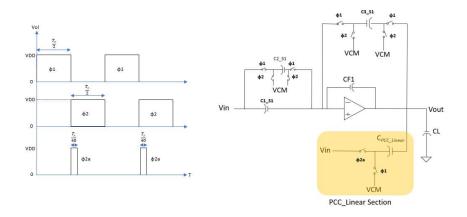

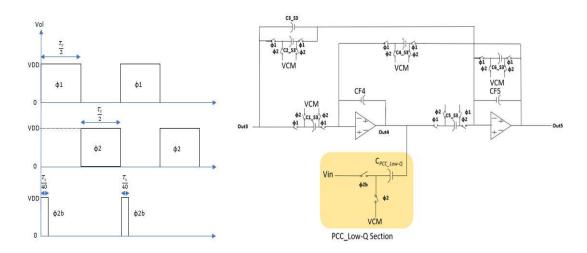

The linear section with a PCC path is shown in Figure 3.32.

Figure 3.32. Linear section with a PCC path.

During the  $\Phi$ 2 phase, by KCL, we can derive equations (3.21) – (3.24), to determine the C<sub>PCC\_Linear</sub>.

Figure 3.33. Linear section with a PCC path during the  $\Phi 2$  phase operation.

$$q_1[n] = C_{1_{S1}} * V_{in}[(n - 1/2)]$$

(3.32)

$$q_2[n] = C_{CF1} * \{V_{out}(n) - V_{out}(n - \frac{1}{2})\}$$

(3.33)

As we know,  $q_2$  and  $q_3$  are discharged to ground.

Then,

$$q_3 = [V_{out}[(n - 1/2)) - 0 - (V_{out}[(n - 1) - 0)]$$

So,  $V_{out}[n - 1/2] = V_{out}[n - 1]$  (3.34)

Put (3) into (3.22),  $q_2[n] = C_{CF1} * \{V_{out}(n) - V_{out}[(n - 1))]$

$V_{out}(n) - V_{out}(n - 1) = \frac{C_{1.S1}}{C_L} V_{in}(n - 1/2)$

$q_L[n] = C_L * V_{out}[n] - 0 - \{V_{out}(n - 1/2) - 0\}$

$$= C_L * V_{out}[n] - V_{out}(n - 1/2)$$

=  $C_L \frac{C_{1.S1}}{C_L} V_{in}(n - 1/2)$  (3.35)

$$C_{PCC\_Linear} = C_{1\_S1} \frac{1 + \frac{C_L}{C_2}}{1 - \frac{C_1}{C_2}} = C_{1\_S1} \frac{C_{2\_S1} + C_L}{C_{2\_S1} - C_{1\_S1}} \approx 264 fF$$

(3.36)

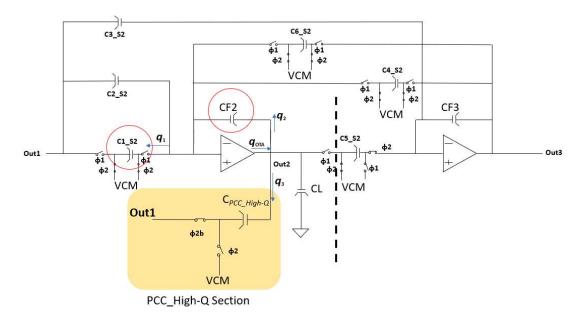

2. Designing the PCC capacitance of the high-Q section

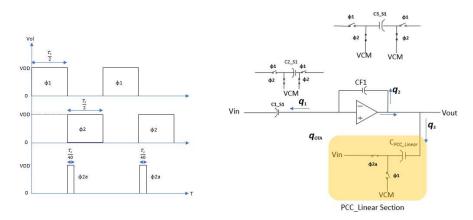

The high-Q section with a PCC path is shown in Figure 3.34.

Figure 3.34. High-Q section with a PCC path.

Figure 3.35. High-Q section with a PCC path at the  $\Phi$ 2 phase.

During the  $\Phi$ 2 phase, by KCL, we derived equations (3.32) – (3.35) to derive C<sub>PCC\_High-Q</sub>,

$$q_1[n] = C_{1_{S2}} * V_{out1}[(n - 1/2)]$$

(3.37)

$$q_2[n] = C_{CF2} * \{V_{out2}(n) - V_{out2}(n - \frac{1}{2})\}$$

(3.38)

As we know, if  $q_2$  and  $q_3$  are discharged to ground.

Then,

$$q_3 = [V_{out2}[(n - 1/2)) - 0 - (V_{out2}[(n - 1) - 0)]$$

So,  $V_{out} [n - 1/2] = V_{out2}[n - 1]$  (3.39)

Put (3) into (3.22),  $q_2[n] = C_{CF2} * \{V_{out2}(n) - V_{out2}[(n - 1))]$

$V_{out2}(n) - V_{out2}(n - 1) = \frac{C_{1.52}}{C_L} V_{in}(n - 1/2)$

$q_L[n] = C_L * V_{out2}[n] - 0 - \{V_{out2}(n - 1/2) - 0\}$

$= C_L * V_{out2}[n] - V_{out2}(n - 1/2)$

$= C_L \frac{C_{1.52}}{C_L} V_{in}(n - 1/2)$  (3.40)

$$C_{PCC\_High-Q} = C_{2\_S2} \frac{1 + \frac{C_L}{C_{F2}}}{1 - \frac{C_2 - S2}{C_F}} = C_{2\_S2} \frac{CF2 + C_L}{CF2 - C_{2\_S2}} \approx 186.6 fF$$

(3.41)

# 3. Designing the PCC capacitance of the low-Q section

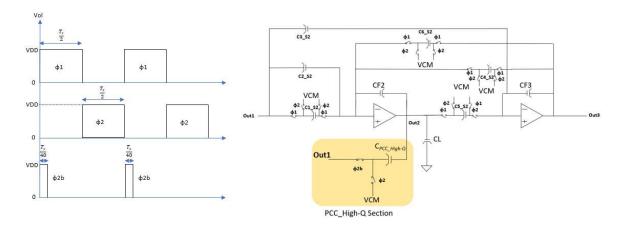

The low-Q section with a PCC path is shown in Figure 3.36.

Figure 3.36. Low-Q section with a PCC path.

Figure 3.37. Low-Q section with a PCC path at the  $\Phi 2$  phase.

During the  $\Phi$ 2 phase, by KCL, we derived equations (3.32) – (3.35) to determine  $C_{PCC\_High=Q}$ ,

$$q_{1a}[n] = C_{1_{S3}} * V_{out3}[(n - 1/2)]$$

(3.42)

$$q_{1b}[n] = C_{2_{S3}} * V_{out3}[(n - 1/2)]$$

(3.43)

$$q_{1}[n] = q_{1a}[n] + q_{1b}[n] = (C_{1_{S3}} + C_{2_{S3}}) * V_{out3}[(n - 1/2)]$$

(3.44)

$$q_2[n] = C_{CF} * \{V_{out4}(n) - V_{out4}(n - \frac{1}{2})\}$$

(3.45)

As we know,  $q_2$  and  $q_3$  are discharged to ground.

Then,

$$q_3 = [V_{out4}[(n - 1/2)) - 0 - (V_{out4}[(n - 1) - 0)]$$

So,  $V_{out4}[n - 1/2] = V_{out4}[n - 1]$  (3.46)

Put (3) into (3.22),  $q_2[n] = C_{CF4} * \{V_{out4}(n) - V_{out4}[(n - 1))\}$

$V_{out4}(n) - V_{out4}(n - 1) = \frac{C_{1.S3} + C_{2.S3}}{C_L} V_{in}(n - 1/2)$

$q_L[n] = C_L * V_{out4}[n] - 0 - \{V_{out4}(n - 1/2) - 0\}$

$= C_L * V_{out4}[n] - V_{out4}(n - 1/2)$

$$= C_L \frac{c_{1_s3} + c_{2_s3}}{c_L} V_{in}(n - \frac{1}{2})$$

(3.47)

$$C_{PCC\_LOW-Q} = (C_{1\_S3} + C_{2\_S3}) \frac{1 + \frac{C_L}{C_{F4}}}{1 - \frac{(C_{1\_S3} + C_{2\_S3})}{C_{2\_S2}}} = (C_{1\_S3} + C_{2\_S3}) \frac{C_{2\_S3} + C_L}{C_{2\_S3} - C_{1\_S3} - C_{2\_S3}} \approx 56 fF(3.48)$$

The completed LPF circuit with the proposed PPC technique is shown in Figure 3.38.

Figure 3.38. Completed work with proposed PCC technique.

# **3.3.2 Simulation Result**

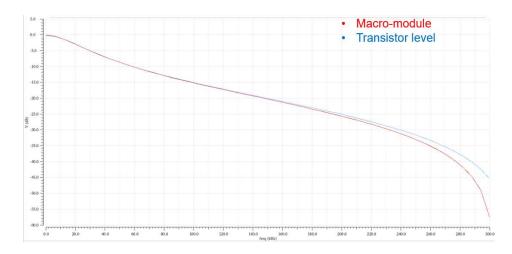

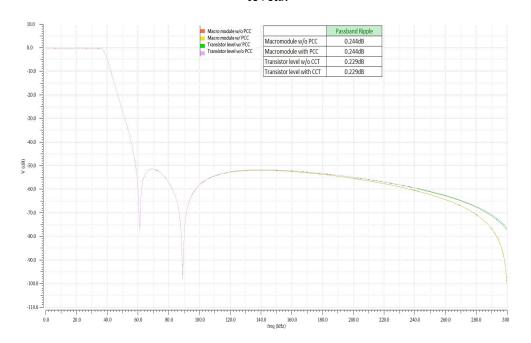

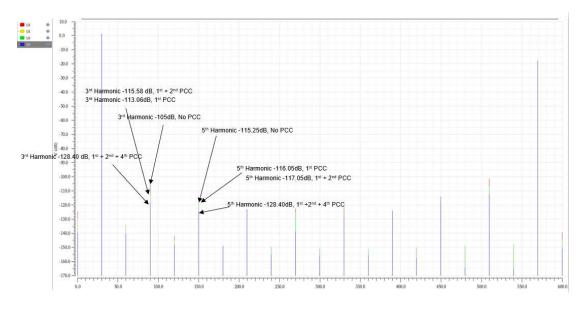

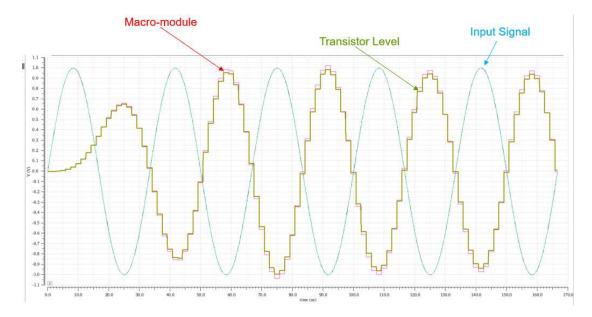

Among the three stages, the linear stage had the highest requirement for slew rate (SR), so the SR requirements of this stage are discussed. The output harmonics with different SR when the input signal frequency was 30 KHz with  $V_{pp}$  sine signal,  $\pm 1.8$  vol, are shown in Figure 3.39, and the comparison of the transient response is shown in Figure 3.40. Table XVIII lists the amplitude values of the 3<sup>rd</sup> and 5<sup>th</sup> harmonics at the conventional LPF circuit. The PCC result shoed that the noise improvement (12.34 dB) noise improvement at the 3rd harmonic distortion was reduced from -105.79dBc to -118.13dBc & improve 13.15dB at 5th harmonic distortion was reduced from was reduced from -115.25dBc to -128.40dBc.

Figure 3.39. Distortions of the conventional LPF.

Figure 3.40. LPF transient time responses of the ideal and transistor levels.

Table XVIII. Simulation results for the macro-module and transistor level.

#### Macro-module

#### Transistor level

| Harmonic Ampliture (Unit: dB)         | 3rd Harmonic | 5th Harmonic | Harmonic Ampliture(Unit: dB)              | 3rd Harmonic | 5th Harmonic |

|---------------------------------------|--------------|--------------|-------------------------------------------|--------------|--------------|

| 5th order macro-module without CCT    | -110.25      | -121.42      | 5th order transistor level without CCT    | -105.79      | -115.25      |

| 5th order macro-module with 1st CCT   | -117.40      | -118.15      | 5th order transistor level with 1st CCT   | -113.06      | -116.05      |

| 5th order macro-module with 1/2 CCT   | -119.71      | -125.9       | 5th order transistor level with 1/2 CCT   | -112.58      | -117.05      |

| 5th order macro-module with 1/2/4 CCT | -125.12      | -131.78      | 5th order transistor level with 1/2/4 CCT | -118.13      | -128.40      |

The dynamic powers at each SC circuit and the individual PCC techniques are given in Table XIX, whereas the comparison between with and without the PCC techniques is given in Table XX. The corresponding dynamic power consumption with the PCC is 0.363 uW as low as expected.

|    |              | Bilinear Sec                    | tion Caps value table | :             |            |  |  |

|----|--------------|---------------------------------|-----------------------|---------------|------------|--|--|

|    |              | DR Unit (fF)                    | Area                  | Dynamic Power | Vrms (Vol) |  |  |

|    | CF1          | 825                             | 825                   |               |            |  |  |

|    | C1_S1        | 100                             | 100 (Unit Cap)        | ]             |            |  |  |

| SC | C2_S1        | 200                             | 200                   | 1.07E-07      | 0.943      |  |  |

| SC | C3_S1        | 200                             | 200                   | 1.02E-07      | 0.922      |  |  |

| SC | C_PCC_Linear | 264                             |                       | 1.89E-07      | 1.093      |  |  |

|    |              | High-Q Section Caps value table |                       |               |            |  |  |

|    |              | DR Unit (fF)                    | Area                  | Dynamic Power | Vrms (Vol) |  |  |

|    | CF2          | 463                             | 100 (Unit Cap)        |               |            |  |  |

| SC | C1_S2        | 133                             | 348                   | 6.92E-08      | 0.931      |  |  |

|    | C2_S2        | 0                               | 363                   |               |            |  |  |

|    | C3_S2        | 100                             | 100 (Unit Cap)        |               |            |  |  |

| SC | C4_S2        | 184.5                           | 0                     | 1.00E-07      | 0.952      |  |  |

|    | CF3          | 374                             | 97                    |               | 33<br>Ale  |  |  |

| SC | C5_S2        | 141                             | 179                   | 6.90E-08      | 0.903      |  |  |

|    | C6_S2        | 103                             | 100 (Unit Cap)        |               |            |  |  |

| SC | C_PCC_HighQ  | 186.6                           |                       | 1.34E-07      | 1.093      |  |  |

|    |              | High-Q Section Caps value table |                       |               |            |  |  |

| 1  |              | DR Unit (fF)                    | Area                  | Dynamic Power | Vrms (Vol) |  |  |

|    | CF4          | 530.5                           | 530                   |               |            |  |  |

| SC | C1_S3        | 141.7                           | 141                   | 8.13E-08      | 0.978      |  |  |

| SC | C2_S3        | 0                               | 0                     | 0.00E+00      | 0.976      |  |  |

| SC | C3_S2        | 100                             | 100 (Unit Cap)        | 5.13E-08      | 0.925      |  |  |

| SC | C4_S2        | 100                             | 100 (Unit Cap)        | 5.65E-08      | 0.97       |  |  |

|    | CF5          | 500                             | 500                   |               |            |  |  |

|    | C5_S3        | 302.5                           | 302                   |               |            |  |  |

| SC | C6_S2        | 169                             | 169                   | 9.23E-08      | 0.954      |  |  |

| SC | C_PCC_HighQ  | 56                              |                       | 4.01E-08      | 1.093      |  |  |

Table XIX. Simulation results of dynamic power at the transistor level circuit.

Table XX. Simulation results of the dynamic power comparison.

|                                                        | Unit(uW) |

|--------------------------------------------------------|----------|

| Grand Total of Dynamic Power w/o PCC (5 OTAs excluded) | 0.728    |

| Grand total of Dynamic Power w/ PCC (5 OTAs excluded)  | 1.091    |

| Dynamic Power_Linear_PCC                               | 0.189    |

| Dynamic Power_HighQ_PCC                                | 0.134    |

| Dynamic Power lowQ PCC                                 | 0.04     |

# **Chapter 4: Conclusion and Future Work**

Designing analog LPF circuits with good linearity, low cost, and area efficiency is critical for the present day mixed-signal designs. In this study, we designed a fully-differential 5<sup>th</sup>-order elliptic low-pass SC filter with a sampling frequency of 600 kHz, a corner frequency of 36 kHz using the PCC technique. This technique improved the linearity of the LPF with a noise reduction of 12.3 dB at the 3<sup>rd</sup> harmonic distortion and 13.1 dB at the 5<sup>th</sup> harmonic distortion without using the active blocks. This indicates that the PCC technique is an efficient approach for designing LPFs.

The future research will focus on the utilization of the PCC technique for designing FIR filters with low power consumption.

## BIBLIOGRAPHY

- [1] Y. Zhao, P. Mak, M. Law and R. P. Martins, "A 0.127-mm<sup>2</sup>, 5.6-mW,5<sup>th</sup>-order SC LPF with +23.5-dBm IIP3 and 1.5-to-15-MHz clockdefined bandwidth in 65-nm CMOS," 2013

IEEE Asian Solid-State Circuits Conference (A-SSCC), Singapore, 2013, pp. 361-364.

- [2] M. H. Naderi, S. Prakash and J. Silva-Martinez, "Operational Transconductance Amplifier With Class-B Slew-Rate Boosting for Fast High-Performance Switched-Capacitor Circuits," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 65, no. 1, pp. 3769-3779, Nov. 2018

- [3] Kareppagoudr, M.; Caceres, E.; Kuo, Y.; Shakya, J.; Wang, Y.; Temes, G.C. Passive slew rate enhancement technique for Switched-Capacitor Circuits. In Proceedings of the 2019 IEEE 62nd International Midwest Symposium on Circuits and Systems (MWSCAS), Dallas, TX, USA, 4–7 August 2019; pp. 913–916.

- [4] Kerry Lacanette, "A Basic Introduction To Filter Devices-Active, Passive And Switched-Capacitor", National Semiconductor Application Note 779, April 1991.

- [5] John G. Prokis. Dimitris G. Manolakis. Digital Signal Processing. Fourth Edition. 2007

- [6] David A.Johns and Ken Martin, "Analog Integrated Circuit Design", John Wiley & Sons, Inc., 1997.

- [7] Behzad Razavi, "Design of Analog CMOS Integrated Circuits", Edition 2002.