#### AN ABSTRACT OF THE DISSERTATION OF

Boyu Shen for the degree of <u>Doctor of Philosophy</u> in <u>Electrical and Computer</u> Engineering presented on December 2, 2020.

Title: Imepdance Sensing Techniques for Integrated Circuits Sensor Applications

| Abstract approved: |  |  |

|--------------------|--|--|

|                    |  |  |

Matthew L. Johnston

Impedance measurements are increasingly utilized in modern integrated circuit sensing systems, as impedance is the most common electrical signal obtained from sensors, delivering physical, chemical and biomedical signals of interest from different sensor types. Impedance sensing for wide frequencies of interest, broad dynamic range, and various sensor interfaces present numerous challenges, especially for targeted implementation in CMOS for miniaturization, which presents power and area limitations. In this thesis, first, a low power impedance-based cytometer architecture for cell analysis applications is presented. Fabricated in 0.18m CMOS process with 6pArms input-referred noise over 200Hz bandwidth at 0.5 MHz modulation frequency, the impedance sensor demonstrates in detecting 3m diameter particles. Secondly, a low-noise, front-end sensor IC that includes both AC impedance spectroscopy and DC amperometric measurement capabilities for electrochemical and biosensor applications is presented. Implemented using a 0.18  $\mu$ m CMOS process, this work achieves  $45 \, \text{fA}/\sqrt{\text{Hz}}$  input current noise density at  $1 \, \text{kHz}$ , and a maximum of  $104 \, \text{dB}$  dynamic range at  $10 \, \text{Hz}$ . Finally, using an impedance sensing technique, a

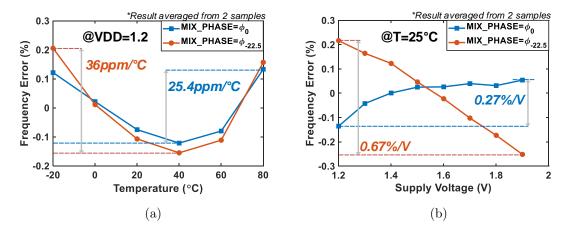

low-power RC oscillator based on IQ-balanced impedance sensing frequency-locked loop is designed and demonstrated, achieving 25.4ppm/°C across temperature variation and 0.27%/V across supply variation at 650kHz output frequency.

©Copyright by Boyu Shen December 2, 2020 All Rights Reserved

## Imepdance Sensing Techniques for Integrated Circuits Sensor Applications

by

Boyu Shen

#### A DISSERTATION

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented December 2, 2020 Commencement June 2021

| <u>Doctor of Philosophy</u> dissertation of <u>Boyu Shen</u> presented on <u>December 2, 2020</u> .                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APPROVED:                                                                                                                                                                                                 |

| Major Professor, representing Electrical and Computer Engineering                                                                                                                                         |

| Head of the School of Electrical Engineering and Computer Science                                                                                                                                         |

| Dean of the Graduate School                                                                                                                                                                               |

|                                                                                                                                                                                                           |

| I understand that my dissertation will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my dissertation to any reader upon request. |

| Boyu Shen, Author                                                                                                                                                                                         |

#### ACKNOWLEDGEMENTS

It has been a great journey since I came to Corvallis in 2015 after I graduated from my bachelor degree in University of Science and Technology of China (USTC) in China. I would first thanks to my advisor, Dr. Matthew Johnston, who brought me here when I was still a fresh man in circuit design with no extra experience and taught me numerous knowledge in conducting, writing, and presenting the research. It is also him who gave all the freedom and support for me to perform research that I am interested in. Secondly, I would like to thank all the people in my research group SIM lab, Soumya, Hyunkyu, Shaan, Kyle, Jinyong, Jacob, Callen, and all the other new members I have not got a chance to works with. Special thanks to Soumya: your encouragement and guidance during the five years mean a lot to me, and working with you for me is really a honor, and Hyunkyu: you are a such good senior colleague and friend who taught me so much in research and in life. Then, I would thanks to all my friends in Kelly and Corvallis during this amazing journey: Yutao, Yang, Yao, Kai, Yanchao, Lukang, Xuanyi, Bo, Jialin, and everyone who helped me. Besides, I want to thank my parents who have always relentlessly supported me for what I want to do. I want to thank my girlfriend, Jianing, who is still in China and has been separated with me in the past four years, but constantly supported me and stood by me to share with my joy and sadness. I love you and wish we can reunite soon. Finally, I want to thank Corvallis where has been a fantastic place for me to live and study. I love every inch of the ground in Corvallis and will never forget the people, the view, and the serenity of Corvallis. See you Corvallis! Zaijian OSU!

# TABLE OF CONTENTS

|   |     | <u>P</u>                                                                                                | age                  |

|---|-----|---------------------------------------------------------------------------------------------------------|----------------------|

| 1 | Int | roduction                                                                                               | 1                    |

|   | 1.1 | Impedance Measurements in Sensors                                                                       | 1                    |

|   | 1.2 | Scope of the Thesis                                                                                     | 3                    |

| 2 | A   | Impedance Sensor for Source-Differential Flow Cytometry                                                 | 6                    |

|   | 2.1 | Introduction                                                                                            | 6                    |

|   | 2.2 | Hybrid-feedback IS for Source-Differential Impedance Cytometry 2.2.1 Source-differential sensing scheme | 9<br>9<br>10         |

|   | 2.3 | System Analysis                                                                                         | 14                   |

|   | 2.0 | 2.3.1 Loop dynamic analysis                                                                             | 14<br>17             |

|   | 2.4 | Circuit Implementation                                                                                  | 19                   |

|   |     | 2.4.1 System overview                                                                                   | 19<br>21<br>24       |

|   |     | 2.4.4 Up-conversion mixer and hybrid feedback impedance                                                 | 25                   |

|   | 2.5 | Verification and Measurement Results                                                                    | 26<br>27<br>31<br>32 |

|   | 2.6 | Conclusion                                                                                              | 38                   |

| 3 | A   | Tunable Readout IC for Impedance Spectroscopy and Amperometric Mea-                                     |                      |

|   | sui | rement of Electrochemical Sensors                                                                       | 40                   |

|   | 3.1 | Introduction                                                                                            | 40                   |

|   | 3.2 | System Design                                                                                           | 42<br>42<br>46       |

|   |     | 3.2.3 Delta-Sigma Impedance Analyzer                                                                    | 47                   |

|   | 3.3 | Measurement Results                                                                                     | 49                   |

|   | 3.4 | Conclusion                                                                                              | 52                   |

# TABLE OF CONTENTS (Continued)

|    |      |                         | $\underline{P}$                                                                   | age                        |

|----|------|-------------------------|-----------------------------------------------------------------------------------|----------------------------|

| 4  | A    | RC Oscil                | lator based on IQ-Balanced Impedance Sensing Frequency-Locked-                    |                            |

|    | Lo   | ор                      |                                                                                   | 55                         |

|    | 4.1  |                         | ction                                                                             | 55<br>55                   |

|    | 4.2  | 4.2.1<br>4.2.2          | cy Voltage Converter (FVC) in FLL-based RC Oscillator FVC design in previous work | 57<br>57<br>62<br>64       |

|    | 4.3  | 4.3.1<br>4.3.2          | nce IQ-balanced FLL                                                               | 65<br>66<br>67<br>71       |

|    | 4.4  | 4.4.1<br>4.4.2<br>4.4.3 | Implementation                                                                    | 74<br>76<br>80<br>82<br>84 |

|    | 4.5  | Measure                 | ement Results                                                                     | 85                         |

|    | 4.6  | Conclus                 | ion                                                                               | 90                         |

| 5  | Lis  | st of Con               | tributions                                                                        | 93                         |

| Ri | blio | graphy                  |                                                                                   | 96                         |

# LIST OF FIGURES

| Fig | gure |                                                                                                                                                                                                                                                      | Page |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|     | 1.1  | Impedance sensing technique used in (a)bioimepdance sensing [1]; (b)gas sensing [2]; (c) Biosening (DNA, cell) [3], [4]                                                                                                                              | 2    |

|     | 2.1  | (a) Equivalent circuit model of a single cell in solution, and (b) top-down illustration of IS electrodes in a microfluidic flow channel                                                                                                             | 7    |

|     | 2.2  | (a) Source-differential impedance cytometry topology, (b) equivalent circuit model of source-differential sensing scheme, and (c) frequency response of sensing current versus baseline current magnitude for source-differential sensing scheme     | - 8  |

|     | 2.3  | Generalized circuit model for a modulation/demodulation impedance measurement architecture with an impedance model cell at the input.                                                                                                                | 11   |

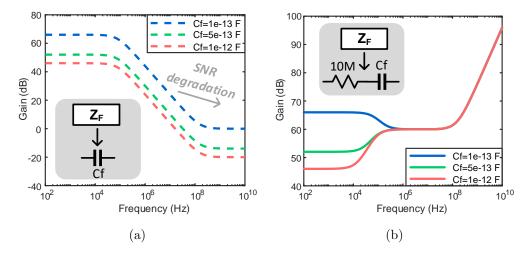

|     | 2.4  | Closed-loop gain $A_{\rm CL}$ frequency response when feedback element is (a) capacitor (b) capacitor series with resistor, assuming loop gain is sufficient                                                                                         | 13   |

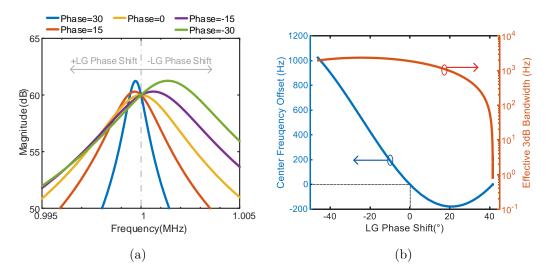

|     | 2.5  | (a) Frequency response of system closed-loop gain, $A_{\rm CL}$ , at different $LG_0$ phase shift $\theta$ conditions when $f_{\rm mod}{=}1{\rm MHz}$ ; (b) center frequency shift and effective 3-dB bandwidth at different loop-gain phase shifts. | 16   |

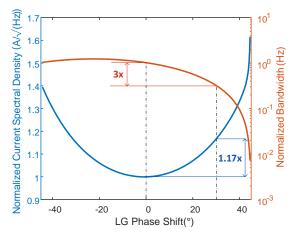

|     | 2.6  | Normalized input-referred noise current spectral density and noise bandwidth versus $LG_0$ phase shift $\theta$ when $f_{\text{mod}}=1\text{MHz.}$                                                                                                   | 18   |

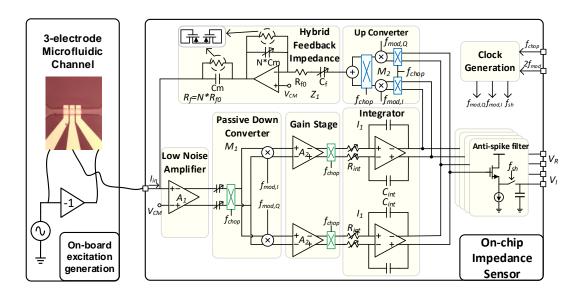

|     | 2.7  | High-level source-differential architecture of on-chip hybrid-feedback impedance sensor and off-chip microfluidic flow channel                                                                                                                       | 19   |

|     | 2.8  | Schematic of low-noise input amplifier and capacitive-coupled current-mode passive down-conversion mixer driven by 25% duty cycle $f_{\text{mod}}$ (chopper is not shown for simplicity)                                                             | 22   |

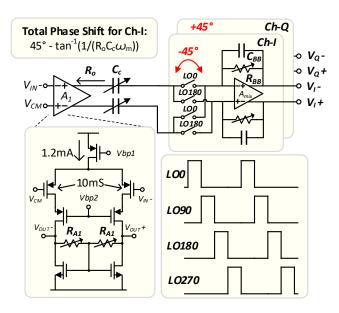

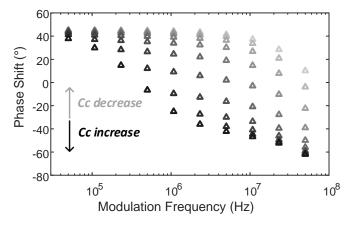

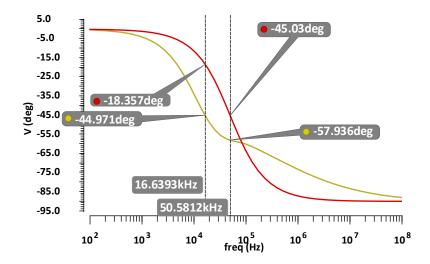

|     | 2.9  | Phase shift coverage of $A_1$ and $M_1$ across $50\mathrm{kHz}$ to $50\mathrm{MHz}$ for given $50\mathrm{fF}$ and $15\mathrm{pF}$ $C_\mathrm{c}$                                                                                                     | 23   |

|     | 2.10 | Schematic of the amplifier in integrator $I_1$                                                                                                                                                                                                       | 24   |

|     | 2.11 | Schematic of up-conversion mixer $M_2$                                                                                                                                                                                                               | 25   |

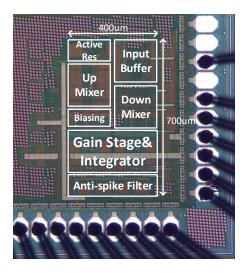

|     | 2.12 | Micrograph of the fabricated 0.18 $\mu m$ CMOS impedance sensor IC                                                                                                                                                                                   | 27   |

| Figure |                                                                                                                                                                                                                                                                                                            | Page |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

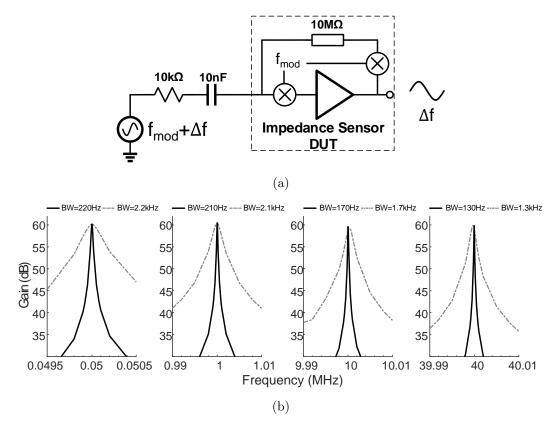

| 2.13   | (a) Measurement setup using a model cell for voltage gain transfer function of impedance sensor, and (b) measured voltage gain transfer function at different $f_{\rm mod}$ (0.05/1/10/40MHz) using low and high bandwidth modes                                                                           | . 28 |

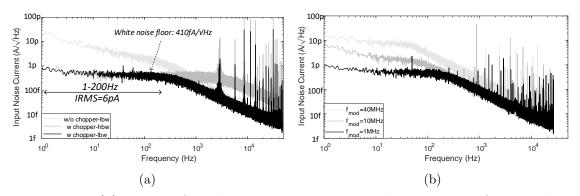

| 2.14   | (a) Input-referred noise current spectral density when $f_{\rm mod}{=}500\rm kHz$ (Both chopper on and off; low-bandwidth and high-bandwidth cases are shown for comparison) (b) Input-referred noise current spectral density when $f_{\rm mod}{=}1\rm MHz$ , $10\rm MHz$ and $40\rm MHz$                 | . 29 |

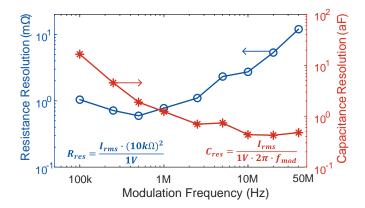

| 2.15   | Effective resistance and capacitance measurement resolution across modulation frequency calculated from the input-referred rms current noise over 200 Hz bandwidth, when input voltage amplitude is $1\mathrm{V.}$ .                                                                                       | . 30 |

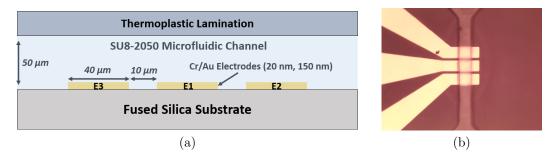

| 2.16   | (a) Illustrated cross-section and (b) top view micrograph of fabricated microfluidic flow channel with 3-electrode sensor used in experiments.                                                                                                                                                             | . 31 |

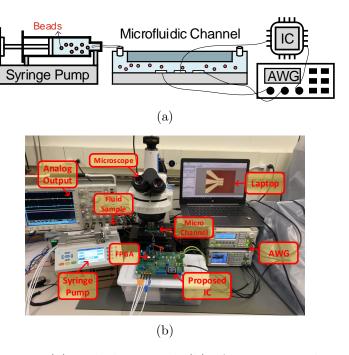

| 2.17   | Illustration (a) and photograph (b) of experimental test setup for evaluating the impedance sensor IC with a microfluidic flow cell, including electrical, optical, and fluidic interfaces                                                                                                                 | . 32 |

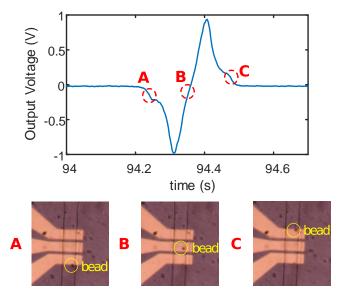

| 2.18   | Measured voltage transient signal real component (I-channel) shown above real-time microscope images taken when a single $10\mu m$ bead is transiting across the electrodes.                                                                                                                               | . 34 |

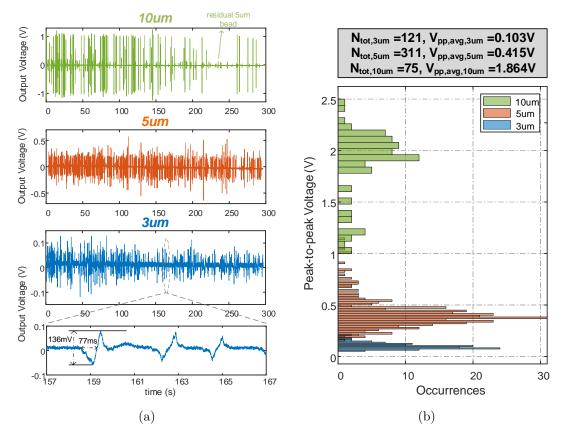

| 2.19   | (a) Measured 5-minute transient waveforms using the impedance-based sensor IC and a custom microfludic flow cell for flowing solutions of 3 µm, 5 µm, and 10 µm polymer microbeads, and (b) the peak-to-peak voltage histogram of each single-cell event, demonstrating clear separation by particle size. | . 35 |

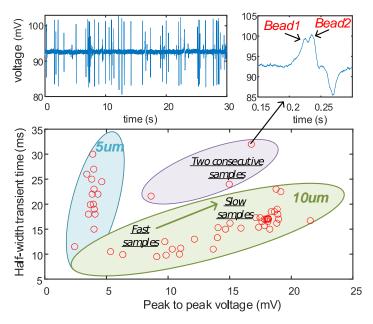

| 2.20   | Measured voltage output $V_{\rm pp}$ versus half-width time; data extracted from 30s recording of $5/10\mu{\rm m}$ bead mixture                                                                                                                                                                            |      |

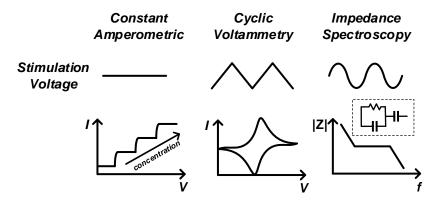

| 3.1    | Stimulation electrode voltage and resulting response of three electro-<br>analytical methods with amperometric readout                                                                                                                                                                                     | . 41 |

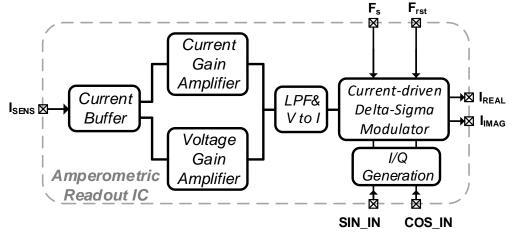

| 3.2    | Architectural level block diagram                                                                                                                                                                                                                                                                          | . 42 |

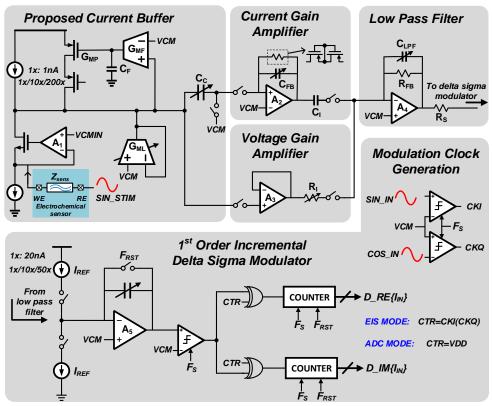

| 3.3    | Block diagram of proposed amperometric sensing interface readout IC for electrochemical sensors                                                                                                                                                                                                            | . 43 |

| Figure |                                                                                                                                                                                                | Page |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

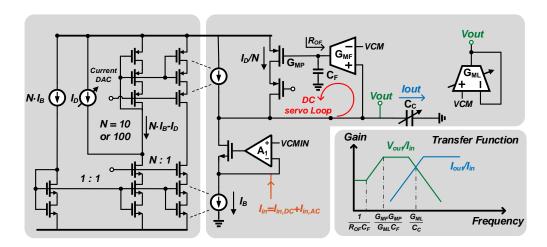

| 3.4    | Schematic of proposed current buffer with current and voltage transfer function                                                                                                                | 44   |

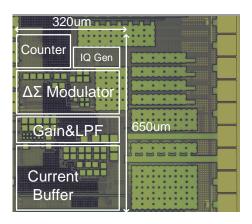

| 3.5    | Die photo of fabricated EIS and amperometric measurement IC                                                                                                                                    | 48   |

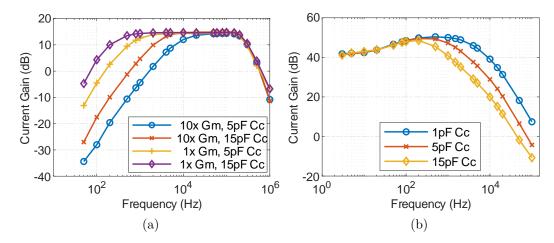

| 3.6    | Measured tunable current gain transfer function for (a) current mode and (b) voltage mode for different values of $G_m$ and $C_C$                                                              | 49   |

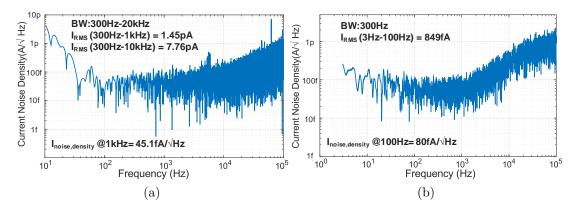

| 3.7    | Input-referred current noise density of proposed front end circuit in (a) current mode (b) voltage mode for 1 nA biasing                                                                       | 50   |

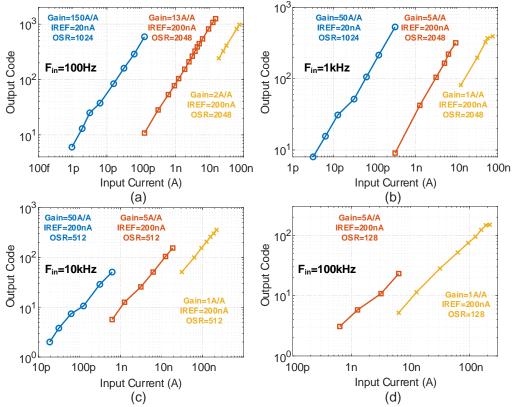

| 3.8    | Linearity of output code versus input sinusoid amplitude for (a) voltage mode at $100\mathrm{Hz}$ , and current mode at (b) $1\mathrm{kHz}$ , (c) $10\mathrm{kHz}$ , and (d) $100\mathrm{kHz}$ | 51   |

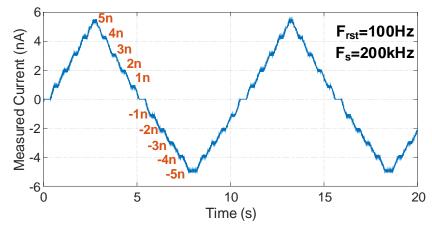

| 3.9    | Transient waveform of measured ADC output with a swept, quasistatic DC current input using a source meter (Keithley 2450)                                                                      | 52   |

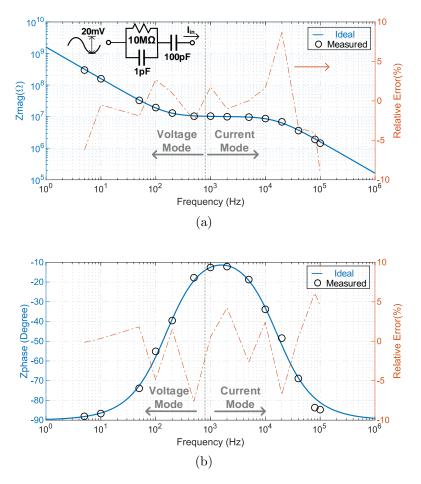

| 3.10   | Impedance spectroscopy measurements using impedance model cell: (a) magnitude response and (b) phase response, both with relative error                                                        | 53   |

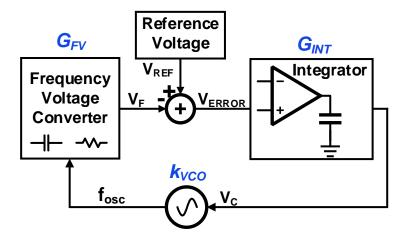

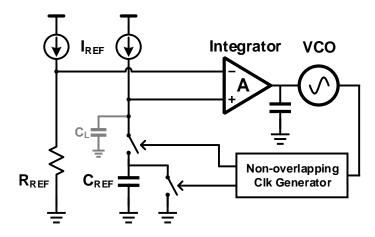

| 4.1    | Block diagram showing the working principle of the frequency-locked-loop                                                                                                                       | 56   |

| 4.2    | Current-driven FVC in FLL system                                                                                                                                                               | 58   |

| 4.3    | Wheatstone Bridge FVC in FLL system                                                                                                                                                            | 59   |

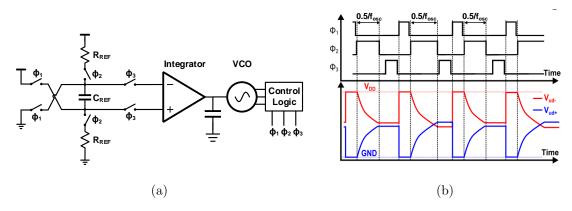

| 4.4    | (a)Schematic of the RC charging FVC, and (b) its operating timing diagram from [5]                                                                                                             | 60   |

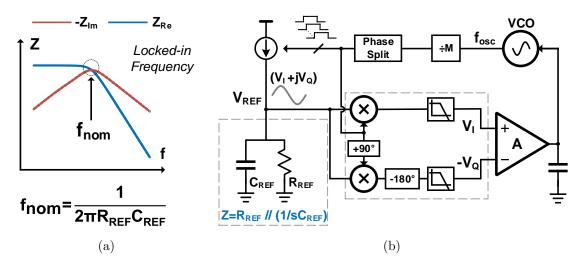

| 4.5    | (a) Magnitude of the real and imaginary impedance of a RC pair (shown in log-scale), and (b) block diagram of FLL using proposed FVC                                                           | 62   |

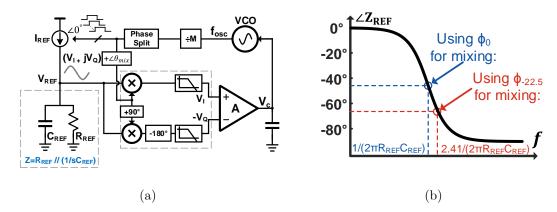

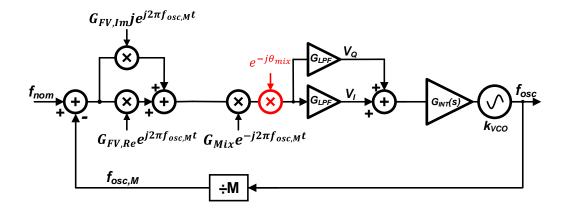

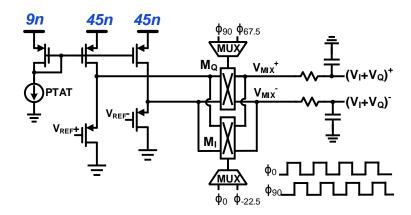

| 4.6    | (a) Block diagram of impedance IQ-balanced FLL with alternative phase mixing. (b) Frequency reconfigurability with different mixing phase                                                      | 66   |

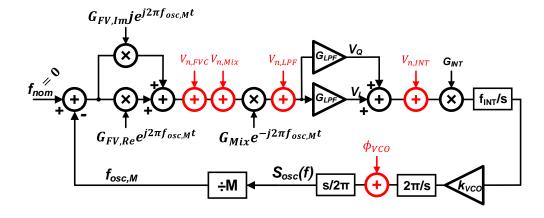

| 4.7    | Linear system model of impedance IQ-balanced FLL                                                                                                                                               | 68   |

| F'igure | :                                                                                                                                                             | Page        |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

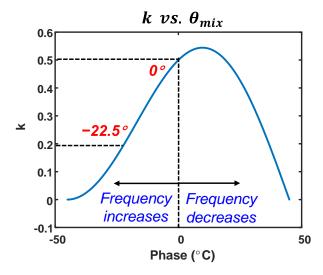

| 4.8     | k versus different mixing phase $\ldots \ldots \ldots \ldots \ldots$                                                                                          | 70          |

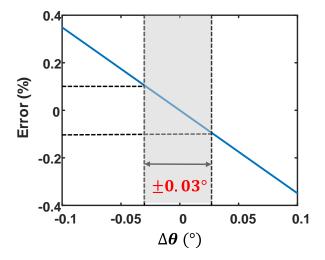

| 4.9     | frequency error with phase variation                                                                                                                          | 71          |

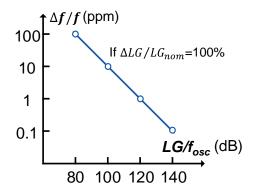

| 4.10    | $f_{osc}$ second-order error by $LG$ at different $LG/f_{osc}$ cases                                                                                          | 72          |

| 4.11    | Linearized noise model of proposed FLL                                                                                                                        | 73          |

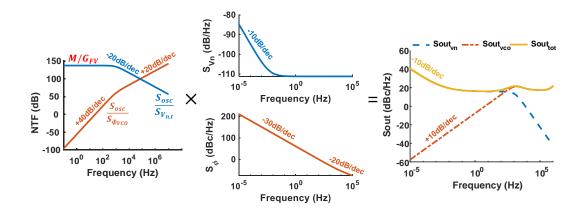

| 4.12    | Noise transfer function plots according to (4.25) and (4.26); PSD of modeled voltage noise and phase noise; PSD of output frequency fluc-                     | <del></del> |

|         | tuation                                                                                                                                                       | 74          |

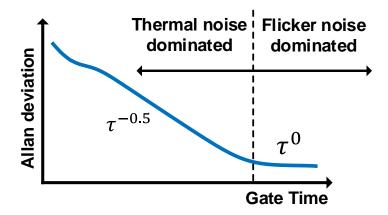

| 4.13    | All<br>an deviation (log-log) plot at gate time $\tau.$                                                                                                       | 75          |

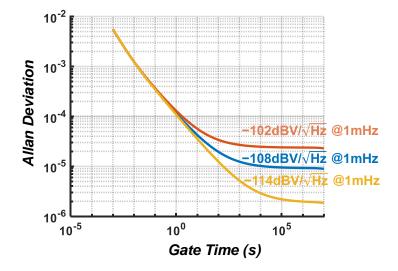

| 4.14    | All<br>an Deviation with different integrator noise                                                                                                           | 76          |

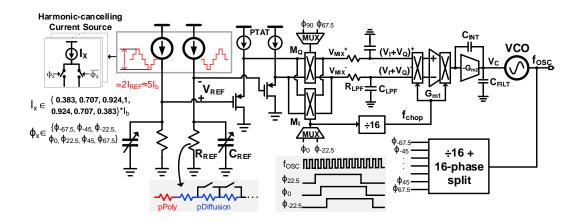

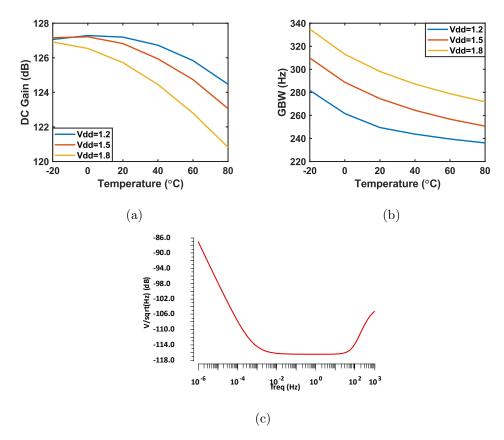

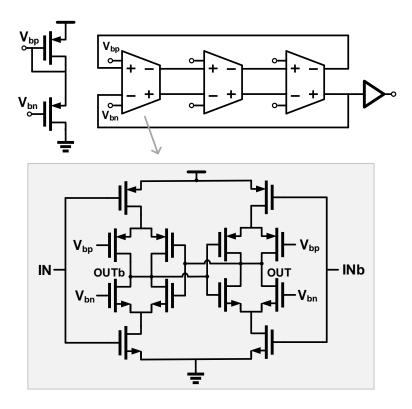

| 4.15    | Schematic of impedance IQ-balanced FLL                                                                                                                        | 77          |

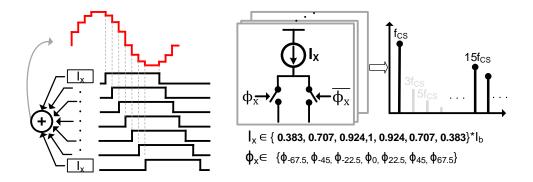

| 4.16    | Harmonic-cancelled step-wise sinusoid waveform generation using phase-shifted square wave                                                                     | -<br>78     |

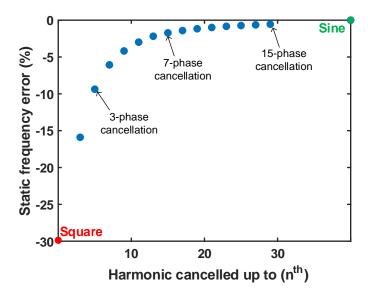

| 4.17    | Static frequency error when $ Z_{Re}  =  Z_{Im} $ holds by excitation with different harmonic cancellation                                                    | 79          |

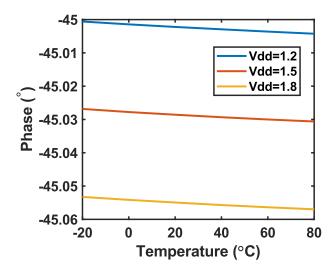

| 4.18    | Output phase variation of current source over temperature and supply voltage                                                                                  | 80          |

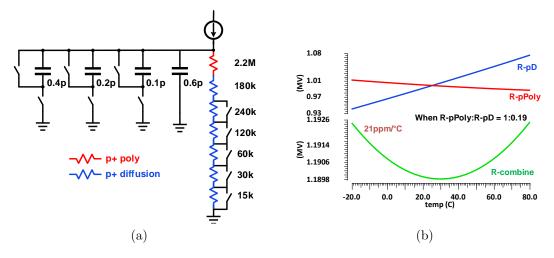

| 4.19    | (a) Schematic of reference capacitance and reference resistance. (b) Simulation results of TC compensation between $R_{poly}$ and $R_{diff}$                  | 81          |

| 4.20    | Parasitic capacitance in resistor implementation causes extra phase shift of $\mathbf{Z}_{REF}$ , limiting FVC maximum achievable frequency                   | 82          |

| 4.21    | Schematic of IQ-Balanced mixer including source-follower, two NRZ passive mixers, and low-pass-filer                                                          | 83          |

| 4.22    | Simulated transient voltage waveform of the key nodes in mixer during frequency locking period                                                                | 84          |

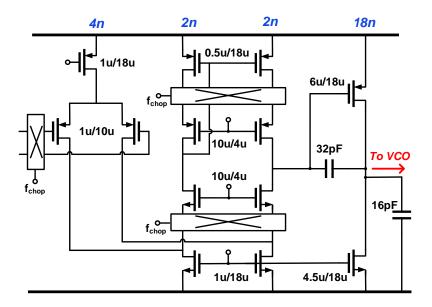

| 4.23    | Schematic of integrator amplifier                                                                                                                             | 85          |

| 4.24    | Simulation results of (a) DC gain and (b) gain-bandwidth-product (GBW) variation over temperature and supply voltage. (c) Noise simulation of the integrator. | 86          |

| <u>Figure</u> |                                                                                                                      | <u>Page</u> |

|---------------|----------------------------------------------------------------------------------------------------------------------|-------------|

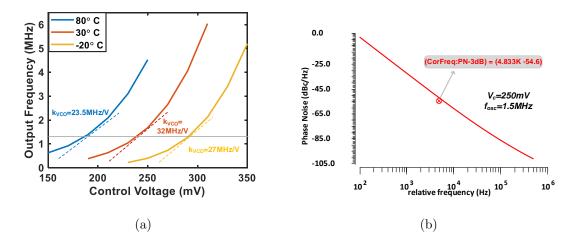

| 4.25          | Schematic of voltage-controlled oscillator                                                                           | 87          |

| 4.26          | (a) VCO output frequency versus control voltage across various temperature. (b) Simulation result of VCO phase noise | 88          |

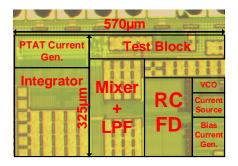

| 4.27          | Die photo of proposed FLL prototype                                                                                  | 89          |

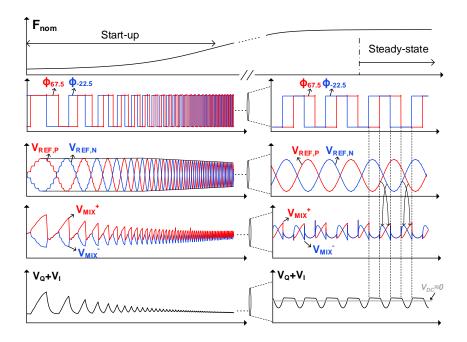

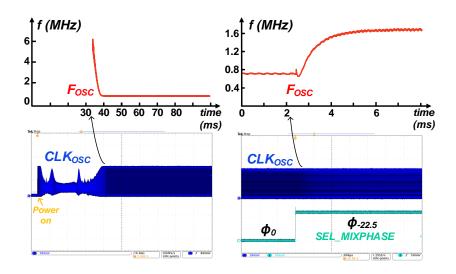

| 4.28          | Transient waveform of proposed FLL                                                                                   | 89          |

| 4.29          | Frequency error over (a) temperature and (b) supply voltage for both $\phi_0$ and $\phi_{-22.5}$ mixing phase        | 90          |

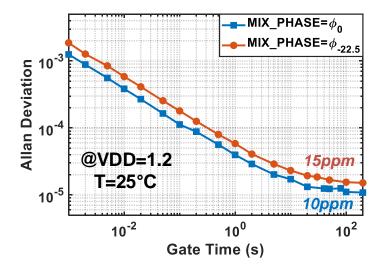

| 4.30          | All<br>an deviation with gate time for both $\phi_0$ and<br>$\phi_{-22.5}$ mixing phase                              | 91          |

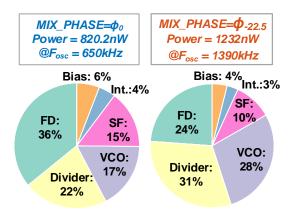

| 4.31          | Power break down of FLL operating at 1.2 V for $\phi_0$ and $\phi_{-22.5}$ mixing phase                              | 91          |

# LIST OF TABLES

| <u>Table</u> |                                                         | $\underline{P}$ | age |

|--------------|---------------------------------------------------------|-----------------|-----|

| 2.1          | Performance comparison with impedance sensor            | •               | 38  |

| 3.1          | Performance comparison of low current interface IC      | •               | 54  |

| 4.1          | Performance Summary of Current-driven FVC               |                 | 59  |

| 4.2          | Performance Summary of Wheatstone Bridge FVC            | •               | 60  |

| 4.3          | Performance Summary of RC Charging FVC                  |                 | 61  |

| 4.4          | Performance Summary of Proposed Impedance Sensing FVC   | •               | 62  |

| 4.5          | Performance Comparison Between Different FVC topologies |                 | 65  |

| 4.6          | Performance comparison with state-of-art RC oscillators |                 | 92  |

## Chapter 1: Introduction

#### 1.1 Impedance Measurements in Sensors

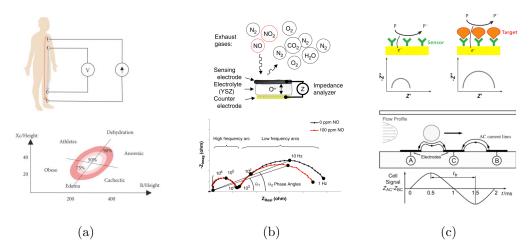

Impedance measurements are increasingly utilized in modern integrated circuit sensing systems, as impedance is the most common electrical signal obtained from sensors, delivering physical, chemical and biomedical signals of interest from different sensor types. Impedance sensing for wide frequencies of interest, broad dynamic range, and various sensor interfaces present numerous challenges, especially for targeted implementation in CMOS for miniaturization, which presents power and area limitations. Fig. 1.1 shows several sensing applications using impedance sensing techniques such as bioimpedance sensing, gas sensing, DNA sensing, and cell sensing. Bioimpedance analysis Fig. 1.1a is a low-cost and noninvasive for body composition measurements and assessment of clinical condition. By accessing the tissue electrical resistance and reactance across the electrodes on the body at different frequency, the body composition can be predicted and analyzed. Gas sensing Fig. 1.1b using impedance spectroscopy is also a popular and well-developed approach, which is attractive to industry and personal use due to its low-cost in production. Electrochemical impedance sensing Fig. 1.1c is also a promising biosensing technique because of its label-free, low-cost and ease of miniaturization.

Alternating-current (AC) impedance sensing technique has its several intrinsic advantages compared with its direct-current (DC) counterpart: 1) AC stimulus over

Figure 1.1: Impedance sensing technique used in (a)bioimepdance sensing [1]; (b)gas sensing [2]; (c) Biosening (DNA, cell) [3], [4]

various frequency can access recatance more than pure resistance information, representing more comprehensive understand in sensor analysis; 2) AC measurement can employ small stimulus amplitude, which is able to preserve the linearity of the sensor, and will not cause heat dissipation with high-DC current; 3) Another important feature for AC impedance measurement is AC operation normally hardly change the characteristics of the electrode, yielding a more stable and predictable measuring environment in long term.

Most of the impedance sensing applications can be classified into two category in terms of how the impedance is accessed and analyzed. The first one is impedance spectroscopy (IS), where impedance of the sensor across the whole interested frequency band are required by sweeping the frequency. This approach is often considered as the most sophisticated and informative because the overall impedance band over frequency can be obtained, however, it requires hardware to be sophisticated as

well, extra post-processing, and sweeping period, which makes it hard for real-time processing. On the other hand, the second approach is fixing the operating frequency at one interested frequency and sensing the change in electrical signal. This is approach is low-cost and easy for circuit miniaturization and multiplexing. However, it is relatively low accuracy and requires calibrating and analysis to select a reliable operating frequency. Both approaches are broadly adopted depending on the applications, and an intermediate approach which uses 2-point or 3-point operating frequencies is also favored.

Implementing impedance sensing technique by integrated circuits and building a on-chip impedance sensing systems have numerous challenges in terms of sensitivity, accuracy, dynamic range, frequency range, interface-compatibility, multi-channel extension, power and chip area based on specific applications and design limitations. This thesis will analyze some of the above-mentioned challenges and propose particular system and circuit techniques to overcome them.

## 1.2 Scope of the Thesis

In this thesis, three projects related to impedance sensing techniques are presented.

In Chapter 2, a low-power, impedance-based cytometer architecture is presented for cell analysis applications. By adopting a 3-electrode layout and a differential excitation voltage, baseline current is cancelled before the sensor front-end to achieve high sensitivity. The difference current is sensed by a closed-loop, impedance sensing circuit architecture, which employs a hybrid-RC feedback network to overcome the SNR degradation seen over a wide operating frequency range when using purely capacitive feedback; this is especially critical when a microfluidic flow channel is used as the input sensing element, which includes a resistive component. The effect of phase shift on the closed-loop system gain and noise performance are analyzed in detail, and optimization strategies are presented. The impedance sensor was fabricated in a 0.18  $\mu$ m CMOS process and consumes 9.7 mW with an operating frequency from 50 kHz to 40 MHz and provides adjustable bandwidth. Measurements demonstrate that the impedance sensor achieves 6 pA<sub>rms</sub> input-referred noise over 200 Hz bandwidth at 0.5 MHz modulation frequency. Combined with a microfluidic flow cell, measured results using this source-differential measurement approach are presented using both monodisperse and polydisperse sample solutions and demonstrate single-cell resolution, detecting 3  $\mu$ m diameter particles in solution with 22 dB SNR.

Chapter 3 presents a low-noise, front-end sensor IC that includes both AC impedance spectroscopy and DC amperometric measurement capabilities for electrochemical and biosensor applications. A common-gate current buffer topology is proposed that supports both current-mode and voltage-mode sensor signals to allow an input frequency range from DC to  $100\,\mathrm{kHz}$ . Low-noise operation is achieved across a wide input frequency range using tunable high-pass and low-pass frequency response. In addition, an incremental delta-sigma modulator with embedded frequency response analysis serves as both on-chip impedance analyzer and current-driven analog-to-digital converter. Implemented using a  $0.18\,\mu\mathrm{m}$  CMOS process, this work achieves  $45\,\mathrm{fA}/\sqrt{\mathrm{Hz}}$  input current noise density at  $1\,\mathrm{kHz}$ . Input dynamic range exceeding

80 dB is achieved up to 10 kHz bandwidth, with a maximum of 104 dB dynamic range at 10 Hz.

In Chapter 4, although particular impedance sensor is not presented, the impedance sensing technique has been applied into the low-power RC frequency generator, and a novel impedance IQ-balanced frequency locked-loop (FLL) is proposed and demonstrated. With alternative phase mixing technique, the proposed FLL achieves 1.26 pJ/Cycle energy efficiency with 25.4 ppm/°C temperature coefficient and 0.27%/V line sensitivity at 650 kHz. A excellent long-term frequency stability with measured 16 ppm Alan deviation is also demonstrated for this work.

# Chapter 2: A Impedance Sensor for Source-Differential Flow Cytometry

#### 2.1 Introduction

Flow cytometry plays a vital role in microbiology and medical diagnostics for counting and classifying heterogeneous cell populations, as well as for measuring single-cell physical properties. Conventional optical flow cytometers provide high throughput counting and cell subtyping, but complex optics drive cost and size for the instruments [6]. Moreover, fluorescent labels are required for some subtyping and downstream cell sorting, including fluorescence activated cell sorting (FACS), which further limits viability for point-of-care (POC) applications. Purely electrical Coulter-counters eliminate optical components, but these have a limited ability to assess cell structure, composition, or type. For a variety of clinical diagnostic applications, there remains a critical need for a miniaturized and label-free flow cytometer.

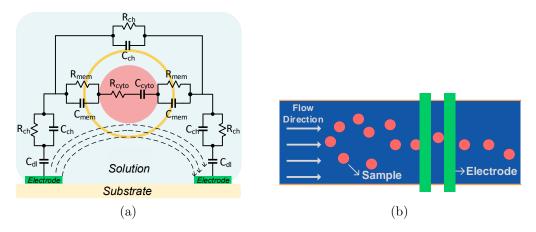

Impedance spectroscopy (IS) can be used to characterize the dielectric properties of cells in solution, providing details of cell membrane structure and cell composition (Fig. 2.1) [7,8]. Combining advances in microfluidic systems with impedance spectroscopy techniques has enabled lab-on-chip flow cytometers with single-cell resolution; prior work has successfully demonstrated micrometer-scale particle detection using microfluidics-based devices and a commercial bench-top impedance analyzer [4,9–12]. Further enhancing the limit of detection (LOD) and throughput for

Figure 2.1: (a) Equivalent circuit model of a single cell in solution, and (b) top-down illustration of IS electrodes in a microfluidic flow channel.

such systems motivates the integration of sensor and sensing electronics into a single chip, which also enables low-noise and multi-channel operation.

General impedance spectroscopy has been demonstrated previously using complementary metal-oxide-semiconductor (CMOS) silicon integrated circuits, primarily for measuring electrochemical reactions at electrode-electrolyte interface [13–16]. These applications typically require operation from 1 Hz to 1 MHz, where a full-span frequency sweep is required to analyze the electrochemical behavior, and thus the dynamic range specification of the IS instrument is essential. Impedance-based flow cytometry, in comparison, requires real-time measurement and is typically performed at one or two fixed operating frequencies to analyze specific cell physical properties in real time. In this case, noise performance is more critical, as the cell dimension is small compared to the channel.

For impedance-based cell analysis, megahertz operating frequency minimizes doublelayer capacitor impedance ( $C_{\rm dl} \approx 100\,{\rm pF}$ ) to enhance SNR; the properties of channel

Figure 2.2: (a) Source-differential impedance cytometry topology, (b) equivalent circuit model of source-differential sensing scheme, and (c) frequency response of sensing current versus baseline current magnitude for source-differential sensing scheme.

resistance ( $R_{\rm ch}$ ), cell membrane capacitance ( $C_{\rm mem}$ ), cell cytoplasm resistance ( $R_{\rm cyto}$ ) and cell cytoplasm capacitance ( $C_{\rm cyto}$ ) can be accessed and analyzed at frequency of 0.5-5 MHz, 5-10 MHz, 10-100 MHz and >100 MHz, respectively [4]. It is important to note that the physical size of the cell primarily induces the  $R_{\rm ch}$  variation, similar to current exclusion in Coulter counting. A closed-loop modulation/demodulation architecture for generalized capacitive sensing applications was introduced in [17] that achieves sub-aF capacitance resolution operating up to 150 MHz. However, this approach uses purely capacitive feedback, which limits closed-loop gain as well as SNR performance for cytometry applications specifically, where microfluidic channel resistance,  $R_{\rm ch}$  (Fig. 2.1a), remains dominant in the megahertz range.

In this paper, we present a modulation/demodulation impedance sensor architecture on chip with hybrid feedback that maintains closed-loop gain across cytometry-relevant operating frequencies with low (<10 mW) power consumption. The impact of loop-gain phase shift on system gain and noise is analyzed and optimized. Following electrical characterization of the architecture implemented in a 0.18 µm CMOS process, the impedance sensor is experimentally characterized using a custom mi-

crofluidic flow cell to demonstrate real-time flow cytometry. A source-differential electrode layout and impedance sensing scheme cancels out baseline current to increase sensitivity. The system demonstrates detection of 3 µm beads and separation of polydisperse beads in solution, demonstrating single-cell resolution under flow conditions.

## 2.2 Hybrid-feedback IS for Source-Differential Impedance Cytometry

## 2.2.1 Source-differential sensing scheme

Source-differential impedance sensing, illustrated in Fig. 2.2a, is commonly used to measure small changes in a large bulk impedance [18]. This is a particularly relevant approach for impedance based cytometry, where cells are typically small compared to the overall microfluidic channel volume. As is shown in Fig. 2.2a, for source-differential readout, anti-phase AC excitation signals are applied to the outer electrodes  $E_{\rm A}$  and  $E_{\rm B}$ , and only sensing current  $\Delta I$  is incident on the middle electrode. This source-differential measurement is advantageous in comparison to single-ended and single-source differential approaches, where without baseline current cancellation, the current output superimposes small cell-induced changes with a large baseline current, and hence a majority of the input dynamic range of the downstream measurement electronics is used for the baseline channel signal, limiting usable gain and achievable measurement sensitivity for the small cell signal.

An equivalent circuit model is shown in Fig. 2.2b, where complex channel impedance and cell impedance are lumped into a parallel RC model for simplicity. If the

impedance between two electrode pairs without a cell present are perfectly matched, the baseline current will flow between each excitation source, with zero current flowing into the sensing electronics. As a cell crosses either electrode pair, the corresponding change  $\Delta C$  in channel capacitance,  $C_{\rm ch}$ , and and  $\Delta R$  in channel resistance,  $R_{\rm ch}$ , yields unbalanced channel pairs, inducing a small difference current at the readout electronics, while balanced baseline current is neutralized.

A current magnitude frequency response of the source-differential equivalent model is shown in Fig. 2.2c, assuming 10 ppm change in both  $R_{\rm ch}$  and  $C_{\rm ch}$ . With baseline current cancelled, the source-differential sensing scheme achieves a 100 dB relaxation in required analog front-end (AFE) dynamic range. In addition to relaxing input dynamic range, additional benefits are gained: correlated noise and fluctuation from the excitation source will be mitigated, two-wire input for measurement electronics is replaced by a single wire, which reduces circuit and system complexity and increases scalability for multichannel applications.

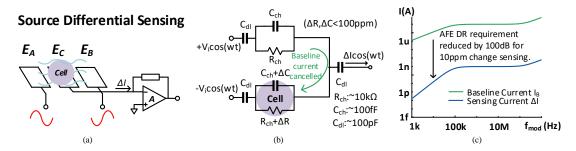

# 2.2.2 Hybrid-feedback Impedance Sensor

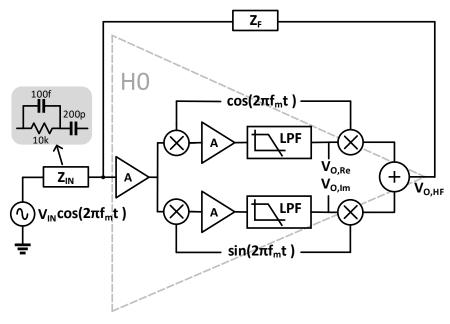

A closed-loop impedance sensing architecture suitable for high frequency operation was used, and a high-level block-diagram is illustrated in Fig. 2.3. Unlike a more conventional coherent detection scheme that uses a transimpedance amplifier (TIA), down-converter, and low-pass filter, this architecture integrates down-conversion and up-conversion into the feedback loop, which alleviates the gain-bandwidth limitation of the conventional TIA-first topology [17].

Figure 2.3: Generalized circuit model for a modulation/demodulation impedance measurement architecture with an impedance model cell at the input.

If we treat the down-converter, low-pass filter, and up-converter chain as a composed amplifier H0, the closed-loop gain from the input,  $V_{\text{IN}}$ , to the high-frequency output,  $V_{\text{O,HF}}$ , can be obtained as

$$A_{\rm CL} = \frac{V_{\rm O,HF}}{V_{\rm IN}} = \frac{Z_{\rm F}}{Z_{\rm IN}} \frac{LG}{1 + LG}$$

(2.1)

where LG is the loop gain of the feedback system. If LG is large enough at the modulation frequency, the output of the impedance sensor  $V_{\rm O,HF}$ , as well as its low-frequency baseband component  $V_{\rm O}$ , is purely dependent on  $Z_{\rm IN}$  if  $V_{\rm IN}$  and  $Z_{\rm F}$  are known in advance. Assuming the gain of up-converter is unity, the real and imaginary components of  $Z_{\rm IN}$  can be calculated as follows, if modulation clock  $cos(2\pi f_{\rm m}t)$  is in

phase with the excitation source,

$$\text{Re}\{Z_{\text{IN}}\} = -\frac{V_{\text{IN}} \cdot Z_{\text{F}}}{V_{\text{O,Re}}}, \quad \text{Im}\{Z_{\text{IN}}\} = \frac{V_{\text{IN}} \cdot Z_{\text{F}}}{V_{\text{O,Im}}}$$

(2.2)

where  $V_{O,R}$  and  $V_{O,I}$  are the impedance sensor voltage outputs of the real and imaginary baseband components.

In [17], the feedback element  $Z_{\rm F}$  is realized solely by a capacitor (100 fF), which is suitable for a purely capacitive sensing elements at  $Z_{\rm IN}$ . However, the cell model given in Fig. 2.3 ( $Z_{\rm IN}$ ) is more typical for cytometry, where the resistive impedance component is dominant in the megahertz range; as such, the closed-loop gain  $A_{\rm CL}$  will decrease as frequency increases, as shown in Fig. 2.4a. This decrease of  $A_{\rm CL}$  leads to a degradation of the impedance sensor noise performance, where signal-to-noise ratio (SNR) at the output of the impedance sensor is given as

$$SNR_{out} = \frac{V_{IN}}{\overline{v_{n,tot}} \cdot BW_{EN}} \frac{A_{CL}}{1 + A_{CL}}$$

(2.3)

if only noise from H0 is considered, where  $\overline{v_{\rm n,tot}}$  is the input-referred noise density of H0 and  $BW_{\rm EN}$  is the equivalent noise bandwidth of the impedance sensor. As  $A_{\rm CL}$  is no longer much greater than unity at high frequency in this case due to the resistive impedance component, the output SNR will degrade based on the series capacitance ratio between  $Z_{\rm IN}$  and  $Z_{\rm F}$ . As the series capacitance for a micron-size particle is smaller than  $100\,{\rm fF}$  [19], in order to avoid SNR degradation at high frequency using purely capacitive feedback, one must implement  $C_{\rm f}$  <10 fF, which is impractical due to minimum unit capacitors in CMOS processes as well as parasitic capacitances.

Figure 2.4: Closed-loop gain  $A_{\rm CL}$  frequency response when feedback element is (a) capacitor (b) capacitor series with resistor, assuming loop gain is sufficient.

In this work, to overcome the limitations of capacitive feedback for resistive sensor inputs, a resistor  $R_{\rm F}$  is added in series with  $C_{\rm F}$  in the feedback loop  $(Z_{\rm F})$  to maintain closed-loop gain at high frequency. High gain across frequency is necessary to leverage the benefits afforded by source-differential impedance sensing; as described in Sec. 2.2.1, an important feature of source-differential sensing is the small input difference current following baseline cancellation, which enables a high-gain downstream measurement system without input saturation due to baseline current. The resulting frequency response is shown in Fig. 2.4b, where  $R_{\rm f} = 10\,{\rm M}\Omega$ . Due to this always-high closed-loop gain, the thermal noise introduced by adding  $R_{\rm f}$  is mitigated and has negligible effect on output SNR.

#### 2.3 System Analysis

#### 2.3.1 Loop dynamic analysis

A system loop dynamic analysis is essential to translate system specifications such as bandwidth and noise into individual block specifications and design targets. In order to simplify this analysis, we assume that  $H_{LPF}$  is the transfer function of the low-pass filter (DC gain of low-pass filter is assumed to be unity), and the remaining combined gain from the low-noise pre-amplifier, down-converter, intermediate gain stage, and up-converter are lumped into  $A_0(s)$ . The loop gain of the feedback system can then be written as

$$LG(s) \approx A_0(s)\beta(s)H_{LPF}(s-jw_m) = \frac{A_0(s)\beta(s)}{1 + \frac{s-jw_m}{p_{LPF}}}$$

(2.4)

where  $w_{\rm m}$  is the modulation frequency in radians,  $\beta({\rm s})$  is the feedback factor based on  $Z_{\rm IN}$  and  $Z_{\rm F}$ , and  $p_{\rm LPF}$  is the frequency of the low-pass pole generated by the integrator. Note that the  $H_{\rm LPF}(s+jw_{\rm m})$  component arising from modulation is omitted due to its negligible effect on LG at frequencies of interest. Therefore, the closed-loop gain  $A_{\rm CL}$  can be obtained as an extension of (2.1),

$$A_{\rm CL}(s) \approx \frac{Z_{\rm F}(s)}{Z_{\rm IN}(s)} \frac{1}{1 + \frac{s - jw_{\rm m}}{p_{\rm LPF}|LG_0(s)|e^{j\theta}}}$$

(2.5)

where  $LG_0(s)$  is the loop gain product  $A_0(s)\beta(s)$  without  $H_{LPF}$  shaping, and  $\theta$  is the phase shift of  $LG_0$  at each frequency.

In the ideal case where all blocks have infinite bandwidth,  $LG_0(s)$  exhibits purely

DC behavior with DC gain of  $LG_{0,DC}$ , and no phase shift is introduced. If  $Z_{IN}(s)$  and  $Z_{F}(s)$  are also frequency-independent at bands of interest, maximum  $A_{CL}$  is obtained at  $w_{m}$  with a 3-dB bandwidth (BW) calculated as

$$BW = p_{\text{LPF}} LG_{0,\text{DC}}.$$

(2.6)

However, in practice, especially for high modulation frequencies,  $LG_0(s)$  exhibits a phase shift due to finite high-pass and low-pass cut-off frequencies in the signal chain, which leads to a scenario where

$$\left| 1 + \frac{j(w_{c} - w_{m})}{p_{LPF}|LG_{0}(jw_{c})|e^{j\theta}} \right| < 1, \tag{2.7}$$

increasing the peak closed-loop gain  $A_{\rm CL}$  greater than  $Z_{\rm F}/Z_{\rm IN}$  and shifting the peak gain center frequency  $w_{\rm c}$  away from  $w_{\rm m}$ .

A system model was implemented in MATLAB to illustrate this behavior. As shown in Fig. 2.5a, the simulated closed-loop gain frequency response varies for different loop gain phase shifts. The simulation is performed for modulation frequency  $f_{\text{mod}}=1\,\text{MHz}$  and assuming a feedback factor  $\beta$  of 1/1000.

If  $LG_0$  exhibits no phase shift  $(\theta = 0)$ , the center frequency  $w_c$  remains at modulation frequency  $w_{\text{mod}}$  with peak gain at  $w_{\text{mod}}$  ( $w_{\text{mod}} = 2\pi f_{\text{mod}}$ ). If  $\theta$  is positive (e.g. a zero near  $f_{\text{mod}}$ ),  $w_c$  moves downward in frequency, and effective bandwidth for  $A_{\text{CL}}$  is reduced. If  $\theta$  is negative (e.g. pole near  $f_{\text{mod}}$ ),  $w_c$  moves upward in frequency and bandwidth increases slightly. Fig. 2.5b describes the detailed relationship between center frequency offset relative to  $f_{\text{mod}}$ , as well as effective 3 dB bandwidth as

Figure 2.5: (a) Frequency response of system closed-loop gain,  $A_{\rm CL}$ , at different  $LG_0$  phase shift  $\theta$  conditions when  $f_{\rm mod}=1\,{\rm MHz}$ ; (b) center frequency shift and effective 3-dB bandwidth at different loop-gain phase shifts.

a function of  $LG_0$  phase shift,  $\theta$ .

It is important to note that the signal gain is fixed by the closed-loop gain  $A_{\rm CL}$  at  $f_{\rm mod}$ , which is equivalent to baseband output DC gain following demodulation; this remains unaltered for non-zero  $\theta$ . However, system bandwidth and noise gain are determined by  $\theta$ , requiring specific design optimization for  $\theta$  anticipated at a certain  $f_{\rm mod}$ ; this is discussed in detail in the following section.

The effect can also be seen in (2.3), where  $A_{\rm CL}$  is fixed and independent of  $\theta$  (e.g. 60 dB), but the effective noise bandwidth ( $BW_{\rm EN}$ ) changes as a function of  $\theta$  (Fig. 2.5).

## 2.3.2 Noise analysis

The noise performance of the impedance sensor is critical for cytometry applications, where it directly determines the limit of detection (LOD). Comprehensive noise analysis of transimpedance amplifiers for low-current measurement applications has been discussed in previous literature [20,21], but without considering the amplifier non-idealities. For the closed-loop architecture shown in Fig. 2.3, if we assume LGis sufficiently high and  $R_f$  dominantes  $Z_F$  at frequencies of interest, the closed-loop noise gain and input-referred noise current density can be derived as

$$\overline{i_{\rm n}^2} \approx \frac{\overline{v_{\rm n,tot}^2} \cdot |A_{\rm CL}(s)|^2 + 4kTR_{\rm f}}{R_{\rm f}^2}$$

$$\approx \overline{v_{\rm n,tot}^2} \left| \frac{1}{Z_{\rm IN}} \right|^2 \left| \frac{1}{1 + \frac{s - jw_{\rm m}}{p_{\rm int}|LG_0(s)|e^{j\theta}}} \right|^2 + \frac{4kT}{R_{\rm f}} \tag{2.8}$$

where  $Z_{\text{IN}}$  is the impedance of the input sensing element, typically dominated by input parasitic capacitance if the input is floating, and  $\overline{v_{\text{n,tot}}^2}$  is the input-referred noise voltage density of H0. Note  $\overline{i_n^2}$  in (2.8) is the input-referred noise current of the high frequency output  $V_{\text{O,HF}}$ , which is treated as equivalent to its demodulated output counterpart in our analysis assuming unity-gain of the up-converter.

Equation (2.8) shows that the input-referred noise density is shaped by the bandpass characteristics of the signal chain, which are in turn dependent on  $\theta$ . As such, loop gain phase shift  $\theta$  not only causes bandwidth deviation (Fig. 2.5), it also directly impacts the SNR of impedance sensor, as noise bandwidth varies even with unaltered signal gain. Additionally, peak gain of  $A_{CL}$  will vary as well, resulting in a change

Figure 2.6: Normalized input-referred noise current spectral density and noise bandwidth versus  $LG_0$  phase shift  $\theta$  when  $f_{\text{mod}}=1 \text{ MHz}$ . in integrated noise.

To better illustrate this tradeoff, one can analyze the noise density as a function of  $\theta$  rather than integrated noise, as bandwidth changes with phase shift as well. In Fig. 2.6, a simulation shows how loop gain phase shift  $\theta$  effects the equivalent input-referred noise current spectral density and bandwidth; both are normalized to  $\theta = 0$  condition. The best noise performance is obtained with  $\theta = 0$ , as expected. Of note, for positive  $\theta$ , the noise bandwidth will decrease faster than the noise density increases, which provides a design opportunity to trade noise density for overall noise if a narrow bandwidth is difficult to implement. For instance, a +30° loop gain phase shift introduces a 1.17X increase in current spectral density and 3X reduction in bandwidth, leading to an effective 1.5X reduction in rms noise.

Figure 2.7: High-level source-differential architecture of on-chip hybrid-feedback impedance sensor and off-chip microfluidic flow channel.

## 2.4 Circuit Implementation

# 2.4.1 System overview

Fig. 2.7 depicts the high-level architecture of the CMOS-integrated impedance sensor readout electronics, as well as a microfluidic flow cell using a source-differential excitation scheme. The impedance sensor loop consists of a low-noise input buffer  $(A_1)$ , a quadrature passive down-converter  $(M_1)$  for demodulation, gain stages  $(A_2)$  and integrators  $(I_1)$  in both IQ channels, an quadrature up-converter  $(M_2)$ , and hybrid feedback impedance  $(Z_1)$  including an active feedback resistor in series with capacitor  $C_f$ . An anti-spike low-pass filter is used to remove high-frequency chopper artifacts, and modulation clock and chopping clock are provided externally.

As  $V_R$  and  $V_I$  are the extracted baseband real and imaginary voltage components, input current components are derived as

$$I_{\text{in,R(I)}} = V_{\text{R(I)}} / (R_{\text{f}} + \frac{1}{2\pi f C_{\text{f}}}).$$

(2.9)

Note that (2.9) assumes zero phase shift in the loop at  $f_{\text{mod}}$ , otherwise  $I_{\text{in,R(I)}}$  should be calibrated by the phase shift, while magnitude remains the same. Any DC offset or harmonics generated by  $f_{\text{mod}}$  and  $f_{\text{chop}}$  will remain in the loop and be amplified until reaching the low-pass integrator, which may saturate certain stages and limit the dynamic range of the loop [17]. As this design employs a square-wave modulation source and does not include a dedicated bandpass filter around the modulation frequency, this issue must be addressed. Here, a current-driven passive down converter is adopted to enhance the dynamic range, and an active-feedback resistor is used to achieve high impedance (up to  $10 \, \text{M}\Omega$ ) over a wide frequency range, without attenuation due to parasitic capacitance.

The noise performance of the impedance sensor can be obtained from (2.8), where  $\overline{v_{n,\text{tot}}^2}$  referred to the input of  $A_1$  can be approximated as

$$\overline{v_{\text{n,tot}}^2} \approx \overline{v_{\text{n,A1}}^2} + \overline{v_{\text{n,M1}}^2} + \frac{2\overline{v_{\text{n,A2}}^2}}{G_{\text{A1}}^2 G_{\text{M1}}^2} + \frac{2\overline{v_{\text{n,A2}}^2}}{G_{\text{A1}}^2 G_{\text{M1}}^2} + \frac{2\overline{v_{\text{n,I1}}^2}}{G_{\text{A1}}^2 G_{\text{A2}}^2} + G_{\text{M2}}^2 (\frac{Z_{\text{IN}}}{Z_{\text{IN}} + Z_{\text{F}}})^2 \overline{v_{\text{n,M2}}^2}$$

(2.10)

where  $\overline{v_{n,A1}^2}$ ,  $\overline{v_{n,M1}^2}$ ,  $\overline{v_{n,A2}^2}$ ,  $\overline{v_{n,II}^2}$ ,  $\overline{v_{n,M2}^2}$  are the equivalent input voltage noise spectral density of  $A_1$ ,  $M_1$ ,  $A_2$ ,  $I_1$ ,  $M_2$  and  $Z_1$ , referred to input modulation frequency. The

noise contribution of the feedback impedance can be treated as the equivalent thermal noise of  $R_{\rm f,eq}$ , which is included in (2.8). From (2.10), the total input-referred noise voltage (2.5 nV/ $\sqrt{\rm Hz}$  from simulation) is mainly dependent on the noise performance of the input low-noise amplifier  $A_1$  (1.9 nV/ $\sqrt{\rm Hz}$ , 1.4 mA) and the second stage down-converters  $M_1$  (5 nV/ $\sqrt{\rm Hz}$ , 0.225 mA) attenuated by  $G_{\rm A1}$ =25. The noise from gain stage  $A_2$  (21 nV/ $\sqrt{\rm Hz}$ , 0.12 mA) and integrator  $I_1$  (557 nV/ $\sqrt{\rm Hz}$ , 0.1 mA) are effectively reduced by the previous gain of  $A_1$  and  $M_1$ . Due to high transimpedance gain provided by the feedback impedance, the noise contribution of up-converter  $M_2$  (450 nV/ $\sqrt{\rm Hz}$ , 2.5 mA) is insignificant when referred to the input. Two chopper sets are utilized to reduced the flicker noise contribution of  $M_1$ ,  $A_2$ , and  $M_2$ . Chopping frequencies range from 75 kHz to 300 kHz based on the modulation frequency  $f_{\rm mod}$ . The flicker noise from input amplifier  $A_1$  and the active feedback resistor are less critical for overall noise performance due to the non-DC signal frequency of interest ( $f_{\rm mod}$ ).

## 2.4.2 Low-noise amplifier and passive down-converter

Fig. 2.8 shows a combined schematic of the low-noise input amplifier  $A_1$  and the capacitive-coupled passive down-converter  $M_1$ . As discussed in the previous section, the noise performance of the impedance sensor is primarily dominated by the  $A_1$ . Therefore, a 1.2 mA bias current is used to reduce the input noise as low as  $1.9 \,\mathrm{nV/yHz}$ . Cascode transistors are added to shield the input virtual ground from subsequent chopping operation. Due to output capacitive-coupling to the next stage,

Figure 2.8: Schematic of low-noise input amplifier and capacitive-coupled current-mode passive down-conversion mixer driven by 25% duty cycle  $f_{\text{mod}}$  (chopper is not shown for simplicity).

a simple resistive CMFB sets the output common mode voltage.  $R_{A1}$  is adjustable for tuning the output resistance,  $R_0$ .

A current-mode passive down-conversion mixer [22] is used, providing multiple advantages: the capacitor  $C_{\rm C}$  decouples any DC offset voltage at the output of  $A_1$  introduced by DC leakage current, and, operating in current mode, the amplifier combined with the mixer has enhanced dynamic range to handle large harmonic components fed back from the up-conversion mixer. A 25% duty-cycle modulation clock is chosen for its superior linearity and noise performance to 50% duty-cycle modulation clock. The modulation clock  $f_{\rm mod}$  is generated using an on-chip flip-flop driven by an external  $2f_{\rm mod}$  clock that is synchronized with the off-chip source-differential excitation source. The combined conversion gain and phase shift including

Figure 2.9: Phase shift coverage of  $A_1$  and  $M_1$  across 50 kHz to 50 MHz for given 50 fF and 15 pF  $C_c$ .

$A_1$  and  $M_1$  at modulation frequency can be respectively derived as

$$A_{\rm LNA+Mixer} = \frac{\sqrt{2}}{\pi} \frac{R_{\rm o}}{\sqrt{Z_{\rm c}^2 + R_{\rm o}^2}} g_{\rm m,A1} R_{\rm BB}$$

(2.11)

$$\theta_{\rm LNA+Mixer} = 45^{\circ} - \tan^{-1}\left(\frac{1}{R_{\rm o}C_{\rm c}\omega_{\rm m}}\right) \tag{2.12}$$

where  $Z_c$  is the equivalent impedance of  $C_c$  at frequency  $\omega_m$ , and  $g_{m,A1}$  is the transconductance of  $A_1$ . As is described in (2.12), a 25% duty cycle clock introduces a  $-45^{\circ}$  phase shift to the loop path, which requires a  $+45^{\circ}$  phase shift compensated by  $R_o$  and  $C_c$  to obtain  $\theta_{LNA+Mixer} = 0$ , as required for optimal noise performance of the overall feedback loop, as discussed in Sec. 2.3.  $C_c$  can also be used to tune the overall LG phase to compensate for any other phase shift created in the loop. The nominal  $+45^{\circ}$  phase shift created by  $R_o$  and  $C_c$  provides the additional benefit of sensitive phase shift tuning using a small  $C_c$  value over a wide range of operating frequency,  $f_{mod}$ .

Figure 2.10: Schematic of the amplifier in integrator  $I_1$ .

To address a wide range of  $f_{\text{mod}}$ ,  $C_{\text{c}}$  is implemented as a capacitor bank with a fine tuning step of 100 fF and a coarse tuning step of 1 pF, providing capacitance values from 50 fF to 16 pF. Fig. 2.9 shows the combined phase offset coverage from  $A_1$  and  $M_1$  for this adjustable  $C_{\text{c}}$  across frequency. Over the expected nominal operating frequency range from 1 MHz to 10 MHz, this provides broad coverage from phase  $-40^{\circ}$  to  $40^{\circ}$ . The combined gain of  $A_1$  and  $M_1$  is adjustable from 45-55 dB using 4-step  $R_{\text{BB}}$  tuning.

## 2.4.3 Gain Stage and Integrator

Gain stage  $A_2$  is implemented as a single-stage common-source amplifier with a resistive load and inserts 20 dB gain between mixer and integrator, reducing the noise contribution from the large resistor  $R_{\rm int}$ . The integrator determines the closed-loop bandwidth of the impedance sensor, controlled by  $R_{\rm int}$  and  $C_{\rm int}$ . In this design,  $R_{\rm int}$  is selectable as  $1\,{\rm M}\Omega$  or  $10\,{\rm M}\Omega$  to accommodate both high-resolution and high-speed applications, and  $C_{\rm int}$  is 16 pF. Fig. 2.10 shows the transistor-level schematic of

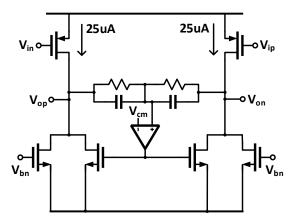

Figure 2.11: Schematic of up-conversion mixer  $M_2$ .

the integrator amplifier. A pseudo-differential common-source amplifier is adopted for its wide output voltage range, and input PMOS transistors are sized with long channel length to reduce flicker noise. The amplifier provides DC gain of  $25\,\mathrm{dB}$  with UGB= $15\,\mathrm{MHz}$  and consumes  $75\,\mu\mathrm{A}$ , including CMFB.

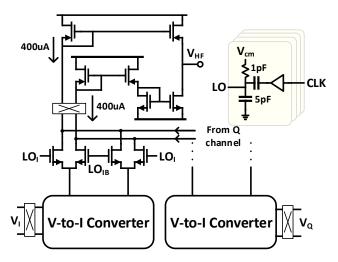

## 2.4.4 Up-conversion mixer and hybrid feedback impedance

A quadrature up-conversion mixer upconverts the demodulated signal for closed-loop feedback operation. The topology of the converter is similar to [17], including a highly linear V-to-I converter [23], a quadrature Gilbert-cell driven by a  $300\,\mathrm{mV_{pp}}$  square wave, and a current summation stage implemented using a current mirror. Chopping is used to mitigate flicker noise from the input transistors in the V-to-I converter.

The feedback element  $Z_1$  (Fig. 2.7) must remain high impedance at high  $f_{\text{mod}}$  operation to maintain closed-loop gain, which is realized by resistance  $R_{\text{f}}$ . As imple-

menting a large resistance (>1 M $\Omega$ ) at megahertz frequencies is challenging due to parasitic capacitance, an active resistor is implemented by a capacitive current divider with selectable capacitor ratio (1/5/50) to boost physical resistor  $R_{\rm f0}$  (200k $\Omega$ ), providing variable resistance (10M $\Omega$ /1M $\Omega$ /200k $\Omega$ ). Pseudo-resistors provide a DC path in the active resistor, as well as input virtual ground for the input low-noise amplifier. Note we expect less than 100 pA input DC current due to the double layer capacitor from electrode-electrolyte interface.

The amplifier in the active feedback path is implemented as a two-stage amplifier with Miller compensation and consumes  $500\,\mu\text{A}$  current, supporting resistance multiplication up to  $100\,\text{MHz}$ . The capacitor  $C_{\rm f}$  not only couples signal from the up-conversion mixer, but it also serves as the dominant feedback impedance when  $f_{\rm mod}$  is low.  $C_{\rm f}$  is adjustable from  $100\,\text{fF}$  to  $3\,\text{pF}$ , and it should be carefully chosen based on desired feedback impedance at the desired operating frequency,  $f_{\rm mod}$ .

## 2.5 Verification and Measurement Results

This impedance sensor IC was fabricated in a 0.18 µm CMOS process and occupies 400 µm×700 µm area; a die photo is shown in Fig. 2.12. The chip operates from a 1.8 V supply, and modulation and chopping clocks are applied externally. A custom test PCB incorporates an FPGA module (Opal Kelly XEM6310) for providing adjustable chopper frequency and static digital controls to the chip, and a low-noise analog op-amp (ADA4896) is included for buffering differential I/Q analog outputs. An audio precision analyzer (Audio Precision APx555) is used to analyze

Figure 2.12: Micrograph of the fabricated 0.18  $\mu$ m CMOS impedance sensor IC.

the demodulated I/Q output spectrum. Total average current consumption of the impedance sensor operating at  $f_{\text{mod}}=1 \text{ MHz}$  is measured at 5.4 mA, including analog and digital power supplies at 1.8 V.

## 2.5.1 Electrical characterization of impedance sensor IC

Standalone electrical characterization of the impedance sensor IC was performed using a model cell with  $10 \,\mathrm{k}\Omega$  resistance, representing channel resistance, in series with  $10 \,\mathrm{nF}$  capacitance representing double-layer capacitance (Fig. 2.13); while larger than a typical double-layer capacitance seen in practice,  $10 \,\mathrm{nF}$  ensures that the resistance value is dominant at frequencies of interest for the purposes of IC characterization. A  $2 \,\mathrm{mV_{pp}}$  sine wave input with frequency  $f_{\mathrm{mod}} + \Delta f$  is input through the model cell to the impedance analyzer with synchronized  $f_{\mathrm{mod}}$  as the modulation frequency. The demodulated sine wave output with frequency of  $\Delta f$  is analyzed to acquire the

Figure 2.13: (a) Measurement setup using a model cell for voltage gain transfer function of impedance sensor, and (b) measured voltage gain transfer function at different  $f_{\rm mod}$  (0.05/1/10/40MHz) using low and high bandwidth modes.

voltage transfer function. Measured closed-loop voltage transfer functions are shown in Fig. 2.13b for modulation frequencies of 50 kHz, 1 MHz, 10 MHz, and 40 MHz, evaluated with  $R_{\rm f,eq}$  set to 10 M $\Omega$  for a expected gain of 60 dB; measured gain of 59 dB with  $\pm 1$  dB accuracy is obtained for all  $f_{\rm mod}$  values. A consistent closed-loop 3-dB bandwidth of approximately 200 Hz in low-bandwidth mode ( $R_{\rm int}$ =10 M $\Omega$ ) and 2 kHz in high-bandwidth mode ( $R_{\rm int}$ =1 M $\Omega$ ) is obtained across 50 kHz-40 MHz. Note  $C_{\rm c}$  is adjusted correspondingly with  $f_{\rm mod}$  to avoid gain and frequency offset variations.

A key metric for an impedance sensor is its noise performance, which determines

Figure 2.14: (a) Input-referred noise current spectral density when  $f_{\rm mod}=500\,\rm kHz$  (Both chopper on and off; low-bandwidth and high-bandwidth cases are shown for comparison) (b) Input-referred noise current spectral density when  $f_{\rm mod}=1\,\rm MHz$ ,  $10\,\rm MHz$  and  $40\,\rm MHz$ .

achievable impedance measurement sensitivity and limit of detection. In this work, comprehensive noise performance of the impedance sensor IC at different frequencies was measured and analyzed. Output noise voltage spectral density was measured using an audio analyzer with the sensor input open, with only parasitic capacitance present. The audio analyzer internal ADC sampling frequency was set to 96 kHz, using a 1.2M-point FFT. The input-referred noise current spectral density is calculated as measured output voltage spectral density divided by mid-band gain.

Fig. 2.14a shows the noise performance of the impedance sensor down to 1 Hz, operating at  $f_{\text{mod}} = 0.5 \,\text{MHz}$ . The current spectral density of both low-bandwidth and high-bandwidth modes are shown, demonstrating a noise floor of  $410 \,\text{fA}/\sqrt{\text{Hz}}$ . The measured noise floor under-performs the expected simulation results due to the parasitic capacitance introduced at the input node of the impedance sensing IC by the bond pad, IC packaging, and PCB. The noise performance without the chopper is shown as well, which demonstrates that the 75 kHz chopping frequency effectively

Figure 2.15: Effective resistance and capacitance measurement resolution across modulation frequency calculated from the input-referred rms current noise over  $200\,\mathrm{Hz}$  bandwidth, when input voltage amplitude is  $1\,\mathrm{V}$ .

reduces the flicker noise contribution frequency by more than 10X near DC. The input rms current at  $0.5\,\mathrm{MHz}~f_\mathrm{mod}$  is calculated as  $6\,\mathrm{pA}$  from 1 to  $200\,\mathrm{Hz}$  for the given spectral density.

To investigate the noise performance at high frequency, the input-referred noise current spectral density at  $f_{\text{mod}} = \{1, 10, 40\}$  Mhz and 300 kHz chopping frequency is shown in Fig. 2.14b. As expected, the noise increases at higher modulation frequencies, as the input parasitic capacitance decreases effective input impedance. The input-referred resistance and capacitance measurement resolution at different modulation frequencies is calculated from the input-referred rms current noise over 200 Hz bandwidth and presented in Fig. 2.15, assuming an input voltage amplitude of 1 V and a nominal input resistance of 10 k $\Omega$ . The minimum resistance resolution is achieved as  $0.6 \Omega$  at 0.5 MHz modulation frequency; this is limited primarily by the input-referred noise current below 500 kHz modulation frequency due to the maximum  $C_c$  value (16 pF). The minimum calculated capacitance measurement resolution

Figure 2.16: (a) Illustrated cross-section and (b) top view micrograph of fabricated microfluidic flow channel with 3-electrode sensor used in experiments. achieved is 0.42 aF at 20 MHz.

#### 2.5.2 Microfluidic flow cell design and fabrication

A microfluidic flow cell was fabricated for testing the impedance cytometer, as shown in Fig. 2.16. Electrodes were lithographically defined and deposited (20/150 nm Cr/Au) on fused silica wafers. Following electrode fabrication, the chamber layer of the microfluidic channel was patterned using a 50 μm spin-coated layer of SU8-2050 (MicroChem). The microfluidic channel was sealed with a thermoplastic laminating process, and fluid ports were installed. As fabricated, the channel width and height are each 50 μm, and electrodes are 40 μm wide with 10 μm spacing.

After fabrication, the flow cell was fixtured to ensure reliable electrical contact between the electrodes and the IC, where pogo pins in contact with the flow cell wafer and connect by wire to the IC test PCB.

Figure 2.17: Illustration (a) and photograph (b) of experimental test setup for evaluating the impedance sensor IC with a microfluidic flow cell, including electrical, optical, and fluidic interfaces.

# 2.5.3 Flow cytometry measurement using micro-beads

The impedance cytometry IC and microfluidic flow cell were used in conjunction for a system-level demonstration of the complete sensor system; the experimental setup is shown in Fig. 2.17. Two differential anti-phase 1 MHz,  $500\,\mathrm{mV_{pp}}$  excitation AC voltages were applied to the two outer electrodes, and a synchronized 2 MHz clock signal was supplied to the IC for lock-in operation. The resulting differential current through the middle electrode was measured by the impedance sensor with  $R_{\mathrm{f,eq}}{=}10\,\mathrm{M}\Omega$  and  $\mathrm{BW}{=}200\,\mathrm{Hz}$ . It is important to note that due to any fabrication-related mismatch of the electrodes and the high gain of the impedance sensor, there will be a DC offset voltage at the impedance sensor output, which can limit the

measurement dynamic range. To address this, calibration is performed by adjusting the relative phase and amplitude of the excitation sources slightly to balance the source-differential excitation and compensate for any offset; this is typically less than  $\pm 1^{\circ}$  from the ideal 180° source-differential offset.

For a fluid sample, micron-scale polystyrene beads (Polysciences) were suspended in 1X phosphate-buffered saline (PBS) solution and injected into the flow cell at 0.3 µL/min using a syringe pump. A microscope was used with attached camera is used to record video of the flow channel, providing synchronized optical verification of the electrical measurement. The differential analog I/Q voltage output of the impedance sensor was recorded at 2.5 kHz sampling rate by the oscilloscope and post-processed in MATLAB.

Dilute solutions of monodisperse beads were prepared to analyze single-cell resolution; a typical measured transient waveform is shown in Fig. 2.18 as a 10 µm diameter bead transits across the electrode. Three microscope images corresponding to the A, B, C moment in the transient waveform are provided, as a flowing bead enters the electrode set, in the middle of electrode set, and leaving the electrode set, respectively. Only the real component of the voltage recorded from the middle (I channel) electrode is plotted, as channel resistance change is dominate at this mid-band modulation frequency (1 MHz). From Fig. 2.18, the peak voltage change obtained is  $0.9\,\mathrm{V}$  for a  $10\,\mathrm{\mu m}$  bead passing electrodes, corresponding to a  $9\,\Omega$  resistance change of approximately  $5\,\mathrm{k}\Omega$  static channel resistance (measured separately by the impedance analyzer chip using 1X PBS in the absence of poly beads).

Multiple measurements using 3 μm, 5 μm, and 10 μm diameter bead solutions

Figure 2.18: Measured voltage transient signal real component (I-channel) shown above real-time microscope images taken when a single  $10\,\mu m$  bead is transiting across the electrodes.

were performed to assess the resolution and size separation capability of proposed cytometer, and Fig. 2.19a shows measured transient results for a 5 minute recording of each sample solution. As in Fig. 2.18, only the real voltage component (I-channel) is shown and analyzed. The output voltage amplitude is relatively consistent for each crossing event for a given bead size, and it scales down as the bead size decrease, as expected.

A zoomed transient plot for the 3 µm bead measurement is also shown in Fig. 2.19a for analysis of detection limit of the proposed cytometry technique. The measured peak-to-peak voltage of given single-bead event is 136 mV, and the measured rms noise from the transient recording is approximately 3 mV. Approximating the crossing response waveform as sinusoidal, this yields a high detection signal-to-noise ra-

Figure 2.19: (a) Measured 5-minute transient waveforms using the impedance-based sensor IC and a custom microfludic flow cell for flowing solutions of 3 μm, 5 μm, and 10 μm polymer microbeads, and (b) the peak-to-peak voltage histogram of each single-cell event, demonstrating clear separation by particle size.

tio (SNR) of 24 dB for  $3\,\mu\text{m}$  bead size. The response time for single bead event in this measurement is around 150 ms, corresponding a throughput of less than 10 beads/second. However, note that this experimental set uses an intentionally low flow rate for unambiguous single-bead verification, which is not limited by the actual impedance sensor bandwidth (200/2000 Hz).

Fig. 2.19b shows the peak-to-peak voltage histogram of 3 μm, 5 μm, and 10 μm particle measurements from the transient recordings in Fig. 2.19a. Due to the ex-

perimental measurement sequence, residual 5  $\mu$ m beads remain in the channel during the 10  $\mu$ m bead, which is annotated in Fig. 2.19a and confirmed in the associated microscope video recording. These events, as well as simultaneous multi-bead events, are excluded from the histogram in order to analyze isolated, single-bead peak-to-peak voltage distribution. A distinct separation from  $3 \mu$ m,  $5 \mu$ m and  $10 \mu$ m group is shown in the histogram.

The average peak-to-peak voltage for  $3 \,\mu\text{m}$ ,  $5 \,\mu\text{m}$ , and  $10 \,\mu\text{m}$  beads in Fig. 2.19b is  $0.103 \,\text{V}$ ,  $0.415 \,\text{V}$ , and  $1.8164 \,\text{V}$ , respectively, which matches the approximation that channel resistance change is proportional to the square of particle diameter, corresponding to change in cross-sectional area presented between the electrodes. These average peak-to-peak voltage amplitudes indicate channel resistance changes of  $9.3 \,\Omega$ ,  $2.1 \,\Omega$ , and  $0.5 \,\Omega$  atop the nominal  $5 \,\text{k}\Omega$  channel resistance for  $10 \,\mu\text{m}$ ,  $5 \,\mu\text{m}$ , and  $3 \,\mu\text{m}$  beads, respectively. Assuming an approximately square relationship of signal amplitude with particle diameter along with the measured noise floor, the proposed impedance-based cytometer IC can achieve sub-1  $\mu$ m cell diameter limit of detection.

Also visible in in Fig. 2.19b, deviation in peak-to-peak amplitude for a given bead size is due primarily to the nonuniform flow velocity profile in a microfluidic channel, where particles near the center move at higher velocity even under constant flow rate, as well as the random vertical position of a bead in the microfluidic channel as it crosses the electrodes. In future work, hydrodynamic focusing, such as sheath flow, can be used in the flow cell to decrease this distribution and further improve cell diameter measurement resolution.

Figure 2.20: Measured voltage output  $V_{\rm pp}$  versus half-width time; data extracted from 30s recording of  $5/10\,\mu$ m bead mixture.