### AN ABSTRACT OF THE DISSERTATION OF

Shaan Sengupta for the degree of <u>Doctor of Philosophy</u> in <u>Electrical and Computer</u> Engineering presented on December 6, 2021.

${\bf Title:} \ \underline{\bf CMOS} \ {\bf Transducers} \ {\bf and} \ {\bf Programmable} \ {\bf Interface} \ {\bf Circuits} \ {\bf for}$

Resource-Efficient Sensing Applications

| Abstract approved: |  |

|--------------------|--|

| 1 1                |  |

#### Matthew L. Johnston

Modern sensors are complex systems comprising multiple sub-systems such as transducers, analog and mixed-signal interface circuits, digital processing circuits, and packaging. Over the last few decades, innovations in these sub-systems combined with their increased integration in complementary metal-oxide semiconductor (CMOS) processes have led to the rapid growth in sensors for the Internet-of-Things (IoT), wearable devices, and fundamental scientific instrumentation. This dissertation introduces novel ideas for various parts of a sensor signal chain.

First, CMOS-based transducers are introduced. Single-photon avalanche diodes (SPADs) fabricated in  $0.18\,\mu\mathrm{m}$  and  $0.13\,\mu\mathrm{m}$  standard CMOS processes are demonstrated and characterized for various optical sensing techniques. A resistor fabricated using standard CMOS-BEOL layers in a  $0.18\,\mu\mathrm{m}$  process, is used to demonstrate a compact fully-integrated single-element flow sensor occupying less than  $0.065\,\mathrm{mm}^2$ .

Second, front-end interface circuits for single-photon optical detectors are introduced. A fully integrated SPAD-based ambient light sensor using mostly digital circuits and fabricated in a  $0.13\,\mu\mathrm{m}$  CMOS process is highlighted. It consumes  $125\,\mu\mathrm{W}$  and achieves one of the lowest reported areas  $(0.046\,\mathrm{mm}^2)$  in the literature. A custom analog front-end (AFE) chip is fabricated in a  $0.18\,\mu\mathrm{m}$  CMOS process for interfacing with a commercial silicon photomultiplier (SiPM) for gamma spectroscopy. It incorporates tunability of dynamic range and integration time, thus making it suitable for different detectors (i.e. SiPM and scintillator crystal combinations).

Third, non-linear analog-to-digital converters (NL-ADCs) are explored as a viable alternative to linear ADCs for information-aware non-uniform quantization and a widely programmable piecewise-linear ADC (PWL-ADC) prototype chip (0.18  $\mu$ m CMOS) is used to validate this. With a 7-bit output word, it achieves 5.6-bit to 9.5-bit resolution in user-defined regions of the input full-scale range (FSR), while consuming  $105 \,\mu$ W at a sampling frequency of 42kHz. Measurements with recorded ECG waveforms highlight the application-specific advantages of the PWL-ADC.

Finally, some of the aforementioned ideas are used at the system level in a gamma spectrometer realized on a printed circuit board (PCB). The PCB design includes the AFE and PWL-ADC IC chips, a commercial SiPM and scintillator crystal, and a field programmable gate array (FPGA) based digital back-end (DBE). Several linear and non-linear isotope spectra with variable energy bin-widths ( $\Delta$ E/bin) are recorded and analyzed to demonstrate the utility of the proposed concepts for peak enhancement and improved peak discrimination in radiation spectroscopy.

©Copyright by Shaan Sengupta December 6, 2021 All Rights Reserved

# CMOS Transducers and Programmable Interface Circuits for Resource-Efficient Sensing Applications

by

Shaan Sengupta

### A DISSERTATION

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented December 6, 2021 Commencement June 2022

| Doctor of Philosophy dissertation of Shaan Sengupta presented on December 6, 2021.                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APPROVED:                                                                                                                                                                                                 |

| Major Professor, representing Electrical and Computer Engineering                                                                                                                                         |

| Head of the School of Electrical Engineering and Computer Science                                                                                                                                         |

| Dean of the Graduate School                                                                                                                                                                               |

|                                                                                                                                                                                                           |

| I understand that my dissertation will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my dissertation to any reader upon request. |

| Shaan Sengupta, Author                                                                                                                                                                                    |

#### ACKNOWLEDGEMENTS

I would not be where I am today without the help and support of several key people. Foremost among them are my parents, Saradindu and Sonali Sengupta, who taught me at an early age, the value of hard work, humility, and a strong moral compass. They have continued to encourage me during my life's adventures and have showered me with unconditional love, and I cannot thank them enough for that.

I could not have asked for a better advisor than Matthew L. Johnston. Matt has played an incredibly important role in my life in these past few years. I feel lucky to have been part of his SIM Lab research group right from its inception to now seeing it flourish under his guidance. Throughout this time, Matt gave me the freedom to explore ideas, provided guidance and course-correction when required, and above all, taught me the important lessons of thinking creatively and independently, staying curious, communicating clearly, and taking ownership of my ideas and actions. My love for research was kindled from a spark into a bright flame by Matt and I will forever be thankful to him for that.

I would like to thank Dr. Un-Ku Moon, Dr. Arun Natarajan and Dr. Tejasvi Anand for the invaluable technical and life lessons I've learned from them through classes, personal interactions, and discussions throughout my time at OSU. I'm also thankful to Dr. Camille Palmer for helpful discussions regarding some of the applications of my designs and agreeing to be the GCR in my committee.

Among my peers, I would especially like to thank my SIM Lab colleagues: Hyunkyu,

Soumya, Boyu, Kyle, Jinyong, Richard, Jacob, Callen, Mckay, and Debbie. The countless technical discussions, meals, and coffees we've shared were instrumental in my grad school experience and I could not have asked for a better set of colleagues and collaborators. My time in the SIM Lab exposed me to many fascinating topics outside the domain of integrated circuit design, giving me a deep appreciation for a systems and applications perspective.

The larger analog/mixed-signal group at OSU has been a bottomless source of information and joy. Their company and support made research fun. I got to interact with students from all around the world and I'm richer for it. I will forever cherish the friendships I developed here and the time that I spent in the office and outside of it with colleagues such as Spencer, Calvin, Jason, Praveen, Ahmed, Hamid, Kamala, Manoj, and Emanuel. Close friends such as Alper, Alp, Nik, Prannoy, Lan, and Tonio always reminded me that there exists a world outside of integrated circuits!

Last, but definitely not the least, I would like to thank my partner Srishti Nayak. "A journey of a thousand miles begins with a single step"...Srishti was the one who encouraged me to take the first step, and then some. Throughout this long and eventful journey that is the PhD, she has drawn upon her own grad school experiences to help and support me in innumerable ways. On my happiest and on my darkest days, she has always greeted me with a smile and a song. An unwavering bulwark of emotional strength, I am incredibly fortunate and happy to have her by my side.

### TABLE OF CONTENTS

|   |                                                        |       |   | гage     |

|---|--------------------------------------------------------|-------|---|----------|

| 1 | Introduction to Sensors                                |       |   | 1        |

|   | 1.1 Dissertation Outline                               |       |   | 5        |

| 2 | Transducers in Standard CMOS Processes                 |       |   | 6        |

|   | 2.1 Single-Photon Avalanche Diodes for Optical Sensing |       |   | 8        |

|   | 2.1.1 Background                                       |       |   | 8<br>18  |

|   | 2.2 Resistive Transducer for Flow Sensing              |       |   | 21       |

|   | 2.2.1 Background                                       |       |   | 21       |

|   | 2.2.2 Proposed Integrated Single-Element Flow Sensor   |       |   | 21       |

|   | 2.3 Conclusion                                         |       |   | 24       |

| 3 | Front-End Interface Circuits                           |       |   | 25       |

|   | 3.1 Readout Circuit Architectures                      |       |   | 26       |

|   | 3.2 Readout Circuits for SPADs                         |       |   | 27       |

|   | 3.3 Case Study: Digital Ambient Light Sensor           |       |   | 29       |

|   | 3.3.1 Introduction                                     |       |   | 29       |

|   | 3.3.2 Proposed System                                  |       |   | 32       |

|   | 3.3.3 System Overview                                  |       |   | 36<br>38 |

|   | 3.3.5 Conclusion and Future Work                       |       |   | 41       |

| 4 | Information Aware Analog-to-Digital Converters         |       |   | 42       |

|   | 4.1 Non-Linear ADCs                                    |       |   | 43       |

|   | 4.2 Proposed Piecewise-Linear ADC                      |       |   | 44       |

|   | 4.2.1 PWL-ADC Architecture                             |       |   | 45       |

|   | 4.2.2 PWL-ADC Design Approach                          |       |   | 47       |

|   | 4.2.3 Circuit Implementation                           |       |   | 52       |

|   | 4.2.4 Measurement Results                              |       |   | 55       |

|   | 4.3 Conclusion and Future Directions                   | <br>• | • | 63       |

| 5 | A Programmable Gamma Spectrometer                      |       |   | 65       |

|   | 5.1 Introduction                                       |       |   | 65       |

## TABLE OF CONTENTS (Continued)

|   |                                                   | Page |

|---|---------------------------------------------------|------|

|   | 5.2 Proposed Reconfigurable Multichannel Analyzer |      |

|   | 5.2.1 Detector                                    |      |

|   | 5.2.2 Multichannel Analyzer                       | 68   |

|   | 5.2.3 Radiation Spectroscopy Measurements         | 72   |

|   | 5.2.4 Conclusion                                  | 80   |

| 6 | Conclusions                                       | 81   |

| 7 | Summary of Contributions                          | 83   |

| В | ibliography                                       | 85   |

| A | ppendices                                         | 93   |

|   | A Calibration Isotope Peak Energies               | 94   |

### LIST OF FIGURES

| Page |                                                                                                                                                                                                                                                                                                            | F'igure |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

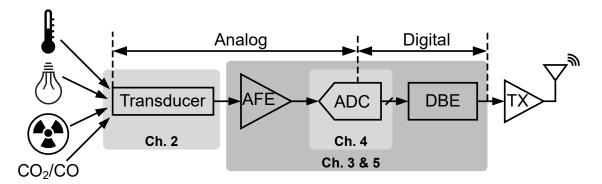

| 2    | High-level illustration of an electronic sensor system with the major signal processing blocks highlighted. Chapters corresponding to specific sub-system(s) are annotated                                                                                                                                 | 1.1     |

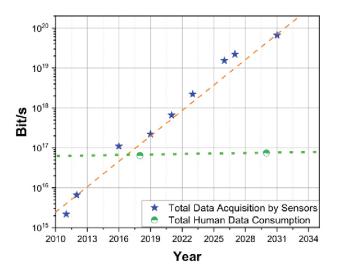

| 4    | Sensor data projection from [3]                                                                                                                                                                                                                                                                            | 1.2     |

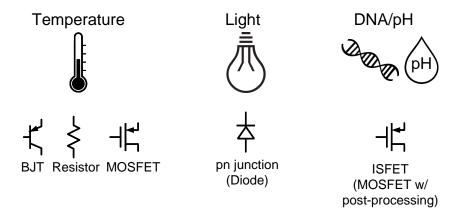

| 6    | Examples of physical quantities and the corresponding CMOS-based transducer structures used to measure them in integrated sensors $$ .                                                                                                                                                                     | 2.1     |

| 14   | A resistor-based passive quench and reset scheme of a SPAD is shown in along with the transient behavior of the anode voltage during photon, DCR and afterpulse events                                                                                                                                     | 2.5     |

| 19   | Cross-sections of variants of a $p$ -well/deep- $n$ -well SPAD implemented in TowerJazz CA18HD 0.18 $\mu$ m CMOS process with variable distance between STI and active area to investigate impact on DCR [34]                                                                                              | 2.6     |

| 20   | Test die with multiple planar SPAD variants, implemented in Tower-Jazz CA18HD 0.18 $\mu$ m CMOS process [34]                                                                                                                                                                                               | 2.7     |

| 23   | 3-D illustration of the structure of the on-chip resistive sensing element formed in the top CMOS routing layers, where each layer change consists of two electrical vias in parallel; this ensures support of sufficiently high current densities, while still maintaining a high resistance density [42] | 2.8     |

| 24   | (a) Chip photo with integrated flow sensor highlighted, (b) zoomed view of flow sensor blocks, and (c) computer layout of heator/sensor resistive element                                                                                                                                                  | 2.9     |

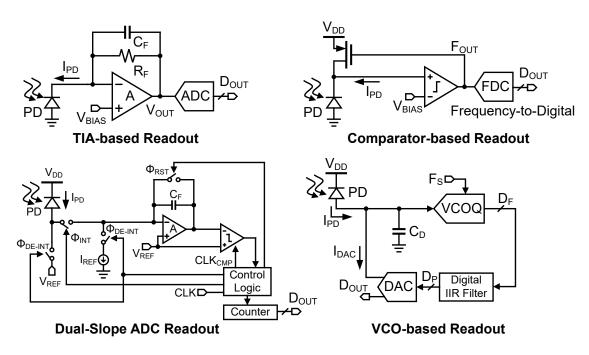

| 26   | Common AFE architectures are shown in (a) and (b). Sensor-in-the-loop architectures with combined AFE and ADC functionalities are shown in (c) and (d)                                                                                                                                                     | 3.1     |

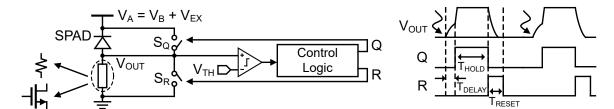

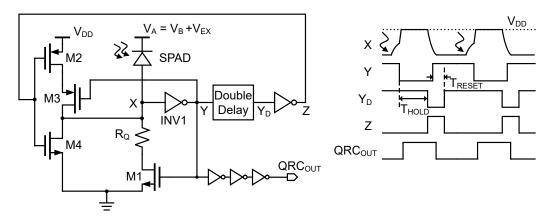

| 28   | Mixed quench and reset scheme used with SPADs and associated timing diagram [14]                                                                                                                                                                                                                           | 3.2     |

| 30   | Common applications for ambient light sensors                                                                                                                                                                                                                                                              | 3.3     |

| 31   | Example photodiode readout circuits                                                                                                                                                                                                                                                                        | 3.4     |

# LIST OF FIGURES (Continued)

| Fig | gure |                                                                                                                                                                                                                                                                                                                                | Page |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

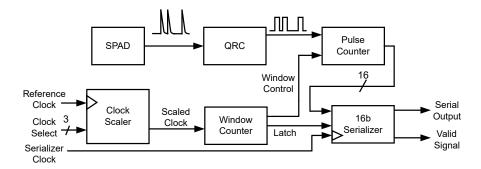

|     | 3.5  | A high-level architecture schematic of the proposed all-digital ambient light sensor [50]                                                                                                                                                                                                                                      | 32   |

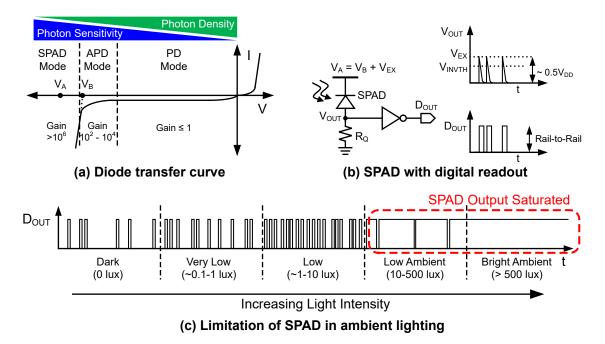

|     | 3.6  | SPAD characteristics with a digital readout and operation across varying light intensity                                                                                                                                                                                                                                       | 34   |

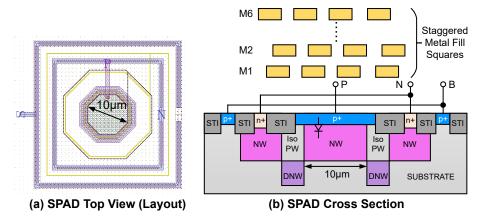

|     | 3.7  | (a) Top view of SPAD layout in $0.13\mu\mathrm{m}$ CMOS process and (b) illustrated cross-section of the SPAD showing metal fill-based filter. [50]                                                                                                                                                                            | 35   |

|     | 3.8  | Schematic illustration of mixed passive-active quench and reset circuit, including self-timed hold-off and reset signals [50]                                                                                                                                                                                                  | 37   |

|     | 3.9  | (a) Chip photograph of the test chip fabricated in GF/IBM 0.13 $\mu$ m CMOS process, (b) zoomed view of the ambient light sensor blocks, (c) test PCB photograph, and (d) illustration of the test setup                                                                                                                       | 38   |

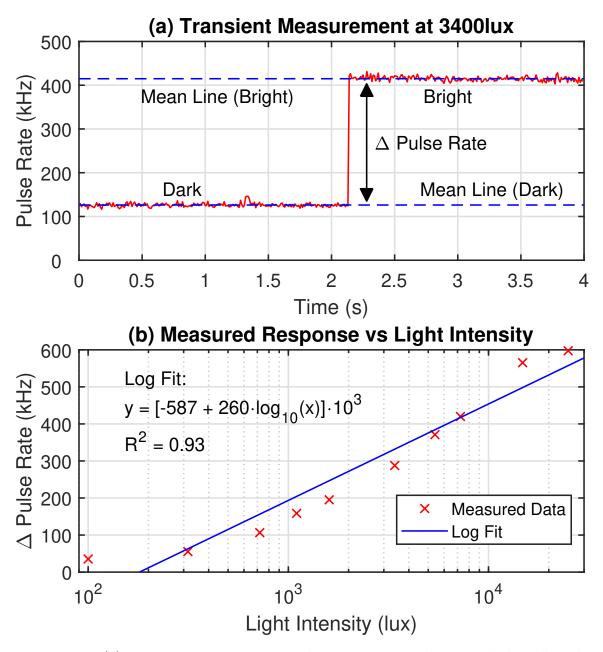

|     | 3.10 | (a) Transient measurements showing transition between dark and bright (at 3400lux) pulse rates. (b) Measured response across varying light intensity, with logarithmic fitting curve                                                                                                                                           | 40   |

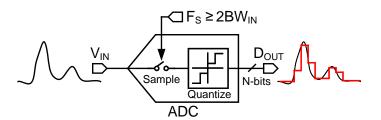

|     | 4.1  | Simplified illustration of Nyquist ADC operation                                                                                                                                                                                                                                                                               | 42   |

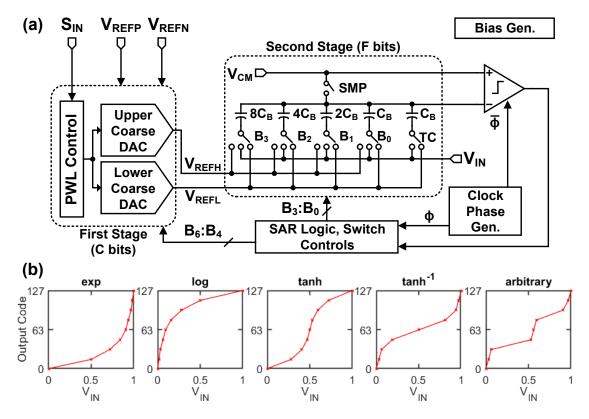

|     | 4.2  | (a) High-level architecture of the proposed PWL-ADC. (b) Example non-linear transfer functions from a behavioral model [63]                                                                                                                                                                                                    | 46   |

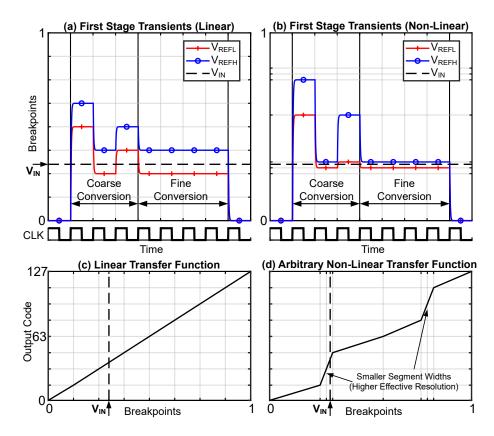

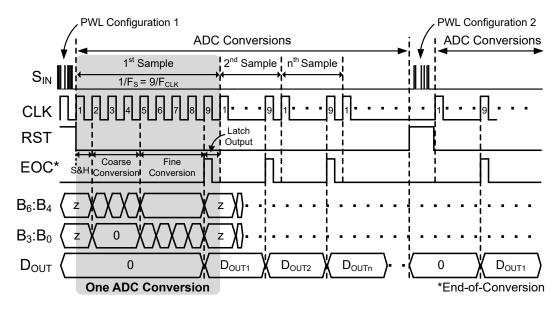

|     | 4.3  | Coarse-conversion stage outputs ( $V_{REFH}$ and $V_{REFL}$ ) are simulated for linear (a) and piecewise-linear (b) operation, along with corresponding transfer functions in (c) and (d). $V_{REFH}$ and $V_{REFL}$ are fixed after coarse conversion, providing voltage references to the linear, fine-conversion stage [63] | 48   |

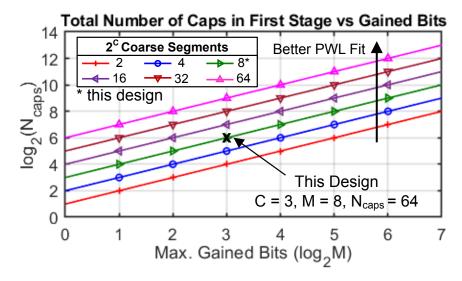

|     | 4.4  | Varying $N_{caps}$ and $C$ results in varying number of maximum gained bits within a coarse segment. For a fixed number of coarse segments, for each additional gained bit, $N_{caps}$ increases exponentially [63]                                                                                                            | 51   |

# LIST OF FIGURES (Continued)

| Page |                                                                                                                                                                                                                                                                                                                                                                                                        | Figure |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

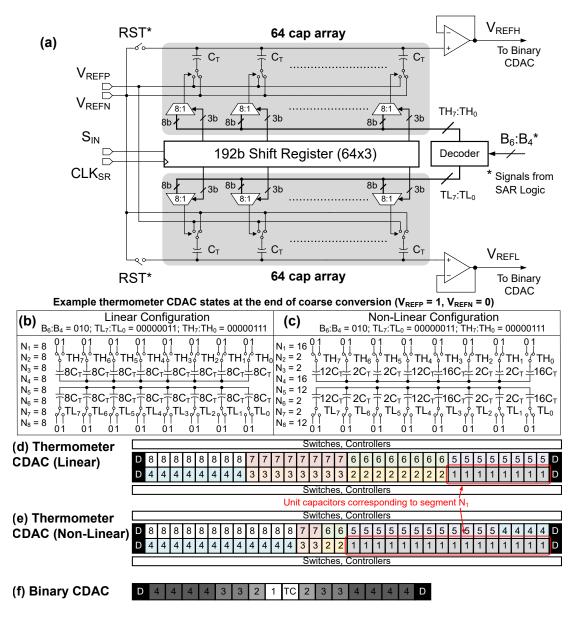

| 53   | The core of the first stage as shown in (a), consists of two programmable thermometer-encoded CDACs with 64 unit capacitors ( $C_T = 10 fF$ ); (b) and (c) show the states of the thermometer CDACs at the end of the coarse-conversion examples as shown in Fig. 4.3(a-b) for linear and non-linear cases, respectively [63]. Corresponding DAC unit capacitor layouts are shown in (d), (e), and (f) | 4.5    |

| 54   | Varying $N_{caps}$ and $C$ results in varying number of maximum gained bits within a coarse segment. For a fixed number of coarse segments, for each additional gained bit, $N_{caps}$ increases exponentially                                                                                                                                                                                         | 4.6    |

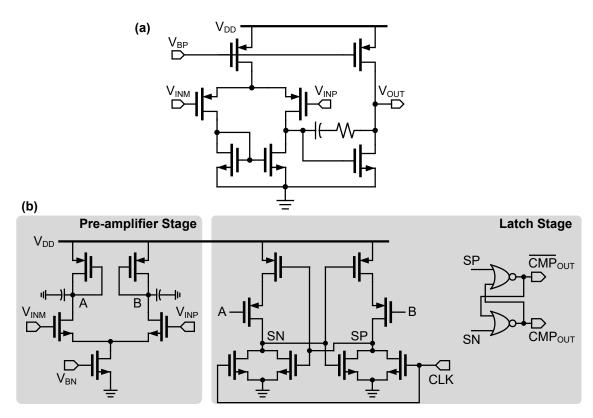

| 56   | Schematics of the (a) two-stage Miller-compensated op-amp used as unity-gain buffer and (b) two-stage comparator based on [64]                                                                                                                                                                                                                                                                         | 4.7    |

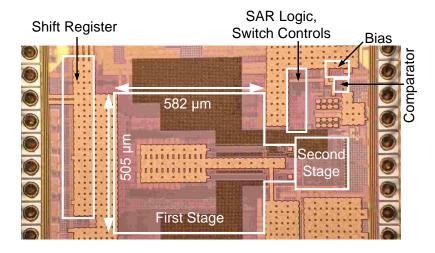

| 56   | Die photograph of the prototype PWL-ADC 0.18 $\mu \mathrm{m}$ CMOS IC [63]                                                                                                                                                                                                                                                                                                                             | 4.8    |

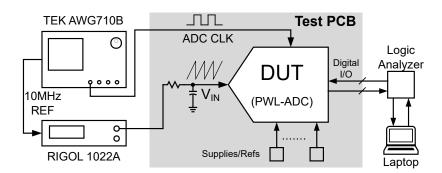

| 57   | Schematic illustration of the ramp input code density test setup used to measure the various linear and non-linear transfer functions                                                                                                                                                                                                                                                                  | 4.9    |

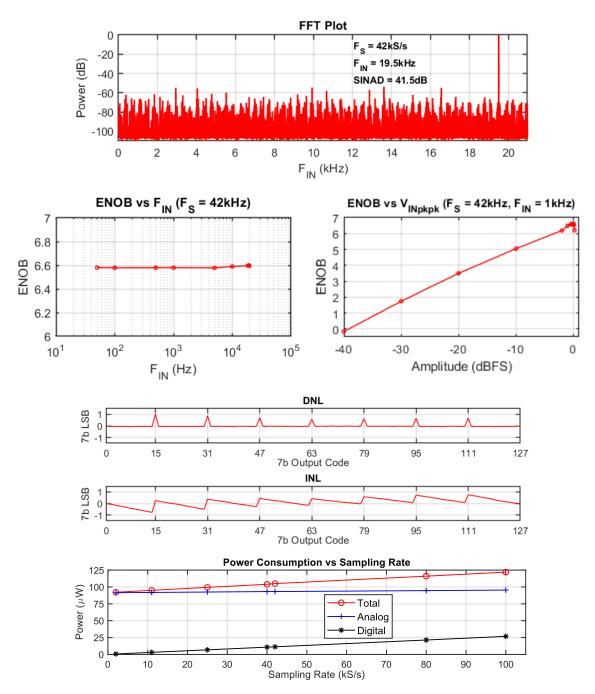

| 58   | Measured static and dynamic performance of the PWL-ADC configured as an un-calibrated 7b linear converter [63]                                                                                                                                                                                                                                                                                         | 4.10   |

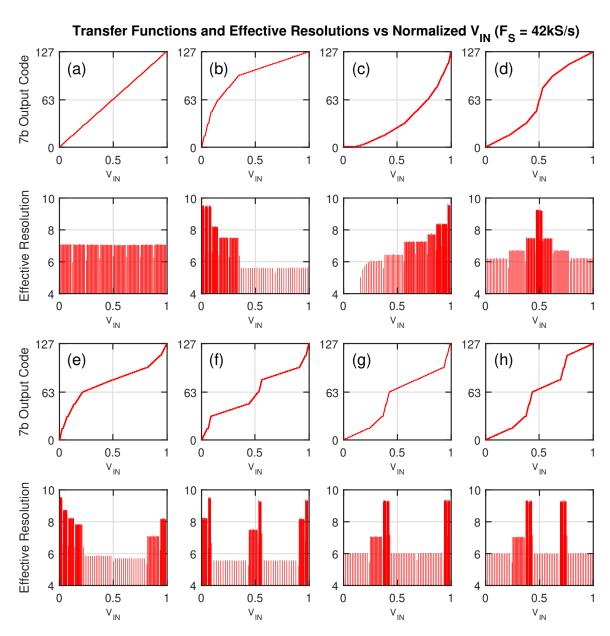

| 59   | 1 Measured transfer functions demonstrating the versatility of the reconfigurable PWL-ADC. Effective resolution within each coarse segment is shown below each corresponding transfer function [63]                                                                                                                                                                                                    | 4.11   |

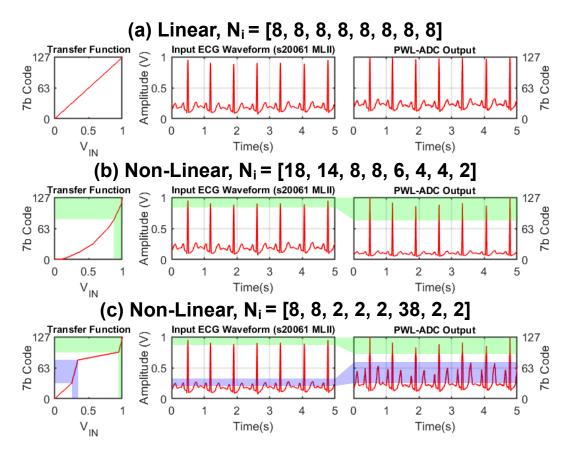

| 61   | Reconstructed output of a measured input linear ramp by using an ideal DAC implementing the inverse of the PWL-ADC transfer function. The highlighted regions are regions of interest with higher effective resolution [63]                                                                                                                                                                            | 4.12   |

| . 62 | 3 Measured ECG waveforms from the Long-Term ST Database [65], [66] digitized using linear and non-linear transformations to demonstrate enhancement of (b) R-peaks, and (c) both R-peaks and ST segments. Regions programmed for higher effective resolution are highlighted [63]                                                                                                                      | 4.13   |

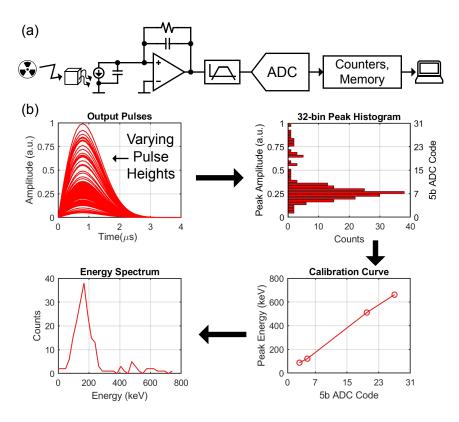

| 66   | (a) A typical signal-chain for pulse-height analysis. (b) shows the steps involved in constructing an energy spectrum                                                                                                                                                                                                                                                                                  | 5.1    |

# LIST OF FIGURES (Continued)

| age  |                                                                                                                                                                                                                                                              | Figure |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

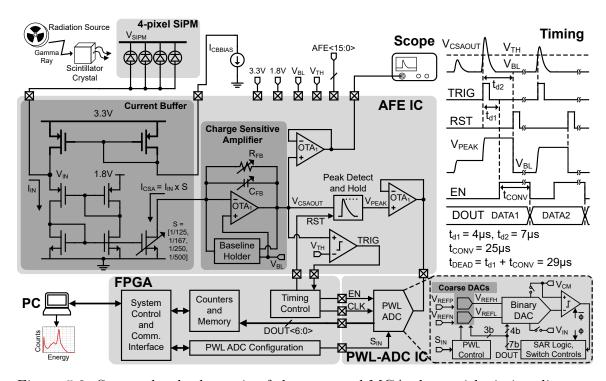

| 69   | System-level schematic of the proposed MCA along with timing diagram of the internal signals [77]                                                                                                                                                            | 5.2    |

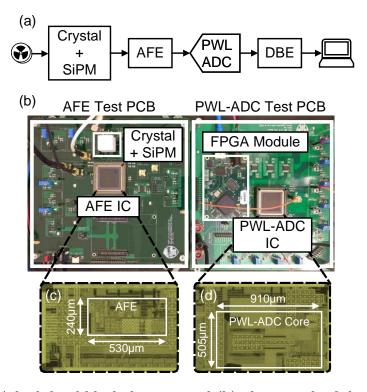

| 72   | (a) A high-level block diagram and (b) photograph of the test setup. Die photographs of the prototype AFE and PWL-ADC 0.18 $\mu$ m CMOS ICs are shown in (c) and (d), respectively                                                                           | 5.3    |

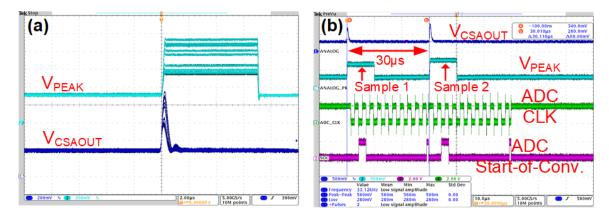

| 74   | Oscilloscope images of (a) persistence capture of CSA and PDH outputs, and (b) MCA system timing validating maximum count rate of 33 kcps                                                                                                                    | 5.4    |

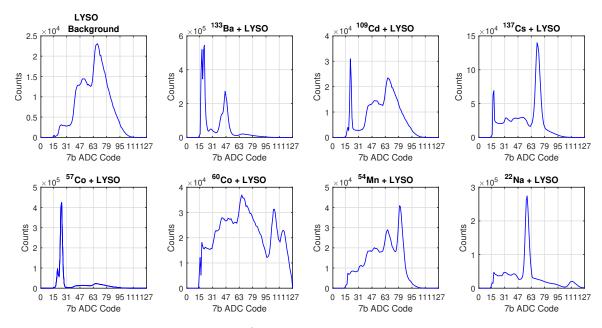

| 74   | Measured histograms/spectra of LYSO background and calibrated isotopes. Each spectrum was recorded for a period of 15 minutes                                                                                                                                | 5.5    |

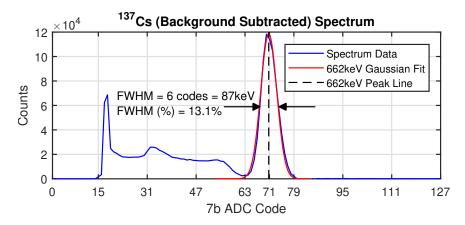

| 76   | Example of Gaussian fitting in background subtracted <sup>137</sup> Cs spectrum to determine location of characteristic 662keV peak and full-width half maximum (FWHM)                                                                                       | 5.6    |

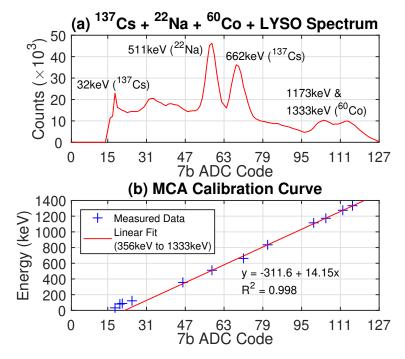

| 76   | An example spectrum of a mix of sources with a wide range of peaks is shown in (a). Multiple measured peak locations used for a linear fit calibration are shown in (b) [77]                                                                                 | 5.7    |

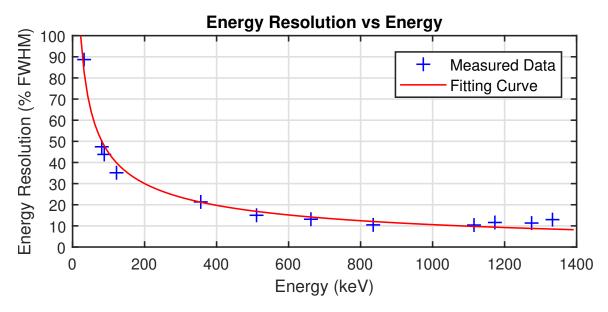

| 77   | Energy resolutions across measured energy peaks when MCA is operated in linear-mode                                                                                                                                                                          | 5.8    |

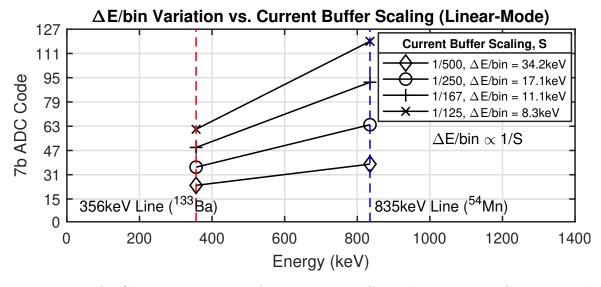

| . 77 | $\Delta E/bin$ across varying AFE current buffer scaling options, S, calculated from spectra containing 356 keV ( $^{133}Ba$ ) and 835 keV( $^{54}Mn$ ) peaks                                                                                                | 5.9    |

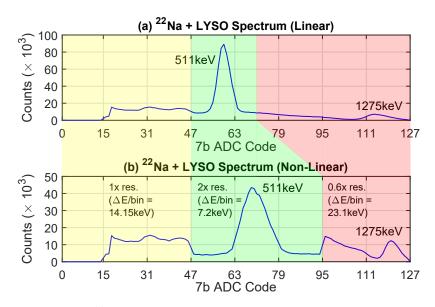

| 79   | Measured <sup>22</sup> Na spectrum (with LYSO background) in (a) linear-mode and (b) non-linear-mode; corresponding regions in linear and non-linear measurements are shaded with the same color [77]                                                        | 5.10   |

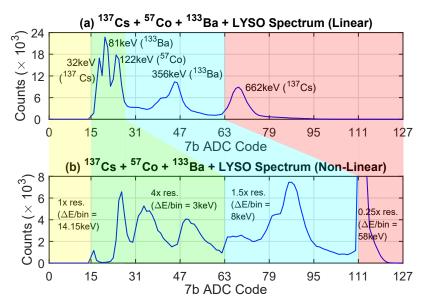

| 79   | 1 Measured spectrum containing <sup>137</sup> Cs, <sup>57</sup> Co, and <sup>133</sup> Ba (with LYSO background) in (a) linear-mode and (b) non-linear-mode; corresponding regions in linear and non-linear measurements are shaded with the same color [77] | 5.11   |

|      |                                                                                                                                                                                                                                                              |        |

### LIST OF TABLES

| Tab | <u>ole</u> | <u> </u>                                                                           | age |

|-----|------------|------------------------------------------------------------------------------------|-----|

|     | 2.1        | Single-Photon Detectors Comparison [Image Source: Hamamatsu] $\ .$ .               | 9   |

|     | 2.2        | SPAD parameter variation with increasing independent variables (adapted from [17]) |     |

|     | 2.3        | Proposed CMOS SPAD Performance Summary                                             | 20  |

|     | 3.1        | Comparison of proposed ambient light sensor with prior art                         | 41  |

|     | 4.1        | Comparison of PWL-ADC with other recent non-linear ADCs                            | 63  |

|     | 5.1        | Performance Summary of Proposed Multichannel Analyzer                              | 80  |

### LIST OF APPENDIX TABLES

| $\overline{\text{Table}}$ |                          |  |  |  |  |  |  |  |  |  | - | Pag | <u>se</u> |

|---------------------------|--------------------------|--|--|--|--|--|--|--|--|--|---|-----|-----------|

| A.1                       | Calibration Isotope Data |  |  |  |  |  |  |  |  |  |   | 9   | )4        |

### Chapter 1: Introduction to Sensors

"First to fall over when the atmosphere is less than perfect; Your sensibilities are shaken by the slightest defect; You live your life like a canary in a coalmine"

- Gordon Sumner, Canary In A Coalmine

Humans, and indeed most living organisms, are constantly sensing their environments, both within and without. Sensing is a critical task that provides organic and inorganic systems with the information to take appropriate actions to accomplish their goals, which could be as diverse as threat detection and survival, regulating the temperature by turning a heater on or off, and closing the eyes in response to bright lights. While it is commonly believed that humans possess five senses: sight, smell, touch, hearing, and vision, as our understanding of the human body continues to evolve, this simplistic definition has been challenged. Nevertheless, irrespective of however many senses humans actually possess intrinsically, we have relied on additional sensors to augment or enhance our understanding of the world around us. An example of this is the canaries that were used in the mining industry until as recently as 1986, to detect colorless and odorless toxic gases such as carbon monoxide, which humans are not particularly good at detecting [1]. Fortunately, nowadays we have access to more humane, cheaper battery-powered gas sensors to do the same task.

Figure 1.1: High-level illustration of an electronic sensor system with the major signal processing blocks highlighted. Chapters corresponding to specific sub-system(s) are annotated.

In the modern era, the word "sensor" is almost universally interpreted to be an electronic system as shown in Fig. 1.1. A typical sensor signal chain comprises the following sub-systems:

- 1. Transducer: This converts the physical quantity of interest (eg: temperature, light, etc.) into an electrical quantity such as charge, current or voltage. Typically, the transducer output is quite small (pC, nA or mV) and requires amplification. Additionally, the input-output relationship can be linear or non-linear, and this information can be exploited by the signal processing blocks.

- 2. Analog Front-End (AFE): The primary task of this block is to amplify the input signal to obtain sufficient signal-to-noise (SNR) ratio and/or convert the input into a desired quantity, like current-to-voltage conversion in a transimpedance amplifier (TIA). Other tasks might include providing and controlling the appropriate bias for the transducer, and filtering and buffering prior to digitization.

- 3. Analog-to-Digital Converter (ADC): The ADC samples and quantizes the AFE output into a digital word, which allows further digital signal processing using computers. This is a mixed-signal block since it translates between the analog and the digital domain. Successive-approximation-register (SAR) ADCs are a popular architecture used in sensor systems with resolutions ranging between 8 to 16 bits.

- 4. Digital Back-End (DBE): The digital blocks comprise of a myriad of functions specific to the application of interest. These can range from simple ripple counting to histogramming to performing fast fourier transforms (FFTs). Increasingly, machine learning (ML) algorithms are also being implemented as part of the sensor's DBE.

- 5. Wireless Transmitter (TX): Modern sensor systems typically include wireless communication blocks for the DBE output to be transferred to a host device like a computer or a smartphone.

Just as the adoption of complementary metal-oxide-semiconductor (CMOS) manufacturing processes revolutionized the computing industry with the integration of billions of transistors in a single chip, sensor systems have also witnessed similar benefits from the adoption of CMOS as an enabling technology. Particularly, the progress in integrated circuit (IC) implementations of signal processing and wireless blocks has been instrumental. These sub-systems are often integrated at the die or package level resulting in even lower cost, ease of system implementation, and improved performance. However, true system-on-chip integration where all the components are on the same CMOS substrate remains a challenge; specifically, the integration of novel transducers for new sensing modalities and emerging applications [2].

With increased integration and lowered costs, there has been an explosion of sensors in consumer and industrial applications. This has been fueled by the evergrowing influence of digitization in our lives, the automation of tasks and entire industries, and the insatiable appetite for more "information". Indeed, the sensors market, one of the biggest drivers in the semiconductor industry, is projected to grow to a value of more than \$400 billion by 2026! With intelligent sensor nodes becoming ubiquitous, there has been a parallel growth in the amount of raw data generated by these nodes. According to a recent report [3], the number of sensors in the world will grow to  $\sim 45$  trillion by 2032, corresponding to a data generation rate of  $> 10^{20}$  bits/s. This is several orders of magnitude greater than the human data consumption rate of  $\sim 10^{17}$  bits/s. Thus, there exists a very clear and obvious need to develop sensors that are more data-efficient by generating relevant and useful information that can be acted upon by intelligent systems.

Figure 1.2: Sensor data projection from [3]

#### 1.1 Dissertation Outline

Having established some key challenges in modern sensor systems, this dissertation aims to address some of these. The rest of this dissertation addresses two broad goals:

The first goal was the CMOS implementation of novel transducers that do not require additional post-processing. Several single-photon avalanche diodes (SPADs) and a resistive transducer were fabricated for optical sensing and flow sensing applications respectively. Chapter 2 focuses on their design, while Chapter 3 highlights how a particular SPAD design allows it to be used for ambient light sensinsg, leading to a massive reduction in area and system complexity. Highly digital interface circuits for SPAD readout are also introduced.

The second goal was the investigation of non-linear ADCs (NL-ADCs) for application specific quantization characteristics. This can lead to reduction in digital data and DBE resource utilization. Chapter 4 introduces the design of a new prototype piecewise-linear ADC (PWL-ADC) that incorporates programmability to extend the role of a single NL-ADC across a wide range of applications. To highlight system-level benefits, a gamma spectrometer with programmable energy bins and wide dynamic range is introduced in Chapter 5. The multichannel analyzer (MCA) in the spectrometer comprises the PWL-ADC IC and a custom programmable AFE IC (both fabricated in  $0.18\,\mu{\rm m}$ . Besides the custom ICs, the spectrometer comprises a commercial silicon photomultiplier (SiPM) array and a FPGA-based DBE for recording linear and non-linear isotope spectra, demonstarting system level utility of the proposed ideas.

### Chapter 2: Transducers in Standard CMOS Processes

A transducer is the first "processing" block in a sensor system, since it converts the physical quantity of interest into a variation of an electrical quantity like charge, current, voltage or impedance that can then be processed by readout electronics. Implementing the transducer of a sensor system in the same substrate as the interface and processing circuits has several benefits. Primary among these benefits are higher levels of integration resulting in reduced area, easier interfacing with readout circuits, and often, significantly improved performance (lower noise, higher bandwidth) owing to significantly reduced interconnect and packaging parasitics. Since CMOS processes are the de-facto standard for implementing integrated circuits, especially digital IPs,

Figure 2.1: Examples of physical quantities and the corresponding CMOS-based transducer structures used to measure them in integrated sensors

it follows that realizing transducers in these processes is a highly useful exercise. Indeed, the widespread use of products like temperature sensors and image sensors in industrial, automotive, and consumer applications has been driven primarily by their CMOS implementations and continued innovations and improvements of these implementations. In the case of temperature sensors, the transducers are typically substrate *pnp* bipolar-junction transistors (BJTs), MOSFETs or a combination of polysilicon or diffusion resistors [4], while various flavors of reverse-biased *p-n* junction diodes are used as the pixels of image sensors [5]. In both cases, the structures are readily available in standard sub-micron CMOS processes and can be easily integrated with circuits. While specialized processes such as BiCMOS or dedicated CMOS Image Sensor (CIS) can be used to realize higher performance transducers, these tend to be more expensive, don't always scale well, and have limited IP vendors compared to standard CMOS processes.

Over the past couple of decades, novel CMOS-based transducers have not only continued to push the boundaries of existing sensing techniques, but have also given rise to entirely new types of sensors. For example, developments in CMOS single-photon avalanche diodes (SPADs) have pushed the boundaries of light detection and imaging, resulting in highly integrated imagers used in instrumentation for high-energy physics and the recent commercialization of Time-of-Flight (ToF) sensing for 3D imagers in smartphones. Similarly, Ion-sensitive field-effect transistors (ISFETs) realized in CMOS were instrumental in lowering the cost and processing time of DNA sequencing, and there is a growing body of work investigating their use in other electrochemical sensing applications.

The rest of this chapter focuses on two types of transducers implemented in standard CMOS processes: SPADs for optical sensing, and a resistive transducer for flow sensing. The goal here was to realize structures that can be used without any additional die-level post-processing. SPAD operation and design is particularly emphasized since Chapters 3 and 5 describe systems using SPAD-based sensors.

### 2.1 Single-Photon Avalanche Diodes for Optical Sensing

### 2.1.1 Background

### 2.1.1.1 Brief History of Single-photon Detectors

Single-photon counting and time-correlated photon counting techniques have been used in a wide range of fields for several years now: cryptography, astronomy, optical communications, bio-medical research and laser ranging, among several others [6], [7]. More recently, single-photon counting has gained more attention than ever before. Bio-medicine is an area where it is finding increased usage for various imaging techniques like fluorescene lifetime imaging (FLIM), positron emission tomography (PET), and time-resolved Raman Spectroscopy [8], [9]. The other big area of thrust for single-photon detection is light detection and ranging (LiDAR). Specifically, the application of LiDAR in 3-D imaging for autonomous vehicles has rapidly accelerated the development of high-performance, low-cost single-photon detectors [10].

Single-photon detection was first developed in the 1960s by exploiting the high current gain performance of photomultiplier tubes (PMTs) [6], [11]. For photon count-

ing, PMTs are operated at high bias voltages (> 100 V and upto 1 kV) to achieve an average current gain of around 10<sup>6</sup> [11]–[13]. These devices exhibit moderate stability and low noise even at such high gain levels [11]. However, they are bulky, fragile and are sensitive to magnetic fields [7], [13], [14]. Additionally, the high bias voltages require expensive power supplies. Therefore, PMTs are expensive and somewhat limited in the scope of their applications. Solid-state single-photon detectors came to the fore in the 1990s [6], [8], [11]. These devices have been referred to in the literature as silicon photomultipliers (SiPMs) and are built from scalable arrays of single-photon avalanche diodes (SPADs). SPADs are sometimes also referred to as Geiger-mode avalanche photodiodes (G-APDs). This is because the operating principle of SPADs is similar to that of Geiger-Muller counters [11]. Compared to PMTs, SiPMs and SPADs require much lower bias voltages (10s of Volts), are much smaller, scalable, sturdier and are insensitive to magnetic fields [6], [7]. SPADs also have much

Table 2.1: Single-Photon Detectors Comparison [Image Source: Hamamatsu]

| Device             | Photomultiplier Tube (PMT) | Silicon Photomultiplier<br>(SiPM) |

|--------------------|----------------------------|-----------------------------------|

| Image              |                            |                                   |

| Gain               | $\sim 10^6$ - $10^7$       | $\sim 10^{6}$                     |

| Bias               | 500 V - 1 kV               | 20 V - 60 V                       |

| Size               | Bulky                      | Compact & Scalable                |

| Noise              | Low                        | Medium                            |

| Magnetic<br>Resist | No                         | Yes                               |

higher detection efficiencies in the red and near-infrared (NIR) range [6]. A feature comparison of PMTs and SiPMs is shown in Table 2.1.

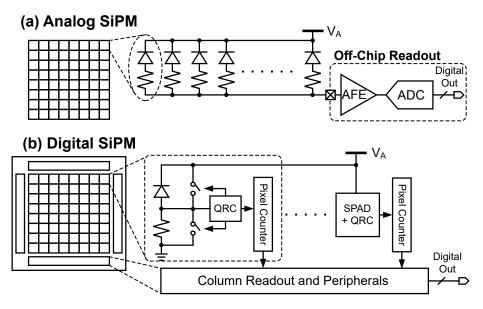

Until the early 2000s, silicon SPADs were fabricated exclusively through custom processes. This allows engineers to control dopant profiles and junction depths to tailor the device performance metrics like spectral response, detection efficiency, noise and timing jitter. SiPMs built from arrays such SPADs, continue to be manufactured in custom silicon processes by manufacturers for a variety of applications, particularly where large arrays and high fill-factors are required. Each pixel consists of a SPAD and an integrated quenching resistor in series with the SPAD. This type of SiPM is often referred to as "Analog" SiPM [15], since the output is an analog current pulse corresponding to incident photon flux. This is usually converted into a voltage by a transimpedance or charge amplifier, followed by digitization by an analog-to-digital converter (ADC) for computer recordings or digital signal processing (Fig. 2.2(a)). In these Analog SiPMs, the readout and processing electronics are external to the detector, which limits system integration, timing performance, as well as cost.

The next major milestone in SPAD design was the exploitation of CMOS processes to design planar SPAD structures. Standard CMOS processes constrain the development of fully customized structural features of SPADs such as doping levels, implant and diffusion depths, and well structures. The lack of access to specific process recipes from semiconductor fabs makes it almost impossible to perform reliable TCAD simulations to predict SPAD performance. As a result, CMOS SPADs typically perform worse when compared to fully customized SPADs. However, several groups have continued to work on developing better CMOS SPADs because of the

Figure 2.2: Conceptual views of (a) Analog SiPMs with off-chip readout and digitization circuits, and (b) Digital SiPMs with on-chip pixel-level integration of digitization and counting circuits.

ease of integration with other blocks on the same chip. These blocks include the analog/mixed-signal sensing circuits and the digital electronics for on-chip counting and photon timing processing [7]. In arrayed implementations, pixel-level integration of SPADs and circuits is made possible, resulting in digital outputs from each pixel (Fig. 2.2(b)). These arrays are sometimes referred to as "Digital" SiPMs [16] and can utilize counting-based techniques, greatly simplifying system complexity and cost. This makes CMOS SPADs a highly attractive low-cost and durable solution for a wide range of photon counting and timing based applications.

### 2.1.1.2 SPAD Operating Principle

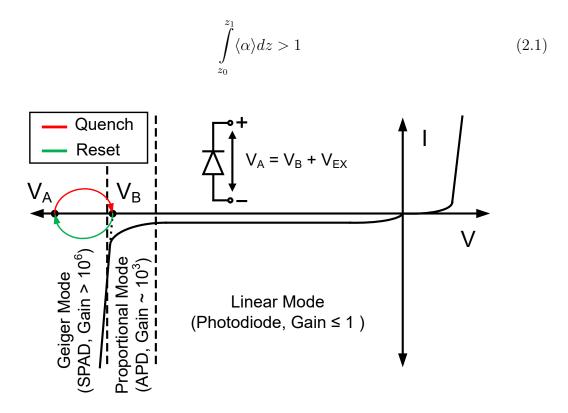

A SPAD is a p-n junction operating in the Geiger mode, i.e. reverse biased beyond its breakdown voltage,  $V_{\rm B}$  as shown in Fig. 2.3. Impact ionization is the mechanism by which the avalanche multiplication of charge carriers occurs in this mode. For the depletion region  $z_0 - z_1$  in Fig. 2.4, the breakdown voltage is defined as the voltage at which the mean ionization per free carrier,  $\langle \alpha \rangle$  equals unity [8], [17], [18]. Therefore, the condition for avalanche is defined by 2.1:

Figure 2.3: Different operating regions of a p-n junction diode based on applied reverse voltage. Photon sensitivity is maximized when the diode is operated in Geiger Mode as a SPAD.

Figure 2.4: Cross-section of a planar p-n junction formed between p+ and n doped silicon. Photon absorption in the multiplication region triggers avalanche breakdown.

The depletion region (shown in Fig. 2.4) is divided into multiplication and drift regions. The multiplication region is defined as the depletion width which contributes to 95% of the integral in (2.1) [17], [18]. The remainder is defined as the drift region. Due to the difference in ionization rates of electrons and holes, for a given doping in silicon, n + /p junctions have narrower multiplication regions compared to p + /n junctions [18]. This influences the peak wavelength that can be detected by a SPAD.

When a p-n junction is biased at a voltage  $V_{\rm A} = V_{\rm B} + V_{\rm EX}$ , where  $V_{\rm EX}$  is known as the excess voltage, the avalanche dynamics can be described as follows [19]: (i) an electron-hole pair is generated either by an absorbed photon or a thermal event; (ii) the number of electron-hole pairs rises exponentially around the primary carrier; (iii) the increase in current lowers the local electric field to the breakdown value due to the drop across the space-charge resistance; (v) the avalanche spreads to another part of the junction. This propagation can only occur in the multiplication region and

therefore, its sizing, relative to the drift region, is important. The mean propagation speed of the avalanche,  $v_p$  is given by

$$v_p = kI_f \tag{2.2}$$

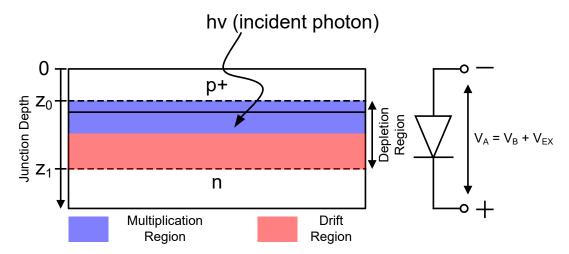

where  $I_f$  is the final avalanche current and  $k = 3 \,\mu\text{m}/(\text{ns-mA})$ ; (vi) the avalanche spreads across the entire junction and reaches a steady state value in the milliampere range in nanoseconds or sub-nanosecond time. The high current, if uncontrolled, can heat up and destroy the device. This necessitates lowering  $V_A$  below  $V_B$  to make  $I_f < 100 \,\mu\text{A}$  to ensure that the avalanche multiplication stops [6], [14]. This operation is known as quenching. In order to detect another photon,  $V_A$  needs to be brought back to above  $V_B$  and this operation is known as resetting or recharging. A large resistor (typically  $\geq 100 \,\mathrm{k}\Omega$ ) in series with the SPAD can be used as a simple quench and reset circuit as shown in Fig. 2.5. However, this scheme suffers from slow recharging, during which the SPAD can get triggered prior to a full reset, resulting

Figure 2.5: A resistor-based passive quench and reset scheme of a SPAD is shown in along with the transient behavior of the anode voltage during photon, DCR and afterpulse events.

in a lower amplitude pulse also known as an afterpulse, which is undesirable. For better timing control and performance, typically active circuits are used to speed up the quench and reset operation in CMOS SPAD pixels. These are explored in further detail in Chapter 3.

#### 2.1.1.3 SPAD Parameters

Some of the most commonly used parameters for evaluating and comparing SPAD performance, as reported in the literature, are:

- 1. Photon Detection Efficiency (PDE): This is defined as the ratio of the number of detected photons, i.e. the number of photons triggering avalanche events to the total number of photons incident on the active area of the SPAD [7]. As  $V_{\rm EX}$  is increased, the electric field increases, which in turn increases the ionization rate and also the probability of the triggering of an avalanche [6]. Therefore, PDE increases as  $V_{\rm EX}$  is increased. It is important to note that the nature and the depth of the junction plays an important role in determining which part of the electromagnetic (EM) spectrum is detected most strongly [17]. Therefore, PDE is reported as a function of the wavelength of incident photons.

- 2. Dark Count Rate (DCR): An avalanche event triggered without the incidence of a photon on the active area contributes to the DCR of a SPAD. The DCR effectively sets the noise floor and therefore, lowering it is often one of the main objectives while designing SPADs. There are two types of contributors to DCR; uncorrelated and correlated to detected photons [7]. The uncorrelated sources are: (i) Trap-assisted

thermal generation, also known as Shockley-Read-Hall (SRH) generation; (ii) Trapassisted tunneling; (iii) Poole-Frenkel emission and (iv) band-to-band tunneling [6], [7], [17]. Sources (i)-(iii) are strongly temperature dependent and (iv) is strongly dependent on electric field. Correlated sources include optical and electrical crosstalk between different pixels and afterpulsing in the same pixel.

3. Area: The active area of the junction that is sensitive to incoming photons impacts performance in several ways. Larger area obviously leads to a higher PDE, but at the cost of a higher DCR. Moreover, a larger area contributes to increased detector capacitance which degrades timing performance. In general, smaller area SPADs, typically with diameters of  $\sim 10 \,\mu \mathrm{m}$  are preferred, and arrays of such devices are used when large detection area is a requirement.

### 2.1.1.4 Design Considerations for CMOS SPADs

Standard sub-micron CMOS processes offer multiple implant layers and well structures, including p+, n+, p-well, n-well, deep-n-well, and p-substrate, any of which can be used to make planar SPAD junctions. Each pairwise p-n junction combination yields different performance characteristics for reverse-bias breakdown voltage, spectral response, DCR, and PDE.

While some SPAD implementations have leveraged high-voltage processes or specialized CMOS image processes to reduce dark count rate [20]–[23], many have used general purpose sub-micron CMOS processes [24]–[28]. Compared to conventional p+/n-well, an n+/p-well junction can be used to reduce parasitic capacitance [29]

and provide wider spectral response [30]. Junctions formed using lightly-doped layers, such as p-well/deep-n-well or n+/p-substrate, have also been demonstrated to reduce noise and improve quantum efficiency at longer wavelengths [22], [31], [32].

Aside from the selection of p-n junction layers, the choice of guard ring structure heavily influences SPAD performance as well [17]. The guard ring plays a key role in the prevention of PEB, and to a large extent it determines the total area of the SPAD detector, limiting overall fill-factor for a detector array [6]. Guard rings are frequently formed using p-well or n-well isolation for p+/n-well or n+/p-well high-field junctions, respectively. Placement of the guard ring around the junction plays a key role in SPAD performance, as does active area diameter [23]. A smaller active area has the benefits of improved timing resolution through faster impulse response, reduced DCR and after-pulsing, and minimal optical crosstalk, at the cost of lower sensitivity [17], [26].

In order to improve fill factor and density scaling, shallow-trench isolation (STI), standard in deep sub-micron CMOS processes, can be used as a guard ring [22]. The use of an STI guard ring may increase DCR and after-pulsing, attributable to increased trapped charges where the p-n junction edge abuts STI [26]. This increase in DCR due to STI can be mitigated using additional fabrication steps, such as hydrogen passivation or process stop masks to isolate the STI from the active area [29], [33]. Another approach uses the active mask to move the STI away from the p+ implant edge and uses a lightly doped p-well structure as a guard ring; these combined techniques enable a low DCR of 231 Hz [28].

Table 2.2: SPAD parameter variation with increasing independent variables (adapted from [17])

| Dependent | Independent | Junction<br>Depth | Diode<br>Area | Excess<br>Voltage | Temperature |

|-----------|-------------|-------------------|---------------|-------------------|-------------|

| DCR       |             |                   | <b>†</b>      | <b></b>           | <b>†</b>    |

| Blue PDE  |             | ↓                 |               | <b> </b>          |             |

| Red PDE   |             | <b>†</b>          |               | <b>†</b>          |             |

| Jitter    |             |                   | <b>↑</b>      | <b>\</b>          | <b> </b>    |

Clearly, there are several variables to consider when designing a CMOS SPAD device. These variables interact with each other and make the design process a non-trivial task. While TCAD simulations can provide some insight, empirical data is essential to characterize both existing and new designs. Thus, different planar CMOS SPAD structures were empirically characterized as part of this work and the results published in [34]. A few of these designs are highlighted in the next section. However, a few rules-of-thumb can still be useful to gain some intuition into the SPAD design/selection process and these are summarized in Table 2.2. An excellent detailed theoretical discussion of CMOS SPAD design can be found in [17].

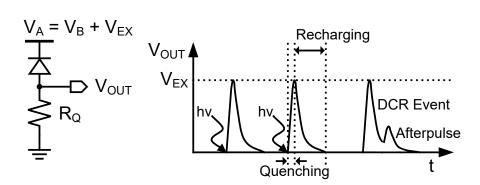

### 2.1.2 Proposed CMOS SPADs

Several structural variants of varying sizes were implemented in a general purpose  $0.18 \,\mu\text{m}$  CMOS process (TowerJazz CA18HD). Of these, a particular structure with a deep junction is further described in detail here. It is realized using the p-well and deep-n-well interface, as shown in Fig. 2.6, where a p+ contact provides the anode terminal of the device. In most CMOS processes, this structure will produce a lightly-doped active region, and subsequently the depletion region across the p-well/deep-n-

Figure 2.6: Cross-sections of variants of a p-well/deep-n-well SPAD implemented in TowerJazz CA18HD 0.18  $\mu$ m CMOS process with variable distance between STI and active area to investigate impact on DCR [34].

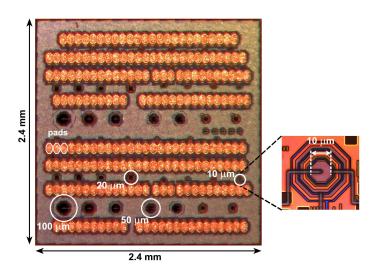

well junction will be wider than in a p+/n-well structure [22]. The n-well acts as a guard ring and isolates the active junction from the p-type substrate. STI is located between the p+ and n-well for electrical isolation, using the active mask for defining STI boundaries, which may require a design rule waiver in some processes. Multiple size variants of this SPAD were implemented by varying the active junction diameter, including  $10 \,\mu\text{m}$ ,  $20 \,\mu\text{m}$ ,  $50 \,\mu\text{m}$ , and  $100 \,\mu\text{m}$  structures. A  $10 \,\mu\text{m}$  variant of this device was also implemented in which the STI was placed at a distance of  $1.5 \,\mu\text{m}$  further from the active p+ region to characterize the effect of STI proximity (Fig. 2.6). The final test IC die size measuring  $2.4 \,\text{mm} \times 2.4 \,\text{mm}$ , and an annotated die photo of the fabricated IC is shown in Fig. 2.7.

Figure 2.7: Test die with multiple planar SPAD variants, implemented in TowerJazz CA18HD  $0.18 \,\mu\mathrm{m}$  CMOS process [34].

The characteristics of the p-well/deep-n-well CMOS SPAD is summarized in Table 2.3. As expected, owing to the deeper and more lightly doped junction, the SPAD has a higher breakdown voltage of 16.4 V compared to that of variants with a shallower junction with higher dopant concentration (11.2 V for p+/n-well and 12.1 V for n+/p-sub). Additionally, because of the deeper junction, the PDE peaks at a lower wavelength of 400 nm compared to the usual  $\sim 500-550$  nm for standard shallow junctions devices. Finally, the SPAD variant with the STI placed further from the junction edge has a significantly lower DCR for the same  $V_{\rm EX}$ , thus validating the

Table 2.3: Proposed CMOS SPAD Performance Summary

| Process             | Junction | $egin{aligned} 	ext{Breakdown} \ 	ext{Voltage} \ 	ext{(V}_{	ext{B}}) \end{aligned}$ | Active<br>Area         | ${ m DCR} \ ({ m V_{EX}} = 0.5{ m V})$ | $egin{aligned} 	ext{Peak PDE} \ (	ext{V}_{	ext{EX}},	ext{@}\lambda) \end{aligned}$ |

|---------------------|----------|-------------------------------------------------------------------------------------|------------------------|----------------------------------------|------------------------------------------------------------------------------------|

| $0.18\mu\mathrm{m}$ | pw/dnw   | $16.4\mathrm{V}$                                                                    | $85  \mu \mathrm{m}^2$ | STI Close: 32 kHz<br>STI Far: 16 kHz   | $2.7\% (0.4 \mathrm{V}, \\ @400 \mathrm{nm})$                                      |

impact of STI distance on DCR performance. For detailed characterization data of the implemented CMOS SPAD variants, the reader is referred to [34].

## 2.2 Resistive Transducer for Flow Sensing

## 2.2.1 Background

Volumetric flow rate and flow velocity of fluids is used in several automobile, environmental, and medical applications. Most flow sensors use thermal techniques and comprise a heater element which provides a known amount of heat, and a separate sensing element which is cooled at a rate depending on the fluid flow rate, thus providing flow related information. Modern low-power flow sensors are highly miniaturized chipscale sensors ( $\mu$ m to mm scale) owing to techniques such as micro-electromechanical systems (MEMS) fabrication [35], and CMOS-compatible transducers such as metal heaters and silicon thermopiles [36], [37]. These techniques, however, almost always require dedicated custom fabrication processes or post-fabrication steps, increasing cost, complexity and difficulty of integration with other sensors.

# 2.2.2 Proposed Integrated Single-Element Flow Sensor

A novel single-element flow sensor is proposed and fabricated in a standard 0.18  $\mu$ m CMOS process. Such a flow sensor that is integrated into a CMOS IC substrate, requires exposure of the heating and sensing elements at the top or bottom chip surface. The transducer used in the sensor is a single resistive element that is realized

in CMOS top metal layers and does not require any post-fabrication. This allows topside interfacing of the flow sensor. Thus, sub-millimeter miniaturization is achieved, which combined with the top-side interface of the sensor enables integration with other CMOS-compatible optical sensors (such as the ones presented in Section 2.1) and micron-scale fluidic channels [38], for lab-on-chip and lab-on-CMOS applications. The choice of top-side interface limits the use of front-end-of-line (FEOL) CMOS layers, such as high-resistivity polysilicon, which could be otherwise used to realize smallarea, large-value resistors to enhance sensitivity. Moreover, FEOL sensors would require flip-chip packaging for backside thermal interface, often using a thinned silicon substrate [39], [40].

For a top-side sensor interface, BEOL top metal layers can be used to implement the sensor element. The element must have low enough resistance to enable heating using CMOS-compatible voltage levels, and large enough resistance to measure useful changes in flow rate; this requires an element on the order of several hundred ohms for the proposed architecture. Implementation using exclusively CMOS top metal is area-inefficient, as this layer has low sheet resistance due to its primary intended use for power routing and I/O. In contrast, electrical vias in modern CMOS processes are typically micron-scale tungsten structures, which have significantly higher resistivity compared to metal routing layers, with  $1-2\Omega$  per via for standard PDK via dimensions. A resistor structure that primarily comprises via resistance can achieve much higher resistance per area than using only planar metal layers.

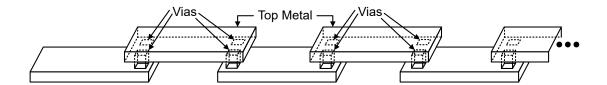

The resistive transducer used in this work employs a vertically serpentine structure that alternates between the top metal layer and the next lower metal layer through

Figure 2.8: 3-D illustration of the structure of the on-chip resistive sensing element formed in the top CMOS routing layers, where each layer change consists of two electrical vias in parallel; this ensures support of sufficiently high current densities, while still maintaining a high resistance density [42].

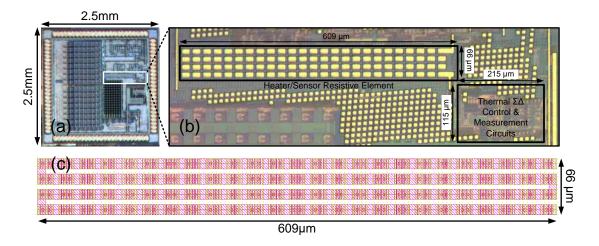

electrical vias, as shown in Fig. 2.8, which is then arranged in a planar serpentine layout. Using this approach, a resistance of approximately  $500\,\Omega$  is achieved within a sub-millimeter footprint, as shown in the chip photograph and the annotated CAD layout in Fig. 2.9. Almost all of the resistance can be attributed to the via resistance, which was validated by simulation using extracted parasitic resistances. Compared to the standalone discrete metallic element in [41], for the same resistance value, this CMOS-integrated approach reduces area by a factor of approximately 250. The entire flow sensor (resistor, and control and measurement circuits) occupies an active area of  $0.065\,\mathrm{mm}^2$ .

The resistor was heated using an off-chip current source, while integrated circuits employing thermal  $\Sigma$ - $\Delta$  techniques (highlighted in Fig. 2.9(b)) were used for heating control and sensor measurement. A 20.5  $\Omega$  change was observed over a range of 19 °C to 64 °C for a measured sensitivity of 0.45  $\Omega$ /°C. Experimental results in a air flow chamber demonstrated the feasibility of the fully integrated CMOS anemometer for air flow rate measurements. Detailed explanation of the system and flow measurements is outside the scope of this chapter and the reader is referred to [42] for further details.

Figure 2.9: (a) Chip photo with integrated flow sensor highlighted, (b) zoomed view of flow sensor blocks, and (c) computer layout of heator/sensor resistive element.

### 2.3 Conclusion

The benefits of integrating transducers in CMOS substrates were highlighted in this chapter. Several SPAD variants and a novel top-metal resistor were implemented in general purpose CMOS processes, without any die-level post-processing. The SPADs were characterized standalone and various design trade-offs were explored and validated using measured data. An example of the system-level integration of CMOS SPADs is further explored in Chapter 3. The top-metal resistor was used as a transducer in a compact single-element integrated CMOS air flow sensor and chip measurements were used to validate the proposed idea.

#### Chapter 3: Front-End Interface Circuits

The output of a transducer is typically a weak analog (continuous-time and continuous-amplitude) signal in the form of charge, current or a voltage. It requires signal conditioning such as amplification, modulation, and filtering, before being read out as an analog value or being digitized by an analog-to-digital converter (ADC). These tasks are done by analog circuits such as amplifiers and filters. These circuits or others might also be responsible for providing appropriate bias conditions for the transducer, and also transform the input signal to a different form (eg: current-to-voltage or vice-versa). Collectively, the set of analog circuits that interface with the transducer are known as the analog front-end (AFE).

This chapter introduces a few popular AFE architectures followed by a brief overview of readout circuits for single-photon avalanche diodes (SPADs). A SPAD-based digital ambient light sensor is used as a case study to understand how transducers can impact the AFE and system design significantly. Additionally, a programmable AFE is also introduced for the readout of silicon photomultiplier (SiPM) arrays. This is covered in Chapter 5 since it forms part of a larger gamma spectroscopy system.

#### 3.1 Readout Circuit Architectures

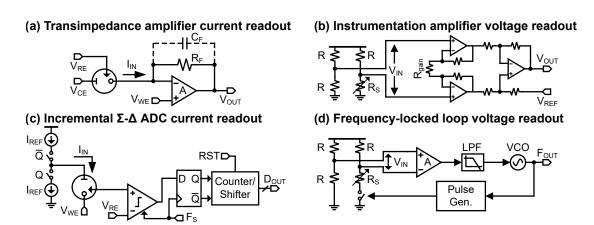

Two popular AFE circuit architectures are shown in Fig. 3.1(a-b). Current sensing is a popular technique used widely in biosensors for measuring very small currents ranging from few fA to several uA [43]. The most common readout scheme employed for this the classic continuous-time transimpedance amplifier, employing a feedback resistor  $(R_{\rm F})$  with an operational amplifier (op amp), as shown in Fig. 3.1(a). The output voltage can then be digitized by a conventional voltage-domain ADC. Discrete-time implementations replace the  $R_{\rm F}$  with a parallel combination of a capacitor and a reset switch [43]. On the other hand, for a voltage reading such as the output of a wheatstone bridge measuring temperature, strain, etc., a popular technique is to use an instrumentation amplifier as shown in Fig. 3.1(b). The small input voltage is multiplied by by a gain factor prior to digitization by an ADC [44]. More recently, highly compact and digital implementations for both types of AFEs (highlighted in

Figure 3.1: Common AFE architectures are shown in (a) and (b). Sensor-in-the-loop architectures with combined AFE and ADC functionalities are shown in (c) and (d).

Fig. 3.1(c-d)) have become popular in the literature where the AFE and ADC functionalities are combined in the front-end block, often also including the transducer in the loop [45], [46]. This results in early digitization resulting in programmable resolution and dynamic range performance with compact areas for easier system-on-chip (SoC) integration. These new architectures are also attractive from the perspective of CMOS technology node scaling, which inherently favors digital circuit performance.

Clearly, for highly integrated sensor SoCs, compact architectures that combine AFE and ADC functionalities are quite attractive. However, this trend is still reliant on an inherently analog input signal that is small and can be sensitive to issues such as switching-induced noise, jitter or mismatch in the readout circuits [45], [46]. As noted in Chapter 2, the output of a SPAD is a digital-like pulse when triggered by a photon. Over time, the output is a train of pulses with the average pulse rate corresponding to the incident photon flux. This output can be easily processed with digital counters and filters. Thus, the task of signal digitization is internal to the transducer, opening the door for use as highly digital sensors that are ideal for SoC integration. For proper SPAD operation, appropriate readout circuits are required and are introduced in the next section.

#### 3.2 Readout Circuits for SPADs

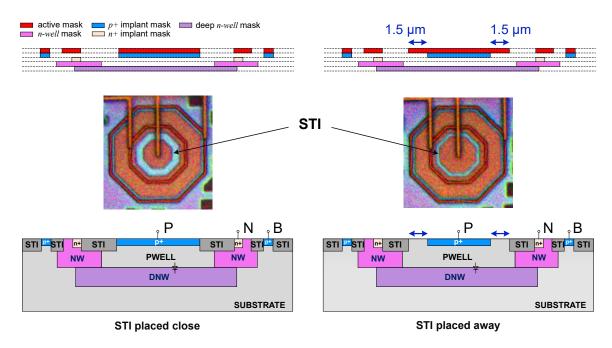

As was noted in Chapter 2, a SPAD requires quenching and recharging, often done by a large series resistor  $R_{\rm Q} > 100 \, \rm k\Omega$ . However, this limits the dead time,  $T_{\rm DEAD}$ , during which no new photons can be detected. It also leads to noise in the form of increased

afterpulsing probability due to a slow recharge (up to several  $\mu$ s). To achieve faster quenching and recharging, active circuits are employed. These are often collectively labeled as active quench and reset circuits (AQRCs) or simply quench and reset circuits (QRCs). A purely active quench and active reset circuit is rarely used [14]. Most often, either a passive quench-active recharge scheme or a mixed active-passive quench and active recharge scheme is used as shown in Fig. 3.2. The SPAD anode is connected to a large impedance (large resistor or MOSFET in triode) for passive quenching, and also to the active quench and reset switches. This takes advantage of the inherently short quench time and focuses on minimizing the recharge (or reset) time,  $T_{\text{RESET}}$ . It is also beneficial in terms of area and fill-factor, when compared to purely active QRCs. When the SPAD is triggered, a large current flows through it and the large series impedance, bringing the anode voltage up. This operation is similar to passive quenching. After time  $T_{\text{DELAY}}$ , the voltage crosses  $V_{\text{TH}}$  and triggers the active quenching through  $S_{\rm Q}$ . This accelerates SPAD quenching, bringing the bias voltage below breakdown. After a defined duration,  $T_{\text{HOLD}}$  during which the SPAD is held in quenched state, the SPAD is actively reset to its original pre-trigger bias condition through  $S_{\rm R}$ . To ensure proper recharging, the SPAD is held in this state for

Figure 3.2: Mixed quench and reset scheme used with SPADs and associated timing diagram [14].

a sufficiently long time,  $T_{\text{RESET}}$ .  $T_{\text{HOLD}}$  and  $T_{\text{RESET}}$  are well determined parameters which the QRC is designed to control. For mixed QRCs, the dead time is therefore defined as  $T_{\text{DEAD}} = T_{\text{DELAY}} + T_{\text{HOLD}} + T_{\text{RESET}}$  [47].  $T_{\text{HOLD}}$  should be optimized to be long enough to minimize afterpulsing but not too long that the maximum count rate gets compromised [14]. For values in 100s of ns,  $T_{\text{DEAD}} \approx T_{\text{HOLD}}$  is a reasonable approximation, since this dominates over the other two terms. With appropriate sizing and supply voltage, the comparator in Fig. 3.2 can be replaced with a simple inverter. Such a QRC is introduced as part of the following case study.

## 3.3 Case Study: Digital Ambient Light Sensor

#### 3.3.1 Introduction

Ambient light sensors are used in a wide range of applications including display backlight control in portable devices, building interior lighting, proximity sensors, smart street lights, and automotive lighting control (Fig. 3.3). With the increasing adoption of automation in industrial and commercial applications, such sensors have become a critical component in control loops for automated systems to conserve power and perform their required tasks. Cost, ease of implementation, and power consumption drive the selection of such sensors.

A typical CMOS-integrated ambient light sensor uses one or more photodiodes for converting light intensity to a proportional current value. This photocurrent is then read out and digitized by one of the many available readout circuits. Some of the commongly used techniques are highlighted in Fig. 3.4. One of the most popular techniques involves amplifying and converting the photocurrent, usually in the pAnA range for reasonably sized photodiodes, to a suitable voltage using a continuous-time transimpedance amplifier (TIA). This voltage is then digitized by an analog-to-digital converter (ADC). Dual-slope ADC-based architectures, such as the one reported in, can provide excellent resolution at the cost of reduced bandwidth, which is an acceptable trade-off for ambient light measurements. Schemes with mostly digital circuits have also been demonstrated, such as a comparator-based light-to-frequency converter in [48] and a VCO-based readout in [49]. In all of these implementations, the intrinsically analog nature of the photodiode output puts stringent requirements on the interfacing analog or mixed-signal blocks with stability, noise, resolution, and matching being critical. Additionally, for sufficient signal-to-noise levels and dynamic range, the photodiodes have to be large enough, often  $\geq 10^4 \, \mu \text{m}^2$ , to generate a large

Figure 3.3: Common applications for ambient light sensors

enough photocurrent. All of the aforementioned factors end up resulting in systems with large silicon area, design complexity, high power, and high cost. Optical filters are also often used leading to additional post-processing and packaging complexity.

Figure 3.4: Example photodiode readout circuits

In this work, we present the design and measured performance of an all-digital ambient light sensor implemented in a standard CMOS process, which leverages the pulse-based, digital-like behavior of single-photon avalanche photodiodes. Combined with digital front-end and processing circuits, this approach achieves a significant reduction in circuit area and required photodiode area.

Figure 3.5: A high-level architecture schematic of the proposed all-digital ambient light sensor [50].

#### 3.3.2 Proposed System

The high-level architecture of the all-digital CMOS ambient light sensor based on a single-photon avalanche diode (SPAD) is shown in Fig. 3.5. In contrast with a typical reversed-biased photodiode detector, which produces a steady current, a SPAD device outputs a train of current pulses proportional to incident light intensity, which can be used to charge the gate of an inverter to produce squared digital pulses. Used this way, a SPAD is a light-to-frequency converter with a digital output.

By exploiting the "digital-like" operation of an individual SPAD device, which eliminates the need for a TIA and general purpose ADC, design effort and circuit area for the sensor readout can be greatly reduced. The inherent signal amplitude noise immunity of the pulse-based SPAD output allows large-area, static power-intensive analog blocks to be replaced by simple dynamic CMOS digital circuits such as counters, registers, and control logic. In addition to the inherent decrease in area and power consumption, the ability to synthesize processing circuits using standard cells further decreases design complexity.

The following sub-sections briefly describe SPAD operation and its use as an ambient light sensor.

#### 3.3.2.1 SPAD Operating Principle

A SPAD device is structurally similar to a standard photodiode. Both comprise a p-n junction diode with a reverse breakdown voltage,  $V_B$ . However, for the diode to function in Geiger mode as a SPAD, the applied reverse bias,  $V_A$ , must be greater than  $V_B$ . Under this condition, upon excitation by a photon, junction breakdown results in a runaway avalanche multiplication, which continues until a high current value is reached, limited only by  $V_A$  and the internal resistance of the diode. By employing passive or active quench and reset circuits (QRC), the bias across the diode can be brought quickly below  $V_B$  to protect from over-current, and the diode can be reset to detect another photon [51]. A stream of current pulses are produced, where pulse height carries no information; pulse current is the same whether one photon or multiple concurrent photons are absorbed. Since light intensity corresponds to the rate of photon arrival, the pulse rate is instead used to determine light intensity. An avalanche event can also be triggered by a thermal event, which contributes to the noise floor of the SPAD, or dark count rate (DCR).

Compared to standard photodiode detectors, SPAD structures must include a guard ring around the p-n junction to limit premature edge breakdown. In deep sub-micron CMOS processes, this can be implemented using shallow trench isolation and well structures [28], [51]. The layout and the cross-section of the SPAD structure

Figure 3.6: SPAD characteristics with a digital readout and operation across varying light intensity.

used in this work are shown in Fig. 3.7, which was implemented in a 0.13  $\mu m$  CMOS process.

# 3.3.2.2 Using SPAD for Ambient Light Sensing

As the name suggests, SPADs can be triggered by single photons and are extremely sensitive devices. They are typically used in applications such as fluorescence lifetime imaging or time-of-flight and radiation detection, where extremely low visible light intensities are of interest (< 0.1 lux). Due to the high sensitivity and inherent DCR, SPADs are easily saturated in light conditions greater than a few 10s of lux as shown in Fig. 3.6(c). For use in ambient light,  $V_{\rm A}$  may be decreased to reduce the photon

Figure 3.7: (a) Top view of SPAD layout in  $0.13 \,\mu\mathrm{m}$  CMOS process and (b) illustrated cross-section of the SPAD showing metal fill-based filter. [50].