### AN ABSTRACT OF THE DISSERTATION OF

Yusang Chun for the degree of Doctor of Philosophy in Electrical and Computer Engineering presented on June 17, 2020.

Title: <u>Design of Energy-Efficient Equalization and Data Encoding/Decoding</u> Techniques for Wireline Communication Systems

Abstract approved:\_

Tejasvi Anand

Ever increasing global internet data traffic has driven up the demand for cuttingedge high-speed wireline communication systems including SerDes PHY for various interfaces, interconnects, data centers servers and switches in optical systems. Operating wireline communications at higher data rates leads to signals suffering from greater channel loss and exponential increase in power consumption, mainly caused by a heavier amount of required equalization.

In this dissertation, two distinct methodologies for designing SerDes transceivers are presented: 1) a pulse width modulated (PWM) time-domain feed forward equalizer (FFE) and linearity improvement technique for higher-order pulse amplitude modulation (PAM) including PAM-8, and 2) an inter-symbol interference (ISI)-resilient data encoding and decoding technique with Dicode encoding and error correction logic for low-bandwidth wireline channels, as an alternative strategy for communicating in an energy-efficient way on bandwidth-limited wireline channels without using conventional equalizers or filters. The first topic is a PAM-8 wireline transceiver with receiver-side pulse-widthmodulated (PWM) or time-domain based feed forward equalization (FFE) technique. The receiver converts voltage-modulated signals or PAM signals to PWM signals and processes them using inverter based delay elements having rail to rail voltage swing. Time-to-voltage and voltage-to-time converters are designed to have nonlinearity with opposite signs with the aim of achieving higher front-end linearity on the receiver. The proposed PAM-8 transceiver can operate from 12.0 Gb/s to 39.6 Gb/s and compensates 14 dB loss at 6.6 GHz with an efficiency of 8.66 pJ/bit in 65 nm CMOS.

The second topic is an alternative strategy for communicating on bandwidthlimited wireline channels without using conventional equalizers or filters (FFE, DFE, and CTLE): Inter-symbol interference (ISI) resilient Dicode encoding and error correction for low-bandwidth wireline channels. The key observation is that Dicode-encoded data have no consecutive 1s or -1s. With this known information, the error correction logic at the receiver can correct multi-bit errors due to ISI. Implemented in 65 nm CMOS, the proposed digital encoding and decoding approach can achieve BER less than  $10^{-12}$  while communicating on a channel with an insertion loss of 24.2 dB and 21.4 dB with 2.56 pJ/bit and 2.66 pJ/bit efficiency while operating at 13.6 Gb/s and 16 Gb/s, respectively. ©Copyright by Yusang Chun June 17, 2020 All Rights Reserved

### Design of Energy-Efficient Equalization and Data Encoding/Decoding Techniques for Wireline Communication Systems

by

Yusang Chun

### A DISSERTATION

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented June 17, 2020 Commencement June 2021 Doctor of Philosophy dissertation of Yusang Chun presented on June 17, 2020.

APPROVED:

Major Professor, representing Electrical and Computer Engineering

Head of the School of Electrical Engineering and Computer Science

Dean of the Graduate School

I understand that my dissertation will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my dissertation to any reader upon request.

Yusang Chun, Author

### ACKNOWLEDGEMENTS

There were times during my Ph.D. program that I became fragile and vulnerable, although I don't regret that I have chosen this path as it helped me grow and mature both academically and personally. Thanks to the support from professors, mentors, colleagues, friends, and family, I managed to hold on from the beginning to even until this very moment. I am truly honored to express my gratitude toward all the people that help me finish my degree.

Above all, I am the most grateful to my advisor, Professor Tejasvi Anand. His genuine enthusiasm to research inspired me the most to help me stay focused. Not only he taught me academic knowledge from the bottom, but also there were considerate lessons that he shared with me as a person who truly understands and sympathizes. I feel really honored to be his first Ph.D. graduate. I also thank Professor Un-Ku Moon, Professor Kartikeya Mayaram, and Professor Arun Natarajan. I feel sincerely honored to have the greatest professors to be the committee members. My gratitude also goes to Professor Hyun Seok Lee for being kind enough to be my respectable Graduate Council Representative.

Even though I might not be his most proud student, I would like to show my deepest respect to my master's advisor Professor Deog-Kyoon Jeong from Seoul National University as well. When I first met him in 2011, I was just one undergraduate student wanting to pursue an analog circuit design career, knowing nothing about it. Even long after I graduated, he still leads me to all the opportunities and learnings without anything in return. None of my Ph.D. work would have been possible without the help of my colleagues, especially Ashwin Ramachandran and Mohamed Megahed, who have been my second advisors. Also, Hyunkyu Ouh and Jinyong Kim were kind enough to be my brothers and helped overcome homesick together. I also thank all the colleagues from OSU analog and mixed signal (AMS) group from the past to the present including Calvin Lee, Subramanian T R, Abhishekh Devaraj, Zhiping Wang, and Xiaohui Lin. I will never forget all the memories we shared here in our office and lab.

I would like to thank Yohan Frans, Jay Im, Kevin Zheng, Haritha Eachempatti, and Xilinx SerDes team who generously provided me with the most valuable internship opportunity. I feel lucky to have been with the nicest mentors and atmosphere, and I truly enjoyed every moment working and interacting with the team. My special thanks go to Kuan-Chang Xavier Chen who made the internship period much more enjoyable. I deeply appreciate Jaeduk Han and Dongwook Kim who shared their most valuable advices and information whenever necessary. Lastly, I have nothing but sincere gratitude to Tamer Ali and MediaTek team members for accepting me in this unprecedented era. I am thrilled to join this great company and contribute whatever I am capable of.

To all my friends, classmates, and colleagues in Korea, I thank you all for welcoming me whenever I visit as if I were there in the first place. As much as I miss the old times spending time with you, it also provides me with the energy to move forward. To my brother Daein, I am glad that I have someone I can trust as much as I trust you. I wish you all the best with the residency program as I am certain that you will be a great internist. To Minjae, Donghyung and Seungmin, and all the other friends I have in Corvallis, I thank them for making my time in Corvallis much less depressing.

Finally, to my family, there is simply no word that could possibly describe how thankful I am to the greatest love you gave to me. I am always too foolish to realize how important the family means to me before leaving them. I hope we can see each other more often as I will live in a bigger city. I will be trying my best to serve and care after you from now on. In loving memory of my grandfather and grandmother who passed away during my Ph.D., I was so lucky that I manage to stay healthy under your care. As I am working on my final defense and dissertation, human being is facing the unprecedented Coronavirus outbreak. Hope we all get through this soon and go back to the normal life that we were so used to before. Thank you very much.

## TABLE OF CONTENTS

1

$\mathbf{2}$

3

| Introduction                                                                                                                                                       | 1  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1 Introduction to PAM-8 Wireline Transceiver with Time-Domain Equal-<br>ization and Linearity Improvement Technique                                              | 1  |

| 1.2 Introduction to Transceiver Design with ISI-Resilient Data Encoding<br>for Equalizer-Free Wireline Communication using Dicode Encoding and<br>Error Correction | 5  |

| PAM-8 Transceiver with Time-Domain (PWM) Feed Forward Equalization                                                                                                 |    |

| and Non-linearity Cancellation Technique                                                                                                                           | 8  |

| 2.1 Linearity Requirement on Pulse Amplitude Modulated Signal                                                                                                      | 8  |

| 2.2 Proposed Transceiver Architecture                                                                                                                              | 11 |

| 2.2.1 Track-and-Hold and Voltage-to-Time Converter                                                                                                                 | 12 |

| 2.2.2 FFE Delay Lines Using Inverters and a Replica DLL                                                                                                            | 13 |

| 2.2.3 Time-to-Voltage Converter                                                                                                                                    | 15 |

| 2.2.4 Effect of Timing Jitter on Time-to-Voltage Converter                                                                                                         | 16 |

| 2.2.5 Receiver Amplifier $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                     | 17 |

| 2.3 Proposed Linearity Improvement Technique                                                                                                                       | 19 |

| 2.3.1 Transfer Function of Voltage-to-Time Converter                                                                                                               | 19 |

| 2.3.2 Transfer Function of Time-to-Voltage Conversion $\ldots \ldots \ldots$                                                                                       | 21 |

| 2.3.3 Overall Receiver Front-End Transfer Function with Linearity                                                                                                  |    |

| Improvement Technique                                                                                                                                              | 23 |

| 2.3.4 Limits of Linearity Improvement                                                                                                                              | 24 |

| 2.4 Measurement Results                                                                                                                                            | 29 |

| Equalizer-Free Wireline Transceiver with ISI-Resilient Data Encoding for Wire-                                                                                     |    |

| line Communication – Dicode Encoding and Error Correction                                                                                                          | 34 |

| 3.1 Dicode as ISI Resilient Encoding and Error Correction Concept                                                                                                  | 34 |

| 3.2 Proposed Architecture                                                                                                                                          | 35 |

3.2.1 Pre-coder and Evolution of Transceiver Architecture . . . .

3.2.3 Noise Budget of Transceiver

3.2.4 Error Correction Logic-1

3.2.5 Error Correction Logic-2

#### Page

38

39

39

43

45

# TABLE OF CONTENTS (Continued)

| —                                                                       |    |

|-------------------------------------------------------------------------|----|

| 3.3 Comparison to Existing Techniques                                   | 48 |

| 3.3.1 Differences and Advantages over Feed Forward Equalizers (FFE)     |    |

| and Tomlinson-Harashima Pre-coding                                      | 48 |

| 3.3.2 Differences and Advantages over Decision Feedback Equaliza-       |    |

| tion $(DFE)$                                                            | 49 |

| 3.3.3 Differences and Advantages over Duobinary                         | 52 |

| 3.3.4 Differences with Line Coding Schemes                              | 52 |

| 3.3.5 Differences and Advantages over Prior Dicode Works $\ldots$       | 53 |

| 3.3.6 Differences with Conventional Forward Error Correction (FEC)      |    |

| Coding                                                                  | 54 |

| 3.4 Mathematical Limit of the Proposed Error Correction Scheme $\ldots$ | 55 |

| 3.5 Measurement Result                                                  | 63 |

| 4 Conclusions                                                           | 69 |

| Bibliography                                                            | 70 |

## Page

## LIST OF FIGURES

| Figure |                                                                                                                                                                                                                                                                                                                                                                                                               | Page       |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

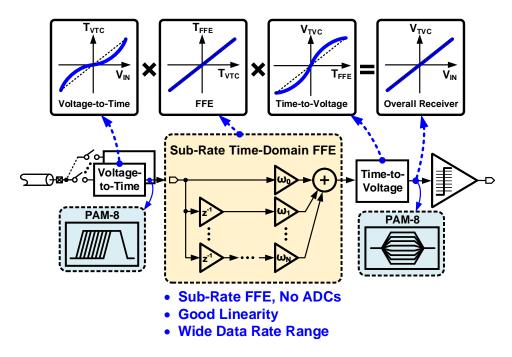

| 1.1    | Conceptual diagram of the proposed transceiver with time-domain feed forward equalization and linearity improvement technique.                                                                                                                                                                                                                                                                                | 4          |

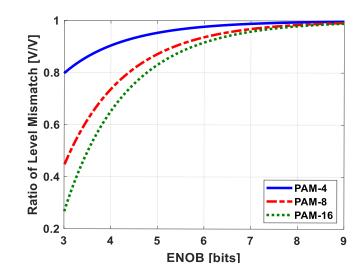

| 2.1    | Relationship between ratio-of-level mismatch (RLM) and effective-numb<br>of-bits (ENOB) in PAM-4, 8, and 16                                                                                                                                                                                                                                                                                                   | oer-<br>10 |

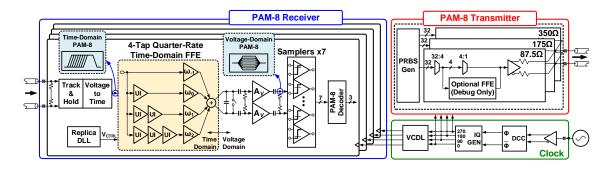

| 2.2    | Proposed PAM-8 transceiver architecture with a time-domain 4-tap feed forward equalizer (FFE) on the receiver                                                                                                                                                                                                                                                                                                 | 11         |

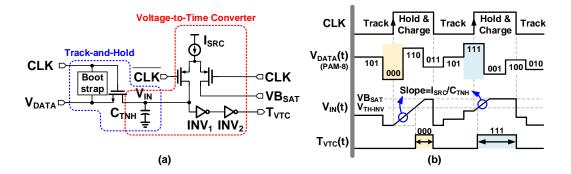

| 2.3    | (a) Schematic of the single-ended track-and-hold and voltage-to-time converter and (b) timing diagram illustrating its operation                                                                                                                                                                                                                                                                              | 12         |

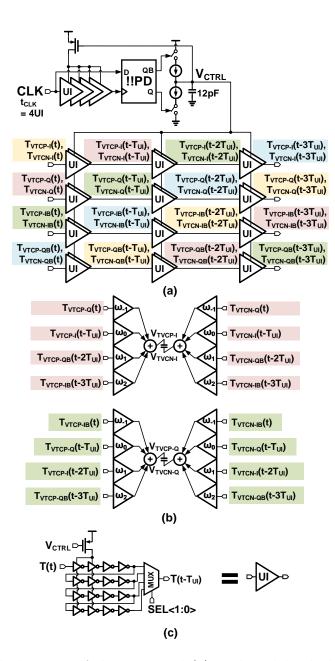

| 2.4    | Block diagram of the proposed (a) replica delay-locked loop, (b) 4-tap quarter-rate FFE summers (only I and Q lanes are presented in figure), and (c) programmable unit interval delay element                                                                                                                                                                                                                | 14         |

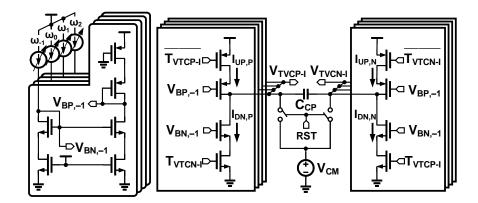

| 2.5    | Schematics of I-lane of the proposed time-to-voltage converter (TVC) in a quater rate receiver.                                                                                                                                                                                                                                                                                                               | 15         |

| 2.6    | (a) Simplified representation of one tap segment of the proposed time-<br>to-voltage converter (TVC). (b) Timing diagram of the TVC operation<br>and eye diagram of the output of the charge pump $V_{TVCP}$ or $V_{TVCN}$<br>without any input data jitter. (c) Timing diagram of the TVC oper-<br>ation and eye diagram of the output of the charge pump $V_{TVCP}$ or<br>$V_{TVCN}$ with input data jitter | 16         |

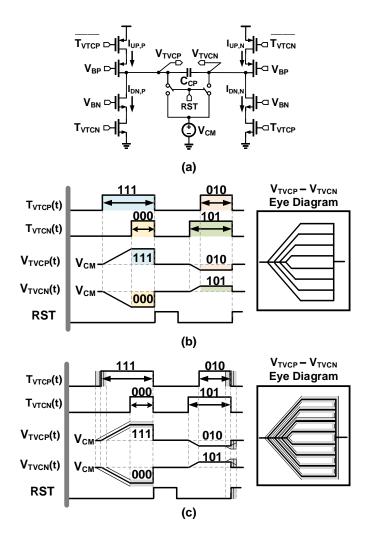

| 2.7    | Proposed linearity improvement technique in the receiver front-end<br>by using voltage-to-time and time-to-voltage converters with opposite<br>non-linearity.                                                                                                                                                                                                                                                 | 18         |

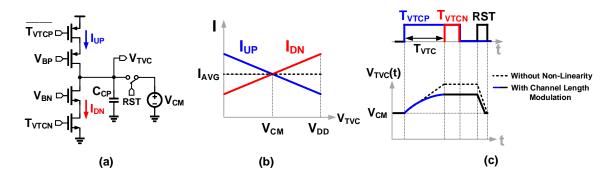

| 2.8    | <ul> <li>(a) Simplified schematic of a single-ended time-to-voltage converter.</li> <li>(b) Transfer function curves of time-to-voltage converter up and down current with the presence of channel length modulation. (c) Timing diagram of time-to-voltage converter input PWM signals and output voltage.</li> </ul>                                                                                        | 21         |

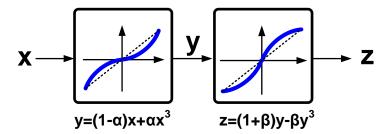

| 2.9    | Block diagram of two non-linear blocks with opposite non-linearity polarity in series.                                                                                                                                                                                                                                                                                                                        | 24         |

# LIST OF FIGURES (Continued)

| Figure |                                                                                                                                                                                                                                                                                                                               | Page |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

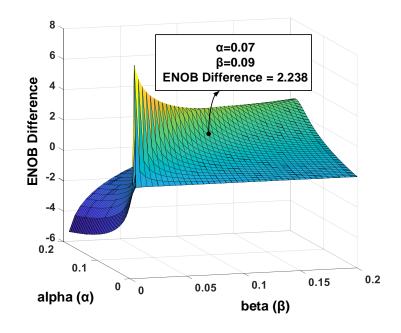

| 2.10   | ENOB difference as a function of non-linear coefficients of each non-linear stage.                                                                                                                                                                                                                                            | 27   |

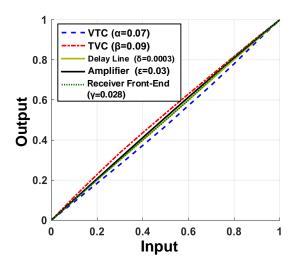

| 2.11   | Graph of normalized simulated transfer functions of voltage-to-time converter, time-to-voltage converter, and the overall receiver front-end.                                                                                                                                                                                 | 28   |

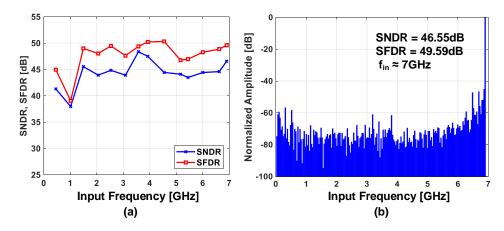

| 2.12   | (a) Simulated end-to-end SNDR and SFDR of the proposed receiver with 500mVpp Input, and (b) Simulated receiver output spectrum with Nyquist frequency input.                                                                                                                                                                  | 28   |

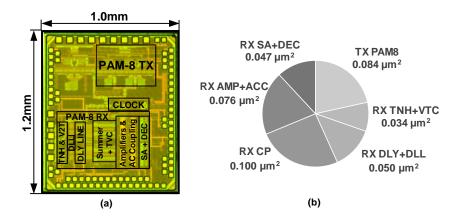

| 2.13   | (a) Prototype chip micrograph. (b) Area breakdown of the transceiver chip active area.                                                                                                                                                                                                                                        | 29   |

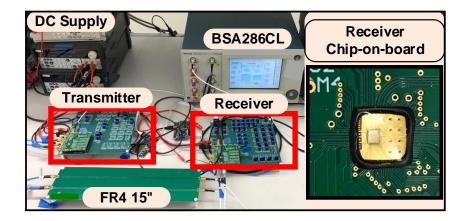

| 2.14   | Measurement setup of the transceiver with a zoomed photo of the re-<br>ceiver showing the chip-on-board                                                                                                                                                                                                                       | 30   |

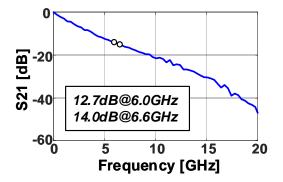

| 2.15   | Insertion loss profile of the channel used for the measurement                                                                                                                                                                                                                                                                | 31   |

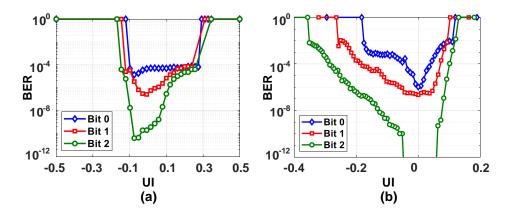

| 2.16   | Measured transceiver BER bathtub curves for 3 bits of PAM-8 at the receiver in PRBS-7 data (a) at 39.6 Gb/s and (b) at 36.0 Gb/s                                                                                                                                                                                              | 31   |

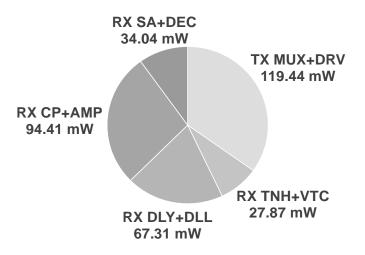

| 2.17   | Power breakdown of the proposed transceiver                                                                                                                                                                                                                                                                                   | 33   |

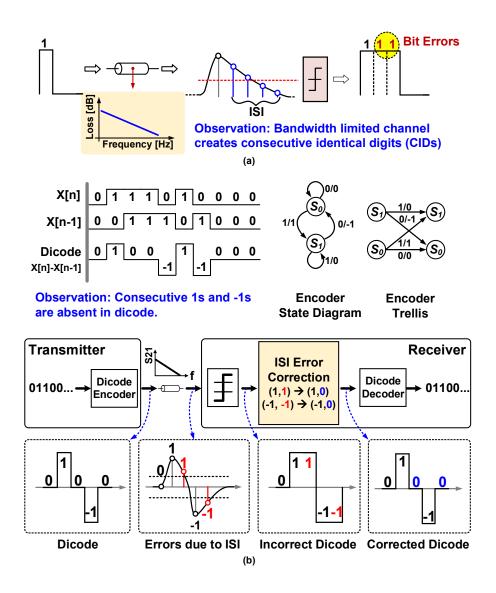

| 3.1    | (a) Effect of a bandwidth-limited channel on the transmitted pulse and generation of CIDs. (b) Proposed approach on correcting errors due to ISI by encoding data using Dicode to avoid CIDs                                                                                                                                  | 35   |

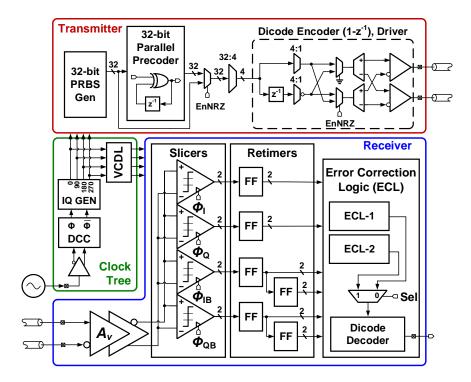

| 3.2    | Proposed transceiver block diagram.                                                                                                                                                                                                                                                                                           | 36   |

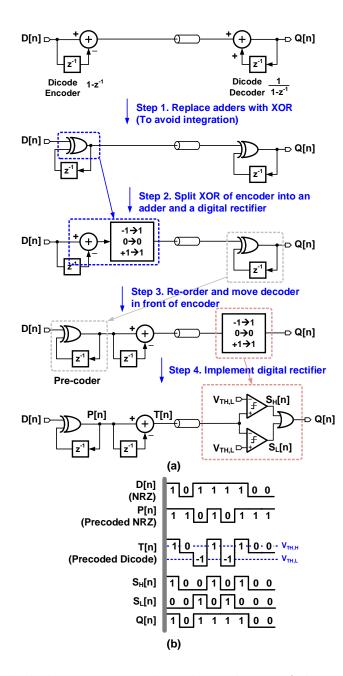

| 3.3    | (a) Block diagrams to explain the evolution of the proposed transceiver architecture with pre-coder. (b) Timing diagram of the precoded Di-<br>code architecture                                                                                                                                                              | 37   |

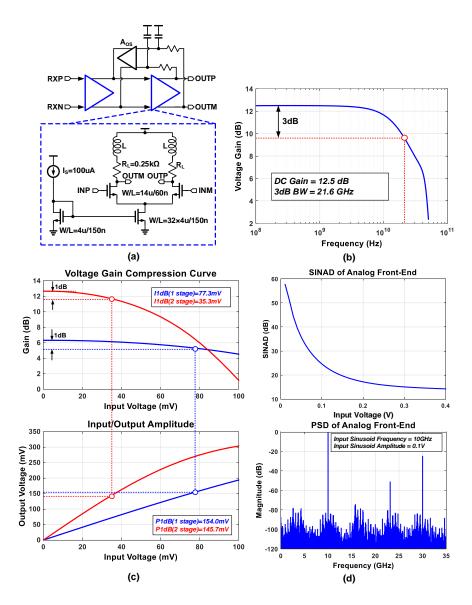

| 3.4    | <ul> <li>(a) Schematic of voltage amplifier stage in the receiver front-end.</li> <li>(b) Simulated frequency response of the overall amplifier stage.</li> <li>(c) Simulated DC linearity of single stage and aggregated voltage amplifier.</li> <li>(d) Simulated AC linearity of the receiver analog front-end.</li> </ul> | 40   |

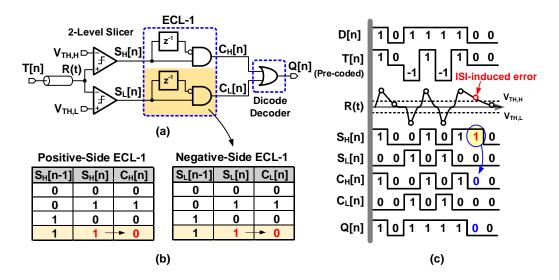

| 3.5    | (a) Block diagram of the full-rate Dicode receiver. (b) Truth table of ECL-1 and Dicode decoder. (c) Timing diagram demonstrating the operation of ECL-1                                                                                                                                                                      | 41   |

# LIST OF FIGURES (Continued)

| Figure | ]                                                                                                                                                                                                                                                                                                         | Page |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

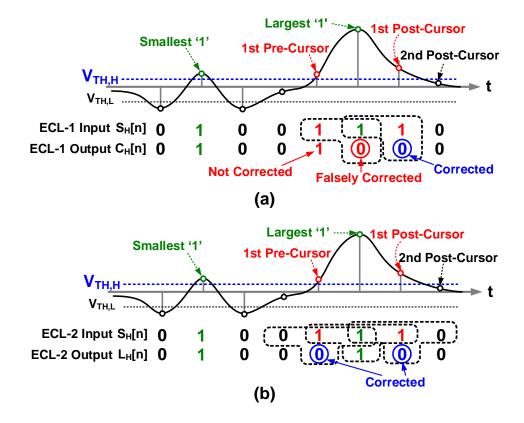

| 3.6    | (a) An example where ECL-1 fails with higher channel loss in the presence of both pre and post cursors. (b) An example where three consecutive data bits are processed by ECL-2 to correct the ISI errors.                                                                                                | 44   |

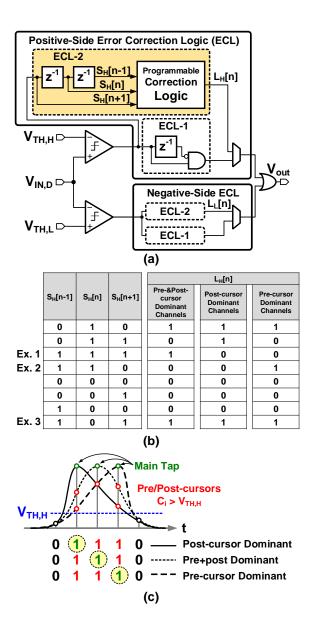

| 3.7    | <ul> <li>(a) Block diagram of the proposed error correction logic-2 (ECL-2).</li> <li>(b) Truth table of the programmable correction logic in ECL-2. (c) Different channel responses generating similar received (sampled) data with ISI errors.</li> </ul>                                               | 46   |

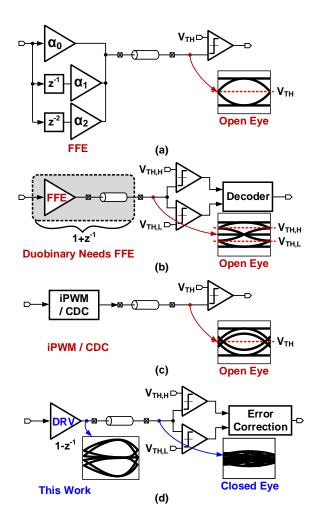

| 3.8    | (a) A feed forward equalizer based transceiver architecture. (b) A conventional Duobinary transceiver architecture with an FFE. (c) A transceiver architecture employing Machester, iPWM and CDC line-coding techniques. (d) Proposed Dicode encoding and error correction based transceiver architecture | 51   |

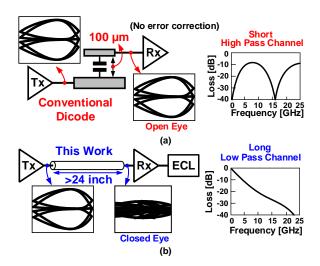

| 3.9    | (a) Conventional Dicode transceiver used on capacitor coupled high-<br>pass channel. (b) Proposed Dicode transceiver used on a typical band-<br>width limited wireline channel                                                                                                                            | 54   |

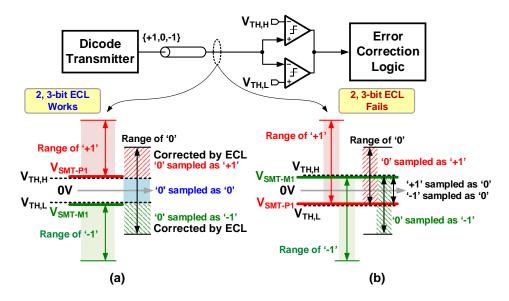

| 3.10   | (a) Voltage range of received signal for low channel loss where 2, 3-bit input error correction logic works. (b) Voltage range of received signal for high channel loss where 2, 3-bit error correction logic fails                                                                                       | 56   |

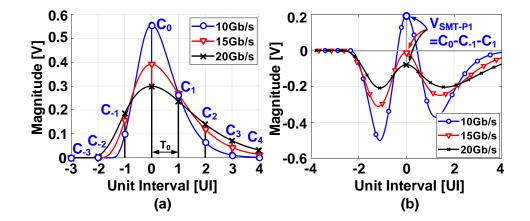

| 3.11   | (a) Simulated pulse response of channel in (3.7) at 10Gb/s, 15Gb/s and 20Gb/s. (b) Simulated response ['-1', '1', '-1'] pattern to show the position of the smallest main tap $(V_{SMT-P1})$ of signal '1' at 10Gb/s, 15Gb/s and 20Gb/s                                                                   | 57   |

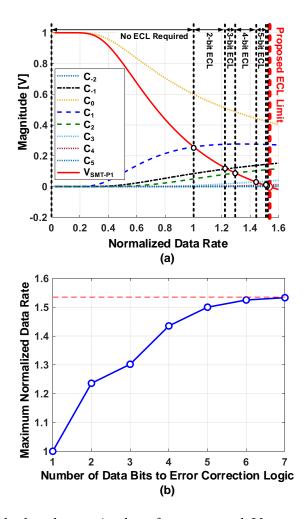

| 3.12   | (a) Calculated magnitudes of cursors and $V_{SMT-P1}$ as function of nor-<br>malized data rate. (b) Calculated normalized data rate as a function<br>of number of error correction logic inputs                                                                                                           | 60   |

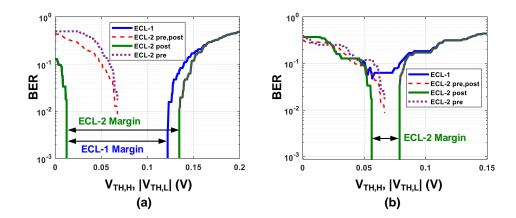

| 3.13   | (a) Simulated BER vs. $V_{TH,H}$ , $ V_{TH,L} $ bathtub curves of ECL-1 and ECL-2 on channel 4. (b) Simulated BER vs. $V_{TH,H}$ , $ V_{TH,L} $ bathtub curves of ECL-1 and ECL-2 on channel 5.                                                                                                           | 61   |

# LIST OF FIGURES (Continued)

| Figure |                                                                                                                                                                                                                                                                                                                                                                                                                                  | Page |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

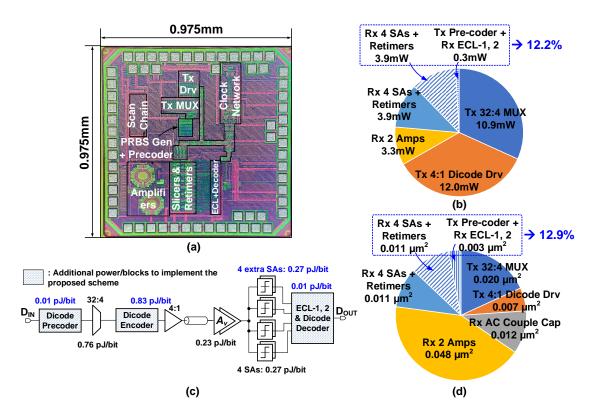

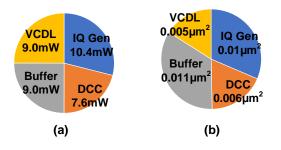

| 3.14   | (a) Die micrograph of the proposed transceiver. (b) Pie chart of the power breakdown at 14.4Gb/s measurement. (c) Additional blocks to implement the proposed scheme in addition to simple NRZ transceiver architecture and their power overhead. (d) Pie chart of the area breakdown.                                                                                                                                           | 64   |

| 3.15   | <ul><li>(a) Simulated clock distribution network power breakdown at 14.4Gb/s.</li><li>(b) Area breakdown of the clock distribution network</li></ul>                                                                                                                                                                                                                                                                             |      |

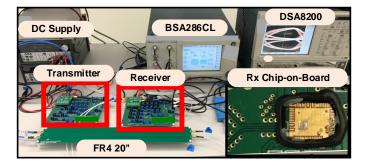

| 3.16   | Transceiver measurement setup with the chip-on-board photograph                                                                                                                                                                                                                                                                                                                                                                  | 65   |

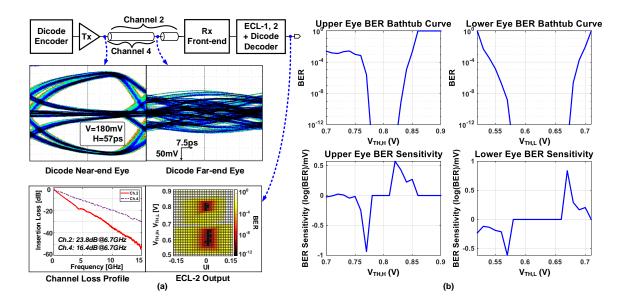

| 3.17   | (a) Measured Dicode near-end eye diagram, far-end eye diagram, chan-<br>nel loss profile, and in-situ eye diagram. (b) BER sensitivity graphs<br>with respect to upper threshold voltage $(V_{TH,H})$ and lower threshold<br>voltage $(V_{TH,L})$ .                                                                                                                                                                              | 67   |

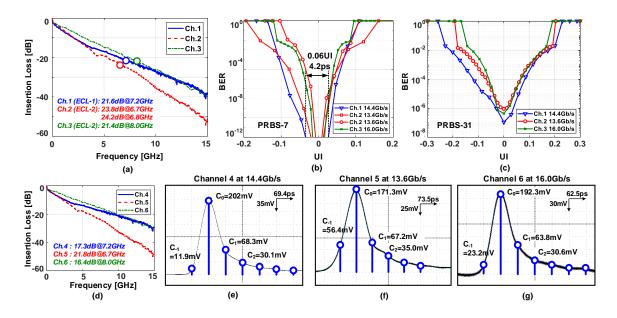

| 3.18   | (a) Measured channel loss profiles. (b) Measured transceiver BER bathtub curves using PRBS-7. (c) Measured transceiver BER bathtub curves using PRBS-31. (d) Measured channel loss profiles without receiver-side loss. Measured single bit response of (e) channel 4 (=channel 1 without receiver-side loss), (f) channel 5 (=channel 2 without receiver-side loss), and (g) channel 6 (=channel 3 without receiver-side loss). | 68   |

|        | 1065)                                                                                                                                                                                                                                                                                                                                                                                                                            | 00   |

## LIST OF TABLES

| Table |                                               | ] | Page |

|-------|-----------------------------------------------|---|------|

| 2.1   | Comparison with state-of-the-art transceivers |   | 32   |

| 3.1   | Comparison with state-of-the-art transceivers |   | 65   |

#### Chapter 1: Introduction

This dissertation consists of two research topics in wireline communication circuits and systems design. The aim of both these research topics is to achieve energy-efficient error-free communication over bandwidth-limited wireline channels. The first one is a PAM-8 transceiver with a time-domain FFE and linearity improvement technique. The second one is an equalizer-less wireline transceiver with Dicode encoding and forward error correction logic.

# 1.1 Introduction to PAM-8 Wireline Transceiver with Time-Domain Equalization and Linearity Improvement Technique

Ever increasing global internet data traffic has driven up the demand for cuttingedge high-speed wireline communication systems in data centers. As a result, data rates of wireline links have been steadily increasing [1]. PAM-4 signaling has been consistently and widely adopted throughout the SerDes industry and research, mostly due to its capability to double the data rate as compared to non-return-to-zero (NRZ) while keeping the same symbol rate [2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13]. As PAM-4 signaling has become more mature and well-established, there has been a need to explore higher-order modulation technique and architecture beyond PAM-4 with the aim to achieve a higher data rate and better energy efficiency. The next modulation technique after PAM-4 is PAM-8, which can help to increase the data rate to 3 times that of NRZ [14] for the same symbol rate. However, due to the presence of 8 voltage levels, the PAM-8 modulation scheme is more sensitive to non-idealities such as (a) residual intersymbol interference (ISI) and (b) non-linearity in the frontend as compared to NRZ. Both of these non-idealities must be minimized as they reduce the vertical eye opening, which reduces the signal to noise ratio (SNR) and consequently increases the bit error rate (BER). In view of this, this work investigates time-domain FFE-based PAM-8 wireline architecture with the aim to achieve more than 7-bit ENOB linearity in the receiver front-end [15].

There are three techniques to mitigate ISI and achieve error free communication on a bandwidth-limited wireline channel. These techniques are – data encoding with forward error correction [16], line coding [17, 18, 19, 20, 21, 22], and equalization/filtering. Among these techniques, equalization or filtering has been the most prominent technique in wireline systems. There are three equalization architectures: feed forward equalizers (FFE) [23, 24, 25], decision feedback equalizers (DFE) [26, 27, 28, 25], and continuous time linear equalizers (CTLE) [29, 30]. While DFE and CTLE are placed on the receiver end, FFE can be either placed on the transmitter side or on the receiver side. Compared to the transmitter-side FFEs, receiver-side FFEs can help to avoid not only jitter amplification but also the requirement of having a backchannel to tune FFE coefficients [31]. Therefore, this work investigates receiver-side FFE architecture for PAM-8 modulation.

Conventional state-of-the-art receiver-side FFEs are generally in a form of either (a) voltage-domain analog FFE architecture [32, 24, 33, 34] or (b) digital-domain or analog-to-digital-converter (ADC)-based FFE architecture [35, 36, 12, 11, 6, 7, 8, 2, 3, 4] Analog FFEs with amplifier-based delay elements suffer from a trade-off between signal swing and linearity. While a large signal swing is desirable for a higher SNR and a lower BER, a large signal swing also results in reduced linearity of the analog delay elements. Moreover, with the reduced supply voltage in the fine technology nodes, it has become challenging to achieve a large swing without compromising linearity. Furthermore, variation in delay due to process, voltage, and temperature (PVT) variations in an amplifier-based delay line can result in under- or over-equalization, which increases the BER. Another type of analog-based FFE architecture is sampleand-hold FFE architecture [37]. While a sample-and-hold-based FFE can avoid using delay elements, the requirement to generate and transmit a 25% duty cycle clock for a 4-tap FFE and a 12.5% duty cycle clock for a 8-tap FFE makes scaling of this architecture challenging [37]. An ADC-based FFE provides flexibility to implement multiple FFE taps. However, high power consumption in the high-resolution highspeed ADCs and digital signal processors (DSP) degrades the transceiver energy efficiency.

Researchers have explored different domains to find alternate equalization strategies while maintaining the same basic principle. Equalization using a pulse-widthmodulated (PWM) signal in a time domain [5, 38, 39, 40] can be a promising alternative to overcome the limitations of voltage-domain and digital-domain equalization techniques. Time-domain signaling in the advanced technology nodes can process the signal in a time domain while operating with a lower supply voltage. However, prior FFE-based time-domain architecture was demonstrated in NRZ [38]. Prior DFE-

Figure 1.1: Conceptual diagram of the proposed transceiver with time-domain feed forward equalization and linearity improvement technique.

based time-domain architectures, on the other hand, were demonstrated in NRZ [41, 39] and PAM-4 [5]. In all the prior time-domain architectures, the number of taps were limited to 2, mainly due to the limited front-end linearity and fixed data rate range. Higher-order modulation techniques such as PAM-8 require a highly linear analog front-end, which translates to a highly linear time-domain FFE or DFE architecture. In view of this, we propose a PAM-8 transceiver with a time-domain 4-tap FFE on the receiver, achieving a wide data rate range from 12.0-to-39.6 Gb/s [15].

The concept of the proposed time-domain equalization and non-linearity cancellation technique is shown in Fig. 1.1. The received voltage signal is sampled at the receiver and converted to a pulse-width-modulated signal. Delay in the FFE is generated by delaying PWM signals using digital delay lines. PWM signals are added together with appropriate weights to equalize the channel. The PWM signal is converted back to voltage signal at the FFE output and the slicers sample the voltage signal to get the PAM-8 data. It was observed that when the two non-linear functions have non-linearity with opposite sign are cascaded, one non-linear function cancels the other out, making the overall aggregated transfer function of the cascaded system more linear. From this observation, the proposed receiver is designed to have voltage-to-time and time-to-voltage converters with an opposite polarity of linearity.

# 1.2 Introduction to Transceiver Design with ISI-Resilient Data Encoding for Equalizer-Free Wireline Communication using Dicode Encoding and Error Correction

Increasing the data rate through bandwidth-limited wireline channels requires equalizations to cancel inter-symbol interferences (ISI). Since wireline channels have lowpass characteristics, the equalization is typically achieved by leveraging high-pass filters or equalizers (FFE, DFE, or CTLE) in the data path to compensate for the low-pass characteristics of the channel. It is estimated that the energy efficiency of wireline links degrades by 10 times for every 30 dB of channel loss compensated [1, 42]. Conventional equalizers require multiple taps (ex: 4-FFE, 15-DFE, 2-CTLE) to compensate for heavy channel loss, which results in high power consumption and reduced energy efficiency [43, 44]. Furthermore, increasing the number of taps gives a diminishing return on the maximum achievable data rate after a certain point [45].

Researchers have also introduced alternative equalization strategies using phase pre-emphasis [18] or using different line-codes such as Manchester code [46, 17, 19, 20], integrated pulse width modulation (iPWM)[47, 48, 49], and consecutive digit chopping (CDC) [49]. To support the ever-increasing data rates and compensate for heavier channel loss, data encoding and error correction techniques can be leveraged. In upper layers of the wireline communication stack, techniques such as convolutional or 8b10b coding and sequence detection-based Viterbi decoding can achieve low BER in the presence of ISI [50]. However, the traditional data encoding and error correction comes at the cost of (a) low energy efficiency, (b) low achievable data rate due to high complexity and feedback requirement in the decoder, (c) high latency in the decoding process (100s of ns), and (d) coding overhead which requires additional bits to be transmitted in the message.

In view of these limitations, we propose an ISI-resilient (ISIR) encoding and error correction concept – Dicode encoding and sequence detection-based error correction and decoding to achieve low BER on bandwidth-limited wireline channels without using any conventional equalizers or filters. This paper presents two types of all-digital error correction logic which can help to achieve BER $<10^{-12}$ . The proposed encoding/decoding approach has (a) a high energy efficiency, (b) no feedback loops in the decoder (it is a feed-forward architecture), (c) small logic depth with error correction and decoding latency of only 5 UIs (3 UIs from re-timers, 2 UIs from error correction + decoding logic), and (d) no additional bits for coding. Operating at 13.6 Gb/s, 14.4 Gb/s, and 16 Gb/s, the 65 nm CMOS transceiver with the proposed

ISIR Dicode encoding can compensate for 24.2 dB, 21.6 dB and 21.4 dB channel loss with an energy efficiency of 2.56 pJ/bit, 2.38 pJ/bit, and 2.66 pJ/bit, respectively [16]. Compared to the state-of-the-art Viterbi-based transceiver [50], the proposed transceiver achieves 4 times better Tx + Rx energy efficiency, 3 times higher data rate, and 30 times lower latency while communicating on a channel which has 3 dB higher channel loss.

# Chapter 2: PAM-8 Transceiver with Time-Domain (PWM) Feed Forward Equalization and Non-linearity Cancellation Technique

### 2.1 Linearity Requirement on Pulse Amplitude Modulated Signal

Non-linearity in the transceiver front-end results in reduction in the horizontal eye opening, and consequently reduction in SNR and increase in the BER. Therefore, it is important to estimate the non-linearity requirement for a given modulation scheme. In this work, the effect of non-linearity on various higher-order modulation schemes is estimated in MATLAB by applying a non-linear function to PAM-4/8/16 modulated data and to observe their eye openings.

Mathematically, a non-linear function (f) can be modeled as:

$$f = (1+\beta)x - \beta x^3 \tag{2.1}$$

where  $\beta \ge 0$  represents the non-linear coefficient or the third-order harmonic coefficient. Assuming the input is a cosine function or  $x = \cos(t)$ , (2.1) can be expanded

as:

$$f = (1+\beta)\cos(t) - \beta\cos^{3}(t)$$

=  $\left(1+\beta+\frac{3}{4}(-\beta)\right)\cos(t) + \frac{1}{4}(-\beta)\cos(3t)$  (2.2)

=  $\left(1+\frac{\beta}{4}\right)\cos(t) - \frac{\beta}{4}\cos(3t).$

To quantify the linearity of (2.2), the total harmonic distortion (THD) and the corresponding effective-number-of-bits (ENOB) can be represented as:

$$THD = 10\log_{10}\left(\frac{(1+\beta/4)^2}{(|-\beta/4|)^2}\right)$$

(2.3)

$$ENOB = \frac{THD - 1.76}{6.02}.$$

(2.4)

To quantify the irregularity of the multiple eye openings, ratio-of-level mismatch (RLM) of a PAM-N signal has been used [51, 52, 53]. RLM can be defined as

$$RLM = \frac{\min(V_N - V_{N-1}, V_{N-1} - V_{N-2}, \dots, V_2 - V_1)}{(V_N - V_1)/N}$$

(2.5)

where  $V_i$  represents an *i*-th voltage level of a PAM-*N* symbol. The numerator is the minimum eye opening which is represented as the minimum voltage difference between adjacent voltage levels. The denominator represents the average of the eye opening, represented as the difference between the highest voltage level ( $V_N$ ) and the lowest ( $V_1$ ) divided by *N*. When RLM is equal to 1, it means that the system is perfectly linear without any distortions in the eye diagram and all the eye openings

Figure 2.1: Relationship between ratio-of-level mismatch (RLM) and effectivenumber-of-bits (ENOB) in PAM-4, 8, and 16.

having the equal heights. On the other hand, if the eye diagram gets distorted due to non-linearity, RLM will be smaller than 1. For example, PAM-4-based wireline papers typically report RLM  $\geq 0.9$  [51, 52, 53], meaning that the most severely distorted eye has 10% less eye opening than the ideal scenario.

A plot of ratio-of-level mismatch versus effective-number-of-bits (ENOB) is shown in Fig. 2.1. This graph illustrates how much eye openings of different pulse-amplitudemodulated signals get distorted as the linearity of the system changes. Two important observations can be made from Fig. 2.1 regarding the relationship between linearity, modulation order (N), and the ratio-of-level-mismatch of any PAM-N system:

- To maintain the same value of RLM, a higher-order PAM requires a greater ENOB, or a more linear system.

- 2. For PAM-8 signaling, a wireline system is recommended to maintain an ENOB

Figure 2.2: Proposed PAM-8 transceiver architecture with a time-domain 4-tap feed forward equalizer (FFE) on the receiver.

greater than 7 bits.

In a conventional amplifier-based analog front-end, its non-linearity is reduced when the signal swing is reduced. However, reduction of signal swing lowers SNR, which increases the BER. Furthermore, reduction of supply voltage puts a limit on maximum signal swing that can be achieved. Therefore, there is a need to investigate alternative signal processing circuits and schemes, which can avoid or minimize the fundamental trade-off between non-linearity and SNR.

#### 2.2 Proposed Transceiver Architecture

A block diagram of the proposed PAM-8 transceiver is shown in Fig. 2.2. The transmitter consists of a pseudo-random binary sequence (PRBS) generator, three 32:1 multiplexers and a source-series-terminated (SST) output driver. The transmitter has an optional 4-bit tunable 2-tap FFE for debugging purpose only (not used in transceiver measurements). The SST output driver has a parallel segmented structure to implement FFE functionality. The receiver has quarter-rate architecture.

Figure 2.3: (a) Schematic of the single-ended track-and-hold and voltage-to-time converter and (b) timing diagram illustrating its operation.

Each lane of the quarter-rate receiver consists of a track-and-hold circuit, a voltageto-time converter (VTC), a 4-tap (2 post-cursors, 1 main-cursor, and 1 pre-cursor) quarter-rate time-domain FFE, a voltage amplifier, 7 samplers, and a PAM-8 data decoder for decoding PAM-8 symbols to a 3-bit binary output.

#### 2.2.1 Track-and-Hold and Voltage-to-Time Converter

A schematic and a timing diagram of the voltage-to-time converter in the receiver is shown in Fig. 2.3 (a). Track-and-hold circuit samples incoming data  $(V_{DATA})$  with a quarter-rate clock and holds the sampled voltage  $(V_{IN})$  in a capacitor  $(C_{TNH})$ . Bootstrap architecture is leveraged for the track-and-hold to achieve high linearity. During the hold and charge phase, a current source  $(I_{SRC} = 25 \ \mu\text{A} \text{ at } 12 \text{ Gbps and } 80 \ \mu\text{A} \text{ at } 39.6 \text{ Gbps in this work})$  charges up a capacitor  $C_{TNH}$  (40 fF) and increases  $V_{IN}$ linearly, as shown in Fig. 2.3 (b). As  $V_{IN}$  goes above threshold voltage  $(V_{TH-INV})$  of the following CMOS inverter (INV<sub>1</sub>), the rising edge of the digital rail-to-rail PWM signal  $(T_{VTC})$  is asserted.  $T_{VTC}$  is de-asserted at the end of the hold period by the falling edge of the clock. If the sampled voltage has smaller magnitude, then it takes more time for  $V_{IN}$  to get charged up, reach  $V_{TH-INV}$ , and create a rising edge of  $T_{VTC}$ . As a result,  $T_{VTC}$  will have a narrower pulse width. In this work, one VTC is present on each of the positive and negative port of the received fully differential data input signal. The output PWM data signal from each of the four lanes is pseudo-differential in time domain. That is, the time difference between rising edges of the differential pulses contains information on the magnitude of the sampled voltage.

#### 2.2.2 FFE Delay Lines Using Inverters and a Replica DLL

A schematic of the FFE delay lines using a replica delay-locked loop (DLL) in the receiver is shown in Fig. 2.4. The pulse-width-modulated signal,  $T_{VTC}$ , is precisely delayed to perform feed forward equalization. Propagation delay of the inverters are sensitive to process, voltage, and temperature (PVT) variations. To minimize its impact, a replica-based DLL shown in Fig. 2.4 (a) is employed to ensure that the unit interval (UI) delay is less affected by PVT variations. DLL consists of a bangbang phase detector, replica delay elements, and a charge pump. Since the proposed receiver is quarter-rate architecture, DLL is locked to a delay of 1 receiver clock cycle which is 4 UIs. For example, at 39 Gb/s or 13 GBaud, receiver clock frequency is 3.25 GHz, and 1 UI corresponds to approximately 307.7 ps and 4 UI is approximately 1.23 ns. Control voltage of the DLL ( $V_{CTRL}$ ) is shared with all the delay elements in all the 4 lanes. Each UI delay element has 2 digital programmable bits, which enable

Figure 2.4: Block diagram of the proposed (a) replica delay-locked loop, (b) 4-tap quarter-rate FFE summers (only I and Q lanes are presented in figure), and (c) programmable unit interval delay element.

Figure 2.5: Schematics of I-lane of the proposed time-to-voltage converter (TVC) in a quater rate receiver.

the proposed FFE to achieve wide data rate range (approximately  $3.5 \times$ ).

### 2.2.3 Time-to-Voltage Converter

A schematic of the time-to-voltage converter (TVC) in the receiver is shown in Fig. 2.5. Both time-to-voltage conversion and FFE coefficient/weight multiplication are performed using a differential charge pump. Differential PWM signals ( $T_{VTCP}$ and  $T_{VTCN}$ ) turn on/off the charge pump switches to charge/discharge the output capacitor ( $C_{CP}$ ). As a result, the differential voltage across  $C_{CP}$ , or  $V_{TVCP} - V_{TVCN}$ , is proportional to the difference between the pulse width of input PWM signals, or  $T_{VTCP} - T_{VTCN}$ , as shown in Fig. 2.6 (b). This charge pump also acts as an FFE summer and combines PWM output signals from four charge pumps with tunable tap coefficients into one output capacitor  $C_{CP}$ . In this work, the FFE tap coefficients were adjusted by changing the individual bias current of 4 charge pumps.

Figure 2.6: (a) Simplified representation of one tap segment of the proposed time-tovoltage converter (TVC). (b) Timing diagram of the TVC operation and eye diagram of the output of the charge pump  $V_{TVCP}$  or  $V_{TVCN}$  without any input data jitter. (c) Timing diagram of the TVC operation and eye diagram of the output of the charge pump  $V_{TVCP}$  or  $V_{TVCN}$  with input data jitter.

### 2.2.4 Effect of Timing Jitter on Time-to-Voltage Converter

Jitter in PWM signals which are the input to the charge pump results in voltage noise and timing jitter at the output of the charge pump, as illustrated in Fig. 2.6 (b) and (c). Power supply noise in delay elements and charge pumps is the major source of jitter in the input PWM signals to the charge pump. This jitter reduces both the vertical and horizontal eye opening. Eye diagrams generated by the output of the charge pump  $V_{TVCP}$  or  $V_{TVCN}$  without and with jitter of input PWM signals ( $T_{VTCP}$ ,  $T_{VTCN}$ ) are shown in the right side of Fig. 2.6 (b) and (c), respectively. When the rising edge of the input PWM signals have jitter, it changes the timing when it starts to charge or discharge the capacitor. As a result, the final voltage value (flat region of eye diagram) is going to be affected by the jitter. Jitter at the falling edge would affect less on the magnitude of the sampled voltage. However, it still reduces the horizontal eye opening or timing margin of the sampling clock. Differential signaling architecture and sufficient decoupling capacitors both on-chip and off-chip help to suppress power supply noise.

### 2.2.5 Receiver Amplifier

The summing nodes or the outputs of the FFE summer ( $V_{TVCP}$  and  $V_{TVCN}$ ) have large output node capacitance because charge pumps from all 4 lanes are connected together (see Fig. 2.5). The charge pump has to drive 7 comparators for PAM-8 which adds up more capacitive loads to the charge pump output. To drive such a large capacitive load and maintain a large voltage swing for high signal-to-noise ratio (SNR) at the charge pump output which is switching at a very high frequency, the charge pump design could be very energy-inefficient and challenging. To improve the efficiency, a voltage amplifier is introduced between the charge pump and comparators. The

Figure 2.7: Proposed linearity improvement technique in the receiver front-end by using voltage-to-time and time-to-voltage converters with opposite non-linearity.

amplifier achieves a gain of 6.5 dB and a bandwidth of 10.6 GHz. In more advanced technology nodes which has a larger transistor current gain and smaller parasitic capacitance, this voltage amplification stage may not be necessary.

#### 2.3 Proposed Linearity Improvement Technique

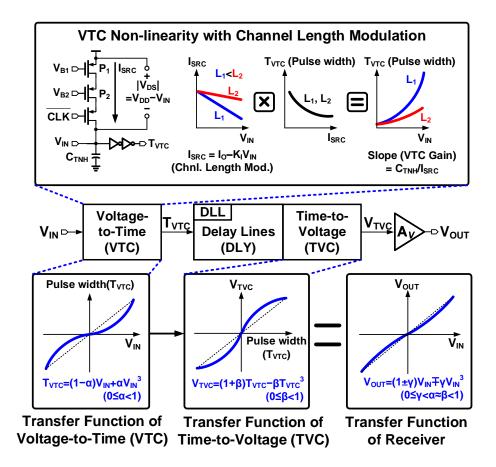

In the proposed approach, higher linearity in the receiver front-end is achieved by using non-linear circuit blocks having non-linearity in opposite directions. The proposed linearity improvement concept is illustrated in Fig. 2.7. The VTC architecture is designed to have non-linearity in the opposite direction to that of the TVC nonlinearity. The aim is to achieve a more linear transfer function from  $V_{IN}$  to  $V_{OUT}$  than the transfer function of TVC by canceling non-linearity of TVC with non-linearity of VTC.

#### 2.3.1 Transfer Function of Voltage-to-Time Converter

Non-linearity of the VTC block is introduced mainly due to channel length modulation of its current source  $(I_{SRC})$  (see Fig. 2.7). To understand the effect of channel length modulation on the VTC non-linearity, Fig. 2.7 provides one example of two different current sources whose W/L ratio is the same but the absolute value of width (W) and length (L) are different. In this example,  $L_1$  (blue curve in Fig. 2.7) is shorter than  $L_2$  (red curve in Fig. 2.7). The blue curve  $(L_1)$  which has shorter device length shows a more non-linear relation between  $T_{VTC}$  vs  $V_{IN}$  than the red curve  $(L_2)$ with longer device length. This non-linearity can be mathematically explained as follows. Assuming a first-order and square-law relationship, the current vs. voltage relationship of a PMOS current source in the presence of channel length modulation is expressed as:

$$I_{SRC} = I_0 - K_I V_{IN} \tag{2.6}$$

$$K_I = \frac{1}{2} \lambda \mu_P C_{OX} \frac{W}{L} (|V_{OV,ISRC}|)^2$$

(2.7)

where  $I_0$  is the maximum current magnitude when  $V_{IN} = 0V$  or  $|V_{DS}| = V_{DD}$ ,  $K_I$  is the slope of the  $I_{SRC}$  vs.  $V_{IN}$  curve which is proportional to  $\lambda = \Delta L/(L \cdot |V_{DS}|)$  [54], and  $|V_{OV,ISRC}|$  is the overdrive voltage of  $I_{SRC}$ . The gain of the VTC output pulse width  $(T_{VTC})$  can be mathematically expressed:

$$\frac{\partial T_{VTC}}{\partial V_{IN}} = \frac{C_{TNH}}{I_{SRC}}.$$

(2.8)

Using (2.6), (2.7) and (2.8) to express  $T_{VTC}$  as a function of  $V_{IN}$  results in a convexshaped transfer function, which is mathematically expressed as:

$$T_{VTC} = T_{const} - \frac{C_{TNH}}{K_I} \ln(I_0 - K_I V_{IN}), \qquad (2.9)$$

where  $T_{const}$  is an integration constant. Note that it shows a similar shape to the blue and red curve in the  $T_{VTC}$  vs.  $V_{IN}$  plot, shown in Fig. 2.7. From (2.9), one can observe that the non-linear relation between  $T_{VTC}$  and  $V_{IN}$  can be either tuned by (a) varying the dimensions (W/L) of the current source  $I_{SRC}$  or (b) by changing the overdrive voltage of the current source ( $|V_{OV,ISRC}|$ ). In this work, the dimensions of the current source was determined during the design time with the help of simulations, and the non-linearity is finely tuned by varying the  $|V_{OV,ISRC}|$  during the measurements.

The non-linear relationship between  $V_{IN}$  and  $T_{VTC}$  of pseudo-differential VTC

Figure 2.8: (a) Simplified schematic of a single-ended time-to-voltage converter. (b) Transfer function curves of time-to-voltage converter up and down current with the presence of channel length modulation. (c) Timing diagram of time-to-voltage converter input PWM signals and output voltage.

architecture can be expressed in a polynomial form as:

$$T_{VTC} = (1 - \alpha)V_{IN} + \alpha V_{IN}^3$$

(2.10)

where  $0 \le \alpha < 1$  is the non-linearity coefficient of VTC. For simplicity of analysis, the normalized differential signaling function of VTC is modeled with only a linear and a cubic term.

### 2.3.2 Transfer Function of Time-to-Voltage Conversion

Non-linearity of TVC is also due to channel length modulation of its charge pump current sources. The magnitude of the up/down current in the charge pump is affected by the voltage of the integration node,  $V_{TVC}$ .

As shown in Fig. 2.8 (b),  $I_{UP}$  and  $I_{DN}$  with the presence of channel length mod-

ulation can be expressed as:

$$I_{UP} = I_{AVG} - k_{CP}(V_{TVC} - V_{CM})$$

(2.11)

$$I_{DN} = I_{AVG} + k_{CP}(V_{TVC} - V_{CM})$$

(2.12)

where  $k_{CP}$  represents the slope or channel length modulation parameter, and  $I_{AVG}$  is the magnitude of UP and DN current when  $V_{TVC}$  is at the common-mode voltage  $V_{CM}$ . The relationship between voltage and current at the output node of the charge pump can be expressed as:

$$\frac{\partial V_{TVC}}{\partial T_{VTC}} = \frac{I_{UP} - I_{DN}}{C_{CP}}.$$

(2.13)

where  $T_{VTC}$  is the pulse width difference between  $T_{INP}$  and  $T_{INN}$ . When  $T_{INP}$  arrives at TVC, the UP current source is turned on, charges up the capacitor  $C_{CP}$ , and increases the voltage  $V_{TVC}$  while the DN current source is off or  $I_{DN} = 0$ . Combining (2.13) with (2.11) would result in a first-order differential equation or

$$\frac{\partial V_{TVC}}{\partial T_{VTC}} = \frac{I_{AVG} - k_{CP}(V_{TVC} - V_{CM})}{C_{CP}}.$$

(2.14)

Consequently, using the condition that  $V_{TVC} = V_{CM}$  when  $T_{VTC} = 0$ , the TVC transfer function while the UP current is charging up can be expressed as:

$$V_{TVC} = V_{CM} + \frac{I_{AVG}}{k_{CP}} \left( 1 - e^{-k_{CP}T_{VTC}/C_{CP}} \right)$$

(2.15)

which is a concave-shaped function of  $T_{VTC}$ .

For the simplicity of the further analysis, instead of using the exponential function, the differential TVC transfer function is approximated as a polynomial function which can be expressed as:

$$V_{TVC} = (1+\beta)T_{VTC} - \beta T_{VTC}^{3}$$

(2.16)

where  $0 \leq \beta < 1$  is the non-linearity coefficient of TVC. A reset signal RST that resets the capacitor  $C_{CP}$  is generated by logically ANDing  $T_{VTCP}$  and  $T_{VTCN}$ . RST is delayed by approximately 10 ps to provide sufficient timing margin for the PAM-8 samplers to sample the data without metastability.

### 2.3.3 Overall Receiver Front-End Transfer Function with Linearity Improvement Technique

In the proposed non-linearity cancellation approach, VTC is intentionally designed to have a certain amount of non-linearity such that the combination of VTC and TVC and amplifiers could achieve a more linear transfer function. In other words, the end-to-end function of the receiver front-end, or  $V_{OUT}$  vs.  $V_{IN}$  relationship, can be described as:

$$V_{OUT} = (1 \pm \gamma) V_{IN} \mp \gamma V_{IN}^3 \tag{2.17}$$

where  $0 \le \gamma < 1$  is the non-linearity coefficient of the overall receiver front-end. The aim of the non-linearity cancellation approach is to make the magnitude of  $\gamma$  smaller than of  $\alpha$  in (2.10) and  $\beta$  in (2.16).

Figure 2.9: Block diagram of two non-linear blocks with opposite non-linearity polarity in series.

### 2.3.4 Limits of Linearity Improvement

Transfer functions of two non-linear stages with non-linearity in opposite directions are shown in Fig. 2.9. Mathematically, they can be expressed as:

$$y = (1 - \alpha)x + \alpha x^3 \ (\alpha \ge 0) \tag{2.18}$$

$$z = (1+\beta)y - \beta y^3 \ (\beta \ge 0) \tag{2.19}$$

where  $\alpha, \beta$  represent the non-linear or third-order harmonic coefficient of the first (VTC) and the second stage (TVC), respectively. The first stage is a convex third-order function and the second stage is a concave third-order function. The final output, z, can be expressed in terms of the input of the system, x, as follows:

$$z = (1+\beta)[(1-\alpha)x + \alpha x^3] - \beta[(1-\alpha)x + \alpha x^3]^3$$

=  $C_1 x + C_3 x^3 + C_5 x^5 + C_7 x^7 + C_9 x^9,$  (2.20)

where the coefficients are

$$C_{1} = (1 - \alpha)(1 + \beta)$$

$$C_{3} = \alpha(1 + \beta) - (1 - \alpha)^{3}\beta$$

$$C_{5} = -3\alpha(1 - \alpha)^{2}\beta$$

$$C_{7} = -3\alpha^{2}(1 - \alpha)\beta$$

$$C_{9} = -\alpha^{3}\beta$$

(2.21)

respectively.

To estimate the non-linearity at the output z, a sinusoidal signal is applied at the input. By substituting  $x = \cos(t)$  in (2.20), the output can be rewritten as:

$$z = C_1 \cos(t) + C_3 \cos^3(t) + C_5 \cos^5(t) + C_7 \cos^7(t) + C_9 \cos^9(t) = Q_1 \cos(t) + Q_3 \cos(3t) + Q_5 \cos(5t) + Q_7 \cos(7t) + Q_9 \cos(9t),$$

(2.22)

where the coefficients are

$$Q_{1} = C_{1} + \frac{3}{4}C_{3} + \frac{10}{16}C_{5} + \frac{35}{64}C_{7} + \frac{126}{256}C_{9}$$

$$Q_{3} = \frac{1}{4}C_{3} + \frac{5}{16}C_{5} + \frac{21}{64}C_{7} + \frac{84}{256}C_{9}$$

$$Q_{5} = \frac{1}{16}C_{5} + \frac{7}{64}C_{7} + \frac{36}{256}C_{9}$$

$$Q_{7} = \frac{1}{64}C_{7} + \frac{9}{256}C_{9}$$

$$Q_{9} = \frac{1}{256}C_{9}$$

(2.23)

respectively. Note that each  $Q_N$  is a function of  $\alpha$  and  $\beta$ , since each  $C_N$  is also a function of  $\alpha$  and  $\beta$  and  $Q_N$  is a linear combination of  $C_N$ .

Linearity of the output z in terms of effective-number-of-bits (ENOB) can be expressed as:

$$THD = 10 \log_{10} \left( \frac{Q_1^2}{Q_3^2 + Q_5^2 + Q_7^2 + Q_9^2} \right), \qquad (2.24)$$

$$ENOB(\alpha, \beta) = \frac{THD - 1.76}{6.02}.$$

(2.25)

To estimate the limits of linearity improvement in the proposed approach, ENOB difference is introduced, which can be mathematically defined as:

$$ENOB Difference(\alpha, \beta)$$

$$= ENOB(\alpha, \beta) - ENOB(\alpha = 0, \beta).$$

(2.26)

The ENOB difference indicates the difference between the ENOB when  $\alpha$  is nonzero indicating the VTC is not perfectly linear, and the ENOB when  $\alpha$  is zero indicating

Figure 2.10: ENOB difference as a function of non-linear coefficients of each non-linear stage.

the VTC is perfectly linear. Note that the overall non-linearity is equal to the nonlinearity of the TVC ( $\beta$ ) when  $\alpha$  is equal to 0. An ENOB difference greater than 0 means the improvement in linearity.

To see the trend of the linearity improvement, ENOB difference is calculated for different combinations of the non-linearity coefficients  $\alpha$  and  $\beta$  using (2.26) whose results are shown in Fig. 2.10. Two observations could be deducted from this simulation result:

- 1. ENOB difference is always greater than 0 when  $\alpha \leq \beta$  for  $0 < \beta < 0.2$ .

- 2. ENOB is maximized when  $\alpha$  and  $\beta$  have a similar value.

Figure 2.11: Graph of normalized simulated transfer functions of voltage-to-time converter, time-to-voltage converter, and the overall receiver front-end.

Figure 2.12: (a) Simulated end-to-end SNDR and SFDR of the proposed receiver with 500mVpp Input, and (b) Simulated receiver output spectrum with Nyquist frequency input.

Curves of simulated input-output transfer function of the VTC, TVC, delay line, amplifier, and the overall receiver designed in this work are shown in Fig. 2.11. While ENOB of the TVC is approximately 5.1 bits ( $\beta = 0.09$ ), introducing the VTC with

Figure 2.13: (a) Prototype chip micrograph. (b) Area breakdown of the transceiver chip active area.

$\alpha = 0.07$  improves the overall linearity of the receiver to have  $\gamma = 0.028$  (see (2.17)) or approximately 6.9 bits. The non-linearity coefficient of both the delay line ( $\delta$ ) and the voltage amplifier ( $\epsilon$ ) show a similar or smaller number than that of the receiver front-end ( $\gamma$ ). The simulated SNDR, SFDR, and output spectrum of the receiver are shown in Fig. 2.12. For a 7-GHz sinusoidal input, the proposed receiver achieves an SNDR of 46.5 dB (7.4 bits). The 0.5 bit error between the linearity obtained from SNDR and linearity from the modeled transfer function of the receiver (using (2.17)) is due to the inaccuracy in modeling the normalized transfer functions into a polynomial with first-order and third-order terms only.

#### 2.4 Measurement Results

The prototype transceiver was fabricated in 65 nm CMOS and the die micrograph is shown in Fig. 2.13 (a). The proposed transceiver operates from 0.9-/1.0-/1.1V supply

Figure 2.14: Measurement setup of the transceiver with a zoomed photo of the receiver showing the chip-on-board.

and occupies an active area of 0.39 mm<sup>2</sup>. Fig. 2.13 (b) shows the area breakdown of the proposed transceiver, which consists of a PAM-8 transmitter (TX), a track-and-hold and a voltage-to-time converter (TNH+VTC), delay lines and a delay-locked loop (DLY+DLL), a charge pump (CP), a stage of voltage amplifiers and AC coupling capacitors (AMP+ACC), and comparators and decoder logic blocks for PAM-8 (SA+DEC).

The measurement setup for the transceiver is shown in Fig. 2.14. The transmitter board is connected to the receiver board through a 15-inch FR4 channel. The clock is generated from the external clock generator (HP 83640B) and the clock is internally divided to generate four phases and connected to the transmitter and the receiver. The threshold voltages are generated using off-chip voltage regulators and potentiometers (variable resistors). Oscilloscope (Tektronix DSA8200) and BER tester (Tektronix BSA286CL) were used to measure the waveforms and bit error rate at the receiver. The chip was bonded to the PCB by wire-bonding chip-on-board (COB).

Figure 2.15: Insertion loss profile of the channel used for the measurement.

Figure 2.16: Measured transceiver BER bathtub curves for 3 bits of PAM-8 at the receiver in PRBS-7 data (a) at 39.6 Gb/s and (b) at 36.0 Gb/s.

The insertion loss profile of the channel which was used during the measurement of the transceiver is presented in Fig. 2.15. The FR4 channel has 12.7 dB and 14.0 dB insertion loss at 6.0 GHz and 6.6 GHz, respectively, which has a similar loss with middle-range (MR) wireline channels targeted for interface applications for chip-tochip communication and mid-range backplanes [55].

The measured BER bathtub curves at 39.6 Gb/s and 36.0 Gb/s are shown in Fig. 2.16 (a) and (b), respectively. Each bathtub graph has three curves, since a

|                     | This Work                    | ISSCC'17 [56]                  | ISSCC'18 [11]                                                                    | ISSCC'18 [12]                                |

|---------------------|------------------------------|--------------------------------|----------------------------------------------------------------------------------|----------------------------------------------|

| Modulation          | PAM-8                        | PAM-4                          | PAM-4                                                                            | PAM-4                                        |

| Process             | $65 \mathrm{nm}$             | 40-nm                          | 16-nm                                                                            | 16-nm                                        |

| Data Rate [Gb/s]    | 12-39.6                      | 56                             | 19-56                                                                            | 64.375                                       |

| Equalization        | 4-tap RxFFE<br>(Time-domain) | 3-tap FFE<br>CTLE<br>3-tap DFE | 4-Tap TxFFE<br>15-tap RxFFE<br>2-tap DFE                                         | 3-tap TxFFE<br>CTLE<br>16-tap DFE (Off-chip) |

| Efficiency [pJ/bit] | $8.65^{ m a}, 8.66^{ m b}$   | 10.39                          | $6.4^{\rm c},  9.7^{\rm d}$                                                      | $2.9^{f^*}, 4.3^{g^*}, 6.2^{h^*}$            |

| Loss [dB]           | $12.7^{\rm a},14^{ m b}$     | 24                             | $7.4^{\rm c}, 32^{\rm d}$                                                        | $8.6^{\rm f}, 13.5^{\rm g}, 29.5^{\rm h}$    |

| Area $[mm^2]$       | 0.39                         | 2.4                            | 8.81                                                                             | $0.25^{*}$                                   |

| Supply [V]          | 0.9/1.0/1.1                  | 1.0/1.5                        | 0.85/0.9/1.2/1.8                                                                 | 0.9/1.2                                      |

| BER                 | $10^{-6a}, 10^{-4b}$         | 10-12                          | $10^{\text{-}12\mathrm{c}},\!10^{\text{-}6\mathrm{e}},10^{\text{-}12\mathrm{d}}$ | $10^{-6\rm f},10^{-5\rm g},10^{-4\rm h}$     |

Table 2.1: Comparison with state-of-the-art transceivers

$^{\rm a}$  36.0Gb/s.

$^{\rm b}$  39.6Gb/s.

<sup>c</sup> 7.4dB.

<sup>d</sup> 32dB without XT.

<sup>e</sup> 32dB with 3mVrms XT.

f 8.6dB.

<sup>g</sup> 13.6dB. <sup>h</sup> 29.5dB.

\* ADC and DSP not included.

PAM-8 symbol consists of three bits. The least significant bit (LSB) being the smallest voltage swing has the lowest signal-to-noise ratio, and consequently, have higher bit error rates as compared to other bits. The proposed proposed transceiver achieves a  $BER < 10^{-4}$ .

Table 2.1 shows the performance summary and comparison with the state-of-theart publications. At 39.6 Gb/s, the transceiver can compensate 14-dB loss using a 4-tap time-domain FFE at the receiver with an energy efficiency of 8.66 pJ/bit. At 36 Gb/s, the transceiver achieves  $BER < 10^{-6}$  with an energy efficiency of 8.65 pJ/bit. Note that the transmitter-side FFE was turned off during all the measurements reported in this paper. Fig. 2.17 shows power breakdown of the transceiver at 39.6

Figure 2.17: Power breakdown of the proposed transceiver.

$\mathrm{Gb/s.}$

# Chapter 3: Equalizer-Free Wireline Transceiver with ISI-Resilient Data Encoding for Wireline Communication – Dicode Encoding and Error Correction

#### 3.1 Dicode as ISI Resilient Encoding and Error Correction Concept

When a data pulse is transmitted on a bandwidth-limited channel, it loses its sharpness and spreads out to neighboring bits. This is known as inter-symbol interference (ISI). As a result, the receiver incorrectly samples the data, as shown in Fig. 3.1 (a). The key observation is that due to the spreading of bit, a wrongly sampled bit is of the same value as that of the previous bit. In other words, the incorrectly sampled data have consecutive identical digits (CIDs) i.e.,  $[1, 1, 1, \cdots]$  or  $[-1, -1, -1, \cdots]$ .

In the proposed work, the transmitter encodes the data with the ISI-resilient (ISIR) Dicode such that the Dicode-encoded data do not contain CIDs, as shown in Fig. 3.1 (b). When the encoded data are transmitted on a bandwidth-limited channel, the individual bit spreads to the neighboring bits ISI, as a result, the receiver incorrectly samples the data with CIDs. However, because Dicode-encoded data do not contain CIDs, the receiver can "identify" the incorrectly sampled bit and "correct" the sampled bits. Using the proposed approach, multiple bit errors caused due to ISI can be corrected. As a result, error-free communication can be achieved without using conventional equalizers or filters.

Figure 3.1: (a) Effect of a bandwidth-limited channel on the transmitted pulse and generation of CIDs. (b) Proposed approach on correcting errors due to ISI by encoding data using Dicode to avoid CIDs.

### 3.2 Proposed Architecture

The proposed transceiver architecture is shown in Fig. 3.2. It consists of 3 major blocks: transmitter, receiver, and clock distribution network. The transmitter con-

Figure 3.2: Proposed transceiver block diagram.

sists of a PRBS generator, a digital-domain parallel pre-coder, and an SST output driver with the Dicode encoding functionality. The receiver front-end consists of two voltage amplifiers to increase the input swing,  $4 \times 2$  comparators or slicers operating at a quarter rate (2 comparators per lane), re-timers, two types of error correction logic (ECL), and a Dicode decoder. The clock distribution network has a duty-cycle correction block, a 4-phase generator, and a voltage-controlled delay line.

Figure 3.3: (a) Block diagrams to explain the evolution of the proposed transceiver architecture with pre-coder. (b) Timing diagram of the precoded Dicode architecture.

#### 3.2.1 Pre-coder and Evolution of Transceiver Architecture

The transfer function of Dicode is  $(1 - z^{-1})$ . In this work, a pre-coding operation is employed on the transmitter to avoid error propagation at the receiver. The transfer function of the pre-coder is  $1/(1-z^{-1})$ . Evolutional steps of the proposed transceiver architecture are shown in Fig. 3.3(a) along with the associated timing diagram in Fig. 3.3(b). The evolution starts with a Dicode encoder in Tx and a Dicode decoder in the Rx. In step-1, the adders in the encoder and decoder are replaced with XOR gates (modulo 2 addition). In step-2, the XOR gate in the encoder are split into an adder and a digital rectifier. In step-3, the blocks are re-ordered such that the  $1/(1-z^{-1})$ function implemented with XOR gate is placed in front of the encoder  $(1 - z^{-1})$  and the digital rectifier is moved from Tx to Rx. Finally, in step-4, the digital rectifier is implemented using two comparators and an OR gate, and since it is on the receiver side to convert Dicode data back to NRZ, it is called as the decoder in this work. By placing the pre-coder before the Dicode encoder, logic 1 is encoded as either '1' or '-1' alternatively and logic 0 is encoded as '0'. Therefore, the correlation between the data bits are broken before they are transmitted. Consequently, the current transmitted bit is independent of the previously transmitted bits. As a result, the receiver does not require a feedback architecture and there is no error propagation.

#### 3.2.2 Receiver Front-End

The receiver front-end consists of two voltage amplifiers, as shown in Fig. 3.4(a). High front-end gain helps to overcome the sampler offset and noise. Simulated frequency response in Fig. 3.4(b) shows that the 2 stages of voltage amplifier achieve a gain of 12.5dB and bandwidth of 21.5GHz. Note that there are no equalizers such as CTLE in the receiver front-end. Fig. 3.4(c) shows the simulated DC linearity of a single stage of the voltage amplifier and aggregated two stages in 11dB and P1dB. For clarity, P1dB is defined as the output voltage swing where the gain is 1dB less than small-signal voltage gain. 11dB is the input voltage swing where the output swing is P1dB. At the DC gain of approximately 12.5dB, the 11dB and P1dB for the two voltage amplifiers (combined) are 35.3mV and 145.7mV, respectively. Fig. 3.4(d) shows the simulated power spectral density with a 10GHz input sinusoidal signal. The signal-to-noise-and-distortion ratio (SINAD) is approximately 25dB. The front-end comparators are equipped with binary-weighted capacitor banks for offset cancellation purpose. However, due to the coarse resolution of the capacitor banks, the offset cancellation was not used in the measurements.

#### 3.2.3 Noise Budget of Transceiver

Assuming thermal noise generated by the SST output driver on the transmitter is attenuated by the channel, the total noise power at the input of the comparator/slicer

Figure 3.4: (a) Schematic of voltage amplifier stage in the receiver front-end. (b) Simulated frequency response of the overall amplifier stage. (c) Simulated DC linearity of single stage and aggregated voltage amplifier. (d) Simulated AC linearity of the receiver analog front-end.

Figure 3.5: (a) Block diagram of the full-rate Dicode receiver. (b) Truth table of ECL-1 and Dicode decoder. (c) Timing diagram demonstrating the operation of ECL-1.

can be mathematically expressed as:

$$P_{n,RX} = P_{n,Term} + P_{n,Amp} + P_{n,Comp,in}$$

$$(3.1)$$

where  $P_{n,Term}$  is the noise power generated by the two 50 $\Omega$  termination resistors,  $P_{n,Amp}$  is the noise power generated by the two amplifiers at the front-end, and  $P_{n,Comp,in}$  is the input-referred noise power of the comparator. Total simulated integrated noise at the input of the comparator is 2.66mVrms. To get a certain bit-error rate (BER), one needs to achieve a minimum signal-to-noise ratio (SNR) at the input of the slicer. Assuming Gaussian noise, the relation between SNR and BER can be mathematically derived as:

$$\frac{1}{2}\left(1 + erf\left(\frac{SNR}{2\sqrt{2}}\right)\right) = 1 - BER \tag{3.2}$$

where erf() represents the error function. For achieving BER <  $10^{-12}$ , the minimum required SNR obtained from (3.2) is 23dB. The minimum required SNR is expressed as  $P_{SNR}$ . In the proposed scheme, the Dicode signal has 3 voltage levels. Therefore, the Dicode signal has half the swing as compared to the NRZ. The loss in the signal swing due to encoding is expressed as  $P_{Dicode}$ =6dB. Due to 50 $\Omega$  termination between Tx and Rx, signal swing reduction is expressed as  $P_{50\Omega}$ =6dB. The channel insertion loss is expressed as  $P_{Channel}$ . Finally, the receiver amplifier provides 12.5dB amplification and this signal gain is expressed as  $P_{Amp}$ . Mathematically, the minimum transmitted signal power required to meet a certain BER in Dicode can be mathematically expressed as:

$$P_{sig,TX,min} = P_{n,RX} \times (Path \ Loss)$$

$$= P_{n,RX} + P_{SNR} + P_{Dicode} + P_{50\Omega} + P_{Channel} - P_{Amp}.$$

(3.3)

Note that  $P_{Amp}$  term is subtracted because it represents an amplification. Assuming 25dB insertion loss from the channel (based on the measurement result), the total path loss is 23dB + 6dB + 6dB + 25dB - 12.5dB = 47.5dB. Therefore, the minimum transmitted differential signal swing is

$$2.66mV \times 47.5dB = 2.66mV \times 237.1 = 0.631V_{pp}.$$

(3.4)

The transmitted signal swing before termination is  $2V_{pp,diff}$  since the supply voltage for the transmitter is 1V. Therefore, the proposed scheme has a noise margin of

$$20\log_{10}\left(\frac{2}{0.631}\right) = 10.02dB. \tag{3.5}$$

#### 3.2.4 Error Correction Logic-1