#### AN ABSTRACT OF THE DISSERTATION OF

<u>Hamidreza Maghami</u> for the degree of <u>Doctor of Philosophy</u> in <u>Electrical and</u> Computer Engineering presented on May 20, 2019.

Title: Digital Friendly Continuous-Time Delta-Sigma Analog-to-Digital

Converters

| Abstract approved:   |  |

|----------------------|--|

| resolution approved. |  |

Terri S. Fiez

Karti Mayaram

Conventional Delta-Sigma ( $\Delta\Sigma$ ) analog-to-digital converters (ADCs) utilize operational transconductance amplifiers (OTAs) in their loop filter implementation followed by multi-bit voltage domain quantizers. As CMOS integrated circuit technology scales to smaller geometries, the minimum transistor length and the intrinsic gain of the transistors decrease. Moreover, with process scaling the voltage headroom decreases as well. Therefore, designing OTAs in advanced CMOS processes is becoming increasingly difficult. Additionally, multibit quantizers are becoming more difficult to design due to the decreased voltage headroom and the challenges of low offset and noise requirements.

In this thesis, alternative digital solutions are introduced to replace traditional analog blocks. In the proposed solutions, compressed voltage-domain processing is shifted to the time-domain which benefits from process scaling as the transistors scale down in size and become faster.

First, a novel highly linear VCO-based 1-1 multi stage noise shaping (MASH) delta-sigma ADC structure is presented. The proposed architecture does not require any OTA-based analog integrators or integrating capacitors. Second-order noise shaping is achieved by using a VCO as an integrator in the feedback loop of the first stage and an open loop VCO quantizer in the second stage. A prototype was fabricated in a 65nm CMOS process and achieves 79.7 dB SNDR for a 2MHz signal bandwidth.

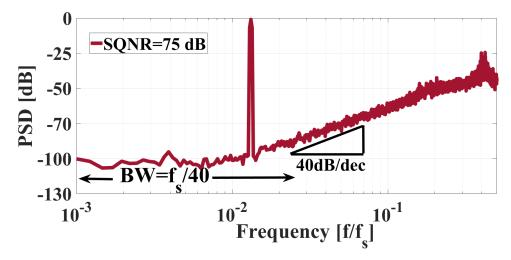

Second, a novel time-domain phase quantization noise extraction for a VCO-based quantizer is introduced. This technique is independent of the OSR and the input signal amplitude of the VCO-based quantizer making it attractive for higher bandwidth applications. Using this technique, a novel 0-1-1 MASH ADC is presented. The first stage is implemented using a 4-bit SAR ADC. The second and the third stages use a VCO-based quantizer (VCOQ). Behavioral simulation results confirm second-order noise shaping with a 75dB SNDR for an OSR of 20.

©Copyright by Hamidreza Maghami May 20, 2019 All Rights Reserved

## Digital Friendly Continuous-Time Delta-Sigma Analog-to-Digital Converters

by

Hamidreza Maghami

#### A DISSERTATION

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented May 20, 2019 Commencement June 2019

| $\underline{\underline{\text{Doctor of Philosophy}}}$ dissertation of $\underline{\underline{\text{Hamidreza Maghami}}}$ presented on $\underline{\underline{\text{May 20, 2019}}}.$                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APPROVED:                                                                                                                                                                                                 |

| Co-Major Professor, representing Electrical and Computer Engineering                                                                                                                                      |

| Co-Major Professor, representing Electrical and Computer Engineering                                                                                                                                      |

| Head of the School of Electrical Engineering and Computer Science                                                                                                                                         |

| Dean of the Graduate School                                                                                                                                                                               |

| I understand that my dissertation will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my dissertation to any reader upon request. |

| Hamidreza Maghami, Author                                                                                                                                                                                 |

#### ACKNOWLEDGEMENTS

First and foremost, I would like to express my gratitude and appreciation to my advisors Professor Terri Fiez and Professor Karti Mayaram to give me the opportunity to work under their supervision. Words cannot fully express my humble admiration and indebtedness toward them. Their abundant kindness and tremendous insights, guidence and motivations helped me immensely throughout the years on my journey. Professor Fiez and Professor Mayaram have thought me how to better communicate my ideas and always have been supportive when I faced difficulties by providing invaluable advices and encouragement. It has been my great honor and privilege to be supervised by them.

My sincere appreciation goes to my Ph.D. program committee members Professor Gabor Temes, Professor Un-Ku Moon and Professor Arun Natarajan for not only their valuable comments on my research but all the lessons I learned from them in the past years. Also, I'd like to thank Professor Sharmodeep Bhattacharyya for serving as my graduate council representative in multiple stages of my program.

I am grateful to my friend and OSU Alumni, Dr. Ramin Zanbaghi. He has been my mentor in the past few years. Without his guidance, this work would not have been anywhere close to its current form. In spite of his busy schedule, he always made himself available to discuss research related or personal issues. I am indebted to him for his help and friendship.

I must thank all the members of the EECS department who have helped me in every step of my way, weather the students of our research group, or other groups. I learned a lot from each and every one of them. Some of these students include Saeed Pourbagheri, Samira Zaliasl, Ankur Guha Roy, Ronghua Ni, Justin Goins, Hossein Mirzaei, Pedram Payandehnia, Siladytia Dey, Hui Zhang, Brian Miller, Kyle Gray, Ravi Teja, Yi Zhang, Tao He, Manjunath Kareppagoudr, Jason Muhlestein, Spencer Leuenberger, Hyuk Sun, Praveen Venkatachala, Ahmed El-Shater, Calvin Lee, Farshad Farhabakhshian, Jerry Leung, Zhiping Wang, Mohamed Megahed, Yu Sang Chun, Azmeen Rahman, Shaan Sengupta, Hyunkyu Ouh, Mahmoud Sadollahi, Manoj Johnson, Yanchao Wang, Robin Garg, Siddarth Mahendra, Bhagirath Thota, Kamala Sadagopan, Emanuel Caceres, Jyotindra Shakya and Subramanian T R. It was great to know you all. If I have not included someone in this list, it is unintentional.

It is a pleasure to thank my closest friends in Corvallis, Hossein Mirzaei, Pedram Payandehnia, Arash Azizi, Milad Ghayour and Ali Ahmed for the wonderful times we shared, specially the Saturday night dinners. In addition, I would like to thank all my friends in Crossfit Train 97333 who gave me the necessary distractions from my research and made my stay in Corvallis memorable.

Finally, my deep and sincere gratitude to my family for their continuous and unparalleled love, help and support. This work could not have been completed without the support and motivation I received from them, even though we have not seen each other for years. Love you all. I am forever indebted to my parents Fatemeh and Javad for their unconditional love and never ending support

and encouragement throughout my life. They have made me who I am today by their sacrifices and giving me the opportunities and experiences. They selflessly encouraged me to explore new directions in life and seek my own destiny. I am forever thankful to my only sister Hoda and brothers Mohammad-Hossein, Amin and Iman for the endless encouragement and love they have given me throughout my life and always being there for me as a friend. Also, I would like to extend my gratitude to my brother in law Mahdi Moein. His hardworking, optimistic, bright and confident attitude has always been my inspiration since we met. Finally, I would like to express my appreciation to other members of my family, specially my dear grandma, who always have been caring to me and keeping me in her prayers. If it was not for her prayers this work would never be where it is today.

## TABLE OF CONTENTS

|   |     |                                                                                                                                                                                                                                                                                                                                           | Page                             |

|---|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 1 | Int | troduction                                                                                                                                                                                                                                                                                                                                | 1                                |

|   | 1.1 | Scope of this work                                                                                                                                                                                                                                                                                                                        | . 5                              |

|   | 1.2 | Thesis organization                                                                                                                                                                                                                                                                                                                       | . 6                              |

| 2 | A   | Highly Linear OTA-free VCO-based 1-1 MASH $\Delta\Sigma$ ADC                                                                                                                                                                                                                                                                              | 8                                |

|   | 2.1 | Introduction                                                                                                                                                                                                                                                                                                                              | . 8                              |

|   | 2.2 | Prior Art                                                                                                                                                                                                                                                                                                                                 | . 11                             |

|   | 2.3 | Proposed Structure                                                                                                                                                                                                                                                                                                                        |                                  |

|   | 2.4 | Performance Analysis with Design Parameters                                                                                                                                                                                                                                                                                               | . 30                             |

|   | 2.5 | Effect of Non-Idealities  2.5.1 VCO non-linearity  2.5.2 Mismatch between analog and digital filters  2.5.3 VCO mismatch  2.5.4 Effect of narrow pulses in Q extraction path  2.5.5 Effect of propagation delay in QPD block  2.5.6 Effect of non-zero setup/hold times of the quantizer  2.5.7 Effect of non-zero rise/fall times of QPD | 40<br>42<br>45<br>47<br>49<br>50 |

|   | 2.6 | Design Example                                                                                                                                                                                                                                                                                                                            | . 56                             |

|   | 2.7 | Conclusion                                                                                                                                                                                                                                                                                                                                | . 63                             |

| 3 | A   | 0.9V 79.7dB SNDR 2MHz-BW 1-1 MASH OTA-less VCO-based $\Delta^2$                                                                                                                                                                                                                                                                           | $\sum$                           |

|   | ΑI  | OC with a Novel Phase Quantization Noise Extraction Technique                                                                                                                                                                                                                                                                             | 68                               |

|   | 3.1 | Introduction                                                                                                                                                                                                                                                                                                                              | . 69                             |

|   | 3.2 | Architectural level analysis of OTA-less 1-1 MASH VCO-based ADC 3.2.1 Open loop first order VCO-based V-to-F converter 3.2.2 Closed loop first-order VCO-based V-to-P converter 3.2.3 Proposed multi-phase VCO-based 1-1 MASH ADC                                                                                                         | . 74                             |

|   | 3.3 | Proposed Quantization Noise Extraction Technique                                                                                                                                                                                                                                                                                          | . 81                             |

## TABLE OF CONTENTS (Continued)

|   |     |                                                                               | Page         |

|---|-----|-------------------------------------------------------------------------------|--------------|

|   | 3.4 | Circuit Details                                                               | . 85<br>. 87 |

|   | 3.5 | Measurement Results                                                           | . 89         |

|   | 3.6 | Conclusion                                                                    | . 91         |

| 4 |     | Novel Time-Domain Phase Quantization Noise Extraction for a VCC sed Quantizer | )-<br>103    |

|   | 4.1 | Introduction                                                                  | . 103        |

|   | 4.2 | Prior Art                                                                     | . 106        |

|   | 4.3 | Proposed Structure                                                            | . 111        |

|   | 4.4 | Simulation Results                                                            | . 116        |

|   | 4.5 | Conclusion                                                                    | . 117        |

| 5 | Со  | onclusion                                                                     | 125          |

|   | 5.1 | Conclusion                                                                    | . 125        |

|   | 5.2 | Future work                                                                   | . 127        |

## LIST OF FIGURES

| Figur |                                                                                                                                                       | Page |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.3   | Egg model for electronic applications [1]                                                                                                             | . 2  |

| 1.2   | 2 Block diagram of a simple receiver chain                                                                                                            | . 2  |

| 1.5   | 3 (a) Effect of process scaling on the maximum signal swing. (b) Effect of process scaling and thermal noise on the resolution of voltage domain ADCs |      |

| 2.1   | 1-1 MASH architecture based on open loop VCO-based ADCs [10].                                                                                         | 12   |

| 2.5   | The timing diagram of the $E_{Q1}(t)$ pulse extraction [10]                                                                                           | . 13 |

| 2.3   | B Proposed 1-1 MASH ADC structure [18]                                                                                                                | . 18 |

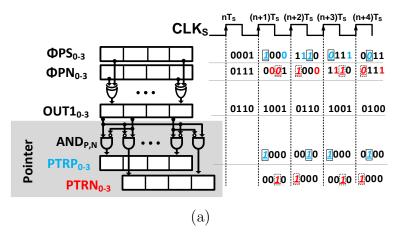

| 2.4   | Block diagram and timing of QPD                                                                                                                       | . 18 |

| 2.5   | 6 Linear model of the proposed 1-1 MASH                                                                                                               | . 19 |

| 2.6   | S Pseudo-differential structure of the proposed 1-1 MASH                                                                                              | . 25 |

| 2.7   | Example of phase extraction in the proposed pseudo-differential architecture.                                                                         |      |

| 2.8   | PSD of the proposed pseudo-differential 1-1 MASH                                                                                                      | . 29 |

| 2.9   | Peak $SQNR$ vs. $(V_{DD}K_{VCO2}/f_{fr1})$                                                                                                            | . 31 |

| 2.3   | 0 Maximum achievable $SQNR$ for different values of $N$                                                                                               | . 35 |

| 2.3   | 1 Maximum achievable $SQNR$ for different values of $OSR$                                                                                             | . 36 |

| 2.1   | 2 Maximum achievable $SQNR$ for different values of $f_{fr1}$                                                                                         | . 38 |

| 2.1   | 13 $PSD$ of the output of a pseudo-differential open loop VCO-based ADC                                                                               |      |

| 2.1   | 4 Maximum achievable $SNDR$ of the proposed ADC vs. $N$ , with linear and non-linear VCO                                                              |      |

| 2.1   | 5 $SQNR$ vs. $f_{fr1}/(K_{VCO2}V_{DD})$ variation from its nominal value                                                                              | . 43 |

| 2.1   | 16 Proposed calibration method. (a) $f_{fr1}$ extraction, (b) $K_{VCO2}$ extraction - phase 1, (c) $K_{VCO2}$ extraction - phase 2                    |      |

## LIST OF FIGURES (Continued)

| Figure |                                                                                                                                                                                                  | Page |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.17   | Effect of VCO mismatch on the pseudo-differential structure                                                                                                                                      | . 46 |

| 2.18   | Pulse width extension in the QPD block                                                                                                                                                           | . 47 |

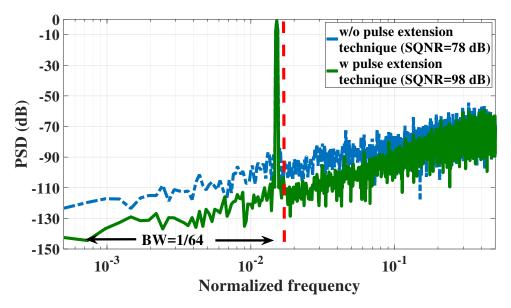

| 2.19   | Effect of pulse width extension technique on the proposed 1-1 MASH ADC                                                                                                                           | . 49 |

| 2.20   | Effect of propagation delay on $E_{Q1}(t)$                                                                                                                                                       | . 50 |

| 2.21   | Effect of non-zero setup/hold times of the quantizer                                                                                                                                             | . 51 |

| 2.22   | Proposed quantizer                                                                                                                                                                               | . 54 |

| 2.23   | B Effect of slow rise/fall times of QPD                                                                                                                                                          | . 56 |

| 2.24   | Simplified schematic of the proposed 1-1 MASH ADC                                                                                                                                                | . 57 |

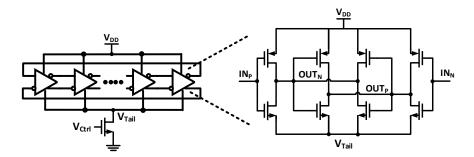

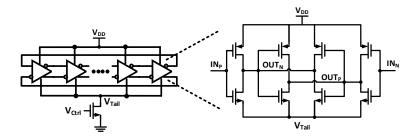

| 2.25   | Delay cell used in the first stage VCO                                                                                                                                                           | . 58 |

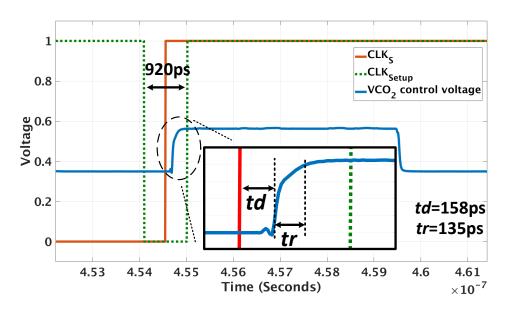

| 2.26   | Transient response of the VCO <sub>2</sub> control voltage                                                                                                                                       | . 60 |

| 2.27   | Spectrum of the proposed 1-1 MASH output. (a) $f_{in}$ =180 kHz, (b) $f_{in}$ =800 kHz                                                                                                           | . 61 |

| 3.1    | Open loop first order VCO-based V-to-F converter. (a) Conceptual realization. (b) Block diagram                                                                                                  | . 73 |

| 3.2    | Closed loop first order VCO-based V-to-P converter. (a) Conceptual realization. (b) Block diagram                                                                                                | . 75 |

| 3.3    | Block diagram of the proposed 1-1 MASH ADC                                                                                                                                                       | . 77 |

| 3.4    | $f_{VCO2}(t)$ behavior when a PWM signal is applied to its input                                                                                                                                 | . 78 |

| 3.5    | Linear model of the proposed 1-1 MASH ADC                                                                                                                                                        | . 79 |

| 3.6    | VCO <sub>1</sub> output and phase quantization noise. (a) Timing diagram. (b) Phase diagram. [29]                                                                                                | . 82 |

| 3.7    | Phase quantization noise extraction in the time domain as a PWM signal. (a) Detecting the proper output phase tap carrying $\phi_{QC1}$ . (b) PWM pulse generation corresponding to $\phi_{QC1}$ | . 84 |

## LIST OF FIGURES (Continued)

| Fig | gure |                                                                                                                                 | <u>P</u> | age |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------|----------|-----|

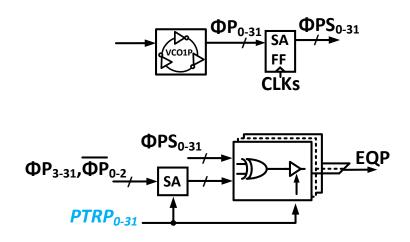

|     | 3.8  | Simplified schematic of the proposed 1-1 MASH ADC                                                                               |          | 86  |

|     | 3.9  | Delay cell used in the first stage VCO                                                                                          |          | 87  |

|     | 3.10 | Pulse extension                                                                                                                 |          | 89  |

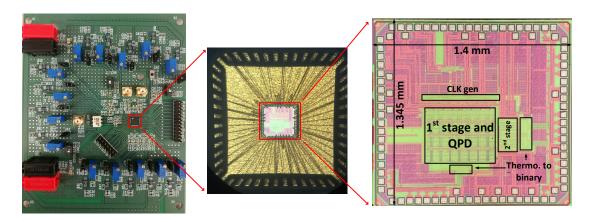

|     | 3.11 | Test board, the package and the die micrograph                                                                                  |          | 90  |

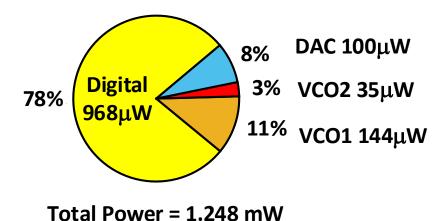

|     | 3.12 | Power breakdown                                                                                                                 |          | 91  |

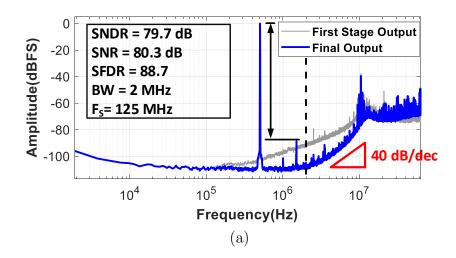

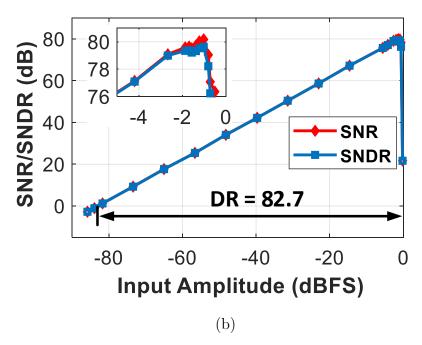

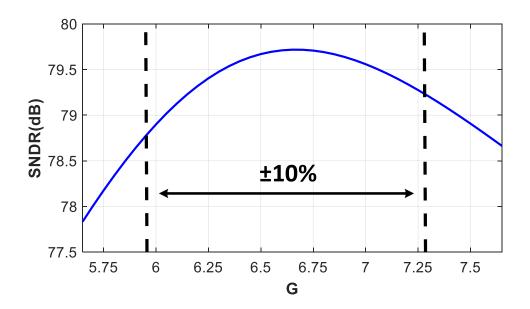

|     | 3.13 | (a) Measured output PSD. (b) Measured SNR/SNDR versus input amplitude. The measurements have been done for 65536 sampled points |          | 92  |

|     | 3.14 | Effect of NCF2 gain $(G)$ variation from its nominal value                                                                      |          | 94  |

|     | 4.1  | Conventional open-loop VCO-based ADC [19]                                                                                       |          | 106 |

|     | 4.2  | VCO quantization noise extraction reported in [23]                                                                              |          | 110 |

|     | 4.3  | Proposed phase quantization noise extraction                                                                                    |          | 112 |

|     | 4.4  | Proposed 0-1-1 MASH ADC structure                                                                                               |          | 115 |

|     | 4.5  | PSD of the proposed 0-1-1 MASH ADC                                                                                              |          | 118 |

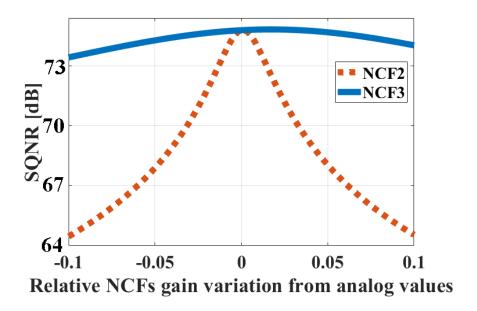

|     | 4.6  | SNDR VS. NCFs gain variation from their nominal values                                                                          |          | 119 |

## LIST OF TABLES

| Table |                                                                | P | age |

|-------|----------------------------------------------------------------|---|-----|

| 2.1   | Specifications of the proposed 1-1 MASH                        |   | 29  |

| 2.2   | Specifications of the proposed 1-1 MASH                        | • | 31  |

| 2.3   | Non-idealities and related solutions                           |   | 39  |

| 2.4   | Required specifications of the proposed PROPOSED 1-1 MASH $$ . |   | 57  |

| 2.5   | Design Parameters of the proposed 1-1 MASH                     | • | 59  |

| 2.6   | Performance Comparison                                         | • | 62  |

| 3.1   | Performance summary and comparison to prior art                |   | 93  |

To my dearest Parents,

Fatemeh and Javad

for their unconditional love and sacrifice

#### Chapter 1: Introduction

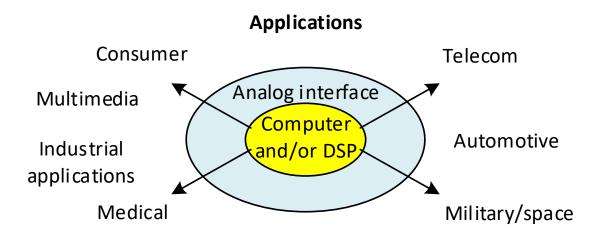

All signals occurring in the real world are analog. A beautiful sound of a bird singing, the light which reflects on objects that helps us see things and the electromagnetic waves used in the communication between two people through cellphones are all analog. The analog signals are continuous in time and magnitude. On the other hand, the processors (computers) process information in the digital domain. Thus, they operate with discrete time and magnitude (digital) signals. Most of the signal processing is performed in the digital-domain using digital signal processors (DSPs). Figure 1.1 shows the egg model for electronic applications [1]. There has to be an interface block to connect the real world signals to the computers for processing. This block is called an analog-to-digital converter (ADC).

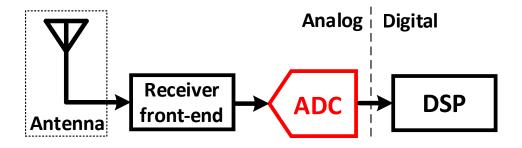

ADCs are the essential components of electronic devices which interact with the real world. A high-quality microphone picking up the sound in nature, photocells in a video camera and a seismographic sensor to detect any small vibration of earth, all require different ADCs with different requirements to convert the analog signals to digital. Figure 1.2 shows an example of an ADC application in a conventional receiver and how the ADC is incorporated. First, the signal is detected by an antenna and then it is amplified and filtered by the receiver front-end. After that, the desired signal is digitized by the ADC and the ADC output which is in the digital domain, is further processed in a DSP.

Figure 1.1: Egg model for electronic applications [1].

Figure 1.2: Block diagram of a simple receiver chain.

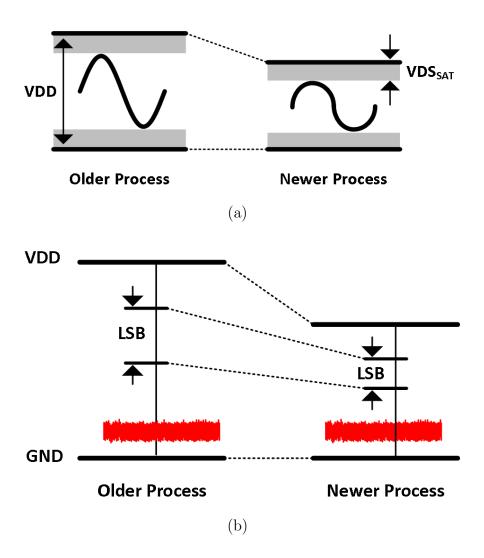

In order to reduce system cost, it is highly desirable to integrate analog and digital systems together onto a single chip. Digital circuitry is the technology driver since it represents the majority of the chip area and functionality. To achieve higher performance with reduced cost for digital systems, the transistor sizes are reduced from one generation to the next. This size reduction greatly benefits digital circuitry switching speed and reduces the area needed to achieve a particular function. Alternately, this scaling handicaps the analog circuit performance due to the reduction in the analog transistor intrinsic gain and voltage headroom. Figure 1.3 (a) shows the voltage headroom reduction in moving to a new process. As the supply voltage scales down as is the case in newer technologies, the maximum allowable signal swing decreases. This has a negative impact on analog circuits such as ADCs. As shown in Fig. 1.3 (b), as the supply voltage reduces, the least significant bit (LSB) voltage of the ADC scales down relatively to provide the same resolution, while the thermal noise remains the same. As a result, for a given signal-to-noise ratio and in a thermal noise limited scenario, the power consumption of the ADC has to be increased to reduce the thermal noise for a new technology node. In addition to this issue, conventional ADCs need high gain high bandwidth (BW) operational transconductance amplifiers (OTAs). Designing high performance OTAs is becoming more challenging in advanced technology nodes due to the reduced voltage headroom and reduced intrinsic gain of the transistors. Due to these issues, new ADC implementations are required that benefit from process scaling [2,3].

One attractive alternative to conventional ADCs is time-domain ADCs. In

Figure 1.3: (a) Effect of process scaling on the maximum signal swing. (b) Effect of process scaling and thermal noise on the resolution of voltage domain ADCs.

these type of ADC, quantization is performed in the time-domain. As the transistor size reduces due to the process scaling, the time-domain resolution improves due to a reduced gate delay. Therefore, these ADCs take advantage of process scaling. Because of these advantages, time-domain ADCs have gained more attention recently [4].

## 1.1 Scope of this work

VCO-based quantizers (VCOQs) are a popular time-domain quantizer architecture. The simple digital friendly implementation of VCO-based quantizers makes them power and area efficient in advanced nano-meter CMOS processes [5]. Also these quantizers provide first order of noise shaping. While these are desirable characteristics, often the major performance limitation of VCO-based ADCs is the VCO nonlinearity.

The focus of this work is mainly on developing new techniques to enhance the precision of VCO-based ADCs without using OTAs or power hungry linearization methods. This precision enhancement is achieved by improving the linearity of VCO-based ADCs and also increasing the order of the noise shaping. To achieve this high precision OTA-less VCO-based ADCs, two novel methods are proposed. First, a highly linear VCO-based 1-1 MASH  $\Delta\Sigma$  ADC structure is presented and measurement results are provided. Second, a novel time-dmain phase quantization noise extraction for a VCO-based quantizer is introduced. Using this technique a second order noise shaping SAR-VCO ADC is realized. Simulation results are

provided to validate the performance of the proposed ADC.

## 1.2 Thesis organization

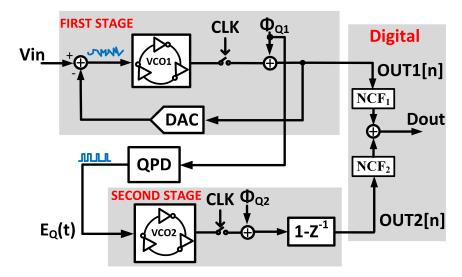

The rest of the thesis is organized as follows. In Chapter 2 a 1-1 MASH OTA-less VCO-based ADC using single phase VCOs is presented. In-depth analysis of the effect of different non-idealities is provided in this chapter. In Chapter 3 a technique is introduced to extract the quantization noise of a multi-phase VCO. Using this technique, the implementation of the 1-1 MASH using multi-phase VCOs is described and then measurement results are provided from a fabricated prototype. In Chapter 4 another high precision quantization noise extraction technique is introduced. Using this technique a second order noise shaping SAR-VCO is realized and simulation results are provided. Finally, Chapter 5 provides a brief summary and concludes the paper.

## Bibliography

- [1] P. R. Gray, P. Hurst, R. G. Meyer, and S. Lewis, *Analysis and design of analog integrated circuits*. Wiley, 2001.

- [2] A. Sanyal, S. Li, and N. Sun, "Low-power scaling-friendly ring oscillator based adc," in 2018 IEEE International Symposium on Circuits and Systems (IS-CAS), May 2018, pp. 1–5.

- [3] A. Babaie-Fishani and P. Rombouts, "A Mostly Digital VCO-Based CT-SDM With Third-Order Noise Shaping," *IEEE Journal of Solid-State Circuits*, vol. 52, no. 8, pp. 2141–2153, Aug 2017.

- [4] W. Yu, K. Kim, and S. Cho, "A 148  $fs_{rms}$  integrated noise 4 MHz bandwidth second-order  $\Delta\Sigma$  time-to-digital converter with gated switched-ring oscillator," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 61, no. 8, pp. 2281–2289, 2014.

- [5] M. Z. Straayer and M. H. Perrott, "A 12-bit, 10-MHz bandwidth, continuoustime ΣΔ ADC with a 5-bit, 950-MS/s VCO-based quantizer," *IEEE Journal* of Solid-State Circuits, vol. 43, no. 4, pp. 805-814, 2008.

# Chapter 2: A Highly Linear OTA-free VCO-based 1-1 MASH $\Delta\Sigma$ ADC

In this chapter, a new VCO-based 1-1 MASH delta-sigma ADC structure is presented. The proposed architecture does not require any OTA-based analog integrators or integrating capacitors. Second-order noise shaping is achieved by using a VCO as an integrator in the feedback loop of the first stage and an open loop VCO quantizer in the second stage. Simple digital circuitry extracts the phase quantization error of the first stage as a pulse signal that is applied to the second stage. The input of the first VCO is a very small amplitude signal and the input of the second VCO is a two-level PWM signal. Therefore, the VCO non-linearity does not limit the overall ADC performance, mitigating the need for power hungry linearization methods. The proposed idea was simulated at the transistor level and the results verify the analysis.

#### 2.1 Introduction

Quantization noise shaping combined with oversampling in data converters enhances the signal-to-quantization-noise (SQNR) ratio in a particular frequency band. By pushing most of the quantization noise out of the signal band, oversampling data converters are able to achieve high resolution at reasonably high

conversion speeds [1]. Although noise shaping techniques have been applied to different types of analog-to-digital converters (ADCs) such as successive approximation register (SAR) ADCs [2,3], integrating quantizer ADCs [4], etc., they are most commonly used in delta-sigma ( $\Delta\Sigma$ ) modulators.

$\Delta\Sigma$  ADCs utilize oversampling and noise shaping to achieve high accuracy despite using inaccurate components. This feature combined with relaxed antialiasing requirements make  $\Delta\Sigma$  ADCs an appropriate choice for various applications from ultra-low-power biomedical devices to ultra-wide-band communications applications [5].

Continuous-time (CT)  $\Delta\Sigma$  ADCs have the advantage of inherent anti-aliasing filtering compared to discrete-time (DT)  $\Delta\Sigma$  ADCs. Loop filter integrators in CT  $\Delta\Sigma$  ADCs are usually implemented using active RC-integrators due to the linearity requirements [1]. However, with process scaling, the intrinsic gain of the transistor reduces, which makes it increasingly difficult to design high gain operational transconductance amplifiers (OTAs) in modern CMOS processes.

As the supply head-room reduces with process scaling, multibit quantizers are becoming more difficult to design due to the offset and noise requirements of the comparators. One attractive alternative is to use time domain quantizers such as time-to-digital converters (TDC) or VCO-based quantizers. TDCs and VCO-based quantizers benefit from process scaling due to the increased time resolution of the delay cells.

Moreover, the digital friendly nature of VCO-based  $\Delta\Sigma$  ADCs makes them power and area efficient in advanced nano-meter CMOS processes [6]. While these

are desirable characteristics, often the major performance limitation of VCO-based ADCs is the VCO non-linearity. Several techniques have been introduced to mitigate the non-linearity issue. In [6] a VCO-based quantizer is implemented inside a closed loop. Here, the high in-band loop gain suppresses the VCO non-linearity. In order to achieve more than first-order noise shaping, however, this architecture needs OTAs which generally have higher power requirements as compared to VCOs and do not scale well with process scaling. In [7–9], two stage architectures were employed to cancel out the harmonic components due to the VCO non-linearity. Although these architectures solve the VCO non-linearity issue, the loop filter implementations employ OTAs. In [10–13] the VCO non-linearity is corrected by using a pulse width modulated (PWM) input signal. However, to achieve high linearity, a power hungry PWM generator is needed at the input. In [14–16] VCOs are used as a phase integrator followed by a quantizer. Therefore, the input signal to the VCO is reduced and VCO non-linearity is suppressed significantly. However, in [14], the order of the modulator is limited to one and [15,16] require OTAs to implement high order noise shaping. In [17] a higher order modulator using enhanced linearity VCOs is introduced. Although, no OTA is used, the linearity of the modulator is still limited to around 10.5 bits.

In this chapter, a novel highly linear VCO-based 1-1 MASH architecture is presented that does not require an OTA or a PWM generator. The first stage is a closed loop first-order VCO-based ADC. The quantization noise of the first stage is extracted in the time domain using simple digital circuitry. The extracted quantization noise, which is in PWM form, is fed to the second stage which is an open

loop VCO-based ADC. The proposed structure suppresses the VCO non-linearity without the added requirement of a PWM generator at the input. Moreover, since no OTA is used in this ADC, this architecture benefits from process scaling.

The organization of this chapter is as follows. In Section 2.2 the 1-1 MASH VCO-based  $\Delta\Sigma$  ADC presented in [10,11] is reviewed to provide a background for the proposed structure. This architecture needs a PWM generator at its input to suppress the VCO non-linearity. The proposed highly linear 1-1 MASH VCO-based  $\Delta\Sigma$  ADC, which mitigates the use of a PWM generator is presented in Section 2.3. Section 2.4 provides design insight for the proposed architecture by examining the effect of different design parameters on the performance. In Section 2.5, the effects of non-idealities on the performance are analyzed. Next, a transistor level design example is demonstrated to verify the analysis in Section 2.6. Finally, Section 2.7 concludes the chapter.

#### 2.2 Prior Art

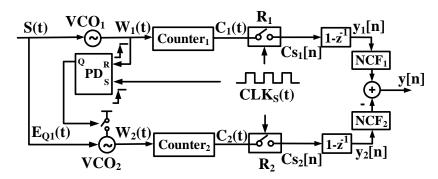

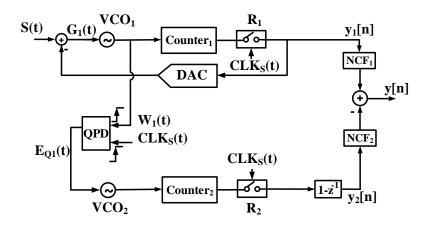

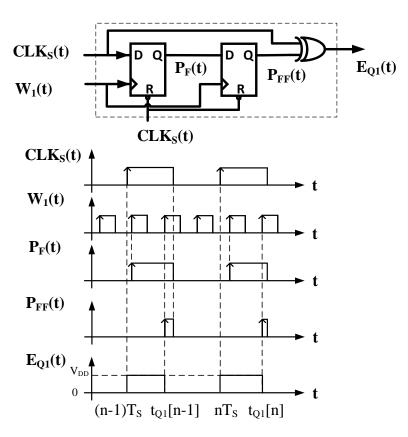

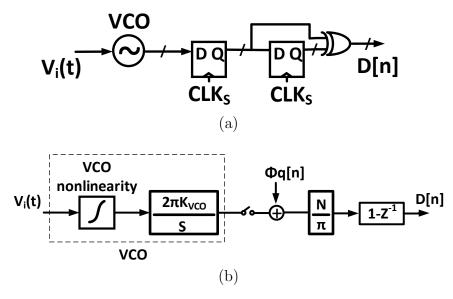

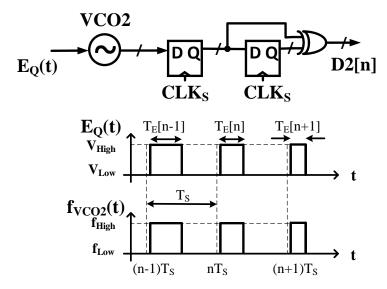

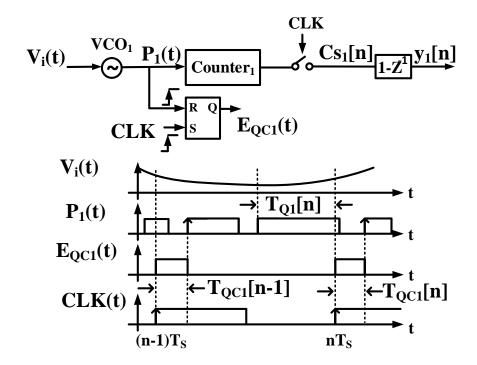

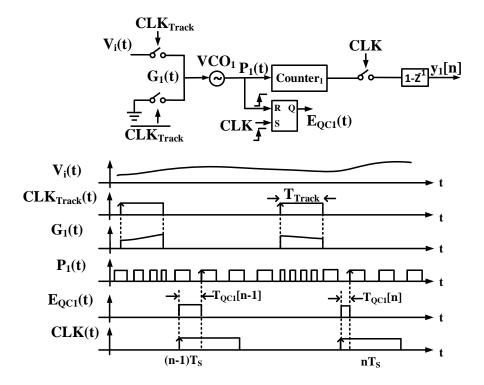

Fig. 2.1 shows a 1-1 MASH VCO-based ADC architecture presented in [10, 11]. Both stages of the ADC are open loop VCO-based quantizers. The first stage quantizers the input voltage. A phase detector (PD) block shown in Fig. 2.1 generates a pulse signal which goes high  $(V_{DD})$  at the positive edge of the sampling clock  $(CLK_S(t))$  and goes low at the first positive edge of the  $VCO_1$  output  $(W_1(t))$  in that sampling period. This signal is shown as  $E_{Q1}(t)$  in Fig. 2.2. In order to process the first stage quantization noise in the second stage, the generated pulse

signal switches on and off VCO<sub>2</sub>. In this architecture, the input signal is required to be fed to VCO<sub>2</sub>. In this way, the quantization error of the first stage will be available at the output of the second stage and can be removed in the final output by using simple digital filters. A more detailed explanation of the architecture is as follows.

Figure 2.1: 1-1 MASH architecture based on open loop VCO-based ADCs [10].

The output of VCO<sub>1</sub> is a square wave signal  $W_1(t)$ , the frequency of which is a linear function of the VCO input signal S(t). Equation (2.1) shows the relationship between VCO<sub>1</sub> output phase  $(\phi_1(t))$  and its input voltage (S(t)). In this equation,  $K_{VCO1}$  and  $f_{fr1}$  are the voltage-to-frequency gain and the free-running frequency of VCO<sub>1</sub>, respectively.

$$\phi_1(t) = \int_0^t (2\pi K_{VCO1}S(t) + 2\pi f_{fr1})dt$$

(2.1)

Counter<sub>1</sub> output increases for each rising edge of  $W_1(t)$  which is equal to a  $2\pi$  radian phase change of the VCO output. The output of Counter<sub>1</sub> is sampled by register  $R_1$  on the rising edge of  $CLK_S$ . Equation (2.2) describes the sampled

output of Counter<sub>1</sub>,  $Cs_1[n]$ . In this equation  $\phi_{q1}$  is the first stage quantization phase error. It is a function of both the input voltage and the time difference between the rising edge of  $CLK_S(nTs)$  and the first rising edge of  $W_1(t)$   $(t_{Q1}[n])$  in each sampling period as shown in Fig. 2.2.

$$Cs_{1}[n] = \frac{\phi_{1}(nT_{S}) + \phi_{q1}(nT_{S})}{2\pi}$$

$$= \int_{0}^{nT_{S}} (K_{VCO1}S(t) + f_{fr1}) dt$$

$$+ \int_{nT_{S}}^{t_{Q1}[n]} (K_{VCO1}S(t) + f_{fr1}) dt$$

(2.2)

The sampled Counter<sub>1</sub> output is digitally differentiated  $(Cs_1[n] - Cs_1[n-1])$  to generate the first stage output which is equal to:

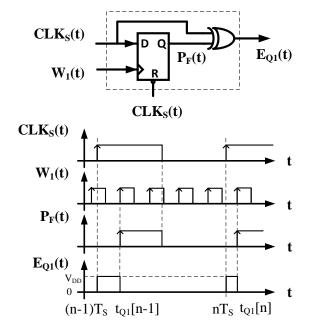

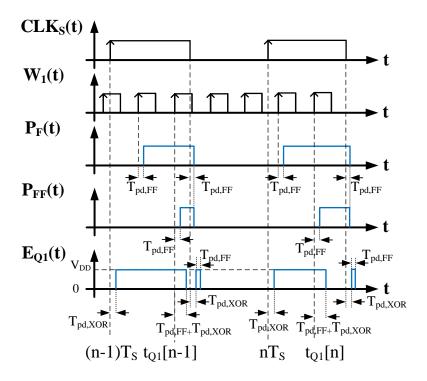

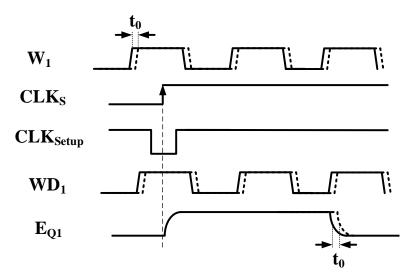

Figure 2.2: The timing diagram of the  $E_{Q1}(t)$  pulse extraction [10].

$$y_{1}[n] = \int_{(n-1)T_{S}}^{nT_{S}} (K_{VCO1}S(t) + f_{fr1}) dt + \frac{\phi_{q1}(nT_{S}) - \phi_{q1}((n-1)T_{S})}{2\pi}$$

(2.3)

Assuming the sampling frequency is much higher than the input signal bandwidth (BW), the input signal can be assumed constant between two consecutive samples. Thus, using z-transforms the first stage output is:

$$Y_{1}(z) = (K_{VCO1}T_{S}z^{-1}) S(z) + f_{fr1}T_{S} + (1 - z^{-1}) \frac{\phi_{q1}(z)}{2\pi}$$

(2.4)

where  $f_{fr1}T_S$  is an offset and can be easily removed in the digital domain. First-order noise shaping can be seen in the above equation.

In a MASH structure, the quantization noise of the first stage is processed by the second stage. The quantization noise in VCO-based ADCs is contained in the phase domain and it does not explicitly exist in this structure. As can be seen in (2.2), the phase quantization error of the first stage is the integral of the input signal between the rising edge of  $CLK_S(nTs)$  and the first rising edge of  $W_1(t)$  ( $t_{Q1}[n]$ ). Fig. 2.2 shows this time difference as a pulse signal ( $E_{Q1}(t)$ ) in the time domain. Since  $E_{Q1}(t)$  is high ( $V_{DD}$ ) only between  $kT_S$  and  $t_Q[k]$  (k = 0,1,2,...)

and zero elsewhere,  $\phi_{q1}((n-1)Ts)$  can be written as:

$$\phi_{q1} ((n-1) T_S) = \int_{(n-1)T_S}^{t_{Q1}[n-1]} 2\pi (K_{VCO1}S(t) + f_{fr1}) dt$$

$$= 2\pi \int_{(n-1)T_S}^{nT_S} \frac{E_{Q1}(t)}{V_{DD}} (K_{VCO1}S(t) + f_{fr1}) dt$$

(2.5)

In order to cancel  $\phi_{q1}$  at the final output of the MASH structure, first  $\phi_{q1}$  is generated at the second stage output. Then, by applying proper digital filtering to each stage output and subtracting the two signals from each other,  $\phi_{q1}$  is canceled at the final output. Equation (2.5) shows that  $\phi_{q1}$  is a function of both  $E_{Q1}(t)$  and S(t). To generate  $\phi_{q1}$  at the second stage output, the input signal is applied to the VCO<sub>2</sub> input. A control switch is added to VCO<sub>2</sub> which turns it off (on) when  $E_{Q1}(t)$  is low (high) as shown in Fig. 2.1. In this way the VCO<sub>2</sub> output phase changes only when  $E_{Q1}(t)$  is high. The VCO<sub>2</sub> output phase holds its value when  $E_{Q1}(t)$  is low. The VCO<sub>2</sub> output phase can be written:

$$\phi_2(t) = \int_0^t \frac{E_{Q1}(t)}{V_{DD}} \left( 2\pi K_{VCO2} S(t) + 2\pi f_{fr2} \right) dt$$

(2.6)

Similar to the first stage, the output of the second stage is calculated by digitally differentiating the sampled Counter<sub>2</sub> output  $(Cs_2[n] - Cs_2[n-1])$  and is equal to:

$$y_{2}[n] = \int_{(n-1)T_{S}}^{nT_{S}} \frac{E_{Q1}(t)}{V_{DD}} (K_{VCO2}S(t) + f_{fr2}) dt + \frac{\phi_{q2}(nT_{S}) - \phi_{q2}((n-1)T_{S})}{2\pi}$$

(2.7)

Assuming both VCOs are perfectly matched, the first term of (2.7) matches (2.5). Thus, using z-transforms the second stage output is:

$$Y_{2}(z) = (z^{-1}) \frac{\phi_{q1}(z)}{2\pi} + (1 - z^{-1}) \frac{\phi_{q2}(z)}{2\pi}$$

(2.8)

Based on (2.4) and (2.8), to cancel  $\phi_{q1}$ , simple digital filters are used as follow:

$$NCF_{1}(z) = z^{-1}$$

$$NCF_{2}(z) = (1 - z^{-1})$$

(2.9)

Therefore, the final output can be derived as:

$$Y(z) = z^{-2} \left( K_{VCO1} T_S \right) S(z) + \left( 1 - z^{-1} \right)^2 \frac{\phi_{q2}(z)}{2\pi}$$

(2.10)

In the architecture presented in [10,11], second-order noise shaping has been achieved using two VCOs in a MASH structure. This architecture does not require OTAs and therefore has the benefits of scalability and reduced power. The frequency of VCO<sub>1</sub> changes proportional to the input voltage (S(t)). Thus, the width of the generated pulse  $(E_{Q1}(t))$  is also a function of S(t) and it does not explicitly correspond to  $\phi_{q1}$ . In order to generate  $\phi_{q1}$  at the output of the second stage, S(t) also has to be applied to VCO<sub>2</sub>. Since the input signal is directly fed to both the VCOs, the non-linearity of the VCOs still limits the overall ADC performance. In [10] a PWM generator is used at the input to generate a PWM signal. The linearity of the PWM generator is important and thus this block consumes

significant power [12]. Additionally, VCO<sub>2</sub> has to hold its phase perfectly when it is turned off which is challenging in practice due to circuit nonidealities, such as leakage current and charge redistribution.

In Section 2.3, a new 1-1 MASH VCO-based  $\Delta\Sigma$  ADC is proposed. In this structure, the VCO non-linearity is inherently suppressed, and two VCOs are utilized to achieve second-order noise shaping. There is also no need for any OTA or a power hungry linearization method.

### 2.3 Proposed Structure

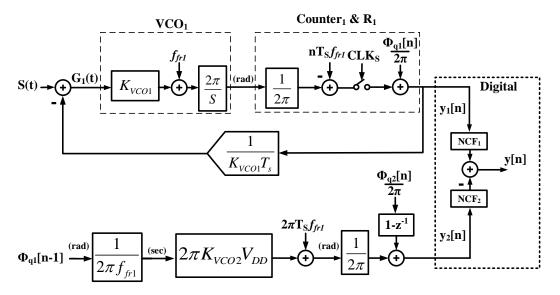

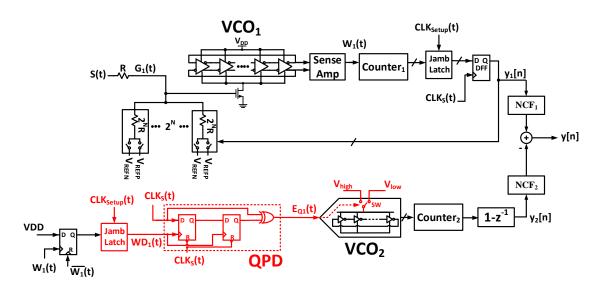

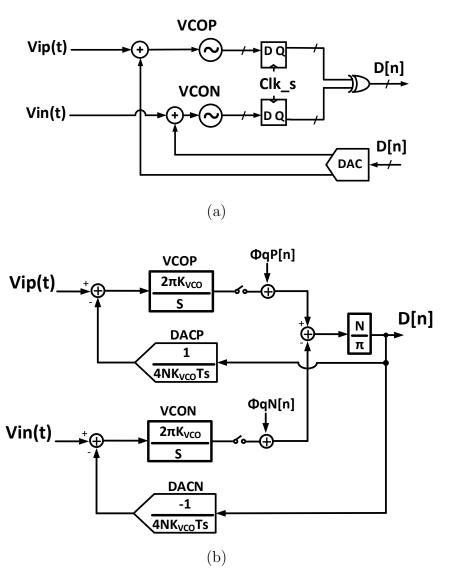

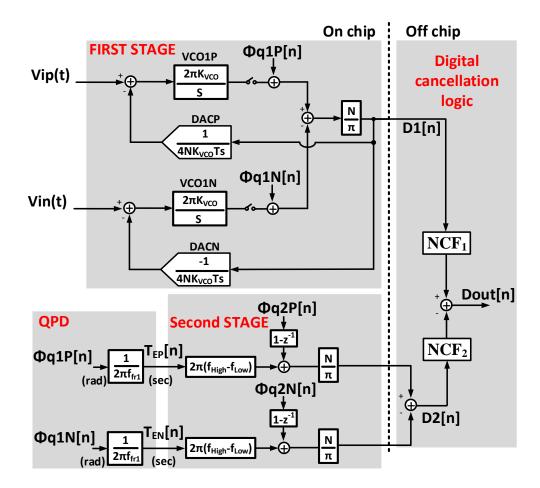

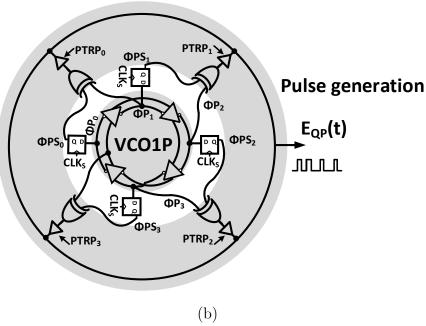

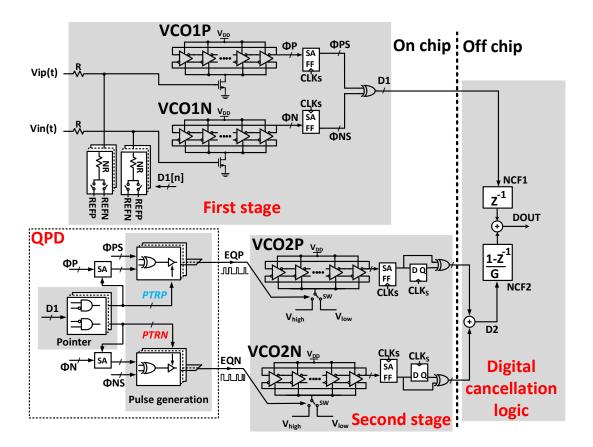

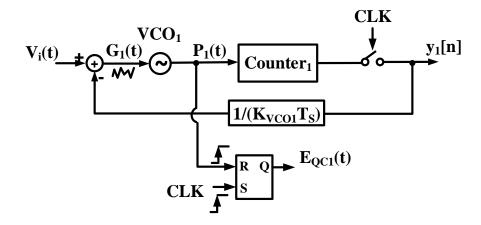

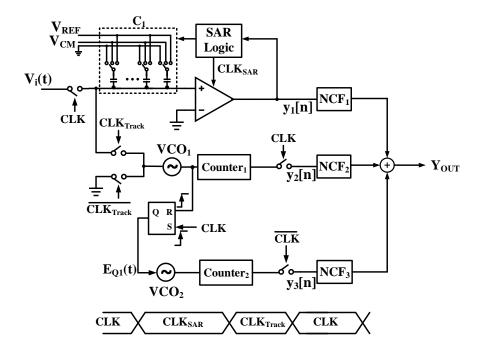

Fig. 2.3 shows the block diagram of the proposed VCO-based 1-1 MASH ADC. In this structure, the first stage is a closed-loop architecture with phase feedback and the second stage is an open-loop VCO-based ADC. VCO<sub>1</sub> in the first stage is used in the phase domain and operates as an integrator. Counter<sub>1</sub> works as an N-bit  $(2^N \text{ level})$  phase quantizer and its output is sampled by a register which generates the first stage output codes. The output of the first stage is fed back to the VCO<sub>1</sub> input using a DAC. Similar to Fig. 2.1, VCO<sub>2</sub> in the second stage is used in the frequency domain. However, in the proposed architecture, the input signal is not connected to the input of VCO<sub>2</sub>, compared to the architecture reported in [10,11]. Here, a two level PWM signal generated in the first stage is applied to VCO<sub>2</sub>. In this work, the PD block shown in Fig. 2.1 is replaced by a quantization phase detector (QPD) block. As shown in Fig. 2.4, the QPD block is made up of a flip-flop and an XOR gate which generates the pulse signal  $E_{Q1}(t)$ . Similar to Fig. 2.2,

$E_{Q1}(t)$  is high  $(V_{DD})$  between the rising edge of  $CLK_S(nT_S)$  and the first rising edge of  $W_1(t)$   $(t_{Q1}[n])$  in each sampling period and zero elsewhere.

Figure 2.3: Proposed 1-1 MASH ADC structure [18].

Figure 2.4: Block diagram and timing of QPD.

Compared to the architecture shown in Fig. 2.1, there is no first-order differentiator after Counter<sub>1</sub> and VCO<sub>1</sub> is used in a feedback loop. As shown below, the signal magnitude at the input of VCO<sub>1</sub> is small and this provides two benefits:

1) the linearity of the first stage is improved significantly, and 2) compared to the architectures in [10,11], the quantization phase error of the first stage can be extracted in the time-domain as a two-level PWM signal. Therefore, the second stage is inherently linear. Also, there is no need for an additional PWM generator at the input.

Figure 2.5: Linear model of the proposed 1-1 MASH.

A linear model of the proposed 1-1 MASH ADC is shown in Fig. 2.5. VCO<sub>1</sub> acts as a phase integrator. When the counter output unit increments, it indicates a phase change of  $2\pi$  radians. The register samples the counter output at each rising edge of  $CLK_S$ . Therefore,  $y_1[n]$  is proportional to the VCO<sub>1</sub> output phase

with some additional phase quantization noise. Due to the free running frequency of VCO<sub>1</sub>, the sampled Counter<sub>1</sub> output contains a ramp signal in the discrete time domain. To cancel the effect of the ramp signal in the linear model,  $nT_Sf_{fr1}$  is subtracted from the sampled Counter<sub>1</sub> output. This issue is explained in more detail in Section 2.3.1.

Using the linear model shown in Fig. 2.5, the STF and NTF of the proposed 1-1 MASH can be calculated. The output of the first stage  $Y_1(z)$  is:

$$Y_{1}(z) = \left(K_{VCO1}T_{S}z^{-1}\right)S(z) + \left(1 - z^{-1}\right)\frac{\phi_{q1}(z)}{2\pi}$$

(2.11)

Similar to (2.2), the quantization phase error  $(\phi_{q1})$  can be derived as a function of the VCO<sub>1</sub> input signal  $G_1(t)$  as follows (refer to Figs. 2.3 and 2.4):

$$\phi_{q1} ((n-1) T_S) = \int_{(n-1)T_S}^{t_{Q1}[n-1]} 2\pi (K_{VCO1} G_1(t) + f_{fr1}) dt$$

(2.12)

Using (2.11),  $G_1(z)$  can be calculated as:

$$G_{1}(z) = S(z) - \frac{Y_{1}(z)}{K_{VCO1}T_{S}} = (1 - z^{-1}) S(z) - (1 - z^{-1}) \frac{\phi_{q1}(z)}{2\pi (K_{VCO1}T_{S})}$$

(2.13)

In (2.12),  $K_{VCO1}G_1(t)$  is negligible compared to  $f_{fr1}$  as explained next. As shown in (2.13), the first and the second terms of  $G_1(z)$  are the first-order shaped input signal and the quantization noise, respectively. At a high enough oversam-

pling ratio (OSR), the signal magnitude at the VCO input is negligible. Since  $\phi_{q1}$  has a value between zero and  $2\pi$  radians, the maximum value of the second term is  $f_s/K_{VCO1}$ . Note that the value of  $f_{fr1}$  is chosen much higher than  $f_s$  in the design of a conventional counter based quantizer [19]. Therefore,  $f_{fr1}$  is much bigger than  $K_{VCO1}G_1(t)$  and (2.12) can be simplified to:

$$\phi_{q1} ((n-1) T_S) \approx \int_{(n-1)T_S}^{t_{Q1}[n-1]} 2\pi f_{fr1} dt$$

$$= \frac{1}{V_{DD}} \int_{(n-1)T_S}^{nT_S} 2\pi f_{fr1} E_{Q1}(t) dt$$

$$= 2\pi f_{fr1} (t_{Q1} [n-1] - (n-1) T_S)$$

(2.14)

Equation (2.14) demonstrates that there is a linear relationship between the phase domain and time domain quantization noise. Therefore, the phase quantization error information can be extracted in the time domain as a pulse signal. The extracted quantization noise of the first stage ( $E_{Q1}(t)$ ) is applied to the second stage which is implemented as an open loop VCO-based ADC. Since the input of this stage is in PWM form, the non-linearity of VCO<sub>2</sub> is no longer an issue. The phase output of VCO<sub>2</sub> and the second stage output code can be written as:

$$\phi_2(t) = \int_0^t 2\pi \left( K_{VCO2} E_{Q1}(t) + f_{fr2} \right) dt$$

(2.15)

$$y_{2}[n] = \left(\int_{(n-1)T_{S}}^{nT_{S}} K_{VCO2}E_{Q1}(t) dt\right) + T_{S}f_{fr2} + \frac{\phi_{q2}(nT_{S}) - \phi_{q2}((n-1)T_{S})}{2\pi}$$

(2.16)

The first term of (2.16) matches (2.14) with a constant gain difference. Therefore, from (2.14) and (2.16) the following equation can be derived.

$$y_{2}[n] = \frac{K_{VCO2}V_{DD}}{2\pi f_{fr1}} \phi_{q1}((n-1)T_{S}) + T_{S}f_{fr2} + \frac{\phi_{q2}(nT_{S}) - \phi_{q2}((n-1)T_{S})}{2\pi}$$

(2.17)

The term  $T_S f_{fr2}$  is a constant value and can be easily removed in the digital domain. Therefore,  $Y_2(z)$  is:

$$Y_{2}(z) = \left(\frac{K_{VCO2}V_{DD}}{f_{fr1}}z^{-1}\right)\frac{\phi_{q1}(z)}{2\pi} + \left(1 - z^{-1}\right)\frac{\phi_{q2}(z)}{2\pi}$$

(2.18)

As shown in Fig. 2.5, to generate the MASH output code, y[n], a simple set of digital filters are used as follows:

$$NCF_{1}(z) = z^{-1}$$

$$NCF_{2}(z) = (1 - z^{-1}) \frac{f_{fr1}}{K_{VCO2}V_{DD}}$$

(2.19)

Therefore, the final output is:

$$Y(z) = NCF_{1}(z) Y_{1}(z) - NCF_{2}(z) Y_{2}(z)$$

$$= z^{-2} (K_{VCO1}T_{s}) S(z)$$

$$+ (1 - z^{-1})^{2} \frac{f_{fr1}}{2\pi K_{VCO2}V_{DD}} \phi_{q2}(z)$$

(2.20)

Equation (2.20) shows second order noise shaping. Considering the input signal is a sine wave, the maximum signal amplitude at the output (assuming N is large enough) is  $2^{N-1}$ . Here N is the number of Counter<sub>1</sub> bits ( $2^N$  level quantizer). Therefore, the maximum signal power at the output is:

$$P_{sig-max} = \left(\frac{2^{N-1}}{\sqrt{2}}\right)^2 = \frac{2^{2N}}{8} \tag{2.21}$$

Based on (2.20) the quantization noise power at the output can be calculated as:

$$P_{Q-noise} = \int_{\frac{-f_S}{2OSR}}^{\frac{f_S}{2OSR}} \frac{\Delta^2}{12f_S} \left| \left( \frac{f_{fr1}}{2\pi K_{VCO2} V_{DD}} \right) \left( 1 - e^{-j\frac{2\pi f}{f_S}} \right)^2 \right|^2 df$$

$$= \left( \frac{f_{fr1}}{V_{DD} K_{VCO2}} \right)^2 \frac{\pi^4}{60OSR^5}$$

(2.22)

where,  $\Delta$  is the LSB of  $\phi_{q1}$  and is equal to  $2\pi$ . Therefore, the peak signal-to-

quantization-noise ratio (SQNR) is

$$Peak \, SQNR = 6 \cdot 02N - 11 \cdot 14 +50 \log \left( OSR \right) + 20 \log \left( \frac{V_{DD} K_{VCO2}}{f_{fr1}} \right)$$

(2.23)

Choosing  $f_{fr1} = V_{DD}K_{VCO2}$  results in the same SQNR as a conventional second-order delta-sigma ADC with an N-bit quantizer [1].

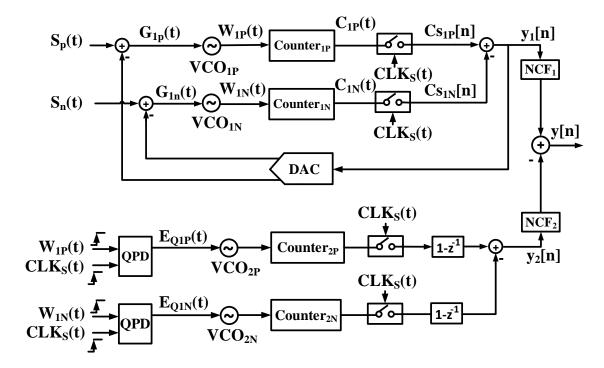

## 2.3.1 Pseudo-differential implementation

In this sub-section, a pseudo-differential implementation of the proposed 1-1 MASH ADC is described. Fig. 2.6 shows the pseudo-differential architecture. In this architecture, two VCOs are arranged in a pseudo-differential manner in each stage. The output phase of the first stage is measured by comparing sampled Counter<sub>1P</sub> and Counter<sub>1N</sub> outputs. In this way,  $y_1[n]$  represents the difference between the two VCO output phases.

Each of the positive and negative paths of the first stage act as a phase integrator followed by a quantizer. Therefore, two different quantization noise sources are in the first stage. As shown in Fig. 2.6, a pair of QPD blocks and a pseudo-differential second stage design are required to remove the first stage quantization noise at the output. As explained in the following, in the pseudo-differential structure, the free running frequency of the VCOs can be chosen arbitrarily.

In a standard VCO, the output phase is the integral of its frequency. The relation between the VCO<sub>1</sub> input voltage (node  $G_1(t)$  shown in Fig. 2.3) and the

output phase is as below:

$$\phi_1(t) = \int_0^t \left(2\pi K_{VCO1}G_1(t) + 2\pi f_{fr1}\right) dt \tag{2.24}$$

Counter<sub>1</sub> converts the phase information to an integer number. According to (2.24), even if  $G_1(t)$  is zero, the output frequency of VCO<sub>1</sub> is  $f_{fr1}$  and the Counter<sub>1</sub> output increases as time goes by. Counter<sub>1</sub> changes counting direction whenever it reaches its range boundaries. Therefore, the sampled Counter<sub>1</sub> output of a single VCO does not convey phase information.

Figure 2.6: Pseudo-differential structure of the proposed 1-1 MASH.

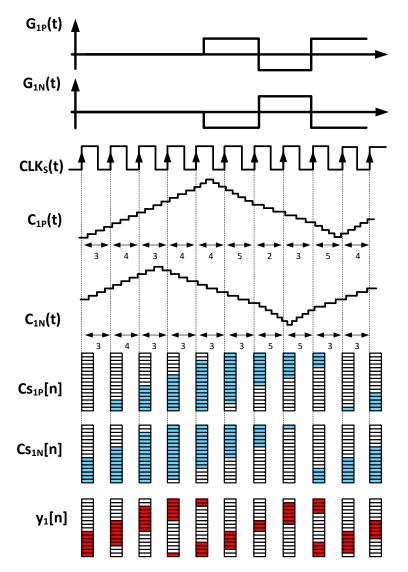

Figure 2.7: Example of phase extraction in the proposed pseudo-differential architecture.

However, this problem is solved in the pseudo-differential structure. The output phases of  $VCO_{1P}$  and  $VCO_{1N}$  shown in Fig. 2.6 are as follows:

$$\phi_{1P,N}(t) = \int_0^t \left(2\pi K_{VCO1P,N} G_{1P,N}(t) + 2\pi f_{fr1P,N}\right) dt \tag{2.25}$$

Similar to (2.2)  $C_{S1P}[n]$  and  $C_{S1N}[n]$  are:

$$Cs_{1P,N}[n] = \frac{\phi_{1P,N}(nT_S) + \phi_{q1P,N}(nT_S)}{2\pi}$$

$$= \int_0^{nT_S} (K_{VCO1P,N}G_{1P,N}(t) + f_{fr1P,N}) dt + \frac{\phi_{q1P,N}(nT_S)}{2\pi}$$

(2.26)

Assuming  $K_{VCO1P} = K_{VCO1N} = K_{VCO1}$  and  $f_{fr1P} = f_{fr1N} = f_{fr1}$ , by taking the difference of  $C_{S1P}[n]$  and  $C_{S1N}[n]$ , the first stage output is:

$$y_{1}[n] = Cs_{1P}[n] - Cs_{1N}[n]$$

$$= \int_{0}^{nT_{S}} K_{VCO1}(G_{1P}(t) - G_{1N}(t)) dt$$

$$+ \frac{\phi_{q1P}(nT_{S}) - \phi_{q1N}(nT_{S})}{2\pi}$$

(2.27)

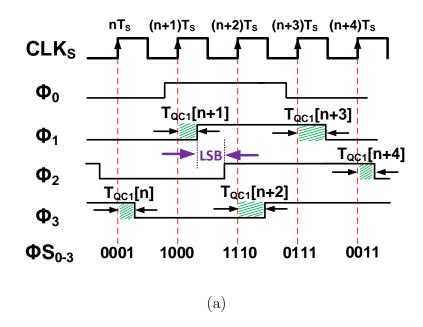

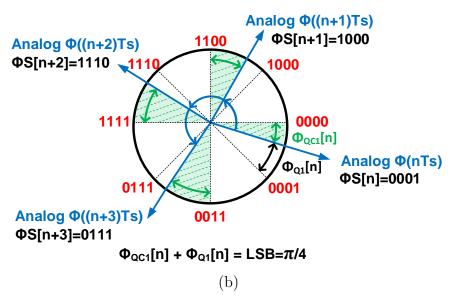

and  $f_{fr1}$  is completely removed at the first stage output. Note that, based on (2.13),  $G_{1P}(t)$  and  $G_{1N}(t)$  are the shaped input signal minus the shaped quantization noise. Fig. 2.7 shows an example of  $f_{fr1}$  cancelation in the first stage of the proposed pseudo-differential structure. In this example, a pair of 4 bit counters (16 level quantizer) is used. Also,  $f_{fr1}$  is assumed to be around  $3.5 \times f_S$ . In the

real implementation, counters have limited output range and the counter output changes direction every time it reaches its highest and lowest counts. To account for this issue, the subtraction of Counter<sub>1P</sub> and Counter<sub>1N</sub> outputs is done by XORing the sampled counter outputs shown as  $y_1[n]$  in Fig. 2.7. Since  $f_{fr1}$  is canceled at the output, it can be chosen arbitrarily.

In Fig. 2.7,  $y_1[n]$  is the output code which corresponds to the DAC selection pattern. The middle point of  $y_1[n]$ , which is the DAC middle point, rotates at approximately  $f_{fr1}/16$  in this example. This results in an inherent clock averaging (CLA) pattern in the proposed ADC [14]. A proper choice of  $f_{fr1}$  pushes the harmonics caused by DAC mismatch out of band. Thus, there is no need for an explicit dynamic element matching (DEM) technique [14].

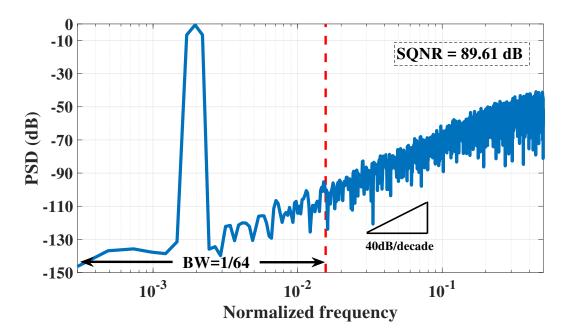

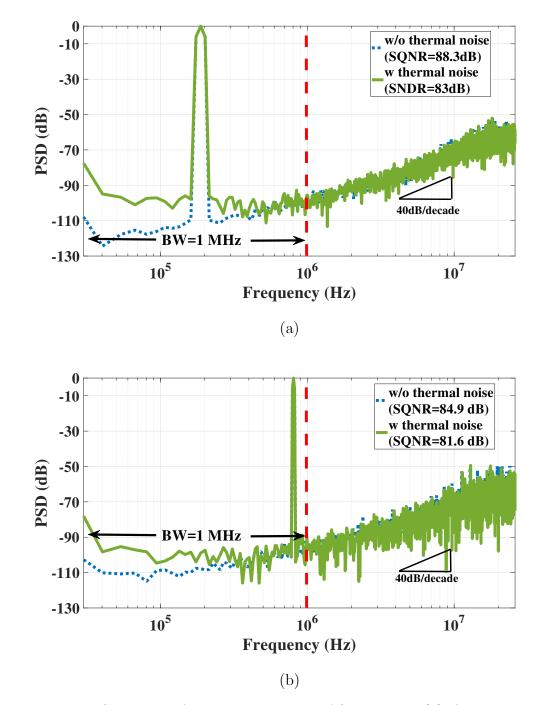

In the proposed pseudo-differential structure, since  $VCO_{1P}$  and  $VCO_{1N}$  are identical, in the absence of mismatches, PVT variations affect the free running frequency of both VCOs in the same way. Therefore, the performance does not change. Also, due to the pseudo-differential structure, even order harmonics are canceled at the output. The behavioral model of the pseudo-differential architecture is simulated in Simulink/MATLAB. Fig. 2.8 shows the PSD of the pseudo-differential structure using the parameters in Table 2.1. Fig. 2.8 shows that the desired second-order noise shaping is achieved.

Table 2.1: Specifications of the proposed 1-1 MASH

| Spec.            | Value           | Spec.             | Value |

|------------------|-----------------|-------------------|-------|

| $f_{fr1}(Hz)$    | $16 \times f_S$ | N                 | 5     |

| $K_{VCO1}(Hz/V)$ | $30 \times f_S$ | OSR               | 32    |

| $K_{VCO2}(Hz/V)$ | $16 \times f_S$ | Input amp. (dBFS) | -0.6  |

| $V_{DD}(V)$      | 1               |                   |       |

Figure 2.8: PSD of the proposed pseudo-differential 1-1 MASH.

In the next section, the performance of the proposed ADC is examined for different design parameters.

#### 2.4 Performance Analysis with Design Parameters

In MASH ADC architectures an interstage gain can be used between different stages to enhance the SQNR. In the proposed scheme, there is an inherent interstage gain between the first stage and the second stage which can be used to improve the output SQNR. In this section, this technique is discussed and verified through comprehensive simulations.

### 2.4.1 SQNR enhancement

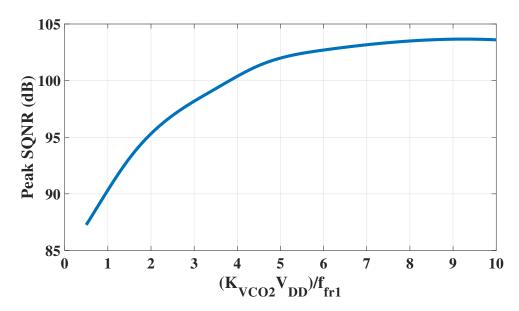

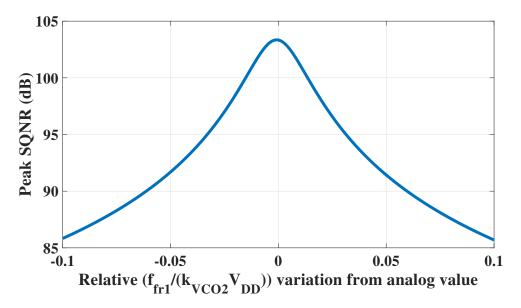

As shown in (2.23), the last term of the equation affects the SQNR. In the linear model shown in Fig. 2.5,  $(V_{DD}K_{VCO2})/f_{fr1}$  acts as an inter-stage gain, which can be used to improve SQNR for the two stage MASH structure. Fig. 2.9 shows the peak SQNR versus  $(V_{DD}K_{VCO2})/f_{fr1}$ . In this simulation,  $f_{fr1}$  and  $V_{DD}$  are kept constant and  $K_{VCO2}$  has been swept. The ADC design parameters used in this simulation are shown in Table 2.2.

As can be inferred from Fig. 2.9, the peak SQNR saturates for high  $K_{VCO2}$  values. This limitation on the maximum achievable SQNR stems from an earlier approximation made from (2.12) to (2.14). This issue is investigated in more detail in the following section.

Table 2.2: Specifications of the proposed 1-1 MASH

| Spec             | Value                  | Spec              | Value |

|------------------|------------------------|-------------------|-------|

| $f_{fr1}(Hz)$    | $16 \times f_S$        | N                 | 5     |

| $K_{VCO1}(Hz/V)$ | $(2^N - 2) \times f_S$ | OSR               | 32    |

| $f_{in}(Hz/V)$   | BW                     | Input amp. (dBFS) | -0.6  |

| $V_{DD}(V)$      | 1                      |                   |       |

Figure 2.9: Peak SQNR vs.  $(V_{DD}K_{VCO2}/f_{fr1})$ .

# 2.4.2 Estimation of phase domain quantization noise of the first stage in time domain

The quantization noise of the first stage is in the phase domain (2.12). As shown in (2.14), if the frequency variation of VCO<sub>1</sub> ( $K_{VCO1}G_1(t)$ ) is small compared to  $f_{fr1}$ , the quantization noise can be extracted in the time domain. Because of this approximation, there is always some  $\phi_{q1}$  leakage to the output. Assuming  $\alpha\phi_{q1}$  is the error due to this approximation of  $\phi_{q1}$  at the second stage input,  $\alpha\phi_{q1}NCF_2$  is the error at the final output. Considering  $\alpha NCF_2 = L(z)$ , (2.20) can be modified to:

$$Y(z) = z^{-2} (K_{VCO1}T_s) S(z)$$

$$+ (1 - z^{-1})^2 \frac{f_{fr1}}{2\pi K_{VCO2}V_{DD}} \phi_{q2}(z)$$

$$+ L(z) \phi_{q1}(z)$$

(2.28)

Since  $NCF_2$  has a first-order noise shaping transfer function, the error in  $\phi_{q1}$  extraction gets one order of noise shaping at the final output.

Based on (2.28), if  $(V_{DD}K_{VCO2})/f_{fr1}$  is high enough, the peak SQNR is limited to  $L(z)\phi_{q1}(z)$  as shown in Fig. 2.9. To investigate the effect of  $L(z)\phi_{q1}(z)$  on SQNR,  $(V_{DD}K_{VCO2})/f_{fr1}$  is assumed to be high enough so that the effect of  $\phi_{q2}$  can be neglected on the peak SQNR in the following analysis. Hereafter, the peak SQNR limited to  $L(z)\phi_{q1}(z)$  is called the maximum achievable SQNR.

L(z) is a function of the relative VCO<sub>1</sub> frequency variation with respect to  $f_{fr1}$ . In order to reduce L(z), VCO<sub>1</sub> frequency variation with respect to  $f_{fr1}$  has to be reduced. From (2.12) and (2.13) it can be seen that the frequency of VCO<sub>1</sub> is:

$$freq_{VCO1}(z) = K_{VCO1}G_1(z) + f_{fr1}$$

$$= (1 - z^{-1}) K_{VCO1}S(z)$$

$$+ (1 - z^{-1}) \frac{f_s \phi_{q1}(z)}{2\pi} + f_{fr1}$$

(2.29)

Equation (2.29) shows that the  $freq_{VCO1}$  is a function of both the shaped input signal and the shaped quantization noise. Maximum  $freq_{VCO1}$  variation happens when the first two terms of (2.29) have their maximum variation. The maximum amplitude of the first stage output  $(y_1[n])$  is  $2^{N-1}$ . Therefore, based on the transfer function in (2.11), the maximum value of  $K_{VCO1}S(z)$  is approximately  $2^{N-1}f_S$ . The first term of (2.29) is a difference of two consecutive samples of the input signal multiplied by  $K_{VCO1}$ . Therefore, the maximum variation of the first term of (2.29) is:

$$\Delta_{\max} \left( \left( 1 - z^{-1} \right) K_{VCO1} S(z) \right)$$

$$= Max \left( \left( 1 - z^{-1} \right) K_{VCO1} S(z) \right)$$

$$- Min \left( \left( 1 - z^{-1} \right) K_{VCO1} S(z) \right)$$

$$= \left| \left( 1 - e^{-\frac{j\pi}{OSR}} \right) \right| 2^{N} f_{S}$$

$$(2.30)$$

$\phi_{q1}$  has a value between 0 to  $2\pi$ . As a result, the maximum difference of two consecutive samples of  $\phi_{q1}$  is  $2\pi$ . Thus, the maximum variation of the second term

in (2.29) is:

$$\Delta_{\text{max}}\left(\left(1-z^{-1}\right)\frac{f_s\phi_{q1}(z)}{2\pi}\right) = f_S$$

(2.31)

Based on (2.30) and (2.31), the maximum  $freq_{VCO1}$  variation normalized to  $f_{fr1}$  is:

$$\frac{\Delta_{\max}\left(freq_{VCO1}\right)}{f_{fr1}} = \left(\left|\left(1 - e^{-\frac{j\pi}{OSR}}\right)\right| 2^N + 1\right) \frac{f_S}{f_{fr1}}$$

(2.32)

In the following sub-sections, the effects of N, OSR, and  $f_{fr1}$  on the maximum achievable SQNR are investigated through behavioral model simulations. The design parameters of the ADC used in these simulations are shown in Table 2.2. In these simulations the value of  $K_{VCO2}$  is chosen high enough to ensure that the maximum SQNR is achieved for the parameters used.

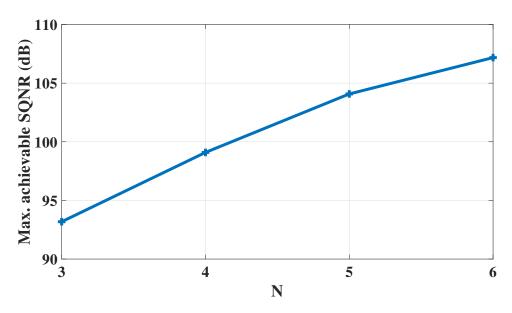

## 2.4.2.1 Effect of N

The first stage is a first order delta-sigma modulator with an N-bit quantizer. The maximum peak-to-peak swing of the ADC output is  $2^N$ . Therefore, increasing N, results in a higher maximum signal swing at the output. It is expected that the maximum achievable SQNR increases by 6 dB with each increment of N. On the other hand, (2.32) shows that increasing N results in more  $freq_{VCO1}$  variation with respect to  $f_{fr1}$ . Therefore, increasing N results in more  $\phi_{q1}$  leakage (L(z)) to

the output. Hence, less than 6 dB improvement in maximum SQNR is achieved. The maximum achievable SQNR is simulated for the proposed scheme for different values of N in Fig. 2.10. As can be seen, since  $\phi_{q1}$  leakage increases with increasing N, the maximum achievable SQNR improvement is less than 6 dB for each increment of N.

Figure 2.10: Maximum achievable SQNR for different values of N.

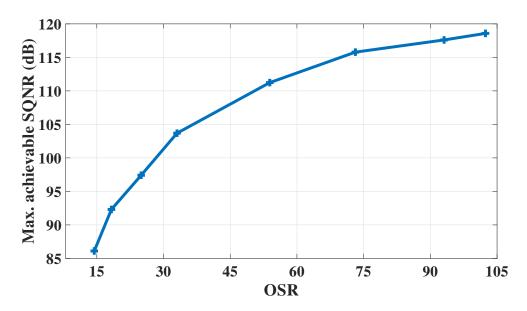

## 2.4.2.2 Effect of OSR

By increasing OSR, the difference of the input signal between two consecutive samples becomes smaller. Therefore, the input voltage variation for VCO<sub>1</sub> due to the ADC input voltage is less. For a fixed value of N, this results in a smaller  $freq_{VCO1}$  variation (Eq. (2.32)). As a result, a more accurate relation between

the time domain and the phase domain quantization noise is achieved. Therefore, the maximum achievable SQNR increases by increasing OSR. The maximum achievable SQNR is simulated for the proposed scheme for different values of OSR in Fig. 2.11. In this simulation  $f_{in}$  is kept at the edge of the BW. As can be seen in Fig. 2.11, the rate of maximum achievable SQNR improvement is smaller for higher values of OSR. This is due to the fact that the maximum  $freq_{VCO1}$  variation relative to  $f_{fr1}$  in (2.32) is due to the signal variation (the first term) and the quantization noise variation (the second term). Since the  $freq_{VCO1}$  variation due to the quantization noise is not a function of OSR, for higher values of OSR, the second term in (2.32) becomes comparable to the first term. This limits the maximum achievable SQNR.

Figure 2.11: Maximum achievable SQNR for different values of OSR.

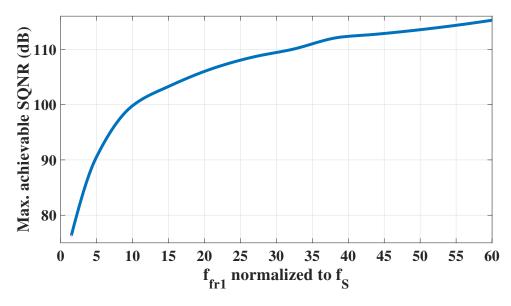

# 2.4.2.3 Effect of $f_{fr1}$

As discussed in Section 2.3.1,  $f_{fr1}$  is removed at the pseudo-differential structure output and, therefore, its value can be chosen arbitrarily. Equation (2.12) shows that increasing  $f_{fr1}$  makes  $K_{VCO1}G_1(t)$  negligible compared to  $f_{fr1}$ . Therefore, increasing  $f_{fr1}$  makes the relation between phase and time domain information (as shown in (2.14)) more linear. The maximum achievable SQNR is simulated for the proposed scheme for different values of  $f_{fr1}$  in Fig. 2.12. Although the maximum achievable SQNR improves for higher  $f_{fr1}$ , as (2.23) suggests a higher value of  $K_{VCO2}$  is required to achieve a high SQNR. On the other hand, a higher  $f_{fr1}$  requires a faster  $VCO_1$  and  $Counter_1$  in the design. This increases the power consumption and the circuit implementation complexity.

Generally, for higher speed applications, the required SQNR of the ADCs is less than lower speed applications. Therefore, depending on the required SQNR,  $f_{fr}/f_S$  can be chosen to reasonably meet the design requirements. Based on Fig. 2.12, even if  $f_{fr}/f_S$  is in the range of 2 to 4, a SQNR of more than 80dB is still achievable using the parameters of Table 2.2.

Figure 2.12: Maximum achievable SQNR for different values of  $f_{fr1}$ .

## 2.5 Effect of Non-Idealities

In a real implementation, non-idealities degrade the performance of the ADC. In this section, some of the non-ideality factors and related solutions, listed in Table 2.3, are described. The effect of each non-ideality factor on the performance of the proposed scheme is explained and Simulink/MATLAB simulation results are presented. The ADC design parameters are the same as in Table 2.2.

Table 2.3: Non-idealities and related solutions

| Non-ideality                                | Solution                                                                |

|---------------------------------------------|-------------------------------------------------------------------------|

| VCO non-linearity                           | $VCO_1$ is in a feedback loop and a two level PWM signal drives $VCO_2$ |

| Mismatch between analog and digital filters | Calibration                                                             |

| VCO mismatch                                | Low sensitivity                                                         |

| Missing narrow pulses in Q extraction path  | Pulse width extension                                                   |

| Propagation delay in QPD block              | Low sensitivity                                                         |

| Setup/hold times of the quantizer           | Modified quantizer                                                      |

| Rise/fall times of the QPD                  | Low sensitivity                                                         |

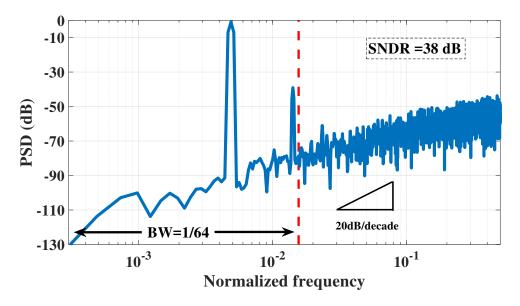

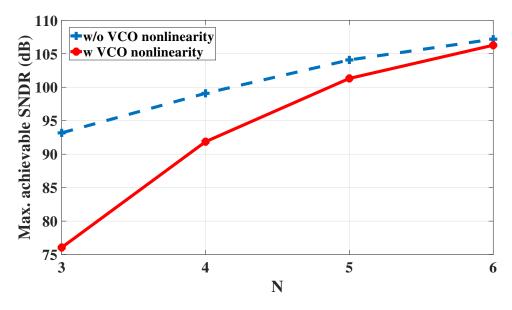

## 2.5.1 VCO non-linearity

The VCO non-linearity is the major bottleneck in designing VCO-based ADCs. To mitigate this issue, the first stage VCO is used as a phase integrator. Therefore, the signal variation at the input of the VCO is small. As a result, the non-linearity of VCO<sub>1</sub> is suppressed significantly [15]. The input of the second stage VCO is a two level PWM signal. Therefore, VCO<sub>2</sub> operates linearly as well [12].

In order to investigate the effect of the non-linearity on the proposed ADC, a non-linear V-to-F tuning characteristic (extracted from VCO transistor level simulations), is used for all the VCOs in the behavioral model. Fig. 2.13 shows the FFT of the output of a pseudo-differential stand-alone open loop VCO-based ADC, using the same V-to-F tuning characteristic. The signal to quantization noise and distortion ratio (SNDR) is limited to 38 dB in the standalone VCO-based topology.

Figure 2.13: PSD of the output of a pseudo-differential open loop VCO-based ADC.

As shown in (2.13), in the proposed architecture, the input signal of VCO<sub>1</sub>  $(G_1(t))$  contains a shaped input signal (the first term) and the shaped quantization noise (the second term). Assuming the OSR is high enough, the first term is small and the non-linearity introduced by the input signal is greatly suppressed. On the other hand, the magnitude of the shaped quantization noise can be large such that it limits the SNDR. Due to the non-linear characteristic of the VCO, high frequency components of the shaped quantization noise get modulated to the in-band frequency range and degrade the performance. Fig. 2.14 shows the maximum achievable SNDR vs. N for two scenarios, with and without the VCO non-linearity. As can be observed in this figure, the degradation due to the VCO

non-linearity reduces significantly by increasing N.

Figure 2.14: Maximum achievable SNDR of the proposed ADC vs. N, with linear and non-linear VCO.

## 2.5.2 Mismatch between analog and digital filters

Mismatch between the analog and digital filters is a common issue for MASH structures [1]. This problem leads to quantization noise leakage to the output. Equation (2.19) shows  $NCF_2$  is a function of  $f_{fr1}$  and  $K_{VCO2}V_{DD}$ . Fig. 2.15 shows the output SQNR variation due to mismatch between  $f_{fr1}/(K_{VCO2}V_{DD})$  in  $NCF_2$  and its ideal analog value. As can be seen, in the presence of  $\pm 10\%$  mismatch between the analog and digital filters, a SQNR of more than 85 dB is achievable, using the parameters of Table 2.2.

Figure 2.15: SQNR vs.  $f_{fr1}/(K_{VCO2}V_{DD})$  variation from its nominal value.

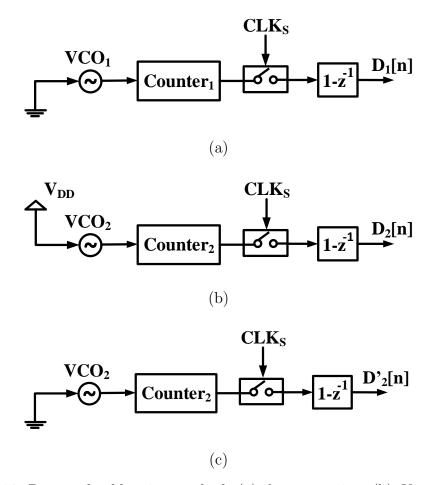

In order to reduce the analog and digital filtering mismatch, a simple calibration method can be used. The ratio of  $f_{fr1}/(K_{VCO2}V_{DD})$  needs to be calculated precisely in the digital domain to match the analog value. In the beginning of the calibration, the first stage loop is broken and VCO<sub>1</sub> is connected to the AC ground (DC common-mode voltage). As shown in Fig. 2.16(a), a digital differentiator is used after Counter<sub>1</sub> to extract the frequency information of VCO<sub>1</sub>.  $D_1(z)$  is as follows:

$$D_1(z) = f_{fr1}T_S + (1 - z^{-1})\frac{\phi_{q1}(z)}{2\pi}$$

(2.33)

In (2.33) by averaging multiple samples of  $D_1[n]$ , the shaped quantization noise

is reduced and  $f_{fr1}T_S$  can be extracted.

Figure 2.16: Proposed calibration method. (a)  $f_{fr1}$  extraction, (b)  $K_{VCO2}$  extraction - phase 1, (c)  $K_{VCO2}$  extraction - phase 2.

Next, extracting  $K_{VCO2}V_{DD}T_S$  takes place in two different phases. First, VCO<sub>2</sub> is connected to  $V_{DD}$  as shown in Fig. 2.16(b) and the frequency information is

extracted as below:

$$D_{2}(z) = K_{VCO2}V_{DD}T_{S} + f_{fr2}T_{S} + (1 - z^{-1})\frac{\phi_{q2}(z)}{2\pi}$$

(2.34)

In the second phase,  $VCO_2$  is connected to the ground as shown in Fig. 2.16(c). Equation (2.35) shows its frequency information.

$$D_2'(z) = f_{fr2}T_S + (1 - z^{-1})\frac{\phi_{q2}(z)}{2\pi}$$

(2.35)

By averaging multiple samples of  $D_2[n]$  and  $D_2[n]$  as before and subtracting the averaged values,  $K_{VCO2}V_{DD}T_S$  can be extracted. By knowing  $f_{fr1}T_S$  and  $K_{VCO2}V_{DD}T_S$  values,  $NCF_2$  can be accurately calibrated in the digital domain and the SQNR reduction can be corrected.

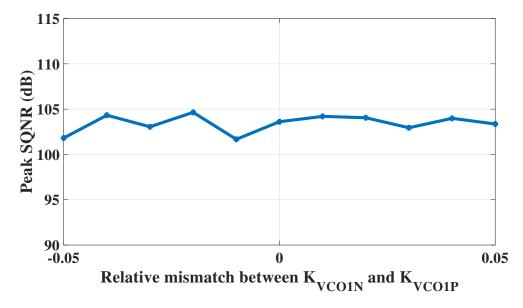

#### 2.5.3 VCO mismatch

There are two types of mismatch with respect to the VCOs. The first type is the mismatch among different delay cells of a VCO. The second type is the mismatch between the two VCOs. Since in the proposed architecture only one delay element drives the counter, mismatch between delay cells does not degrade the performance. Although this mismatch can change  $K_{VCO}$  and  $f_{fr}$  of each VCO, this can be modeled as a mismatch between the different VCOs.

In the proposed pseudo-differential structure, the design specifications of the

first stage VCO and the second stage VCO dont need to be identical. Therefore, they can be designed independently.

The mismatch between  $f_{fr1P}$  and  $f_{fr1N}$  causes offset at the first stage output, which results in a dynamic range (DR) reduction.

Since, the input signal swing at the VCO<sub>1</sub>s' inputs is small, the mismatch between  $K_{VCO1P}$  and  $K_{VCO1N}$  does not degrade the output SQNR. This is simulated in Fig. 2.17.

Figure 2.17: Effect of VCO mismatch on the pseudo-differential structure.

The second stage is a pair of open loop VCO quantizers operating in the frequency domain. Mismatch between  $f_{fr2P}$  and  $f_{fr2N}$  results in an offset in the second stage output. This offset can be avoided by measuring  $f_{fr2P}$  and  $f_{fr2N}$  in the calibration phase, similar to Fig. 2.16(b). Also,  $K_{VCO2P}$  and  $K_{VCO2N}$  can be

measured in the calibration phase and therefore their mismatch can be compensated in digital filters.

Figure 2.18: Pulse width extension in the QPD block.

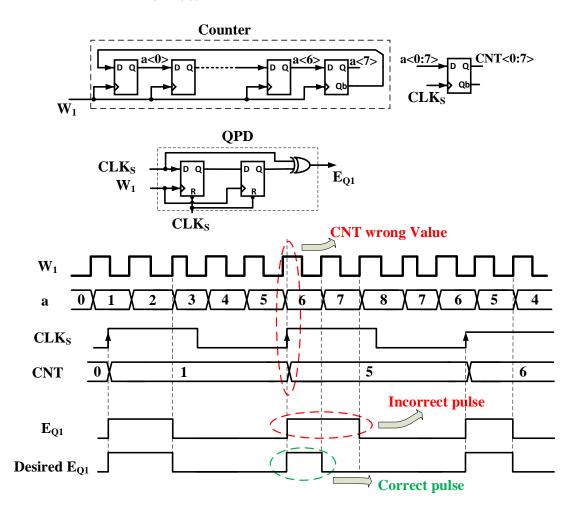

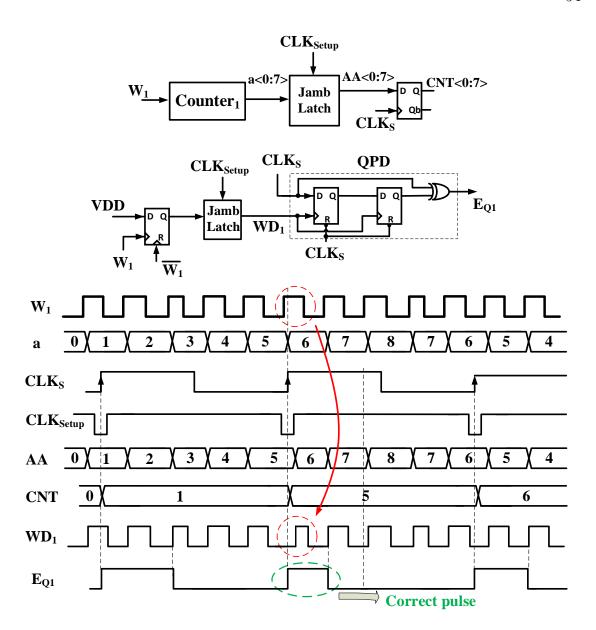

# 2.5.4 Effect of narrow pulses in Q extraction path

As shown in (2.14) the pulse width of  $E_{Q1}(t)$  (shown in Fig. 2.3) is a linear function of the phase quantization noise of the first stage. This pulse width can be very narrow and if it is smaller than the rise time of the QPD block, the pulse can