# PRINCIPLES OF LOGIC DESIGN

W. Richards Adrion

1

James H. Herzog

**Robert A. Short**

PRINCIPLES

OF

LOGIC DESIGN

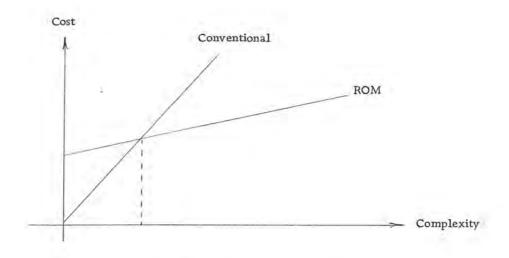

W. Richards Adrion James H. Herzog Robert A. Short

Oregon State University Corvallis, Oregon

1

H

Copyright © 1974 by

W. Richards Adrion James H. Herzog Robert A. Short

1.5

Ħ

1

# TABLE OF CONTENTS

Γ

ſ

I

l

1

U

Ħ

|    |                                       |                                                                                      | Page |

|----|---------------------------------------|--------------------------------------------------------------------------------------|------|

| 1. | Logi                                  | c Design and Digital Machines                                                        | 1.1  |

|    | 1.1                                   | The Basic Digital Design Problem                                                     | 1.2  |

|    | 1.2                                   | Number Systems and Binary Encoding                                                   | 1.8  |

|    | 1.3                                   | Design Specifications                                                                | 1.24 |

|    | 1.4                                   | The Problems of Existence and Minimization                                           | 1.48 |

|    | 1.5                                   | Notes - References - Problems                                                        | 1.50 |

| 2. | Com                                   | 2 1                                                                                  |      |

|    | 2.1                                   | Logical Connectives and Electronic Gates                                             | 2.1a |

|    | 2.2                                   | 그는 것 같은 영상 수가 있다. 방법 이 것 방법에서 가장 가슴에서 가장 않는 것 같은 것 같이 봐. 가지 않는 것 같이 많이 가지 않는 것 같이 봐. | 2.2  |

|    | 2.3                                   | Switching Functions and Their Representations                                        | 2.21 |

|    | 2.4                                   | Alternative Representations                                                          | 2.30 |

|    | 2.5                                   | Notes - References - Problems                                                        | 2.38 |

| 3. | Elen                                  | nents of Logic Design                                                                | 3.1  |

|    | 3.1                                   | Branch Networks                                                                      | 3.2  |

|    | 3.2                                   | Gate Networks                                                                        | 3,13 |

|    | 3.3                                   | Multiple Output Networks                                                             | 3.49 |

|    | 3.4                                   | Iterative Combinational Networks                                                     | 3.58 |

|    | 3.5                                   | Notes - References - Problems                                                        | 3.66 |

| 4. | Intro                                 | oduction to Sequential Design                                                        | 4.1  |

|    | 4.1                                   | Sequential Logic Circuits                                                            | 4.1  |

|    | 4.2                                   | The State Diagram                                                                    | 4.4  |

|    | 4.3                                   | The Latch                                                                            | 4.7  |

|    | 4.4                                   | Clocked Flip Flops                                                                   | 4,11 |

|    | 4.5                                   | Binary Counters                                                                      | 4.14 |

|    | 4.6                                   | Shift Registers                                                                      | 4.16 |

|    | 4.7                                   | The Arithmetic Register                                                              | 4.20 |

|    | 4.8                                   | Notes - References - Problems                                                        | 4.23 |

| 5. | Design of Clocked Sequential Circuits |                                                                                      | 5.1  |

|    | 5.1                                   | Clocked Sequential Logic                                                             | 5.1  |

|    | 5.2                                   | The Design Procedure                                                                 | 5.2  |

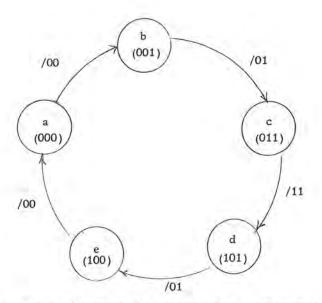

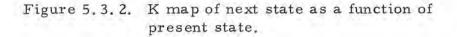

|    | 5.3                                   | Design of Sequence Generators:/Counters                                              | 5.5  |

|    | 5.4                                   | Design of Input Sequence Detectors                                                   | 5.10 |

|    | 5.5                                   | Minimization Revisted                                                                | 5.16 |

|    | 5,6                                   | Sequential Design Using Read Only Memory                                             | 5.21 |

|    | 5.7                                   | Notes - References - Problems                                                        | 5.23 |

|    |                                       |                                                                                      |      |

# TABLE OF CONTENTS (continued)

B

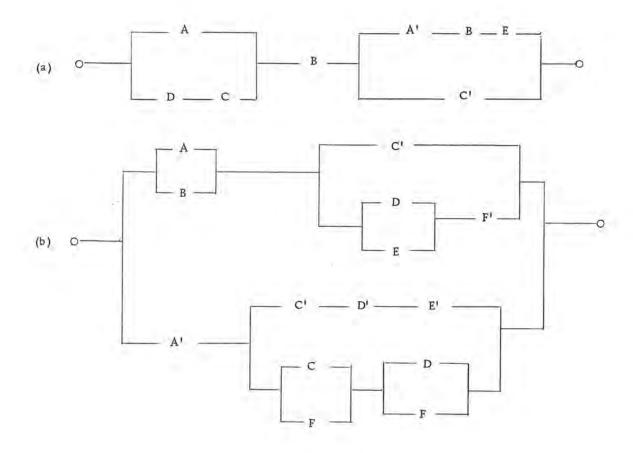

| 6. | Desi | ign of Asynchronous Sequential Circuits    | 6.1  |

|----|------|--------------------------------------------|------|

|    | 6.1  | Introduction                               | 6.1  |

|    | 6.2  | Analysis of Relay Sequential Circuits      | 6.2  |

|    | 6.3  | Design of Asynchronous Sequential Circuits | 6.9  |

|    | 6.4  | Assignment of State Variables              | 6.18 |

|    | 6.5  | Notes - References - Problems              | 6.21 |

| 7. | Faul | t Tolerant Design                          | 7,1  |

|    | 7.1  | Hardware Redundancy                        | 7.3  |

|    | 7.2  | Coding Redundancy                          | 7.18 |

|    | 7.3  | Fault Diagnosis                            | 7.28 |

|    | 7.4  | Comments - Problems - References           | 7.35 |

| 8. | The  | Impact of New Technology on Logic Design   | 8.1  |

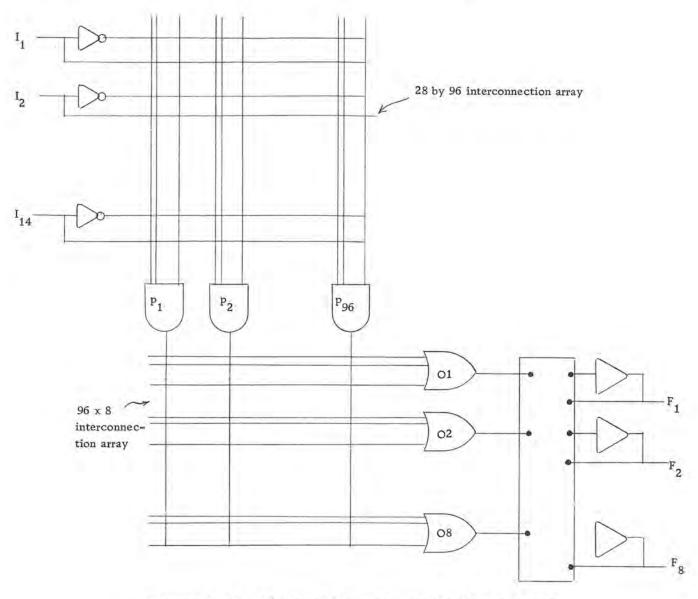

|    | 8.1  | Read Only Memory Design                    | 8.2  |

|    | 8.2  | Cellular Arrays                            | 8.8  |

|    | 8.3  | Programmable Logic Arrays                  | 8.13 |

|    | 8.4  | Universal Logic                            | 8.15 |

|    | 8.5  | Notes - Problems - References              | 8.21 |

#### 1 Logic Design and Digital Machines

This study involves logic design and switching theory, in particular their practical application to the logic design and understanding of digital machines. Digital machines, of course, play an extremely important role in that large class of machines known as digital computers. But they also play an important role in many other kinds of practical devices important in the design of communications systems, digital control systems, counters, registers, digital meters, and so on.

The basic content of switching theory is very simple. It embodies that body of machines and machine behavior that can be realized with "switches", things that are either "on" or "off", and nothing, really, could be much simpler than that. Of course the world is really comprised of very many complex structures which are really composed of exceedingly simple lesser structures, so that we really shouldn't be too surprised that even though the elements of switching theory are quite simple, their consequences are not necessarily so.

The goals of our study are several, and include at least the following: 1) to develop some understanding and capability in using the techniques, design procedures, and models that have been developed for understanding and designing digital networks;

2) to explore in some modest detail the kinds of questions with which logic designers and practitioners concern themselves;

3) to develop an appreciation for the tremendous variation possible in digital design requirements and specifications, i.e., for the complexity of the 'finite' digital problem, and hence an understanding of the need for systematic design techniques by which to attack such problems;

4) to gain some practice with the fundamental tools and techniques of logic design so that the reader can adapt the techniques to the "new" problem presented by his own particular design constraints; and

5) to provide an introduction to the literature so that the discerning student can, in the future, dip into the ever growing literature in the field, and find it to some degree comprehensible, and advantageous to use.

#### 1.1 The Basic Digital Design Problem

As an abstract statement, logic design, representing the practical applications of switching theory, is that formal discipline concerned with the analysis and synthesis techniques that are appropriate for the design of digital networks. Of course that is almost like saying that "Computer Science is that discipline involved with the study of computers". It's very true, but not at all illuminating. So let's be a little more explicit -- at least insofar as agreeing on what we mean by a digital network.

A <u>digital network</u> is an assemblage of digital elements. At least that divides our problem. And we can quickly agree that by <u>assemblage</u> we mean any arbitrary interconnection of digital elements. So that leaves everything really dependent on our agreement on what digital element is. Here we have one of three paths that we can follow. The first two are valueless, although frequently used. The first calls on circularity which is the basis for most dictionary definitions:

a digital element is the kind of thing of which digital networks are composed.

The second calls on authoritarianism:

everybody knows what a digital element is, it is a thing that assumes one of two possible output states as a function of its inputs, including possibly its own output

and that usually ends the whole discussion right there. Actually everything is contained in that one, although it's a little obtuse and hard to get any essential features out of it. Instead we'll take the third alternative and simply define what we mean by a digital element.

- c) a digital element is one of two kinds of things: it is either

- i) a thing which is capable of exhibiting one of two outputs, and it does so as an instantaneous, deterministic function of its inputs, or it is

- a thing which is capable of exhibiting one of two outputs, and it does so strictly as a function of what its input was an agreed (synchronous) moment ago.

This last definition we shall accept and use as our operative definition, for it divides switching theory into the two halves with which we shall be concerned:

combinational switching theory versus sequential switching theory. For the first kind of element indicated above is assumed to develop its output strictly as a function of its present inputs. Time is not normally considered to play a role in its operation. This is, of course, a simplifying assumption, but is appropriate for an adequately large range of devices. A basic assumption implicit in the above is that the number of possible inputs is finite, and that the number of values of each is likewise finite. The specification of a particular device, then, reduces to a determination of which <u>combination</u> of inputs produces a particular output, hence the term <u>combinational</u> networks.

The second kind of element inferred above introduces the final full range of complexity that enables us to describe and characterize everything of which digital machines are capable. For something that simply reproduces its own input an agreed time later introduces the notion of controlled time into the picture. It doesn't take a great leap of imagination to presume that it might be useful in some instances to take advantage of that time lapse to return the element's output to its own input in some way, so that its output can indeed be a function of its own previous outputs, i.e., of the past history of the element. This basic element is termed a simple <u>delay element</u>. It is the epitome of "memory" in machines and brings us to the larger class of networks known as <u>sequential networks</u> or sequential machines.

At first it might seem that we have made a rather severe set of restrictions in defining our baisc memory element as a simple delay. It can be shown, however, that the simple delay generalizes so that it can model any other kind of memory element, hence that the restriction in no way limits that kind of behavior we can observe in our resulting machines. And we shall quickly develop transformation procedures for moving from any of the machine types to any other.

Another assumption that we shall generally make is one that is satisfying from an engineering point of view, and furthermore is one that essentially delimits switching theory from the broader class of activity embraced by the term <u>automata</u> <u>theory</u>. This assumption refers to the finiteness that we shall presume regarding everything to be realized physically. Not only shall we usually assume a finite number of digital elements in any network, but also that the number of inputs is finite as well. Because of this finiteness of the number of digital elements we can

conclude that the number of states of any machine is also finite, as well as the number of different outputs that are possible. Actually we have really said the same thing twice there because the <u>states</u> of a machine will simply refer to the different number of possible combinations on those outputs of the memory elements which are used internally in the machine itself. We shall make all these terms more precise as we need them. We note at present, however, that the usefulness of this concept of the state of a machine leads directly to the use of the term <u>finite state</u> machines to describe the kinds of digital machines with which we are concerned.

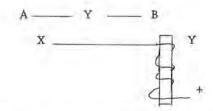

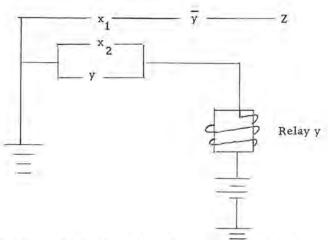

Examples of digital elements are many, and we shall point to only a few to make firm the kinds of things we are talking about. A familiar example is the relay coil and contact which schematically can be shown as in Figure 1.1.1.

Figure 1.1.1. Simple relay machine

wherein some variable x (a two-valued variable; either ground or not-ground) determines whether the relay coil Y is energized or not. Of course relays have contacts, and this one is a "make" contact (i. e., it closes when the coil is energized) labeled y. Clearly we can refer also to a useful transmission function that characterizes the connectivity between terminals A and B of the contact network. It is either shorted or open as a function of the variable x. We note that this transmission function is also two-valued. (We also note in passing that this sort of schematic diagram is called a "detached schematic", i. e., the contact related to a certain coil need not be drawn in proximity to the coil itself. This obvious convenience makes the schematics of some quite complex contact networks easily drawn -- but an historically interesting note is that it wasn't until the mid-fifties that this obvious graphical simplification was taken advantage of. Prior to this time the insistence that each contact had to be shown next to its coil led to horrendously complex diagrams that were exceedingly difficult to analyze.)

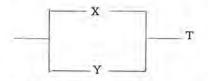

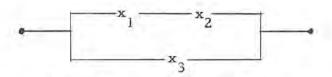

It is then easy to indicate assemblages of such contacts such as in Figure 1.1.2 which defines a transmission function T which is two-valued (being shorted if

1,4

Figure 1.1.2. A contact network.

and only if both coils X and Y are energized), or like that in Figure 1.1.3 for

Figure 1.1.3. Altenative contact network.

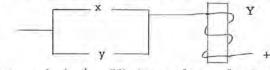

which the function T is shorted if and only if either of the coils X or Y is energized. Clearly such transmission functions can become almost arbitrarily complex. For now we note only the possibility that the energization of a particular coil might be a function of itself. A simple example is shown in Figure 1.1.4 in which X is

Figure 1.1.4. History-dependent relay network.

energized if either x or y is shorted, and of course once y is shorted then the coil is energized for all future time regardless of subsequent changes in x. Thus this network does react as a function of its own history, and verifies that a network need not be simply a (combinatorial) function of its own inputs. Thus this network <u>remembers</u> and this facility is only possible when feedback paths exist within the network.

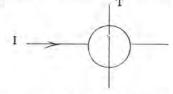

Another example of a digital element is the cryotron of Figure 1.1.5 which

Figure 1.1.5. Cryotron element.

is a (super cooled) device wherein the transmission function T is a short circuit whenever the current I is nonzero. Thus the cryotron is essentially the same "kind" of element as a relay contact; both are examples of a broader class of things referred to as <u>branch elements</u>, and assemblages of such are referred to

as <u>branch networks</u>. The essential feature is that the two-valued function involved is basically a transmission function that describes the condition of connectivity throughout the network.

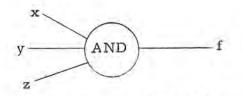

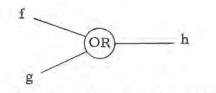

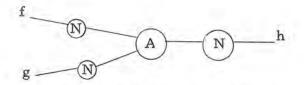

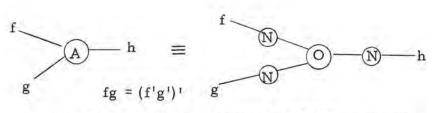

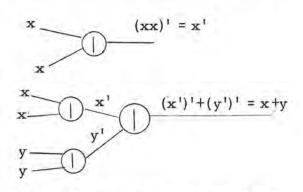

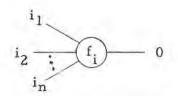

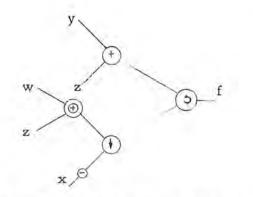

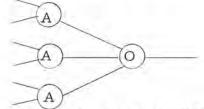

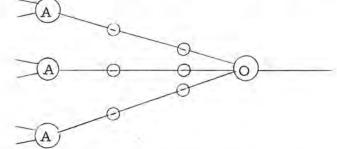

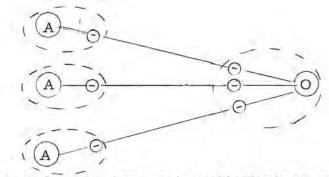

This is in opposition to the familiar <u>gate networks</u> exemplified by electronic <u>gate elements</u>, realized by semiconductors or tubes usually, and symbolized by such diagrams as in Figure 1.1.6

Figure 1.1.6. Gate element.

in which the "output" function f is at a high (or low) voltage if and only if inputs x and y and z are all at a high (or low) voltage. Of course these (as well as many other different logic gate types) can be interconnected in a great many ways so that functions of functions can be built up to any desired complexity.

We could mention any number of other kinds of digital elements such as magnetic cores, fluidic valves, mechanical linkages, mechanical switches, storage spots on electrostatic devices, etc., etc., but this would not further serve our present purposes.

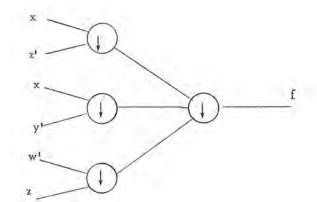

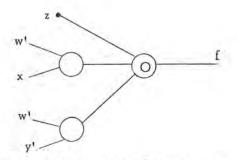

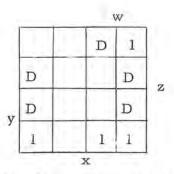

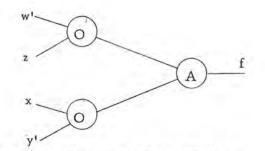

The point is, to return to our original train of thought, that a digital network or machine is simply a collection of these things, suitably interconnected, usually with certain variables which we control ("inputs" or "independent variables") and certain variables which we wish to produce ("outputs" or "dependent variables"). The basic engineering problem, then, is the consideration of the <u>transfer network</u> N of Figure 1.1.7

so that we can produce a prescribed set of digital outputs as functions of the digital

input. In these terms, the <u>analysis</u> problem is to determine the  $y_i$ 's when given the  $x_i$ 's and N. The <u>synthesis</u> problem is to determine an appropriate N when given the  $x_i$ 's and the prescribed dependent  $y_i$ 's.

This puts our problems into the desired engineering context, and it remains only for us to fill in the details. This is the function of the sequel.

#### 1.2 Number Systems and Binary Encoding

A salient characteristic of digital networks that are realizable is that they are finite in all respects. It follows that the action of any digital machine is describable as being in one of a set of "conditions" or "states" corresponding to the particular values assumed by each of the elements of which they are composed. With the passage of time the machine perambulates through a set of such states as it responds to its input changes, as well as to autonomous changes in its own internal variables. Since the set of such states must be finite, as must the allowable set of inputs, it follows that a sufficient description of a machine is some sort of listing of one "number" followed by another, each number related one-for-one with the particular state it represents. Now in fact these numbers might be the natural numbers, in which case we are concerned with conventional arithmetic and arithmetic operations. Or they might be simply <u>marks</u> or <u>symbols</u> in another area of discourse, in which case we speak of non-numeric processing.

For openers, then, we shall briefly review some of the salient facts concerning numbers and their representations. We shall also consider assuring facts about the efficiency of bases, and we shall pay a passing glance at the propositional calculus, which is the historical antecedent to the switching algebra.

#### 1.2.1 Positional or Polynomial Encoding

As a starter, then, we point to the familiar fact that a most useful way of representing a number is the one we use all the time--the so-called polynomial representation

$$N = \sum_{i=-m}^{n} d_{i}r^{i}$$

$$= d_{n}r^{n} + d_{n-1}r^{n-1} + \dots + d_{-m}r^{-m}$$

or more commonly written as

$$N = (d_n d_{n-1} \dots d_{-m})_r$$

where we also conventionally omit the r and the parentheses when the r is clear in context. We shall make little more of this subject as some familiarity will be

assumed. The r is of course the <u>base</u>, usually a positive integer greater than 1 (but not necessarily) and the  $d_i$  refer to the <u>digits</u>, and these are also usually the integers such that  $0 \leq d_i < r$ .

Thus, for example,

(123)

represents a number to the base 6, while

(51)10

is evidently a number to the familiar base 10. That they are in fact the same number points to the necessity for conversions from one base to another. Since <u>every</u> number is representable in the form

(N)

for appropriate r, it follows that there must always exist transformations from one base to another. In fact there are pretty algorithms for doing so in an impressive way, but for our purposes straightforward, "brute-force" methods will suffice. Thus

$$(123)_6 = 1(6^2) + 2(6^1) + 3(6^0) = 36 = 12 + 3 = (51)_{10}$$

while the fact that

$$(109)_{10} = 1(2^6) + 1(2^5) + 1(2^3) + 1(2^0) = (1101101)_2$$

can be affirmed simply by subtracting out the largest possible powers of 2 at each step in a successive, systematic sequence of subtractions. Thus

$\begin{array}{r}

109 \\

\underline{64} \\

45 \\

\underline{32} \\

13 \\

\underline{8} \\

5 \\

\underline{4} \\

1

\end{array}$

will develop the result above. The reader will be left to further develop these techniques in ways most compatible to his liking.

Similarly we shall not go into details of the arithmetics involved for the various bases, and a basic familiarity with the techniques involved is assumed.

As with base 10 arithmetic it suffices to agree on addition and multiplication tables. For base 2 these are so simple that we can quickly construct them as an example:

<u>Addition</u> x + y

| X  | у О | 1 | xy | 0   | 1 |

|----|-----|---|----|-----|---|

| 0  | 0   | 1 | 0  | 0   | 0 |

| 1  | 1   | 0 | 1  | 0   | 1 |

| Su | ım  |   | Ca | rry |   |

Multiplication xy

| /x | У | 0 | 1 |  |

|----|---|---|---|--|

| 0  |   | 0 | 0 |  |

| 1  |   | 0 | 1 |  |

|    |   |   |   |  |

e.g.,

| $1 \ 0 \ 1 \ 1 = 11$                            |

|-------------------------------------------------|

| $\underline{x \ 1 \ 0 \ 0 \ 1} = \underline{9}$ |

| 1 0 1 1                                         |

| 1011                                            |

| 1100011 99                                      |

|                                                 |

with subtraction and division being analogously defined. These are straightforward augmentations and will not be detailed here.

Now this is all well and good, but several questions remain. In the first place we have affirmed a multitude of representations for numbers, and we have agreed that "number" in some sense must involve everything that finite state machines can possibly be about. But a moment's reflection will reveal that we really must say much more about such representations for we have described an infinity of representable numbers, whereas the salient fact about finite state machines is that we can only accommodate a finite set of things, hence in any given context can only represent a finite subset of the natural numbers.

Once we recognize the possibility that we can talk only about a finite set of the numbers in any given context, then we are faced with the annoying task of

deciding just which finite set we shall talk about. This involves the notion of selecting the particular encoding of the numbers that we shall use, and we shall verify that indeed a very large number of different possible codes are possible. We shall look briefly at but a few of them, and the salient point we shall try to make is that different codes are used to enhance different features of the machine, but that furthermore each different code requires a re-examination of the computational algorithms involved, and that things are not exactly as simple and straightforward as the tables above would indicate.

First we shall affirm in a simple way that the base 2 is indeed one of the most natural bases for machines, arguing from the standpoint of efficiency.

## 1.2.2 Efficiency of Bases

Although everybody knows that base 2 is most commonly used in machines, it is worth noting that other representations have also been used. Ternary logic machines (base 3) have been widely discussed in the literature, and some machines have been built, principally to capitalize on the error-correcting and detecting features that are possible with such encodings. Base 8 frequently occurs in representations, principally because of the efficiency of packing numbers into base representations that are a power of two.

Decimal machines have also been built, more so in the early days, and the principal motivation here has been the necessity for human communication with the machine.

It must be admitted, however, that most of these nonbinary representations were really binary when looked at at a lower level than the numbers themselves, e.g., the decimal number 9, represented by a binary four-tuple 1001 looks strangely binary, but the point is that the algorithms for handling such "decimal" numbers were decimal algorithms, not binary algorithms. Thus though "9" might be represented by the four-tuple above, "10" might look like 0001 0000, which is strangely "unbinary", and the addition, for example, of two such decimal numbers involves strictly decimal rules for addition. Also there have been other direct representations of the nonbinary bases. Parametrons, for example, turn out to exhibit three states rather than two, and have been the stimulus for much of the ternary logic development. Even base ten elements have been used,

principally in relay machines, however, where the element involved is such as a ten-position stepping switch, or the like. Electronic elements with ten stably discernible states are not easy to come by, however, hence direct representations of nonbinary bases have been few and far between.

Given the fact that radix r will suffice to represent any number, it is nonetheless interesting to ask whether there are any good engineering reasons for preferring one base over another. We have mentioned the physical fact that things like semiconductors, tubes, cores, cryotrons, etc., etc., operate most reliably when switched between one of two states (e.g., "saturated" versus "unsaturated", or "ON" versus "OFF"). These are compelling engineering reasons for naturally favoring the base two in machine realizations. But these are not entirely convincing since a number of discernible levels could be carefully engineered appropriate for some larger radix if we <u>care enough</u>, i.e., if it costs us enough not to do so.

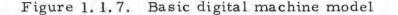

To this end let us complete a modest, brief sort of engineering cost analysis that will suggest the appropriateness of bases for number representations from a little different sort of argument.

Since we are always talking about a finite representation, we shall suppose that the maximum number of numbers to be represented by our machine is some prescribed M. We shall represent these numbers with some n digits, with each digit capable of representing digit d to the base r. Clearly as r grows large, n will diminish, and conversely, but this is reasonable since M bounds the size of computational task we are able to do, and it is surely this computational task that provides the prime motivation for our design in the first place.

Of course as r grows larger it is reasonable to expect that the "cost" of realizing a single digit will grow as well. Certainly it is going to cost more to realize a ternary digit than a binary digit, or a decimal digit than either. As a reasonable and explicit engineering assumption, then, we shall suppose that the cost of realization of a digit is proportional to the base selected. Thus if number N is represented as

$$N = \Sigma d_{i}r^{1}$$

then the cost c of representing a single digit is

$$c = K_1 r.$$

For our total number of n digits, then, the total cost C is

$$C = K_{1}nr.$$

This gives our total cost C as a function of two variables that are related, namely n and r. If we can specify another relation between them, then we ought to be able to eliminate one in our cost equation, and get our total cost in terms of one of them, in particular in terms of r alone. But this relation is given by our preselected constant M which represents the size of our computational task. Clearly for n digits in base r we have

$$M = r^{n}$$

and since M is a constant, then so also is 1n M, so we can solve for n as

$$\ln M = n \ln r = K_2$$

or

$$n = \frac{K_2}{\ln r}$$

Substituting this expression for n into our original formula for total cost we get

$$C = K_{1}nr = K_{1}K_{2} \frac{r}{\ln r} = K \frac{r}{\ln r}$$

expressing our total cost strictly as a function of r, the radix we choose.

Of course we're now in a position to plot our results as in Figure 1.2.1. Differentiating to detect the minimum we get

$$\frac{dC}{dr} = K \quad \frac{\ln r - r \frac{1}{r}}{(\ln r)^2} = 0$$

ln r = 1

r = e = 2.712...

as the optimal value of radix from these cost arguments.

Of course an irrational radix is a little hard to realize with physical elements, but the obvious conclusion is that base 3 is optimum from this point of view, base 2 is next best, base 4 is pretty good. Base 10, on the other hand, is about twice as expensive to realize as base 2.

Obviously this argument depends upon the original cost assumption, and the reader is invited to insert his own assumption based upon more particular relevance to the technology he might be considering. Probably the cost per digit is something more than just proportional, i.e., it probably costs considerably more to get a base 4 digit than simply twice as much as for a base two digit, especially when considerations of equal reliability, tolerance on element parameters, etc., are included. But at least to this point we have buttressed from a little different analytic point of view our almost complete preoccupation in the following with things that are two-valued.

#### 1.2.3 Binary Codes

Probably the first point to be made about codes and coding is their all pervasiveness in all of our communication activities. There is almost literally nothing we can do about avoiding the use of codes in one form or another, whether we have reference to artificial or natural intelligence, hence it follows that it is to our best interest to study them intelligently, and with an awareness of their capabilities so that we can maximize their application to our own best interests.

Even in our cultural activities most of our communication is via codes of

one sort or another, especially is there if much structure involved. For example, even in art a great deal of the form, proportion, ratios of vertical to horizontal lines, color schemes, etc., involve the acceptance of certain patterns which we accept as culturally good. Only in some of the recent abstract paintings could we agree that no coding is involved, but rather a direct appeal to primal feelings. Certainly much of our musical symbolism involves coding -- if this does not seem evident compare the music from two very different cultures, e.g., country Irish, say, versus Indian, and it is apparent codes are quite different from one another, and probably mutually unintelligible.

Of course we are interested in codes for the transfer of information of a more pristine sort. In these applications codes have been designed for two fundamental purposes: either to achieve secrecy, or to match the information to the particular vagaries of the communication channel. While a great deal has been written about the former, we shall be interested only in the latter. In the context of machines, the character of codes in adapting to the "channel" involved is molded by at least three considerations:

- the physical characteristics of the channel (in the case of machines this results in codes being almost exclusively binary codes, and if not directly so, then at least binary at the next level, e.g., as in the binarycoded decimal codes);

- the noise characteristics of the channel (in the case of machines this results in the design of codes that have various error detection and correction properties); and

- 3) the particular operation involved (in the case of machines this points attention to codes that have particular algorithmic simplifications perhaps, or that speed up addition, or in any other way accomplish the computational task better).

Even within the context of codes based upon binary representations the number of possibilities is literally limitless. We shall consider briefly only the wellknown binary-coded decimal codes at this point, and shall see that even this restricted set presents a very large number of possibilities. Our present purpose is to define the codes, and to illustrate that the algorithmic properties involved are very code sensitive, i.e., that even such a simple algorithm as that for addition must be re-invented for each different code representation. We shall leave further examination of special codes for error detection and correction for a later chapter.

By far the most common types of binary encodings involve the binary-coded decimal codes and the name given to these codes reveals the purpose. We wish to encode the decimal digits in binary form. Clearly at least four bits are required in order to represent the decimal digits, but four bits yields 16 different characters which can be assigned to the ten decimal digits, and this can be done in a remarkably large number of different ways. The natural tendency (only because it's easy for us to read and to remember) is to assign the digits so that the four-tuples can be read in the natural binary ordering; thus

| Digit | Code |

|-------|------|

| 0     | 0000 |

| 1     | 0001 |

| 2     | 0010 |

| 3     | 0011 |

| 4     | 0100 |

| 5     | 0101 |

| 6     | 0110 |

| 7     | 0111 |

| 8     | 1000 |

| 9     | 1001 |

so that, for example, decimal 927 would be represented as 1001 0010 0111, and all this is very simple. But notice we could have made the assignment of code character to decimal digits in any one of

(16) (15) (14)

$$\cdots$$

(7) =  $\frac{16!}{6!} \neq 3 (10^{10})$

different ways, which truly leaves a lot of options. All of these would be binarycoded decimal (BCD) codes, and each would potentially yield different computational algorithms.

Of the BCD codes there are some that possess the property that there exists a set of numbers  $n_1, n_2, n_3, n_4$  such that all ten decimal digits can be represented as

$w_1^{n_1} + w_2^{n_2} + w_3^{n_3} + w_4^{n_4}$

for some set of  $w_i = 0, 1$ . The codes of this type are called the <u>weighted codes</u> and the n are called the weights. The code given above is such a code with weights of 8, 4, 2, 1 (since it corresponds with the polynomial binary representation), hence is sometimes called the 8421 BCD code. There are many such weighted codes, and all have the advantage of computational simplicity which accrues from being associated with the particular set of known weights. (Not all the weights need be positive either, nor unique from one another. For example there is a 6421 BCD code: 8 is coded as 1010, 9 as 1011. Many others exist as well, but we shall not concern ourselves further with them here.)

Of course if we don't limit ourselves to the efficiency of four-tuples for our representation, then the number of possibilities is literally boundless. For example a well known code based on five-tuples is the 2-out-of-5 code

| Digit | 2-out-of-5 |

|-------|------------|

| 0     | 00011      |

| 1     | 00101      |

| 2     | 00110      |

| 3     | 01001      |

| 4     | 01010      |

| 5     | 01100      |

| 6     | 10001      |

| 7     | 10010      |

| 8     | 10100      |

| 9     | 11000      |

|       |            |

which is a nice "packing" of the possibilities since this exhausts all the five-tuples with exactly two 1's since there are just 10 possible. What are the advantages of such a code? For one thing it is an example of a single-error-detecting code. That is any error in a single bit must transform the "word" into another which is not in the code. If we designate the <u>weight</u> of a word as the number of 1's contained therein, then the 2-out-of-5 code is a code of weight 2. Any single error must transform the word into one of weight either 3 or 1, hence any such error is detectable simply by counting the number of ones. (Obviously the well known "parity check" code possesses a similar error detecting capability. It is formed from the 8421 BCD code by adding a fifth bit determined so that the total number of 1's will be even; thus

| Digit | Parity Code |

|-------|-------------|

| 0     | 00000       |

| 1     | 00011       |

| 2     | 00101       |

| 3     | 00110       |

| 4     | 01001       |

| 5     | 01010       |

| 6     | 01100       |

| 7     | 01111       |

| 8     | 10001       |

| 9     | 10010       |

|       |             |

and the occurrence of any single error will transform the parity code work into one of odd weight, hence into a detectable error.) The 2-out-of-5 code has one other important characteristic, however, and that is the constant weight-2 words. This means that whatever "drives" the ones does so with a constant "load" on the drivers. If this is important, then so is the code. An important application is in representing the decimal digits on punched paper tape. Not only is the load on the punch drivers constant, but so are the stress points on the tape so that no digit is apt to "tear" more than any other.

By now it should be clear that the number of possibilities is truly without limit, and one cuts and tailors to meet the particular application. Certainly for every code, a complementary code exists wherein 1's and 0's are replaced with one another. In most cases this would be an irrelevant change. But consider the complementary code to the 2-out-of-5 code. If the particular environment were such that 1's were less error prone than 0's (an unsymmetric channel) then clearly the complementary 2-out-of-5 code would be less error prone than the direct code, i.e., the "message" would get through correctly more often.

Of course if we are really worried about correcting errors, direct replication codes are sometimes used. For example, suppose that we simply replicate each bit position in the 8421 BCD code. Thus, for example, 6 would be encoded as 00111100, resulting in an 8 bit code word. Clearly if an error occurs in any single position we can detect it. It seems that this is not a useful thing to do in this case since we've already indicated the even parity code which will also detect an error in any single position. But we need to be careful. If detection of a single error is our only concern, then our observation is sound. But notice that the replicated code will do much more. It will detect an error in every original bit position, and furthermore will tell us exactly in which bit positions the errors occurred -- i.e., it is error locating as well as error detecting. Depending on the context, this might be important information as well. A conceivable response to the detection of an error is to request a retransmission or recomputation. Depending on the probability of error it may indeed be necessary to limit the amount of recomputation in order to get any useful work done at all.

Further replication continues to provide greater error capabilities. For example in a triply replicated 8421 BCD code, if 001101111010 is received we can quickly decode it as the decimal 6, since the code not only exhibits error detecting capabilities, but also can correct a single error in every original bit position. Thus even though three errors were present in the word, as above, we could correctly decode it. Caution is necessary though, and the use of codes is <u>always</u> fraught with dire consequences if the code is not able to adequately cope with the error producing characteristics of the environment. Thus if two errors had actually occurred in the last (original) bit position in the above example, then we would not only decode the word as a 7, but furthermore we would not even be aware that an error had occurred. (All is not lost even in this case for there are also useful codes called "burst" codes which tend to be good for errors that occur in clusters, e. g., as might be the usual event in the presence of lightning flashes, or other long duration but infrequent disturbances, but these are far beyond the scope of our present considerations.)

Rather, let us now turn to the question of the dependence of arithmetic algorithms (or any other algorithm for that matter) on the particular encoding that is used. This is not an evident thing, and we shall indicate that differences exist by pointing only to a very simple example. For it would seem clear that if it is the decimal numbers that are represented, then the addition algorithm, for example, should of course be the decimal addition table, with suitable allowances for occasional carrys of course. But this is only true at the level of the decimal character itself, and is not true at all at the level of the binary representation. If we are to build an adder, it is exactly at that binary level at which we must operate. The

reader who is unconvinced at this point should address himself to the logic design of an adder where the two addends are decimal characters, but represented in terms of the 2-out-of-5 code. That code is well adapted to paper tape applications, but is definitely inappropriate if addition is what we have in mind. In fact the appropriate answer when asked to derive an algorithm for addition using the 2-out-of-5 code is:

- 1) convert all characters to the 8421 BCD code

- 2) use an appropriate 8421 BCD code algorithm for addition

- 3) convert the sum back to the 2-out-of-5 code

This is an eminently practical way of avoiding the real meaning of the question in the first place, and reaffirms the original point; the algorithm for one code is not the same as the algorithm for another.

To illustrate this in a simple example, let us compare the addition algorithms for the well known 8421 BCD with another variant of the BCD codes known as the excess-three, or XS3 code. Both are shown below for comparison purposes.

| Binary  | Decimal Character |     |  |

|---------|-------------------|-----|--|

| 4-tuple | 8421              | XS3 |  |

| 0000    | 0                 |     |  |

| 0001    | 1                 |     |  |

| 0010    | 2                 |     |  |

| 0011    | 3                 | 0   |  |

| 0100    | 4                 | 1   |  |

| 0101    | 5                 | 2   |  |

| 0110    | 6                 | 3   |  |

| 0111    | 7                 | 4   |  |

| 1000    | 8                 | 5   |  |

| 1001    | 9                 | 6   |  |

| 1010    |                   | 7   |  |

| 1011    |                   | 8   |  |

| 1100    |                   | 9   |  |

| 1101    |                   |     |  |

| 1110    |                   |     |  |

| 1111    |                   |     |  |

and as we've noted before the original decimal characters can be assigned to only a subset of the sexteen possible four-tuples. The origin of the name excess-three should be clear--each BCD representation is simply the 8421 code "plus 3". Thus

4-tuples which have no assignment are known as <u>forbidden</u> characters since some special allowance must be made for them when they occur. To derive our 8421 algorithm, let us proceed by example. Suppose we add, say 5 + 2 in decimal. In the 8421 we confirm

$$\frac{5}{2} = \frac{0101}{0111}$$

and we perceive no difficulty since the code 0111 correctly denotes the proper decimal character. Now try 6 + 5:

$$\begin{array}{rcl}

6 &=& 0110 \\

\underline{5} &=& \underline{0101} \\

11 & 1011

\end{array}$$

which is correctly determined as "11" of course, but the machine doesn't know that, for "11" is not one of the decimal characters it has been taught to assign to each decimal position. The proper path to resolve the problem is to augment our algorithm so that whenever a "forbidden" character appears, and "11" is one of them, then we should "add 6" to the result in order to pass completely over the forbidden range. Of course a carry will be produced in this process, but that is the problem of the next stage. This gives 1 0001 as the correct result.

Finally, let's try something like 9 + 8:

$$9 = 1001 \\ \frac{8}{17} = \frac{1000}{10001}$$

indicating the sum is one, and of course producing a carry. The carry is all right, but the sum is definitely wrong. The problem again is that we have passed over the forbidden range and landed, without signal, past it. Without signal, that is, except for the production of the carry, and that means that we should "add 6" again in order to ignore the six invalid or forbidden characters. Doing this in this example we get 1 0111, again the correct result.

This turns out to encompass all possible cases, and our 8421 addition algorithm for each digit becomes something like:

1) Perform regular binary addition

- If the character perceived is a valid character without carry, then make no further correction; if not then

- 3) if an invalid character, add 6, producing a carry for the next stage; or

- if a valid character but with a carry, then add 6 anyway, and pass the carry along.

Now all this can be compared with the algorithm for the excess-3 code. Again suppose we add 5 and 2:

| 5 = | 1000 |

|-----|------|

| 2 = | 0101 |

|     | 1101 |

Since each addend was in excess-3, then the sum must be in excess-6, hence must have a three removed in order to return it to the proper XS-3 character. Doing this

|   | 1101 |

|---|------|

| - | 0011 |

|   | 1010 |

which then compared with the proper code for decimal 7 is seen to be the correct XS-3 result.

Again let's try 6 and 5:

$$\begin{array}{rcl}

6 &=& 1001 \\

5 &=& 1000 \\

& 1 & 0001

\end{array}$$

resulting in a carry, but also in an invalid character. To convert to XS-3 we should again subtract 3, but to "jump" the forbidden band we should this time add a 6. The net result is to add a 3 which we do

$$\begin{array}{r}1 & 0001 \\

+ & 0011 \\

1 & 0100

\end{array}$$

which is the correct XS-3 result for a "1" as the sum and a "1" as the carry.

No different kinds of things occur in this case, so the XS-3 algorithm becomes:

- 1) Perform regular binary addition.

- 2) If a carry is not produced, subtract 3.

## 3) Otherwise add 3.

Comparing the two algorithms, they are certainly different, although it remains moot whether one is "better" than the other or not. The 8421 requires a correction only in the event of an invalid character or a carry. The XS-3 requires the same correction at each addition, but only its sign depends upon the carry. The point to be illustrated here was that they were different, and if you were going to build an adder, based upon one or the other, it would be crucial to your career to know which.

## 1.3 Design Specifications

Paramount amongst the problems of logic design is the first step: that of transforming the verbal specification of exactly what is desired into a nonambiguous, realizable network which does that job which is intended. Since the first step in this process involves the human mind in determining exactly what is required, it should not be surprising that the initial specification of a problem statement and solution is often not well defined, and the steps to an ultimate solution involve a feedback sort of process whereby the "problem solver" must many times query the "problem poser" to reconsider just exactly what "answer" was wanted to a particular (unanticipated) set of values of the input variables.

In this section we shall briefly delineate two aspects relevant to the problem of design specifications. The first concerns the formal reduction of the arbitrary (binary) problem to the well-defined specification of the desired output for all possible sets of values of the inputs. The second is an historically accurate resume of the propositional calculus, at least those portions of interest to logic design. The calculus was the first formal attempt at quantifying human thought processes, and leads directly to the algebraic formalism of interest to logic designers: the switching algebra.

1.3.1 Binary Mappings and Combinational Functions

If we are to simplify our (computational) world to a set of binary values, then it follows that the only kinds of networks of such values that we can build are those which assign binary values to particular sets of the binary inputs involved.

This simplification of our world seems perhaps a little harsh, but it is complete, and anything that is computatable, in a very complete and abstract sense, is computable in terms of such a binary quantification.

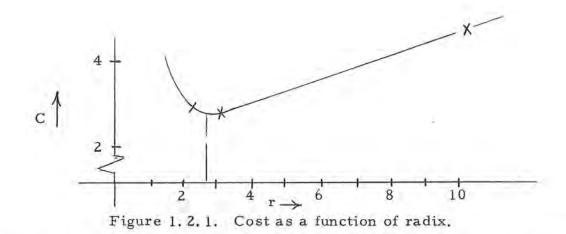

As a very simple example, suppose we are concerned with the design of a heater control to regulate the temperature in our office. We can easily address the problem in terms of identifiable binary variables concerned with the environment of the office. First of all, we can agree that the heater should be either ON or OFF. Our remaining problem is to determine the operation of this control in terms of the independent variables of interest.

For example we might identify the variables of interest as whether our office window is open or closed (distinctly a binary variable), whether the outside temperature is less than 55<sup>°</sup> or not, and whether the door to the office is open (hence drafty) or not. All these are clearly binary variables and it is our problem to design the heater control as a desired function of these three variables:

w = true, implies that the window is open

- t = true, implies that the outside temperature is less than  $55^{\circ}$

- d = true, implies that the door is open.

Our desired solution might turn out to be that:

The heater is to be on if and only if the window is open, the temperature is greater than  $55^{\circ}$ , and the door is open; or the window is closed, but the temperature is less than  $55^{\circ}$ , and the door is closed.

Now this solution may be happy or not, depending on the particular individual. The point is that it is a solution in that it prescribes a response for the heater control as a function of the binary variables of interest. Suppose that we have a relay coil that operates in response to each of the variables in the sense that when a variable is "true" then the corresponding relay coil is operated. Then if, for example

indicated a contact on the w relay that is open when the w relay is not operated, while

\_\_\_\_\_\_!\_\_\_\_

\_\_\_\_ W \_\_\_\_

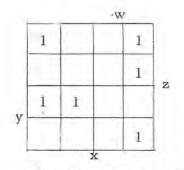

indicates a contact on the w relay that is closed when the w relay is not operated, then surely the network of Figure 1.3.1.1

Figure 1.3.1.1. Switching network for heater control

properly operates the relay "h" which in turn controls the office heater.

This sort of design technique is surely appropriate to digital design, and is of sufficient generality to handle all possible such problems, whether they involve the control of heaters, or the next "bit" to be inserted in a register as a function of fifteen binary variables associated with a pattern to be recognized by a digital machine.

1

In some sense, then, our problem is completely solved by such ad hoc techniques. The reason that the problem is not completely solved, however, is that our simple example does not reveal the complexities of the problem that can exist when the number of variables involved in the problem statement grows larger than two or three. Furthermore, even our interpretation of the English statement that we posed above as a solution to the problem is not well defined, and can be interpreted in various ways.

To avoid these problems, it is necessary that an appreciable amount of formalism be adopted in order to handle such problems systematically, and without ambiguity. To this end we shall briefly review some of the first attempts at formalizing such verbal statements, and we shall see that these attempts lead directly to the switching algebra appropriate for making such verbal specifications explicit and realizable by switching networks of abritrary complexity.

## 1.3.2 The Calculus of Propositions

It might appear that the propositional calculus is properly the study of logicians and philosophers, and hardly should be of interest to practical engineers and computer designers. Our compelling interest is to work our way into a consideration of a switching algebra that will be of immediate utility in the design of networks of switches, and of things that act like switches.

Yet, as is often the case, the switching algebra that we shall develop is a simple example of the early propositional calculus studied by George Boole in the middle nineteenth century. Just as surely as Heaviside, Gardner and Barnes stood on the shoulders of Laplace, Fourier and Newton in the development of modern circuit theory, so did Shannon stand on the shoulders of Boole in his first presentation of modern switching theory not very many years ago.

There are several reasons for a brief consideration of the calculus. A not

minor one is that it is historically relevant, and provides a convenient introduction to the stark formalism of the switching algebra. Another major reason is that the specifications of ultimately deterministic machines start off as English literal statements, and the formalism of something like the calculus is always necessary in order to make such statements exact, manipulatable, and, as we shall see, unambiguous.

Another reason is that it allows us to introduce many terms and procedures in the calculus which we shall use later in the algebra, and hopefully by that time they will seem like old familiar concepts.

Of course we have our option in the order in which we consider these matters. Many texts treat the propositional calculus, and then show the switching algebra as a particular case of it. Others develop the algebra in a purely formalistic way, and then give the propositional calculus as a "practical" application of it. We shall choose the former, but we should realize that the ordering is just a matter of taste.

#### 1.3.2.1 Elements of the Calculus

The objective of the propositional calculus, which is a branch of symbolic logic, is the <u>pursuit of truth</u>, and not many objectives could be much nobler than that. "Truth", however, much like the word "information" in information theory, must be taken in context, (i.e., Humpty Dumpty-like, it means exactly what we mean it to mean at the time that we say it, and nothing more nor less.)

Thus in this context, truth is a two-valued thing which can be assigned to declarative statements. That is, a declarative statement is looked upon as a variable which can assume one of two values: True (T), or not true (False, F). Of and other pair of marks would do all well (examples are T,  $\bot$ ; or 1,0) but T, F will serve our purposes.

Such declarative statements are called <u>propositions</u>. Thus a proposition is a declarative sentence to which the value T or F can be assigned. For example, such a proposition is i, where

i ; Iran is in South America.

This proposition reminds us that it is with <u>logical truth</u> that we are concerned, and the fact that the above statement is <u>factually false</u> is irrelevant. Thus a

proposition is a logical variable with the evaluation T of F to be determined, or arbitrarily assigned. Of course, Boole wasn't concerned with anything so trivial as single propositions. His aim was to develop a model for the complex "laws of thought" by which compounds of elementary propositions could be composed and evaluated.

Thus in general we shall deal with a list of propositions designated by the symbols p, q, r, ... and in this form they are called <u>unspecified</u> or <u>arbitrary</u> propositions (i.e., propositions to which a truth value has not been assigned). That is, they are our <u>propositional variables</u>. It should be clear that propositions are to considered en toto; that is

p: Panama is in Asia

q: Quentin has red hair

are not to be split apart into classes, or sets, such as the "set of countries in Asia" or the "class of people having red hair" such as would be our want if we were considering the syllogisms of classical (or Lewis Carrol) type logic, and were attempting to come to conclusions about set membership. Rather our propositions are to be considered as an unbreakable set of atoms with which one of the two truth values are to be associated.

Of course we immediately disassociate ourselves from the logically undecidable sorts of statements like "the sentence I am uttering right now is false" as being in the class of things with which we are not concerned. These are games from a sort of "naive propositional calculus" which need not concern us.

Having recognized the variables of our calculus, we then recognize the values that they may assume as being the <u>constants</u> of our discourse; these are the marks T and F. Thus T and F are our propositional constants and we identify them immediately as those particular propositions that are either <u>always true</u>, or always false.

We shall of course want to relate propositions to one another. In particular given p and q, if we have the situation that p is T whenever q is, and conversely, then we write

$\mathbf{p} = \mathbf{q}$

which is called a tautology.

#### 1.3.2.2 Compound Propositions

Given p, q, r, ... (which are thus statements or elements describing some universe of discourse of interest to us--perhaps even the real world!) we wish to augment our propositions to include <u>functions</u> of these elemental propositional variables. This of course was Boole's goal as well; he conjectured that all of the reaches of rational human thought might be analyzable by examining the functions of simple propositional variables. Thus we want to consider things such as

## f(p,q,r)

which, we shall insist, must be another proposition, i.e., another construct to which an assignment of T or F is again relevant. Thus f is a dependent variable which is to depend for its evaluation on the particular values of T or F assigned to the independent variables which are the elemental propositions p, q, r....

Now can we go about systematically examining the nature of these functions of propositional variables? One way is suggested by the finiteness of the number of constants in our system. Since they are finite in number, we ought to be able to exhaustively examine the functions of n variables, starting with n = 0 and proceeding for n = 1, 2, 3, ... We shall start this way, but shall not go very far before we conclude that any further is folly.

Are there any functions of no variables? Certainly. These are simply our two constants T and F. That is, the values of T and F are evidently independent of the assignment of values to any other propositions.

What about functions of a single variable? What do we mean by f(p)? Clearly f(p) = p is such a function, and it is T whenever p is, which is all rather trivial, and we don't seem to be making much headway. Of course there is only one other possible (nontrivial) case and this is the single variable f(p) that is T whenever p is F, and F whenever p is T. This f(p) is called the denial of p'(alternatively the negative or complement of p). This f(p) is also written

$\overline{p}$ , p',~p, not p

and so on, depending upon the stylistic taste of the particular user. The point is that these symbols introduce the notion that functions can also be interpreted as

<u>operators</u> on the variables of the argument of f. Thus we are considering in this instance unary operators, i.e., operators that require only a single argument. For example if p is the proposition "Panama is in Asia", then  $\overline{p}$  is the proposition "Panama is not in Asia", or, probably better: "It is not the case that Panama is in Asia".

Have we exhausted the possibilities? Clearly so, in this case, although we can always confirm the situation by systematically examining <u>all</u> of the possibilities by enumerating them. This can be most easily done by means of the so-called <u>truth table</u>, or <u>table of combinations</u>, which is simply a way of displaying all the possible values that the independent variables can assume, and examining the number of possible f(p) that can be formed by assigning the same constants to f(p). Thus for the single-variable case we have

| р | f(p)           |

|---|----------------|

| F | a <sub>0</sub> |

| Т | a <sub>l</sub> |

where the a<sub>i</sub> can be assigned arbitrarily as F or T. Thus the total number of different possible functions in such a table is exactly the number of different ways of filling in the column labeled f(p) by filling in the different constants. Since there are only two constants it follows that the number of different functions is exactly

2<sup>No.</sup> of rows in the table

and in this case we have the possibilities

| р | f <sub>0</sub> (p) | f <sub>1</sub> (p) | f <sub>2</sub> (p) | f <sub>3</sub> (p) |

|---|--------------------|--------------------|--------------------|--------------------|

| F | F                  | F                  | т                  | т                  |

| Т | F                  | т                  | F                  | т                  |

which we see are just

| f <sub>0</sub> (p) | 4  | F |

|--------------------|----|---|

| $f_1(p)$           | 10 | р |

| f2(p)              |    | p |

| f <sub>3</sub> (1) | -  | Т |

and we are through with this case.

But what are the constants T and F doing in our tabulation, when we agreed that they were functions of no variables? Clearly, this sort of enumeration includes amongst the function of n variables, also the functions of n-1 variables, n-2 variables, etc. If a function f(p) is not actually a function of its argument p, we say that it is <u>vacuous</u> in p (or <u>redundant</u> in p, or <u>degenerate</u>). We shall concern ourselves with examining this situation more thoroughly later.

Now how about the functions of two arguments, i.e., the f(p,q)? Certainly there are more of them, but again we can enumerate all possibilities by extending our truth table

| р | g | f(p,q)         |

|---|---|----------------|

| F | F | a <sub>0</sub> |

| F | т | a              |

| Т | F | a <sub>2</sub> |

| т | т | a <sub>3</sub> |

and substituting all the possible values for the  $a_i = 0, 1$ . Since there are four rows, there will clearly be

$$4^2 = 16$$

functions of the two variables. As before, of course, some of these will be degenerate in the two variables. Also, some of them are of particular importance, so we shall draw them forth in a little more detail at this point.

#### AND.

Given p and q we form the f(p, q, ) that asserts both of them are T. This f(p, q) is called their <u>conjunction</u>. Of course this is a two-variable operator, since two arguments are involved. It is symbolized by f(p, q) = pAq (or p·q, or just pq, which we shall favor later on). Thus pAq is just the proposition that is true when and only when both p and q are true. We exhibit this function (or binary operator) by the appropriate truth table

| р | g    | pAq          |

|---|------|--------------|

| F | F    | F            |

| F | т    | F            |

| F | F    | $\mathbf{F}$ |

| т | т    | т            |

| 1 | . 31 |              |

The rule for a combination, i.e., the name of the binary operation, is called a <u>logical connective</u>, and in the case of conjunction the connective is seen to correspond directly with the English usage of the word "and". Thus

p: Panama in is Asiaq: Quentin has red hair

pAg: P is in A and Q has R.

Furthermore, although we shall not dwell on such properties, we note that the connective  $\Lambda$  displays all sorts of verifiable properties such as

$$p \wedge q = q \wedge p$$

$$p \wedge p = p$$

$$T \wedge T = T$$

$$T \wedge F = F \wedge T = F$$

$$p \wedge \overline{p} = F$$

which can be used to "evaluate" or "simplify" more complex forms, e.g.,

$$p \wedge p \wedge q \wedge p$$

$$\begin{vmatrix} p = T \\ q = F \end{vmatrix} T, F$$

$$= T \wedge F \wedge T = T \wedge F = F$$

and so on,

OR.

In similar fashion, English statements are often "or-ed" together. To simulate this two-variable operator we define the f(p,q) that is T whenever either p or q is T by the table

| р | g | pvq |

|---|---|-----|

| F | F | F   |

| F | Т | Т   |

| т | F | т   |

| Т | Т | т   |

|   |   |     |

which defines the connective "v" (also written as p + q), and also called the <u>disjunc</u>-<u>tion</u> or inclusive-OR of p and q.

Of course, admitting that there is something called the inclusive-OR suggests

that there might be something called the exclusive-OR, and comparing the two possibilities reveals an ambiguity that occurs in common English usage. Thus, if we say either "p or q" we may mean to include "or both", or we may really mean "but not both", and it is not always clear in language usage just which is meant. If we say

"Either Paul is first in line or Quentin is first in line"

there is probably no ambiguity, since it's hard to admit that both might be first. But if we say

"Either Paul is first in line or Quentin is last in line"

then it is not at all clear whether we mean to include the possibility of both or not, since the events are not mutually exclusive.

In order to avoid this ambiguity we shall have to be precise where the meaning is not clear. We shall assume that p + q represents the inclusive-OR read as "p or q or both", and for the other case we shall use  $p \oplus q$  to be read as "p or q but not both". Thus the exclusive-OR,  $p \oplus q$  is defined by the table

| р            | q | p⊕q |

|--------------|---|-----|

| F            | F | F   |

| F            | Т | Т   |

| т            | F | T   |

| $\mathbf{T}$ | т | F   |

The operator " $\oplus$ " is also written sometimes as " $\neq$ " and called the "not equivalence" or "not-equiv" operation. This suggests the possibility of relations between the various operators that can be defined. For example, we can define intuitively another binary operator as follows. Surely p and q are equivalent if they are prescribed to have the same truth value, in order for the compound statement "p' is equivalent to q" to be true. Thus the following truth table, using  $p \equiv q$  for the relationship, surely defines  $p \equiv q$ , hence the operator " $\equiv$ ".

|   |              | (1) | (2)   | (3) |

|---|--------------|-----|-------|-----|

| р | g            | pΞq | p ≣ d | p≢q |

| F | F            | т   | F     | F   |

| F | т            | F   | т     | Т   |

| т | F            | F   | т     | т   |

| т | $\mathbf{T}$ | т   | F     | F   |

Now column (2) shows the denial of  $p \equiv q$ , which is reasonably called " $\notin$ ", and can be quickly identified as being the <u>same</u> operator as our exclusive-OR " $\oplus$ ". Hence the "not-equiv" operator is just another name for our exclusive-OR operator.

Incidently we have concluded that

$\overline{p \equiv q} = p \neq q = p \oplus q$

and this "theorem" can be considered proved simply by the fact that we have shown the corresponding columns in the truth table to be identical.

For, after all, two function are the same if for every point in the domain (combinations of values of the arguments) they have the same value in the range (i.e., the same mapping to the function values). For a finite number of values of the discrete variables we can always (in principle at least) list all of the combinations of the arguments, and exhaustively verify whether the two functions are the same or not. Clearly the rows of the truth table constitute such a listing, and the identity of two columns verifies the assertion in a completely adequate way. This method of proof is perfectly general, provided we have time to list all the possibilities. It is called <u>proof by perfect</u> induction, and is so referenced in the literature.

As before, with respect to any of these operators, a number of useful computational tautologies can be derived. For example, with respect to v:

$p \mathbf{v} p = p; \ \mathbf{T} \mathbf{v} p = \mathbf{T}$   $p \mathbf{v} \overline{p} = \mathbf{T}; \ \mathbf{F} \mathbf{v} p = p$   $p \mathbf{v} q = q \mathbf{v} p, \text{ etc.}, \text{ etc.}, \text{ and for the } \mathbf{\Phi}$   $p \mathbf{\Phi} p = \mathbf{F}$  $p \mathbf{\Phi} \overline{p} = \mathbf{T}, \text{ etc.}, \text{ etc.}$

In evaluation, we proceed as before; thus

$pq \lor \overline{p}r \lor s | = TT \lor FF \lor T = T \lor F \lor T = T \lor T = T$  p = T q = T r = F s = T

and so on, for arbitrary expressions on these operators.

It is also important to note that just as in other case of binary operators these connectives might also be <u>order sensitive</u>. Thus it is generally important that we either agree beforehand on precedence of operators, or else we must carefully use parentheses in order to designate which compound operator we actually mean. Thus, for example, in the compound declarative sentence "John is sick or Mary is away and the house is cold", properly symbolized by

### j∨mh

it is not immediately clear whether we mean  $j \vee (mh)$  or  $(j \vee m)h$ . Of course these might be the same, but it is not evident.

In order to verify whether they are the same or not, we can again call upon perfect induction to check:

| j | m | h | mh | j∨m          | j ∨ (mh) | (j ∨ m)h     |

|---|---|---|----|--------------|----------|--------------|

| F | F | F | F  | F            | F        | F            |

| F | F | т | F  | F            | F        | F            |

| F | т | F | F  | $\mathbf{T}$ | F        | F            |

| F | т | т | T  | $\mathbf{T}$ | т        | $\mathbf{T}$ |

| т | F | F | F  | т            | Т        | F            |

| т | F | т | F  | $\mathbf{T}$ | т        | т            |

| т | т | F | F  | т            | т        | F            |

| т | т | т | Т  | Т            | т        | т            |

and since the last two columsn are <u>not</u> identical, it follows that it is <u>not</u> the case that

# $j \lor (mh) = (j \lor m)h$

hence that in general we must be careful to prescribe our ordering, or else to observe parentheses carefully in writing expressions in the binary operators we're considering.

Notice that the above was again an example of perfect induction. To show that two functions are not the same, it suffices to show that they differ in at least one row of the truth table that displays all of their possible values.

We could continue with an exhaustive consideration of the two-variable operators, but instead we'll pause for a bit and consider a few points that can be made at this time for arbitrary n-variable functions.

#### 1.3.2.3 Some n-Variable Observations

What do we mean by an n-variable function in the first place? By extension we mean an  $f(p_1, p_2, ..., p_n)$ , where n is a finite (though arbitrary) number, and the  $p_i$  are again our elementary or independent propositional variables. The function is well-defined if for every set of "values" for the  $p_i$ 's a value of f is determined as either a T or an F.

Again, because of the finiteness of things, we can describe such a function by simply listing all of its function values for each point in the domain. I.e., again our truth table formalism extends directly to any n, and we can write immediately that

| Pn | 1.25 | P <sub>2</sub> | $\mathbf{P}_1$ | $f(p_1, \ldots, p_n)$       |

|----|------|----------------|----------------|-----------------------------|

| F  | 1.1  | F              | F              | a.                          |

| F  | 5.9  | F              | т              | a                           |

| F  |      | т              | т              | a.2                         |

| т  | :    | Т              | т              | :<br>a<br>2 <sup>n</sup> -1 |

and be assured that each of the possible n-variable functions corresponds to a selection of the values of the a, from either T or F.

Of course, we can also use this vehicle again to answer the question of how many n-variable functions there are. As before, the answer is the number of different ways of specifying the column for f in the table. This is still

No. of rows in the table

and the number of rows is in turn a function of the number of independent variables

and is easily seen to be 2<sup>n</sup>. It follows that the number of different n-variable functions is

2<sup>2<sup>n</sup></sup>

which is eminently finite as predicted, and alluringly simple looking. But the allure is deceptive for the number N(n) of such functions grows alarmingly fast, and becomes very large even for reasonably small values of n. Thus we have

|                         | n   | N(n)                        |

|-------------------------|-----|-----------------------------|

|                         | 0   | 2                           |

|                         | 1   | 4                           |

| (Number of neurons in ) | 2   | 16                          |

| (human nervous system)  | 3   | 256                         |

| (Total number of games) | 4   | $2^{16} = 65,536$           |

| of chess                | 15  | $2^{32} = 4, 294, 967, 296$ |

| (Total number of atoms) | - 6 | $2^{64} \doteq 2(10^{19})$  |

| (nuniverse              | ×7  | $2^{128} \doteq 4(10^{38})$ |

|                         | > 8 | $2^{256} = 10^{75}$         |

|                         |     |                             |

|                         |     | 1                           |

and it becomes clear that any sort of exhaustive examination is completely out of the question, and any proposed technique for doing so rapidly becomes hopelessly swamped.

Nevertheless, we can completely, and formally describe all possible situations by the augmented truth table:

|                              | p <sub>n</sub> p <sub>1</sub> | $f_0(p_1,, p_n)$ | f <sub>1</sub> | <br>f<br>2 <sup>2<sup>n</sup>-1</sup> |

|------------------------------|-------------------------------|------------------|----------------|---------------------------------------|

| $2^n$ rows $\left\{ \right.$ | F F<br>:<br>T T               |                  |                |                                       |

At this point we might hope to proceed exactly as before for the case of two variables. That is, we might define n-variable connectives, although we have already seen that we can't do anything exhaustive. But some subset might be

useful. For example, we can certainly define an n-variable AND by extension as

$A_n(p_1, ..., p_n) =$  that f which is true whenever <u>every</u>  $p_i$  is true

and the n-variable OR as something like

$O_n(p_1, \dots, p_n) =$  that f which is true whenever any  $p_i$  is true.

Obviously, then, our binary connectives are special cases of such things, and we agree that when n = 2 we can write

$$A_2(p_1, p_2) = p_1 \wedge p_2$$

$O_2(p_1, p_2) = p_1 \vee p_2$

and so on,

But can we do better? We should certainly hope so, for keeping track of the possibilities, even the interesting ones, would simply become too horrendous a bookkeeping task.

It turns out that we can do better, in fact we can easily show that just the twovariable connectives we've defined so far will suffice to represent any n-variable connective that we wish.

To verify this assertion we first of all need to affirm associativity for our binary connectives; namely we need to affirm that

$$(P_1 \wedge P_2) \wedge P_3 = P_1 \wedge (P_2 \wedge P_3) = P_1 \wedge P_2 \wedge P_3$$

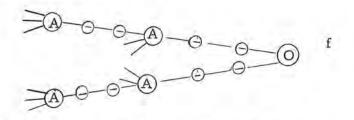

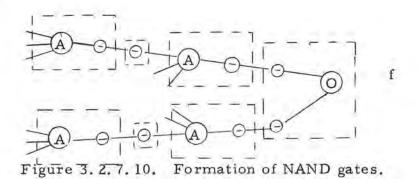

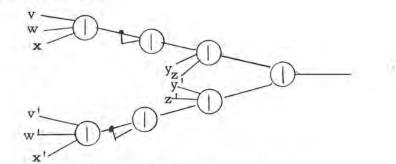

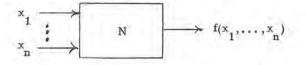

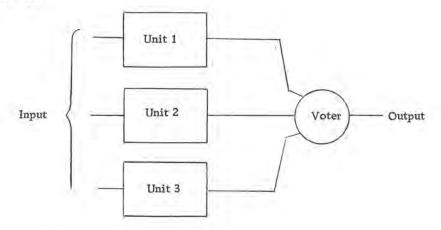

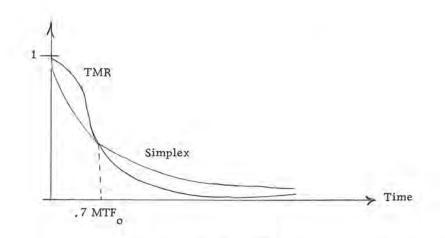

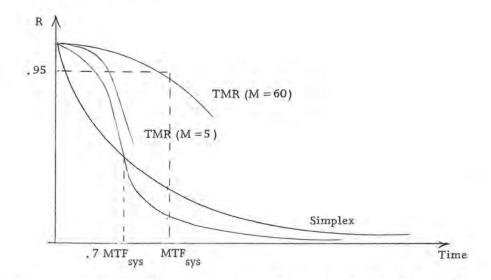

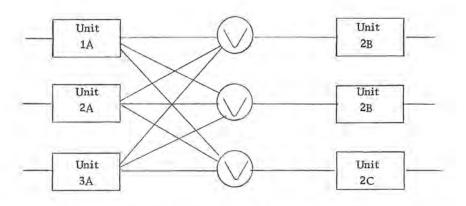

and that