#### Assessment of Outphasing Power Amplifiers and Their MMIC

Implementations

by

### DANIEL N. MARTIN

M.S., University of Texas at Dallas, 2016

B.S., University of Texas at Dallas, 2015

A thesis submitted to the

Faculty of the Graduate School of the

University of Colorado in partial fulfillment

of the requirements for the degree of

Doctor of Philosophy

Department of Electrical and Computer Engineering

September 2020

Committee Members:

Taylor Barton

Zoya Popovic

Gregor Lasser

Paolo De Falco

Michael Roberg

Martin, Daniel N. (Ph.D., Electrical Engineering)

Assessment of Outphasing Power Amplifiers and Their MMIC Implementations

Thesis directed by Professor Taylor W. Barton

Power amplifier (PA) applications consistently require increased performance for bandwidth, power, and efficiency. Modern communication and telemetry systems are required to operate across multiple bands that can span octaves while scaling down unit power amplifier cells to fit on the back-end of phased array systems. Phased array implementation scales branch complexity for both signal generation and linearization. This creates problems with conventional approaches for back-off efficiency enhancement techniques as well as increasing the importance of linearity optimization. This reduces the complexity of the digital pre-distortion (DPD) required to operate the system while maintaining high average efficiency for large peak to average power ratio (PAPR) signals.

This thesis presents advanced outphasing PA architectures. Each of the architectures answers a different design challenge for modern communication and telemetry systems. Analog signal separation reduces the need for a digital signal split removing cost, size, weight, and power (C-SWaP). Improved modeling and understanding of the design of the inphasing splitter allows for optimization of linearity and efficiency. This work looks at utilizing novel power combining implementations with reconfigurable matching networks to operate outphasing PA's across multiple bands spanning an octave allowing for functional flexibility and reduced system complexity.

The thesis works on two distinct outphasing implementations: the RF-input outphasing power amplifier (RFIO PA) and the dual-input reconfigurable outphasing power amplifier (DIRO PA). The designs presented in this work are as follows:

- Hybrid X-band RFIO PA utilizing a previously designed dual-input X-band outphasing monolithic microwave integrated circuit (MMIC) in an unreleased Qorvo GaN 150 nm process

- Hybrid X-band RFIO PA utilizing three different non-linear elements (PIN diode, diode-connected transistor, and mesa resistor) in the signal splitter design to optimize for linearity and efficiency in

conjunction with a custom designed dual-input outphasing PA MMIC in Qorvo 150 nm GaN es process

- MMIC RFIO PA utilizing diode-connected transistors for integrated signal splitter design in Qorvo 150 nm GaN es process

- MMIC 6-12 GHz reconfigurable outphasing combiner with a switchable shunt line to control reactive loading in Qorvo's GaAs 250 nm process

- MMIC DIRO PA which is reconfigurable from 18-38 GHz with >2 GHz of instantaneous bandwidth in the WIN semiconductor PIH-110 process

# DEDICATION

To my family, especially my parents (Maria and Tim), for all the love and support they have given me throughout my educational journey.

## ACKNOWLEDGMENTS

I am extremely thankful for my graduate advisor Prof. Taylor Barton for the excellent guidance, assistance, and education throughout my graduate experience spanning two universities. I am extremely honored to have had the privilege to experience the group being built up from the beginning.

I would like to thank Prof. Zoya Popovic and Prof. Gregor Lasser who have helped through numerous classes and side projects with advice and guidance on research topics as well as making me feel welcome into the group when first transferring into the University of Colorado Boulder at the beginning. In addition, I would like to thank Dr. Michael Roberg and Dr. Scott Schaffer for their professional and technical guidance through my Ph.D. and my internship at Qorvo.

I thank all my close friends and colleagues both current and graduated during my time at CU Boulder -Shane, Mike, Maxwell, Gregor, Eric, Patrick, Nina, Allison, Paolo, Prathamesh, and Scott for their friendship and all the great times. I would also like to thank everyone else across all research groups for their technical and emotional support. I would like to thank my amazing girlfriend Anna Nixon for her continuous love and support.

Finally I would like to thank Qorvo and WIN Semiconductors for their assistance on many numerous MMIC fabrication issues and access to the amazing processes.

# Contents

| 1 | Int | RODUCTION                            | 1  |

|---|-----|--------------------------------------|----|

|   | 1.1 | Background and Motivation            | 1  |

|   |     | 1.1.1 Data Transmission              | 2  |

|   | 1.2 | Load Modulation                      | 4  |

|   | 1.3 | Outphasing                           | 7  |

|   |     | 1.3.1 Chireix Outphasing             | 9  |

|   |     | 1.3.2 Mixed-Mode Outphasing          | 0  |

|   | 1.4 | Thesis Contents                      | 12 |

| 2 | RF  | -Input Outphasing 1                  | 13 |

|   | 2.1 | RF-Input Outphasing PA Theory        | 4  |

|   |     |                                      |    |

|   | 2.2 | X-BAND HYBRID RFIO PA                | 16 |

|   |     | 2.2.1 Measurements                   | 8  |

|   | 2.3 | RFIO Analysis                        | 23 |

|   |     | 2.3.1 RFIO Model and Design Approach | 26 |

|   | 2.4 | Non-Linear Elements                  | 32 |

|   |     | 2.4.1 PIN DIODE                      | 33 |

|   |     | 2.4.2 Diode-connected transistor     | 35 |

|   |     | 2.4.3 Mesa Resistor                  | 37 |

|   |     | 2.4.4 MMIC Design 3                  | 39 |

|   |     | 2.4.5 RFIO System Measurement        | 12 |

|   | 2.5   | X-BAND MMIC RFIO PA                                      | 47 |

|---|-------|----------------------------------------------------------|----|

|   | 2.6   | Conclusion                                               | 51 |

| 3 | WI    | de-Band Outphasing Combiners                             | 52 |

|   | 3.1   | Frequency-Reconfigurable Outphasing                      | 53 |

|   | 3.2   | MMIC Implementation                                      | 55 |

|   | 3.3   | Measurements                                             | 57 |

|   | 3.4   | Conclusion                                               | 60 |

| 4 | DIF   | RO PA                                                    | 61 |

|   | 4.1   | Outphasing Theory and Limitations                        | 64 |

|   | 4.2   | Frequency-Reconfigurable Outphasing Architecture         | 66 |

|   |       | 4.2.1 Broadband floating to single-ended load conversion | 66 |

|   |       | 4.2.2 Compensating reactances                            | 68 |

|   | 4.3   | MMIC Implementation                                      | 69 |

|   | 4.4   | Measurements                                             | 74 |

|   |       | 4.4.1 Modulated Measurements                             | 79 |

|   | 4.5   | Conclusion                                               | 81 |

| 5 | Sun   | MMARY AND FUTURE WORK                                    | 84 |

|   | 5.1   | Summary                                                  | 84 |

|   | 5.2   | Future Work                                              | 85 |

| B | IBLIC | OGRAPHY                                                  | 86 |

| A | PPEN  | IDICES                                                   | 96 |

| A | MN    | AIC Process Technology                                   | 96 |

|   | A.1   | Wolfspeed (Cree)                                         | 96 |

|   |       | A.1.1 250 nm GaN                                         | 97 |

|   | A.2                                                       | Qorvo                                                                                                                             | 97                   |

|---|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------|

|   |                                                           | A.2.1 250 nm GaAs                                                                                                                 | )7                   |

|   |                                                           | A.2.2 150 nm GaN es                                                                                                               | 98                   |

|   | A.3                                                       | WIN Semiconductor                                                                                                                 | 18                   |

|   |                                                           | A.3.1 PIH-110 GAAs                                                                                                                | 19                   |

|   |                                                           | A.3.2 Pre-Production 150 nm GaN                                                                                                   | 19                   |

|   | A.4                                                       | Conclusion                                                                                                                        | )0                   |

|   |                                                           |                                                                                                                                   |                      |

| В | MN                                                        | IIC INFORMATION 10                                                                                                                | )1                   |

| В |                                                           | IIC Information       10         X-Band Inverse Class-F PA       10                                                               | -                    |

| B | B.1                                                       |                                                                                                                                   | )1                   |

| В | B.1                                                       | X-Band Inverse Class-F PA                                                                                                         | )1<br>)2             |

| В | B.1<br>B.2<br>B.3                                         | X-Band Inverse Class-F PA                                                                                                         | )1<br>)2<br>)2       |

| В | <ul><li>B.1</li><li>B.2</li><li>B.3</li><li>B.4</li></ul> | X-Band Inverse Class-F PA       10         Wideband Outphasing Combiner       10         X-Band Dual Input Outphasing PA       10 | )1<br>)2<br>)2<br>)3 |

# LIST OF TABLES

| 2.1 | Performance summary for 100-MHz LTE signal.                                                 | 45 |

|-----|---------------------------------------------------------------------------------------------|----|

| 2.2 | Comparison to state-of-the-art PA MMICs operating near X-band for CW and modulated          |    |

|     | performance (where reported) PART I                                                         | 46 |

| 2.3 | Comparison to state-of-the-art PA MMICs operating near X-band for CW and modulated          |    |

|     | performance (where reported) PART II.                                                       | 47 |

| 3.1 | Summary of switch states for operation across 6-14 GHz                                      | 58 |

| 4.1 | Summary of switch states for operation across nominal center frequencies 20-36 GHz          | 73 |

| 4.2 | Comparison to state-of-the-art broadband, frequency reconfigurable, and efficiency enhanced |    |

|     | K/Ka-band PAs                                                                               | 79 |

| 4.3 | Comparison to state-of-the-art broadband, frequency reconfigurable, and efficiency enhanced |    |

|     | K/Ka-band PAs                                                                               | 80 |

# LIST OF FIGURES

| 1.1 | 16-QAM modulated signal constellation with voltage vector representation showing time-           |   |

|-----|--------------------------------------------------------------------------------------------------|---|

|     | instantaneous package value                                                                      | 2 |

| 1.2 | Simplified block diagram of a standard RF/microwave transmitter architecture                     | 3 |

| 1.3 | (a) 64-QAM ideal transmit constellation, (b) 64-QAM transmit constellation including Gaus-       |   |

|     | sian noise (blue), and (c) 64-QAM transmit constellation with aggregated Gaussian noise          |   |

|     | and AMAM/AMPM distortion of a highly efficient PA model (black).                                 | 4 |

| 1.4 | (a) Theoretical PA efficiency vs output power for different traditional classes of operation.    |   |

|     | (b) Corresponding PDF of normalized 64-QAM signal from Fig. 1.3 output power (dB)                | 5 |

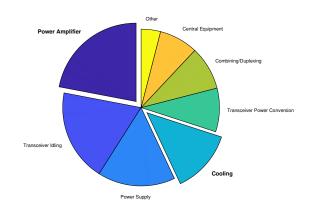

| 1.5 | Pie chart of the power consumption within a typical 4G base-station. Highest power con-          |   |

|     | suming component is the power amplifier itself with a close fourth highest consumer being        |   |

|     | the cooling system for the power amplifier [1]                                                   | 5 |

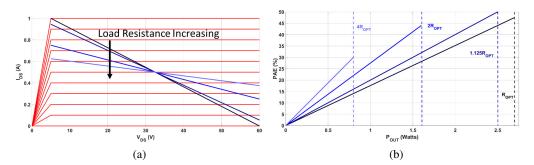

| 1.6 | (a) Load line varying as a function load resistance. (b) Theoretical PAE as a function of        |   |

|     | output power at different load impedance values for an idealized Class A PA. Lighter shades      |   |

|     | correspond to increasing load impedance. shows control of the load line can be used to           |   |

|     | achieve higher efficiencies at a given output power in comparison to controlling $P_{IN}$        | 6 |

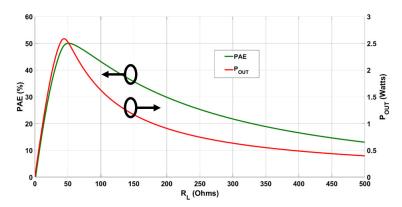

| 1.7 | PAE (left) and $P_{OUT}$ (right) of an idealized class A PA as a function of the load impedance. |   |

|     | Shows that load modulation only works in a specific trajectory (in the ideal case an increasing  |   |

|     | load impedance).                                                                                 | 7 |

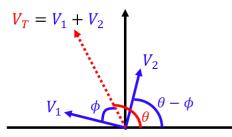

| 1.8  | Vector sum theory of how outphasing power amplifiers store amplitude and phase data.                                   |    |

|------|------------------------------------------------------------------------------------------------------------------------|----|

|      | $V_1 = Ae^{\theta + \phi}$ and $V_2 = Ae^{\theta - \phi}$ where both vectors have a similar constant amplitude and the |    |

|      | outphasing angle $\phi$ is varied between them to control the output amplitude $V_T = 2Ae^{\theta}$ . The              |    |

|      | phase modulation of the input signal is stored in $\theta$ and represents a coordinate system rotation.                | 8  |

| 1.9  | Chireix outphasing combiner block diagram.                                                                             | 9  |

| 1.10 | Chireix outphasing reactance compensation effect. Dashed lines show un-compensated                                     |    |

|      | branch amplifier loading. The solid lines show the branch amplifier loading when using re-                             |    |

|      | actance compensation reducing the average reactance seen by each of the branches across the                            |    |

|      | range of outphasing angles that are being used. Blue corresponds to $Z_1$ and red corresponds                          |    |

|      | to $Z_2$ in Fig. 1.9                                                                                                   | 10 |

| 1.11 | Chireix outphasing combiner branch load contours for an idealized combiner (blue corre-                                |    |

|      | sponds to branch 1 and gray corresponds to branch 2). The dotted red lines show a load                                 |    |

|      | contour plot for an idealized transistor. Sweeping the outphasing angle from $0^{\circ}$ to $360^{\circ}$              |    |

|      | produces two circular load trajectories. Due to the combination of the shape of the load                               |    |

|      | contours for the transistor output power and the combiner load trajectories, a limited output                          |    |

|      | power dynamic range is shown.                                                                                          | 11 |

| 1.12 | Mixed-mode with a shaping function for input power control vs. classical outphasing without                            |    |

|      | input power shaping.                                                                                                   | 11 |

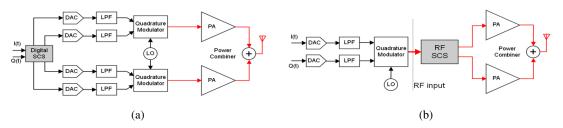

| 2.1  | Outphasing signal decomposition networks in (a) the digital domain and (b) the analog                                  |    |

|      | domain. Reduced complexity by moving signal decomposition network into the analog                                      |    |

|      | domain. Allows the leveraging of RF fractional bandwidth scaling                                                       | 13 |

| 2.2  | Idealized RF input outphasing splitter schematic showing time reversal duality drive to                                |    |

|      | generate a relative phase split from an AMPM signal.                                                                   | 14 |

| 2.3  | Simplified block diagram of the X-band RFIO PA described in this work. The passive                                     |    |

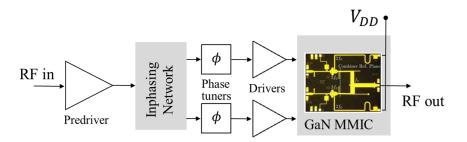

|      | inphasing network provides the required phase signals to drive the outphasing PA MMIC                                  | 16 |

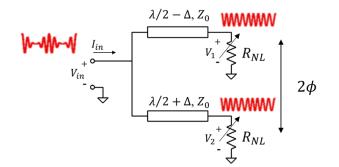

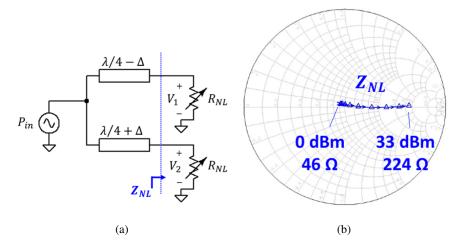

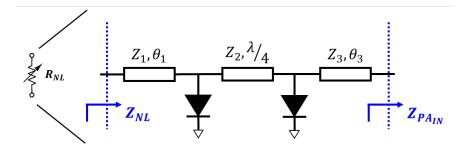

| 2.4  | The inphasing network (a) is based on transmission lines loaded with a non-linear termination.      |    |

|------|-----------------------------------------------------------------------------------------------------|----|

|      | As $R_{NL}$ varies, so does the relative phase of the outputs. Simulated limiter large-signal       |    |

|      | impedance across input power is shown in (b)                                                        | 16 |

| 2.5  | Schematic of the limiter design using PIN diodes. Replaces $R_{NL}$ element in Fig. 2.4             | 17 |

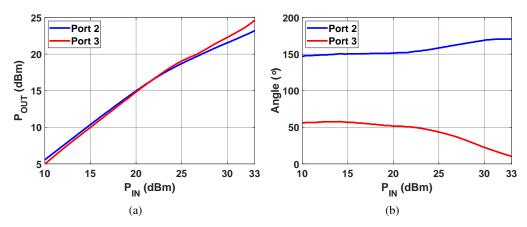

| 2.6  | Simulated performance of the inphasing network, showing the power (a) and relative phase            |    |

|      | (b) of the two output signals                                                                       | 18 |

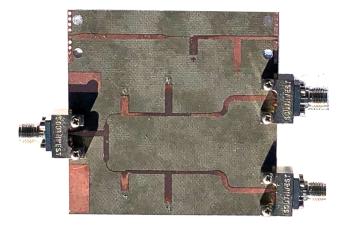

| 2.7  | Photograph of the fabricated X-band inphasing network. The board, including a limiter               |    |

|      | drop-out, measures 60 mm by 59.8 mm                                                                 | 19 |

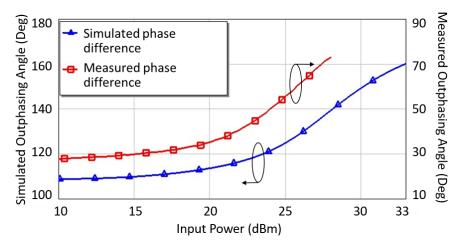

| 2.8  | Measured and simulated outphasing angle produced by the inphasing network. The calibrated           |    |

|      | drive power of the VNA setup is limited to 28 dBm                                                   | 19 |

| 2.9  | Block diagram of the experimental test setup. Driver amplifiers and fixed phase shift tuners        |    |

|      | are included to compensate for non-idealities in the inphasing network                              | 20 |

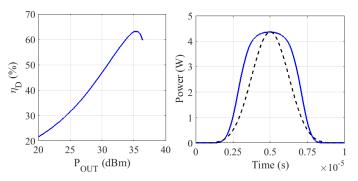

| 2.10 | Measured drain efficiency vs. output power of the outphasing MMIC in the RFIO architecture,         |    |

|      | characterized for the pulse shown at right.                                                         | 21 |

| 2.11 | Mixed-mode outphasing drive schematic for measurements                                              | 21 |

| 2.12 | RFIO drive schematic for measurements                                                               | 21 |

| 2.13 | Measured drain efficiency vs. output power of the outphasing MMIC in the RFIO architecture          |    |

|      | (blue) vs. the same MMIC operated in conventional dual-input mixed-mode outphasing (red),           |    |

|      | with limited variation in PA drive power [2]                                                        | 22 |

| 2.14 | Measured AM/AM and AM/PM characteristics of the RFIO PA, characterized for pulsed                   |    |

|      | measurements                                                                                        | 22 |

| 2.15 | Measured output spectrum for a rectangular RF pulse and for an amplitude-modulated pulse            |    |

|      | with raised-cosine pulse profile. In both cases, the pulse duration is $10\mu$ s and the repetition |    |

|      | period is $100\mu$ s                                                                                | 22 |

| 2.16 | Block diagram of the RFIO PA architecture. Inphasing networks based on three different              |    |

|      | non-linear elements are designed and their performance compared                                     | 24 |

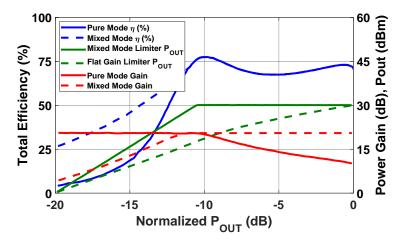

| 2.17 | Classical outphasing drive vs mixed-mode outphasing drive performance, with the branch                   |    |

|------|----------------------------------------------------------------------------------------------------------|----|

|      | amplifiers assumed to be ideal class-B PAs. Ideal limiter performance shown for the ideal                |    |

|      | AM-AM response for mixed-mode operation.                                                                 | 26 |

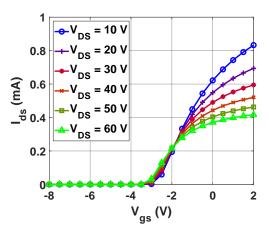

| 2.18 | Simulated $I_{ds}$ vs. $V_{gs}$ curves for the $8x100\mu m$ GaN device used in this design, at different |    |

|      | $V_{ds}$ values                                                                                          | 27 |

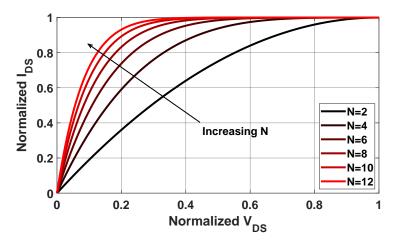

| 2.19 | Analytical model for $I_{DS}$ vs $V_{DS}$ curves given a knee factor (N) and comparing strong            |    |

|      | vs. weak knee effect. A strong knee effect corresponds to a smaller N value and a slower                 |    |

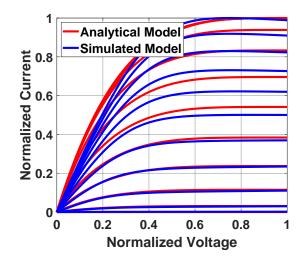

|      | transition into saturation. Reproduced based on [3]                                                      | 28 |

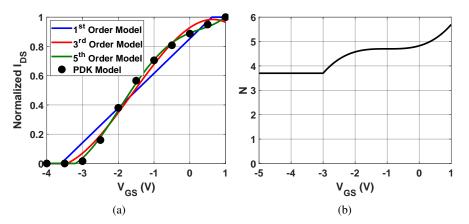

| 2.20 | Proposed analytical model describing the device saturation characteristics. (a) $A(V_{gs})$ func-        |    |

|      | tion modeling transconductance as a polynomial, (b) Variation of N with $V_{gs}$                         | 28 |

| 2.21 | IDS with clipping effect, Daniel model                                                                   | 29 |

| 2.22 | PDK Model IV curve (Blue) vs analytical model IV curve (Red).                                            | 30 |

| 2.23 | Load pull based on analytical model. Ideal outphasing combiner load trajectories (black)                 |    |

|      | overlayed                                                                                                | 31 |

| 2.24 | Ideal signal decomposition based on non-linear model.                                                    | 31 |

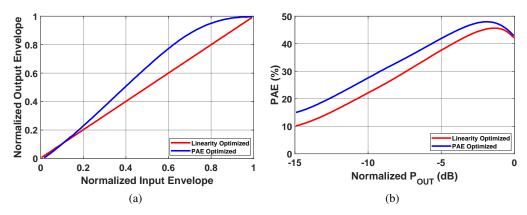

| 2.25 | Normalized (a) output power and (b) efficiency of the outphasing output stage for the linearity  |    |

|------|--------------------------------------------------------------------------------------------------|----|

|      | and efficiency optimized signal decompositions.                                                  | 32 |

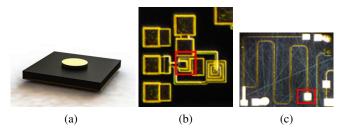

| 2.26 | The three non-linear components used for inphasing signal separation: (a) PIN diode MA-          |    |

|      | COM MA4L101-134, (b) diode-connected GaN HEMT in Wolfspeed 250 nm GaN process.                   |    |

|      | The transistor is single 150 um finger shown in the red box. The surrounding circuitry is        |    |

|      | a bias tee to enable active biasing of the diode.(c) mesa resistor with on-chip pre-matching     |    |

|      | network in the Qorvo GaN 150 nm ES process. The resistor is a 35 $\mu$ m x 15 $\mu$ m equivalent |    |

|      | to $175 \Omega$ shown in the red box.                                                            | 33 |

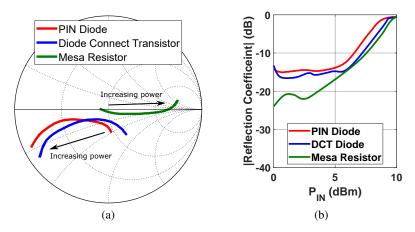

| 2.27 | Simulated power-dependent impedance of the three non-linear elements as the applied power        |    |

|      | is swept from 0–10 dBm. (a) Smith chart showing large-signal impedance at the fundamental        |    |

|      | frequency; (b) Magnitude of fundamental-frequency reflection coefficient vs. applied power       |    |

|      | from large-signal simulation.                                                                    | 33 |

| 2.28 | Summary of the inphasing network based on the PIN diode: (a) schematic, (b) simulated            |    |

|      | and measured outphasing angle and (c) normalized power delivered to the two ports. $\ldots$      | 34 |

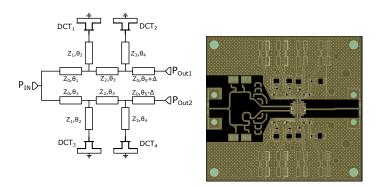

| 2.29 | Summary of the inphasing network based on the diode-connected HEMT: (a) schematic, (b)           |    |

|      | simulated and measured outphasing angle and (c) power delivered to the two ports. $\ldots$       | 36 |

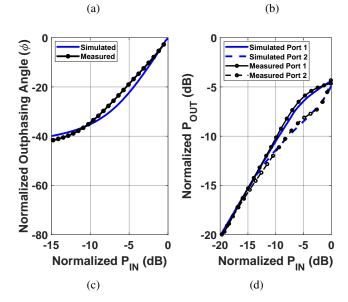

| 2.30 | Summary of the inphasing network based on the non-linear mesa resistor: (a) schematic, (b)       |    |

|      | simulated and measured outphasing angle and (c) power delivered to the two ports. $\ldots$ .     | 38 |

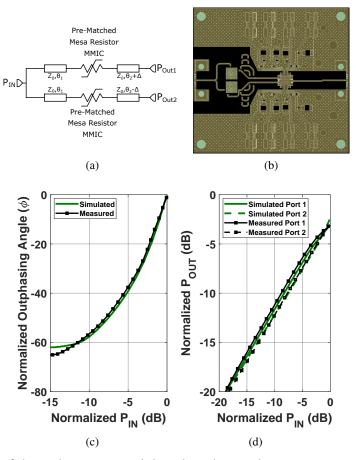

| 2.31 | Summary of the measured inphasing characteristics for the three non-linear designs, com-         |    |

|      | pared to the linearity and efficiency optimized transfer functions                               | 38 |

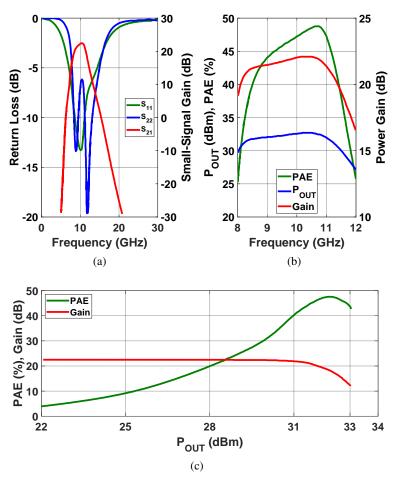

| 2.32 | Simulated performance of the two-stage branch PAs. (a) – S-parameters, (b) – large-signal        |    |

|      | performance, (c) – driveup.                                                                      | 40 |

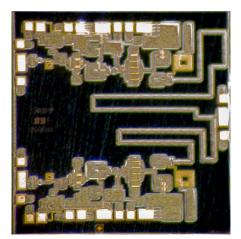

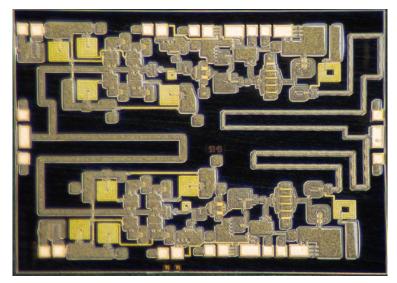

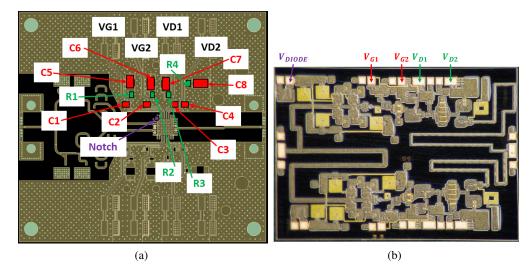

| 2.33 | Die photograph. The total die area is $2.5 \text{ mm} \times 2.3 \text{ mm}$                     | 41 |

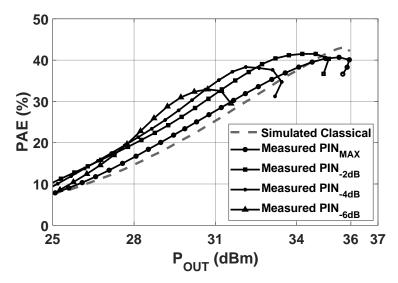

| 2.34 | Simulation and CW measurements of the dual-input outphasing MMIC operated in pure-               |    |

|      | mode outphasing at 10 GHz. Mixed mode outphasing curves for measured dual-input out-             |    |

|      | phasing MMIC in 2 dB input power steps.                                                          | 42 |

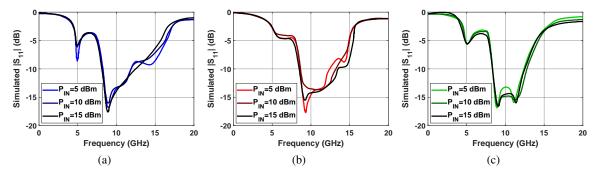

| 2.35 | Simulated power-dependent input reflection coefficient at 3 different input drive levels with      |    |

|------|----------------------------------------------------------------------------------------------------|----|

|      | darker shades as input drive increases for the three different splitter board implementations.     |    |

|      | (a) DCT diode is shown in blue shades (b) PIN diode is shown in red shades (c) Mesa resistor       |    |

|      | is shown in green shades.                                                                          | 42 |

| 2.36 | Measured and simulated CW performance of the RFIO PA comparing the three different                 |    |

|      | inphasing networks based on the diode-connected transistor (DCT), PIN diode, and mesa              |    |

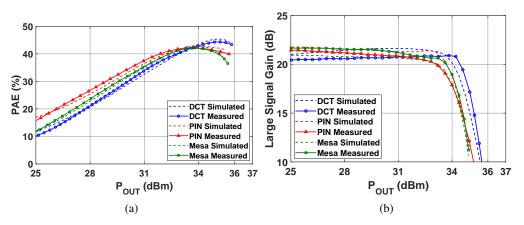

|      | resistor. (a) measured PAE vs output power, (b) measured gain vs. output power                     | 43 |

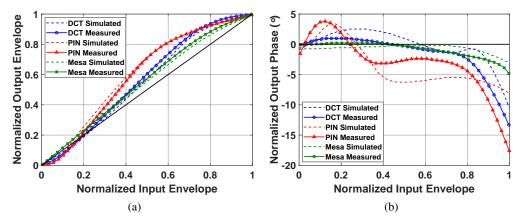

| 2.37 | RFIO: Measured and simulated (a) AMAM and (b) AMPM for the three different splitters.              | 43 |

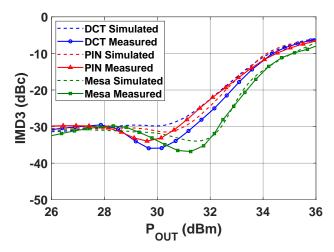

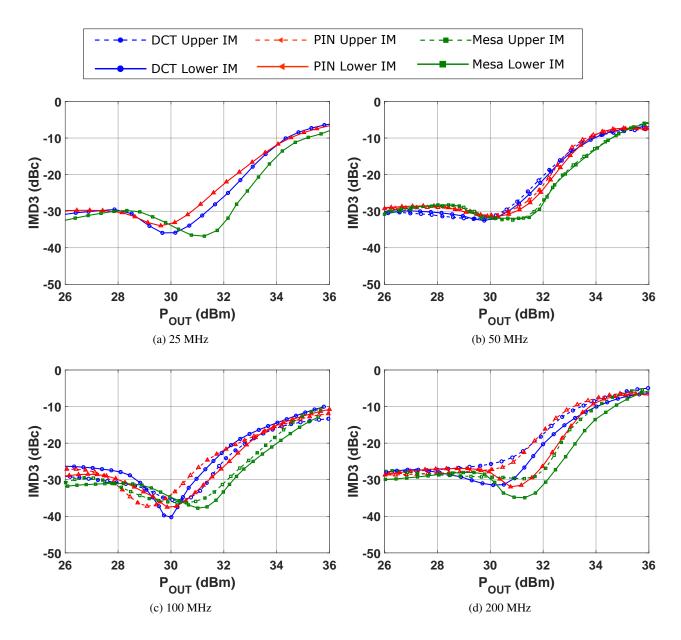

| 2.38 | IMD3 measurements vs simulation for a 25 MHz tone spacing and averaged power. Upper                |    |

|      | tones shown, however, no memory effects are present at this tone spacing                           | 44 |

| 2.39 | Measured IMD3 response of the three RFIO PAs for two-tone excitation centered at 10 GHz,           |    |

|      | with 25, 50, 100, and 200 MHz frequency spacings.                                                  | 45 |

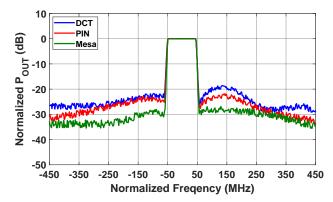

| 2.40 | Comparison of the three RFIO PAs when characterized with a 100-MHz LTE signal with an              |    |

|      | 8.9 dB output PAPR. Each spectrum plot is normalized to its peak output power                      | 46 |

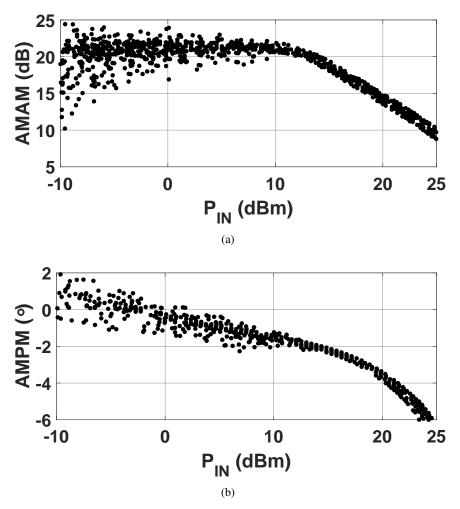

| 2.41 | Dynamic AMAM and AMPM measurements of the mesa resistor RFIO PA with 100-MHz                       |    |

|      | LTE signal.                                                                                        | 48 |

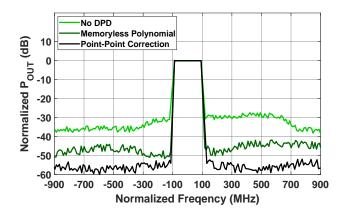

| 2.42 | Measurements of the RFIO PA with mesa resistor inphasing network driven by a 200-MHz               |    |

|      | LTE signal, without DPD (light green), with point-by-point DPD (black), and with a $6^{th}$ -order |    |

|      | memoryless polynomial DPD (dark green).                                                            | 48 |

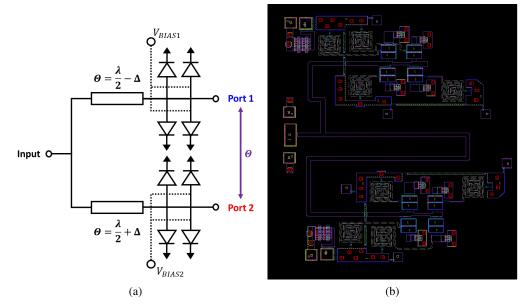

| 2.43 | RFIO splitter (a) schematic and (b) layout designed in Qorvo 150 nm GaN es process                 | 49 |

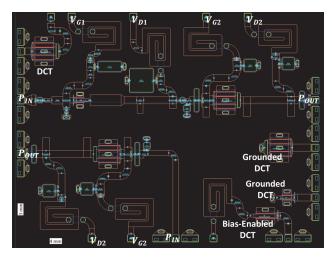

| 2.44 | RFIO MMIC die photo in Qorvo GaN 150 nm es process. Die is 3.5 mm x 2.3 mm. The                    |    |

|      | outphasing PA is identical to the design shown in the previous section                             | 49 |

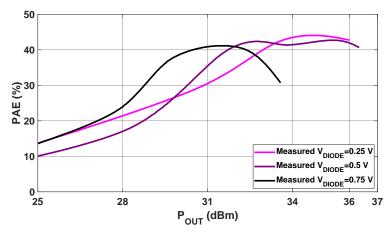

| 2.45 | Measured RFIO MMIC performance PAE vs $P_{OUT}$ for different bias states for the diodes in        |    |

|      | the inphasing splitter. Both branches have similar applied biases for this measurement             | 50 |

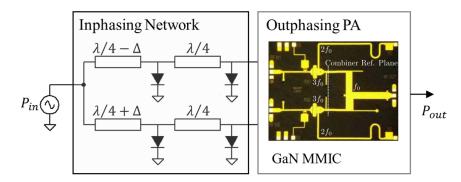

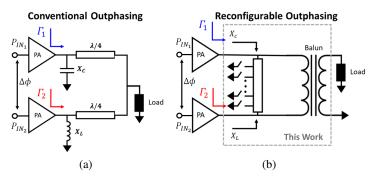

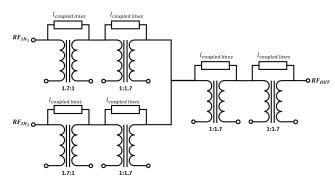

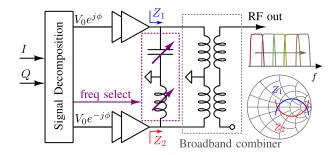

| 3.1  | (a) Conventional narrowband outphasing structure. (b) Simplified schematic of the recon-      |    |

|------|-----------------------------------------------------------------------------------------------|----|

|      | figurable outphasing combining network. An octave-bandwidth balun provides single-ended       |    |

|      | to floating load conversion, while a transmission line with shunt switches provides reconfig- |    |

|      | urable shunt compensating reactances $X_C$ and $X_L$                                          | 53 |

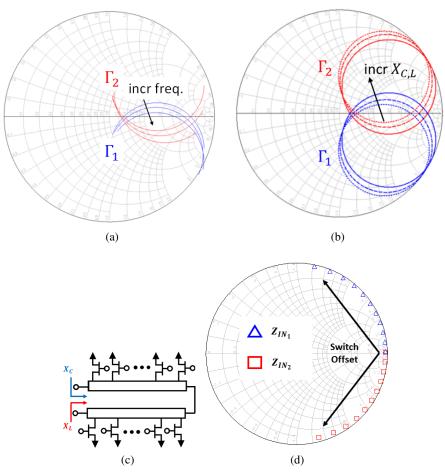

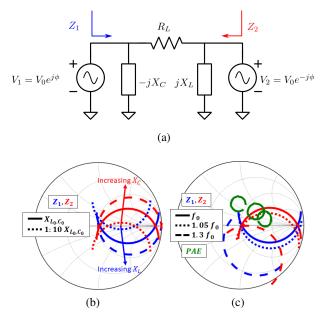

| 3.2  | Reconfigurable outphasing combiner operation: (a) conventional outphasing combiner input      |    |

|      | impedances as reactance varies; (b) frequency-dependence (20% total increase in frequency)    |    |

|      | of outphasing input impedance trajectories for a conventional network; (c) sketch of half-    |    |

|      | wavelength transmission line with shunt switches (reduced number shown for clarity); (d)      |    |

|      | complex-conjugate input impedances to the line when a single switch is turned on (starting    |    |

|      | from the center and moving towards one side)                                                  | 54 |

| 3.3  | Standard broadside-coupled transformer cross-section (a) and modified transformer cross-      |    |

|      | section (b).                                                                                  | 55 |

| 3.4  | Circuit diagram of the overall transformer based combining structure.                         | 56 |

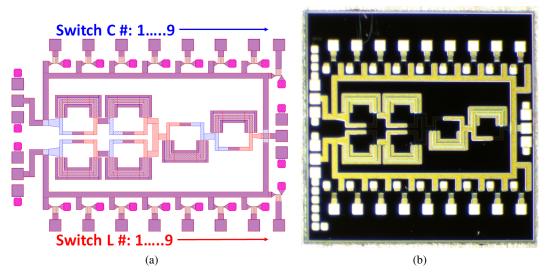

| 3.5  | Layout and photograph of the 2.5 mm x 2 mm 250-nm Qorvo GaAs MMIC prototype                   | 56 |

| 3.6  | Photograph of the experimental break-out board used to characterize the outphasing combiner   |    |

|      | MMIC                                                                                          | 57 |

| 3.7  | Simplified schematic of the simulation test-bench used to determine the port input impedance  |    |

|      | trajectories as a function of outphasing angle based on measured 3-port S-parameter data      | 58 |

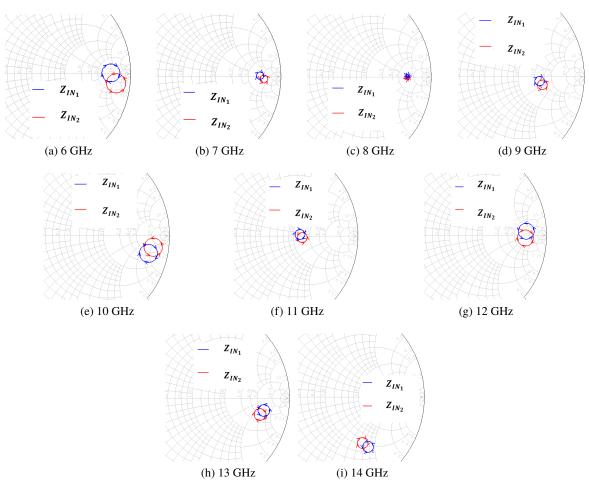

| 3.8  | Measured results summary showing the combiner input impedance trajectories as outphasing      |    |

|      | angle is swept                                                                                | 59 |

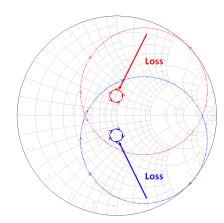

| 3.9  | Simulated effect of circuit loss on input trajectories, comparing ideal lossless outphasing   |    |

|      | contours (dashed) to the outphasing contours with 10 dB of loss (solid).                      | 59 |

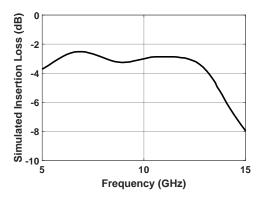

| 3.10 | ) EM simulated insertion loss of breakout board including connector loss. Loss is aggregated  |    |

|      | for both the input and output.                                                                | 60 |

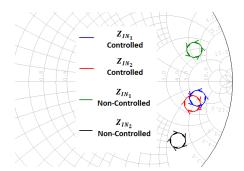

| 3.11 | Measured outphasing contours at 13 GHz with switch reconfiguration (blue and red) com-        |    |

|      | pared to without switch reconfiguration (green and black) for port 1 (blue and green) and 2   |    |

|      | (red and black) respectively. Similar behavior is observed at other frequencies               | 60 |

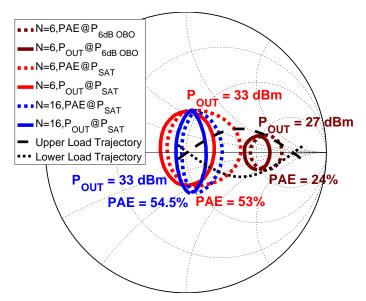

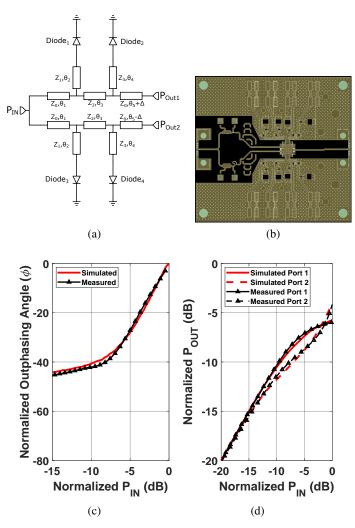

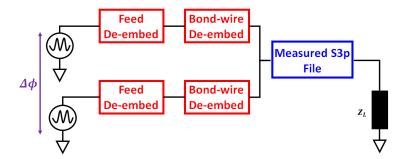

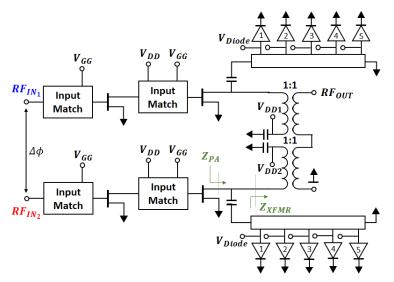

| 4.1 | Overview block diagram of the frequency-reconfigurable Chireix outphasing architecture              | 62 |

|-----|-----------------------------------------------------------------------------------------------------|----|

| 4.2 | Conceptual operation of the Chireix outphasing PA. (a) Simplified schematic. (b) Load               |    |

|     | trajectory control through manipulation of shunt reactances $X_L$ and $X_C$ , showing a decade      |    |

|     | increase in the shunt reactances from their nominal values. (c) Load trajectory degradation         |    |

|     | for an ideal Chireix outphasing combiner when frequency is deviates by $5\%$ and $30\%$ from        |    |

|     | the nominal design frequency, compared to simulated PAE impedance targets based on the              |    |

|     | MMIC device.                                                                                        | 64 |

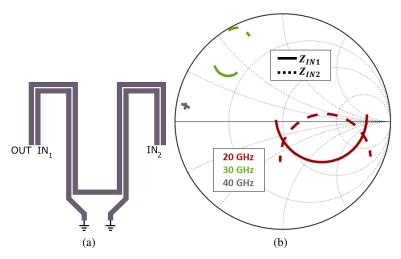

| 4.3 | Simulated combiner response for edge coupled (capacitive-mode) combiner based on EM                 |    |

|     | extraction. (a) Combiner layout and port definitions. (b) Simulated outphasing operation            |    |

|     | across frequency when port 3 is is loaded with 50 $\Omega$ and ports 1 (IN1) and 2 (IN2) are driven |    |

|     | with equal amplitude and swept relative phase                                                       | 67 |

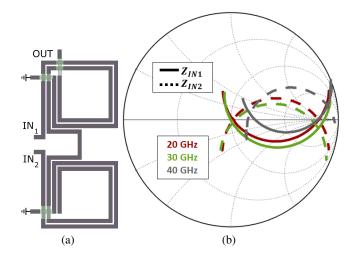

| 4.4 | Simulated combiner response for implementation of spiral edge coupled (partially inductive          |    |

|     | mode) combiner. (a) Combiner layout and port definitions. (b) Simulated outphasing                  |    |

|     | operation across frequency when port 3 is loaded with 50 $\Omega$ and ports 1 (IN1) and 2 (IN2)     |    |

|     | are driven with equal amplitude and swept relative phase                                            | 67 |

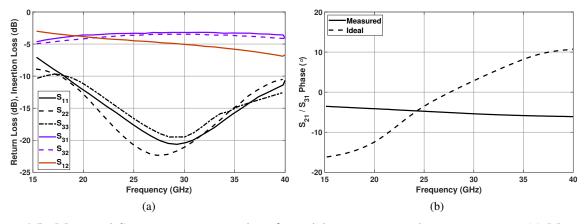

| 4.5 | Measured S-parameter magnitudes of standalone power combining structure. (a) Measured               |    |

|     | magnitude response. (b) Measured phase response, compared to ideal transmission phase               |    |

|     | based on simulated load-pull of the device. The negative phase shift with frequency of the          |    |

|     | physical transformer is compensated for using the shunt reactive elements                           | 69 |

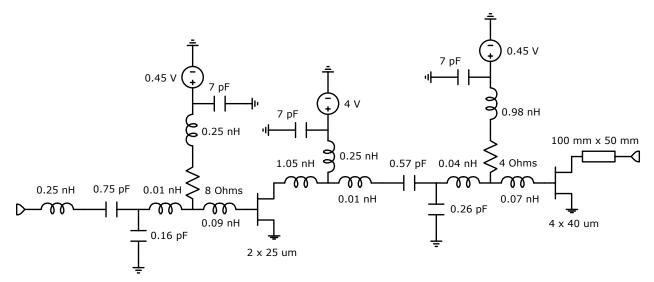

| 4.6 | Simplified circuit schematic of branch amplifier layout with component values. Input and            |    |

|     | interstage matching network designed to maximize operation across entire reconfigureable            |    |

|     | bandwidth while remaining stable.                                                                   | 71 |

| 4.7 | Simplified circuit schematic of the frequency-reconfigurable outphasing PA MMIC. The                |    |

|     | diode switches are numbered as shown.                                                               | 71 |

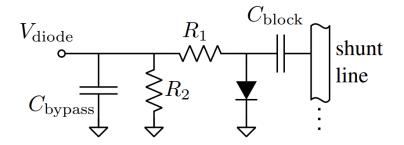

| 4.8 | Details of the switched-reactance element bias structure.                                           | 72 |

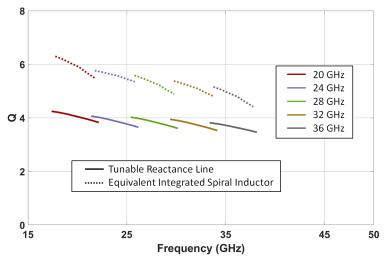

| 4.9 Simulated quality factor of the shunt inductive stub when the appropriate switch correspond-                 |

|------------------------------------------------------------------------------------------------------------------|

| ing to each frequency range is selected (solid lines). Shown for comparison is the Q of a fixed                  |

| integrated spiral inductor (2 nH) in this process having the same reactance value (dashed lines). 72             |

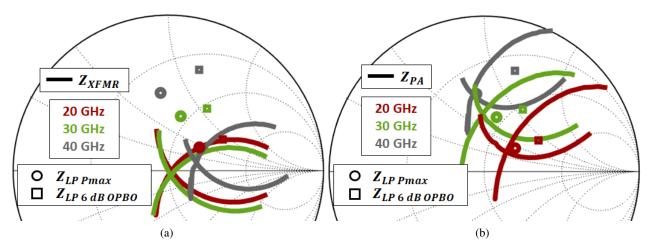

| 4.10 Simulated target impedances for highest PAE at peak power ( $Z_{LP Pmax}$ ) and 6-dB back-                  |

| off ( $Z_{LP \ 6dBOPBO}$ ) across frequency at reference plan $Z_{PA}$ Fig. 4.7. (a) Simulated input             |

| impedances to the combiner shown at the transformer plane $Z_{XFMR}$ . (b) Impedance trajec-                     |

| tories at $Z_{PA}$ after compensation by the shunt elements                                                      |

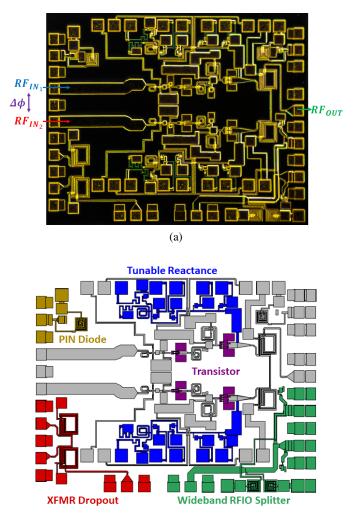

| 4.11 Completed design of the MMIC, with overall dimensions $2.5 \text{ mm x} 2 \text{ mm}$ . (a) Die photograph. |

| (b) Annotated layout diagram                                                                                     |

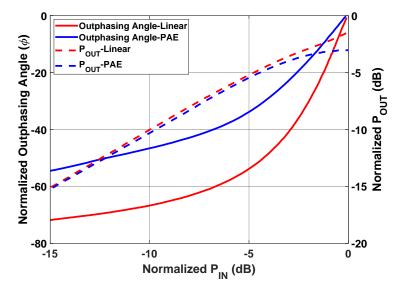

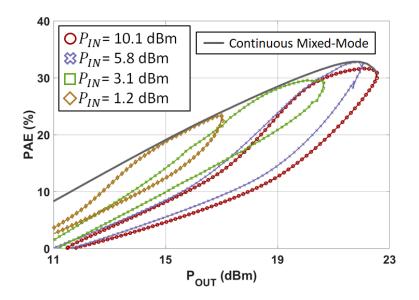

| 4.12 Outphasing performance curves at discrete input power levels, measured in CW at 28 GHz.                     |

| The input power and phase corresponding to the highest PAE is determined, and then a                             |

| function fit to determine the mixed-mode signal decomposition                                                    |

| 4.13 Empirically determined amplitude and phase signal separation for CW measurements, based                     |

| on the measurements shown in Fig. 4.12                                                                           |

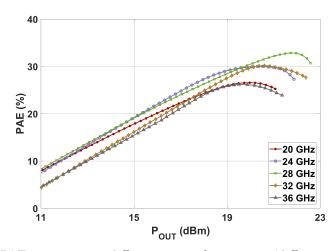

| 4.14 Measured PAE vs. $P_{OUT}$ at different center frequencies (different switch state configurations           |

| denoted by different color traces). In this and subsequent measurement plots, every 2nd                          |

| measurement point is indicated with a marker                                                                     |

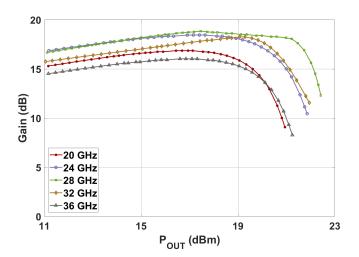

| 4.15 Measured gain vs. $P_{OUT}$ at different center frequencies(different switch state configurations           |

| denoted by different color traces)                                                                               |

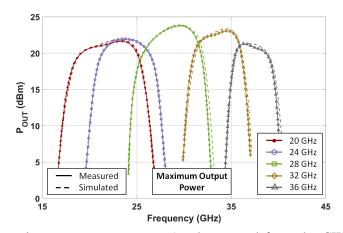

| 4.16 Measured peak output power, $P_{MAX}$ (as determined from the CW center-frequency mea-                      |

| surements in Fig. 4.14), measured across frequency for different center frequencies (different                   |

| switch state configurations denoted by different color traces)                                                   |

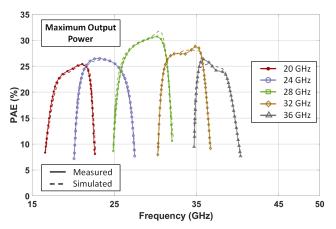

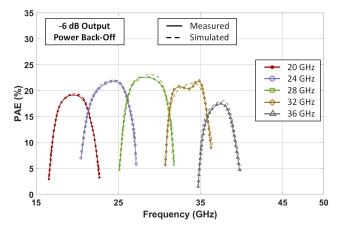

| 4.17 Measured (solid line) and simulated (dashed line) PAE at $P_{MAX}$ across frequency for different           |

| center frequencies (different switch state configurations denoted by different colors) 78                        |

| 4.18 Measured (solid line) and simulated (dashed line) PAE at $P_{MAX}$ – 6 dB across frequency for              |

| different center frequencies (different switch state configurations denoted by different colors). 78             |

xviii

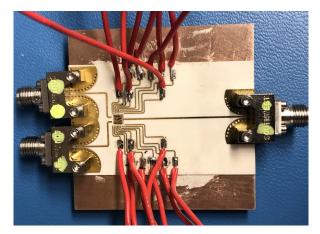

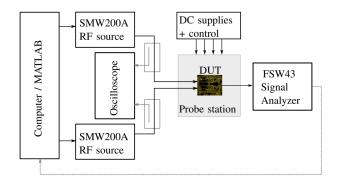

| 4.19 | Experimental testbench used to characterize the frequency-reconfigurable outphasing MMIC      |

|------|-----------------------------------------------------------------------------------------------|

|      | for modulated signals. (a) Block diagram of the setup. (b) Photograph (probe station, located |

|      | at front right, not shown).                                                                   |

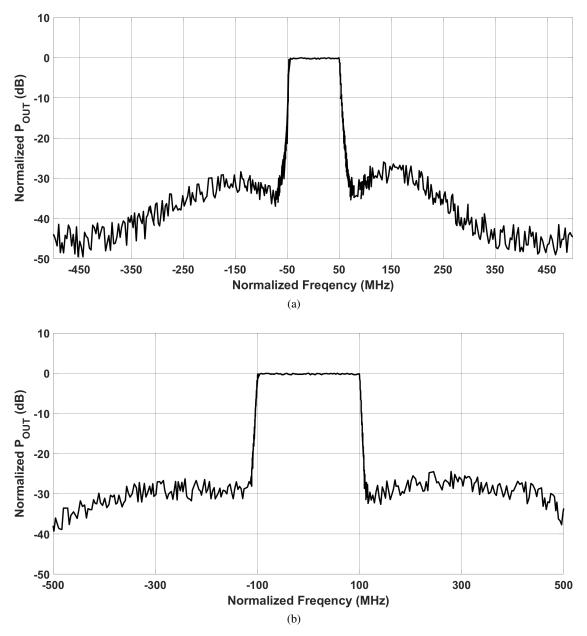

| 4.20 | Modulated performance of the PA using mixed-mode signal decomposition centered at             |

|      | 19.5 GHz. (a) Measured 100-MHz LTE signal with 7.3 dB PAPR, average output power              |

|      | 14.3 dBm, average efficiency 15.4%, and ACLR 25.22 dBc. (b) Measured 200-MHz LTE              |

|      | signal with 7.3 dB PAPR, average output power 14.3 dBm, average efficiency 15.3%, and         |

|      | ACLR 24.18 dBc                                                                                |

| B.1  | X-Band inverse class-F PA diagram for bias and mounting setup [4]                             |

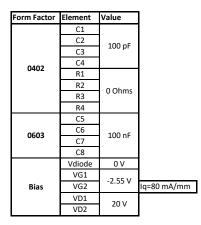

| B.2  | Measurement diagram for (a) the RFIO splitter PCBs for hybrid implementation and (b) the      |

|      | RFIO MMIC in the case of probing and/or mounting                                              |

| B.3  | Table showing component and bias values for the RFIO PA implementations using the             |

|      | diagrams found in Fig. B.2                                                                    |

## Chapter 1

# INTRODUCTION

Maintaining high power amplifier (PA) efficiency for wide dynamic range signals is becoming increasingly critical in many applications including RADAR systems with enhanced spectral confinement and next generation high speed communication systems. The increased signal requirements on both PAPR as well as instantaneous operating bandwidth are driving factors in modern PA design. Moving towards active phased array system implementations for both high-speed communications and telemetry applications from single antenna designs has redefined current integration and module design challenges due to spatial design constraint driven by fundamental wavelength.

### 1.1 BACKGROUND AND MOTIVATION

The proliferation of RF/microwave wireless technology for the use of telemetry and communications has exploded in the last decade. The expansion of automotive RADAR into the standard vehicle safety technology offerings and the continuing advancement of wireless communication standards for high speed data transmission has lead to an increase in demand for active phased array system design. The increasing demands on the wireless infrastructure for increased transmission speeds and reduced latency presents new RF and microwave design problems and challenges [5].

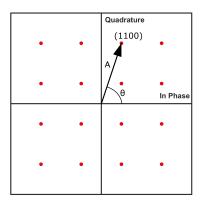

Figure 1.1: 16-QAM modulated signal constellation with voltage vector representation showing timeinstantaneous package value.

#### 1.1.1 DATA TRANSMISSION

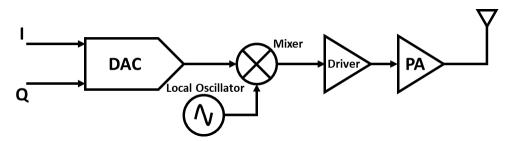

Wireless data transmission has continued to evolve as use cases become more complex over time. More recently, spectrum is difficult to obtain leading to requirements for high spectral efficiency of modulation schemes in next generation communication standards. There are many different forms of signal modulation schemes in order to encode digital data into symbols. A symbol is defined as a magnitude (A) and a phase  $(\theta)$  that represents a string of bits as shown in Fig. 1.1 represented by red dots. The two most common forms of signal modulation include phase shift keys (PSK) and quadrature amplitude modulation (QAM). PSK modulation schemes are a special case of QAM schemes which encode data by setting the magnitude (A) to a constant value and varying the phase ( $\theta$ ) value. This style of data encoding allows for optimal operation out of a traditional PA where it is necessary to operate at maximum output power in order achieve the highest possible power efficiency. PSK modulation schemes are spectrally inefficient, especially when compared to full QAM modulation schemes. Higher-order QAM modulation schemes are highly spectrally efficient and are commonly used for the high data rate communication standards such as 4G LTE and the future 5G standard. QAM achieves high spectral efficiency through utilization of both amplitude and phase to encode information allowing for longer bit streams per symbol for a similar bandwidth. This increases the number of discrete amplitude and phase levels that are passed through the amplifier increasing the complexity for the transmitter path, especially the PA (shown in the transmit chain in Fig. 1.2), when attempting to make

Figure 1.2: Simplified block diagram of a standard RF/microwave transmitter architecture.

the system efficient due to the requirement for higher symbol accuracy (directly related to PA linearity performance).

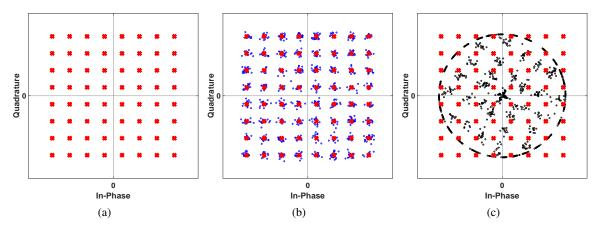

PAs operate at a significantly reduced linearity when operating at higher power levels. The PAs create both amplitude and phase distortion referred to as AMAM and AMPM distortion respectively. These effects are input drive dependent for the power amplifier and are created through the intrinsic device current-voltage relationship. As the device starts reach current and voltage limits, the current and voltage waveforms begin to clip generating a non-linear AMAM characteristic. The closer to saturation a PA is being operated, the stronger the AMAM characteristics are. In addition to AMAM characteristics, AMPM characteristics are also observed in power amplifiers. AMPM typically occurs due to non-linear device capacitances that are modulated due bias modulation effects and overall drive level. These effects combine to create problems for the overall linearity and symbol integrity of the transmit chain. Fig. 1.3 shows the symbol integrity reduction due to major non-linear transmit chain contributions, specifically aggregated Gaussian noise and PA AMAM/AMPM effects, in Fig. 1.3 (c).

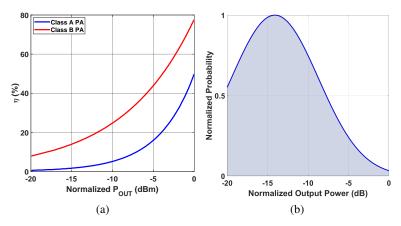

The relationship between the efficiency of a power amplifier in two traditional modes of operation and its output power is shown in Fig. 1.4a. There is a steep drop-off in efficiency ( $\eta$ ) as the output power of the PA is backed-off through reducing input drive. The lower efficiency is due to the reduction of output power ( $P_{OUT}$ ) while at any given point the same amount of DC power is being consumed:

$$\eta = \frac{P_{OUT}}{P_{DC}} \tag{1.1}$$

When combining the reduced power efficiency shown in Fig. 1.4a with a 64-QAM LTE modulation scheme in Fig. 1.3b and Fig. 1.4b it is apparent that even though the traditional classes of PAs can exhibit high

Figure 1.3: (a) 64-QAM ideal transmit constellation, (b) 64-QAM transmit constellation including Gaussian noise (blue), and (c) 64-QAM transmit constellation with aggregated Gaussian noise and AMAM/AMPM distortion of a highly efficient PA model (black).

theoretical efficiency, the average efficiency when operating under higher order QAM (subsequently large PAPR) signals will be poor. Power amplifier average efficiency is a major factor on the overall transmitter and base station efficiency as shown in Fig. 1.5. The PA and the equipment used to keep the PA cool account for up to 50% of the total power consumption of a 4G LTE base station [1]. Improving the average efficiency of the PA for a given modulated signal can heavily reduce the total DC power consumption not only allowing for reduced operating costs, but reducing the carbon footprint of each base station. This provides for a double reduction in DC power since improving power efficiency of the PA reduces DC power consumption of the PA itself as well as the cooling system due to reduced heat dissipation inside the PA. These large dynamic range signals require high peak efficiency out of an amplifier and the ability for it to operate at high efficiencies across a wide range of output power back-off (OBO).

## 1.2 LOAD MODULATION

Traditional power amplifiers control output power as a function of input power  $P_{OUT}(P_{IN})$  [6]. This gives linear control of the output power since an ideal linear PA can be modeled as a simple gain block  $P_{OUT} = AP_{IN}$  where A is the power gain of the amplifier. Power amplifiers designed this way can operate with a high efficiency at a specific output power point. All other output power points will suffer a degradation

Figure 1.4: (a) Theoretical PA efficiency vs output power for different traditional classes of operation. (b) Corresponding PDF of normalized 64-QAM signal from Fig. 1.3 output power (dB).

Figure 1.5: Pie chart of the power consumption within a typical 4G base-station. Highest power consuming component is the power amplifier itself with a close fourth highest consumer being the cooling system for the power amplifier [1].

in efficiency due to reduced output power (which corresponds to reduced load line utilization) and constant DC power consumption. Another method for output power control is needed in order to improve the efficiency at lower output power levels. Fig. 1.6a shows how the effective load line can be controlled through increasing load resistance (corresponds to lighter shades). The output power of an idealized linear PA can be written as:

$$P_{OUT} = \frac{V_o^2}{R_L} \tag{1.2}$$

where  $V_o$  is the fundamental component of the voltage across the output load. In controlling the output power with  $P_{IN}$  the  $V_o$  is effectively being modulated. The output power is also a function of  $R_L$ . By

Figure 1.6: (a) Load line varying as a function load resistance. (b) Theoretical PAE as a function of output power at different load impedance values for an idealized Class A PA. Lighter shades correspond to increasing load impedance. shows control of the load line can be used to achieve higher efficiencies at a given output power in comparison to controlling  $P_{IN}$ .

varying the effective load resistance at the output of the PA the output power can be controlled. The benefit to this technique is that while the output power is being reduced you are optimizing the voltage swing of the system by an inverse relationship of  $P_{OUT}$  and  $R_L$  as shown in Fig. 1.6b. By fixing  $R_L$  and reducing the input power to reduce output power, the efficiency of the PA is significantly reduced when compared to actively manipulating the load as the output power is reduced. This technique is called load modulation and is commonly used to improve the average efficiency of PA's for large peak to average power ratio (PAPR) signals [6].

An important consideration when utilizing load modulation as a technique for improved back-off efficiency is the trajectory of load modulation. Trajectory refers to the direction the load varies as a function of output power. In the idealized case this is limited to the single dimension of the real component of the complex impedance plane. In the case of a real transistor the optimal load modulation trajectory can be obtained through load pulling the transistor and exists as a vector in the complex impedance plane. Fig. 1.7 shows the idealized case of a load modulation trajectory [7]. The peak power added efficiency (PAE) of the PA is located at 50 ohms and the peak output power is located at 45 ohms. As you increase the load resistance the output power falls off faster than the PAE. This maintains efficiency even as the output power is reduced. If the load resistance is reduced instead of increased from the peak output power and PAE points the PAE reduces at a faster rate than the output power. This provides a poor efficiency performance at reduced output power levels. This effect is even more important to consider when dealing with a real transistor whose load

Figure 1.7: PAE (left) and  $P_{OUT}$  (right) of an idealized class A PA as a function of the load impedance. Shows that load modulation only works in a specific trajectory (in the ideal case an increasing load impedance).

modulation trajectory will be a complex vector due to the non-linear parasitic output and input capacitances of the device. [8].

Load modulation is a heavily implemented technique for improved average efficiency of PA's when operating under large PAPR signals. The PA architectures that utilize the technique can be found from handsets to base stations. Typical architectures include Doherty [9], envelope tracking [10], and LMBA [11]. This thesis will focus on a another form of load modulation architecture known as outphasing [12].

### 1.3 Outphasing

Outphasing is a load modulation PA architecture that was initially published by H. Chireix in 1935 [13]. The architecture utilizes load modulation for output power control. This allows the architecture to be constantly operating the PAs in saturation (maximum load line swing) and therefore at peak efficiency. This is accomplished by completing a vector decomposition. A single RF amplitude modulated (AM) and phase modulated (PM) signal is deconstructed into two constant envelope phase modulated signals:

$$A_{IN}(t) = A(t)cos(\theta(t))$$

(1.3)

$$A_{IN}(t) = \frac{A_{MAX}}{2} \cos(\theta(t) + \phi(t)) + \frac{A_{MAX}}{2} \cos(\theta(t) - \phi(t))$$

(1.4)

The amplitude data of the original signal is stored in the relative phase shift between the two vectors  $2\phi$  and the original phase data is maintained in  $\theta$  which represents a rotation of the vector coordinate

Figure 1.8: Vector sum theory of how outphasing power amplifiers store amplitude and phase data.  $V_1 = Ae^{\theta+\phi}$  and  $V_2 = Ae^{\theta-\phi}$  where both vectors have a similar constant amplitude and the outphasing angle  $\phi$  is varied between them to control the output amplitude  $V_T = 2Ae^{\theta}$ . The phase modulation of the input signal is stored in  $\theta$  and represents a coordinate system rotation.

space. These constant amplitude phase modulated signals are passed through two separate power amplifiers which are amplified and then recombined at the output through a vector sum operation. The in-phase components are added together and output and the out-of-phase components are subtracted and dissipated. This specific implementation of outphasing, which requires an isolated power combining network, is called linear amplification using non-linear components (LINC). Because the two signals going through each of the branch PA's are utilizing a constant amplitude, AMAM linearity of the branch PA isn't theoretically important due to the amplitude data being stored in the relative phase shift.

The isolating power combiner acts as the vector sum operation required to extract the original AM and PM signal at the output of the combiner. The two signals coming out of the two PA branches are:

$$A_{1}(t) = \frac{A_{MAX}}{2} \cos(\theta(t) + \phi(t)) \text{ and } A_{2}(t) = \frac{A_{MAX}}{2} \cos(\theta(t) - \phi(t))$$

(1.5)

$$A_{OUT} = A_{MAX} cos(\theta(t)) cos(\phi(t)) \text{ and } i_{diss} = -\frac{A_{MAX}}{Z_0} sin(\theta(t)) sin(\phi(t))$$

(1.6)

where  $i_{diss}$  is the current through the isolation resistor of a classic Wilkinson combiner. Therefore the dissipated power through the isolation resistor is:

$$P_{diss} = 2i_{diss}^2 Z_0 \tag{1.7}$$

Due to the dissipated power, which is quite large at lower power levels (larger relative phase shift), the PAE of a LINC PA as a function of output power is actually worse than that of a Class B PA and similar to that of a Class A PA. For this reason, a non-isolating power combiner is the standard implementation

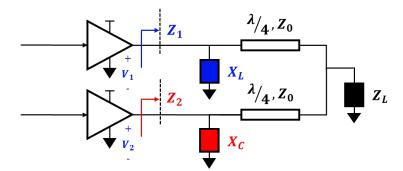

Figure 1.9: Chireix outphasing combiner block diagram.

when utilizing the outphasing architecture. The non-isolating power combiner still allows for a vector sum operation while not dissipating the out-of-phase vector components. The traditional non-isolating outphasing power combiner is the Chireix outphasing combiner.

#### 1.3.1 CHIREIX OUTPHASING

Chireix outphasing is an implementation of the outphasing PA architecture which uses a non-isolating power combiner. This allows the architecture to take advantage of the improved efficiency that the branch amplifiers see in OBO operating regions without dissipating the out-of-phase vector components into an isolation resistor. The non-isolating combiner allows for the branch amplifiers to load each other allowing for a load modulation operating mode. This topology is shown in Fig. 1.9. The load impedances seen by each of the branch PA's is a function of the outphasing angle:

$$Z_1 = \frac{Z_L}{2} (1 - j \cot(\phi))$$

(1.8)

$$Z_2 = \frac{Z_L}{2} (1 + j \cot(\phi))$$

(1.9)

When two PA's are combined in a non-isolating power combiner the PA's will reactively load each other. One branch PA will see an inductive load while the other branch PA will see a capacitive load. The magnitude of the reactive mismatch is a function of the outphsaing angle (phase offset) between the two branches. When sweeping the relative phase between the two branch PA's between 0° and 180° the two branch PA's are only resistively matched at maximum power and at zero output power. There are also massive reactive impedance

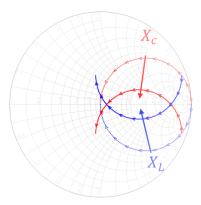

Figure 1.10: Chireix outphasing reactance compensation effect. Dashed lines show un-compensated branch amplifier loading. The solid lines show the branch amplifier loading when using reactance compensation reducing the average reactance seen by each of the branches across the range of outphasing angles that are being used. Blue corresponds to  $Z_1$  and red corresponds to  $Z_2$  in Fig. 1.9.

swings on both branches shown in Fig. 1.10 with the dashed lines. Shunt reactances are added to each of the input ports of the combiner which shifts the load contours towards the real axis of the smith chart. This allows for a resistive match at two outphasing angles (output power levels). These compensatory reactances are shown as  $X_C$  and  $X_L$  in Fig. 1.9. This allows for a reduced impedance range that the branch amplifiers see both resistive and reactive. The more compensation added allows the curves to move closer to the real axis of the smith chart. The trade-off is as the load contours move closer together the dynamic range of the outphasing PA reduces. The ratio of the the impedance of the first real axis crossing to the second real axis crossing determines the dynamic range of the outphasing PA. This means that a Chireix outphasing PA will start to degrade as relative output power levels reach <-12 dB from max. when attempting to make zero output power the outphasing PA must use two maximum power signals and perfectly cancel the two signals out. This is an extremely inefficient method for producing low output powers. Mixed-mode outphasing is the most common current method of driving outphasing PA's. This gets rid of the issue of needing to perfectly cancel out two high power signals to produce a low or zero output power signal.

#### 1.3.2 MIXED-MODE OUTPHASING

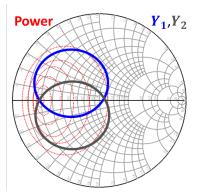

A problem with the Chireix outphasing architecture is the trade-off that is inherent with branch PA resistive matching and dynamic range of the PA. There is also significant efficiency degradation at lower output power

Figure 1.11: Chireix outphasing combiner branch load contours for an idealized combiner (blue corresponds to branch 1 and gray corresponds to branch 2). The dotted red lines show a load contour plot for an idealized transistor. Sweeping the outphasing angle from  $0^{\circ}$  to  $360^{\circ}$  produces two circular load trajectories. Due to the combination of the shape of the load contours for the transistor output power and the combiner load trajectories, a limited output power dynamic range is shown.

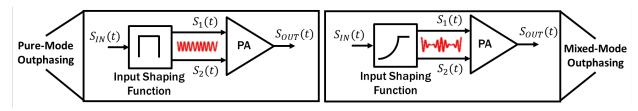

Figure 1.12: Mixed-mode with a shaping function for input power control vs. classical outphasing without input power shaping.

levels due to the fact that the branch amplifiers are constantly running at maximum power while attempting to phase cancel the two signals to produce a small or zero output power signal. To counteract the need to perfectly cancel out the two signals, amplitude control can be introduced back in as shown in Fig. 1.12. This provides a boost in efficiency at extremely low power levels since the power being input into the system is also reduced. The efficiency of the system can still be maintained through coherently controlling both the outphasing angle and the input amplitude in order to get the desired output power. The branch PA's can still maintain saturation if the outphasing angle, which directly corresponds to the load impedance seen by each of the branches, is controlled correctly with the input power to ensure the branches are still operating at peak efficiency at any given output power point.

Reducing the input power into the branch PA's will shift the optimum load for maximum  $P_{OUT}$  and PAE to higher load impedances which are within the outphasing combiner load trajectory regions. This

adds a significant performance advantage to the outphasing PA over a classically driven outphasing PA. The back-off efficiency benefit comes at a trade-off of complexity. Now a another dimension must be added to the look-up table (LUT) that is required for the signal decomposition in the digital domain since the amplitude and phase of both input signals must be coherently controlled.

### 1.4 Thesis Contents

This research work has proposed 2 different PA architectures which resulted in 3 conference publications and 3 journal publications. The work will address the issue of complexity when decomposing the outphasing signal from a desired AM and PM signal into two mixed-mode outphsaing signals. It will also address the issue of implementing outphasing into wide-band/multi-band systems for modern communications and telemetry.

## Chapter 2

# **RF-INPUT OUTPHASING**

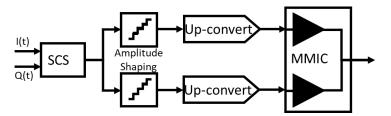

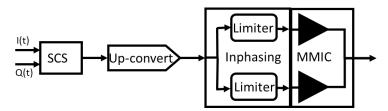

Since the inception of of the first outphasing power amplifier by Chireix in 1935, the strongest limitation of the architecture is the need for multiple coherent input drive signals. The generation of the input signals typically means the implementation of multiple modulator paths to generate the two or four constant-envelope phase-modulated signals. Modern realization of dynamic phase modulation for the generation of the outphasing signals is done through high frequency digital to analog converter (DAC) IQ modulators. These DAC modules take the separated outphasing signals that were generated in a digital baseband signal component seperator as shown in Fig. 2.1a and convert them into an RF signal.

The use of multiple TX up-conversion chains in each of the outphasing PA branches negatively impacts the C-SWaP (Cost Size Weight and Power) considerations of the overall TX module. In addition, it adds to

Figure 2.1: Outphasing signal decomposition networks in (a) the digital domain and (b) the analog domain. Reduced complexity by moving signal decomposition network into the analog domain. Allows the leveraging of RF fractional bandwidth scaling.

Figure 2.2: Idealized RF input outphasing splitter schematic showing time reversal duality drive to generate a relative phase split from an AMPM signal.

the overall complexity of linearizing the power amplifier through the use of DPD. Recent frequency scaling of RF systems has also posed a problem for traditional multiple input outphasing systems because the baseband computation doesn't scale with frequency. For many current system designs, an easier to implement solution would be to move the signal generation from the digital domain, where processing is costly from a C-SWaP standpoint especially when considering frequency scalability, and move it to the analog domain. This would create a drop-in replacement for a traditional RF power amplifier with a single RF input and and single RF output as shown in Fig. 2.1b.

### 2.1 **RF-INPUT OUTPHASING PA THEORY**

In order to generate the outphasing signals in the RF domain an analog splitting network needs to be developed. It is discovered in [14] that a time reversal duality can be applied to an outphasing combiner network in order to generate the model for how an analog outphasing splitter network (inphasing splitter) needs to behave. A time reversal duality of the combiner shown in Fig. 1.9 would mean that  $Z_L$  is replaced with a power source that generates an AM and PM signal and the transistors on the two branches are swapped with loads. In order to properly model the varying impedances at each of the amplifier ports, the loads need to be power dependent loads. The network created is represented by Fig. 2.2. The voltage across the loads is:

$$V_{1,2} = V_{in} \frac{\pm j R_{NL}}{Z_0 sin\sigma \mp j R_{NL} cos\sigma}$$

(2.1)

where  $R_{NL}$  is a function of  $P_{in} = V_{in}i_{in}^*$  and

$$\sigma = \frac{2\pi\Delta}{\lambda} \tag{2.2}$$

Then the magnitude and outphasing angle are:

$$|V_1| = |V_2| = \frac{V_{in} R_{NL}}{\sqrt{Z_0^2 sin^2 \sigma + R_{NL}^2 cos^2 \sigma}}$$

(2.3)

$$\phi = \arctan\left(\frac{Z_0 tan\sigma}{R_{NL}}\right) \tag{2.4}$$

This gives a direct relationship between output voltage and the non-linear loading of the splitter network:

$$V_{out} = \sin\left(\tan^{-1}\left(\frac{Z_0 t a n \sigma}{R_{NL}}\right)\right) \tag{2.5}$$

To complete the relationship so that  $P_{out}(P_{in})$ , a non-linear impedance element with a  $R_{NL}(P_{IN})$  transfer function optimized for outphasing control of the system needs to be chosen. The ideal transfer function is a non-limiting characteristic at lower power levels, where the outphasing control is predominately amplitude based, with gradually increased limiting as input drive approaches amplifier saturation region. This allows the impedance at the splitter's output ports to vary at an increasing rate modulating the phase shift between the two ports. This allows for mixed-mode outphasing control which maximizes the efficiency that is obtained from the outphasing PA without having to add additional digital processing or complexity.

The default element/circuit with a characteristic that is described above is a limiter circuit. A limiter circuit provides a power clamp on the maximum amount of power that can be output through the limiter. This effect is achieved through the use of anti-parallel diodes and a RF matching circuitry. The limiting transition of a limiter circuit is typically faster than what is desired based on the analytically derived transfer functions above (as will be shown later in this thesis), however, its combination of AMAM and AMPM splitting characteristics fit well for the use of an RF-input outphasing (RFIO) PA splitter (inphasing splitter). This effect has been previously demonstrated at lower frequencies [15]. The scalability of the RFIO architecture will be addressed in the following section showing its capabilities at X-band.

Figure 2.3: Simplified block diagram of the X-band RFIO PA described in this work. The passive inphasing network provides the required phase signals to drive the outphasing PA MMIC.

Figure 2.4: The inphasing network (a) is based on transmission lines loaded with a non-linear termination. As  $R_{NL}$  varies, so does the relative phase of the outputs. Simulated limiter large-signal impedance across input power is shown in (b).

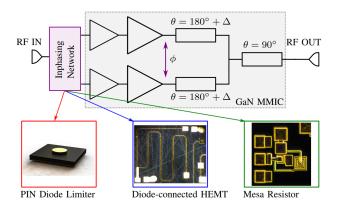

#### 2.2 X-BAND HYBRID RFIO PA

The proposed X-band RFIO PA, shown in Fig. 2.3, comprises an outphasing PA MMIC implemented in  $0.15 \,\mu\text{m}$  GaN [16] and the hybrid inphasing network that is the focus of this work. The inphasing network is based on a non-linear technique that has been previously proposed for L band, but with topology adaptations to enable operation at X-band. Hybrid board fabrication at X-band was a major considering when designing the inphasing splitter as well as selecting non-linear elements.

RF-input outphasing uses a non-linear resistive element to produce a varying termination impedance

Figure 2.5: Schematic of the limiter design using PIN diodes. Replaces  $R_{NL}$  element in Fig. 2.4

at the output ports of a lossless splitter network, as shown schematically in Fig. 2.4. As the resistance  $R_{NL}$  varies, the relative phase (and magnitude) of the two outputs of the network will vary. By selecting a power-dependent non-linear element for  $R_{NL}$ , the network can be designed such that its output signals vary as an appropriate function of input power. These phase- and amplitude-modulated signals are then used to drive PAs in an outphasing architecture. This approach has been previously described in the previous section as providing a time-reversal dual of the Chireix outphasing combiner, and can be applied to two-way and multi-way power combining system.

The inphasing network must be designed to produce the correct input trajectory (i.e., input power levels and relative phases). The MMIC outphasing PA used in this work [16] is characterized and requires an outphasing angle of 159 degrees and input power at each port of 25 dBm for maximum output power, with the phase decreasing for subsequent lower output power levels. To generate this characteristic, a limiter is first designed to produce a wide-range resistive impedance variation in response to varying input power, and with a maximum output power of 25 dBm. The MACOM MA4L101-134 PIN diode was selected due to its high power handling and availability as a chip diode package. This allows for the lowest package parasitics while allowing for a wire-bond connection to the the top terminal and a soldered ground connection. The limiter architecture shown in Fig. 2.5 employs two cathode-grounded diodes separated by a quarter-wavelength transmission line, with stub lengths tuned to ensure that the impedance variation lies along the resistive axis of the Smith Chart. The input and output transmission lines provide additional system match to both the splitter and the input of the PA. The simulated impedance of the limiter network is shown in Fig. 2.4 as the power applied to the limiter is varied from 0 to 33 dBm.

Figure 2.6: Simulated performance of the inphasing network, showing the power (a) and relative phase (b) of the two output signals.

The simulated inphasing network performance is shown in Fig. 2.6. The target outphasing angle (phase difference) of 159 degrees with 25 dBm output power at each of the ports is met. The difference in power between the two ports is less than 0.5 dB which will prevent excessive asymmetrical driving of the branch power amplifiers. The asymmetric drive is a result of the parasitic reactances of both the package and the non-linear element itself. The minimum phase difference of the network is 80 degrees, providing an expected power dynamic range of approximately 6 dB in the outphasing operating mode. Below this power level, the relative phases are held constant (due to the limiter diodes remaining off) and only amplitude modulation is applied. This results in mixed-mode operation, an established method in which amplitude modulation is used to extend the output power back-off range [14]. During the outphasing operating regime, amplitude modulation prevents over-driving of the branch PAs.

#### 2.2.1 Measurements

The inphasing network, shown in Fig. 2.7, is fabricated using a Rogers 5880 20 mil thickness substrate. The outphasing angle of the inphasing splitter is measured using a four-port network analyzer with a calibrated power sweep (limited to 28 dBm due to vector network analyzer output power limitation). The resulting outphasing angle, calculated as the difference of phase( $S_{21}$ ) and phase( $S_{31}$ ), is shown in Fig. 2.8. It can be seen that the phase response matches simulation well in shape, but is offset in terms of absolute value. In

Figure 2.7: Photograph of the fabricated X-band inphasing network. The board, including a limiter drop-out, measures 60 mm by 59.8 mm.

Figure 2.8: Measured and simulated outphasing angle produced by the inphasing network. The calibrated drive power of the VNA setup is limited to 28 dBm.

our experimental setup, this offset is compensated for using static phase shifters. The phase shift tuners are adjusted such that the phase at peak power corresponds to that required for the outphasing MMIC. The phase response of the inphasing network provides the dynamic phase modulation in back-off.

The output power required from the splitter when operating at maximum input drive (33 dBm) is 25 dBm at each port. Although this constraint is met in simulation, when measured the network was found to have approximately 10 dB additional loss: under peak drive conditions, the output powers at ports 2 and 3 are only 14.7 dBm and 14.06 dBm, respectively. This loss is attributed to fabrication issues, in particular relating to modeling of the diode ground return path. To compensate for the unanticipated loss, driver amplifiers are

Figure 2.9: Block diagram of the experimental test setup. Driver amplifiers and fixed phase shift tuners are included to compensate for non-idealities in the inphasing network.

used between the inphasing network and outphasing PA to ensure sufficient drive power to saturate the PAs. These bench drivers are set up to provide approximately 10 dB gain.

The block diagram of the characterized RFIO system including phase shift tuners and drivers is shown in Fig. 2.9. Due to the inclusion of the drivers, only drain efficiency is reported in this work. The modulated RF signal is generated and analyzed using a National Instruments PXIe-5645R VST with 80 MHz analog bandwidth. The baseband I/Q signal is up/down converted at 3 GHz within the VST and an external frequency extension at 9.7 GHz is added to the VST and realized by off-the-shelf mixers and image-rejection filters.

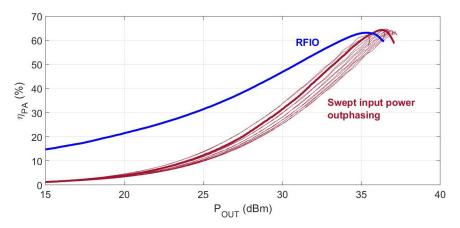

The RFIO is characterized using modulated RADAR signals. Measured drain efficiency is shown in Fig. 2.10, with a peak drain efficiency of 63%. The outphasing "banana curve" characteristic is also visible, with the peak efficiency point located below the peak output power level. It is interesting to note that similar efficiency trajectories have been obtained in [2] for the same MMIC by means of digitally-controlled continuous input phase and amplitude modulation. The slightly lower peak efficiency reported in [2] is due to the inclusion of a supply modulator in the efficiency calculation.

Figs. [2.11,2.12] show the drive setup for the RFIO measurement setup as well as the mixed-mode measurement setup for comparison. Fig. 2.13 shows a comparison of the outphasing MMIC when measured in the RFIO setup (blue) vs when measured in a classical dual-input mixed-mode outphasing setup (red). The degradation of the drain efficiency at peak power and the improvement at 1.5 dB back off in the RFIO architecture is attributed to an uneven power split in the inphasing network, which generates unequal drive powers to the two branch PAs. This asymmetry modifies the load trajectories from their design values, and produces an optimum efficiency point further into power back off. The 0.65 dB less peak output power for

Figure 2.10: Measured drain efficiency vs. output power of the outphasing MMIC in the RFIO architecture, characterized for the pulse shown at right.

Figure 2.11: Mixed-mode outphasing drive schematic for measurements.

Figure 2.12: RFIO drive schematic for measurements.

the RFIO system is due to the accuracy of the static phase shifters in reaching the optimum outphasing angle for the outphasing MMIC. This comparison shows that the RFIO setup tracks the mixed-mode outphasing deep into power back off. We note that the dual-input measurement employs only a narrow range of input amplitude variation, whereas the RFIO system continuously modulates the PA drive power. The back-off efficiency of the dual-input system could be enhanced by increasing the extent of mixed-mode operation used.

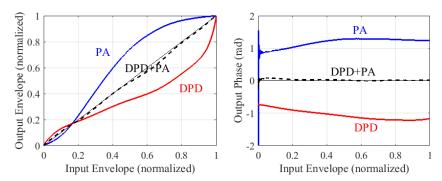

Measured AM/AM and AM/PM characteristics of the PA are shown in Fig. 2.14. A generalized memory polynomial with non-linearity and memory order respectively equal to nine and one is used to model the inverted non-linear behavior with memory of the RFIO PA. The DPD is extracted off-line by characterizing

Figure 2.13: Measured drain efficiency vs. output power of the outphasing MMIC in the RFIO architecture (blue) vs. the same MMIC operated in conventional dual-input mixed-mode outphasing (red), with limited variation in PA drive power [2].

Figure 2.14: Measured AM/AM and AM/PM characteristics of the RFIO PA, characterized for pulsed measurements.

Figure 2.15: Measured output spectrum for a rectangular RF pulse and for an amplitude-modulated pulse with raised-cosine pulse profile. In both cases, the pulse duration is  $10\mu$ s and the repetition period is  $100\mu$ s.

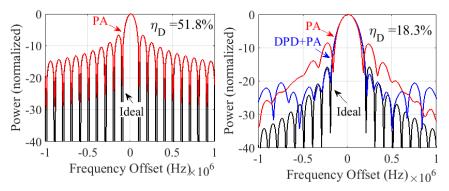

the PA with the same sequence used as a test signal. An indirect learning architecture is employed, with the post-inverse model of the PA extracted at first, and then used to predistort the input signal of the PA. Rectangular and raised-cosine AM signals are used to evaluate the spectrum of the system without DPD and with DPD and the resulting spectrums are shown in Fig. 2.15. The system linearity improves by using DPD as shown in Fig. 2.15 where the first side-lobe of the raised-cosine pulse approaches the ideal signal spectrum. Although some distortion is still present, DPD clearly improves the system linearity. The average PA efficiency is 51.8% for the rectangular RF pulse and 18.3% for the raised cosine pulse. We note that in this work we do not employ a drain switch as in most typical radar PAs, therefore the PA continues to draw power during the off part of the period and this penalizes the average efficiency.

This work was successful in showing the scalability of the RFIO PA architecture into mm-wave frequencies. It was able to track the mixed-mode outphasing contours of the outphasing MMIC well giving back-off efficiency benefits equivalent to the complicated drive technique of the dual-input outphasing PA. The splitter ended up having significantly more loss than was initially simulated. This was due to discrepancies in the diode model as well as fabrication inconsistencies that have major performance impacts due to the 10 GHz frequency operation. The AMAM characteristic of the RFIO PA was heavily non-linear and required multiple memory taps to linearize. Utilizing the non-linear element characteristic as a way to linearize the PA is an un-utilized control knob in this design.

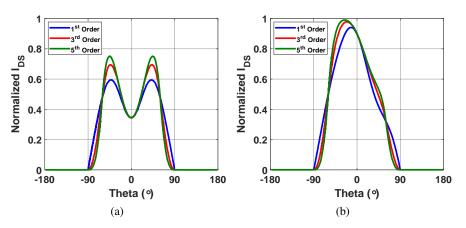

## 2.3 **RFIO Analysis**