## Process Variation in Silicon Photonic Devices

by

#### Xi Chen

B.S., Peking University, 2006

M.S., University of Colorado Boulder, 2009

A thesis submitted to the Faculty of the Graduate School of the University of Colorado in partial fulfillment of the requirements for the degree of Doctor of Philosophy Department of Electrical, Computer and Energy Engineering

2013

This thesis entitled: Process Variation in Silicon Photonic Devices written by Xi Chen has been approved for the Department of Electrical, Computer and Energy Engineering

Prof. Alan Mickelson

Prof. Li Shang

Date \_\_\_\_\_

The final copy of this thesis has been examined by the signatories, and we find that both the content and the form meet acceptable presentation standards of scholarly work in the above mentioned discipline.

#### Chen, Xi (Ph.D., Electrical Engineering)

Process Variation in Silicon Photonic Devices

Thesis directed by Prof. Alan Mickelson

The high index contrast of the silicon - silicon dioxide material system allows for dense integration of optical waveguide devices. Possible applications include intra-chip, inter-chip and fiber optic interconnection systems. Optical intra-chip interconnections become more desirable as the complementary metal-oxide-semiconductor (CMOS) circuit density puts ever tighter constraint on on-chip interconnection performance. Board level, rack level and rack-to-rack data center interconnections are ever more constrained by space and bandwidth to which silicon photonic modules may offer an improvement. As fiber optic systems serve smaller and smaller area systems, integrated switching systems that are enabled by silicon photonic devices involving wavelength division multiplexing (WDM) become more desirable.

In this thesis, we firstly take a brief review of the development history of information technology, optical communication and silicon photonics. Secondly we examine the optical performance of an array of photonic devices which are the basic building blocks for silicon photonic circuits. Thirdly we turn the attention to the fabrication related issues. Silicon photonic circuits are prone to the thermal and fabrication induced process variations. We discover the process variation exhibits a "random walk" pattern with spatial extent at wafer scale. Fourthly we propose a simple method to extract fundamental parameters out of fabricated silicon photonic devices. Based on the systemic wafer-scale measurement results, our method combines the advantage of both numerical simulation and simple analytical modeling techniques. Lastly, we propose a variation-aware on-chip interconnect design for multi-core processors. This design adapts to on-chip thermal and process variation effects, pointing to the improvement of wafer-scale fabrication yield and interconnect network communication throughput. Dedication

To my family.

#### Acknowledgements

In the journey of my Ph.D. study here in Boulder, I feel so fortunate to have Prof. Alan Mickelson as my academic advisor. Alan introduced me to this fascinating topic of silicon photonics that eventually develops into a thesis. Besides exciting results I discovered in lab through out the years, the process of research could be challenging at times. Alan's wisdom and kindness constantly encourage me to overcome barriers and lead me to greater achievements. I always enjoy the office meeting with Alan and his humor always brings out a little laughter after long serious discussion.

I also would like to extend my sincere gratitude to my thesis committee members: Prof. Dejan Filipovic, Prof. Juliet Gopinath, Prof. Yung-Cheng Lee, Prof. Wounjhang Park and Prof. Li Shang. It has been a great experience to collaborate with them on various projects at different stages of my study and learn from their advices and insights.

My fellow labmates and colleagues have been very supportive to each other's work and I enjoy the positive atmosphere we have at the Guided Wave Optics Lab (GWOL). I would like to express my thankfulness to Dr. Zheng Li, Dr. Moustafa Mohamed, Dr. Hongyu Zhou, Dr. Eric Dudley, Dr. Brian Schwartz, David Espinoza, Jyothi Karri, Jian Wang, Todd Houghton, Keyon Janani, Eric Jacobson and Dr. Yonghao Cui for their direct and indirect contributions to this thesis.

I would like to thank Jim Marcelli and folks at Lightwave Logic Inc. for their support of my research. I would not forget the countless helps from friends in the ECEE administrative office. My appreciation also goes to all the other friends in the ECEE department and at CU.

Finally, I would like to express my deep love to my family for their enormous support and love in my life.

## Contents

## Chapter

| 1        | Intro | duction 1                                                                       |   |

|----------|-------|---------------------------------------------------------------------------------|---|

|          | 1.1   | Moore's Law and Beyond                                                          |   |

|          | 1.2   | The Electrical Interconnection                                                  | : |

|          | 1.3   | The Optical Interconnection                                                     |   |

|          | 1.4   | Silicon Photonics                                                               |   |

|          | 1.5   | Statement of the Research                                                       | 1 |

|          |       | 1.5.1 The Vision $\ldots$ 12                                                    |   |

|          |       | 1.5.2 List of Publications and Origins of Contribution                          |   |

|          | 1.6   | Thesis Outline and Origins of Contribution                                      |   |

|          |       | 1.6.1 Thesis Outline                                                            |   |

|          |       | 1.6.2 Origins of Contribution                                                   |   |

| <b>2</b> | Fabi  | ication, Measurement and Design Characterization of Silicon Photonic Devices 20 |   |

|          | 2.1   | Introduction                                                                    | 1 |

|          | 2.2   | Fabrication                                                                     |   |

|          | 2.3   | Measurement Apparatus and Its Use                                               |   |

|          | 2.4   | Design Characterization of Silicon Photonic Devices                             | : |

|          |       | 2.4.1 Grating Coupler                                                           | : |

|          |       | 2.4.2 Ring Resonator                                                            | ļ |

|   |      | 2.4.3    | Directional Coupler                                                                                                                           | 34 |

|---|------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

|   |      | 2.4.4    | Optical Antenna                                                                                                                               | 37 |

|   |      | 2.4.5    | Photonic Crystal                                                                                                                              | 42 |

|   | 2.5  | Conclu   | usion                                                                                                                                         | 45 |

| 3 | Proc | cess Vai | riation in Silicon Photonic Devices                                                                                                           | 46 |

|   | 3.1  | Introd   | $uction \ldots \ldots$ | 46 |

|   | 3.2  | Test S   | tructures and Their Measurement                                                                                                               | 49 |

|   |      | 3.2.1    | The Fabricated Devices                                                                                                                        | 50 |

|   |      | 3.2.2    | Measurements and Analysis of Wavelength Dependent Transmission                                                                                | 51 |

|   | 3.3  | Measu    | urement and Analysis to Determine Process Variation                                                                                           | 54 |

|   |      | 3.3.1    | Micro-ring                                                                                                                                    | 54 |

|   |      | 3.3.2    | Racetrack                                                                                                                                     | 57 |

|   |      | 3.3.3    | Directional Coupler                                                                                                                           | 60 |

|   | 3.4  | Discus   | $\operatorname{ssion}$                                                                                                                        | 62 |

|   | 3.5  | Concl    | usion                                                                                                                                         | 62 |

| 4 | Para | ameter   | Extraction from Fabricated Silicon Photonic Devices                                                                                           | 64 |

|   | 4.1  | Model    | ling Framework                                                                                                                                | 66 |

|   |      | 4.1.1    | The Effective Index of Refraction                                                                                                             | 67 |

|   |      | 4.1.2    | Wavelength Dependent Transmission                                                                                                             | 69 |

|   |      | 4.1.3    | Models for Wavelength-Selective Devices                                                                                                       | 70 |

|   |      | 4.1.4    | Sample Preparation                                                                                                                            | 72 |

|   |      | 4.1.5    | Tracking Thermal Variations with Effective Index                                                                                              | 73 |

|   | 4.2  | Extra    | cting Effective Index from Experimental Data                                                                                                  | 75 |

|   |      | 4.2.1    | Micro-ring                                                                                                                                    | 76 |

|   |      | 4.2.2    | Racetrack Resonator                                                                                                                           | 80 |

|   |      | 4.2.3    | Directional Coupler                                                                                                                           | 82 |

|          | 4.3  | Conclusion                        | 84 |

|----------|------|-----------------------------------|----|

| <b>5</b> | Vari | ation-Aware On-chip Interconnect  | 85 |

|          | 5.1  | Introduction                      | 85 |

|          | 5.2  | The Design                        | 86 |

|          | 5.3  | Demonstration of the WDM Channels | 91 |

|          | 5.4  | Scalability                       | 92 |

|          | 5.5  | Conclusion                        | 95 |

| 6        | Con  | clusion                           | 97 |

# Bibliography

101

viii

## Tables

| 2.1 | Fabrication induced variations on the antenna geometry                        | • • | <br>40 |

|-----|-------------------------------------------------------------------------------|-----|--------|

| 3.1 | Summary of the thermal and local process variation of the fabricated devices. |     | <br>62 |

# Figures

# Figure

| 1.1  | (a) Data for the component counts on IC chip during 1960s and 1970s verifies the                            |    |

|------|-------------------------------------------------------------------------------------------------------------|----|

|      | Moore's Law. (b) Images of IC chips that were used in constructing the Moore's Law.                         | 2  |

| 1.2  | The reduction of fiber optical propagation loss over the years                                              | 5  |

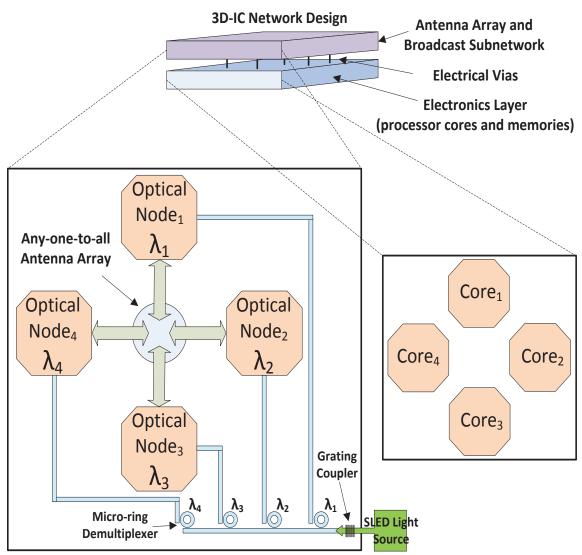

| 1.3  | A schematic plot of 3D-IC network design                                                                    | 12 |

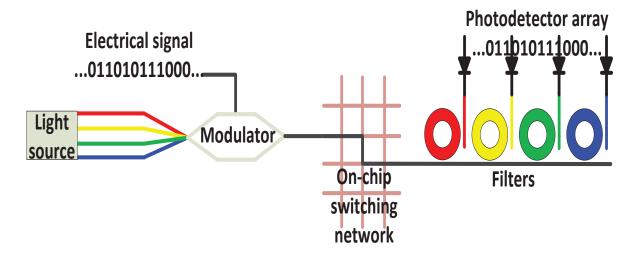

| 2.1  | A schematic diagram of a silicon photonic on-chip WDM network                                               | 20 |

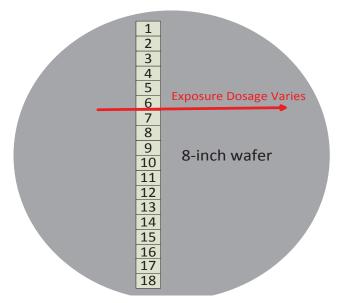

| 2.2  | Schematic depiction of an 8-inch wafer that details the vertical cells (repeated dies)                      |    |

|      | of a single column.                                                                                         | 22 |

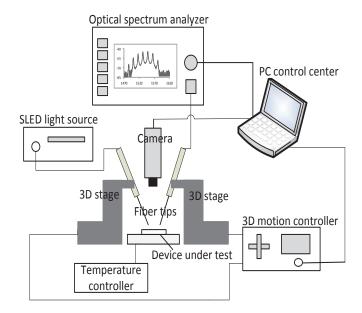

| 2.3  | Schematic of the in-house measurement setup                                                                 | 23 |

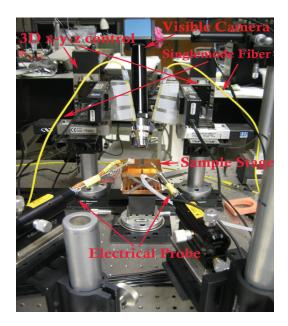

| 2.4  | Image of the in-house measurement setup                                                                     | 23 |

| 2.5  | A schematic setup of a single-mode fiber to grating coupler                                                 | 25 |

| 2.6  | The Bragg condition for grating coupling mechanism.                                                         | 26 |

| 2.7  | A scanning electron microscope image of a grating coupler that was fabricated at                            |    |

|      | the ePIX<br>fab. The area size of the grating coupler is about 10 $\mu{\rm m}$<br>$\times$ 15 $\mu{\rm m}.$ | 27 |

| 2.8  | Schematic of the cross-section view of the grating coupler design on the SOI wafer                          | 27 |

| 2.9  | Grating coupler efficiency measurement                                                                      | 28 |

| 2.10 | Schematics of two kinds of ring resonator.                                                                  | 30 |

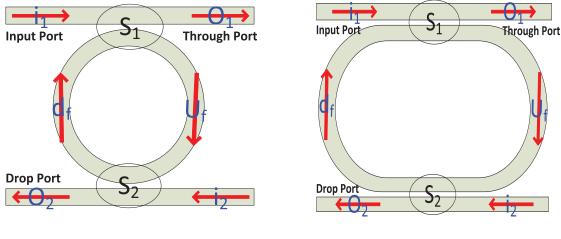

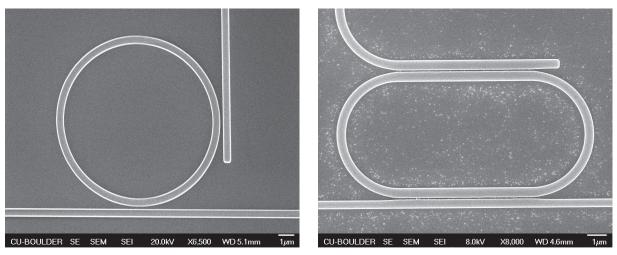

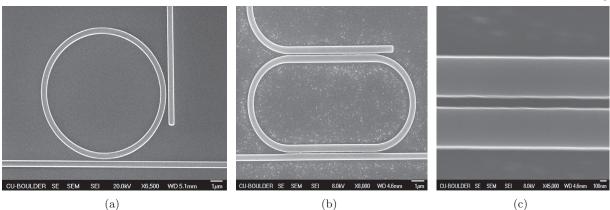

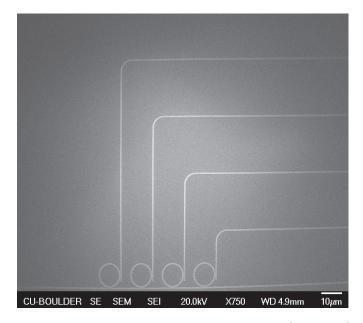

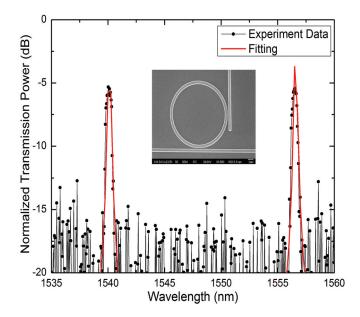

| 2.11 | SEM images of fabricated ring resonators.                                                                   | 32 |

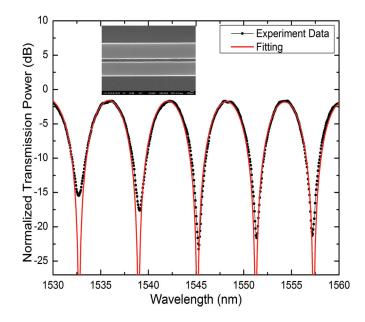

| 2.12 | Optical transmission measurement of the ring resonators in Figure 2.11                                      | 33 |

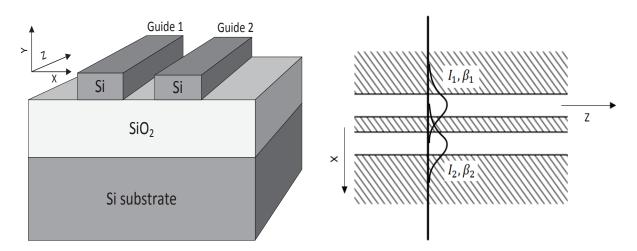

| 2.13 | Schematic of a directional coupler.                                                                      | 34 |

|------|----------------------------------------------------------------------------------------------------------|----|

| 2.14 | Schematic of mode coupling in SOI directional coupler structure                                          | 35 |

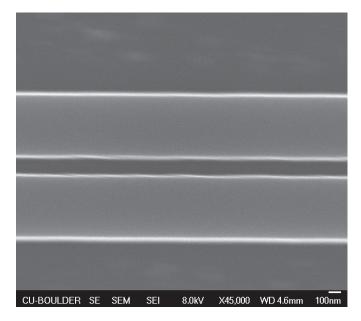

| 2.15 | A SEM image of part of a directional coupler that was fabricated at the ePIXfab                          | 37 |

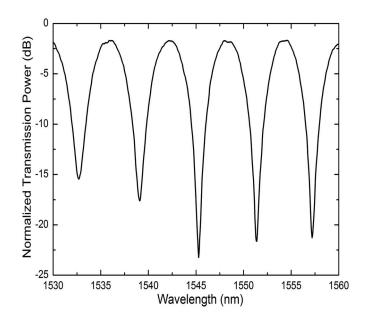

| 2.16 | Optical transmission measurement of the directional coupler in Figure 2.15                               | 37 |

| 2.17 | A pair of diagrams that illustrate the functionality of power overlay for in-plane                       |    |

|      | antennas                                                                                                 | 38 |

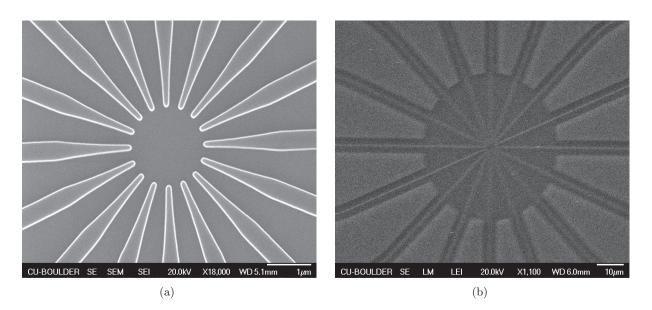

| 2.18 | Optical dielectric rod antenna design and fabrication.                                                   | 39 |

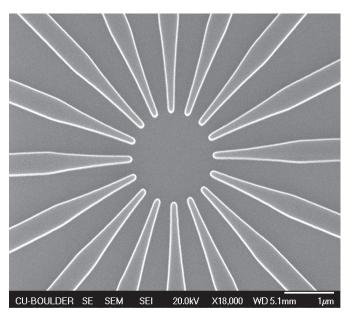

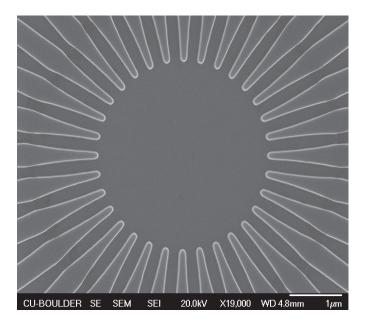

| 2.19 | SEM images of a 16-antenna any-one-to-all circular array before and after polymer                        |    |

|      | coating                                                                                                  | 41 |

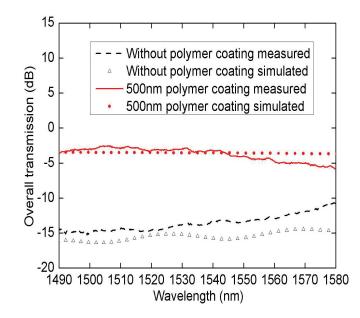

| 2.20 | Comparison between the simulated and the measured results of the 16-antenna any-                         |    |

|      | one-to-all array without and with 500-nm thick polyimide coating. $\ldots$                               | 42 |

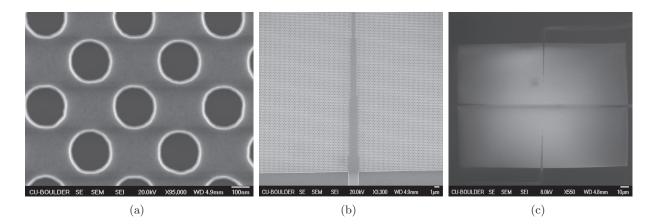

| 2.21 | SEM images of a photonic crystal waveguide structure                                                     | 43 |

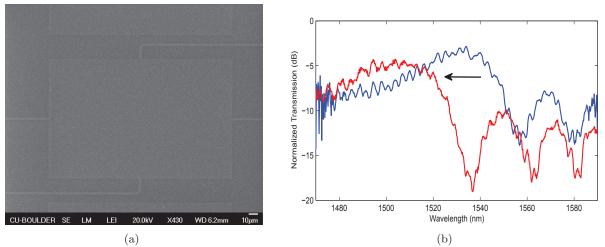

| 2.22 | SEM image of the polymer coated photonic crystal waveguide and measurement                               |    |

|      | results of its transmission characteristics before and after polymer turning. $\ldots$ .                 | 44 |

| 3.1  | SEM images of the 450 nm x 220 nm waveguide structures of interest including a                           |    |

|      | micro-ring resonator, a racetrack resonator and a section of the coupling region of a                    |    |

|      | directional coupler                                                                                      | 49 |

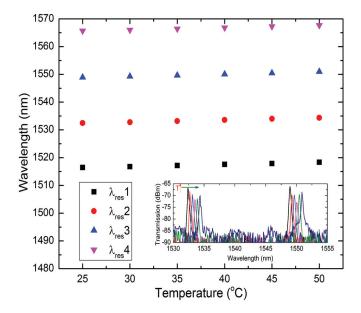

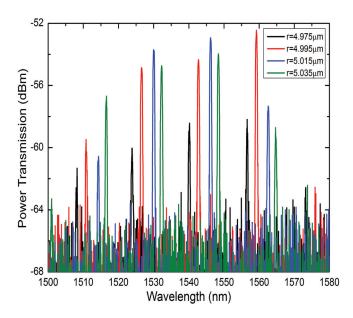

| 3.2  | Study of the variation of 4 maximum transmission wavelengths of the 4.975- $\mu {\rm m}$                 |    |

|      | radius micro-ring in Figure 3.1(a) at 6 temperatures in the range of $25^\circ \rm C$ - $50^\circ \rm C$ | 51 |

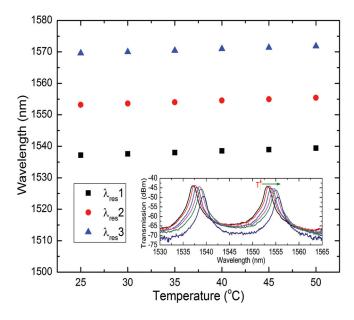

| 3.3  | Study of the variation of 3 maximum transmission wavelengths of the racetrack of                         |    |

|      | Figure 3.1(b) at 6 temperatures in the range of $25^{\circ}$ C - $50^{\circ}$ C.                         | 52 |

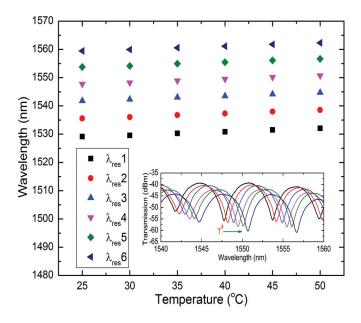

| 3.4  | Study of the variation of 6 minimum transmission wavelengths of the directional                          |    |

|      | coupler of Figure 3.1(c) at 6 temperatures in the range of 25°C - 50°C                                   | 52 |

| 3.5  | A SEM image of a wavelength-division multiplexer (WDM'er) that consists of four                          |    |

|      | micro-ring resonators with 200-nm gaps and 450-nm waveguides.                                            | 55 |

xi

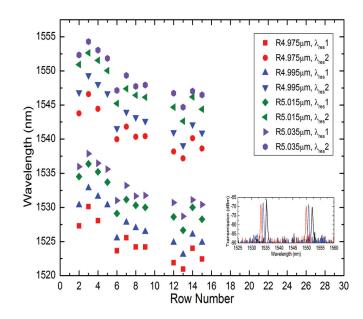

| 3.6  | A scatter plot containing two of the maximum transmission wavelengths of each of        |    |

|------|-----------------------------------------------------------------------------------------|----|

|      | the four transmission functions of the WDM device of Figure 3.5 realized on $12$ dies   |    |

|      | of a 28 die column (for example, see the layout of the 18 die column of Figure 2.2)     | 55 |

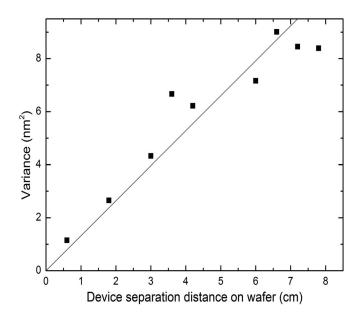

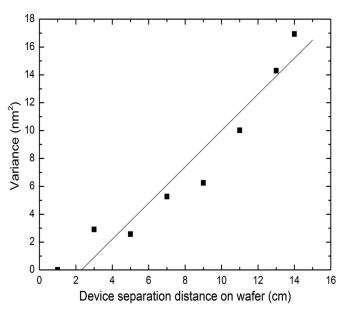

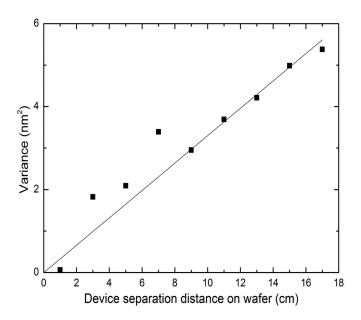

| 3.7  | A plot of the variance of transmission wavelength peaks of the WDM structures over      |    |

|      | the device separation distance on wafer.                                                | 57 |

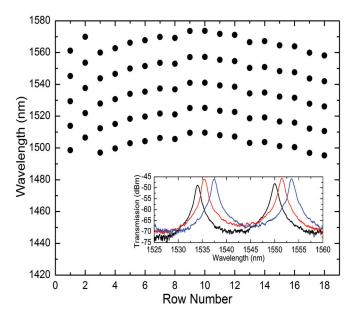

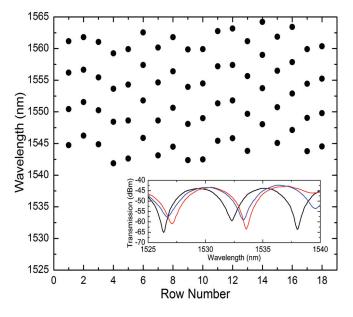

| 3.8  | A scatter plot of 5 wavelength peaks of each of 18 transfer functions                   | 58 |

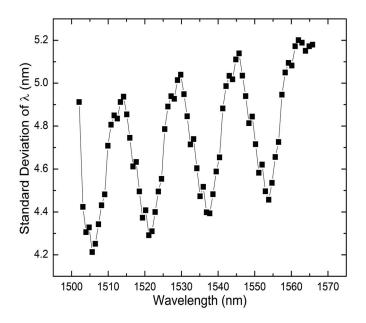

| 3.9  | Plot of the standard deviation versus mean of each set of 18 consecutive wavelengths    |    |

|      | that can be constructed from the scatter data of Figure 3.8                             | 58 |

| 3.10 | A plot of the variance of transmission wavelength peaks of the racetrack structures     |    |

|      | over the device separation distance on wafer.                                           | 59 |

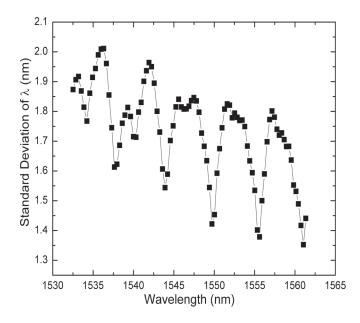

| 3.11 | A scatter plot of the four adjacent minima of directional coupler transfer functions    | 60 |

| 3.12 | A plot of standard deviation (STD) versus mean value for each possible grouping of      |    |

|      | 18 adjacent wavelength data points of Figure 3.11                                       | 61 |

| 3.13 | A plot of the variance of transmission wavelength minima of the directional couplers    |    |

|      | over the device separation distance on wafer.                                           | 61 |

| 4.1  | Schematic depictions of the devices of interests: micro-ring, racetrack and directional |    |

|      | coupler                                                                                 | 70 |

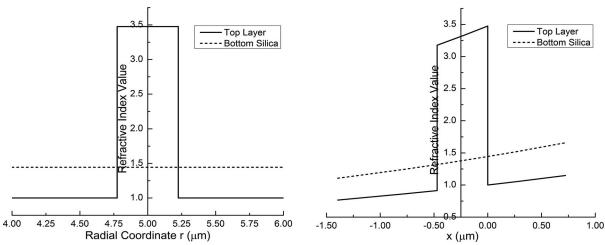

| 4.2  | Cross-sectional distribution of the refractive index in the bending structure before    |    |

|      | and after using conformal mapping technique                                             | 72 |

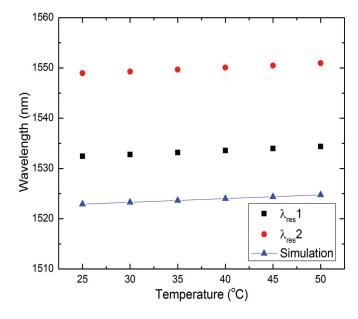

| 4.3  | Thermal variation measurement and numerical modeling results of a micro-ring in         |    |

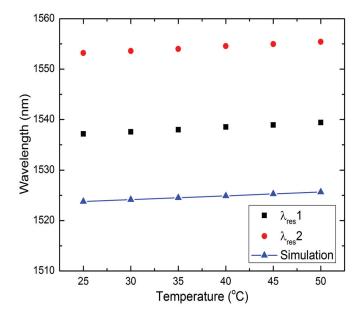

|      | the temperature $25^{\circ}$ C - $50^{\circ}$ C                                         | 73 |

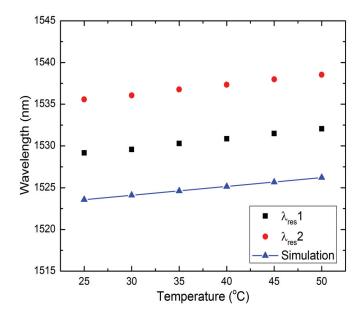

| 4.4  | Thermal variation measurement and numerical modeling results of a racetrack in the      |    |

|      | temperature $25^{\circ}$ C - $50^{\circ}$ C.                                            | 74 |

| 4.5  | Thermal variation measurement and numerical modeling results of a directional cou-      |    |

|      | pler in the temperature $25^{\circ}$ C - $50^{\circ}$ C                                 | 74 |

|      |                                                                                         |    |

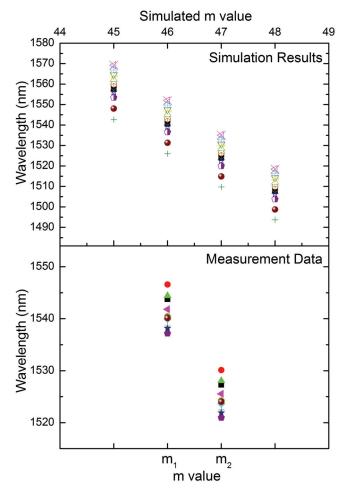

| 4.6  | Illustration of the process to find the mode number m from the measured resonant                         |    |

|------|----------------------------------------------------------------------------------------------------------|----|

|      | wavelengths and simulation                                                                               | 77 |

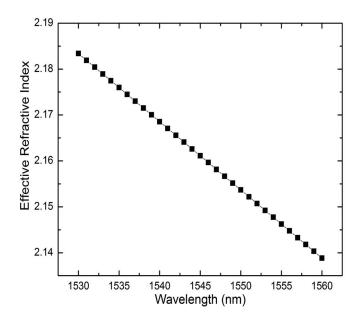

| 4.7  | Effective index dispersion curves extracted from measured data for a micro-ring $(450$                   |    |

|      | nm waveguide width, coupling gap 200 nm, radius of 4.975 $\mu$ m)                                        | 79 |

| 4.8  | Optical transmission measurement of a micro-ring and its corresponding numerical                         |    |

|      | model fitting.                                                                                           | 79 |

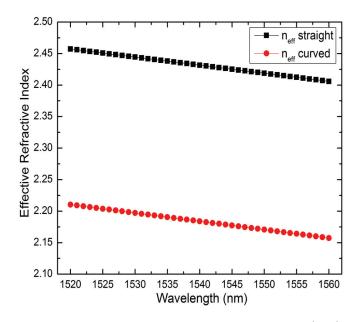

| 4.9  | Effective index dispersion curves for the straight region $(n^s_{\rm eff})$ and the curved re-           |    |

|      | gion $(n_{\rm eff}^c)$ extracted from measured data for a racetrack (450 nm waveguide width,             |    |

|      | coupling gap 130 nm for 7 $\mu$ m, bending radius of 3 $\mu$ m)                                          | 81 |

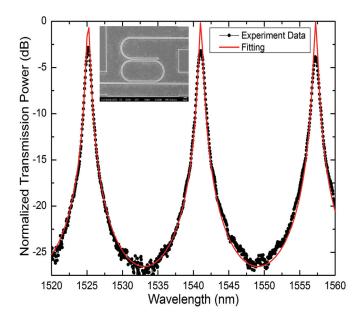

| 4.10 | Optical measurement of a racetrack and its corresponding numerical model fitting                         | 81 |

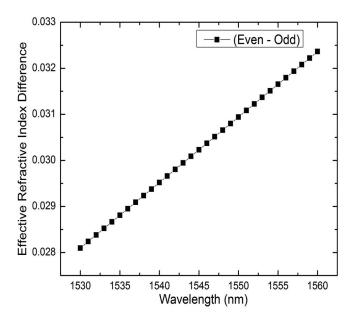

| 4.11 | Effective index dispersion curves for $n_{\rm eff}^e$ – $n_{\rm eff}^o$ extracted from measured data for |    |

|      | a direction coupler (450 nm waveguide width, 130 nm coupling gap and 1063 $\mu {\rm m}$                  |    |

|      | coupling length).                                                                                        | 83 |

| 4.12 | Optical measurement of a directional coupler and its corresponding numerical model                       |    |

|      | fitting                                                                                                  | 84 |

| 5.1  | A schematic plot of an optical interconnect topology with 4 nodes designed for a                         |    |

|      | 4-core processor                                                                                         | 87 |

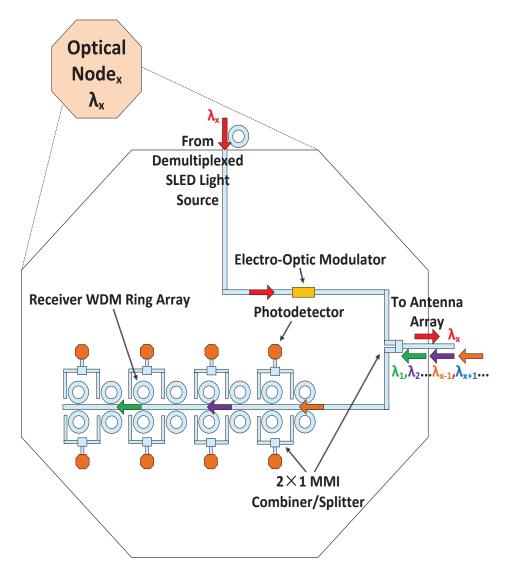

| 5.2  | A schematic of our proposed variation-aware silicon-organic hybrid design at the                         |    |

|      | optical node level.                                                                                      | 89 |

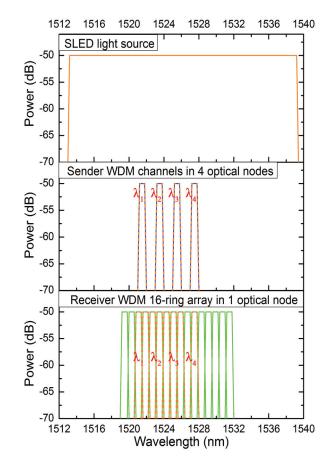

| 5.3  | A hypothetical wavelength spectrum plot of the SLED light source, the sender WDM                         |    |

|      | channels in 4 optical nodes and the WDM 16-ring array in 1 optical node in the                           |    |

|      | proposed multi-core design.                                                                              | 90 |

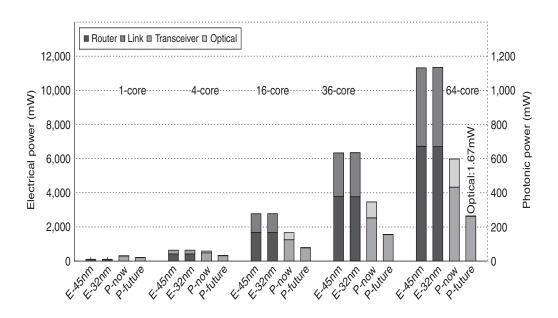

| 5.4  | A plot of wavelength spectra of the 4-channel WDM device                                                 | 91 |

| 5.5  | Comparison of power consumption of the broadcasting by electrical and photonic                           |    |

|      | interconnect links.                                                                                      | 92 |

| 5.6  | The SEM image of a fabricated 16-antenna any-one-to-all array                                            | 93 |

xiii

| 5.7 | The SEM image of a fabricated 32-antenna any-one-to-all array                         |

|-----|---------------------------------------------------------------------------------------|

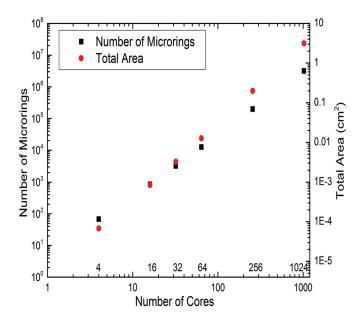

| 5.8 | The estimation of micro-ring quantity and corresponding foot print for a series of    |

|     | processor designs with $2^n$ (n being integer) cores. The radius of the micro-ring is |

|     | about 5- $\mu$ m                                                                      |

#### Chapter 1

#### Introduction

### 1.1 Moore's Law and Beyond

In the modern society, we enjoy daily life with the convenience that advanced communication and computation technologies bring to us. Mobile broadband and high-speed Internet keep people stay connected almost everyday and everywhere around the world. Information is transmitted and shared in the global community at an unimaginable fast rate. Data centers, supercomputing centers and cloud computing service businesses are growing ever faster around the world. Enormous amount of data is generated, stored and processed at every second to meet the society development needs and help accelerate scientific exploration and advancement. All of these activities started with the invention of the Integrated Circuit (IC) technology when Robert Noyce filed the "Semiconductor device-and-lead structure" patent in the late 1950s with engineers from the legendary Fairchild Semiconductor. Ever since, the semiconductor industry began a race for producing IC chips with denser and denser transistor components. From the small-scale integration (SSI) and mediumscale integration (MSI) in 1960s to the very large-scale integration (VLSI) in the 1980s and the modern three-dimensional integrated circuit (3D-IC), each step represents breakthroughs in terms of industry material research and circuit fabrication progress.

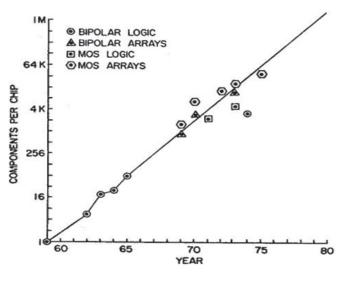

One of the driving principles and guidelines enabling higher density integration in the semiconductor industry was defined by Gordon Moore in his 1965 paper [1] where he observed and predicted the number of components in integrated circuits doubles every year since the invention of integrated circuits. A period of eighteen-month later became the industry standard for a doubling in chip performance and widely known as the "Moore's Law".

(a)

(b)

Figure 1.1: (a) Data for the component counts on IC chip during 1960s and 1970s verifies the Moore's Law. (b) Images of IC chips that were used in constructing the Moore's Law.<sup>1</sup>

<sup>&</sup>lt;sup>1</sup> Image (a): courtesy of Intel Corporate. Image (b): courtesy of Fairchild Camera & Instrument Corporation.

Moore's Law has been accurate for half a century. Figure 1.1 illustrates this trend for transistor component counts in the early 1960s and 1970s, together with the images of early IC chips. The semiconductor industry has been striving to keep up with the pace defined by this trend. The critical dimension (the gate length) of transistor on the IC chip is shrunk down from 10-100  $\mu$ m range in the early IC chips to the current sub-100 nm. The integration density has improved exponentially from the 60 transistors of 1965 as shown in the figure to today's over one billion transistors in an area the size of a fingernail. Decades of research and investment has substantially boosted IC chip's performance while the cost of manufacturing drops down dramatically. At present, the cost of a single transistor on IC chip is estimated to be comparable to that of a printed newspaper character. Information is being generated and shared at a more and more affordable rate around the world.

With the ever glowing demands for information technology and transistor reaching its physical limit for the critical dimension, the concern is that the semiconductor industry would soon meet the end of Moore's Law. A closer examination reveals that there are problems associated with the higher and higher density in IC chip integration. One important issue is that the high power density of IC chips becomes untenable. Take the microprocessor for example. Transistor density growth inherently brings up power usage on chip. Even though the power consumption increment trend slows down, the overall processor power has exponentially grown to over 100 Watts today for high performance microprocessors [2, 3]. The power consumption requirement would limit chip achievable performance and becomes a significant constraint for modern chip design [4]. Power density at some point would reach a level that is beyond the capability of heat extraction [5]. Hot spot on chip would substantially cause issues for the overall on-chip thermal management, leakage current, cooling cost and reliability [6, 7, 8].

The rising constraint towards the on-chip power density changes the approach of processor design in computer system. Over the past few years, multi-core and many-core structures emerged as one way to keep the chip performance scalability alive [9, 10, 11, 12]. Parallel computing is an energy-efficient way to achieve high performance. In this new paradigm, innovations are being explored on the chip architecture and circuit design towards low power, high efficiency computing domain [13, 14, 15, 16].

#### **1.2** The Electrical Interconnection

The idea of parallel computing in multi-core and many-core microprocessor on a single chip began to thrive since IBM delivered the first general-purpose non-embedded multi-core processor, the POWER4, in 2001 [17]. In these systems, while chip performance can be enhanced with multiple processor cores, chip size also grows. One of the interesting and challenging problems is the wiring and latency issue in the on-chip interconnection, that is, how to build effective communication channels among cores and chips without sacrifices on delays. Solving the problem on wiring delay is equally important as improving transistor's switching speed, as wiring delay gradually becomes a dominant issue that hampers efficiently utilizing each clock cycle in microprocessor [18]. Onchip communication turns into a key performance bottleneck. For instance, the total on-chip wire length is estimated to be more than  $2 \text{ km/cm}^2$  [19]. The global interconnect latency in the traditional on-chip electrical interconnect is not scaled down as the technology node evolves. On contrary, wire delay is worsen with technology scaling. Global interconnect delay is continuously increasing [20]. It becomes a problem that signals cannot travel across the entire die within a global clock cycle. Although introducing copper wire [21] and low- $\kappa$  dielectric insulators [22] would help reduce delay, the problems are multi-fold. With increment in chip complexity for more functionality, local interconnect wire density grows exponentially. At global interconnect level, aggressive use of repeaters and buffers leads to increased chip area and power consumption. Studies showed that an average of 50% power is consumed in the on-chip interconnect [23]. Cross-talk becomes serious with increasing cross-coupling capacitances between electrical interconnects on the same metal layer [24]. Under these circumstances, interconnect solution that can provide low latency, high sustained bandwidth and low energy consumption is mostly desired for the multi-core and manycore systems.

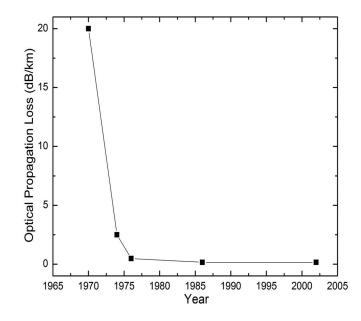

Figure 1.2: The reduction of fiber optical propagation loss over the years.

#### 1.3 The Optical Interconnection

In parallel with the development of microprocessor chips in the past half a century, the optical interconnection technology revolution has experienced many important milestones over the years. The size of optical communication devices evolves from the large long-haul communication form factor towards the integrated on-chip small form factor.

The development of fibers and modern optical devices began around 1960 and continues strongly today. The first mile stone was undoubtedly the invention of the "Light Amplification by Stimulated Emission of Radiation" (Laser) by T.H. Maiman at Hughes Research Laboratories in the early 1960s. Laser immediately distinguished itself from other light sources by the exceptional property of highly spatial and temporal coherence. The ability of providing high radiances and low divergence over long propagation distance set laser as the ideal light source for optical telecommunication.

The second milestone was the development of low-loss optical fiber in the 1970s. The idea of using glass fiber to transmit optical communication signals can be dated back to Alexander Graham Bell's "Photophone" [25]. However, like many other inventions, fiber communication had to experience a long waiting time before better glass appeared and low-cost electronics became available. K.C. Kao and G.A. Hockham showed that, in their 1966 paper, it was possible to decrease the attenuation in optical fiber down to a few dB/km by eliminating impurity ions [26]. As a transmission medium, glass fiber is immune to electromagnetic interference. This discovery opened up the opportunity for the telecommunication industry to develop long-haul optical communication link and the possibility of replacing bulky copper telephone lines with thin glass fibers. Since then, the refinement of glass fiber had never stopped. Figure 1.2 plots the progress on fiber propagation reduction over the years. From Corning Glass Works's 20 dB/km in 1970 [27] to Sumitomo Electric's 0.1484 dB/km in 2002 [28], the loss reduction advanced with emergence of new generations of technology. Currently, the fiber optical loss is approaching the theoretical limits. Because of its superior merits of low loss, low power consumption and high bandwidth, glass fiber gradually became the standard medium to carry large information capacity over long-haul telecommunication transmission. Kao was awarded the Nobel Prize in Physics in 2009 for this discovery.

In the 1980s, long-haul telephone links were deployed, thanks to the development of singlemode fiber. Single-mode fiber, operated together with 1300 nm laser source, was incorporated into the national telecommunication backbone by carriers across the United States. The Northeast Corridor system started to link Washington D.C. and New York together in 1983. New generation of single-mode fiber system with a 1550 nm laser wavelength operation window demonstrated feasibility of transmitting at even longer distance for the submarine cable operation. The first transatlantic fiber system, TAT8, started its operation in 1988. The third milestone was established when the optical fiber amplifier was invented. Erbium-doped fiber amplifier (EDFA) eliminated the need for installing electro-optic repeaters in the long-haul communication. It further reduced the cost of fiber operation and lifted the economic development barrier for the fiber-optic communication. The telecom industry was then well on its development high way.

Similar to the concept of parallel computing in the microprocessor world, wavelength division multiplexing (WDM) was firstly introduced in the 1970s [29]. WDM is a technology that allows a number of different optical signals (channels) to be transmitted simultaneously in a single fiber

by using multiple laser wavelengths. The idea of WDM was advocated by telecom carriers, as it enabled them to upgrade the bandwidth capacity without overhauling the infrastructure that was already installed. In the 1990s, high capacity WDM systems with up to 80 channels were delivered to the market, capable of carrying terabit/second of information. Fiber-optic technology entered the "Tera-era". With the maturing of the WDM technology, fiber-optic communication presents itself as a viable solution that possesses the merits of low loss, low latency and high bandwidth. As multi-core and many-core microprocessor chips reach the bottleneck in interconnection, the obvious question is can the fiber-optic communication technology be utilized in the microprocessor on-chip interconnection?

#### 1.4 Silicon Photonics

The equivalent question is can the fiber-optic communication system be transformed and fabricated in a form of optical integrated circuit? The concept of "integrated photonics" was firstly introduced around 1970 [30, 31, 32]. An integrated photonic circuit should be able to facilitate the interaction between electrons and photons, using advanced fabrication technique to control the flow of photons on chip. It should contain the counterparts of microwave components that have functions of generating, splitting, coupling, filtering, switching, multiplexing, de-multiplexing and detecting light signals in the on-chip circuit. When this concept is mingled with the semiconductor fabrication technology, a more specific form of "integrated photonics" is born. That is "silicon photonics", using silicon integrated circuit to control the flow of photons. The pioneer works on silicon photonics were conducted by R. Soref in the 1980s and 1990s [33, 34]. The idea of creating cost-effective silicon photonic complementary metal-oxide-semiconductor (CMOS) hybrid "superchip" was investigated. These fundamental research works explored basic on-chip photonic components, including silicon waveguiding structures, silicon electro-optic effects and related fabrication techniques, etc. The results demonstrated the feasibility for the CMOS compatible photonic on-chip communication.

With the rapid development of information technology, silicon is the most studied semiconductor material on earth. Intrinsic silicon has an indirect bandgap of 1.11 eV at room temperature, therefore it is transparent to wavelengths longer than 1100 nm in the near infrared (NIR) region. The absorption loss in silicon material is minimum for the telecommunication wavelength window of 1300 nm and 1550 nm. This is one of the advantages that helps accelerate the mergence of photonics and electronics. Meanwhile, silicon waveguides can be conveniently fabricated on the Silicon-on-Insulator (SOI) wafer. Although the wafer material of choice is different from those used for IC chips, the fabrication process is still virtually the same. The process is CMOS compatible. Without too much modification, silicon photonic devices can be produced in a CMOS foundry. Moreover, with the 130 nm or more advanced lithography technology tools available, single-mode silicon waveguide with several hundred nanometers width can be patterned on SOI wafer. Singlemode silicon waveguide prevents modal dispersion and its core size is about 1000 times smaller than that of a single mode fiber, due to the high index contrast in the forming waveguide of silicon and silica interfaces. Fabrication advancement in 2004 by Vlasov [35] lowered the propagation loss in silicon waveguide to a few dB/cm. Even though the loss factor seems high comparing with the optic fiber, silicon photonics deals with signal transmission at chip scale and a few dB/cm becomes acceptable within several millimeters. At this point, silicon photonic integration became practical.

Although silicon has an indirect bandgap that does not seem to promote light emitting, heterogeneous epitaxy of germanium on silicon creates opportunities for on-chip laser. Lasing from electrically pumped n-type Germanium-on-Silicon Fabry-Perot cavities was observed [36]. Meanwhile, solid-state off-chip laser components, such as amplified spontaneous emission (ASE) source, superluminescent light emitting diode (SLED) and supercontinuum source that provide superior bandwidth and power, are widely available in the market. These off-chip laser devices when coupled via fibers are capable of providing the wavelength spectrum required for the on-chip WDM components. Germanium-on-Silicon heterostructure also emerged as the preferred photodiode for high speed light detection in silicon photonic circuits [37, 38]. Silicon photonic foundries such as IMEC [39] and LETI [40] of ePIXfab/EuroPractice [41, 42] already started offering on-chip germanium photodetector as a feature in their wafer shuttle runs. Concurrently, optical modulators that convert electrical and optical signals were created. Silicon photonic crystal waveguide modulator [43], p-n junction modulator [44] and silicon/electro-optic polymer hybrid modulator [45] looked promising for the on-chip integration. Therefore, the answer to the question at the beginning of this section is YES. Silicon photonic research is moving towards realizing a complete integrated on-chip optoelectronic system. The miniaturization of the optical telecommunication system into the integrated circuit form would deeply revolutionize this ecosystem and further reduce production cost. Silicon photonics is on the horizon of being a matured next generation technology.

In the past, the high cost of the optical interconnection technology could only be justified for the long-haul transmission. Optical interconnect could only be found in the long distance telecommunication backbone. Recently, with the advancement of photonic integration technology, optical interconnect gradually migrates to shorter and shorter communication regions, such as metropolitan area networks (MANs), local area networks (LANs) and Network on chip (NoC). Silicon photonic technology has emerged and will play an important role in speeding up this revolution. No matter for the short distance off-chip communication or for the multi-core and many-core on-chip interconnection, the advantages of optical interconnect over electrical interconnect is apparent. Optical interconnect brings high bandwidth, lower power consumption and lower latency to the communication link [46, 47, 48]. The demand for optical interconnect to replace electrical interconnect is growing stronger. The positive economy benefit and impact of silicon photonics are increasingly being recognized. An initial silicon photonics market starts to surface. Cisco bought silicon-photonics startup Lightwire and Mellanox purchased Kotura. All these moves indicate that in the current telecom and datacom markets, industry leaders and dominant players sense the opportunity in silicon photonics and adjust their strategic market alignment in order to keep the edge for future growth.

#### 1.5 Statement of the Research

The interconnection problem is power dissipation and latency of the interconnection. The interconnection between cores is necessary because cores are necessary. Multiple cores became necessary when the circuit density on the standard size die became so great that the only way designers knew how to harness the computing resources was by limiting the transistors to processor cores that were already understood. No one knows how to layout transistors all over the die and still be able to use them. These cores will continue to generate just as much heat as the transistors within them no matter how they are interconnected. There are references made in our work to architectures where 30% or more of the chip dissipation is in the interconnect [23, 49]. This was not the case in rack to rack interconnects where we were clearly told that the interconnection dissipates negligible heat compared to the processors on a board, on a backplane or in a rack. Not all multicore processor architectures generate so much heat in the interconnect. The problem may become worse with the increasing number of cores.

The voltage and current required by metal stripe circuits do not scale well with size of stripes and frequency of transmission. An important measurement of interconnect system stability is the system receiver signal-to-noise ratio (SNR). The SNR is quantified by

$$SNR = \frac{P_{\rm rec}}{N_r + N_x} \tag{1.1}$$

where  $P_{\rm rec}$  is the signal level received at detector,  $N_r$  is the receiver noise generated by thermal noise, shot noise and dark current noise, and  $N_x$  is the crosstalk noise. The receiver noise  $N_r$  is proportional to the detection bandwidth. That is to say, the signal power must increase at least linearly with bandwidth to preserve the SNR. As circuits become denser and wires size shrinks down, electrical interconnect wires are packed closer together, the capacitance per unit length increases as size decreases ( $C = \varepsilon A/d$  where separation distance d decreases). The resistance per unit length increases with decreasing size ( $R = \rho L/S$  where wire cross-section area S shrinks down). The total resistance and capacitance increase with length of the interconnection. Because the RC time constant increases, the electronic noise (Johnson noise) increases in the circuits. This raises the crosstalk noise  $N_x$  at the receiver, therefore more power must be applied to the interconnect to preserve the SNR.

To reduce latency in long wires, the length of interconnections can be kept shorter by using

repeaters in the lines [50]. However, repeaters require more power be dissipated and it may end up with the increased total power overhead. Another solution that is being tested is use of only nearest neighbor connections in order to support packet situation. Packet-switching network moves data in small blocks (pocket) based on the destination of each block. Data will be reassembled into normal sequence once the block is received. This will increase power dissipation but more importantly leads to an exponential increase in latency, due to runtime multihop data buffering, resource arbitration and link contention [51].

A broadcast interconnection solves latency as well as power dissipation problems. Broadcast avoids long copper wire and transmits data at light speed. This would greatly reduce latency. Meanwhile, silicon optical waveguide strongly confines propagation waves and has excellent power efficiency. Our results show significantly power dissipation reduction can be achieved in photonic broadcast design [52]. However, a broadcast interconnection may not improve performance as much as is necessary to justify such a disruptive technology. A silicon photonic broadcast subnetwork on top of CMOS circuit would require hybrid integration of both technologies. CMOS circuit production has high yield but silicon photonic fabrication technology is yet mature. Silicon photonic hybrid integration has to demonstrate orders of magnitude in performance improvement for further hybrid integration development. In many cases, more communication layers may be necessary, for example, the broadcast layer may be employed to circuit interconnect channels for large scale node-to-node data transfer that is not so latency critical as short burst synchronization messages. The broadcast layer can be used for transferring latency-critical global synchronization messages in the critical path of system performance, while circuit switching layer is setup for large scale data transfer.

To fully utilize the advantage of deploying broadcast interconnect, it is of interest to see whether broadcast communication theme could eliminate the switching layer in between sender and receiver which causes most of the latency and consumes significant portion of the on-chip power. If silicon photonic WDM technology applied to the broadcast interconnect could be able to create enough separate channels for all the nodes in the network, there would be no need to use circuit switching. It is also in the research interest to investigate what can be achieved for broadcast interconnect with today's technology.

#### 1.5.1 The Vision

The importance of silicon photonics has drawn widespread interests in the academia and research community. The effort by our team at the Guided Wave Optics Lab (GWOL) of the University of Colorado Boulder started in 2008 under the NSF "EMT-NANO" project<sup>2</sup>. We focused on designing and characterizing components for the next generation silicon photonic interconnect in the multi-core and many-core environment. This thesis comes out of my effort in participating the "EMT-NANO" project and related on-going projects<sup>3</sup>.

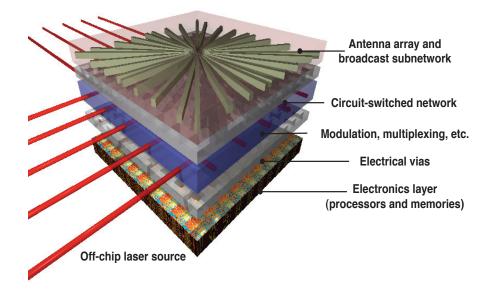

Figure 1.3: A schematic plot of 3D-IC network design. Off-chip light source is connected to an on-chip silicon photonic layer that modulates and multiplexes/demultiplexes the light signals. A CMOS electronic control layer at the bottom is connected to the silicon photonic layer through electrical vias. The processed signals is switched and broadcast using antenna array and broadcast subnetwork.

Our research direction has been guided under one silicon photonic broadcast optical intercon-

<sup>&</sup>lt;sup>2</sup> National Science Foundation (NSF) Award #CCF-0829950 — EMT-NANO: Broadcast Optical Interconnects for Global Communication in Many-Core Chip-Multiprocessor.

$<sup>^3</sup>$  Part of the content in this thesis is from the papers listed in Section 1.5.2 that I have published or that is under review.

nection architecture. Figure 1.3 is a depiction of the architecture we envisioned. The whole system is a 3D hybrid integration of SOI silicon photonic layer and CMOS electronics layers. The system is capable of light detecting, modulating, multiplexing/demultimplaxing, switching and broadcasting. At the bottom sit the multi-core and many-core processors and memories, the control units. This layer connects the middle silicon photonic layers through electrical vias. Broadband light source is sliced into many channels and routed via photonic circuit-switching network. The processed light signal is sent out via the top antenna array and broadcast subnetwork layer. WDM technique is fully deployed in this 3D on-chip network. Together, this architecture addresses the latency, bandwidth and power efficiency issues that nest in traditional electrical interconnect network.

#### 1.5.2 List of Publications and Origins of Contribution

GWOL team worked collectively on the "EMT-NANO" project. Our work has resulted in many journal and conference publications over the course of the project. In this section, I include these publications and describe the origins of contribution.

#### 1.5.2.1 Journal Publications

J1 X. Chen, M. Mohamed, Z. Li, L. Shang, and A. R. Mickelson, "Process variation in silicon photonic devices," Appl. Opt., vol. 52, no. 31, pp. 7638–7647, Nov 2013.

Contribution: The wafer-scale process variations on devices of interest are characterized and analyzed. Chen carried out the experiments and wrote the manuscript; co-authors edited the manuscript.

J2 X. Chen, Z. Li, M. Mohamed, L. Shang, and A. R. Mickelson, "Parameter extraction from fabricated silicon photonic devices (in review)," Appl. Opt., 2013.

Contribution: A simple method is proposed to determine effective indices of fabricated devices and a calibrated T-matrix model is presented for device of interest. Chen finished the analysis and wrote the manuscript; co-authors edited the manuscript. J3 H. Zhou, X. Chen, D. Espinoza, A. Mickelson, and D. Filipovic, "Nanoscale optical dielectric rod antenna for on-chip interconnecting networks," Microwave Theory and Techniques, IEEE Transactions on, vol. 59, no. 10, pp. 2624–2632, 2011.

Contribution: A new on-chip optical dielectric rod antenna array is simulated, fabricated and analyzed. Zhou designed the antenna and wrote the manuscript; Chen did physical and optical characterization of the fabricated antenna design and wrote the manuscript on experiment; Espinoza did polymer coating for the antenna; Mickelson and Filipovic edited the manuscript.

J4 D. Espinoza, X. Chen, M. Mohamed, H. Zhou, E. Dudley, W. Park, D. Filipovic, and A. Mickelson, "Nanometric polymer coatings for silicon on insulator circuits," in Proc. SPIE 8173, Photonics 2010: the 10th International Conference on Fiber Optics and Photonics, Aug 2011, p. 81730H.

Contribution: The effect of polymer coating on variety of silicon photonic devices is investigated. Espinoza and Mickelson wrote the manuscript. Espinoza did polymer coating and part of microscope imaging; Chen did optical characterization of the devices of interest, part of microscope imaging and writing the manuscript on optical measurement; co-authors edited the manuscript.

J5 M. Mohamed, Z. Li, X. Chen, L. Shang, and A. Mickelson, "Reliability-aware design flow for silicon photonics on-chip interconnect (in press)," Very Large Scale Integration (VLSI) Systems, IEEE Transactions on, no. 99, Oct 2013.

Contribution: A reliability-aware design flow to address variation-induced reliability issues is proposed and analyzed. Mohamed and Li did analysis and wrote the manuscript; Chen provided physical and optical characterization data of the devices of interest and built Tmatrix models; co-authors edited the manuscript.

J6 Z. Li, M. Mohamed, X. Chen, E. Dudley, K. Meng, L. Shang, A. Mickelson, R. Joseph,

M. Vachharajani, B. Schwartz, and Y. Sun, "Reliability modeling and management of nanophotonic on-chip networks," Very Large Scale Integration (VLSI) Systems, IEEE Transactions on, vol. 20, no. 1, pp. 98–111, 2012.

Contribution: Run-time techniques are proposed to address on-chip system variation in photonic network. Li and Mohamed did analysis and wrote the manuscript; Chen provided physical and optical characterization data of the devices of interest; co-authors edited the manuscript.

J7 Z. Li, M. Mohamed, X. Chen, A. Mickelson, and L. Shang, "Device modeling and system simulation of nanophotonic on-chip networks for reliability, power and performance," in Proceedings of the 48th Design Automation Conference, ser. DAC '11. New York, NY, USA: ACM, 2011, pp. 735–740.

Contribution: A novel modeling and simulation methodology is proposed for silicon photonic network that is affected by process and thermal variations. Li and Mohamed did analysis and wrote the manuscript; Chen provided physical and optical characterization data of the devices of interest and built T-matrix models; co-authors edited the manuscript.

J8 Z. Li, M. Mohamed, X. Chen, H. Zhou, A. Mickelson, L. Shang, and M. Vachharajani, "Iris: A hybrid nanophotonic network design for high-performance and low-power on-chip communication," J. Emerg. Technol. Comput. Syst., vol. 7, no. 2, pp. 8:1–8:22, Jul 2011.

Contribution: An Iris topology is proposed for silicon photonic on-chip network. Li and Mohamed did analysis and wrote the manuscript; Chen provided physical and optical characterization data of the devices of interest; co-authors edited the manuscript.

J9 Z. Li, M. Mohamed, H. Zhou, L. Shang, A. Mickelson, D. Filipovic, M. Vachharajani, X. Chen, W. Park, and Y. Sun, "Global on-chip coordination at light speed," Design Test of Computers, IEEE, vol. 27, no. 4, pp. 54–67, 2010. Contribution: Multi-core chip interconnect and broadcasting concept with silicon photonics are discussed and analyzed. Li and Mohamed did analysis and wrote the manuscript; Zhou designed the antenna; Chen provided physical and optical characterization data of the devices of interest; co-authors edited the manuscript.

#### 1.5.2.2 Conference Publications

C1 X. Chen, D. Espinoza, E. Dudley, Z. Li, M. Mohamed, Y. Cui, W. Park, L. Shang, and A. Mickelson, "Polymer-clad silicon on insulator slot modulator," in Advanced Photonics. Optical Society of America, 2011, p. IMB7.

Contribution: A polymer-clad slot waveguide with FIB deposited electrodes for phase modulator is fabricated and investigated. Chen did physical and optical characterization of the devices of interest and wrote the manuscript on introduction and fabrication and measurement; Espinoza did polymer coating; Dudley did simulation work and wrote the manuscript on design; Cui did FIB deposition work; co-authors edited the manuscript.

C2 X. Chen, Z. Li, M. Mohamed, L. Shang, and A. Mickelson, "Matrix analysis of nanophotonic devices," in Photonics 2010: the 10th International Conference on Fibre Optics and Photonics, Guwahati, India, Dec 2010.

Contribution: T-matrix modeling technique is proposed for silicon photonic devices. Chen did the analysis and wrote the manuscript; co-authors edited the manuscript.

C3 X. Chen, M. Mohamed, B. Schwartz, Z. Li, L. Shang, and A. Mickelson, "Racetrack filters for nanophotonic on-chip networks," in **Integrated Photonics Research, Silicon and Nanophotonics and Photonics in Switching**. Optical Society of America, 2010, p. ITuB5.

Contribution: Three different-order racetrack resonators are fabricated and analyzed. Chen did physical and optical characterization of the fabricated devices and wrote the manuscript on theory and experiment; Mohamed analyzed and wrote the manuscript on numerical simulation; co-authors edited the manuscript.

C4 D. Espinoza, X. Chen, H. Zhou, D. Filipovic, and A. Mickelson, "Nano-photonic antennas propagation through a polymer medium," in Photonics 2010: the 10th International Conference on Fibre Optics and Photonics, Guwahati, India, Dec 2010.

Contribution: The on-chip antenna propagation with polymer cladding is investigated. Espinoza did polymer coating and wrote the manuscript; Chen provided physical and optical characterization data of the devices of interest; Zhou designed the antenna; co-authors edited the manuscript.

C5 M. Mohamed, Z. Li, X. Chen, A. Mickelson, and L. Shang, "Modeling and analysis of micro-ring based silicon photonic interconnect for embedded systems," in Proceedings of the seventh IEEE/ACM/IFIP international conference on Hardware/software codesign and system synthesis, ser. CODES+ISSS '11. New York, NY, USA: ACM, 2011, pp. 227–236.

Contribution: Analytical models are developed and calibrated for widely used passive and doped micro-ring resonators. Mohamed and Li did analysis and wrote the manuscript; Chen provided physical and optical characterization data of the devices of interest and built T-matrix models; co-authors edited the manuscript.

C6 M. Mohamed, Z. Li, X. Chen, L. Shang, A. Mickelson, M. Vachharajani, and Y. Sun, "Power-efficient variation-aware photonic on-chip network management," in Low-Power Electronics and Design (ISLPED), 2010 ACM/IEEE International Symposium on, 2010, pp. 31–36.

Contribution: Run-time management solution, inter-channel hopping, wavelength tuning and routing are proposed for silicon photonic network that is affected by variations. Mohamed and Li did analysis and wrote the manuscript; Chen provided physical and optical characterization data of the devices of interest; co-authors edited the manuscript.

C7 M. Mohamed, Z. Li, E. Dudley, X. Chen, L. Shang, W. Park, and A. Mickelson, "Adiabatic couplers for linear power division," in Advanced Photonics. Optical Society of America, 2011, p. IMD6.

Contribution: A silicon photonic adiabatic 3dB coupler is designed and fabricated. Mohamed designed the structure and wrote the manuscript; Chen provided physical and optical characterization data of the device of interest; co-authors edited the manuscript.

### 1.6 Thesis Outline and Origins of Contribution

#### 1.6.1 Thesis Outline

The work presented in this thesis focuses on the fabrication and characterization related issues in silicon photonic technology.

Chapter 1 examines the development trend for microprocessor and the potential problems for on-chip electrical interconnect. A brief history of optical communication is introduced and the emergence of silicon photonic technology for on-chip interconnect application is discussed. The scope of our research on silicon photonics is presented.

Chapter 2 introduces the wafer-scale fabrication for silicon photonic devices and describes our in-house photonic measurement testbed for device optical characterization. The majority of the content focus on the discussion of several fundamental silicon photonic devices, namely grating coupler, micro-ring and racetrack resonator, directional coupler, optical on-chip antenna array and photonic crystal. Their operation mechanisms and optical transfer functions are explained.

Chapter 3 presents the characterization work of the wafer-scale process and thermal variations in three classes of devices including micro-ring, racetrack and directional coupler. Measurement results on thermal variation verify the accuracy of the measurements. Process variation shows a uniformly wafer-scale "random walk" pattern across the devices. The results provide a quantitative base for fabrication-yield-aware design. Chapter 4 talks about phenomenological modeling of using T-matrix to describe fabricated photonic devices. It shows that the effect of process and thermal variations which exist in the fabricated devices can be well expressed in the effective index. A simple method that combines Comsol full wave simulation and analytical models is presented for extracting the effective index out of fabricated photonic devices. T-matrix with calibrated effective index values displays excellent fitting result for the optical measurements.

Chapter 5 introduces a variation-aware on-chip broadcast interconnect design for multi-core processor. This design utilizes the demonstrated WDM micro-rings and any-one-to-all antenna array to create broadcasting channels. With the cluster design of micro-rings, it shows this architecture can be realized with today's technology.

Chapter 6 concludes this topic.

#### 1.6.2 Origins of Contribution

In Chapter 1, Section 1.1 to Section 1.4 are the review of literature. Section 1.5 to Section 1.6 are my original work.

In Chapter 2, the operation mechanism of the antenna in Section 2.4.4.2 and the introduction of the photonic crystal in Section 2.4.5.1 are written by Prof. Alan Mickelson in our publication [J4] of Section 1.5.2.1 and adapted in this thesis. The rest of sections are my original work.

Chapter 3 to Chapter 6 are my original work. Prof. Alan Mickelson, Dr. Zheng Li and Dr. Moustafa Mohamed help edit the contents in Chapter 3 and Chapter 4.

### Chapter 2

# Fabrication, Measurement and Design Characterization of Silicon Photonic Devices

### 2.1 Introduction

For the interconnection network of the multi-core and many-core systems, one of the great advantages of silicon photonics is that it offers on-chip wavelength division multiplexing (WDM) technology. Silicon photonics technology brings the WDM from the long-haul optical telecommunication to the chip scale. The use of WDM enables bidirectional communications. It can increase the bandwidth capacity by a large factor, depending on how many wavelength channels are deployed simultaneously. It addresses the bandwidth constraint in current on-chip communication network at ease.

Figure 2.1: A schematic diagram of a silicon photonic on-chip WDM network.

A complete WDM functioning link is comprised of a broadband light source, demultiplexer and multiplexer units at the transmitter side, waveguide with multiple routes that compose of the WDM network, demultiplexer unit at the receiver side. Figure 2.1 illustrates the idea of a silicon photonc on-chip WDM network. When the broadband light signal is off-chip, it can be delivered to the on-chip waveguide via grating coupler. The signal is then split into many wavelength channels by the demultiplexer at the transmitter. Each wavelength passes through individual electro-optic (EO) modulation device and the electrical digital information is transformed into the optical information via EO conversion. All the modulated wavelengths are combined and broadcast out at the multiplexer unit. At the receiving end, the demultiplexer unit would slice the wavelength bundle into separate wavelength channels for the detectors. On-chip germanium detector is oftentimes used for high-speed detection. At the destinations, signals are amplified and processed individually by CMOS circuit components.

In this chapter, we will discuss the basic components of a WDM link in the silicon photonic onchip network. Our effort focuses on the passive devices. In Section 2.2, the wafer-scale fabrication is introduced. In Section 2.3, the details of our in-house measurement setup is described. In Section 2.4, several key photonic device components are introduced and their optical performance is characterized.

#### 2.2 Fabrication

All silicon photonic devices used in our study were fabricated at ePIXfab [41] during the period 2009-2012. ePIXfab offers a standard CMOS-compatible photonic foundry process where the 8-inch Silicon-on-Insulator (SOI) wafer (Soitech) is adopted as the standard substrate. The functional layers of the wafer are comprised of a 220-nm ( $\pm 3.5$  nm) crystalline silicon layer on top of a 2- $\mu$ m buried silicon oxide layer. The silicon oxide layer is sufficiently thick to reduce optical leakage through the substrate. Deep UV lithography of 193 nm line is used in fabricating our designs. The wafers that we measure are diced into repeated units (dies) across the wafer. The lithography exposure is flashed in steps of increasing/decreasing dosage across the columns from

Figure 2.2: Schematic depiction of an 8-inch wafer that details the vertical cells (repeated dies) of a single column. The lithographic exposure was swept horizontally such that each column received a different exposure, but each cell within a column received nominally the same exposure.

left to right, as depicted in Figure 2.2. As a result, different columns consist of devices with slightly different physical dimensions for a single design. Only one column contains the desired physical dimensions of our design. Our optical measurement characterization is focused on this particular column. Within one column, the devices of each design repeated on the dies receive a fixed amount of exposure dosage and have nominally same physical dimensions. The size of each die on the wafer from LETI ([40] an ePIXfab/EuroPractice [42] facility) is smaller than those of wafers from IMEC ([39] another ePIXfab/EuroPractice facility). There are, therefore, more dies in one single column on the LETI wafer. The number of dies per column can reach up to 28 dies on the LETI wafer and 19 dies on the IMEC wafer depending on the location on the wafer. Moreover, within one die, devices are laid out row by row with 25  $\mu$ m separation distance vertically in between.

## 2.3 Measurement Apparatus and Its Use

All the device measurements are carried out in-house using the apparatus depicted in Figure 2.3. The system employs a broadband super luminescent light emitting diode (SLED) light

Figure 2.3: Schematic of the in-house measurement setup. The set-up is comprised of a SLED light source, an optical spectrum analyzer, two single mode fibers that couple light to and from the photonic chips, two sub-micron accurate 3D motion controllers, a visible camera that monitors the fiber movement and a temperature controlled sample stage.

Figure 2.4: Photo of the in-house measurement setup. It shows the physical images of the key components of the setup.

source whose wavelength range is 1480-1600 nm. The photonic chip is placed on a temperature controlled sample stage. A single mode fiber delivers the light signal to the photonic chip where

light is coupled into device through a grating coupler located at one end of each device. The grating coupler is optimized for passing transverse electric (TE) modes where E-field is parallel to the grating grooves. After passing through the device, light is coupled out through another TE-mode grating coupler into an optical spectrum analyzer (OSA) via the second single mode fiber. The maximum resolution of the OSA is 80 pm throughout the wavelength range of 600-1700 nm. The fiber movements are precisely controlled by two 3D motion controllers which are capable of submicrometer adjustment. A visible camera is used to monitor the movement of the two fiber tips. Two probes are used to apply electrical signals to the photonic chip where necessary. Figure 2.4 displays the physical image of the setup in our lab.

## 2.4 Design Characterization of Silicon Photonic Devices

In this section, we take a closer look at the silicon photonic devices that are found in a WDM communication link. These components include grating coupler, waveguide, micro-ring, racetrack, directional coupler, broadband antenna and photonic crystal.

## 2.4.1 Grating Coupler

#### 2.4.1.1 Introduction

In order to characterize and operate a silicon photonic, light signal has to be efficiently delivered to the device. Recently, on-chip light source has been demonstrated in experiment [36, 53, 54]. However, before the on-chip light source technology produces matured reliable products, the silicon photonics development depends on off-chip light source as the light signal generator. How to effectively couple light into a silicon waveguide becomes an interesting and challenging problem. Oftentimes it becomes crucial to the success of a photonic circuit design when the power budget is tight. One straightforward way of coupling light into a silicon waveguide is end-fire coupling [55, 56]. In the end-fire coupling setup, the efficiency coupling depends on the spatial overlap of a free-space Gaussian beam in fiber and a bound waveguide mode. Focusing lens is

regularly implemented to help increase the overlap therefore to get higher efficiency. The setup could be bulky and not flexible. The other issue with end-fire coupling is that it requires a clean and well-cut waveguide end-face. It usually involves wafer cleaving and polishing. It complicates the post-process procedures and lower the yield.

One way to get around these troubles is to use grating coupler as the coupling mechanism. Grating coupler allows out-of-plane coupling. That is, launching the mode via vertical coupling instead of horizontal coupling. Grating coupler can be fabricated on the SOI wafer via standard CMOS technology and resembles periodic structures on the surface. With grating coupler, a waveguide mode can be excited by a free-space beam when the Bragg condition is satisfied. The vertical coupling eliminates the wafer cleaving process. Fiber that delivers the light signal can move above wafer for coupling and presents an advantage for fast wafer testing process. Grating coupler is convenient in use and becomes a standard in silicon photonic technology [57].

Figure 2.5: A schematic setup of a single-mode fiber to grating coupler. The core diameter of a sing mode fiber is about 10  $\mu$ m. The grating coupler area on waveguide is comparable to this size.<sup>1</sup>

<sup>&</sup>lt;sup>1</sup> Image credit: ePIXfab, "Silicon photonics platform: building a vertical fibre coupling setup", Dec. 2006.

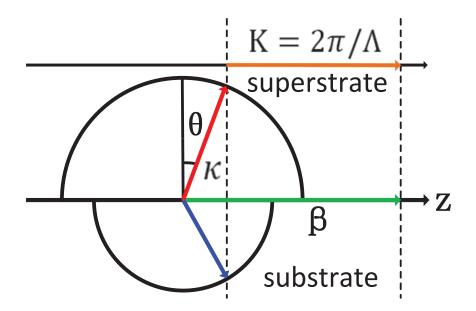

Figure 2.6: The Bragg condition for grating coupling mechanism.  $\theta$  and  $\kappa$  are the coupling angle and the wave vector of the incident beam.  $\Lambda$  is the grating period.  $\beta$  is the propagation constant for the waveguide mode.

Figure 2.5 displays the fiber-to-grating setup where the core of a single-mode fiber is aligned to the area of grating coupler. The area of the grating coupler is comparable to that of the fiber core end-face. Once a waveguide mode is excited, it passes through a low loss taper waveguide region in order to be converted to a single mode of the input wavelength. The Bragg condition for the grating coupler can be written in the following form:

$$\kappa \sin(\theta) n_{\text{sup}} + mK = \beta, \qquad m = 1, 2, 3... \tag{2.1}$$

where  $\kappa = 2\pi/\lambda$  is the wave number of the input wavelength,  $\theta$  is the incident angle with respect to the surface normal,  $n_{sup}$  is the refractive index of the superstrate, m is the grating diffraction number,  $K = 2\pi/\Lambda$  in which  $\Lambda$  is the grating period and  $\beta$  is the propagation constant of the excited waveguide mode.  $\beta = 2\pi n_{eff}/\lambda$  where  $n_{eff}$  is the effective index of the grating coupler. The Bragg condition for first order diffraction grating is plotted in Figure 2.6. m = 1 in this case.

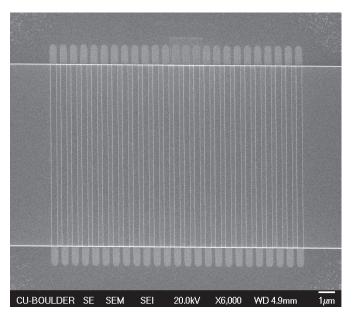

Figure 2.7: A scanning electron microscope image of a grating coupler that was fabricated at the ePIXfab. The area size of the grating coupler is about 10  $\mu$ m × 15  $\mu$ m.

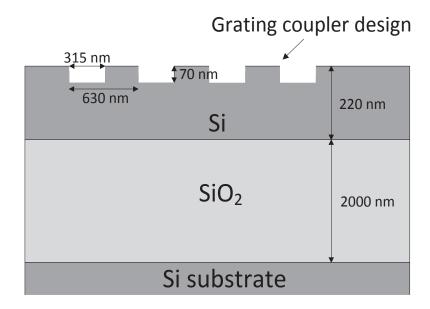

Figure 2.8: Schematic of the cross-section view of the grating coupler design on the SOI wafer. The SOI wafer is comprised of a silicon substrate, a  $2-\mu m$  thick silicon dioxide insulating layer buried under a 220-nm silicon device layer. In the grating coupler area, the grating groove is shallow-etched about 70 nm down the surface. The trench width is around 315 nm and the pitch width is about 630 nm in total.

Our silicon photonic devices which were fabricated at the ePIXfab all have standard grating coupler. Figure 2.7 shows a scanning electron microscope (SEM) image of a fabricated grating coupler. The width of the grating coupler region is 10  $\mu$ m and the length of the region is about 15  $\mu$ m. Figure 2.8 depicts the cross-section view of the grating coupler design on the SOI wafer. The grating coupler is fabricated on the 220-nm silicon layer. The grating groove is etched 70 nm down the surface. The grating coupler design is optimized for the operation in the wavelength range of 1550 nm - 1560 nm where its groove trench width is about 315 nm with a total pitch width of 630 nm. The grating coupler acts as a polarization filter. This specific design couples the TE polarized light well into the grating with 10° of incident angle. TE polarization is defined as the direction parallel with the grating grooves. Maintaining TE polarization in waveguide and device is specially convenient for polarization sensitive devices and applications.

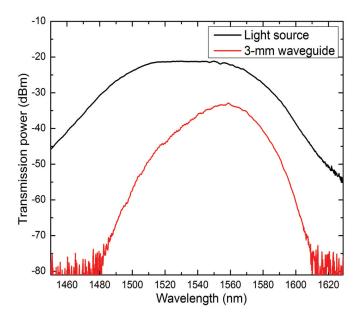

Figure 2.9: Grating coupler efficiency measurement. The black curve shows the input light source spectrum and power level. The red curve is the output light spectrum and corresponding power after passing through a 3-mm long bare waveguide with two grating couplers at both ends. The maximum transmission peak is at around 1560 nm.

We characterized the coupling efficiency of grating coupler in our lab. Figure 2.9 displays the measurement result. The input light source spectrum and power was captured by the OSA directly from a SLED light source. The light power was coupled into a 3-mm long bare waveguide on one

end firstly via a grating coupler and then coupled out via a second identical grating coupler on the other end of the waveguide. The output power spectrum was recorded by the OSA. As shown in the plot, the maximum transmission peak is at around 1560-nm wavelength. The power loss for the maximum transmission is about -10 dB. The ePIXfab standard waveguide propagation loss is about 2.5 dB/cm. A 3-mm long waveguide contributes about -0.75 dB loss. Therefore, the coupling efficiency for a single grating coupler is about 30 % at the optimized wavelength.

# 2.4.2 Ring Resonator

#### 2.4.2.1 Introduction

One of the important functions of a WDM system is enabling switching and routing different wavelength channels. In a silicon photonic WDM system, this function can be realized by using variety of ring resonators designs, such micro-ring and racetrack resonators. Due to its resonant structure, ring resonator is a wavelength-selective device. It can be used to slice a broadband spectrum into WDM channels for downstream processing. By using silicon photonic ring resonator, efficient on-chip wavelength add-drop filters [58, 59] and optical network switches [60, 61] have been demonstrated. Moreover, ring resonator can realize high speed modulator with proper doping level inside its waveguide structures [62, 63, 64]. Ring resonator is versatile in terms of on-chip wavelength-selective functionality.

Another attractive feature of ring resonator for the integrated photonics is that its size can be very compact. A salient feature of the SOI waveguide is its high-index contrast between the waveguide interface materials with 3.48 for silicon, 1.45 for silicon dioxide and 1 for air. High-index contrast allows strong confinement of optical mode inside waveguide, therefore enabling extremely compact ring resonator devices. Micro-ring resonators with radii less than 2  $\mu$ m were produced [65, 66]. The small foot print of ring resonator promotes high-density photonic device integration. Although tight waveguide bending induces optical radiation loss, balancing between bending loss and device size offers photonic circuit architect more flexibility. Ring resonator generates more and more interest in silicon photonic device design.

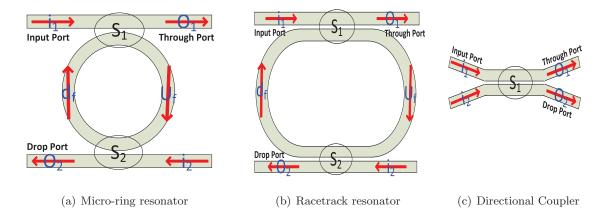

(a) Micro-ring resonator

(b) Racetrack resonator

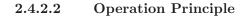

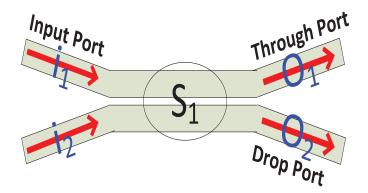

Figure 2.10: Schematics of two kinds of ring resonator.  $S_1/S_2$  are the coupling regions,  $i_1/i_2$  are the input ports,  $O_1/O_2$  are the output ports in the devices and  $d_f/U_f$  are the connecting ports in the resonance structures.

In general, ring resonator is a four-port device that consists of a circular resonant cavity and two coupling waveguides. Figure 2.10 illustrates two kinds of ring resonator: micro-ring resonator and racetrack resonator. They both have two input ports  $i_1/i_2$  and two output ports  $O_1/O_2$ . The design difference lies in the coupling region. Micro-ring resonator has a circular ring that is pointcoupled to its adjacent waveguides as displayed in Figure 2.10(a), whereas in racetrack resonator as shown in Figure 2.10(b), the coupling region is elongated into two straight lines parallel with the neighboring waveguides. Optical waves inside the input waveguides are evanescently coupled to the resonant cavity and travel round trips inside the cavity. Resonance condition is satisfied when the phase shift of the coupled waves built up inside the cavity equals  $2\pi m$  where m is an integer. Resonant waves are then coupled out through the output ports. Comparing with the microring resonator, racetrack resonator provides longer coupling length, allowing for broader spectral responses. For a ring resonator, its resonant wavelength  $\lambda_{res}$  is defined as:

$$\lambda_{\rm res} m = L n_{\rm eff}, \qquad m = 1, 2, 3...$$

(2.2)

where L is the circumference of the ring resonant cavity,  $n_{\text{eff}}$  is the effective index of the ring cavity waveguide, and m is an integer. It means a resonant wavelength is selected when the optical length of the ring structure equals to a number of times the specific wavelength and the rest of wavelengths are suppressed by the cavity.

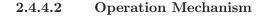

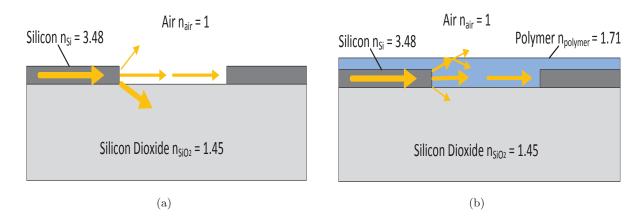

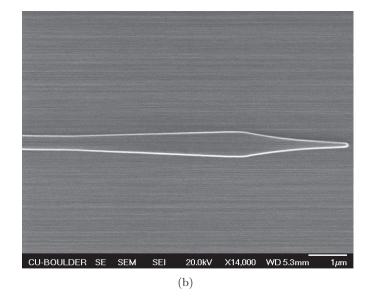

Another important parameter for a ring resonator is the free spectral range (FSR). It is defined as the wavelength spacing between adjacent resonant wavelengths and can be approximated as: