## Efficient SMT Solving for Hardware Model Checking

by

Hyondeuk Kim

B.E., Ajou University, Korea, 2002

M.S., University of Colorado at Boulder, USA, 2005

A thesis submitted to the

Faculty of the Graduate School of the

University of Colorado in partial fulfillment

of the requirements for the degree of

Doctor of Philosophy

Department of Electrical and Computer Engineering

2010

This thesis entitled: Efficient SMT Solving for Hardware Model Checking written by Hyondeuk Kim has been approved for the Department of Electrical and Computer Engineering

Fabio Somenzi

Professor Aaron Bradley

Date \_\_\_\_\_

The final copy of this thesis has been examined by the signatories, and we find that both the content and the form meet acceptable presentation standards of scholarly work in the above mentioned discipline.

Kim, Hyondeuk (Ph.D., Electrical and Computer Engineering)

Efficient SMT Solving for Hardware Model Checking

Thesis directed by Professor Fabio Somenzi

The Satisfiability Modulo Theories (SMT) problem is a decision problem for the satisfiability of first-order formulas with background theories. In the last few years, decision procedures for SMT have been studied intensively, and they are applied successfully to hardware and software verification, compiler optimization, scheduling, and other design automation areas. In particular, during our study, we have found that they are also applicable to constrained random simulation.

SMT solvers have been effectively applied to software verification with predicate abstraction [BMMR01, LNO06] and bounded model checking [GG08, AMP06]. Only to a lesser extent, they have been applied to hardware verification. In today's hardware designs, bit-level and word-level operations are often tightly intermingled. On some designs, a bit-level model checker may perform better than a word-level model checker or vice versa.

In my dissertation, we study several efficient SMT solving techniques that can be applied to hardware model checking and constrained random simulation. In particular, we present a hybrid approach [KJS07a, KS06] for integer difference logic that combines finite instantiation method with Bellman-Ford algorithm. In addition, we present an efficient term-ITE conversion method [KSJ09] that improves SMT solving by word-level simplifications. Efficiency of these techniques have been shown in our SMT solver SatEEn that won the 1st places in **Integer Difference Logic** (IDL) and **Linear Integer Arithmetic Logic** (LIA) divisions of SMT Competition 2009.

In SMT-based model checking, an efficient encoding plays an important role along with the efficient SMT solving. For hardware model checking, we propose an SMT-based model checking system that consists of modeling and constraint solving components. The modeling component selectively decides the encoding method by analyzing the model, and the constraint solving component uses either **Linear Integer Arithmetic Logic** (LIA) or **Bit-Vector** (BV) solver for the encoding. On the other hand, hardware modeling is nontrivial since the behavior of hardware is described with the detailed event semantics of Standard Verilog [IEE06]; hence we define a subset of Verilog with restrictions that guarantee behavioral equivalence between verification condition and simulation of synchronous hardware. The restrictions lead to a concise verification condition and allow controlled nondeterminism that can be easily eliminated for synthesis. In addition, we propose an encoding method that improves SMT solving by maximizing the use of word-level information. For constrained random simulation, we propose to use word-level simplification [KJR<sup>+</sup>08] that reduces the bit-width of each variable in the design.

#### Acknowledgements

I am extremely grateful to my advisor Professor Fabio Somenzi for his guidance, encouragement and patience during my graduate studies. I started to learn how to do research by conquering several peaks and taking extra credits in the Rocky Mountains with him. Whenever I faced an obstacle during my research, he has always guided me to the right direction to find a solution to the problem. I also would like to thank Professor Clark Barrett, Professor Aaron Bradley, Professor Sriram Sankaranarayanan and Professor Manish Vachharajani for kindly serving as my thesis committee and providing valuable suggestions that improved the quality of my thesis.

During my study, I had great opportunities to work on real-world problems in formal verification area. I would like to thank Dr. Chao Wang and Dr. Aarti Gupta for giving such an opportunity to work on hardware model checking problems in NEC Laboratories. I also would like to thank Dr. Kavita Ravi, Dr. HoonSang Jin, and Dr. Robert P. Kurshan for giving an opportunity to apply my work to constrained random simulation in Cadence Design Systems.

The members of our research group made my work more interesting and fun through many discussions. I would like to thank HoonSang Jin, Hyojung Han, and Saqib Sohail for sharing interesting ideas about my work. Many thanks to HoonSang Jin and Hyojung Han for enjoying the research and hiking together and encouraging me to finish my thesis.

Finally, I would like to thank my parents for their love and support. Without their sacrifice, I would not be able to finish this thesis. I dedicate this thesis to them.

# Contents

# Chapter

| 1 | Intro | luction 1                                                                                                                                                                     |   |

|---|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|   | 1.1   | Background                                                                                                                                                                    |   |

|   | 1.2   | Thesis Contribution                                                                                                                                                           | í |

|   | 1.3   | Thesis Organization    5                                                                                                                                                      | i |

| 2 | Preli | ninaries 7                                                                                                                                                                    | , |

|   | 2.1   | Satisfiability Modulo Theories                                                                                                                                                | 1 |

|   |       | 2.1.1 Bit-Vector Logic                                                                                                                                                        | , |

|   |       | 2.1.2 Linear Integer Arithmetic Logic                                                                                                                                         | , |

|   |       | 2.1.3 $BV \cup LIA \operatorname{Logic} \ldots \ldots$ | ) |

|   |       | 2.1.4 Integer Difference Logic                                                                                                                                                | ) |

|   |       | 2.1.5 DPLL(T)                                                                                                                                                                 |   |

|   | 2.2   | Model Checking                                                                                                                                                                | , |

|   | 2.3   | Hardware Description Language                                                                                                                                                 | ; |

| 3 | Finit | e Instantiation for Integer Difference Logic 17                                                                                                                               | , |

|   | 3.1   | Introduction                                                                                                                                                                  | , |

|   | 3.2   | Preliminaries                                                                                                                                                                 | ; |

|   | 3.3   | Minimizing the Abstract Models                                                                                                                                                | ) |

|   | 3.4   | Bounds on Solutions                                                                                                                                                           | ) |

|   |       | 3.4.1 Bound Computation                               | 22 |

|---|-------|-------------------------------------------------------|----|

|   |       | 3.4.2 Inconsistency Check for Partial Interpretations | 23 |

|   |       | 3.4.3 Consistency Check for Abstract Models           | 24 |

|   | 3.5   | Algorithm                                             | 25 |

|   |       | 3.5.1 The Theory Solver                               | 26 |

|   | 3.6   | Related Work                                          | 32 |

|   | 3.7   | Experimental Results                                  | 33 |

|   | 3.8   | Conclusions                                           | 36 |

| 4 | Effic | cient Term-ITE Conversion                             | 38 |

|   | 4.1   | Preliminaries                                         | 40 |

|   | 4.2   | Term-ITE Conversion                                   | 41 |

|   |       | 4.2.1 Two Methods for Term-ITE Conversion             | 41 |

|   |       | 4.2.2 Term-ITE Conversion with Cofactors              | 43 |

|   | 4.3   | Simple Preprocessing                                  | 45 |

|   | 4.4   | Algorithm                                             | 46 |

|   | 4.5   | Related Work                                          | 50 |

|   | 4.6   | Experimental Results                                  | 50 |

|   | 4.7   | Conclusions                                           | 53 |

| 5 | Avoi  | iding Mismatches in Verification of Verilog Designs   | 54 |

|   | 5.1   | Introduction                                          | 54 |

|   | 5.2   | Verification Conditions for Hardware                  | 55 |

|   | 5.3   | Correctness                                           | 60 |

|   | 5.4   | Discussion                                            | 67 |

|   | 5.5   | Related Work                                          | 69 |

|   | 5.6   | Experimental Results                                  | 70 |

|   | 5.7   | Conclusions                                           | 70 |

vii

| 6 | Sele | ctive SMT Encoding for Hardware Model Checking                          | 72 |

|---|------|-------------------------------------------------------------------------|----|

|   | 6.1  | Introduction                                                            | 72 |

|   | 6.2  | From Hardware Description to BV                                         | 73 |

|   | 6.3  | SMT Encoding for Hardware Designs                                       | 75 |

|   |      | 6.3.1 LIA Encoding                                                      | 75 |

|   |      | 6.3.2 SMT Encoding with Combined Theories ( $BV \cup LIA$ )             | 78 |

|   | 6.4  | Model Analysis                                                          | 80 |

|   |      | 6.4.1 Analysis of Bit-Select Operations                                 | 80 |

|   |      | 6.4.2 Analysis of Bit-Wise Operation                                    | 81 |

|   |      | 6.4.3 Scoring System                                                    | 82 |

|   |      | 6.4.4 Experimental Evaluation                                           | 82 |

|   | 6.5  | Related Work                                                            | 84 |

|   | 6.6  | Conclusions                                                             | 84 |

| 7 | App  | lication of Formal Word-Level Analysis to Constrained Random Simulation | 86 |

|   | 7.1  | Introduction                                                            | 86 |

|   | 7.2  | Constraint Solving in Simulation                                        | 87 |

|   | 7.3  | DomRed: Technical Details                                               | 88 |

|   | 7.4  | Experimental Results                                                    | 89 |

| 8 | Cond | clusions                                                                | 91 |

|   | 8.1  | Thesis Conclusions                                                      | 91 |

|   | 8.2  | Future Work                                                             | 92 |

viii

# Bibliography

## Appendix

A Tables for Comparison

101

94

# Tables

# Table

| 3.1 | Number of Calls and Conflicts                                                                                                                                                                                |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.1 | Number of term-ITE reduction with simple preprocessing                                                                                                                                                       |

| 5.1 | Result of Vl2smt on Verilog designs                                                                                                                                                                          |

| 6.1 | Comparison of using selective, SAT, BV, and LIA encodings on evaluation set                                                                                                                                  |

| 7.1 | Comparison Table of without and with Bound Reduction                                                                                                                                                         |

| A.1 | Comparison of using BV solvers and LIA solvers on Verilog design                                                                                                                                             |

| A.2 | Comparison of using BV solvers and LIA solvers (Bit-Blast) on training set of Verilog designs 103                                                                                                            |

| A.3 | Comparison of LIA encodings with and without value enumeration                                                                                                                                               |

| A.4 | Comparison of LIA encoding with Term-ITEs and LIA encoding with fresh variables 105                                                                                                                          |

| A.5 | Comparison of LIA with Bit-Blast, pure LIA and $BV \cup LIA$ encoding $\ldots \ldots \ldots$ |

| A.6 | Comparison of using BV solvers and LIA solvers (Bit-Blast) on evaluation set of Verilog                                                                                                                      |

|     | designs                                                                                                                                                                                                      |

# Figures

# Figure

| 2.1  | DPLL(T) algorithm                                                                      | 11 |

|------|----------------------------------------------------------------------------------------|----|

| 2.2  | Theory solver algorithm                                                                | 12 |

| 2.3  | 4x4 Shidoku problem                                                                    | 15 |

| 3.1  | Theory solver algorithm                                                                | 27 |

| 3.2  | Theory solver algorithm (continued)                                                    | 28 |

| 3.3  | SCC without any negative cycle                                                         | 30 |

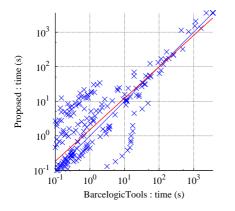

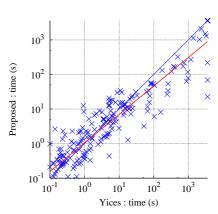

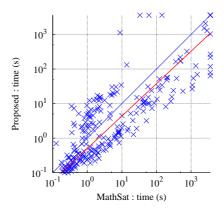

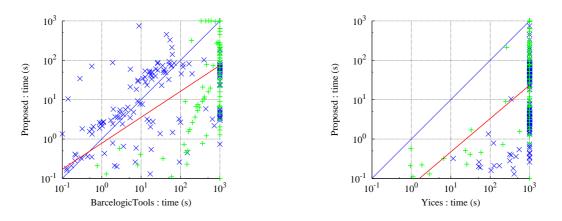

| 3.4  | BARCELOGICTOOLS vs. Sateen on QF_IDL                                                   | 34 |

| 3.5  | YICES vs. Sateen on QF_IDL                                                             | 34 |

| 3.6  | MATHSAT vs. Sateen on QF_IDL                                                           | 35 |

| 3.7  | BARCELOGICTOOLS vs. Sateen on Job Shop Scheduling and Queen suites                     | 36 |

| 3.8  | YICES vs. Sateen on Job Shop Scheduling and Queen suites                               | 36 |

| 3.9  | MATHSAT vs. Sateen on Job Shop Scheduling and Queen suites                             | 37 |

| 3.10 | Sateen with splitting disequalities vs. Sateen on Job Shop Scheduling and Queen suites | 37 |

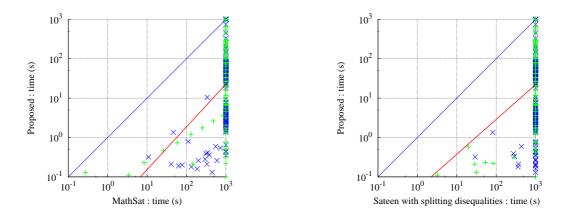

| 4.1  | Verification condition $\mathcal{F}$ with term-ITEs                                    | 39 |

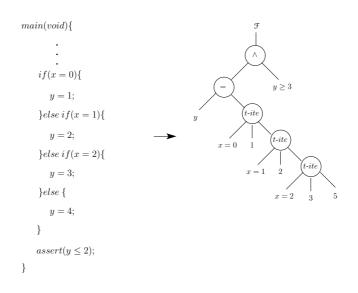

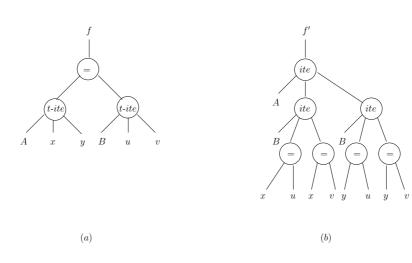

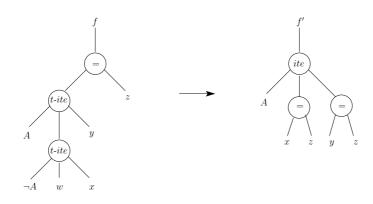

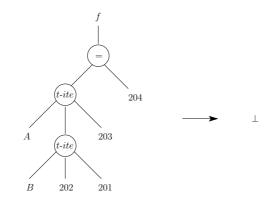

| 4.2  | Term-ITE conversion                                                                    | 42 |

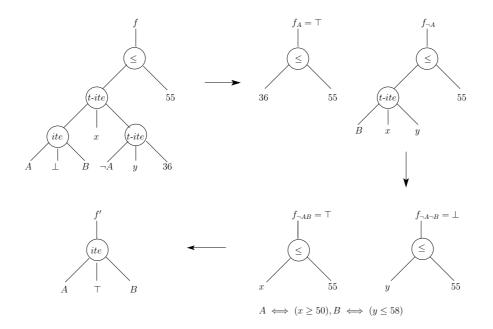

| 4.3  | Term-ITE conversion with cofactor                                                      | 43 |

| 4.4  | Term-ITE conversion with simple check                                                  | 45 |

| 4.5  | Term-ITE conversion algorithm                                                          | 47 |

| 4.6  | Term-ITE conversion algorithm                               | 48 |

|------|-------------------------------------------------------------|----|

| 4.7  | Term-ITE conversion                                         | 49 |

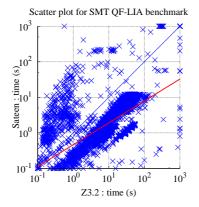

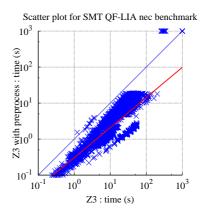

| 4.8  | Z3 vs. Sateen on QF_LIA                                     | 52 |

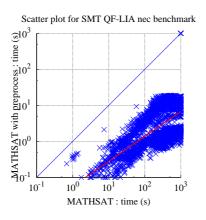

| 4.9  | MATHSAT vs. Sateen on QF_LIA                                | 52 |

| 4.10 | YICES vs. Sateen on QF_LIA                                  | 52 |

| 4.11 | Z3 WITH PREPROCESS vs. Z3 on QF_LIA                         | 52 |

| 4.12 | MATHSAT WITH PREPROCESS vs. MATHSAT on QF_LIA               | 52 |

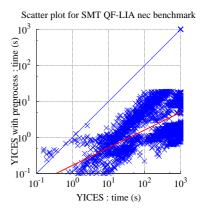

| 4.13 | YICES WITH PREPROCESS vs. YICES on QF_LIA                   | 52 |

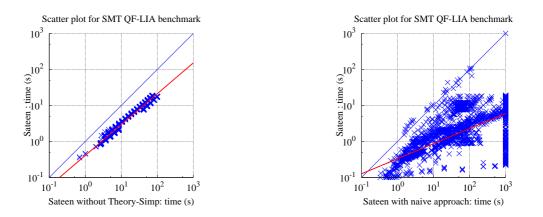

| 4.14 | SATEEN vs. Sateen without Theory-Simp on QF_LIA             | 53 |

| 4.15 | SATEEN vs. Sateen with naive approach on QF_LIA             | 53 |

| 5.1  | Conversion from <b>MSV</b> description to intermediate form | 57 |

| 5.2  | Verilog code for a test bench                               | 61 |

| 5.3  | Nondeterministic behavior of Verilog simulation (a)         | 63 |

| 5.4  | Nondeterministic behavior of Verilog simulation (b)         | 64 |

| 5.5  | Deterministic Verilog design                                | 69 |

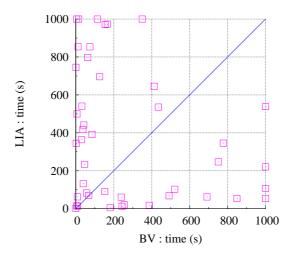

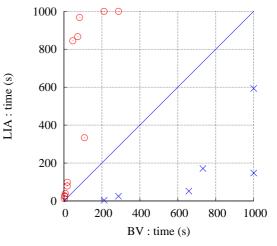

| 6.1  | BV vs. LIA                                                  | 73 |

| 6.2  | Conversion from HDL to SSA form                             | 74 |

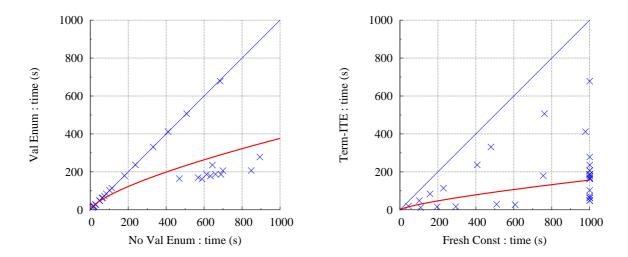

| 6.3  | VAL ENUM vs. No Val Enum                                    | 78 |

| 6.4  | TERM-ITE vs. Fresh Variable                                 | 78 |

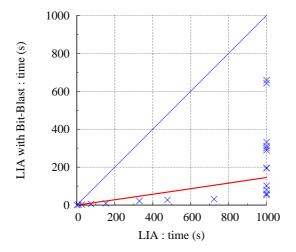

| 6.5  | LIA WITH BIT-BLAST VS. LIA                                  | 81 |

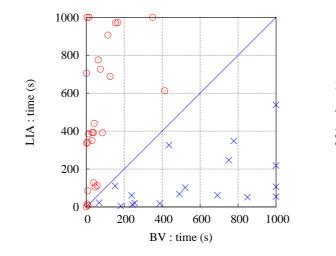

| 6.6  | BV vs. LIA for Training Set                                 | 83 |

| 6.7  | BV vs. LIA for Evaluation Set                               | 83 |

## Chapter 1

## Introduction

#### 1.1 Background

The Satisfiability Modulo Theories (SMT) problem has been the subject of intense scrutiny in the last few years. On the one hand, emerging applications like model checking of infinite state systems rely on such decision procedures for tasks like predicate abstraction [BMMR01]. On the other hand, algorithmic advances have significantly increased the range of problems that can be tackled, and hence have stimulated interest.

Recently, a dramatic performance increase in propositional satisfiability (SAT) solvers has led to the development of decision procedures that rely on the **propositional abstraction** [BDS02] of formulae from more expressive logics like the logic of **Linear Arithmetic** (LA) constraints, Presburger arithmetic, the logic of array, the logic of bit-vector, or the logic of equality and uninterpreted function symbols (EUF). In the propositional abstraction of a formula, atomic formulae of the specific theory (e.g.,  $x - y \leq 5$  or f(x) = f(y), where f is an uninterpreted function symbol) is replaced with fresh propositional variables. Each model of the abstraction maps to a conjunction of literals in the original formula that can be checked for consistency with theory-specific procedures. If such a procedure establishes consistency, then the given formula is satisfiable and the enumeration terminates. Otherwise, from the proof of inconsistency a refinement of the propositional abstraction is extracted and the search is resumed.

There are several ways to combine the propositional reasoning engine with the theory-specific procedures. One broad classification is into **lazy** and **eager** approaches. A lazy solver produces an initial propositional approximation that is concise and possibly quite coarse; it relies on refinements during the enumeration of solutions. By contrast, an eager solver adds constraints to the initial propositional abstraction that embody known relationships among the literals. An example is given by the constraints that encode transitivity of equality. The most effective solvers often adopt elements of both approaches and tailor their strategies to the theory (theories) at hand.

Despite the recent progress in SMT solving, several challenges still remain to be solved. The challenges in SMT can be broadly divided into two major parts: enhancement of SMT solving and applicability of the solver. As mentioned in [NORCR07], one of the big challenges in SMT solving is to obtain hybrid procedures that combine the benefits of both lazy and eager approaches. Depending on the problem, one may perform well, and the other may not. One simple way to combine these two approaches is that we analyze the problem features and apply adaptively one of the two approaches. For the adaptive method, an intelligent problem analysis method will be required.

Another challenge in SMT solving is on the simplification of the problem. In practice, SMT instances contain a lot of redundancies and retaining them in SMT solving resulted in poor performance of the solver. Recently, SAT preprocessing techniques [EB05] have been intensively studied, and the techniques are widely used in most SAT solvers. These techniques are also used in SMT, but they have some limitations since the theories are not considered for the simplification. In LA logic, the solvers are required to handle the infinite precision numbers for the soundness of the results. As a result, the solvers use infinite precision libraries such as GMP [GMP]; however, the cost of using the library is expensive due to the complex computations with the cumbersome numbers. Finding the practical way to avoid using the infinite precision library, or to lessen the burden for the library is a big challenge in LA logic.

Handling quantifiers and dealing with the combination of logics in SMT still remain to be as interesting research topics. In real world problems, one is often required to use quantifiers or multiple logics to describe the problem. Although there are several works [BCF<sup>+</sup>06, GBT07, GdM09] on quantifiers and the combination of logics, only a few SMT solvers support these features; thus there are still more room for the improvement.

Although SMT solvers have been widely used in software verification, the challenge still remains in the hardware verification. In today's hardware designs, bit-level and word-level operations are often tightly

intermingled to describe the model behavior. Recently, bit-vector solvers [BB09, Bru08] have been applied to hardware verification; however the most bit-vector solvers are based on the eager approach that encodes the bit-vector variables and the operations into SAT, and only utilize partial word-level information.

Among these challenges in SMT, we study an efficient SMT solver that combines lazy and eager approaches, and adopts word-level preprocessing technique to simplify the problem. As an application of SMT solver, we study an effective SMT-based model checking for hardware verification, and a formal word-level analysis to constrained random simulation.

#### **1.2** Thesis Contribution

In this section, we describe the contributions of my thesis to SMT solving and its application.

• Finite Instantiations for Integer Difference Logic [KS06, KJS07b]: We describe a theory solver for **Integer Difference Logic** (IDL) that is effective when the formula to be decided contains equality and disequality (negated equality) constraints so that the decision problem partakes of the nature of the pigeonhole problem. Atomic formulae in IDL constrain the difference between the values of pairs of integer variables. This logic finds extensive application to problems involving timing and scheduling constraints, resource allocation, and program analysis. IDL is closely related to Real Difference Logic (RDL), to the point that a decision procedure for the latter based on propositional abstraction also works for the former, as long as the coefficients are integers. It is sufficient to rewrite each equality constraint (of the form x - y = n) as the conjunction of two inequalities. However, if an equality constraint is negated, then the conjunction turns into a disjunction, which requires case splitting in the enumeration of the propositional solutions. In contrast, we propose an approach that does not decompose equalities and their negations; rather, it converts the problem of checking satisfiability of a conjunction of arithmetic atomic formulae into a set of propositional satisfiability checks-whose cardinality is bounded by the number of strongly connected components (SCC) of a suitable constraint graph. The conversion to propositional satisfiability that we have proposed is based on the ability to bound the values of the integer variables that appear in the formula. While in general such bounds do not exist, we have shown that to decide satisfiability of a set of constraints whose graph is a single SCC, it is sufficient to consider a subset of the solutions for which bounds are easily established. We also showed how the general case can be efficiently solved given solutions for the individual SCCs of the constraint graph. Experimental study shows that our new approach greatly improves the efficiency of our decision procedure for problem instances in which disequalities play a significant role, and makes it very competitive with respect to state-of-the-art tools.

- Efficient Term-ITE Conversion for SMT [KSJ09]: We describe how *term-if-then-else (term-ITE)* is handled in SMT. Term-ITEs allow one to conveniently express verification conditions; hence, they are very common in practice. However, the theory provers of SMT solvers are usually designed to work on conjunctions of literals; therefore, the input formulae are rewritten so as to eliminate term-ITEs. The challenge in rewriting is to avoid introducing too many new variables, while avoiding as often as possible the exponential explosion that is frequent when a naive approach is applied. We proposed a solution that is based on the computation of cofactors and theory propagation, and the experimental shows that the conversion method often produces orders-of-magnitude speedups in several SMT solvers for LIA problems.

- Avoiding Mismatches in Verification of Verilog Designs: We present a subset of Verilog with restrictions that guarantee behavioral equivalence between verification condition and simulation of synchronous hardware. The restrictions lead to a concise verification condition and allow controlled nondeterminism that can be easily eliminated for synthesis. Under a cycle-based simulation environment, we prove that every execution trace that may be produced by a standard-compliant simulator for synchronous hardware is captured in the verification condition, and vice versa.

- Selective SMT Encoding for Hardware Model Checking: We present a selective SMT encoding for hardware model checking. In particular, we introduce a model analysis method that considers each bit-vector operation in the design and selects the encoding based on the analysis. In addition, we present some enhancements to SMT encoding for hardware designs. Our experiments show that our

approach selects the right encoding for most of the hardware designs and improves the efficiency of hardware model checking.

• Application of Formal Word-Level Analysis to Constrained Random Simulation [KJR<sup>+</sup>08]: We have presented a new application of using SMT to constrained random simulation. In the constrained random simulation, the word-level analysis with SMT solver on word-level model enables the bit-level solver to avoid size explosion problem. Our main objective is to give bound reduction to the variables that are used in bit encoding. For bound computation, we use Bellman-Ford algorithm for the **difference** constraints and use simple coefficients checking for other linear arithmetic constraints. We can also detect a overconstraint from the set of **difference** constraints using Bellman-Ford algorithm. From the experiment, we found that our simple and fast algorithm can give huge amount of reduction to the variables in the real problem.

## **1.3** Thesis Organization

The rest of this thesis is organized as follows.

Chapter 2 introduces Satisfiability Modulo Theories and model checking. In addition, we review the Verilog hardware description language.

Chapter 3 presents an approach to solve IDL problem that contains many disequality constraints. We describe a theory solver that employs clique generation and finite instantiations to check the feasibility of a conjunction of inequality and disequality constraints. We present a bound computation algorithm that computes the bounds of integer variables in the constraints.

Chapter 4 presents an efficient term-ITE conversion method for SMT. We present a term-ITE conversion method that is based on cofactoring and theory simplification. We show the effectiveness of our approach by applying the method to LIA instances that make extensive use of the term-ITE operator.

Chapter 5 we present a subset of Verilog with restrictions that guarantee behavioral equivalence between verification condition and simulation of synchronous hardware. We show that the restrictions lead to a concise verification condition and allow controlled nondeterminism that can be easily eliminated for synthesis.

In chapter 6, we present a selective SMT encoding method for hardware model checking that predicts the encoding for a hardware design based on model analysis method. We describe the model analysis method that considers several characteristics of the design. We also present several enhanced encoding techniques for LIA solvers. We show the experimental evaluation to show the effectiveness of the approach.

In chapter 7, we presents a word-level pre-processor, **DomRed**, that simplifies the constraints in constrained random simulation. A bound reduction algorithm is presented that reduces the bound of the variables that are used in bit-encoding.

In chapter 8, conclusions and some future research directions are presented.

## Chapter 2

## Preliminaries

In this chapter, we introduce Satisfiability Modulo Theories (SMT) solving and model checking. In addition, we review the Verilog hardware description language (HDL) that is commonly used in verification of hardware.

### 2.1 Satisfiability Modulo Theories

The Satisfiability Modulo Theories (SMT) problem is a decision problem that decides the satisfiability of first-order formulas with background theories. SMT solvers find increasing applications in areas like formal verification in which one needs to reason about complex Boolean combinations of numerical constraints. The most common approach to this problem leverages the efficiency of modern propositional satisfiability solvers that work on a propositional abstraction of the given formula. At the same time, they interact with theory solvers, which check conjunctions of literals for consistency and learn consequences (new lemmas) from them. This approach has come to be known as DPLL(T) [NO05].

Recently, word-level model checking [Bje09, Joh01, CKZ96] has received growing attention. In particular, SMT solvers have been effectively applied to software verification with predicate abstraction [BMMR01, LNO06] and bounded model checking [GG08, AMP06]. Only to a lesser extent, they have been applied to hardware verification. The most natural SMT encodings for hardware description are bit-vector (BV) and linear integer arithmetic (LIA) encodings. LIA encoding for RTL constructs is presented in [BBC<sup>+</sup>06], where control variables are encoded as Boolean variables and datapath variables as integer variables. In [Bru08], the author presents a bit-vector (BV) solver with a layered approach for RTL design

verification.

In this section, we recall the definitions of the logics BV, LIA,  $BV \cup LIA$ , and IDL which we use to encode hardware. In addition, we review the DPLL(T) framework and discuss its algorithm.

#### 2.1.1 Bit-Vector Logic

Let  $V_B(n)$  for  $n \in \mathbb{Z}^+$  be the set of BV variables whose domains are bit-vectors with n bits. Let  $V_P$ be the set of propositional variables. We assume that  $i \neq j \rightarrow V_B(i) \cap V_B(j) = \emptyset$ . Let  $T_B(n)$  be a set of BV terms whose values are bit-vectors with n bits. The formulae in BV logic are inductively defined as follows.

- If  $c \in \mathbb{N}$  and  $c < 2^n$ , then  $c[n] \in T_B(n)$ .

- If  $x \in V_B(n)$ , then  $x[n] \in T_B(n)$ .

- If  $x \in V_B(n)$  and  $0 \le j \le i < n$ , then  $x[i : j] \in T_B(i j + 1)$ , and if  $t[n] \in T_B(n)$ , then  $\sim t[n] \in T_B(n)$ . ( $\sim$  is the bit-wise negation operator.)

- If  $t_1[n], t_2[n] \in T_B(n)$ , and  $\circ$  is an arithmetic or bit-wise operator in  $\{+, -, \cdot, /, \%, \&, |\}$ , then  $t_1[n] \circ t_2[n] \in T_B(n)$ .

- If  $t_1[i] \in T_B(i)$  and  $t_2[j] \in T_B(j)$ , then  $concat(t_1[i], t_2[j]) \in T_B(i+j)$ .

- A propositional variable  $a \in V_P$  is a formula.

- If t<sub>1</sub>[n], t<sub>2</sub>[n] ∈ T<sub>B</sub>(n), and ◊ is a relational operator in {=, ≠, <, ≤, >, ≥}, then t<sub>1</sub>[n] ◊ t<sub>2</sub>[n] is a formula.

- If  $f_1$ ,  $f_2$ , and  $f_3$  are formulae, then  $\neg f_1$ ,  $f_1 \land f_2$ ,  $f_1 \lor f_2$  and  $ite(f_1, f_2, f_3)$  are formulae, and if  $t_1[n], t_2[n] \in T_B(n)$  and f is a formula, then  $tite(f, t_1[n], t_2[n]) \in T_B(n)$ .

Further formulae can be defined as abbreviations. For instance,  $x[n] \ll k$ , a left shift of x[n] by a constant k, is defined as concat(x[n-k-1:0], 0[k]). An **atomic formula** is one of the form  $t_1[n] \diamond t_2[n]$ , where  $\diamond$  is a relational operator. The semantics are defined in the usual way; in particular, arithmetic

is modular, x[i : j] is the subfield of x[n] comprising the bits from i to j included,  $concat(t_1[i], t_2[j])$ concatenates  $t_1[i]$  and  $t_2[j]$ , and  $ite(f_1, f_2, f_3)$  is equivalent to  $(f_1 \wedge f_2) \vee (\neg f_1 \wedge f_3)$ . In addition, the **term if-then-else (tite)** operator is defined by the equivalence, for all formulae f and g and for all terms  $t_1[n]$  and  $t_2[n]$ , of  $f(tite(g, t_1[n], t_2[n]))$  and  $ite(g, f(t_1[n]), f(t_2[n]))$ .

For  $A, B, C, D, E \in V_B(2)$ , (2.1) is a BV formula.

$$(C[2] = A[2] \& B[2]) \land (D[2] = C[2] + E[2]) .$$

$$(2.1)$$

#### 2.1.2 Linear Integer Arithmetic Logic

Let  $V_Z$  be the set of integer-valued variables. The formulae in LIA logic are inductively defined as follows.

- An integer number  $c \in \mathbb{Z}$  is a (constant) LIA term, and a variable  $x \in V_Z$  is an LIA term.

- A variable x ∈ V<sub>Z</sub> is an LIA term, and the product c ⋅ x of an integer number c ∈ Z and a variable x ∈ V<sub>Z</sub> is an LIA term.

- If  $t_1$  and  $t_2$  are LIA terms, so are  $t_1 + t_2$  and  $t_1 t_2$ .

- A propositional variable  $a \in V_P$  is a formula.

- If t<sub>1</sub> and t<sub>2</sub> are LIA terms, and ◊ is a relational operator in {=, ≠, <, ≤, >, ≥}, then t<sub>1</sub> ◊ t<sub>2</sub> is a formula.

- If  $f_1$ ,  $f_2$ , and  $f_3$  are formulae, then  $\neg f_1$ ,  $f_1 \land f_2$ ,  $f_1 \lor f_2$  and  $ite(f_1, f_2, f_3)$  are formulae.

- If  $t_1$  and  $t_2$  are LIA terms, and f is a formula, then  $tite(f, t_1, t_2)$  is an LIA term.

For  $A, B, C, D, E \in V_Z$ , (2.2) is an LIA formula:

$$(C = A - B) \land (D = C + E)$$

. (2.2)

#### **2.1.3 BV** $\cup$ **LIA** Logic

Let  $R_B$  be a set of rules for BV logic and  $R_Z$  be a set of rules for LIA logic. The formulae in BV  $\cup$ LIA are inductively defined as the largest set that satisfies the rules in  $R_B \cup R_Z$ .

For  $A \in V_B(2)$  and  $C \in V_Z$ , (2.3) is a BV  $\cup$  LIA formula:

$$C = tite(A[1:1] = 1[1], 2, 0) + tite(A[0:0] = 1[1], 1, 0)$$

(2.3)

With the use of  $V_P$  in BV and LIA logics, a BV formula can be easily converted into a Boolean formula. The conversion is called bit-blasting in which a set of propositional variables replaces each bit-vector. Through bit-blasting, a BV  $\cup$  LIA formula can be converted into an LIA formula, which is often decided more efficiently.

Given  $A_0, A_1 \in V_P$  and  $C \in V_Z$ , Eq. (2.4) shows the LIA formula obtained from Eq. (2.3) by bit-blasting A[2]:

$$C = tite(A_1, 2, 0) + tite(A_0, 1, 0) .$$

(2.4)

#### 2.1.4 Integer Difference Logic

We define inductively Integer Difference Logic (IDL) formulae as follows.

- A propositional variable  $a \in V_P$  is a formula.

- $x y \le n$  and x y = n are formulae, for  $x, y \in V_P$ ,  $n \in Z$ .

- If  $\varphi$  and  $\psi$  are formulae, so are  $\varphi \land \psi$  and  $\neg \varphi$ .

The following abbreviations are also defined:

$$\begin{aligned} x - y < n &\doteq x - y \le n - 1 \\ x = y &\doteq (x - y = 0) \end{aligned} \qquad \begin{aligned} x - y \neq n &\doteq \neg (x - y = n) \\ x \neq y &\doteq \neg (x = y) \end{aligned}.$$

In SMT, a literal is an atomic formula, or the negation of an atomic formula. A **clause** is the disjunction of a set of literals, and a formula in **conjunctive normal form** (CNF) is the conjunction of a set of clauses.

#### 2.1.5 **DPLL**(T)

DPLL(T) architecture [GHN<sup>+</sup>04, NO05] combines DPLL(X), the propositional reasoning engine, with the theory specific procedure. Given an SMT formula  $\varphi$  with a specific theory T, DPLL(T) computes a **propositional abstraction**  $\varphi^b$  of  $\varphi$  by replacing the atomic formulae of T with fresh propositional variables. A model for  $\varphi^b$  maps to a conjunction of literals in  $\varphi$  that is checked for consistency with the theory solver. If the model is consistent in T,  $\varphi$  is satisfiable and the enumeration of the model terminates. Otherwise, the theory solver returns the explanation of the inconsistency for the refinement of the propositional abstraction, and the search is resumed. Checking consistency of the partial interpretation enables the solver to detect the inconsistency earlier and learn so-called **theory consequences** in T that often improve the efficiency of the search.

| 1  | DPLL_T () {                                                      |

|----|------------------------------------------------------------------|

| 2  | while (ChooseNextAssignment () == FOUND)                         |

| 3  | while $(\top)$ {                                                 |

| 4  | if (Deduce () == $CONFLICT$    TheorySolver () == $CONFLICT$ ) { |

| 5  | <pre>blevel = AnalyzeConflict ();</pre>                          |

| 6  | if (blevel $< 0$ ) return UNSAT;                                 |

| 7  | else Backtrack (blevel);                                         |

| 8  | continue;                                                        |

| 9  | }                                                                |

| 10 | if (TheoryConseq () == $\emptyset$ ) break;                      |

| 11 | }                                                                |

| 12 | return SAT;                                                      |

| 13 | }                                                                |

|    |                                                                  |

Figure 2.1: DPLL(T) algorithm

The pseudo-code of DPLL(T) procedure is presented in Fig. 2.1. The algorithm is not much different from the David-Putnam-Logemann-Loveland (DPLL) procedure [DP60, DLL62]. It works as the DPLL procedure if the condition **TheorySolver** () == *CONFLICT* is removed and the condition **TheoryConseq** () ==  $\emptyset$  is converted into  $\top$ . The DPLL(T) algorithm is applied to a **propositional abstraction**  $\varphi^b$  of  $\varphi$  where  $\varphi$  is an SMT formula in CNF. It maintains an **assignment stack** that records all the assignments currently in effect and an **assignment queue** that records the assignments that are not in effect yet. The procedure **ChooseNextAssignment** checks if the queue is empty and selects an unassigned variable to make a decision on the value of the variable if it is empty. If no unassigned variable is selected, the algorithm returns SAT, which means  $\varphi$  is satisfiable. The newly assigned variable, if it exists, is entered into the queue, and its implications are added in the queue by the **Deduce** procedure. If **Deduce** does not cause a conflict, the procedure **TheorySolver** checks if the conjunction of the atomic formula is consistent or not. If either **Deduce** or **TheorySolver** returns *CONFLICT*, then **AnalyzeConflict** analyzes the reason of the conflict. The procedure **AnalyzeConflict** returns the backtracking level, and if it is less than zero, the algorithm terminates by giving the *UNSAT* result for  $\varphi$ ; otherwise, the procedure **Deduce** resumes in the backtracking level. If there is no conflict in both **Deduce** and **TheorySolver**, the algorithm checks if **TheorySolver** generated theory consequences. If theory consequences are generated, the algorithm continues with the while loop in line 3; otherwise, it continues with the while loop in line 2.

| 1  | TheorySolver () {                        |

|----|------------------------------------------|

| 2  | for each $l \in I^b$ {                   |

| 3  | if $(I \models_T \neg l)$ {              |

| 4  | $L_E$ = Explanation $(I, \neg l)$ ;      |

| 5  | $\varphi^b = \varphi^b \wedge \neg L_E;$ |

| 6  | return CONFLICT;                         |

| 7  | } else {                                 |

| 8  | $I = I \cup l;$                          |

| 9  | }                                        |

| 10 | }                                        |

| 11 | for each $l \in L \setminus I$ {         |

| 12 | if $(I \models_T l) I^b = I^b \cup l;$   |

| 13 | }                                        |

| 14 | return NULL;                             |

| 15 | }                                        |

|    |                                          |

Figure 2.2: Theory solver algorithm

The procedure **TheorySolver** in Fig. 2.2 is called with a conjunction of literals in T whose corresponding propositional literals are true in a (partial) interpretation  $I^b$  of the propositional formula  $\varphi^b$ . It decides whether there is an interpretation to the variables in the atomic formula that satisfies the conjunction of all those literals. Let L be the set of all the literals in  $\varphi^b$  and I be the set of literals that is a (partial) interpretation of  $\varphi$ . The set I is initially empty, and the negation of  $l \in I^b$  is checked with I for a theory consequence. A literal l is a theory consequence of I, denoted  $I \models_T l$ , if l is true in I. If  $I \models_T \neg l$  is true, an explanation  $L_E$  of the theory consequence is generated, where  $L_E$  is a conjunction of literals. The negation of  $L_E$  is conjoined with  $\varphi^b$  to prevent this to be happen again. Since a conflict is found in I with l, the procedure returns with the *CONFLICT* result. If  $I \models_T \neg l$  is not true, the literal  $l \in I^b$  is added to I. The procedure continues to check  $I \models_T \neg l$  for each  $l \in I^b$  until it finds a conflict or all the literals in  $I^b$  are added to I, a new (partial) interpretation of  $\varphi$ . With the new interpretation I, each  $l \in L \setminus I^b$  is checked for a theory consequence to deduce more literals. The literal  $l \in L \setminus I^b$  is added to  $I^b$  if  $I \models_T l$ . After checking all the theory consequences, the procedure returns with *NULL*.

#### 2.2 Model Checking

Model checking [CE81, CGP99] is an algorithmic approach to verify the correctness properties of a finite state system automatically. Given a model M of a hardware or software system, the transition system of M is explored with a temporal property  $\varphi$  to check if the property holds in the model, denoted  $M \models \varphi$ . If the model does not meet the property, denoted  $M \not\models \varphi$ , the model checking algorithm provides a counterexample trace that demonstrates how the property can be violated.

Traditionally, explicit-state model checking [CE81] approach has been widely used, where the set of states and the transition relations are explicitly represented and the search algorithm explores the states to check if the state violates the property. Due to the explicit representation of the states, the method often suffers with the state explosion problem. As an alternative approach, symbolic model checking [McM94, BCCZ99] approach uses a Boolean formula to represent the set of states and the transition relations, where the Boolean formula is often represented with Binary Decision Diagrams (BDDs) [Bry86] or propositional satisfiability (SAT) [MMZ<sup>+</sup>01, GN02, JS04]. Since BDDs are canonical representation, the BDD-based model checking may suffer with the size explosion problem; however, once the BDDs are built, the model checking problem can be solved efficiently. On the other hand, SAT- based model checking avoids the size explosion problem by not using the canonical representation. It converts the Boolean formula into a **Conjunctive Normal Form** (CNF) to be solved by propositional SAT solvers.

In SAT-based Bounded Model Checking (BMC), the transition relation of a model is unrolled k

times and conjoined with the set of initial states and the negation of the Linear Time Logic (LTL) property [WVS83, LP85]. The conjoined Boolean formula in CNF is solved by a propositional SAT solver and is satisfiable if there exists a counterexample of the length k to the property. In contrast to BDD-based model checking, SAT-based BMC suffers less to the size explosion problem and produces counterexamples of minimum length for all LTL properties.

Given a model  $\mathcal{M}$ , an LTL property  $\phi$ , and a bound k, BMC constructs a Boolean formula denoted by  $\llbracket \mathcal{M}, \neg \phi \rrbracket_k$ , that is satisfiable if and only if there exists a counterexample of the length k to  $\phi$ ;  $\llbracket \mathcal{M}, \neg \phi \rrbracket_k$ is defined as follows:

$$\llbracket \mathcal{M}, \neg \phi \rrbracket_k = I(s_0) \land \bigwedge_{0 \le i < k} T(s_i, s_{i+1}) \land \llbracket \neg \phi \rrbracket_k \quad ,$$

(2.5)

where I is the predicate describing the initial states, T is the transition relation, and  $[\![\neg\phi]\!]_k$  expresses the satisfaction of  $\neg\phi$  along that path defined by  $s_0, s_1, \ldots s_k$ .

In recent years, SMT-based model checking has received growing attention. In SMT-based BMC, a model is encoded into an SMT formula that is more concise and that preserves more structure of the model compare to the corresponding Boolean formula. In terms of efficiency of the solver, representing the model in SMT gives more flexibility to choose a suitable approach for the problem and often increases the deductive power of the solver. The following example compares SMT and SAT encodings for a **Shidoku problem** and shows the effectiveness of the SMT encoding.

Consider a  $4 \times 4$  Shidoku problem in Fig. 2.3. The objective of the  $4 \times 4$  Shidoku problem is to fill a  $4 \times 4$  grid so that each column, each row, and each of the four  $2 \times 2$  blocks contains the digits from 0 to 3 only one time each. It is well known that Shidoku problem can be encoded into either a SAT or an SMT problem. Suppose the values  $x_0 = 0, x_1 = 1, x_2 = 3$  in the first column are given for the problem in Fig. 2.3. If we encode the problem into a SAT problem, we introduce Boolean variables  $x_i^1, x_i^0$  for each integer variable  $x_i$ . The partial encoded SAT problem for  $x_0 = 0, x_1 = 1, x_2 = 3$  and  $x_0 \neq x_3, x_1 \neq x_3, x_2 \neq x_3$  is given below.

$$(x_3^1 \lor x_3^0) \land (x_3^1 \lor \neg x_3^0) \land (\neg x_3^1 \lor \neg x_3^0) .$$

(2.6)

| $x_0$ |  |  |

|-------|--|--|

| $x_1$ |  |  |

| $x_2$ |  |  |

| $x_3$ |  |  |

Figure 2.3: 4x4 Shidoku problem

As Eq. (2.6) shows, one of the Boolean variables in the clause should be decided to make assignments to the variables  $x_3^1$  and  $x_3^0$ .

On the other hand, if the problem is encoded into a LIA formula, the formula is

$$\neg(x_3 = 0) \land \neg(x_3 = 1) \land \neg(x_3 = 3) \land (x_3 \ge 0) \land (x_3 \le 3)$$

(2.7)

The equalities in Eq. (2.7) can be converted into inequalities, and the converted formula is

$$((x_3 < 0) \lor (x_3 > 0)) \land ((x_3 < 1) \lor (x_3 > 1)) \land ((x_3 < 3) \lor (x_3 > 3)) \land (x_3 \ge 0) \land (x_3 \le 3)$$

. (2.8)

By applying theory propagation with  $(x_3 \ge 0)$  and  $(x_3 \le 3)$  in the unit clauses, Eq. (2.8) is simplified into

$$(x_3 > 1) \land (x_3 < 3)$$

. (2.9)

From Eq. (2.8), we can infer  $(x_3 = 2)$ .

The comparison of SAT and SMT encodings shows that SMT encoding introduces fewer number of variables and clauses for the problems that require word-level reasoning. As a result, the size of SMT encoding is much smaller than the size of SAT encoding. In addition, SMT encoding often gives more deductive power to the solver by considering the problem in word level.

#### 2.3 Hardware Description Language

Verilog is a hardware description language (HDL) used to describe digital systems. Verilog HDL is the most commonly used language in verification, synthesis, and testing of hardware designs. Verilog describes a hardware design as a hierarchy of modules, where modules communicate each other through a set of declared inputs, outputs, and bidirectional ports. Each module contains net, variable, function, and task declarations, procedural and parallel blocks, and instances of other modules. A net can be of type **supply0**, **supply1**, **tri**, **triand**, **trior**, **tri0**, **tri1**, **wire**, **wand**, or **wor**. A variable can be of type **reg**, **integer**, **real time**, or **realtime**. A constant is an integer or real number; expressions are made of variables, constants, and operators, which are categorized into arithmetic, concatenation, reduction, bit-selection, shift, bit-wise, logical, conditional, and relational operators.

In Verilog, a blocking assignment (=) updates the target variable immediately, while the update of a nonblocking assignment ( $\Leftarrow$ ) is deferred. A continuous assignment updates the target wire whenever the values of the operands in the right-hand side of the assignment is changed. A statement may be an assignment, an **if** / **else** conditional statement, a **case** statement, a looping statement, or a sequence of statements enclosed by the keywords **begin** and **end**.

A procedural block in Verilog can be either **inital** or **always**. An **initial** block is executed only once, and is used to describe the initial values and the updates of memory elements. On the other hand, an **always** block is executed repeatedly, and is used to describe combinational and sequential logics. The statements in a procedural block are executed sequentially in the given order, whereas the statements in a parallel block such as **fork-join** block are executed concurrently.

The statement in either a procedural or parallel block is controlled by explicit timing controls such as a delay control (**#d**) and an event control (**@ event\_identifier**, **@ (event\_expression**), **@ (\*)**, or **@ \*)**. The delay control specifies the time duration for executing a statement and the event control defers the execution of a statement until there is an occurrence of a declared event or value change on a net or variable.

## Chapter 3

#### **Finite Instantiation for Integer Difference Logic**

#### 3.1 Introduction

Decision procedures for fragments of first-order logic have been the subject of intense scrutiny in the last few years. On the one hand, emerging applications like model checking of infinite state systems rely on such decision procedures for tasks like predicate abstraction [BMMR01]. On the other hand, algorithmic advances have significantly increased the range of problems that can be tackled, and hence have stimulated interest.

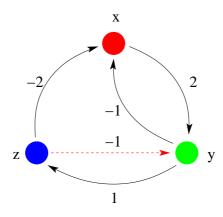

In this chapter, we focus on **Integer Difference Logic** (IDL), in which arithmetic atomic formulae constrain the difference between the values of pairs of integer variables. This logic finds extensive application to problems involving timing and scheduling constraints, resource allocation, and program analysis. IDL is closely related to **Real Difference Logic** (RDL), to the point that a decision procedure for the latter based on propositional abstraction also works for the former, as long as the coefficients are integers. It is sufficient to rewrite each **equality** constraint (of the form x - y = n) as the conjunction of two inequalities. However, if an equality constraint is negated, then the conjunction turns into a disjunction, which requires case splitting in the enumeration of the propositional solutions. In contrast, we propose an approach that does not decompose equalities and their negations; rather, it converts the problem of checking satisfiability of a conjunction of arithmetic atomic formulae into a set of propositional satisfiability checks—whose cardinality is bounded by the number of strongly connected components (SCC) of a suitable constraint graph.

The conversion to propositional satisfiability that we propose is based on the ability to bound the values of the integer variables that appear in the formula. While in general such variables are not bounded,

we show that to decide satisfiability of a set of constraints whose graph is a single SCC it is sufficient to consider a subset of the solutions for which bounds are easily established. We also show how the general case can be efficiently solved given solutions for the individual SCCs of the constraint graph. Experiments show that our new approach, which combines techniques typical of both the lazy and the eager approaches, greatly improves the efficiency of our decision procedure for problem instances in which disequalities play a significant role, and makes it very competitive with respect to state-of-the-art tools.

This chapter is organized as follows: Section 3.2 reviews background and introduces notation. Section 3.3 and Section 3.4 discuss the minimizing the abstract models and the bounds on solutions, while Sect. 3.5 deals with the implementation of our theory solver. After a survey of related work in Sect. 3.6, experiments are presented in Sect. 3.7, and conclusions are offered in Sect. 3.8.

#### **3.2** Preliminaries

Propositional logic is the fragment of IDL obtained by omitting the rule that defines arithmetic atomic formulae. Efficient algorithms to decide the satisfiability of propositional logic formulae are based on the DPLL procedure [DP60, DLL62], and exploit techniques like clause recording, conflict analysis, nonchrono-logical backtracking, and fast Boolean constraint propagation [MS96, MMZ<sup>+</sup>01].

In recent times, decision procedures for IDL, and other fragments of quantifier-free first-order logic, have been based on the DPLL procedure as well. Given a set of propositional variables B such that  $B \cap P = \emptyset$ , one obtains a propositional formula  $\varphi^b$  from an IDL formula  $\varphi$  by replacing each arithmetic atomic subformula of  $\varphi$  with a distinct variable from B. The resulting formula  $\varphi^b$  is unsatisfiable only if  $\varphi$  is unsatisfiable. Each model of  $\varphi^b$  corresponds to a conjunction of literals of  $\varphi$ . Given a decision procedure for the conjunction of arithmetic atomic propositions in IDL (a **theory solver**), one therefore derives a complete decision procedure for IDL by enumerating the models of  $\varphi^b$ , extracting from each of them the corresponding conjunction of arithmetic atomic propositions and their negations, and checking these conjunctions for satisfiability using the theory solver. In the following, we refer to the conjunction of a set of arithmetic literals as a **set of IDL constraints**.

The theory solver rewrites the IDL constraints to be checked according to their form:

- (1)  $x y \le n$ : unchanged;

- (2) x = y: unchanged;

- (3) x y = n, with  $n \neq 0$ : split into  $(x y \leq n) \land (y x \leq -n)$ ;

- (4)  $\neg (x y \le n)$ : rewritten as  $y x \le -n 1$ ;

- (5)  $\neg(x = y)$ : rewritten as  $x \neq y$ ;

- (6)  $\neg(x y = n)$ , with  $n \neq 0$ : rewritten as  $x y \neq n$ .

Constraints of type 1, 3, and 4 are **inequalities** (*I*). Constraints of type 2 are **equalities** (*Q*), and finally, constraints of type 5 and 6 are **disequalities** (*D*). Specifically, constraints of type 5 form the set  $D_0 \subseteq D$ . Let  $C = I \cup Q \cup D$ .

An edge integer-labeled directed graph is a triple  $G = (V, E, \lambda)$ , where V is a set of vertices,  $E \subseteq V \times V$  is a set of edges, and  $\lambda : E \to Z$  is an edge labeling function. A **strongly connected component** (SCC) of G is a maximal subgraph G' of G such that every two nodes of G' are connected by a path in G'. An SCC is **trivial** if it consists of one vertex and no arcs. The SCCs of G define a partition of V. The **SCC quotient graph**  $\hat{G} = (\hat{V}, \hat{E})$  of G is a directed acyclic graph with one vertex for each SCC of G and an edge  $(A, B) \in \hat{E}$  if and only if there exist  $x \in A$  and  $y \in B$  such that  $(x, y) \in E$ .

Given a distinguished source vertex  $s \in V$ , distances of all vertices from s are well defined provided there exists no **negative cycle** in G; that is, no cycle such that the sum of the labels on the edges along the cycle is negative. The Bellman-Ford algorithm [CLR90] reports negative cycles if they are present, and computes the distance  $\delta(x)$  of each vertex in V from the source s otherwise. The **slack** of an edge  $(x, y) \in E$ is given by  $\sigma((x, y)) = \lambda((x, y)) - (\delta(y) - \delta(x))$ . It is easy to see that for all  $e \in E$ ,  $\sigma(e) \ge 0$  and that  $\sigma((x, y)) = 0$  if and only if (x, y) is on a shortest path from s to y in G. Distances and slacks obviously depend on the choice of source vertex.

Given a (finite) set I of inequality constraints (i.e., of the form  $x - y \le n$ ), their constraint graph  $G = (V, E, \lambda)$  is a labeled directed graph defined as follows:

•  $V \subseteq V_Z$  is the set of variables appearing in the constraints in *I*.

• There is an arc  $(x, y) \in E$  with  $\lambda((x, y)) = n$  if and only if there is a constraint  $y - x \leq n$  in I.

It is well known [CLR90] that I is satisfiable if and only if G contains no negative cycle. In fact, adding both sides of the constraints forming a cycle of length w, one gets  $0 \le w$ , which is not satisfiable when w < 0. If, on the other hand, no negative cycle exists in G, then one can find a model for I by solving a single-source shortest-path problem on an augmented graph  $G_a$ , obtained from G by adding a new reference vertex  $x_r$  and arcs labeled 0 from  $x_r$  to all the other vertices. Let  $\delta(x)$  be the distance of  $x \in V$  from  $x_r$ in  $G_a$ . Then  $\delta$  is a model for I. It is also well known that, given a model of I,  $\alpha : V \to Z$ , and a constant,  $c \in Z$ , the interpretation  $\alpha' : V \to Z$  defined by  $\alpha'(x) = \alpha(x) + c$  is also a model of I, because  $\alpha'(x) - \alpha'(y) = \alpha(x) - \alpha(y)$ . This observation allows an easy encoding of **range constraints** in IDL. A set of constraints  $\{l_i \le x_i \le u_i\}$  is translated to  $\{x_i - y \le u_i\} \cup \{y - x_i \le -l_i\}$ , where y is a fresh variable. The solution  $\alpha$  obtained from the constraint graph is then translated so that  $\alpha'(y) = 0$ . One fresh variable suffices for multiple range constraints.

Since integer labels imply integer distances, if the right-hand sides of the constraints are integervalued, and the constraints are satisfiable when the variables range over the real numbers, then an integervalued solution is also guaranteed to exist. Loosely speaking, the satisfiability problem for **inequalities** is the same for IDL and real difference logic (RDL). Adding **equality** constraints to the inequalities does not change this state of affairs: Given a constraint x - y = n, one replaces x by y + n; if no immediate inconsistencies arise, one continues with the construction of the constraint graph. In contrast, if disequality constraints (i.e., negations of equalities) are allowed, an unsatisfiable conjunction of IDL constraints may be satisfiable when regarded as an RDL formula. An example is given by  $\bigwedge_{1 \le i \le p} (1 \le x_i \le h) \land \bigwedge_{1 \le i \le p} (x_i \ne x_j)$ , which exemplifies the pigeonhole principle.<sup>1</sup>

#### 3.3 Minimizing the Abstract Models

Given the set of clauses  $\varphi^b$  and a complete model for them produced by the propositional reasoning engine, we consider now the problem of identifying a minimal (partial) model such that at least one literal

<sup>&</sup>lt;sup>1</sup> This does not contradict what was observed in Sect. 3.1 because  $x \neq y$  translates into  $(x < y) \lor (y < x)$  for RDL, but translates into  $(x \le y - 1) \lor (y \le x - 1)$  for IDL.

for each clause is true. The intent of finding such minimal model is twofold: to alleviate the task of the theory solver and to make the exploration of the models of  $\varphi^b$  more efficient. A greedy solution to our problem is easily obtained by considering each variable in turn and removing it from the model if no clause becomes unsatisfied as a result. We now describe how such a solution can be implemented efficiently in the context of the algorithm that enumerates the solutions to the propositional abstraction. That is, we show how we can take advantage of the information gathered by the propositional SAT solver to significantly speed up the choice of the minimal model.

Two observations from [RS04] provide the foundation for our method. The first is that no variable that received its value by implication (rather than decision) by the SAT solver can be removed from the model. This fact greatly reduces the number of variables that are candidates for removal. The second observation concerns the list of watched literals and assumes that only two literals are watched by the SAT solver [MMZ<sup>+</sup>01]. It can then be shown that when a complete model is found, at least one watched literal in every clause is true. Therefore, when considering a variable for removal it is sufficient to check if it provides the only true literal in the clauses in which the satisfied literal of the variable is watched. The clauses in which that literal is not watched can be safely ignored. Moreover, conflict clauses recorded by the SAT solver do not need to be examined because they are known to be satisfied whenever the original clauses are satisfied.

When a clause in which the candidate literal is watched is examined, a substitute literal that is true is sought so as to maintain the invariant. If there is no substitute and the other watched literal is false, the candidate is rejected. On the other hand, if this process manages to empty the watched-literal list of the candidate (except possibly for conflict clauses), the candidate is removed from the model.

The effect of the minimization procedure is to alter the watched-literal lists of the solver. However, the enumeration process can resume from the modified lists without any adverse consequence. The algorithm that we have described runs in polynomial time, but only guarantees a minimal set of variables. Reduction from set covering shows that deciding whether a model of size k exists for a set of propositional clauses is NP-complete.

The order in which literals are considered for removal depends on the constraints they represent.

The check for consistency of a set of constraints tends to be easier if disequality constraints are the first candidates for elimination. They are followed by inequality constraints, and finally equality constraints, in that order.

#### **3.4** Bounds on Solutions

In this section we show how bounds to the solutions of a set of constraints are computed and how those bounds are used in checking for consistency of (partial) interpretations of  $\varphi^b$ . Two cases must be distinguished depending on whether the interpretation to be checked is known to be a model of  $\varphi^b$ : If it is not known to be a model, a cheap check is applied, which can only report inconsistency. Otherwise, a more expensive, complete check is applied in addition, which decides consistency and computes a model of  $\varphi$  if it exists.

#### 3.4.1 Bound Computation

It was recalled in Sect. 3.2 that from a solution  $\alpha$  to a set of inequality constraints, one can derive a family of solutions  $\{\alpha + c\}$ . In general, however, not all solutions are obtained one from the other by **translation**. Consider the constraints  $\{(x - y \le 1), (y - x \le 0)\}$ . The two interpretations  $\alpha_1(x) = 0$ ,  $\alpha_1(y) = 0$  and  $\alpha_2(x) = 1$ ,  $\alpha_2(y) = 0$  satisfy the constraints, though there is no *c* such that  $\alpha_1 = \alpha_2 + c$ . Such solutions are called **independent**. In general, there may be several families of independent solutions, and therefore, multiple distinct solutions that assign a given value to a distinguished variable. The following result characterizes these sets of solutions and forms the basis for our treatment of disequality constraints in IDL.

**Theorem 3.1.** Let I be a set of inequality constraints. Let  $G = (V, E, \lambda)$  be the constraint graph associated to I. Suppose that G contains no negative cycle and consists of one SCC. Let  $\delta_{ab}$  be the distance from a to b in G. For  $x \in V$  and  $n \in Z$ , let  $S_x^n$  be the set of solutions  $\alpha : V \to Z$  to I such that  $\alpha(x) = n$ . Then, for each vertex  $y \in V$ , there exist bounds  $y_l = n - \delta_{yx}$  and  $y_u = n + \delta_{xy}$ , such that for every solution in  $S_x^n$ ,  $y_l \leq \alpha(y) \leq y_u$ . *Proof.* By definition of SCC, every vertex in V is reachable from x in G; likewise, x is reachable from any vertex in G. Let  $\delta_{xy}$  be the distance of y from x (the length of a shortest path). Such a distance is defined because there are no negative cycles in G. Adding both sides of all the constraints along the path yields  $y - x \le \delta_{xy}$ . Therefore, for every solution  $\alpha \in S_x^n$ , it must be  $\alpha(y) \le n + \delta_{xy}$ . Said otherwise,  $y_u = n + \delta_{xy}$ . For the lower bound, if  $\delta_{yx}$  be the distance of x from y in G, then, for every solution  $\alpha \in S_x^n$ , it must be  $\alpha(y) \ge n - \delta_{yx}$ ; that is,  $y_l = n - \delta_{yx}$ .

Satisfaction of disequalities is not affected by translation. Therefore, a set of constraints including both inequalities and disequalities is satisfiable if and only if there exists a solution  $\alpha$  such that  $\alpha(x) = n$ . This allows us to limit the search to the set  $S_x^n$  for an arbitrarily chosen n. Theorem 3.1 asserts that solutions in this set are bounded. The way this result is exploited depends on whether the set of constraints corresponds to a model of  $\varphi^b$ . The next two subsections discuss the two cases.

#### 3.4.2 Inconsistency Check for Partial Interpretations

Given a partial abstract interpretation that is not known to be a model of  $\varphi^b$ , we want to check the corresponding constraints for inconsistency to prune the search space (as in theory propagation) or to possibly avoid the more expensive check of Section 3.4.3. A set of constraints is assumed to be given along with ranges for every variable in them. It is also assumed that the graph has one SCC. If that is not the case, each SCC is checked in turn: The constraints are inconsistent if at least one SCC is inconsistent. Though the check described in the next section could be applied in this case, we are interested in a cheaper criterion.

The quick check for inconsistency is based on two observations: The first is that if all variables in the SCC have the same range, then the disequalities define a graph whose chromatic number must not exceed the size of the range for the constraints to be satisfiable. (The chromatic number is the least number of colors needed to assign different colors to adjacent vertices in the graph.) The second observation is that the chromatic number of a graph is bounded from below by the size of a clique of the graph and from above by the number of vertices. From these observations, it is easy to prove the following theorem.

**Theorem 3.2.** Let  $D_0$  be a set of disequality constraints of the form  $x_i - x_j \neq 0$ . Let  $X = \{x_1, \ldots, x_n\}$  be

the set of variables in  $D_0$ . Let  $L = \{l_1, \ldots, l_n\} \in Z^n$  and  $U = \{u_1, \ldots, u_n\} \in Z^n$  be the bounds on the variables in X ( $l_i \leq x_i \leq u_i$ ). For  $y_l, y_u \in Z$ , let  $\Gamma = \{\gamma_1, \ldots, \gamma_p\}$  be the subset of X such that

$$\Gamma = \{ x_i \in X \mid y_l \le l_i \land u_i \le y_u \} .$$

Let  $\rho = y_u - y_l + 1$ . Let  $G_D = (V, E)$  be the disequality graph associated to  $D_0$ , such that  $V = \{v_1, \dots, v_n\}$ and  $\{v_i, v_j\} \in E$  if and only if  $x_i - x_j \neq 0 \in D_0$  or  $x_j - x_i \neq 0 \in D_0$ . If  $G_D$  contains a clique of size greater than  $\rho$  then  $D_0$  is inconsistent.

**Example 3.3.** Consider the set of disequality constraints  $D_0 = \{(x - y \neq 0), (y - z \neq 0), (z - x \neq 0)\}$ with variables y, z that have the same range,  $0 \le y, z \le 1$ , and variable x that has range  $0 \le x \le 0$ which is a subset of the common range. Let  $y_l = 0$  and  $y_u = 1$ ; then  $\Gamma = \{x, y, z\}$ . A clique consisting of variables x, y, z is present in  $G_D$ . Since  $|\Gamma| = 3 > 2 = \rho$ , the constraints are inconsistent. An explanation of inconsistency consists of the disequality constraints  $\{(x - y \neq 0), (y - z \neq 0), (z - x \neq 0)\}$  and the inequality constraints that generated the range,  $0 \le y, z \le 1, 0 \le x \le 0$ .

The check based on Theorem 3.2 results in one of three outcomes: A suitable clique has been found and inconsistency is declared; a large enough clique was not found because of the heuristic nature of the algorithm; a large enough clique is known not to exist. In the first case, an explanation of inconsistency is derived from the disequalities forming the clique and the inequalities responsible for the bounds. In the last two cases, the result is inconclusive, because the chromatic number of a graph can be arbitrarily larger than the size of the largest cliques. However, if a large enough clique does not exist in the graph, and the interpretation is not known to be a model, we avoid a full check for inconsistency, which is rather expensive and likely to fail. (If the interpretation is a model, on the other hand, the consistency check must be performed for the whole decision procedure to be sound.)

#### 3.4.3 Consistency Check for Abstract Models

If the constraints correspond to a model of  $\varphi^b$ , we want to decide consistency and compute a model of  $\varphi$  in case the answer is affirmative. For this, we resort to finite instantiation. Specifically, we can encode

each integer variable with enough binary variables to span its range and translate the satisfiability problem for a conjunction of inequality and disequality constraints into a propositional satisfiability problem.

Theorem 3.1 applies when the constraint graph consists of one SCC. If that is not the case, we examine the SCC quotient graph one SCC at the time. If there is no negative cycle in the constraint graph G, the only reason for unsatisfiability is the inability to satisfy the disequalities within some SCC of G. Therefore, if the finite instantiation of each SCC is satisfiable, the entire set of constraints is satisfiable. This can be shown as follows.

Let G be the constraint graph. Extend G by adding one edge for every disequality constraint  $x-y \neq n$ (where n may be 0) such that x and y belong to different SCCs. Let  $\leq$  be the preorder defined by  $u \leq v$ if there is a path in G from u to v. (The preorder is updated after each edge addition.) If  $x \leq y$ , add  $y-x \leq -n-1$  to E; if  $y \leq x$ , add  $x-y \leq n-1$ . If x and y are not comparable in the preorder, add either  $y-x \leq -n-1$  or  $x-y \leq n-1$ , but not both. Note that adding these edges does not create cycles, and therefore does not change the SCCs of G. (See Sect. 3.5.)

Let  $\widehat{G} = (\widehat{V}, \widehat{E})$  be the SCC quotient graph of the extended G. Consider the vertices in  $\widehat{V}$  starting from the minimal SCCs (those with no predecessors) and proceeding in a chosen topological order. Let  $A_i$  be the *i*-th SCC in that order and let  $\alpha_i$  be a solution for the constraints corresponding to its edges. Inductively assume that  $\beta_{i-1}$  is a solution for the constraints in the subgraph induced by  $\bigcup_{0 < j < i} A_j$ . Let kbe the maximum amount by which any constraint corresponding to an edge into  $A_i$  is violated. (Let k = 0if no such violation exists.) Finally, let  $\alpha'_i = \alpha_i - k$ . Then,  $\beta_i = \beta_{i-1} \cup \alpha'$  is a solution for the constraints in the subgraph induced by  $\bigcup_{0 < j < i} A_i$ .

# 3.5 Algorithm

We assume a decision procedure for IDL based on propositional abstraction. The given IDL formula  $\varphi$  is translated into a propositional formula  $\varphi^b$  as described in Sect. 3.2. A **propositional reasoning engine** enumerates the models to  $\varphi^b$  and calls the **theory solver** to determine whether that abstract model corresponds to a consistent interpretation of the integer-valued variables.

The theory solver for IDL is relatively efficient. Therefore, it is advantageous to call it also on a

partial interpretations to terminate the fruitless search of part of the state space, or to learn so-called **theory consequences** [NO05]. Our implementation follows this approach, though the equality constraints ( $x - y = n \neq 0$ ) are split and the full check for inconsistencies due to disequalities is applied only to abstract models. (See lines 38–42 of Fig. 3.1.) We omit the details of the incremental implementation of the Bellman-Ford algorithm. The interested reader is referred to [WIGG05].

#### 3.5.1 The Theory Solver

The theory solver is called with a collection of arithmetic literals whose corresponding propositional literals are true in a (partial) interpretation of the propositional formula  $\varphi^b$ ; it then decides whether there is an interpretation to the integer-valued variables that satisfies the conjunction of all those literals. The first step is to obtain a set of arithmetic atomic formulae (without negations) from the given set of literals. The given literals are rewritten and divided into Q, I, and D as described in Sect. 3.2.

The theory solver, whose pseudocode is shown in Figures 3.1 and 3.2, adopts the **layered** approach of MathSAT [BBC<sup>+</sup>05b]. For IDL, it considers three main layers: equalities, inequalities, and disequalities. Let  $X_{=} \subseteq X$  be the set of integer-valued variables appearing in the equalities in Q. The theory solver creates an undirected equality graph  $Q = (X_{=}, \Gamma)$ , where

$$\Gamma = \{\{x_i, x_j\} : x_i = x_j \in Q\}$$

.

The vertices of  $\Omega$  are in the same class if they are made equivalent by the equality constraints. The feasibility of Q with  $D_0$  is checked by comparing the equivalence class of the two vertices of each disequality constraint in  $D_0$ . If two vertices are in the same class, an explanation of infeasibility is returned. If the set of equality constraints is feasible, the variables in the same class are merged into a single variable, and some simplified constraints in D and I are dropped from the set.