## Cache Attacks and Defenses

by

William Kosasih

This thesis is submitted for the degree of

Master of Philosophy

School of Computer Science

University of Adelaide

## Abstract

In the digital age, as our daily lives depend heavily on interconnected computing devices, information security has become a crucial concern. The continuous exchange of data between devices over the Internet exposes our information vulnerable to potential security breaches. Yet, even with measures in place to protect devices, computing equipment inadvertently leaks information through side-channels, which emerge as byproducts of computational activities. One particular source of such side channels is the cache, a vital component of modern processors that enhances computational speed by storing frequently accessed data from random access memory (RAM). Due to their limited capacity, caches often need to be shared among concurrently running applications, resulting in vulnerabilities. Cache side-channel attacks, which exploit such vulnerabilities, have received significant attention due to their ability to stealthily compromise information confidentiality and the challenge in detecting and countering them. Consequently, numerous defense strategies have been proposed to mitigate these attacks. This thesis explores these defense strategies against cache side-channels, assesses their effectiveness, and identifies any potential vulnerabilities that could be used to undermine the effectiveness of these defense strategies.

The first contribution of this thesis is a software framework to assess the security of secure cache designs. We show that while most secure caches are protected from eviction-set-based attacks, they are vulnerable to occupancy-based attacks, which works just as well as eviction-set-based attacks, and

therefore should be taken into account when designing and evaluating secure caches.

Our second contribution presents a method that utilizes speculative execution to enable high-resolution attacks on low-resolution timers, a common cache attack countermeasure adopted by web browsers. We demonstrate that our technique not only allows for high-resolution attacks to be performed on low-resolution timers, but is also Turing-complete and is capable of performing robust calculations on cache states. Through this research, we uncover a new attack vector on low-resolution timers. By exposing this vulnerability, we hope to prompt the necessary measures to address the issue and enhance the security of systems in the future.

Our third contribution is a survey, paired with experimental assessment of cache side-channel attack detection techniques using hardware performance counters. We show that, despite numerous claims regarding their efficacy, most detection techniques fail to perform proper evaluation of their performance, leaving them vulnerable to more advanced attacks. We identify and outline these shortcomings, and furnish experimental evidence to corroborate our findings. Furthermore, we demonstrate a new attack that is capable of compromising these detection methods. Our aim is to bring attention to these shortcomings and provide insights that can aid in the development of more robust cache side-channel attack detection techniques.

This thesis contributes to a deeper comprehension of cache side-channel attacks and their potential effects on information security. Furthermore, it offers valuable insights into the efficacy of existing mitigation approaches and detection methods, while identifying areas for future research and development to better safeguard our computing devices and data from these insidious attacks.

## Declaration of Authorship

I certify that this work contains no material which has been accepted for the award of any other degree or diploma in my name in any university or other tertiary institution and, to the best of my knowledge and belief, contains no material previously published or written by another person, except where due reference has been made in the text. In addition, I certify that no part of this work will, in the future, be used in a submission in my name for any other degree or diploma in any university or other tertiary institution without the prior approval of the University of Adelaide and where applicable, any partner institution responsible for the joint award of this degree.

The author acknowledges that copyright of published works contained within this thesis resides with the copyright holder(s) of those works.

I give permission for the digital version of my thesis to be made available on the web, via the University's digital research repository, the Library Search and also through web search engines, unless permission has been granted by the University to restrict access for a period of time.

# Acknowledgements

This research endeavor has been an enlightening experience for me, made possible by the collaboration, support, and warm encouragement from numerous individuals during my time at the University of Adelaide. I could not have embarked on this journey without the guidance of my supervisors, Professor Yuval Yarom and Dr. Chitchanok Chuengsatiansup. Without their assistance, this thesis would not have been achievable.

I owe immense gratitude to Dr. Cheryl Pope and Dr. Muhammad Uzair for their invaluable help and insights during some of the most difficult times in my academic journey. Their assistance allowed me to persist in my candidacy and ultimately complete this thesis.

I wish to extend my heartfelt thanks to Professor Olaf Maennel, Dr. Atanas Parashkevov, Dr. Cheryl Pope, and Dr. Muhammad Uzair for dedicating their time to review my thesis and offering valuable feedback.

Furthermore, I would like to express my appreciation to Emeritus Professor Michael Liebelt, Dr. Atanas Parashkevov, Ms. Diana Reed, and Professor Nelson Tansu for their irreplaceable counsel, support, and direction during the intricate process of my research. They have offered motivation in difficult moments and have been there to help when I faced challenges.

I am thankful for the University of Adelaide scholarship, which covered all my living expenses and allowed me to concentrate on my studies.

Lastly, I extend my heartfelt gratitude to my parents, partner, and close friends in Adelaide for their unwavering support, love, and care throughout my educational journey.

# Contents

| 1 | <b>Int</b> r<br>1.1      | Thesis Organization and Contributions                                                                                                                                                                                                                |

|---|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | Bac<br>2.1<br>2.2<br>2.3 | kground       9         Caches       9         Cache Side-Channel Attacks       13         The Processor Microarchitecture       14         2.3.1 Front End       15         2.3.2 Execution Engine       15         2.3.3 Memory Subsystem       15 |

|   | 2.4<br>2.5               | 2.3.3 Memory Subsystem15Branch Prediction16Transient-Execution Attacks162.5.1 Spectre17                                                                                                                                                              |

| 3 | A F                      | ramework to Evaluate Cache Security 19                                                                                                                                                                                                               |

|   | 3.1                      | Background                                                                                                                                                                                                                                           |

|   | 3.2<br>3.3               | Problem Description                                                                                                                                                                                                                                  |

|   | 5.5                      | CacheFX Design         22           3.3.1 Cache Model         22                                                                                                                                                                                     |

|   |                          | 3.3.2 Attack Model                                                                                                                                                                                                                                   |

|   |                          | 3.3.3 Victim Model                                                                                                                                                                                                                                   |

|   |                          | 3.3.4 The Attack Controller Function                                                                                                                                                                                                                 |

|   | 3.4                      | Evaluation                                                                                                                                                                                                                                           |

|   |                          | 3.4.1 Relative Eviction Entropy                                                                                                                                                                                                                      |

|   |                          | 3.4.2 Eviction-Set Creation                                                                                                                                                                                                                          |

|   |                          | 3.4.3 Eviction-Set Attack                                                                                                                                                                                                                            |

|   |                          | 3.4.4 Cache-Occupancy Attack                                                                                                                                                                                                                         |

|   | 0.5                      | 3.4.5 Optimal Eviction-Set Size                                                                                                                                                                                                                      |

|   | $\frac{3.5}{3.6}$        | Threats to Validity and Limitations                                                                                                                                                                                                                  |

|   | $\frac{3.0}{3.7}$        |                                                                                                                                                                                                                                                      |

|   | 5.1                      | Conclusion                                                                                                                                                                                                                                           |

| 4 | Spe                      | culative Execution Against Low-Resolution Timers 43                                                                                                                                                                                                  |

|   | 4.1                      | Gates                                                                                                                                                                                                                                                |

|   |                          | 4.1.1 Computational Model                                                                                                                                                                                                                            |

|   |                          | $4.1.2  NOT \text{ Gate}  \dots  45$                                                                                                                                                                                                                 |

|   |                          | 4.1.3 More Complex Gates                                                                                                                                                                                                                             |

|   |                          | 4.1.4 Multiple Inputs and Outputs                                                                                                                                                                                                                    |

|   |                          |                                                                                                                                                                                                                                                      |

|   |                          | 4.1.6 Gates With a Fixed Branch Delay                                                                                                                                                                                                                |

|   |                          | 4.1.7 Gates Without Branch Training                                                                                                                                                                                                                  |

|   | 4.2                      | Circuits                                                                                                                                                                                                                                             |

|   |                          |                                                                                                                                                                                                                                                      |

|                  |                          | 4.2.1 ALU                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | 4.3                      | 4.2.3 Game of Life54Probe Amplification554.3.1 Single-Gate Amplification564.3.2 Probe Time Amplification Tree574.3.3 Amplification Hyper-tree57                                                                                                                                                                                                                               |

|                  | 4.4                      | 4.3.5       Eviction Set Creation       60         Prime+Store: Fast Attacks with Slow Clocks       60         4.4.1       Prime+Store       61         4.4.2       Attacking ElGamal       61         4.4.3       Trace Acquisition       62         4.4.4       Trace Processing       63         4.4.5       Key Recovery       64         4.4.6       Evaluation       65 |

|                  | $\frac{4.5}{4.6}$        | Related Work         65           Conclusions         67                                                                                                                                                                                                                                                                                                                      |

| 5                | <b>Har</b> 5.1           | dware Performance Counters in Cache Attack Detection69Background705.1.1 Hardware Performance Counters705.1.2 HPC-Based Cache-Side Channel Attack Detection Methods71                                                                                                                                                                                                          |

|                  | 5.2                      | Survey of HPC-Based Cache Side-Channel Attack Detection Method Evaluation                                                                                                                                                                                                                                                                                                     |

|                  | 5.3                      | Assessing the Quality of Attack Detection Methods 78 5.3.1 Experiment Environment 78 5.3.2 Our Method 78 5.3.3 Accuracy 80 5.3.4 Overhead 81 5.3.5 Detection Speed 83 5.3.6 Threat Model 83                                                                                                                                                                                   |

|                  | 5.4                      | Conclusions                                                                                                                                                                                                                                                                                                                                                                   |

| 6                | Fut                      | ure Directions 90                                                                                                                                                                                                                                                                                                                                                             |

| 7                | Con                      | clusion 92                                                                                                                                                                                                                                                                                                                                                                    |

| R                | efere                    | nces 94                                                                                                                                                                                                                                                                                                                                                                       |

| $\mathbf{A}_{]}$ | A.1<br>A.2<br>A.3<br>A.4 | dix A Chapter 4107Hyper-tree Amplification Implementation107Gates With and Without Branch Training108Gate Accuracy110Gates on Other Processors112Number of Cases in Gates Without Branch Training114                                                                                                                                                                          |

# List of Tables

| 4.1                                                         | Game of Life glider accuracy                                                                                                                                                                                                                                                                                                                                                                                                                       | 55                                           |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9 | Survey result.  PAPI events used in our detection method.  Accuracy of three detection methods.  Accuracy of HPCache with various sampling interval.  Overhead of detection methods.  True positive rate of proof-of-concept and camouflaged attacks.  False positive rate of proof-of-concept and camouflaged attacks.  Accuracy of HPCache trained on camouflaged attacks.  Attack times for different Flush+Reload camouflaging aggressiveness. | 75<br>79<br>80<br>80<br>82<br>85<br>85<br>86 |

| A.2<br>A.3                                                  | Accuracy of gates on Intel Core(TM) i5-8250U Accuracy of gates on AMD Ryzen 5 3500U Accuracy of gates on Apple M1 and Samsung Exynos 2100 Accuracy and run time for $\operatorname{nbt} NAND_1^{12}$ and $\operatorname{nbt} NOT_2^1$ gates with different number of cases on Intel Core(TM) i5-8250U                                                                                                                                              | 111<br>113<br>114<br>115                     |

# List of Figures

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5 | Relationship between memory address and cache lines Mapping from memory to cache entries in direct-mapped caches Mapping from memory to cache lines in fully-associative caches. Mapping from memory to cache lines in set-associative caches. Simplified diagram of the Intel Skylake microarchitecture | 9<br>10<br>11<br>12<br>18 |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 3.1<br>3.2<br>3.3<br>3.4        | CacheFX design overview                                                                                                                                                                                                                                                                                  | 22<br>23<br>28            |

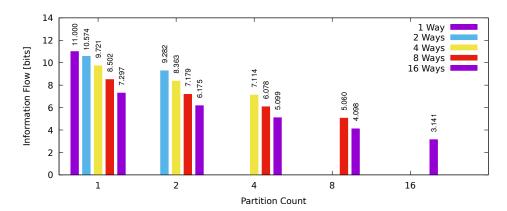

| 3.5                             | partitions                                                                                                                                                                                                                                                                                               | 29                        |

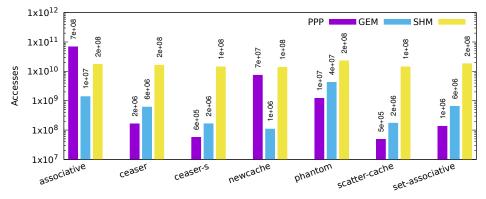

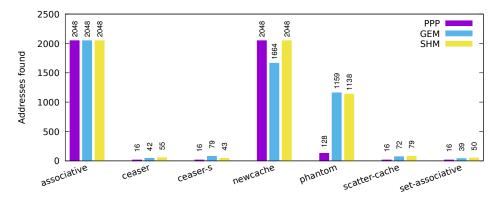

| 2 C                             | techniques for different 2048-line caches                                                                                                                                                                                                                                                                | 31                        |

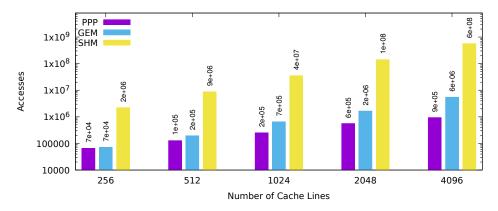

| 3.6                             | Number of memory accesses required by eviction-set building techniques for CEASER-S depending on cache size                                                                                                                                                                                              | 32                        |

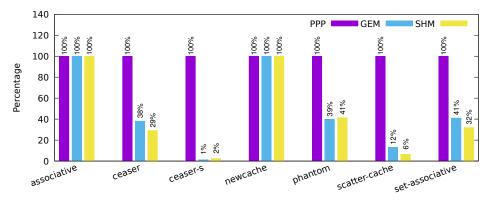

| 3.7                             | Percentage of addresses in the constructed eviction sets that conflict with the victim's address, using different eviction-set construction techniques and 2048-line caches                                                                                                                              | 32                        |

| 3.8                             | Eviction set sizes found by eviction-set building techniques for different 2048-line caches.                                                                                                                                                                                                             | 33                        |

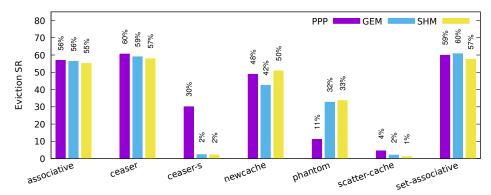

| 3.9                             | Eviction success rate for the eviction sets found for different 2048-line caches.                                                                                                                                                                                                                        | 34                        |

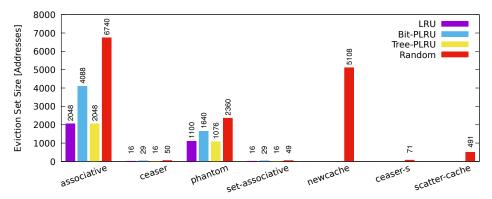

|                                 | Eviction set size for 2048-line caches and 90% eviction probability.                                                                                                                                                                                                                                     | 34                        |

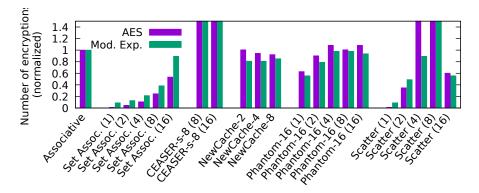

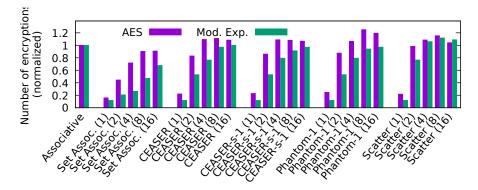

| 3.11                            | Eviction-set attack: Number of encryptions required to break AES and modular exponentiation with random replacement                                                                                                                                                                                      | 36                        |

| 3.12                            | Occupancy attack: Number of encryptions required to break AES and modular exponentiation with random replacement                                                                                                                                                                                         | 37                        |

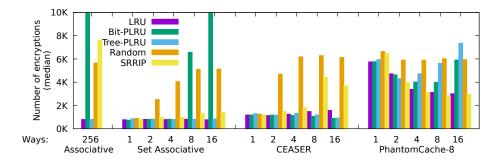

| 3.13                            | Median number of encryptions required to break AES with different cache designs and replacement algorithms                                                                                                                                                                                               | 38                        |

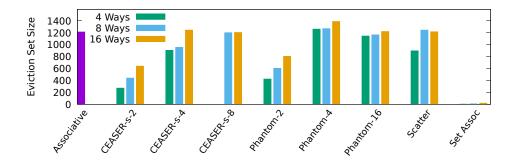

| 3.14                            | Optimal eviction set sizes for 1024-lines caches                                                                                                                                                                                                                                                         | 39                        |

| 4.1                             | NOT Gate                                                                                                                                                                                                                                                                                                 | 45                        |

| 4.2                             | A Buffer Gate with a fixed branch delay                                                                                                                                                                                                                                                                  | 49                        |

| 4.3                             | ALU accuracy.                                                                                                                                                                                                                                                                                            | 52                        |

| 4.4                             | SHA-1 accuracy                                                                                                                                                                                                                                                                                           | 54                        |

| 4.5                             | T-tetromino heatmap.                                                                                                                                                                                                                                                                                     | 54                        |

| 4.6                             | One generation Game of Life accuracy                                                                                                                                                                                                                                                                     | 56                        |

| 4.7                             | Amplification tree based on $NOT_Y^1$ Gates                                                                                                                                                                                                                                                              | 57                        |

| 4.8                             | Amplification Hyper-Tree in native                                                                                                                                                                                                                                                                       | 59                        |

| 4.9                             | Amplification Hyper-Tree in WebAssembly                                                                                                                                                                                                                                                                  | 59                        |

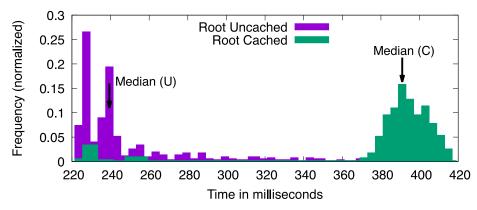

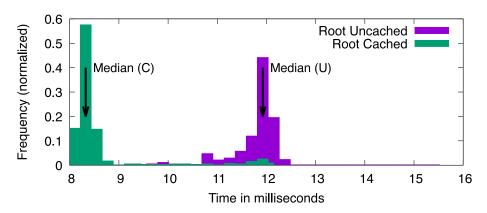

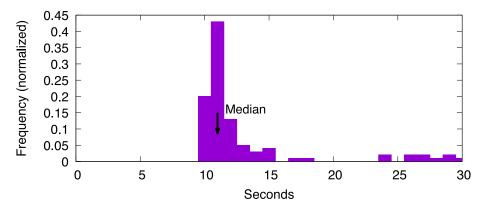

| 4.10                            | Time to find an eviction set in Chrome using 0.1 millisecond                                                                                                                                                                                                                                             |                           |

| 4 4 4                           | low-resolution timer                                                                                                                                                                                                                                                                                     | 60                        |

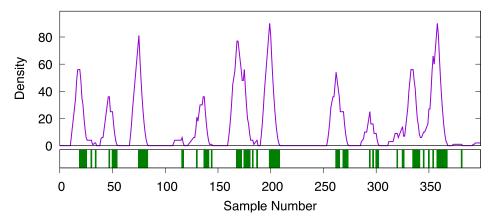

| 4.11                            | A segment of samples of the square operation in modular expo-                                                                                                                                                                                                                                            | 00                        |

|                                 | nentiation                                                                                                                                                                                                                                                                                               | 63                        |

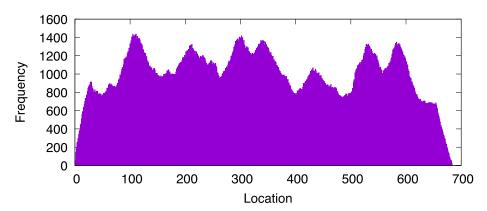

4.12 Distribution of stitched key in relation to ground truth location. 65

# Chapter 1

## Introduction

Information security in computing is a very critical issue, especially in this day and age that almost all aspects of our lives are in one way or another reliant on computers as well as the network that connect them, the Internet. Used for trivial activities such as a simple web browse, to tasks that are sensitive in nature, such as banking, our computing devices are constantly interacting with all kinds of other computers all around the globe. While this digital interconnection has gifted us with communication ease and agility [Adams, 2017; Elijah et al., 2018; Levy and Strombeck, 2002], much to our unknowing (or perhaps ignorance), it has simultaneously created a risk of exposing our data essentially to anyone, or anything that we interact with on the web [Adams, 2017; Karunakaran et al., 2018; Wheatley et al., 2016].

Given the situation, it is only natural to expect people and organizations to pay utmost attention towards the security of their computing devices. Yet, day after day we continue to hear headlines about major data breaches each affecting thousands, and even millions of unfortunate users [Adams, 2017; Biddle et al., 2022; Booth, 2022; Cadwalladr and Graham-Harrison, 2018; Karunakaran et al., 2018; Pilla et al., 2023; Wheatley et al., 2016]. With these evidences in hand, it is clear that people, and especially major corporations need to allocate even more efforts towards protecting information security [Fedele and Roner, 2022; IBM, 2022].

Nevertheless, regardless of how much effort we allocate into safeguarding our devices, we cannot escape the reality that computing equipment innately leaks information as it operates [Briongos et al., 2016; Martin et al., 2012]. Computers leave traces of their computing activities as they function, in the same manner that biological organisms leave footprints of their metabolism activities as they go about living. These traces are basically side-effects of computation, called side-channels. These side-effects include acoustic [Genkin et al., 2014; O'Malley and Choo, 2014], electromagnetic [Elibol et al., 2012; Hongxin et al., 2009], power [Kocher et al., 1999; Mangard, 2003], cache [Liu et al., 2015; Osvik et al., 2006], and timing [Dhem et al., 2000; Kocher, 1996].

In this thesis, we direct our attention towards the cache side-channel. The

cache is a piece of temporary memory intended to speed up computation. Advances in technology have brought about performance enhancements to all aspects of computing. Most notably of all is the processor, which has sped up dramatically over the decades. Working in close conjunction to the processor is the random access memory (RAM). The RAM is used as a storage to provide input and store output of intermediate data to/from the processor before they are permanently recorded on disks. While the RAM has also gained significant performance improvement over the years, since the late 1990s their increase in speed has lagged considerably behind that of the processor, and the gap continues to widen as time goes by. This situation prompted the introduction of caches to processors. They are a form of smaller but much faster memory that stores copies of frequently used data from the RAM, enabling the processor to work at a much higher rate as it can now avoid the delays caused by the slow RAM.

Due its finite size, the cache often has to be shared between different applications that are simultaneously running in a computer. As mentioned above, all computing operations leave traces on the hardware they operate on, including the cache. The execution of programs alter the state of the cache. When a program performs a large number of data accesses, the cache eventually has to remove older data to make room for new ones. The cache decides what data need to be evicted typically based on their age, and is completely agnostic to whether the eviction of data is caused by the application who owns the data. Removal of other applications' data may appear harmless, after all, the processor seamlessly orders reinsertion of needed data back into the cache on an ad-hoc basis, and execution continues as usual. However, this slightly affects the data access speed of those applications whose data are temporarily removed from the cache. By closely monitoring this access time difference caused by data eviction, any application suddenly gains a potentiality to infer the execution of other programs running on the system. In other words, gaining an access to a side-channel. The act of a malicious application, seeking to gain illicit information about the system through measurements of cache-related phenomena is called cache side-channel attack.

Cache side-channel attacks have received attention both in academia and the industry in recent years given their ability to stealthily compromise information confidentiality through the exploitation of the cache hardware [Aciiçmez and Seifert, 2007; Aldaya et al., 2019a; Aldaya et al., 2019b; Genkin et al., 2020; Gullasch et al., 2011; Gülmezoglu et al., 2019b; Liu et al., 2015; Oren et al., 2015; Osvik et al., 2006; Percival, 2005; Ristenpart et al., 2009; Ronen et al., 2019; Shusterman et al., 2019; Yarom and Falkner, 2014; Yarom et al., 2017; Zhang et al., 2012]. Unlike traditional malware that leaves obvious traces of their activities, cache side-channel attacks leave only microarchitectural traces and are more difficult to detect and mitigate [Alam et al., 2021; He and Lee, 2017]. Yet, they are sometimes seen as an improbable

<sup>&</sup>lt;sup>1</sup>Microarchitecture refers to the internal implementation of the processor.

threat, and a very specialized domain of computer systems security. This view may be held as a result of the high complexity involved with implementing such attacks [Apple, 2018; Easdon et al., 2022; Yarom, 2016], the "black-box" nature of microarchitectural components due to the lack of official documentations [Easdon et al., 2022], possibly leading to an incorrect viewpoint that cache attacks are more of an academic proof of concept rather than a practical attack.

In actuality, history has shown the potential for disastrous outcomes of such attacks, particularly when combined with other microarchitectural attacks such as transient-execution attacks, forming a highly effective pairing. This was evident in the 2018 discovery of Spectre [Kocher et al., 2019] and Meltdown [Lipp et al., 2018], which showcased the potential of these attacks to compromise crucial operating system information and sensitive user data. In this context, it is important to uncover and tackle potential hardware vulnerabilities and create countermeasures for existing devices.

While completely eradicating cache attacks is challenging, there are approaches designed to reduce or obscure cache side-channels, making it difficult for attackers to extract valuable information. Hardware-level mitigation such as secure caches are available [Domnitser et al., 2012; Liu et al., 2016b; Qureshi, 2018; Qureshi, 2019; Tan et al., 2020; Wang and Lee, 2007; Werner et al., 2019], along with software-level mitigation such as low-resolution timers [Chromium, n.d.; Hazen, 2018; Wagner, 2018], attack detection systems [Akram et al., 2020; Depoix and Altmeyer, 2018; Mushtaq et al., 2018a; Mushtaq et al., 2018b; Payer, 2016], and constant-time programming [Bernstein et al., 2012; Liu et al., 2015]. Despite the protection that these countermeasures presently offer, we must consistently search for new security vulnerabilities proactively, rather than reactively responding only after attacks have occurred.

The same principle applies to cache side-channel attack defense techniques; we must continuously evaluate, scrutinize, and explore ways in which they can be compromised. Therefore, this thesis aims to 1) evaluate the effectiveness of defense techniques against cache side-channel attacks, 2) identify their short-comings and reveal new attack scenarios that may lead to their compromise, and 3) evaluate the practicality of these techniques for broad adoption.

We begin our investigation by focusing on the hardware-level, specifically on secure caches. Numerous secure cache designs have been proposed that aim to protect against data leakage. However, the diverse range of these proposals and their unique evaluation metrics make it difficult to empirically analyze their security features. While several metrics have been suggested for performing such evaluations, these tend to be limited both in terms of the potential adversaries they consider and in the applicability of the metric to real-world attacks, as opposed to attack techniques. Moreover, all existing metrics implicitly assume that a single metric can encompass the nuances of side-channel security. To fill this gap, this thesis presents CacheFX, a software-

based cache simulation framework as a way for assessing the security of secure caches, specifically by determining their effectiveness against side-channel attacks. CacheFX allows the evaluator to implement various cache designs, victims, and attackers, as well as to exercise them for assessing the leakage of information via the cache.

We then continue our investigation by focusing on software-level cache defense, specifically low-resolution timers. As cache attacks often require a high-resolution timing source to successfully distinguish between cache hits and misses, low-resolution timers limit the resolution of available timers, thus making attacks more difficult. As mentioned, proactive investigation of computing devices is crucial for detecting and eliminating vulnerabilities. As part of our proactive research effort, we examine the potential vulnerability of lowresolution timers as a countermeasure to attacks, specifically how this defense mechanism can be compromised by attacks capable of bypassing its safeguards. While numerous studies have looked into cache states as a "receiver" of microarchitectural outcomes from transient execution attacks [Kocher et al., 2019; Lipp et al., 2018, none have investigated the reverse perspective: the possibility of leveraging transient execution to facilitate cache attacks on systems using mitigation measures such as low-resolution timers. This thesis delves into this alternative viewpoint and evaluates the security implications of such a method against low-resolution timers as a cache attack defense technique.

We conclude our investigation with an examination of an emerging defense technique known as attack detection systems. Previously mentioned hardwarebased defenses, such as secure caches, cannot be implemented on current hardware, while software-based countermeasures such as low-resolution timers may significantly disrupt functionality and degrade performance. Instead of incurring the cost of continuous protection, even during periods without attacks, an alternative approach aims to identify ongoing attacks and only activate countermeasures when an attack is detected. A widely used approach in this domain involves the utilization of hardware performance counters (HPCs). These counters monitor microarchitectural events and analyze statistical deviations to differentiate between malicious and benign software. With numerous proposals and promising reported results, we seek to investigate whether published HPC-based detection methods are evaluated in a proper setting and under the right assumptions, such that their quality can be ensured for realword deployment against cache side-channel attacks. To achieve this goal, this thesis presents a comprehensive evaluation and scrutiny of existing literature on the subject matter in a form of a survey, accompanied by experimental evidences to support our evaluation.

## 1.1 Thesis Organization and Contributions

Background (Chapter 2)

This chapter provides the background for the rest of this thesis. Initially, we provide an overview of the cache and its application in computers, as well as its operational principles and the potential security risks associated with it. We then delve into the topic of cache side-channel attacks, exploring their various types. We continue by introducing the concept of the processor microarchitecture, and branch prediction which are integral parts of modern processors. We conclude with the discussion on branch prediction, and transient execution attack.

#### A Framework to Evaluate Cache Security (Chapter 3)

This chapter presents CacheFX, a software-based cache simulation framework as a way for assessing the security of secure caches, specifically in the context of mitigating contention-based attacks. CacheFX allows for the emulation of various cache designs, victims, and attackers, and measures the resulting leakage. Within this framework, we implement and evaluate nine cache designs: fully-associative and set-associative caches, PLCache [Wang and Lee, 2007], Newcache [Liu et al., 2016b], PhantomCache [Tan et al., 2020], Scatter-Cache [Werner et al., 2019], way-partitioned caches [Domnitser et al., 2012], and the two variants of CEASER [Qureshi, 2018; Qureshi, 2019]. Furthermore, we modeled five replacement algorithms: random replacement, least recently used (LRU) [Denning, 1968], two variants of pseudo-LRU, and SRRIP [Jaleel et al., 2010].

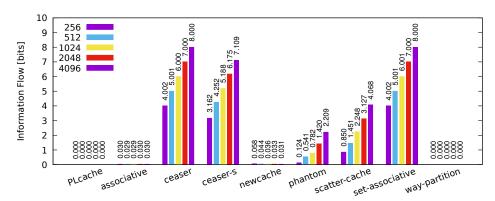

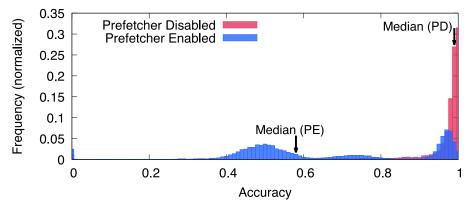

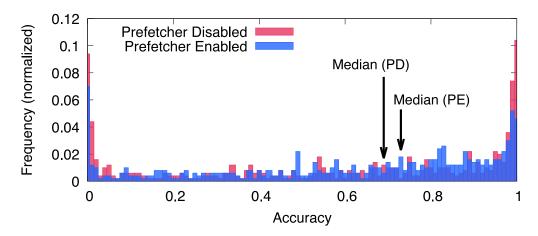

We further contribute three evaluation metrics. These not only add to the existing portfolio of metrics proposed in prior works, allowing cache designers more options for cache evaluation, but also demonstrate the flexibility of CacheFX and its ability to measure a variety of metrics. The first metric we contribute is the *Relative Eviction Entropy* (REE), which we propose to measure the information leakage from a single victim access via the cache side channel. The second evaluation metric we contribute measures the difficulty of eviction-set creation. We implement and evaluate three eviction-set building strategies: Single Holdout Method (SHM) [Liu et al., 2015], Group Elimination Method (GEM) [Vila et al., 2019] and Prime+Prune+Probe (PPP) [Purnal et al., 2021b]. The final metric we contribute evaluates the protection that the cache provides for cryptographic code. We evaluate both traditional attacks that aim to exploit eviction sets, and occupancy-based attacks [Shusterman et al., 2019; Shusterman et al., 2021a].

Through this chapter, we gain three key insights. First, we establish that different metrics highlight different aspects of the caches. In particular, we find that building eviction sets is faster in skewed caches such as ScatterCache and CEASER-S, than other randomized caches, such as fully associative caches or PhantomCache. Faster eviction-set construction reduces the effort required for mounting attacks. At the same time, our experiments show that, with the right parameters, skewed caches are not less secure when it comes to cryptographic attacks. Second, we find that the security against cryptographic attackers depends not only on the design, but also on other parameters, such

as the replacement policy and the cache associativity. We also show that all non-partitioned caches are vulnerable to both eviction-set and occupancy attacks. Third, we find that most non-partitioned secure cache designs offer protection against eviction-set attacks. However, cache-occupancy attacks are left unconsidered and for highly secure designs occupancy attacks are no less effective than eviction-set attacks. Our evaluation thus demonstrates that partitioning is preferable from a side-channel perspective and the resistance to eviction-set attacks of non-partitioned solutions may be tuned to match the respective complexity of cache-occupancy attacks to balance overall cache side-channel resistance and cost.

#### **Personal Contribution**

In this research, my personal contributions include various aspects. I was involved in the development of the simulator, taking on tasks such as refactoring and reorganizing its structure, as well as extending it by incorporating experiments to establish the ideal eviction set size for different cache designs. Additionally, I implemented a new replacement policy in the simulator, specifically SRRIP, and carried out the experiment to determine the optimal eviction set size, collecting the relevant data. Lastly, I wrote the sections detailing the design of the simulator and the experiments I performed.

#### **Publication**

Daniel Genkin, William Kosasih, Fangfei Liu, Anna Trikalinou, Thomas Unterluggauer, and Yuval Yarom. "CacheFX: A Framework for Evaluating Cache Security". In: *The 18th ACM ASIA Conference on Computer and Communications Security*, ACM ASIACCS 2023.

#### Speculative Execution Against Low-Resolution Timers (Chapter 4)

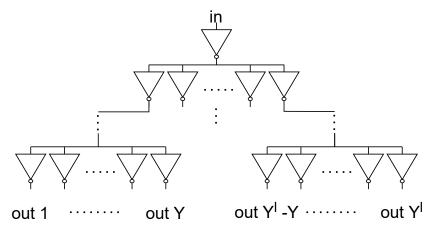

In this chapter, we present a novel transient-execution method aimed at circumventing low-resolution timers, a common defense against cache side-channel attacks used in web-browsers. We investigate, for the first time, how transient execution can be used for improving cache attacks, specifically on systems with low-resolution timers. This chapter contributes novel logical gates whose underlying operating concept lies on speculative execution. These gates are capable of manipulating the state of the cache based on whether data is cached or not, and are both generic and versatile. They work on multiple architectures including Intel and AMD, Samsung Exynos, and Apple M1, and can even be implemented in WebAssembly.

The next contribution of this chapter is a novel cache state amplification technique using our gates. We show that our gates can be used to amplify a small timing difference and distinguish whether a memory address is cached with a low-resolution timer, and use this amplification to build eviction sets in WebAssembly, using only a low-resolution timer. In addition, this chapter contributes a novel attack, called Prime+Store that allows for high-resolution cache attacks with a low-resolution timer.

In addition to facilitating cache attacks on low-resolution timers, we show that these gates can also be leveraged to perform logical manipulation of cache states. Intrigued by this discovery, we investigate the possibility of leveraging these gates to carry out meaningful computations within the cache, without elevating the state to the architectural level. We use these gates to construct an arithmetic logic unit (ALU), the Secuire Hash Algorithm 1 (SHA-1), and the Game of Life. We demonstrate that our gates are sufficiently robust to perform arbitrary calculations in the cache.

#### **Personal Contribution**

In this research, I designed the experiments for, collected data on, and analyze the results of the arithmetic logic unit (ALU), Secure Hash Algorithm 1 (SHA-1), and Game of Life implementations. Furthermore, I conducted statistical tests on all samples and adapted gates for AMD, Samsung Exynos, and Apple M1 platforms while evaluating their performance. I also devised the key-stitching technique, improved the method for converting Prime+Store traces into square and multiply sequences, and extracted the complete ElGamal key from the traces. In addition, I created an error-correction mechanism for microarchitectural computation and authored sections related to my work.

#### **Publication**

Daniel Katzman, William Kosasih, Chitchanok Chuengsatiansup, Eyal Ronen, and Yuval Yarom. "The Gates of Time: Improving Cache Attacks with Transient Execution". In: *The 32nd USENIX Security Symposium*, USENIX Security 2023.

# Hardware Performance Counters in Cache Attack Detection (Chapter 5)

This chapter presents a comprehensive survey on existing hardware performance counter (HPC)-based cache side-channel detection methods. evaluate the settings and assumptions under which these detection methods are evaluated, and discover that the promising results reported in most of them may not be applicable in realistic scenarios. We subsequently identify four main shortcomings in many proposals: improper evaluation settings and assumptions of accuracy, overhead, and detection speed, and a weak threat model used to evaluate detection methods. Notably, we find that the threat model employed assumes that attackers use variants of published proof-ofconcept attacks. To underscore the limitations of this assumption, we present a new variant of the Flush+Reload attack on GnuPG that camouflages its malicious execution behind that of a benign application, demonstrating how real-world attacks may differ significantly in terms of implementation and behavior from proof-of-concept attacks. We demonstrate the feasibility of such attacks in evading detection, while at the same time, capable of effectively stealing private encryption keys. We conclude that addressing the evaluation shortcomings we have highlighted is essential to determine the true effectiveness of these detection methods for real-world deployment.

#### **Personal Contribution**

In this study, I established the paper's foundation, developed its contents, conducted experiments, and completed the writing process. I performed an extensive literature review on cache side-channel attack detection and critically analyzed the subject. I identified weaknesses and drawbacks in the 48 papers examined and organized my analysis accordingly. I developed the cache side-channel attack detection method used in this chapter and evaluated its detection accuracy alongside two other publicly available detection methods. I also devised a new type of camouflaged Spectre and Flush+Reload attacks that interleave malicious activities within benign program execution. Additionally, I assessed the detection rate of these camouflaged attacks by various detection methods. I demonstrated that our camouflaged attacks successfully perform Flush+Reload attacks by stealing the ElGamal key and evaluated the duration of these attacks in relation to their camouflaging aggressiveness.

#### Conclusion (Chapter 7)

This chapter provides a summary of the key findings and results presented in this thesis.

#### Future Directions (Chapter 6)

This chapter outlines potential directions for future research that can be pursued based on the findings and results presented in this thesis.

## Chapter 2

# Background

#### 2.1 Caches

Modern processors takes advantage of caches to exploit spatial and temporal locality and speed up accesses to memory data, address translation, and branch prediction information. These caches are commonly organized in hierarchies, e.g., modern Intel CPUs have dedicated L1 data and instruction caches, a unified L2 cache for each core, and a last-level cache (LLC) shared by all cores. The L1 has the lowest latency, yet is smallest in size. Conversely, the LLC is the slowest but has the largest capacity.

Cache Hits and Misses. When the processor requires memory data, it first checks in the relevant L1 cache. In a cache hit, when the data is found, it is served from the cache. Otherwise, in a cache miss, the processor retrieves the data from a lower cache level or from memory if the requested data is not present on any level in the cache hierarchy. Once the data is fetched, it is stored in the cache for future use. A similar process is used for retrieving address translation and branch prediction results.

Cache Structure. Cache memory stores data in fixed-size blocks referred to as *lines*, which serve as the smallest unit for loading and storing cached data to and from memory, for example, 64 bytes. These lines are situated in one of the available spaces, or entries, within the cache hardware. Consequently, in this thesis, the term *line* refers to the actual data block housed in the cache, while the word *entry* denotes the hardware slot within the cache that accommodates the lines.

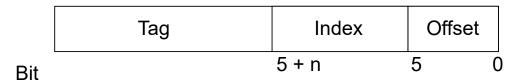

Figure 2.1: Relationship between memory address and cache lines

Figure 2.1 illustrates the relationship between memory addresses and lines

Figure 2.2: Mapping from memory to cache entries in direct-mapped caches

for a cache with 64 byte-wide line. The *offset* bits represents the position of a specific byte or word within a cache line, and is derived from the lower-six bits of the memory address. This means that access to any 64 byte within addresses with matching tag and index bits falls within a same cache line. The index bits determine which entry in the cache an address maps into. And finally, the tag is used to differentiate between addresses of different memory locations that share the same index bits, and are mapped to the same entry in the cache.

Direct-Mapped Cache A direct-mapped cache associates addresses with entries based on their index bits. This creates a one-to-one mapping between the index and the cache entry, which wraps-around when the index bits overflow. As a result, addresses sharing identical index bits are mapped to the same cache entry. To differentiate between different lines, the tag bits are used. They indicate that although different addresses are directed to the same cache entry, they are distinct cache lines if they have distinct values in their more significant bits.

Figure 2.2 illustrates the association between memory addresses and their corresponding entries in a direct-mapped cache with a 16-line capacity. Observe that the first and last address mappings align with the cache's first entry, as their index bits are identical. However, the cache can differentiate the two due to their distinct tags.

The issue with this cache design is the potential for thrashing, which can occur when multiple memory locations with matching indexes but distinct tags

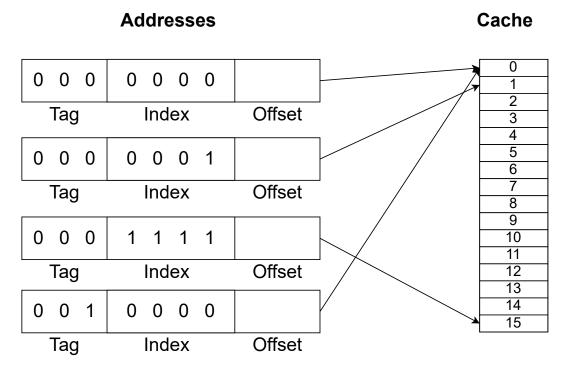

Figure 2.3: Mapping from memory to cache lines in fully-associative caches. Any address may occupy any entry in the cache.

are accessed frequently. In this situation, each access will continuously replace the others' line, irrespective of the cache's actual usage.

Fully-Associative Cache In a fully-associative cache, any memory location can be placed in any cache entry. As a result, the tag and index bits serve the sole purpose of distinguishing between cache lines and hold no significance in determining the entry where the line is to be stored. Figure 2.3 demonstrates how memory addresses map to cache entries in a fully associative cache, noting that data can reside in any of the 16 available entries. When searching for a line, fully-associative caches simultaneously searches all the cache entries for data corresponding to that line.

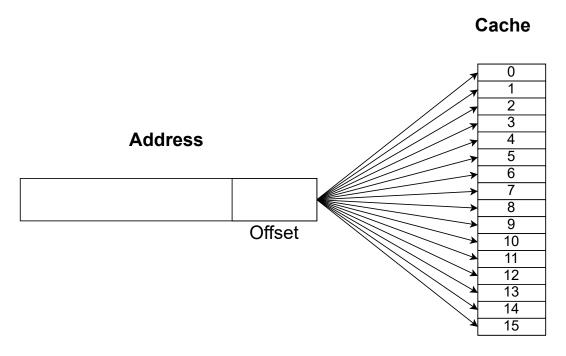

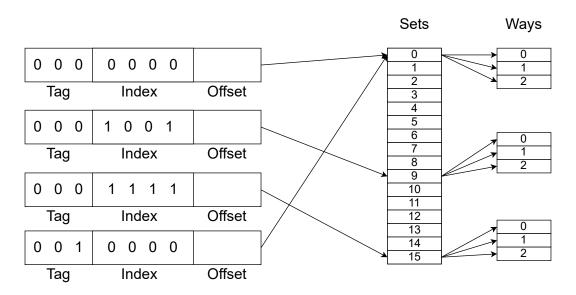

Set-associative Caches In this model, the cache is arranged into sets and ways. Identical to direct-mapped caches, index bits are used to determine the entry of an address in the cache. However, each entry is capable of holding more than a single line at a time. A set-associative cache capable of holding k lines in each entry is called a k-way set-associative cache. Entry in the cache as determined by the index bits is called a set, and each of the k entries within a set is called a way. Note that data can be placed in any of the k ways within a set, meaning that access within a set is associative. When searching for a line in a set-associative cache, the processor first finds the set it maps to and then uses an associative lookup in the set. Figure 2.4 illustrates the mapping of addresses in a three-way set-associative cache.

Small caches are often fully-associative, as they offer optimal hit-rate and cache utilization. However, fully-associative caches do not scale well in terms

Addresses Cache

Figure 2.4: Mapping from memory to cache lines in set-associative caches. Addresses are map to the set based on their index bits. Within a set, that address may occupy any way.

of power and performance. Thus, larger caches are often set-associative, which gives a better trade-off between capacity, hit-rate, and implementation complexity.

Cache Replacement Policies. As caches eventually run out of space due to their limited size, when new data needs to be stored, the cache evicts older data to make room for new ones. The choice of which data to evict is dictated by replacement policies. One such policy is the random policy, which randomly chooses any cache line to evict. Another policy is the LRU (Least Recently Used) policy, which keeps track of the access time of data in the cache. It selects the candidate that has not been used for the longest duration. To approximate the LRU algorithm without maintaining the full access order, methods such as: Bit-PLRU and Tree-PLRU are used. Bit-PLRU utilizes a single bit for each candidate line. Initially, these bits are set to zero and are changed to one upon access. If setting a bit to one would result in all candidate bits being set, all the candidate bits are cleared before setting the bit. The replacement algorithm selects an arbitrary candidate whose bit is clear. Tree-PLRU constructs a binary tree with candidates located at the leaves. Each internal node of the tree has a direction bit that indicates the side of the most recent access. The replacement candidate is chosen by traversing the tree and selecting the half whose direction bit indicates least recently accessed data.

### 2.2 Cache Side-Channel Attacks

While data eviction caused due to program activity is non-malicious in the context of a single process, cross-eviction between different application contexts could potentially be exploited to break information isolation guarantees between applications. By observing timing differences of access to data, an attacker can infer whether or not the data is present in the cache, and therefore learn about the execution of a victim program.

The pioneering work of Tsunoo et al. (2002) demonstrated the ability to exploit this information for the recovery of secret cryptographic keys. Initial attacks primarily focused on the L1 data cache [Osvik et al., 2006; Percival, 2005; Tsunoo et al., 2003, but soon expanded to include other caches as well [Aciicmez, 2007; Aciicmez et al., 2007; Gras et al., 2018; Gullasch et al., 2011; Irazoqui Apecechea et al., 2015; Liu et al., 2015; Yan et al., 2019a; Yarom and Falkner, 2014]. Cache attacks have also been successfully deployed against various cryptographic systems, including symmetric cryptography [Genkin et al., 2020; Gullasch et al., 2011; Irazoqui Apecechea et al., 2015; Moghimi et al., 2017; Osvik et al., 2006; Tsunoo et al., 2002; Tsunoo et al., 2003], public-key schemes [Aciiçmez et al., 2007; Dall et al., 2018; Gras et al., 2018; Liu et al., 2015; Percival, 2005; Pereida García and Brumley, 2017; Ronen et al., 2019; Yarom and Falkner, 2014, post-quantum cryptography [Groot Bruinderink et al., 2016; Pessl et al., 2017, and even non-cryptographic software [Brasser et al., 2017; Evtyushkin et al., 2016; Gras et al., 2017; Gruss et al., 2015; Hund et al., 2013; Oren et al., 2015; Shusterman et al., 2019; Yan et al., 2020].

Reload-Based Attacks Reload-based attacks involve monitoring shared memory access [Gruss et al., 2015; Gullasch et al., 2011; Yarom and Falkner, 2014]. To prepare for an attack, an adversary evicts data from the cache either by issuing a special command [Gullasch et al., 2011; Yarom and Falkner, 2014] or by creating contention within the cache sets that contain the data [Gruss et al., 2015]. After waiting for a certain amount of time, the attacker then measures how fast its access is to the previously removed data. If the data is accessed by the victim while the attacker is waiting, the data will be brought back into the cache, allowing the attacker to also quickly fetch the data, thus learning about the cache state of said data.

Contention-Based Attacks, Contention-based attacks are attacks that exploit the limited storage capacity within the cache, particularly within individual cache sets [Aciçmez, 2007; Aciçmez et al., 2007; Gras et al., 2018; Irazoqui Apecechea et al., 2015; Liu et al., 2015; Osvik et al., 2006; Percival, 2005; Yan et al., 2019a]. The most commonly used technique in contention-based attacks is Prime+Probe. In this technique, the attacker accesses its own data, to fill some or all of the cache sets, i.e., priming the cache. After allowing the victim to execute for a certain period of time, the attacker measures the access time to the cached data. If the access is slow, it suggests that the data has been removed from the cache set as a result of victim activities.

Variations of this attack refrain from using timing information by utilizing performance counters [Bhattacharya and Mukhopadhyay, 2015; Brasser et al., 2017; Uhsadel et al., 2008] or transaction aborts [Disselkoen et al., 2017] for contention detection, instead of relying on timing measurements.

Another contention-based attack technique is Evict+Time [Gras et al., 2018; Jain et al., 2019; Osvik et al., 2006; van Schaik et al., 2017]. In this approach, the attacker first evicts data from the cache prior to measuring the execution time of the victim. If the evicted data is accessed by the victim, it leads to a longer execution time, thereby revealing information about the cache sets accessed by the victim.

Other Types of Cache Attacks. There are certain cache attacks that do not fall under the previously mentioned categories. These attacks aim to take advantage of specific implementation characteristics of the cache itself. Examples of such attacks include leveraging port contention [Yarom et al., 2017], cache flushing time [Gruss et al., 2016], replacement policies [Purnal et al., 2021a; Vila et al., 2020; Xiong and Szefer, 2020], cache inspection operations [Brumley, 2015], or variations in power consumption [Page, 2002].

Eviction-Set Construction. In many of the aforementioned attacks, the attacker requires the ability to regularly remove certain data from the cache. This is often achieved by creating an eviction set, which comprises memory locations, all of which are mapped to the same set in the cache as the targeted data that needs to be evicted. Constructing an eviction set is usually straightforward when the attacker is able to gain access to the mapping information for the cache. However, in cases where the mapping function is undisclosed or the cache indexing information is not accessible to the attacker, more advanced techniques can be used to recover the absent mapping details. Previous research has demonstrated methods to reverse-engineer undocumented mapping functions [Gras et al., 2018; Inci et al., 2016; Maurice et al., 2015b; McCalpin, 2021; Yarom et al., 2015] and create eviction sets without relying on physical address information [Liu et al., 2015; Purnal et al., 2021b; Vila et al., 2019].

## 2.3 The Processor Microarchitecture

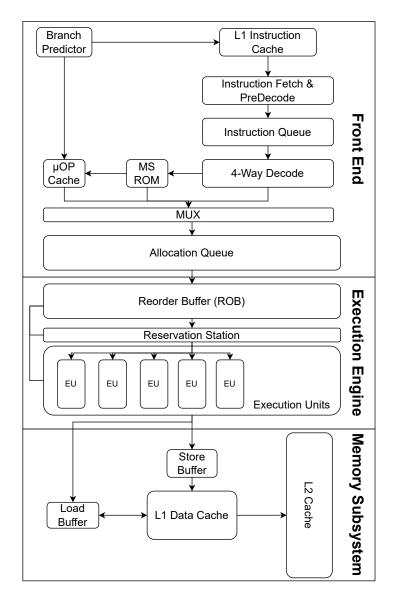

Contemporary processors are composed of an extensive array of components and algorithms that together execute the instruction set architecture (ISA), which is collectively referred to as the *microarchitecture*. The microarchitecture defines how program executions are carried out internally within modern processors. Program execution in these processors entails numerous stages and elements that work in tight conjunction to one another to achieve optimal performance and efficiency. A simplified representation of the Intel Skylake microarchitecture can be seen in Figure 2.5, which illustrates that three main components are responsible for this process: the front end, the execution engine, and the memory subsystem. For the purposes of this thesis, our primary focus is on gaining a deeper understanding of the Intel microarchitecture.

#### **2.3.1** Front End

The front end is responsible for fetching instructions from memory, decoding them, and transferring them to the execution engine for execution. This involves several sub-stages, including instruction prefetching, branch prediction, and instruction decoding. Prefetching anticipates the instructions that will be needed in the near future. Branch prediction, on the other hand, attempts to predict the outcome of conditional branches, allowing the processor to speculatively execute instructions and thereby reduce the impact of control dependencies on performance. Instruction decoding is the process of translating instructions into simpler, fixed-length micro-operations ( $\mu$ ops), which can be more efficiently processed by the execution engine.

### 2.3.2 Execution Engine

The execution engine is responsible for executing the  $\mu$ ops provided by the front end. It comprises several sub-components, including the reorder buffer, reservation stations, and execution units. To maximize instruction-level parallelism, the execution engine does not strictly follow the program's specified order of instructions. Instead, it executes instructions immediately after their dependencies are resolved and suitable execution units are available. This is called out-of-order execution. To support out-of-order execution, the front end and execution engine utilize a shared data structure called the reorder buffer (ROB). The front end adds instructions to the tail of the ROB, and the execution engine employs a variation of the Tomasulo algorithm [Tomasulo, 1967] to execute instructions in a more optimal order. The ROB keeps track of the instructions in flight and records when execution is completed. Once the instruction at the head of the ROB finishes execution, it is removed from the ROB and retired by the front end, marking the end of its life cycle within the processor. This ensures that the retirement of instructions follows the original program order, regardless of the order in which they were executed. Reservation stations hold instructions and their operands until all dependencies are resolved, and the necessary execution units become available. The execution units consist of arithmetic logic units (ALUs), floating-point units (FPUs), and other specialized units that perform the actual computations required by the instructions.

## 2.3.3 Memory Subsystem

The memory subsystem is responsible for handling load and store instructions, and the ordering of memory accesses [Lipp, 2021; Schor, n.d.].

Memory instruction execution consists of three steps. The first step is the memory address generation, where addresses are computed either with absolute or segment-offset addressing mode. The second step is address translation, which does a virtual-to-physical translation of addresses computed in the first step, if virtual memory is used. Page tables are used to facilitate this translation. To speed-up future accesses to previously translated addresses, a translation-look aside buffer (TLB) is used to cache translation information. The final step is the actual memory access. In this step, data is first retrieved from the data cache and stored in a renamed register or the reorder buffer. A cache miss occurs if the data can not be located in the data cache, in which case, the data is requested from the main memory [Lipp, 2021].

The load buffer queues load instructions that can not complete when they are dispatched by the reservation station. It is also used to listen for stores performed in other cores against completed loads to ensure memory ordering. Meanwhile, the store buffer queues all store instructions before they are dispatched to the memory in order, that is, when they have retired [Lipp, 2021].

### 2.4 Branch Prediction

When a branch instruction is decoded by the front end of a processor, it often encounters a situation where it cannot determine the next instruction due to pending computation of the branch condition or target address. Instead of stalling the pipeline, the front end employs a technique known as branch prediction. It predicts the branch outcome according to the history of recently executed branches and proceeds to issue instructions accordingly.

By making correct predictions, this approach optimizes the execution flow by allowing younger instructions to proceed before the branch is resolved. However, in cases where the prediction is incorrect, the execution engine invalidates all younger instructions and requests the front end to resume execution from the correct branch outcome. These squashed instructions are ignored by the front end and are never committed, meaning their results are not stored to the architectural state. The same mechanism is applied when older instructions cause exceptions, such as division by zero or memory access violations, leading to the squashing of younger instructions.

Executed instructions that are eventually squashed are called *transient* instructions. While their results are not committed to the architectural state, any effects they have on the microarchitectural state of the processor are not reversed, which can potentially introduce vulnerabilities [Canella et al., 2019a; Kocher et al., 2019; Lipp et al., 2018].

## 2.5 Transient-Execution Attacks

While the results of such *transient* instructions are dropped, the microarchitectural components that were affected by the computation's side effects are not reversed. Attackers can exploit this by triggering the transient execution of instructions that access confidential data and transmitting it through

microarchitectural components such as caches. These attacks are known as transient-execution attacks and have been studied extensively [Canella et al., 2019a; Kocher et al., 2019; Lipp et al., 2018; Xiong and Szefer, 2021].

Spectre [Kocher et al., 2019] is one of the most prevalent transient-execution attacks and will be discussed further below, as it is pertinent to the subject matter of this thesis.

### 2.5.1 Spectre

Spectre-type attacks are a type of transient-execution attack that takes advantage of the way processors execute instructions after a control or data-flow misprediction. The attacker manipulates the branch-prediction unit, causing the processor to speculatively execute instructions that do not appear in the actual instruction stream. This is made possible by multiple prediction units that work together to determine the outcome and target of a branch. By poisoning one or more of these prediction units, Spectre-type attacks direct the processor's execution to "gadgets" which are code sequences that allow the attacker to uncover sensitive data by exploiting microarchitectural state changes.

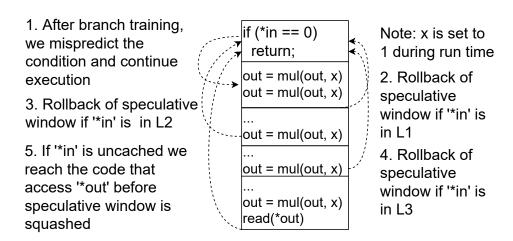

In this thesis, we are specifically looking at the Spectre-PHT, which takes advantage of a component in modern processors called the Pattern History Table (PHT), which is a component of the branch predictor that predicts the outcome of conditional branches [Canella et al., 2019a]. The PHT consists of saturating counter that records recent branch history [Evtyushkin et al., 2018. The attacker repeatedly trains the PHT with valid inputs to take a certain branch direction, such that targeted instructions are executed. After training, the attacker then executes the branch with an invalid input (e.g., out-of-bounds or restricted values) that would not cause the targeted instructions to execute according to the architectural specification. However, because the PHT is trained with valid inputs prior to this execution, it mispredicts the branch direction, causing processor speculatively executes the targeted instructions with the invalid input. The attacker can use this technique to perform architecturally-invalid reads, and forward the illicit data into a temporary buffer such as the cache for the purpose of retrieval into the architectural state later.

Figure 2.5: Simplified diagram of the Intel Skylake microarchitecture [Schor, n.d.].

# Chapter 3

# A Framework to Evaluate Cache Security

As we commence this thesis endeavor, in this chapter, our attention is directed towards the first cache side-channel attack defense approach, particularly safeguarding against contention-based attacks through secure cache designs. Various designs have been proposed to address contention-based cache attacks. For example, partitioned caches aim to prevent contention [Domnitser et al., 2012; Wang and Lee, 2007], while randomized caches create noise in the signal, obstructing attackers from analyzing the side-channel [Liu et al., 2016b; Qureshi, 2018; Qureshi, 2019; Tan et al., 2020; Werner et al., 2019]. Randomized caches generally prevent attackers from linking addresses to predicted cache line indexes, an essential element for the attack. Additionally, some suggestions aim to counter cross-core attacks by modifying the inclusion properties of shared cache levels in modern processors [Green et al., 2017; Kayaalp et al., 2017; Yan et al., 2019b].

As various proposals exist for defending against cache side-channel attacks, a technique to assess their security is essential. Several methods for evaluating secure caches have been proposed [Cock et al., 2014; Demme et al., 2012; Demme et al., 2013; Deng et al., 2019; Deng et al., 2020; Doychev et al., 2013; Ge et al., 2018; Ge et al., 2019; Ghasempouri et al., 2020; He and Lee, 2017; Köpf et al., 2012; Wang et al., 2019; Zhang and Lee, 2014; Zhang et al., 2013]. Nonetheless, these approaches have certain drawbacks as they either work only with basic cache models, focus on theoretical analysis, lack automation, or do not address the entire spectrum of cache attacks. Moreover, evaluating multiple metrics is crucial to bolster confidence in cache design security. Consequently, we explore the following question in this chapter:

How can we evaluate the security that cache designs offer against contention-based cache attacks?

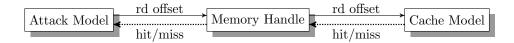

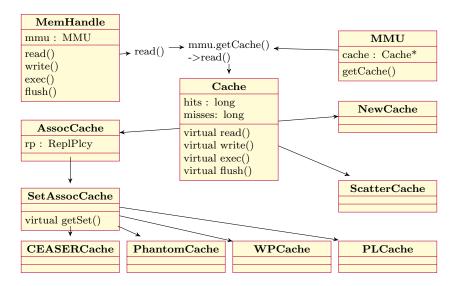

To address this question, we introduce in this chapter a software framework, called CacheFX, to assess cache security. CacheFX allows for the emulation

of various cache designs, victims, and attackers, and measures the resulting leakage using various metrics.

## 3.1 Background

In this section we present specific background on secure caches. Several proposed cache designs aim to mitigate contention-based attacks. Their mitigation strategies are either based on partitioning [Domnitser et al., 2012; Wang and Lee, 2007] or randomization [Liu et al., 2016b; Qureshi, 2018; Qureshi, 2019; Werner et al., 2019].