# Instituto Tecnológico y de Estudios Superiores de Occidente

Reconocimiento de validez oficial de estudios de nivel superior según acuerdo secretarial 15018, publicado en el Diario Oficial de la Federación del 29 de noviembre de 1976.

### Departamento de Electrónica, Sistemas e Informática Maestría en Diseño Electrónico

# Optimization of Electrical Validation and Debug time in Reference Clocks

ESTUDIO DE CASO que para obtener el GRADO de MAESTRO EN DISEÑO ELECTRÓNICO

Presenta: LUIS EDUARDO ARREDONDO SANDOVAL Director: DR. MANUEL SALIM MAZA

Tlaquepaque, Jalisco. Junio de 2023.

# Instituto Tecnológico y de Estudios Superiores de Occidente

Reconocimiento de validez oficial de estudios de nivel superior según acuerdo secretarial 15018, publicado en el Diario Oficial de la Federación del 29 de noviembre de 1976.

### Departamento de Electrónica, Sistemas e Informática Maestría en Diseño Electrónico

# Optimización de la validación eléctrica y reducción de tiempos de diagnóstico en relojes

ESTUDIO DE CASO que para obtener el GRADO de MAESTRO EN DISEÑO ELECTRÓNICO

# Presenta: LUIS EDUARDO ARREDONDO SANDOVAL Tutor: DR. MANUEL SALIM MAZA

Tlaquepaque, Jalisco. Junio de 2023.

#### ACKNOWLEDGEMENTS

The author would like to express gratitude to the ITESO school for their tuition discount and for facilitating class progress during the COVID pandemic, to INTEL company, including my manager for approving financial support to cover part of the cost, to the professors for their dedication and patience, to my director, Dr. Manuel Salim Maza for sharing his knowledge and guiding me in the development of this work.

#### AGRADECIMIENTOS

El autor desea dar las gracias a la escuela ITESO por el descuento en la colegiatura y por facilitar el progreso de las clases durante la pandemia de COVID, a la empresa INTEL y a mi mánager por aprobar el apoyo económico para cubrir una parte del costo, a los profesores por su dedicación y paciencia, a mi director, el Dr. Manuel Salim Maza por compartir su conocimiento y guiarme en el desarrollo de este trabajo.

#### DEDICATION

I dedicate this work to my wife María de Jesús Ávila Rodriguez, for all her support, for taking care of the children while I concentrated and for feeding me while I was taking classes or doing homework; to my eldest son Erick Eduardo for encouraging me by telling me that this was possible; to my younger sons Marco Leonardo and Luis Angel for waiting long hours for me to play with them and letting me study; to my mother María de los Ángeles, my father Ramiro Arredondo and my siblings for their moral support.

#### DEDICATORIA

Dedico este trabajo a mi esposa María de Jesús Ávila Rodriguez, por todo su apoyo, por cuidar a los niños, por dejarme concentrar y por alimentarme mientras tomaba clases o hacia tarea; a mi hijo mayor Erick Eduardo por darme ánimos diciéndome que si se podía; a mis hijos más pequeños Marco Leonardo y Luis Angel por esperarme largas horas para jugar con ellos y dejarme estudiar; a mi madre Maria de los Ángeles, a mi padre Ramiro Arredondo y a mis hermanos por su apoyo moral.

#### ABSTRACT

The Electrical Validation and Debugging, at the system level, of the Reference Clock signals, requires a lot of Signal Integrity and High-Frequency knowledge and skills. This work intends to improve the actual validation methodology and to increase technical knowledge, so our validation team could find defects and root causes sooner. We are analyzing, modeling, and simulating the top four debug cases seen during past validation cycles, by designing and using clock buffers with controlled impedance, as well as transmission lines. The result obtained is that, besides the great knowledge and skills that have been created, we're also observing a very good correlation between simulation and real product behavior.

#### RESUMEN

La Validación Eléctrica y depuración, a nivel de sistema, de las señales de reloj de referencia, requiere muchos conocimientos y habilidades de Integridad de Señal y Alta Frecuencia. La intención de este trabajo es mejorar la metodología de validación actual e incrementar el conocimiento técnico, de esta manera nuestro equipo de validación podrá encontrar defectos y causas raíz rápidamente. Estaremos analizando, modelando y simulando los principales cuatro casos de depuración vistos en los ciclos de validación anteriores, diseñando y utilizando búferes de reloj con impedancia controlada, así como líneas de transmisión. El resultado obtenido es que, aparte de haber creado habilidades y conocimiento, también estamos observando muy buena correlación entre la simulación y el comportamiento real de nuestros productos.

# TABLE OF CONTENTS

| ACKN   | OWLEDGEMENTS                                            |   |

|--------|---------------------------------------------------------|---|

| AGRA   | DECIMIENTOS                                             | 5 |

| DEDIC  | CATION                                                  | 6 |

| DEDIC  | CATORIA                                                 | 7 |

| ABSTI  | RACT                                                    |   |

| RESU   | MEN                                                     | 9 |

| TABL   | E OF CONTENTS                                           |   |

| LIST ( | OF FIGURES                                              |   |

| LIST ( | OF TABLES                                               |   |

| LIST ( | OF ACRONYMS AND ABBREVIATIONS                           |   |

| 1. IN  | NTRODUCTION                                             |   |

| 1.1.   | BACKGROUND                                              |   |

| 1.2.   | JUSTIFICATION                                           |   |

| 1.3.   | The Problem                                             | - |

| 1.4.   | Hypothesis                                              |   |

| 1.5.   | OBJECTIVES                                              |   |

|        | 1.5.1. General Objective:                               |   |

|        | 1.5.2. Specific Objectives:                             |   |

| 1.6.   | CONTRIBUTION OF SCIENTIFIC AND TECHNOLOGICAL INNOVATION |   |

| 2. T   | HE STATE OF THE ART                                     |   |

| 2.1.   | THE ELECTRICAL VALIDATION                               |   |

| 2.2.   | THE DEBUG                                               |   |

| 3. T   | HEORETICAL FRAMEWORK AND HISTORICAL DEBUG CASES         |   |

| 3.1.   | THE ELECTRICAL VALIDATION OF CLOCKS AT THE SYSTEM LEVEL |   |

| 3.2.   | DEBUGGING CLOCK DEFECTS                                 |   |

| 3.3.   | IMPACT ANALYSIS                                         |   |

| 3.4.   | ELECTRICAL PARAMETERS REVIEW                            |   |

| 4. C   | LOCK BUFFER ARCHITECTURE                                |   |

| 4.1.   | The Pmos and Nmos models                                |   |

|        | 4.1.1. Configuring ADS to use the Pmos/Nmos model       |   |

| 4.2.   | THE INVERTER                                            |   |

| 4.3.   | NMOS LEG TUNING                                         |   |

| 4.4.   | Pmos Leg Tuning                                         |   |

| 4.5.   | PROGRAMMABLE IMPEDANCE DRIVER                           |   |

| 4.6.   | NMOS RCOMP FOR A $50\Omega$ Driver                      |   |

| 4.7.   | Pmos RComp for a 50 $\Omega$ Driver                     |   |

| 4.8.      | Nmos and Pmos Rcomp for a $33\Omega$ Driver                                                                   |    |

|-----------|---------------------------------------------------------------------------------------------------------------|----|

| 4.9.      | Single-Ended Non-Ideal 50 $\Omega$ Transmission Line                                                          |    |

| 4.10.     | Differential Non-Ideal 100 $\Omega$ Transmission Line                                                         |    |

| 4.11.     | Single-Ended Buffer                                                                                           |    |

| 4.12.     | COMPLEMENTARY BUFFER                                                                                          |    |

| 5. CA     | ASE STUDIES                                                                                                   | 60 |

|           |                                                                                                               |    |

| 5.1.      | THE "UNDERSHOOT" CASE STUDY                                                                                   |    |

|           | 5.1.1. Simulation Scenario # 1                                                                                |    |

| -         | 5.1.2. Simulation Scenario # 2                                                                                |    |

| -         | 5.1.3. Simulation Scenario # 3                                                                                |    |

| -         | 5.1.4. Conclusion                                                                                             |    |

| 5.2.      |                                                                                                               |    |

| -         | 5.2.1. Noise Frequency Effect                                                                                 |    |

|           | 5.2.2. System Variation Effect                                                                                |    |

|           | 5.2.3. Conclusion                                                                                             |    |

| 5.3.      |                                                                                                               |    |

| -         | 5.3.1. Parts per Million                                                                                      |    |

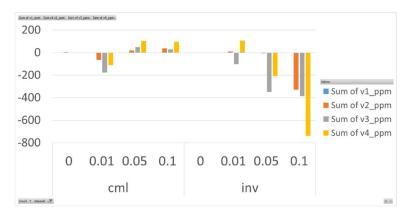

|           | 5.3.2. Colpitts LC Oscillator, Frequency Tuning                                                               |    |

|           | <ul><li>5.3.3. Ppm and Jitter, Inverters vs. CML, noise in supply voltage</li><li>5.3.4. Conclusion</li></ul> |    |

| 5.4.      |                                                                                                               |    |

| • • • • • | 5.4.1. Slew Rate                                                                                              |    |

| -         | 5.4.1. Siew Rate                                                                                              |    |

| -         | 5.4.3. Conclusion                                                                                             |    |

|           |                                                                                                               |    |

| 6. CO     | DNCLUSIONS                                                                                                    |    |

| 6.1.      | CONCLUSIONS                                                                                                   |    |

| 6.2.      | FUTURE WORK                                                                                                   |    |

| BIBLIO    | )GRAPHY                                                                                                       |    |

|           |                                                                                                               |    |

| APPEN     | IDIX A. MEASUREMENTS IN LTSPICE                                                                               |    |

| A.1       | 1 Measurement in Colpitts circuit at 32.768kHz                                                                |    |

| A.2       | 2 Measurement in Colpitts circuit at 100MHz                                                                   |    |

| A.3       | 3 Measurement in cascaded Inverters circuit                                                                   |    |

| A.4       | 4 Measurement in cascaded CMLs circuit                                                                        |    |

| APPEN     | DIX B. PHASE LOCK LOOP (PLL)                                                                                  |    |

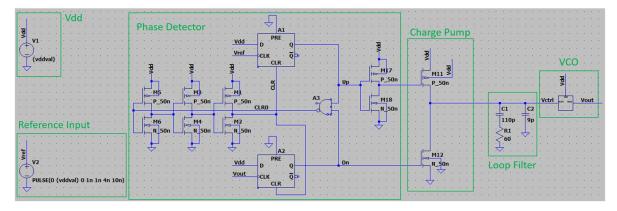

| B.1       | I Supply Voltage and Reference Input                                                                          |    |

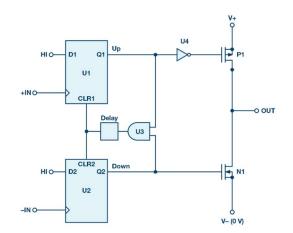

|           | 2 Phase Detector and Charge Pump                                                                              |    |

|           | 3 Loop Filter                                                                                                 |    |

|           | 4 Voltage Controlled Oscillator (VCO)                                                                         |    |

|           | 5 Measurements                                                                                                |    |

|           | 6 Size of the transistors                                                                                     |    |

|           |                                                                                                               |    |

|           | 7 Spice directives for the measurements                                                                       |    |

|           | 8 Spread Spectrum Clock (SSC)                                                                                 |    |

| B.9       | 9 Conclusion                                                                                                  |    |

| APPENDIX C. WCS, TYP, BCS, AND MONTE-CARLO ANALYSIS |     |

|-----------------------------------------------------|-----|

| C.1 Wcs, Typ, Bcs Simulations                       |     |

| C.2 Monte Carlo Simulations                         | 102 |

| C.3 Conclusion                                      | 105 |

## LIST OF FIGURES

| FIGURE 1: 100MHz CLOCK SIGNAL. A) FEW CLOCK-CYCLES. B) MORE THAN 100,000 CLOCK CYCLES       | . 23 |

|---------------------------------------------------------------------------------------------|------|

| FIGURE 2: RESULTS REPORT. A) CONFIG SCREEN. B) PHASE JITTER. C) PEAK TO PEAK AND RMS JITTER | . 23 |

| FIGURE 3: MEASUREMENTS PERFORMED WITH DPOJET FROM TEKTRONIX                                 | . 24 |

| FIGURE 4: OVERSHOOT AND UNDERSHOOT                                                          | . 29 |

| FIGURE 5: JITTER                                                                            | . 30 |

| FIGURE 6: FREQUENCY PPM                                                                     | . 30 |

| FIGURE 7: SLEW RATE                                                                         |      |

| FIGURE 8: BASIC PLL CONFIGURATION                                                           | . 31 |

| FIGURE 9: CROSS TALK                                                                        | . 31 |

| FIGURE 10: PHASE NOISE                                                                      | . 31 |

| FIGURE 11: SPREAD SPECTRUM CLOCK PROFILE                                                    | . 32 |

| FIGURE 12: POWER MANAGEMENT STATES                                                          |      |

| FIGURE 13: DUTY CYCLE.                                                                      | . 32 |

| FIGURE 14: NMOS AND PMOS MODELS                                                             | . 34 |

| FIGURE 15: CONFIGURATION OF MODEL IN ADS.                                                   | -    |

| FIGURE 16: CMOS INVERTER                                                                    |      |

| FIGURE 17: PMOS TO NMOS COMPENSATION.                                                       |      |

| FIGURE 18: IN VS. OUT PLOT, SWEEPING "IN" VOLTAGE                                           | . 36 |

| FIGURE 19: IN VS. OUT, APPLYING A SQUARE SIGNAL.                                            |      |

| FIGURE 20: NMOS LEG                                                                         | . 37 |

| FIGURE 21: NMOS WIDTH ADJUSTMENT CIRCUIT.                                                   | . 38 |

| FIGURE 22: SELECTED NMOS WIDTH.                                                             |      |

| FIGURE 23: PMOS LEG.                                                                        | . 40 |

| FIGURE 24: PMOS WIDTH ADJUSTMENT CIRCUIT                                                    |      |

| FIGURE 25: SELECTED PMOS WIDTH.                                                             |      |

| FIGURE 26: NMOS LEG. A) CIRCUIT. B) SYMBOL                                                  | . 43 |

| FIGURE 27: NMOS RCOMP VERIFICATION CIRCUIT.                                                 |      |

| FIGURE 28: NMOS RCOMP CIRCUIT SIMULATION RESULT.                                            | . 45 |

| FIGURE 29: PMOS LEG. A) CIRCUIT. B) SYMBOL                                                  | . 45 |

| FIGURE 30: PMOS RCOMP VERIFICATION CIRCUIT.                                                 |      |

| FIGURE 31: PMOS RCOMP CIRCUIT SIMULATION RESULT.                                            |      |

| Figure 32: Nmos RCOMP simulation for a $33\Omega$ driver                                    | . 47 |

| FIGURE 33: PMOS RCOMP SIMULATION FOR A $33\Omega$ driver                                    | . 48 |

| FIGURE 34: JLCPCB TRACK STRUCTURE FOR SINGLE-ENDED TL                                       | . 49 |

| FIGURE 35: JLC7628 PCB STACK-UP.                                                            |      |

| FIGURE 36: LINE CALCULATOR, IN ADS.                                                         |      |

| FIGURE 37: LINECALC IN ADS, 50 $\Omega$ Single-Ended TL                                     | . 50 |

| FIGURE 38: JLCPCB TRACK STRUCTURE FOR DIFFERENTIAL TL.                                      | . 51 |

| Figure 39: LineCalc in ADS, $100\Omega$ Differential TL.                                    |      |

| FIGURE 40: SINGLE-ENDED BUFFER. A) IMPEDANCE CONTROL. B) SINGLE-ENDED BUFFER.               |      |

| FIGURE 41: MLIN TRANSMISSION LINE.                                                          |      |

| FIGURE 42: 10PF CAPACITOR LOAD.                                                             |      |

| FIGURE 43: SMALLEST INVERTER, SINUSOIDAL INSTEAD OF SQUARE.                                 | . 54 |

| FIGURE 44: INVERTER FOR BUFFER, THE ADJUSTMENT CIRCUIT.                  | 55  |

|--------------------------------------------------------------------------|-----|

| FIGURE 45: INVERTER ADJUSTED, THE SQUARE SIGNAL AT FAR END.              | 56  |

| FIGURE 46: INVERTER. A) CIRCUIT. B) SYMBOL.                              | 56  |

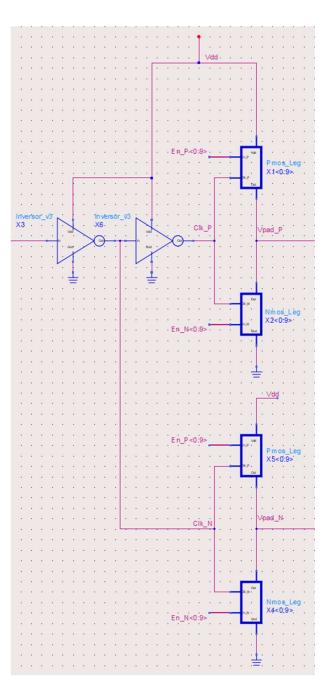

| FIGURE 47: COMPLEMENTARY BUFFER                                          | 57  |

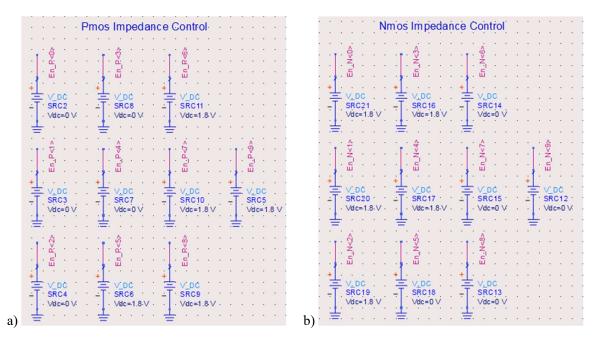

| Figure 48: Impedance Control for 50 $\Omega$ . A) Pmos. B) Nmos          | 58  |

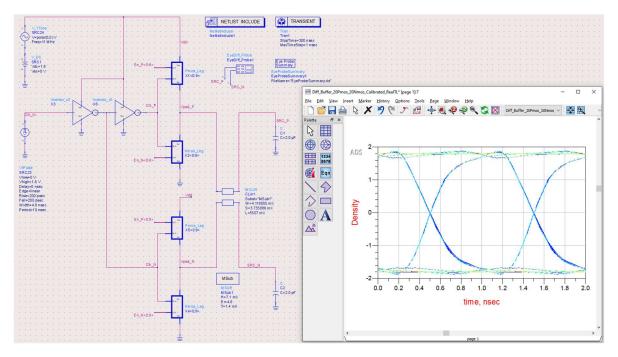

| Figure 49: Complementary Buffer driving a $100\Omega$ Differential TL.   | 59  |

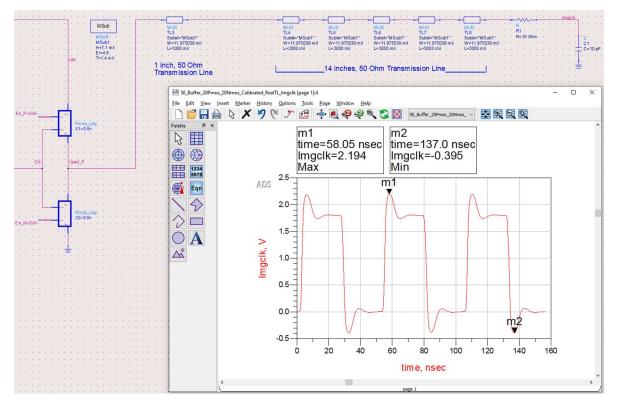

| FIGURE 50: UNDERSHOOT, SCENARIO 1                                        | 62  |

| FIGURE 51: UNDERSHOOT, SCENARIO 2                                        | 63  |

| FIGURE 52: UNDERSHOOT, SCENARIO 3                                        | 64  |

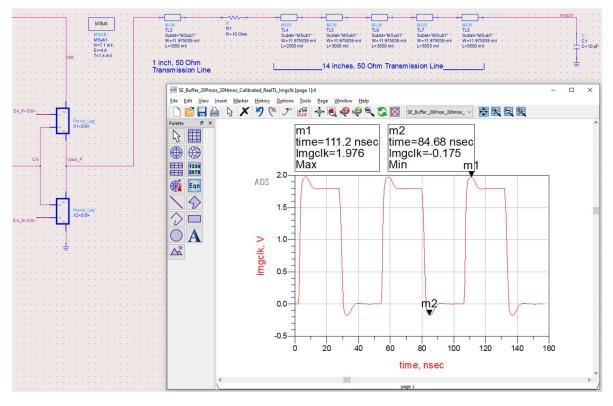

| FIGURE 53: POWER SUPPLY PLUS NOISE.                                      |     |

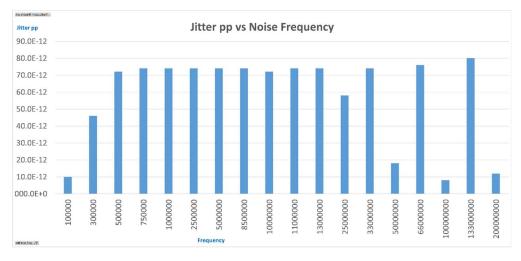

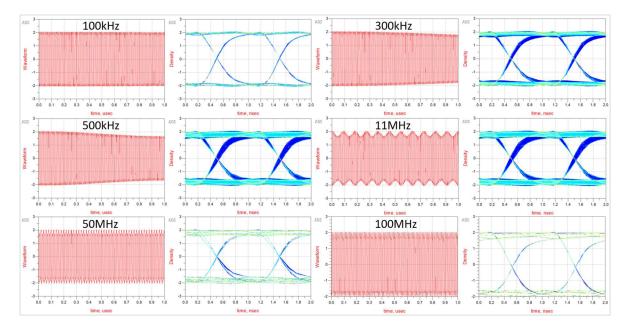

| FIGURE 54: JITTER PP VS. NOISE FREQUENCY.                                |     |

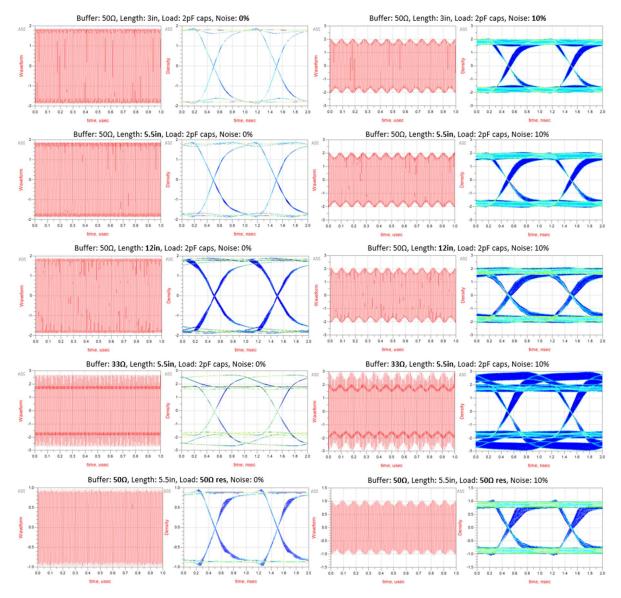

| FIGURE 55: WAVEFORM AND DENSITY, FREQUENCY EFFECT.                       | 67  |

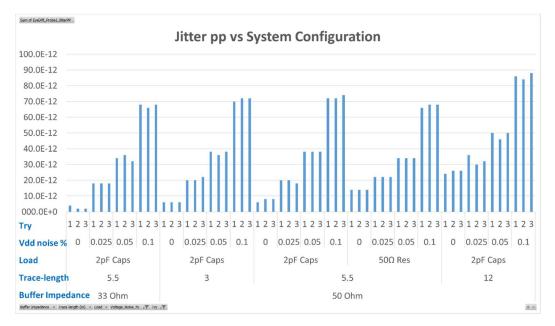

| FIGURE 56: JITTER PP VS. SYSTEM CONFIGURATION.                           | 67  |

| FIGURE 57: WAVEFORM AND DENSITY, BUFFER, LENGTH, LOAD, AND NOISE EFFECT. | 68  |

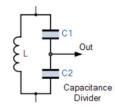

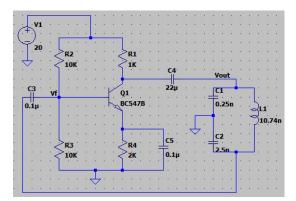

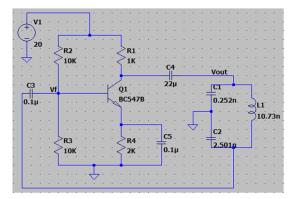

| FIGURE 58: COLPITTS OSCILLATOR TANK CIRCUIT                              | 70  |

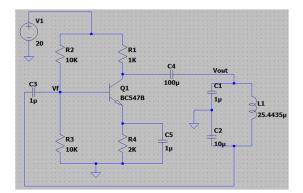

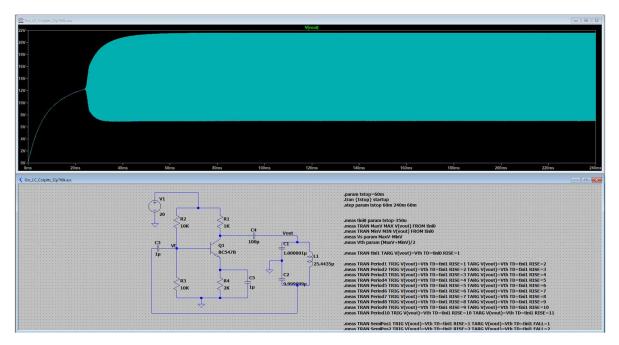

| FIGURE 59: OSCILLATOR LC COLPITTS AT 32.768KHz.                          | 70  |

| FIGURE 60: OSCILLATOR LC COLPITTS AT 100MHz                              | 71  |

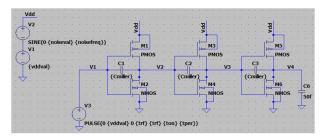

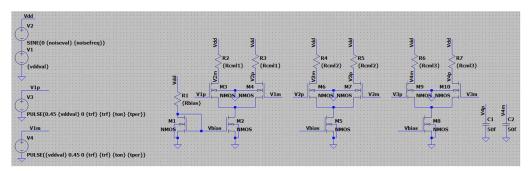

| FIGURE 61: THREE CASCADED INVERTERS                                      | 72  |

| FIGURE 62: THREE CASCADED CML                                            | 73  |

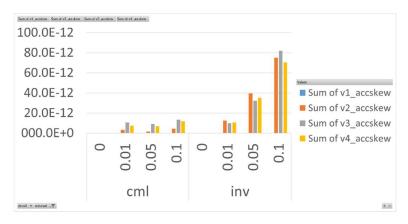

| FIGURE 63: PPM RESULTS, CML VS. INVERTER.                                |     |

| FIGURE 64: JITTER RESULTS, CML VS. INVERTER.                             | 74  |

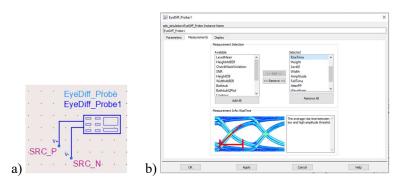

| FIGURE 65: EYE DIFF PROBE SETUP. A) EYE DIFF PROBE. B) CONFIG SCREEN.    | 76  |

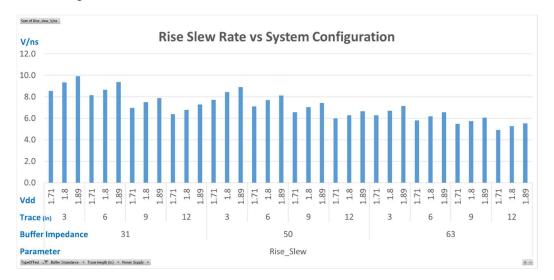

| FIGURE 66: RISE SLEW RATE VS. SYSTEM CONFIGURATION.                      | 76  |

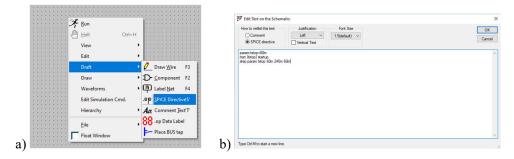

| FIGURE 67: SPICE DIRECTIVES. A) MENU. B) EDITOR.                         | 82  |

| FIGURE 68: COLPITTS FOR 32.768KHZ SIMULATION                             | 82  |

| FIGURE 69: OSCILLATOR LC COLPITTS AT 100MHz                              | 84  |

| FIGURE 70: THREE CASCADED INVERTERS                                      | 85  |

| FIGURE 71: THREE CASCADED CML                                            | 87  |

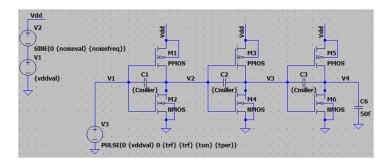

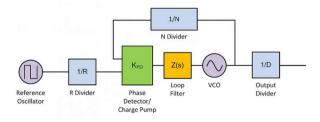

| FIGURE 72: BASIC PLL CONFIGURATION                                       | 91  |

| FIGURE 73: PLL CIRCUIT, IMPLEMENTED IN LTSPICE                           | 91  |

| FIGURE 74: PHASE FREQUENCY DETECTOR AND CHARGE PUMP                      | 92  |

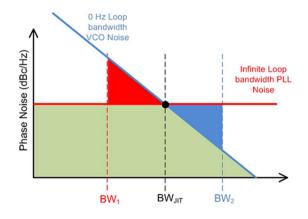

| FIGURE 75: PLL BANDWIDTH.                                                | 93  |

| FIGURE 76: VOLTAGE CONTROLLED OSCILLATOR.                                | 94  |

| FIGURE 77: SPREAD SPECTRUM ADDITION TO PLL.                              | 97  |

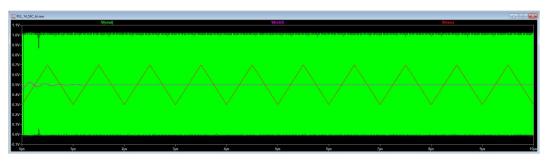

| FIGURE 78: TRIANGULAR SSC SIGNAL.                                        | 97  |

| FIGURE 79: VREF VS. VOUT WITH SSC. A) FFT ANALYSIS. B) ZOOM AT 100MHz.   | 98  |

| FIGURE 80: VREF VS. VOUT WITHOUT SSC. A) FFT ANALYSIS. B) ZOOM AT 100MHz | 98  |

| FIGURE 81: THREE CASCADED CML                                            | 99  |

| FIGURE 82: MODELS TWEAKED. TOP LEFT: WCS. TOP RIGHT: TYP. BOTTOM: BCS    | 100 |

| FIGURE 83: INCLUSION OF THE MODEL. A) WCS. B) TYP. C) BCS.               |     |

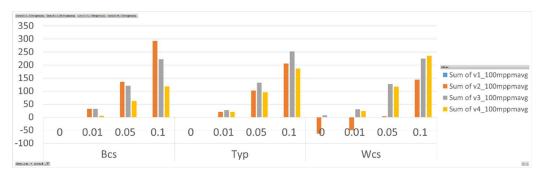

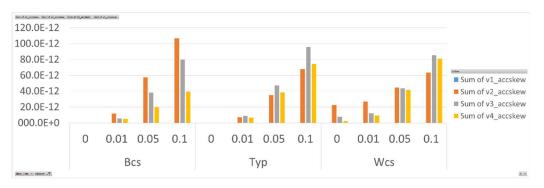

| FIGURE 84: BCS, TYP, WCS, PPM RESULTS                                    |     |

| FIGURE 85: BCS, TYP, WCS, JITTER RESULTS.                                | 101 |

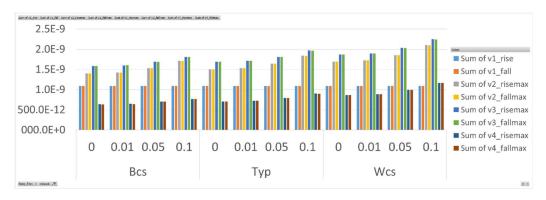

| FIGURE 86: BCS, TYP, WCS, RISE TIME, FALL TIME, MAX RESULTS.             | 101 |

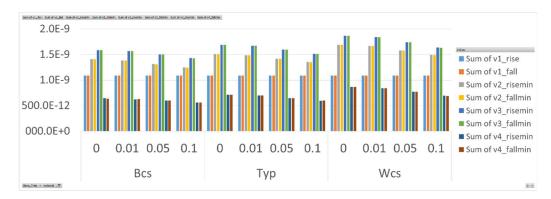

| FIGURE 87: BCS, TYP, WCS, RISE TIME, FALL TIME, MIN RESULTS.             |     |

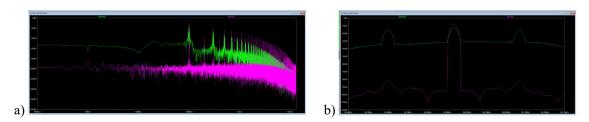

| FIGURE 88: MONTE CARLO CONFIGURATION OF THE NMOS. A) M3. B) M7. C) M9.   | 102 |

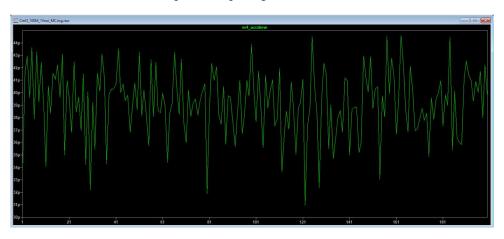

| FIGURE 89: MONTE CARLO RESULTS, PART 1 | 103 |

|----------------------------------------|-----|

| FIGURE 90: MONTE CARLO RESULTS, PART 2 | 103 |

| FIGURE 91: MONTE CARLO RESULTS, PART 3 | 103 |

| FIGURE 92: MONTE CARLO RESULTS, PART 4 | 104 |

| FIGURE 93: MONTE CARLO RESULTS, PART 5 | 104 |

## LIST OF TABLES

| TABLE 1: RESULTS REPORT, GENERATED WITH THE SKYWORKS TOOL.                  | 23 |

|-----------------------------------------------------------------------------|----|

| Table 2: Electrical parameter failed vs. Impact.                            | 28 |

| Table 3: Pmos Width adjustment of the Inverter.                             | 36 |

| TABLE 4: NMOS WIDTH ADJUSTMENT                                              |    |

| TABLE 5: PMOS WIDTH ADJUSTMENT                                              | 41 |

| TABLE 6: L, W, AND R, FOR 50 $\Omega$ and 250 $\Omega$ Nmos Legs            | 42 |

| TABLE 7: L, W, AND R, FOR 50 $\Omega$ and 250 $\Omega$ Pmos Legs            | 45 |

| TABLE 8: TUNING OF THE INVERTER FOR THE BUFFER.                             |    |

| TABLE 9: COLPITTS 32P768KHz, SIMULATING 240MS                               | 71 |

| TABLE 10: COLPITTS 100MHz, SIMULATING 400US                                 | 72 |

| TABLE 11: PARAMETER CHANGE VS. SLEW RATE                                    | 77 |

| TABLE 12: ELMORE'S DELAY                                                    |    |

| TABLE 13: DESIGN GOAL VS. BANDWIDTH.                                        |    |

| TABLE 14: PLL LOOP FILER ADJUSTMENT, C1 SWEEP.       9                      | 94 |

| TABLE 15: PLL LOOP FILTER ADJUSTMENT, C2 SWEEP                              | 94 |

| TABLE 16: PLL LOOP FILTER ADJUSTMENT, R1 SWEEP                              | 95 |

| TABLE 17: MONTE CARLO, JITTER AT OUTPUT V4, AN EXAMPLE OF RESULTS.       10 | 04 |

### LIST OF ACRONYMS AND ABBREVIATIONS

| ADS            | Advanced Design System (simulation tool from Keysight)       |  |  |

|----------------|--------------------------------------------------------------|--|--|

| Client segment | The market segment for Laptop and Desktop computers          |  |  |

| CML            | Current Mode Logic                                           |  |  |

| CMOS           | Complementary Metal Oxide Semiconductor                      |  |  |

| DC             | Direct Current                                               |  |  |

| Debug          | Process of identifying and correcting errors or issues in    |  |  |

|                | electronic circuits                                          |  |  |

| Device segment | The market segment for mobile devices like Tablets and       |  |  |

| -              | Cellphones                                                   |  |  |

| EMI            | Electromagnetic Interference                                 |  |  |

| FR4            | Flame Retardant level 4                                      |  |  |

| GS/s           | Giga Samples per second                                      |  |  |

| IC             | Integrated Circuit                                           |  |  |

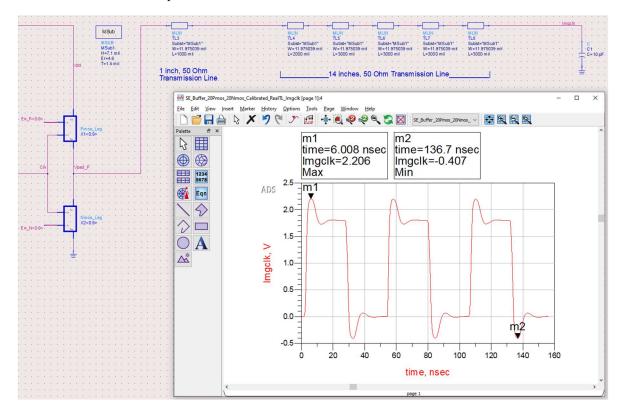

| Imgelk         | Image Clock, for camera circuit                              |  |  |

| ITESO          | Instituto Tecnológico y de Estudios Superiores de Occidente  |  |  |

|                | Western Institute of Technology and Higher Education         |  |  |

| Nmos           | N-channel Metal Oxide Semiconductor                          |  |  |

| PCB            | Printed Circuit Board                                        |  |  |

| PCIe           | Peripheral Component Interconnect Express                    |  |  |

| PLL            | Phase Lock Loop                                              |  |  |

| Pmos           | P-channel Metal Oxide Semiconductor                          |  |  |

| Post-silicon   | Silicon physically built                                     |  |  |

| PPM            | Parts per Million                                            |  |  |

| Pre-silicon    | Before building silicon                                      |  |  |

| PVT            | Process, Voltage, Temperature                                |  |  |

| Rcomp          | Compensating Resistor                                        |  |  |

| RVP            | Reference Validation Platform                                |  |  |

| Rx             | Receiver                                                     |  |  |

| SCLK           | System Clock                                                 |  |  |

| Server segment | The market segment for server systems                        |  |  |

| SoC            | System on Chip                                               |  |  |

| SR             | Slew Rate                                                    |  |  |

| SSC            | Spread Spectrum Clock                                        |  |  |

| Stepping       | The version or release of the IC                             |  |  |

| Test Plan      | Plan or list of electrical tests for validation              |  |  |

| Tx             | Transmitter                                                  |  |  |

| VCO            | Voltage Controlled Oscillator                                |  |  |

| Vdd            | Drain Voltage, a typical name for a circuit's supply voltage |  |  |

| Ζ              | Impedance                                                    |  |  |

# 1. INTRODUCTION

**Summary:** In this chapter, we will discuss the electrical validation of clock signals at the system level. We will explain the problem, justify it, and present hypotheses. We will also define general and specific objectives to achieve in this work.

#### 1.1. Background

System Clock (SCLK) is the name of a circuit, which is inside of an Integrated Circuit (IC), that generates and distributes clock signals to several components, inside and outside of the IC, so they can perform their function. The clock signals in a system are, comparably, what the heart is for the human body, these are pulses that set the rhythm at which diverse circuits get synchronized and work in harmony.

The SCLK circuit, besides clocking internal circuitries within the IC, provides clock signals to several components in a system, at the printed circuit board (PCB) level, also known as a "motherboard" or platform, with multiple ICs, and connectors for external electronic cards. At the system level, the SCLK must manage several frequencies, trace lengths, and market segments, such as device, client, or server segments. More details are in section 3.1.

Similarly, to any commercialized product, the SCLK circuit must pass through the electrical validation process before mass production. The validation process, at a high level, consists of several phases, such as readiness or planning (during pre-silicon), test plan execution (during post-silicon), repetitions, and approval.

The execution phase includes debugging in case of unsatisfactory results. The repetitions occur when improvements are done to the prototype, and approval is for mass production when all technical requirements are met.

During the test plan execution, it is expected that the SCLK works within electrical specifications when it is subjected to diverse stress types, for example, supply voltage and temperature variations. Also, we must test ICs that resulted to be faster or slower than the average speed of the produced units, this is called process corners. By testing at several PVT combinations (process, voltage, temperature), we can discover design problems, sooner, during the validation [1].

#### 1.2. Justification

It is very important to uncover problems in the SCLK circuit in the early phases of the design or validation and to look for the root cause. If defects are found in late phases, it is very expensive to correct them, and customers would be impacted. One example of the cost of not discovering a problem in the design, prototype, or validation phases, is the so-called "Pentium flaw", which cost \$475 million to the company [2].

The phases of the product design process are:

The idea – although building something "new" can be creative, many of the best ideas are the result of working on a product that already exists.

Investigation – We need to test the idea first, before producing the product, this way we can guarantee that we are creating a product that people will buy, for example, by making online surveys and asking for opinions in forums, among others.

Planning – to draw an initial draft of the product, as detailed as possible, with labels explaining its characteristics and functions, to make it clear what components or materials will be needed to create the product.

Prototypes – the objective is to create a product, that will be used as a sample for mass production. It is unlikely to occur, to have a finished product on the first try, it's more probable to experiment with several versions of the product and make improvements until we get what we're looking for.

Validation – every prototype must pass through a validation phase, this is, to put the product to the test, and discover its functionality and specifications meeting level, as well as to uncover defects that must be corrected and implemented in the next prototype version.

Supplies – When creating the prototype, we need also to create the supply chain, with suppliers, resources, and necessary activities to create the product, and put it in our customer's hands, storage, and shipment.

Look for the lower cost – when completing the previous phases, we'll have a better idea of the cost of producing the product, this way we can determine a price and margin [3].

#### 1.3. The Problem

The electrical validation at the system level, of the SCLK's clocks, requires a lot of Signal Integrity knowledge [4], as well as to perform measurements in several PVT combinations, topology, clock types, etc. This makes the validation cycle so long that it often fits within the validation window, leaving no time for debugging.

The validation timeframe goes from Power-On, which is when the product is just built and ready to get powered, to the Tape-In, which occurs when all needed changes have been applied to create the next stepping of the product [5]. This time usually takes from 7 to 13 weeks, leaving very little or null time to analyze defects. Similarly, being a very complex branch, when there are problems and debugging needs to be done, it takes a lot of time due to the complexity of the circuit and the implementation at the system level.

#### 1.4. Hypothesis

We may currently be running too many tests, such as many PVT combinations that do not provide new information about the health of the SCLK, that is, validating more than needed. It's also probable that the specific tests that we are running, not all are the best to find defects in the clock's circuits.

It is also believed that the lack of certain technical knowledge, about the SCLK and the implementation at the system level, is preventing us from finding the root causes of problems in a more efficient manner. Such technical knowledge could be, electrical parameters or physical phenomenon comprehension, about Jitter, Phase Noise, Slew Rate, Reflections, Impedance mismatches, etc.

We believe that, by developing technical knowledge and implementing some root cause analysis techniques, we could execute a more efficient validation and debugging.

#### 1.5. Objectives

#### 1.5.1. General Objective:

To improve the actual validation methodology and to increase the technical knowledge about SCLK architecture, so our team could easily find defects and their root cause within the validation time frame.

#### 1.5.2. Specific Objectives:

To reduce the clock's electrical validation time from 20% to 30% of the actual time. This is, from 10 weeks down to 7 or 8 weeks, so we can dedicate 2 to 3 weeks to look for the root cause of the defects found, before the tape-in of the next stepping. We're also trying to reduce the debug time by 20% to 30% of the current time.

#### 1.6. Contribution of Scientific and Technological Innovation

This work is a contribution, aiming to optimize the actual clocks electrical validation methodology, as well as, to generate technical knowledge, which helps to debug and root cause the defects more efficiently.

# 2. THE STATE OF THE ART

**Summary:** This chapter shows a summary of the current electrical validation techniques, and some electrical parameters, that once understood, debugging tends to be easier.

#### 2.1. The Electrical Validation

Currently, there exist several tools to calculate electrical parameters, one example is the "PCIe Clock Jitter Tool" from Skyworks company [6], which analyzes reference clock signals for PCIe and provides a report with an extensive variety of electrical parameters and their values or measurements. The clock signal to be entered in the tool must be taken with an Oscilloscope, able to capture 100,000 or more clock cycles, with a minimum sample rate of 25 GS/s. Figure 1 shows a 100MHz reference clock signal for PCIe.

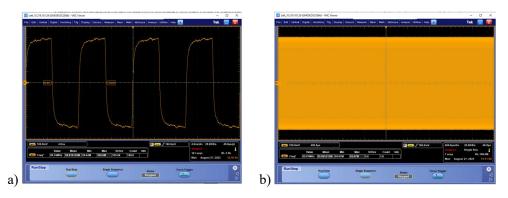

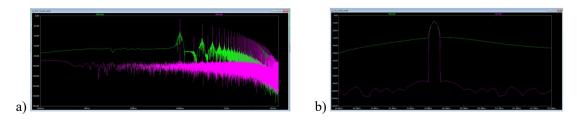

Figure 1: 100MHz Clock Signal. a) Few clock-cycles. b) More than 100,000 clock cycles.

The signal is saved and introduced into the Skyworks tool, which will perform an analysis and generate a report with the measurements, Table 1 shows an example.

| Class | Data Rate | Architecture      | Specs           | Measur    | ed Jitter (1) | Spec Limit | Compliance<br>Summary |

|-------|-----------|-------------------|-----------------|-----------|---------------|------------|-----------------------|

| GEN1  | 2.5 Gb/s  | Common Clock      | 1.1 , 2.1 , 3.1 | 33.15 ps  | peak-to-peak  | 86 ps      | AII PASS              |

| GEN2  | 5 Gb/s    | Common Clock      | 1.1.2.1.3.1     | 1.18 ps   | HFRMS         | 3.1 ps     | AII PASS              |

| GENZ  | 5 GD/S    | Gors Common Clock | 1.1, 2.1, 3.1   | 1.14 ps   | LF RMS        | 3 ps       |                       |

| GEN3  | 8 Gb/s    | Common Clock      | 3.1,4.0         | 343.97 fs | RMS           | 1 ps       | AI PASS               |

| GEN4  | 16 Gb/s   | Common Clock      | 4.0             | 329.75 fs | RMS           | 500 fs     | AII PASS              |

| GEN5  | 32 Gb/s   | Common Clock      | 5.0             | 120.14 fs | RMS           | 150 fs     | AII PASS              |

| GEN6  | 64 Gb/s   | Common Clock      | 6.0             | 72.66 fs  | RMS           | 100 fs     | AII PASS              |

Table 1: Results report, generated with the Skyworks tool.

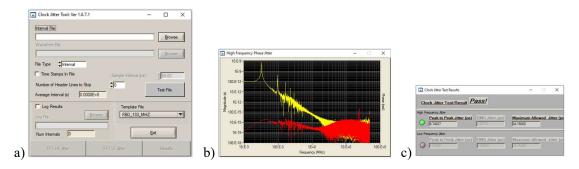

Another tool is the "Clock Jitter Tool" from Intel [7], which analyzes the clock signal and provides the rms jitter value, along with a "pass" or "fail" statement. Figure 2 shows an example of the analysis generated by this tool.

Figure 2: Results report. a) Config screen. b) Phase Jitter. c) Peak to Peak and RMS Jitter.

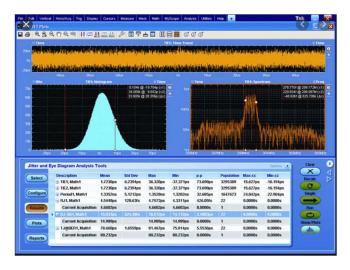

Another tool is the Dpojet software from Tektronix [8], which can perform several types of analyses of the clock signal, Figure 3 is an example of the measurements obtained with this tool.

Figure 3: Measurements performed with Dpojet from Tektronix.

#### 2.2. The Debug

Debug is the ability to root cause problems, in this case, on clocks at the system level. It is essential to understand most of the physical phenomena that occur in electronic systems, such as Jitter, Phase Noise, Slew Rate, Reflections, Impedance Mismatch, etc. There exists a lot of bibliographies that explain these phenomena, many times these are complicated themes, and it is difficult to associate them with the system.

In this work, it is planned to cover multiple electrical parameters, and how they are affected by the different characteristics of the system, such as topologies, trace lengths, terminations, etc. With this knowledge, the validator can do it reversed way, to attack a problem by knowing what could be affecting that specific physical phenomenon, then make some experiments or simulations, and find the root cause sooner.

There are many methodologies to root cause problems, for example, the 5 whys, which consists of making consecutive "why" questions on why something is occurring, then asking another "why" to the answer, and continuing up to the root cause. Two iterations would be enough, or typically 5, but more could be needed.

Another methodology is the "changes analysis" or "events analysis", which consists of carefully analyzing the changes made, from the moment that the failure didn't exist up to this moment, this way we can find which of the changes provoked the failure to appear.

Another method is the cause-and-effect fishbone diagram, also known as Ishikawa's diagram, which visually helps to map causes and effects. It can help to identify the possible causes of a problem and encourage us to follow categoric branches to the possible causes until we find the correct one. It is like the 5 whys, but much more visual [9].

# 3. THEORETICAL FRAMEWORK AND HISTORICAL DEBUG CASES

**Summary:** In this chapter, the theoretical and conceptual foundations for the electrical validation of clocks are presented, as well as the parameters or electrical phenomena whose lack of knowledge makes it difficult to find root causes in clock integrated circuits and their implementation in a system. We can also see the historic list of defects that have been debugged during the validation of past products, in which electrical parameters involved are explained to generate technical knowledge.

#### 3.1. The electrical validation of clocks at the system level

Performing system-level electrical validation of clocks means, validating that clock signals arrive with signal integrity to the receiver circuits that require them. This document is focused on systems of the "Client" market segment. Although it is not focused on the "Devices" or "Server" segments, many of the concepts can be applied as well. The Client segment refers to computer systems like Laptops and Desktop. The Devices segment refers to mobile devices like Tablets and Cellphones. Similarly, the Server segment refers to Server systems.

Electrical Validation consists of two main phases, pre-silicon, and post-silicon. Pre-silicon is when the integrated circuit hasn't been built yet, many activities occur in this phase for our group, such as product specification study, board design guideline review, specifications, schematic and motherboard analysis, and test plan creation. Post-silicon starts at Power-On, which is the first time the physical Integrated Circuit is being powered up, and The Test Plan is executed, which is when several tests are performed on the product, and it finishes at the Production Release milestone. During the execution of the Test Plan, when defects are found, debugging must be done to find the root cause as soon as possible. Though the debug is not a planned phase, it is inherently added to the process when failures occur.

This work focuses mainly on reference clocks for PCIe, which are differential clocks that have a frequency of 100MHz and travel distances of 3 to 12 inches across the motherboard before reaching the receiver, using FR4 board material in either micro-strip or strip-line traces. Clocks, like any other signal, are susceptible to being contaminated by other signals as they travel across the board, which generates physical phenomena such as jitter, crosstalk, and noise in general.

In a "Client" system there are many other clocks with several frequencies and topologies, including Single-Ended clocks.

In this document, some failure cases will be reviewed on both, differential and single-ended clocks.

#### 3.2. Debugging clock defects

There is no specific debugging methodology or step-by-step guide to finding the root cause of a clock problem on the platform. Instead, based on the electrical parameter where the fault is observed, a series of experiments are implemented to help expose and understand the defect. There are many methodologies to find the root causes of problems, as described in section 0.

A more efficient debug can be performed when technical knowledge of parameters or phenomena that occur in electronic systems is available, such as jitter, crosstalk, slew rate, and reflections, among others.

Just like these parameters, many others will be analyzed throughout this work to generate knowledge that serves to discover the root causes of failures more efficiently and promptly in the validation phase.

#### 3.3. Impact Analysis

The historical debug cases are analyzed in Table 2, The table contains six columns, and the meaning of each column is:

"Electrical Parameter Failed" – This is the parameter or specification that failed to meet the spec during validation.

"Clock affected" - This is the name of the clock or the circuit that showed the malfunction.

"Impact" – It shows the actions to do to fix the problem, either redesigning the board or silicon or re-validation efforts.

"Recurrence" – In this column there's a quantification of how frequently the issue has been seen in previous projects.

"Time to fix" – This is the average time that it takes to fix the problem.

"Rating" – This is the weighing of every parameter, the value in this column shows the result of multiplying the factors from columns: Impact, Recurrence, and Time to fix, the higher the value, the more problematic issue.

| Electrical<br>Parameter<br>Failed | Clock<br>affected                       | Impact                                                                                                                                                                                                       | Recurrence                                   | Time to<br>fix<br>(weeks)                           | Rating |

|-----------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------------------------|--------|

| Undershoot                        | Imaging gpio<br>clock for<br>Camera     | 5- Very high, it might trigger board redesign.                                                                                                                                                               | 3- Medium,<br>only seen in<br>one project    | 20 weeks                                            | 300    |

| Jitter                            | PCIe Serial<br>Reference<br>Clock (SRC) | 5- Very high, we need to<br>perform experiments to<br>find the cause, it might<br>trigger board or Silicon<br>circuit redesign or<br>settings workaround.                                                    | 4- High, seen<br>in some<br>projects         | Few to<br>several<br>weeks (10<br>weeks<br>average) | 200    |

| Frequency ppm                     | Susclk from<br>Real Time<br>Clock       | 4- High, we need to tune<br>the capacitor value for<br>the board. Replace and<br>remeasure.                                                                                                                  | 5- Very high,<br>seen in many<br>projects    | 7 weeks                                             | 140    |

| Slew Rate                         | PCIe Serial<br>Reference<br>Clock (SRC) | 4- High, we need to<br>collect a lot of data, in<br>several topologies,<br>involve many<br>stakeholders in meetings                                                                                          | 5- Very high,<br>seen in many<br>projects    | 7 weeks                                             | 140    |

| Other PLL<br>issues               | PLL itself                              | 2- Low impact on our<br>team because we don't<br>own the PLL validation.<br>It could trigger settings<br>changes or Silicon<br>circuit changes. Either<br>way, we need at least to<br>understand PLL basics. | 5- Very high,<br>seen in many<br>projects    | Few to<br>several<br>weeks (10<br>weeks<br>average) | 100    |

| Cross talk                        | Crystal<br>circuit, latest<br>in 2015   | 4- High, it might trigger board redesign.                                                                                                                                                                    | 1- Very low,<br>issue not seen<br>since 2015 | 20 weeks                                            | 80     |

| Phase Noise                       | Universal<br>Flash<br>Storage<br>(UFS)  | 4- High, We can't afford<br>the cost of a PXA<br>because it is used only a<br>few weeks per year, and                                                                                                        | 3- Medium,<br>only seen in<br>one project    | 5 weeks                                             | 60     |

Table 2: Electrical parameter failed vs. Impact.

|                               | Reference<br>Clock                      | we only have an oscilloscope.                                                                                                                                               |                                                                     |                             |    |

|-------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------|----|

| SSC profile<br>from PLL       | PCIe Serial<br>Reference<br>Clock (SRC) | 2- Low, we typically<br>need to tune two settings<br>in the PLL.                                                                                                            | 5- Very high,<br>seen in many<br>projects                           | 3 weeks                     | 30 |

| Power<br>Management<br>states | It could be<br>any                      | 2- Low impact on our<br>team because we don't<br>own the PM validation.<br>It could trigger Software<br>flow changes. We could<br>study more on this in<br>future analyses. | 1- Very low,<br>our team hasn't<br>been involved<br>in these debugs | A few<br>weeks (3<br>weeks) | 6  |

| Duty Cycle                    | Imaging gpio<br>clock for<br>Camera     | 1- Very low, last time it<br>was seen by the pre-<br>silicon team, it was not<br>seen during post-silicon<br>validation                                                     | 1- Very Low,<br>issue not seen<br>yet during<br>validation          | 3 weeks                     | 3  |

#### 3.4. Electrical Parameters Review

Explaining every electrical parameter from Table 2.

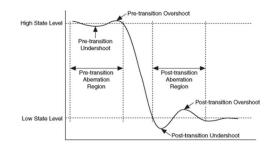

**Undershoot**: This is a type of signal integrity issue that occurs when a signal's voltage drops below its intended low level, Figure 4, It can cause incorrect data transmission, especially in digital circuits, or even damage to the circuits [4]. Undershoot occurs when the impedance of the signal path is not matched properly, leading to reflections that cause the voltage to drop below the expected level. This can be caused by factors such as improper termination, incorrect trace lengths, or insufficient drive strength. To mitigate undershoot, designers use techniques such as adding series resistors to limit the current flow and prevent overshoot/undershoot, adjusting the drive strength of the signal source, or using impedance matching techniques to ensure that the signal path is properly matched.

Figure 4: Overshoot and Undershoot.

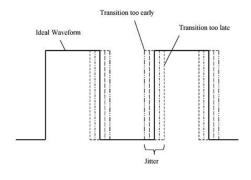

**Jitter**: It is a measure of significant variations of a digital signal from its ideal position in time, affecting signal phase, width, and period, Figure 5. Jitter is an unwanted factor that can lead to an increase in the bit error rate of a serial link [10]. One type of jitter is Random, which is unbounded and can take any shape, also known as Gaussian jitter, the other type is Deterministic, which is a predictable jitter, it is further subcategorized as period jitter, bounded uncorrelated jitter, and data-dependent jitter.

Figure 5: Jitter.

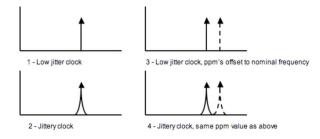

**Frequency ppm**: This is a measure of frequency precision, Figure 6, represents the output variation due to external conditions like temperature, voltage, and load changes, as well as aging. It is typically expressed in parts per million (ppm) [11]. For example – if a quartz oscillator has an output frequency of 1MHz (1,000,000 Hz) and it has a Frequency Stability of 5ppm, it will vary in frequency by 5 Hz.

Figure 6: Frequency ppm.

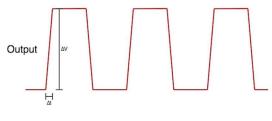

**Slew Rate**: It is defined as the rate at which an electronic circuit or device can change its output voltage or current, Figure 7. It is often expressed in volts per nanosecond (V/ns) or amperes per nanosecond (A/ns) [12].

Figure 7: Slew Rate.

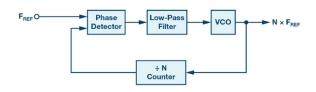

**Other PLL issues**: These refer to a variety of issues seen in PLLs, Figure 8, such as locking, lock time, bandwidth, stability, and others. This document doesn't intend to explain PLL debugging since it is out of our team validation scope, but still, we're trying to explain PLL's functionality for engineers to have a basic understanding of it [13].

Figure 8: Basic PLL Configuration.

**Cross talk**: It is one of the signal-integrity problems. It is the transfer of an unwanted signal from one net to an adjacent net and will occur between every pair of nets, Figure 9. The net with the source of the noise is typically called the active net of the aggressor net. The net receiving the noise is called the quiet net or the victim net [14].

Figure 9: Cross Talk.

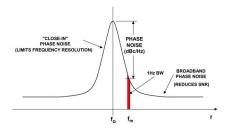

**Phase Noise**: It is typically characterized by a frequency offset from the carrier frequency, and it is usually expressed in units of decibels relative to the carrier (dBc), Figure 10. The lower the dBc value, the better the phase noise performance of the oscillator. Phase noise is defined as the ratio of the noise in a 1-Hz bandwidth at a specified frequency offset, fm, to the oscillator signal amplitude at frequency fo [15].

Figure 10: Phase Noise.

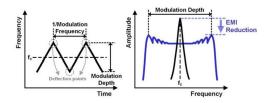

**SSC profile from PLL**: SSC is the variation of the frequency of a clock signal in a controlled way, Figure 11. In the frequency domain, the SSC reduces the peak amplitude of a digital clock signal by shifting the frequency. In other words, the energy of the clock is spread, decreasing the peak values of the radiation, and it can help with EMI reduction [16].

Figure 11: Spread Spectrum Clock Profile.

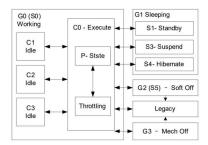

**Power Management states**: These relate to states where the power consumption, of a system, is lower or higher. To the user, a computer system appears to be either on or off, there are no other detectable states, Figure 12. However, the system supports multiple power states, such as working, standby, sleep, and hibernating, among others [17].

Figure 12: Power Management States.

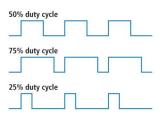

**Duty Cycle**: It is the ratio of time a load or circuit is "on" compared to the time the load or circuit is "off", Figure 13. It is sometimes called the "duty factor", and it is expressed as a percentage of "on" time [18]. A 60% duty cycle is a signal that is "on" 60% of the time and "off" the other 40%.

Figure 13: Duty Cycle.

# 4. CLOCK BUFFER ARCHITECTURE

**Summary:** Many circuits are being designed and explained within this chapter, from CMOS inverters to single-ended and complementary buffers with controlled impedance. The design of the transmission lines is also explained here.

#### 4.1. The Pmos and Nmos models

One of the tools used during this work is ADS from Keysight company, this tool was learned from the course "High Frequency Electronic Design" in ITESO.

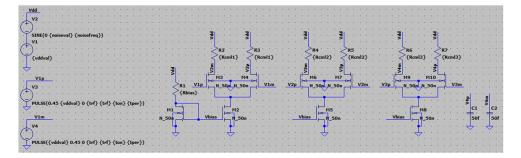

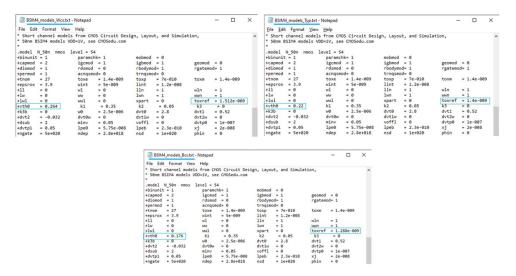

Many of the circuits that we'll simulate use Pmos and Nmos transistors, and we need to get their model, shown in Figure 14, these models are obtained from the "Predictive Technology Model" web page [19]. I decided to use the 180nm transistor model [20] because this is the technology we studied in the course "Design of Analog Integrated Circuits" so I could use the license owned by the ITESO if needed.

| 180nm_bulk_nmos_pmos.txt - N | otepad                     |                        |

|------------------------------|----------------------------|------------------------|

| File Edit Format View Help   |                            |                        |

| *                            |                            |                        |

| * Predictive Technolog       | y Model Beta Version       |                        |

| * 180nm NMOS SPICE Par       | ametersv (normal one)      |                        |

| *                            |                            |                        |

| .model NMOS NMOS             |                            |                        |

| +Level = 49                  |                            |                        |

| +Lint = 4.e-08 Tox = 4       | .e-09                      |                        |

| +Vth0 = 0.3999 Rdsw =        | 250                        |                        |

| +lmin=1.8e-7 lmax=1.8e       | -7 wmin=1.8e-7 wmax=1.0e-4 | Tref=27.0 version =3.1 |

| +Xj= 6.000000E-08            | Nch= 5.9500000E+17         |                        |

| +lln= 1.0000000              | lwn= 1.0000000             | wln= 0.00              |

| +wwn= 0.00                   | 11= 0.00                   |                        |

| +1w= 0.00                    | lw1= 0.00                  | wint= 0.00             |

| +wl= 0.00                    | ww= 0.00                   | wwl= 0.00              |

| +Mobmod= 1                   | binunit= 2                 | xl= 0                  |

| +xw= 0                       | binflag= 0                 |                        |

| +Dwg= 0.00                   | Dwb= 0.00                  |                        |

Figure 14: NMOS and PMOS models.

#### 4.1.1. Configuring ADS to use the Pmos/Nmos model

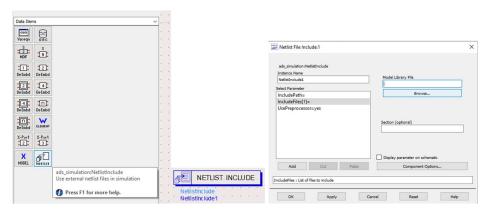

In ADS, under "Data Items", select "Netlist", then double click on the "Netlist Include" object from the schematic, select "IncludeFiles[1]=", browse for the model's .txt file, click apply and Ok. Figure 15.

Figure 15: Configuration of Model in ADS.

#### 4.2. The Inverter

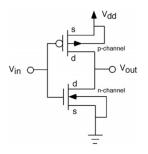

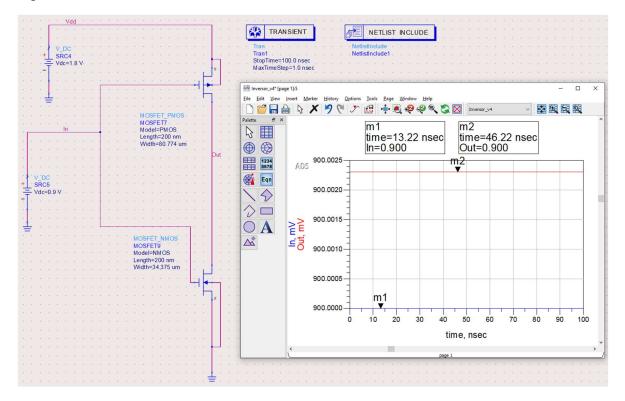

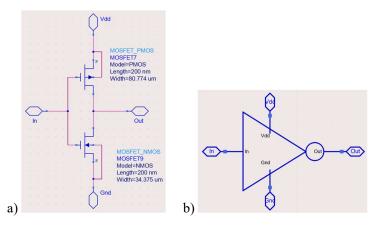

One of the basic CMOS circuits is the Inverter, which is built with one Pmos and one Nmos transistor, connected as in Figure 16. When one transistor is On, the other is Off [21].

Figure 16: CMOS Inverter.

Though Nmos and Pmos supposedly work the same, in reverse to each other, this is not physically true, electrons in Nmos move faster than holes in a Pmos; therefore, Pmos transistors must be compensated, and this is done by increasing its "width" to more than twice the Nmos "width". The circuit in Figure 17 is used to make this compensation.

According to my notes from the course "Design of Analog Integrated Circuits", for a 180nm technology, the minimum channel "length" is  $L_{min} = 180$ nm, and it is recommended to use L = 200nm for layout. The minimum channel "width" is  $W_{min} = 320$ nm, which is derived from the rules of escalation of the technology, and it takes "distance to edge", "contact size" and "contact separation" into consideration, it is recommended to use W = 360nm for layout, which is twice the  $L_{min}$ , so we avoid manufacturing issues by separating from the minimum sizes.

Figure 17: Pmos to Nmos compensation.

Steps to do the compensation: use the smaller recommended Length/Width values for the Nmos, which is 200nm/360nm, then use the smaller recommended Length and twice the Nmos Width for the Pmos, which is 200nm/720nm. Apply 0.9V (which is half of Vdd) to input "In" and measure Output "Out".

Increase or decrease the Pmos Width until "Out" is equal to "In". In this example, "Out" equal to "In" was obtained in Try # 8, Table 3. And Pmos width is 2.35 times Nmos width.

| Try # | In   | Out      | Nmos L/W    | Pmos L/W    |

|-------|------|----------|-------------|-------------|

| 1     | 0.9V | 0.646V   | 200nm/360nm | 200nm/720nm |

| 2     | 0.9V | 0.813V   | 200nm/360nm | 200nm/800nm |

| 3     | 0.9V | 0.994V   | 200nm/360nm | 200nm/900nm |

| 4     | 0.9V | 0.907V   | 200nm/360nm | 200nm/850nm |

| 5     | 0.9V | 0.889V   | 200nm/360nm | 200nm/840nm |

| 6     | 0.9V | 0.898V   | 200nm/360nm | 200nm/845nm |

| 7     | 0.9V | 0.902V   | 200nm/360nm | 200nm/847nm |

| 8     | 0.9V | 0.90014V | 200nm/360nm | 200nm/846nm |

Table 3: Pmos Width adjustment of the Inverter.

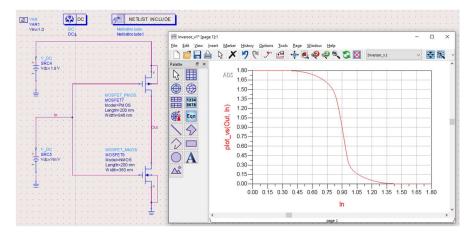

Another way to do the compensation is by sweeping Input "In" from 0 to 1.8V, plotting In vs. Out signals, then increasing or decreasing Pmos Width till "In" and "Out" cross at 0.9V. Figure 18.

Figure 18: In vs. Out plot, sweeping "In" voltage.

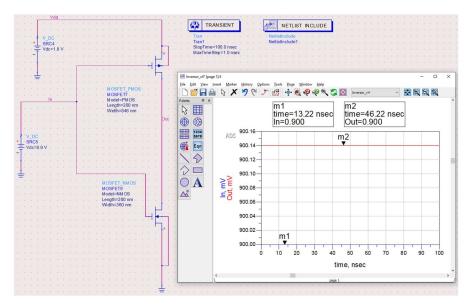

The "Out" signal should have the same amplitude as the "In" signal but delayed 180°, so when the Input is a 1 logic, the Output is a 0 logic, and the other way around. This can be verified by applying a square signal to the Inverter and measuring the output. Also, the cross point, where signals are crossing each other, occurs at half Vdd, which is 0.9V. Figure 19.

Figure 19: In vs. Out, applying a square signal.

## 4.3. Nmos Leg Tuning

The Nmos leg is one of the circuits of a complementary buffer with controlled impedance. When designing a 50 $\Omega$  driver, the three typical designs are: 90/10 design, which means 90% resistor, 10% transistor, similarly, an 80/20 design means 80% resistor, 20% transistor, as well as 70/30 design meaning 70% resistor, 30% transistor. The resistors in silicon show fewer variations to process and temperature because their response is linear to voltage, while the transistors show more variations to process, voltage, and temperature, because the response is not linear, it passes through different operation regions.

In this case, I'm focusing on an 80/20 design, in which, the driver consists of one resistor of  $40\Omega$  in series with two Nmos transistors, from Out to Gnd as in Figure 20.

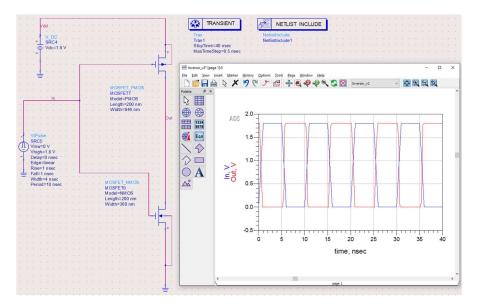

Figure 20: Nmos leg.

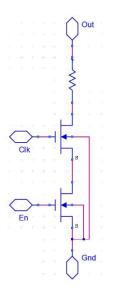

One of the Nmos transistors receives the clock signal from the controller, to be transmitted out of the buffer. The other Nmos transistor is gated by an "En" control signal, it helps to enable or disable a specific leg, so we can create a controlled impedance buffer.

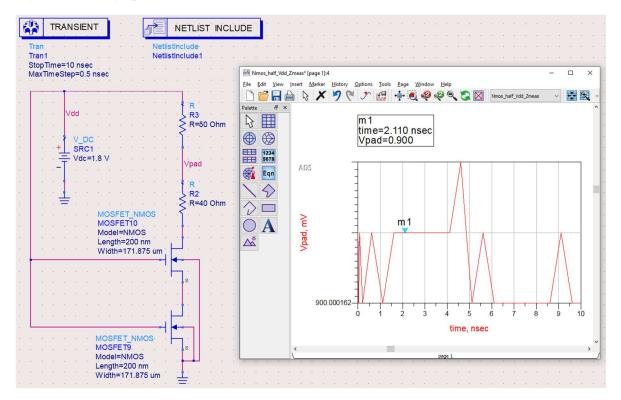

The width of the Nmos transistors must be adjusted to get ~5 Ohm dc resistance on each, and both added to the  $40\Omega$  resistor, create a  $50\Omega$  driver. The circuit in Figure 21 is used to adjust the Width of the Nmos transistors. When using the minimum recommended Length/Width, whose are 200nm/360nm, we are getting 1.793V at Vpad.

Figure 21: Nmos Width adjustment circuit.

The objective is to have half Vdd, which is 0.9V, at the Vpad node. This can be done by increasing the Width of the Nmos transistors while keeping the minimum recommended Length, of 200nm. Table 4 shows the iterations tried, increasing the Width of the Nmos transistors, and measuring Vpad until we get 0.9V.

| Nmos 1 and 2, Length | Nmos 1 and 2, Width | Vpad   | Error (Vpad – Target) |

|----------------------|---------------------|--------|-----------------------|

| 200nm                | 360nm               | 1.793V | 893mV                 |

| 200nm                | 720nm               | 1.787V | 887mV                 |

| 200nm                | 1.44um              | 1.774V | 874mV                 |

| 200nm                | 2.88um              | 1.748V | 848mV                 |

| 200nm                | 5.76um              | 1.696V | 796mV                 |

| 200nm                | 11.52um             | 1.595V | 695mV                 |

| 200nm                | 23.04um             | 1.402V | 502mV                 |

| Table 4: | Nmos | Width | adjustment. |

|----------|------|-------|-------------|

|----------|------|-------|-------------|

| 200nm | 46.08um   | 1.146V       | 246mV                 |

|-------|-----------|--------------|-----------------------|

| 200nm | 92.16um   | 0.983V       | 83mV                  |

| 200nm | 184.32um  | 0.893V       | -7mV                  |

| 200nm | 180.00um  | 0.896V       | -4mV                  |

| 200nm | 175.00um  | 0.898V       | -2mV                  |

| 200nm | 170.00um  | 0.901V       | 1mV                   |

| 200nm | 171.00um  | 0.90049V     | 0.49mV                |

| 200nm | 172.00um  | 0.899929220V | 0.07078mV             |

| 200nm | 173.00um  | 0.899V       | -1mV                  |

| 200nm | 171.90um  | 0.899985966V | -0.014034mV           |

| 200nm | 171.85um  | 0.900014363V | 0.014363mV            |

| 200nm | 171.875um | 0.90000162V  | 0.000162mV - Selected |

| 200nm | 172.876um | 0.899999594V | -0.000406mV           |

Figure 22 shows the circuit with the selected values, Length=200nm and Width=171.875um for the Nmos leg and measuring Vpad.

Figure 22: Selected Nmos Width.

## 4.4. Pmos Leg Tuning

Similarly, the Pmos leg is a circuit as shown in Figure 23, for an 80/20 design, the driver consists of two Pmos transistors in series with one resistor of  $40\Omega$ , from Vdd to Out.

Figure 23: Pmos leg.

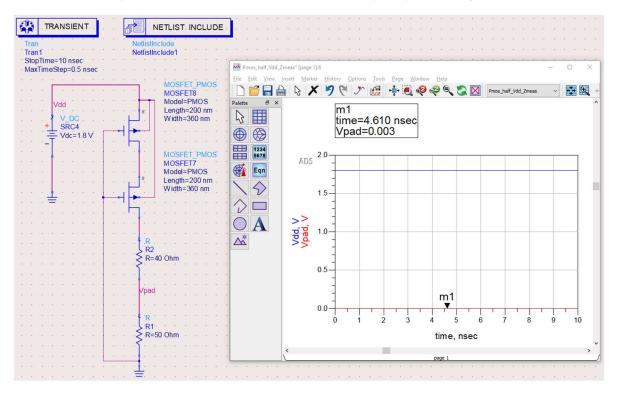

The circuit in Figure 24 is used to adjust the Width of the Pmos transistors. When using the minimum recommended Length/Width, whose are 200nm/360nm, we are getting 3mV at Vpad.

Figure 24: Pmos Width adjustment circuit.

Similarly, as in the Nmos leg adjustment, the objective is to have half Vdd, which is 0.9V, at the Vpad node. This can be done by increasing the Width of the Pmos transistors while keeping the minimum recommended Length, of 200nm. Table 5 shows the iterations by increasing the Width of the Pmos transistors and measuring the Vpad until we get 0.9V.

| Pmos 1 and 2, Length | Pmos 1 and 2, Width | Vpad          | Error (Vpad – Target)  |

|----------------------|---------------------|---------------|------------------------|

| 200nm                | 360nm               | 0.003V        | -897mV                 |

| 200nm                | 720nm               | 0.005V        | -895mV                 |

| 200nm                | 1.44um              | 0.011V        | -889mV                 |

| 200nm                | 2.88um              | 0.021V        | -879mV                 |

| 200nm                | 5.76um              | 0.043V        | -857mV                 |

| 200nm                | 11.52um             | 0.084V        | -816mV                 |

| 200nm                | 23.04um             | 0.166V        | -734mV                 |

| 200nm                | 46.08um             | 0.317V        | -583mV                 |

| 200nm                | 92.16um             | 0.550V        | -350mV                 |

| 200nm                | 184.32um            | 0.750V        | -150mV                 |

| 200nm                | 368.64um            | 0.869V        | -31mV                  |

| 200nm                | 737.28um            | 0.933V        | 33mV                   |

| 200nm                | 700um               | 0.930V        | 30mV                   |

| 200nm                | 600um               | 0.919V        | 19mV                   |

| 200nm                | 500um               | 0.903V        | 3mV                    |

| 200nm                | 450um               | 0.892V        | -8mV                   |

| 200nm                | 475um               | 0.898V        | -2mV                   |

| 200nm                | 485um               | 0.8997753784V | -0.2246216mV           |

| 200nm                | 486um               | 0.899975262V  | -0.024738mV            |

| 200nm                | 487um               | 0.900174352V  | 0.174352mV             |

| 200nm                | 486.2um             | 0.9000151435V | -0.0151435mV           |

| 200nm                | 486.1um             | 0.8999952068V | -0.0047932mV           |

| 200nm                | 486.15um            | 0.900005176V  | 0.005176mV             |

| 200nm                | 486.14um            | 0.900003182V  | 0.003182mV             |

| 200nm                | 486.13um            | 0.900001189V  | 0.001189mV             |

| 200nm                | 486.12um            | 0.899999195V  | -0.000805mV            |

| 200nm                | 486.121um           | 0.8999993941V | -0.0006059mV           |

| 200nm                | 486.122um           | 0.8999995935V | -0.0004065mV           |

| 200nm                | 486.123um           | 0.899999793V  | -0.000207mV            |

| 200nm                | 486.124um           | 0.899999992V  | -0.000008mV - Selected |

| 200nm                | 486.125um           | 0.900000192V  | 0.000192mV             |

Table 5: Pmos Width adjustment.

Figure 25 shows the circuit with the selected values, Length=200nm and Width=486.124um for the Pmos leg and measuring Vpad.

Figure 25: Selected Pmos Width.

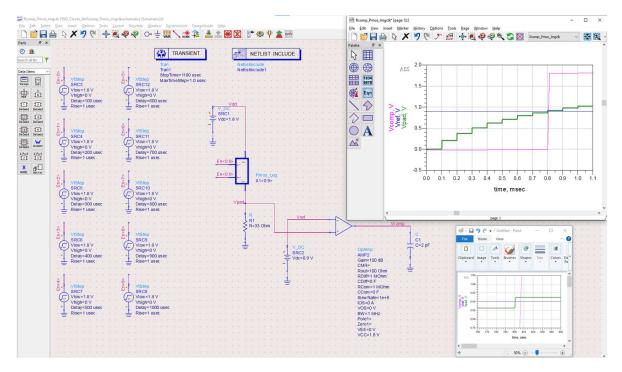

## 4.5. Programmable Impedance Driver

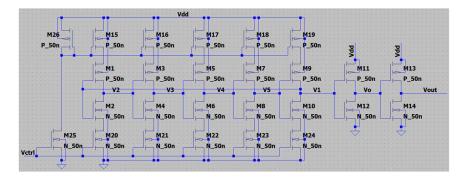

We can create a programmable impedance driver by putting some replicas of the Nmos and Pmos tuned legs. In this example we're putting 10 legs of each, Nmos and Pmos, we're selecting the values of W, L, and R to get a 50 $\Omega$  driver when 5 of the 10 legs are used. Every one of the 10 legs must have a DC resistance of 250 $\Omega$ , so when 5 legs are On, the equivalent DC resistance will be 50 $\Omega$ , this is because they are in parallel to each other.

We want the driver to be tuned at  $50\Omega$  with 5 of the 10 legs, in typical, this is in the middle, so when working with best and worst cases, we can have the margin to add or remove legs.

## 4.6. Nmos Rcomp for a $50\Omega$ Driver

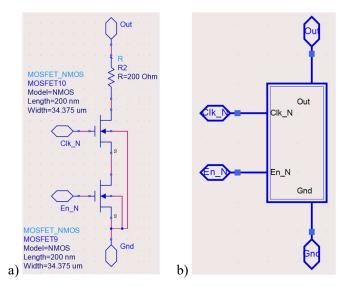

From the tuned values, found at the Nmos leg tuning, section 4.3, we can create a  $250\Omega$  leg by multiplying the Resistor by 5 and dividing the Width by 5. Length mustn't change. Values can be seen in Table 6 and the Nmos leg is shown in Figure 26.

| Length | Width     | Resistor | Nmos Leg DC resistance |

|--------|-----------|----------|------------------------|

| 200nm  | 171.875um | 40Ω      | 50Ω                    |

| 200nm  | 34.375um  | 200Ω     | 250Ω                   |

Table 6: L, W, and R, for  $50\Omega$  and  $250\Omega$  Nmos Legs.

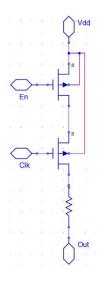

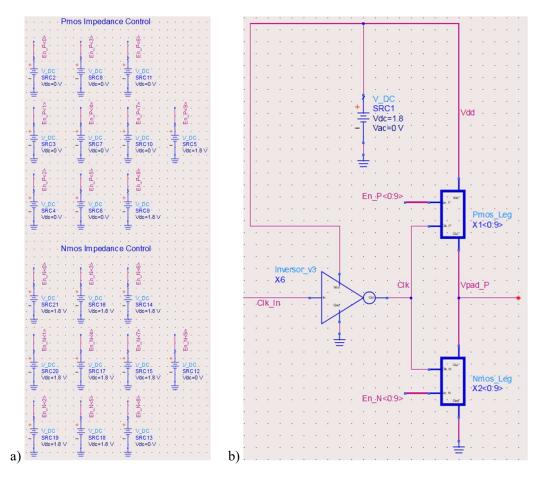

Figure 26: Nmos Leg. a) Circuit. b) Symbol.

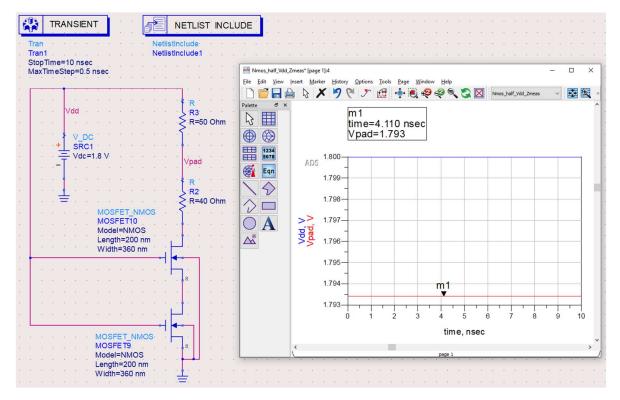

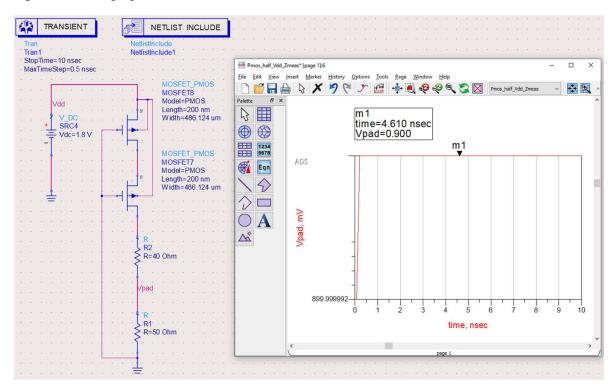

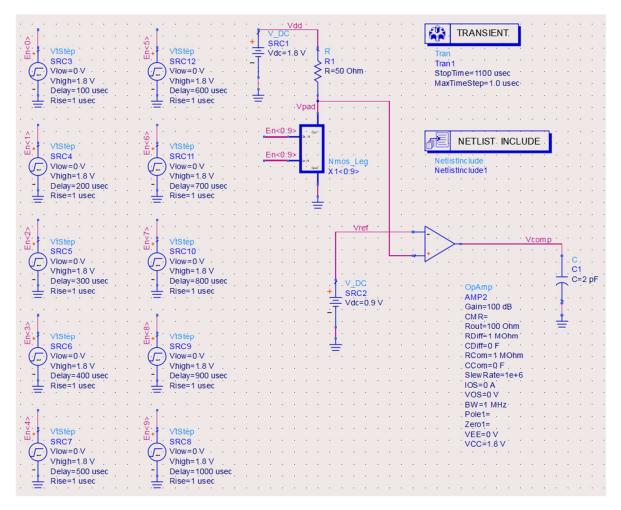

The circuit in Figure 27 helps to verify that the Nmos driver is tuned to  $50\Omega$  when 5 of the 10 legs are turned On. The "Nmos\_Leg" X1<0:9> block contains 10 Nmos legs in parallel, the Nmos leg Clk\_N and En\_N pins are controlled with VtStep sources, which transition from 0V to 1.8V in a sequence, after 100usec each. The Nmos are activated with 1.8V. The OpAmp is an Operational Amplifier used as a comparator, it compares the 0.9V Vref to the voltage at Vpad. We're putting a 2pF load at the output of the comparator, this is only to have a small load and not an open circuit and to avoid errors in the simulation tool. Vdd is 1.8V.

Figure 27: Nmos Rcomp verification circuit.

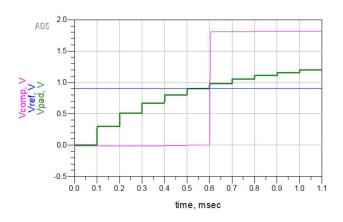

The expectation is that the Vcomp output transitions from 1.8V to 0V when Vpad is equal to Vref=0.9V, this is expected to happen when 5 of the 10 legs are activated. Figure 28 shows the simulation of the circuit, we can see that effectively, the Vpad is equal to Vref when 5 legs are active, and Vcomp transitions correctly. Every step on the Vpad signal represents one more leg that has turned On.

Figure 28: Nmos Rcomp circuit simulation result.

## 4.7. Pmos Rcomp for a $50\Omega$ Driver

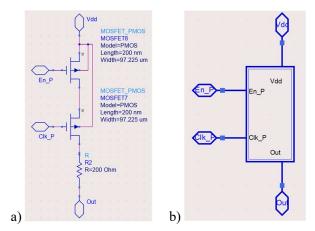

Similarly, from the tuned values, found at the Pmos leg tuning, section 4.4, Table 7 shows the Length, Width, and Resistor values for a  $250\Omega$  Pmos leg. This is done by multiplying the Resistor by 5 and dividing the Width by 5. Length mustn't change. The Pmos leg is shown in Figure 29.

| Length | Width     | Resistor | Nmos Leg DC resistance |

|--------|-----------|----------|------------------------|

| 200nm  | 486.124um | 40Ω      | 50Ω                    |

| 200nm  | 97.225um  | 200Ω     | 250Ω                   |

Table 7: L, W, and R, for  $50\Omega$  and  $250\Omega$  Pmos Legs.

Figure 29: Pmos Leg. a) Circuit. b) Symbol.

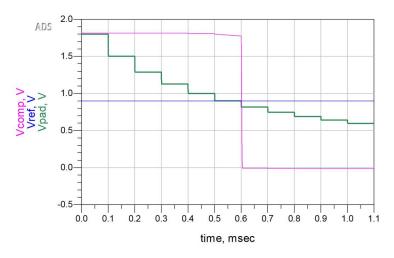

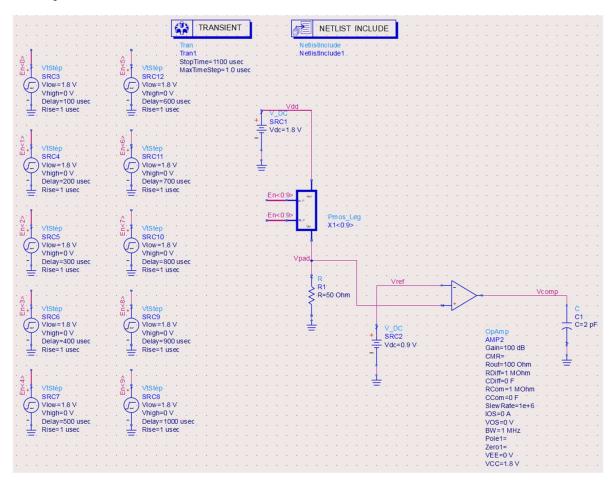

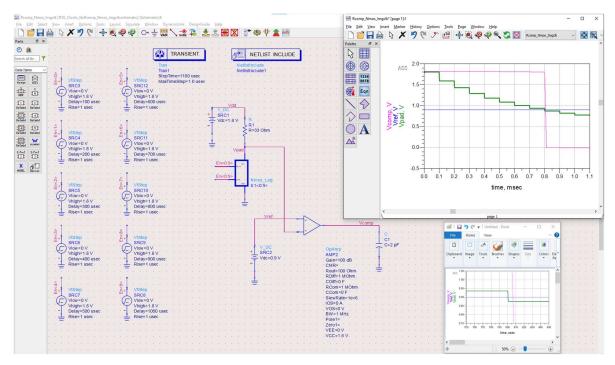

Figure 30 shows the circuit to verify that the Pmos driver is tuned to  $50\Omega$  when 5 of the 10 legs are turned On. The "Pmos\_Leg" X1<0:9> block contains 10 Pmos legs in parallel, the Pmos leg Clk\_P and En\_P pins are controlled with VtStep sources, which transition from 1.8V to 0V in sequence, after 100usec each.

The Pmos are activated with 0V. The OpAmp is comparing the 0.9V Vref to the voltage at Vpad. The 2pF load capacitor avoids errors in the simulation tool. Vdd is 1.8V.

Figure 30: Pmos Rcomp verification circuit.

As expected, the Vcomp output transitions from 0V to 1.8V when Vpad is equal to Vref=0.9V, this occurs when 5 of the 10 Pmos legs are activated. Every step on the Vpad signal represents one more leg that has turned On. Figure 31 shows the result of the simulation.

Figure 31: Pmos Rcomp circuit simulation result.

## 4.8. Nmos and Pmos Rcomp for a $33\Omega$ Driver

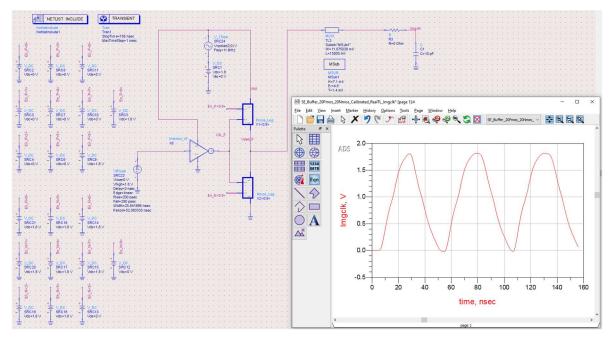

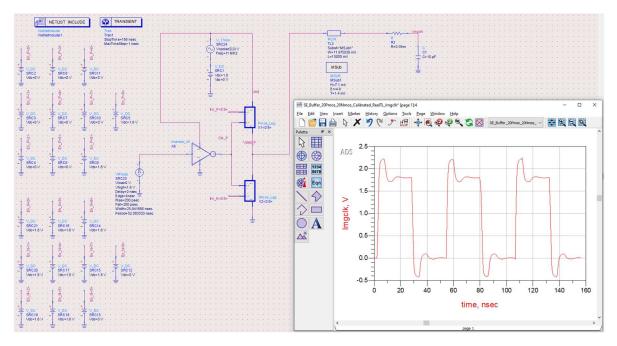

The image clock (Imgclk) is a Single-Ended 33 $\Omega$  driver. By using the "Programmable Impedance Driver" reviewed in section 4.5, we only need to run the Rcomp simulations and check how many legs are needed to be enabled to get a 33 $\Omega$  driver. From the simulation in Figure 32 and Figure 33, we can see that we need to activate 8 of the 10 legs to obtain a 33 $\Omega$  driver.

Figure 32: Nmos Rcomp simulation for a  $33\Omega$  driver.

Figure 33: Pmos Rcomp simulation for a  $33\Omega$  driver.

## 4.9. Single-Ended Non-Ideal $50\Omega$ Transmission Line

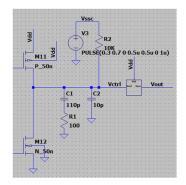

In this section we'll review how to create a non-ideal Single-Ended Transmission Line in ADS, We need it to make simulations with a driver and a transmission line and understand how the clock signal arrives at the Far-End receiver, which will be closer to the reality.

In one of the classes at the ITESO, named "Printed Circuit Board Design Workshop", I learned that we could use specific tools from the PCB suppliers, calculators that help to understand the physical dimensions of the tracks for a specific Impedance, one of such calculators is from JLCPCB company [22]. In this tool, we need to specify the Impedance that we want, In this example we want a 4-layer PCB because we're considering a simple circuit, we're selecting the Thickness 1.6mm for a cheaper PCB, the thicker the PCB, the more expensive it is. We are considering routing the clock in the outer layer, so the inner layer will act as the Return Path, and selecting Single-ended, which is the type on the required transmission line.

The result of the calculation is shown in Figure 34, we're focusing on the JLC7628 stack-up, which is shown in Figure 35, we can see that our  $50\Omega$  Single-Ended Transmission Line can be built with a trace width of 11.55mil, a height H1 of 7.10mil, a Dielectric Constant of 4.6, and a copper thickness T1 of 1.4mil.

| impedance + trace space 🗸                        | trace width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Impedance value(ohm): 50                         | Type 1: Recommend trace width: 11.55mill<br>Order selection:ILC7628 View stackup<br>Type 2: Recommend trace width: 5.78mil<br>Order selection:ILC3313 View stackup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |