DEPARTAMENT OF ELETRICAL AND COMPUTER ENGINEERING

João Pereira Cabacinho BSc in Electrical and Computer Engineering

PUFs based on Coupled Oscillators Static Entropy

MASTER IN ELECTRICAL AND COMPUTER ENGINEERING NOVA University Lisbon September, 2022

## PUFs based on Coupled Oscillators Static Entropy

#### João Pereira Cabacinho

## BSc in Electrical and Computer Engineering

Adviser: Dr. Luís Augusto Bica Gomes de Oliveira Associate Professor, NOVA University Lisbon

#### **Examination Committee:**

| Chair:       | Dr. André Teixeira Bento Damas Mora,<br>Assistant Professor, NOVA University Lisbon     |

|--------------|-----------------------------------------------------------------------------------------|

| Rapporteurs: | Dr. João Carlos Ferreira de Almeida Casaleiro,<br>Adjunct Professor, ISEL               |

| Adviser:     | Dr. Luís Augusto Bica Gomes de Oliveira,<br>Associate Professor, NOVA University Lisbon |

MASTER IN ELETRICAL AND COMPUTER ENGINEERING NOVA University Lisbon September 2022

#### PUFs based on Coupled Oscillators Static Entropy

Copyright © João Pereira Cabacinho, NOVA School of Science and Technology, NOVA University Lisbon.

The NOVA School of Science and Technology and the NOVA University Lisbon have the right, perpetual and without geographical boundaries, to file and publish this dissertation through printed copies reproduced on paper or on digital form, or by any other means known or that may be invented, and to disseminate through scientific repositories and admit its copying and distribution for non-commercial, educational or research purposes, as long as credit is given to the author and editor.

This document was created with Microsoft Word text processor and the NOVAthesis Word template [1].

To my parents for always supporting me.

#### ACKNOWLEDGMENTS

This dissertation is the culmination of several years of study, distress, setbacks, dedication, perseverance, joy, happiness, that have shaped the way I face life and the inherent challenges. There were many ups and downs, but without them there is no learning and evolution.

First, I would like to thank my supervisor, Prof. Luís Oliveira for his constant availability, for guiding me throughout this work without letting me lose the focus, for having trusted me with this work, and finally for his contagious enthusiasm in electronics that certainly helped me to keep motivated.

To Marta, for her patience in tolerating me in the most difficult moments, for not letting me ever give up by always believing in me, and for the love that was never lacking and that helped me through this journey. Without you, there would certainly have been more difficult moments. Thank you for being my companion and for always being there. You are my light.

To my friends, for their unconditional support and help and for helping to ease my mind. A special thanks to my colleagues André Félix, Carlos Sequeira, Diogo Dias, Diogo Pragosa and João Corvo, who always supported me and provided the most joyful moments along this journey.

To my father, for the example he is to me, for the demand he transmits and for always trying to teach his knowledge about any subject. Without you I wouldn't be the student I am today, and I wouldn't have the necessary rigor to get here. Thank you!

To my mother, for always believing in me and in my abilities. You were never one of the most demanding people, but your unconditional support was very important in getting through challenges and keeping me committed. Thank you for all the love, affection, and dedication.

ix

To my brother, he was certainly the person I've annoyed the most during my life. All the TV shows you insisted I watched and all the video games I played because of you were important to clear my head and continue to overcome challenges.

Finally, to my grandmother Pilar, for having accepted me in her house throughout these years and for all her attention so that I lacked nothing. Thank you.

"You face many defeats in life, but never let yourself be defeated." (Maya Angelou).

## ABSTRACT

We live in a digital era, this led to a shift from traditional industry to a society focused on information and communication technologies. The amount of shared information is exponentially growing every year. Protecting all this shared information is keeping everyone's privacy, is making sure the information is authentic, is keeping everyone safe.

The solution for such problems is cryptography using hardware-based, System on Chip, SoC solutions such as Random Number Generators, RNGs, and Physical Unclonable Functions, PUFs. RNGs generate random keys from random processes that occurs inside the system. PUFs generate fixed random keys using random processes that originated in the fabrication process of the chip. The objective of this work is to study and compare a static entropy source based on coupled relaxation oscillators against a state-of-the-art architecture like the static entropy source based on ring oscillators, in advanced 130nm technology. The characteristic studied were, area, power consumption, entropy, resistance to temperature, and supply voltage variations.

Compared to the ring oscillator implementation, the static entropy source designed showed promising results as a static entropy source, however, it revealed poor results in terms of area, power consumption, and entropy. Such results mean, the coupled relaxation oscillator may not be good at generating random numbers, however, it may be good at keeping its state when under temperature and supply voltage variations.

Keywords: Cryptography, Random, Entropy, Key, Oscillator, Coupled, PUF,

### Resumo

Vivemos numa era digital, o que levou a uma mudança da indústria tradicional para uma sociedade centrada sobre as tecnologias da informação e da comunicação. A quantidade de informação partilhada está a crescer exponencialmente todos os anos. Proteger toda esta informação partilhada é manter a privacidade de todos, é garantir que a informação é autêntica, está a manter todos seguros.

A solução para tais problemas é a criptografia com base em soluções de *hardware*, *System on Chip*, SoC tais como Geradores de Números Aleatórios, RNGs e Funções Físicas Inclonáveis, PUFs. Os RNGs geram chaves aleatórias a partir de processos aleatórios que ocorrem no interior do sistema. Os PUFs geram chaves aleatórias fixas utilizando processos aleatórios que se originaram no processo de fabrico do chip. O principal objetivo deste trabalho é estudar e comparar uma fonte estática de entropia baseada em osciladores de relaxação acoplados contra uma arquitetura de estado de arte como a fonte estática de entropia baseada em osciladores de anel, em tecnologia avançada de 130nm. As características estudadas foram, a área, o consumo energia, a entropia, e a resistência à temperatura e variações de tensão de alimentação.

Em comparação com a implementação do oscilador do anel, a fonte estática de entropia projetada mostrou resultados promissores como fonte estática de entropia, no entanto, revelou maus resultados em termos de área, consumo de energia e entropia. Estes resultados significam que o oscilador de relaxação acoplado pode não ser bom a gerar números aleatórios, no entanto, pode ser bom para manter o seu estado quando sujeito a variações de temperatura e tensão de alimentação.

Palavas chave: Criptografia, Aleatório, Entropia, Chave, Oscilador, PUF.

# **CONTENTS**

| 1 | ΙΝΤ   | RODUCTION                                  | 1   |

|---|-------|--------------------------------------------|-----|

|   | 1.1   | Motivation                                 | . 1 |

|   | 1.2   | Proposed goals                             | 3   |

|   | 1.3   | Contributions                              | 3   |

|   | 1.4   | Report Structure                           | 3   |

| 2 | BAG   | CKGROUND                                   | 5   |

|   | 2.1   | Entropy                                    | 5   |

|   | 2.1.7 | 1 Static Entropy                           | 7   |

|   | 2.1.2 | 2 Dynamic Entropy                          | 7   |

|   | 2.2   | Oscillators                                | 7   |

|   | 2.2.7 | 1 Linear Oscillator                        | 10  |

|   | 2.2.2 | 2 Non-Linear/Relaxation Oscillator         | 14  |

|   | 2.2.3 | 3 Non-Linear/Relaxation Coupled Oscillator | 17  |

|   | 2.2.4 | 4 Ring Oscillator                          | 19  |

|   | 2.3   | PUFs                                       | 20  |

|   | 2.3.7 | 1 Weak PUFs                                | 21  |

|   | 2.3.2 | 2 Strong PUFs                              | 21  |

|   | 2.3.3 | 3 Architecture                             | 21  |

|   | 2.3.4 | 4 Quality Metrics                          | 23  |

|   | 2.4   | Statistics/Statistical Tests               | 23  |

|   | 2.4. | 1      | NIST Test                       | 24 |

|---|------|--------|---------------------------------|----|

|   | 2.4. | 2      | Chi-square Goodness of Fit Test | 24 |

|   | 2.4. | 3      | Monte Carlo Method              | 25 |

| 3 | ST   | ATE C  | F THE ART                       | 27 |

|   | 3.1  | Arb    | iter PUF                        | 27 |

|   | 3.2  | Me     | mory Based PUF                  | 29 |

|   | 3.3  | Osc    | illator Based PUF               | 30 |

|   | 3.3. | 1      | Relaxation Oscillator           | 30 |

|   | 3.3. | 2      | Coupled Oscillator              | 33 |

|   | 3.3. | 3      | Ring Oscillator                 | 34 |

| 4 | CII  | RCUIT  | IMPLEMENTATION                  | 39 |

|   | 4.1  | Vol    | tage Controlled Resistor        | 39 |

|   | 4.2  | Ent    | ropy Source                     | 40 |

|   | 4.2. | 1      | Relaxation Oscillator           | 41 |

|   | 4.2. | 2      | Coupled Relaxation Oscillator   | 46 |

|   | 4.2. | 3      | Ring Oscillator                 | 51 |

| 5 | An/  | ALYSIS | S AND DISCUSSION OF RESULTS     | 53 |

|   | 5.1  | Vol    | tage controlled Resistor        | 53 |

|   | 5.2  | Ent    | ropy Source                     | 55 |

|   | 5.2. | 1      | Relaxation Oscillator           | 57 |

|   | 5.2. | 2      | Coupled Relaxation Oscillator   | 65 |

|   | 5.2. | 3      | Ring Oscillator                 | 73 |

|   | 5.2. | 4      | Results Comparison              | 81 |

| 6 | Cor  | NCLUS  | SIONS AND FUTURE WORK           | 87 |

|   | 6.1  | Cor    | nclusions                       | 87 |

|   | 6.2  | Fut    | ure Work                        | 89 |

| Α | CF   | II-SQ  | JARE VALUES                     | 95 |

| В | Ν   | Ionte Carlo Tutorial                                                        | 97    |

|---|-----|-----------------------------------------------------------------------------|-------|

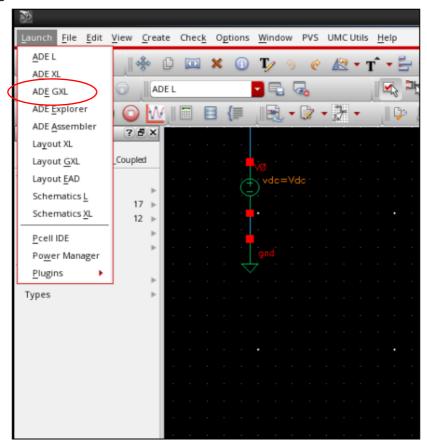

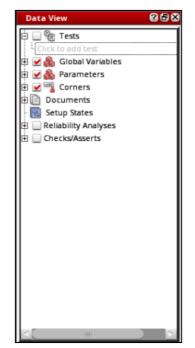

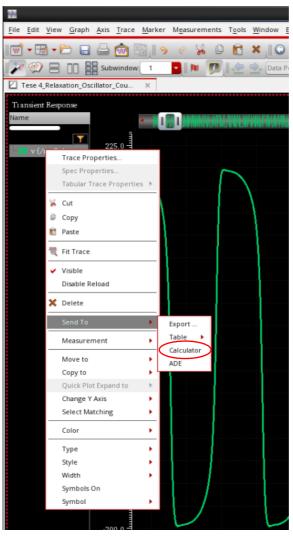

| E | 3.1 | Test set up                                                                 | 98    |

| E | 3.2 | Monte Carto sampling set up                                                 | 104   |

| С | M   | ATLAB CODE                                                                  | . 111 |

| ( | 2.1 | Plot histogram example                                                      | . 111 |

| ( | 2.2 | Plot Histogram with temperature/voltage variation example                   | 112   |

| ( | 2.3 | Plot standard variation with temperature/voltage variation graphics example | . 117 |

| ( | 2.4 | Plot jitter example                                                         | .119  |

# LIST OF FIGURES

| Figure 2.1 Shannon Entropy and Min-Entropy with the probability of the bit being 0     | and their          |

|----------------------------------------------------------------------------------------|--------------------|

| acceptable key length degradation [5]                                                  | 6                  |

| Figure 2.2 Time Measurement [10]                                                       | 8                  |

| Figure 2.3 System behavior using one pole [10]                                         | 9                  |

| Figure 2.4 Resonator circuit using a inductor and a capacitor                          | 9                  |

| Figure 2.5 Linear Oscillator block diagram [12]                                        | 10                 |

| Figure 2.6 Wien Bridge Oscillator a) Closed loop [12] b) Open loop                     | 11                 |

| Figure 2.7 Linear Oscillators a) Colpitts Oscillator [12] b) Hartley Oscillator [12]   | 13                 |

| Figure 2.8 Non-Linear Oscillator a) Integrator signal [10] b) Periodic signal [11]     | 14                 |

| Figure 2.9 Basic Relaxation Oscillator block diagram [11]                              | 15                 |

| Figure 2.10 Schmitt Trigger transfer function [15]                                     | 16                 |

| Figure 2.11 High-level model of relaxation oscillator using a Schmitt-trigger          | 16                 |

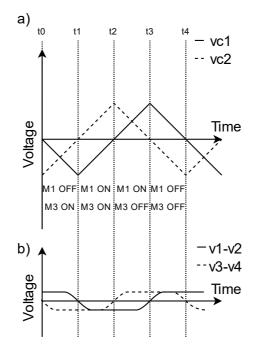

| Figure 2.12 High-level model of cross-coupled relaxation oscillator using a soft-limit | er [16].18         |

| Figure 2.13 Cross Coupled Relaxation Oscillator signals [16] a) Input (vint1) and outp | out ( <i>vsl</i> ) |

| of soft-limiter b) Integrator signal (vint1) and coupling output (v1)                  | 18                 |

| Figure 2.14 Ring oscillator [17]                                                       | 19                 |

| Figure 2.15 Inverter                                                                   | 19                 |

| Figure 2.16 Transfer function characteristic of the inverter                           | 20                 |

| Figure 2.17 Block structure of a typical PUF [22]                                      | 22                 |

| Figure 2.18 Histogram example                                                          | 26                 |

| Figure 3.1 Arbitre PUF [23]                                                            | 27                 |

| Figure 3.2 Proposed single-bit PUF cell [30]                                           | 28                 |

| Figure 3.3 SRAM cell Schematic [32]                                                    | 29                 |

| Figure 3.4 Methodology for robust SRAM-PUF [31]                                        |                    |

| Figure 3.5 Classical CMOS Relaxation oscillator schematic [23]                             | 31        |

|--------------------------------------------------------------------------------------------|-----------|

| Figure 3.6 Basic Relaxation Oscillator [23]                                                | 32        |

| Figure 3.7 Relaxation Oscillator PUF [23]                                                  | 32        |

| Figure 3.8 Simple Coupled Oscillator [35]                                                  | 33        |

| Figure 3.9 Simplified schematic of coupled chaos PUF [36]                                  | 34        |

| Figure 3.10 Conventional Ring Oscillator                                                   | 35        |

| Figure 3.11 Conventional Ring Oscillator PUF [37]                                          | 35        |

| Figure 3.12 Configurable Ring Oscillator [38]                                              | 36        |

| Figure 3.13 Configurable RO proposed by [37]                                               | 36        |

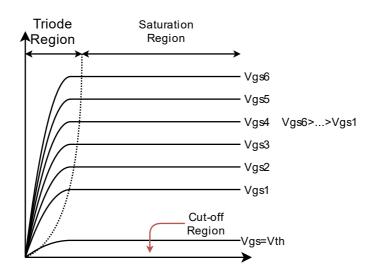

| Figure 4.1 NMOS IV characteristic curve                                                    | 40        |

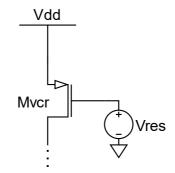

| Figure 4.2 Voltage Controlled Resistor Circuit                                             | 40        |

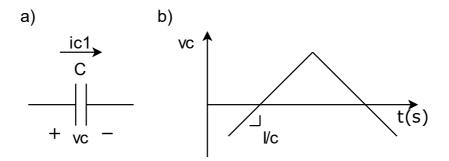

| Figure 4.3 Integrator a) Implementation b) Characteristic curve                            | 41        |

| Figure 4.4 Schmitt trigger [16] a) Circuit b) Characteristic curve                         | 42        |

| Figure 4.5 Relaxation Oscillator [16]                                                      | 43        |

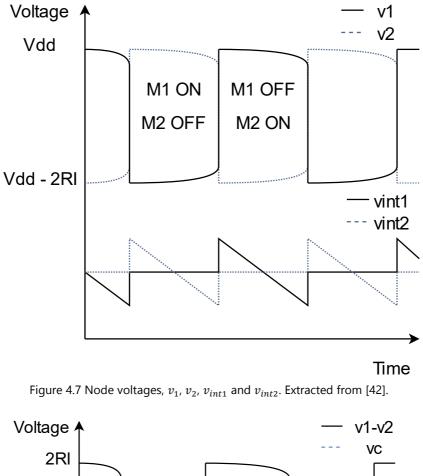

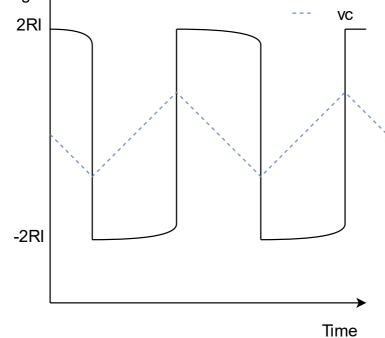

| Figure 4.6 Node voltages, v1, v2, vint1 and vint2 [41]                                     | 44        |

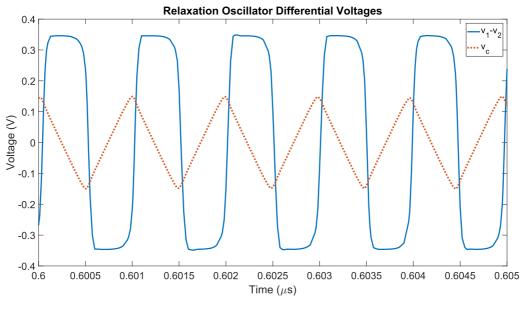

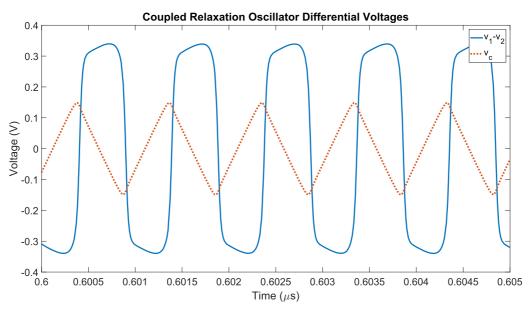

| Figure 4.7 Differential voltages $v1 - v2$ and $vc$ [41]                                   | 44        |

| Figure 4.8 Relaxation Oscillator implemented design                                        | 45        |

| Figure 4.9 Relaxation Oscillator designed differential voltages                            | 46        |

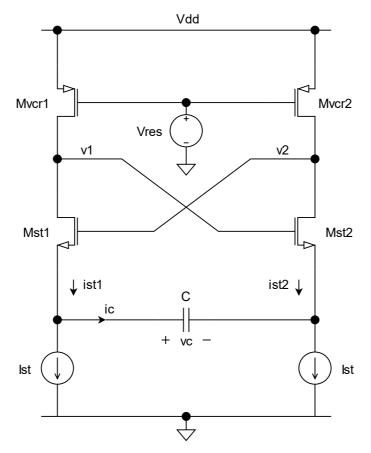

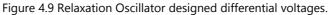

| Figure 4.10 Soft limiter implementation                                                    | 47        |

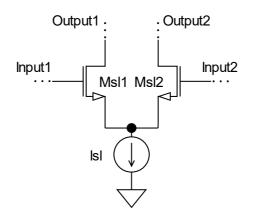

| Figure 4.11 Coupled Relaxation Oscillator architecture using two oscillators [16]          | 47        |

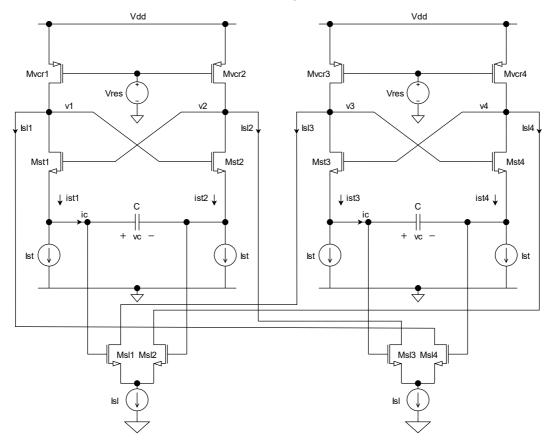

| Figure 4.12 Coupled Relaxation Oscillator differential signals a) $vc1$ and $vc2$ b) $v1-$ | v2 and    |

| v3 - v4Erro! Marcador não                                                                  | definido. |

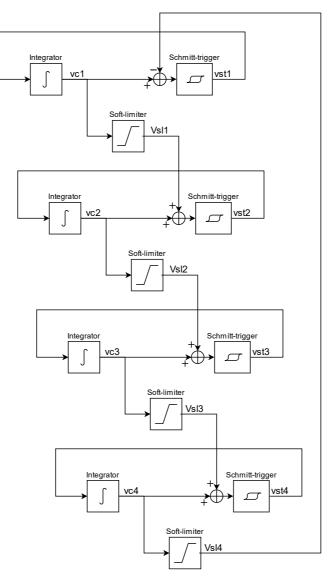

| Figure 4.13 High level model of four coupled relaxation oscillators.                       | 49        |

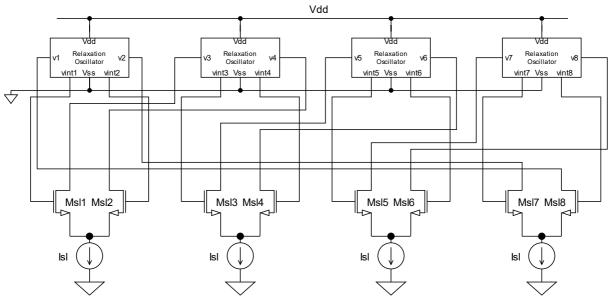

| Figure 4.14 Coupled Relaxation Oscillator implemented design                               | 50        |

| Figure 4.15 Coupled Relaxation Oscillator designed differential voltages                   | 51        |

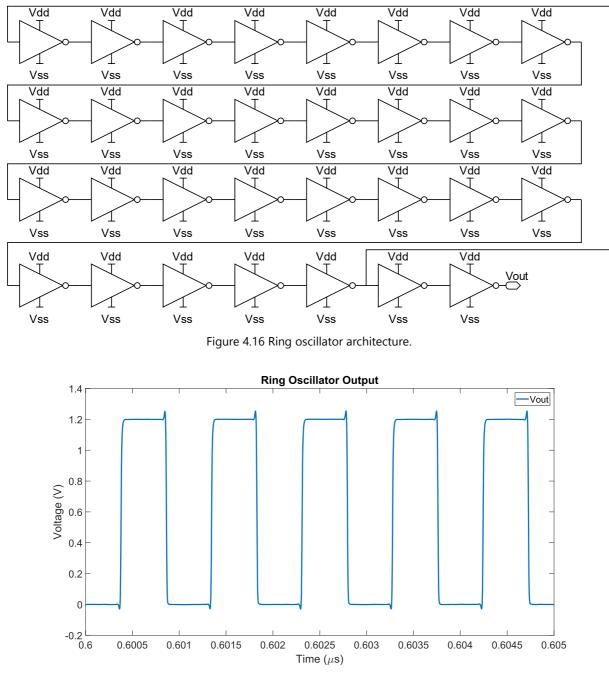

| Figure 4.16 Ring oscillator architecture                                                   | 52        |

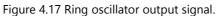

| Figure 4.17 Ring oscillator output signal                                                  | 52        |

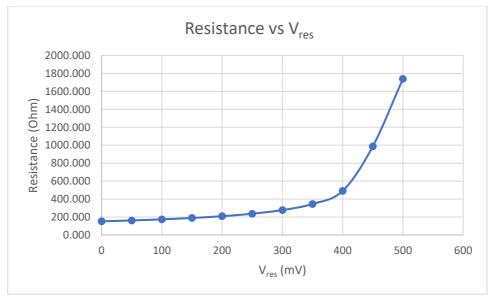

| Figure 5.1 Graphic of $R_{ds}$ and $V_{res}$                                               | 54        |

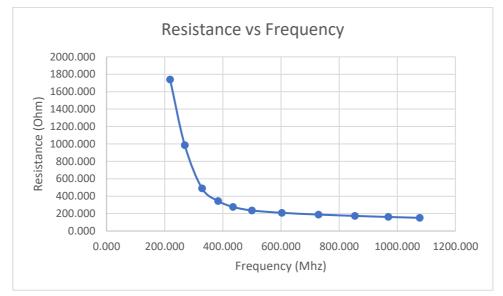

| Figure 5.2 Graphic of Rds and frequency                                                    | 55        |

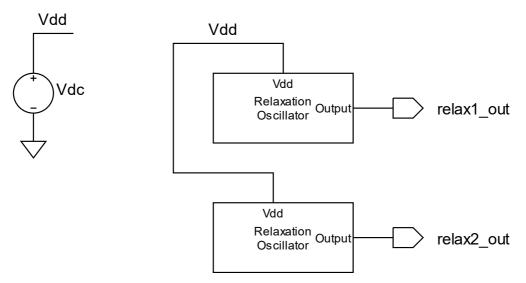

| Figure 5.3 Relaxation Oscillator entropy source test circuit                               | 58        |

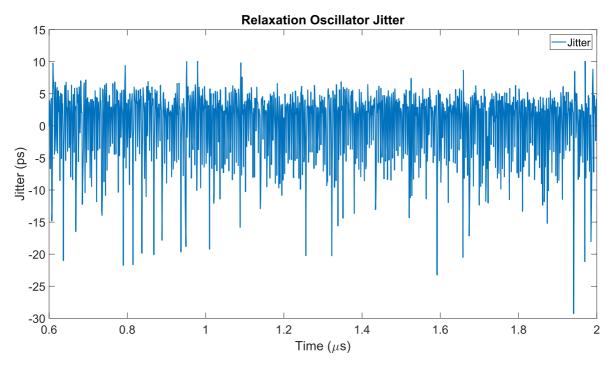

| Figure 5.4 Relaxation Oscillator period jitter                                             | 59        |

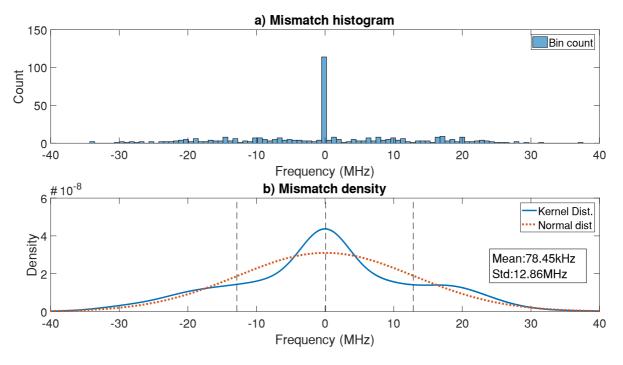

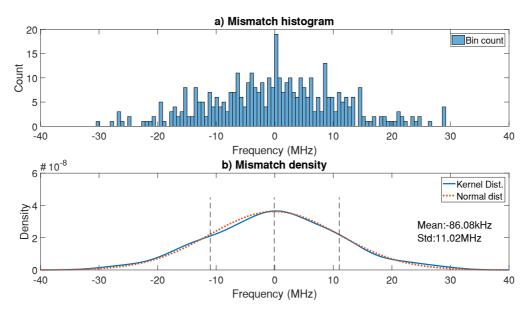

| Figure 5.5 Relaxation Oscillator a) Mismatch histogram b) Mismatch density                 | 60        |

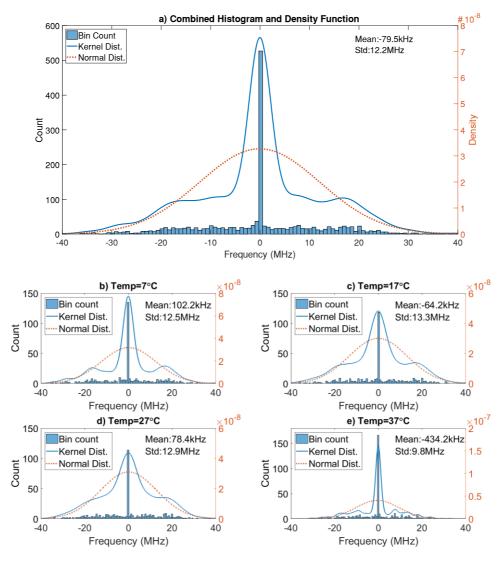

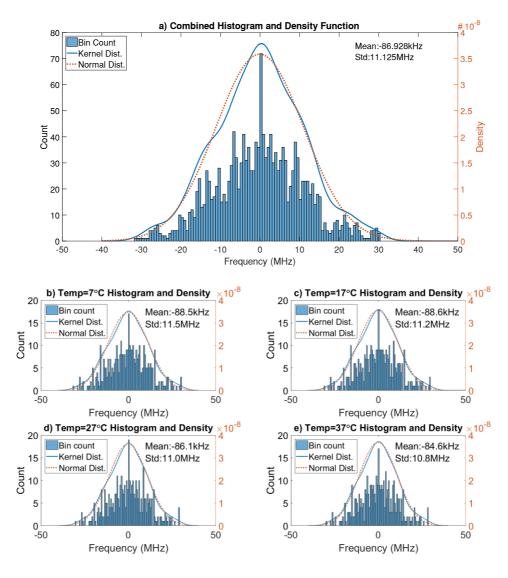

| Figure 5.6 Relaxation Oscillator temperature variation mismatch results                    | 62        |

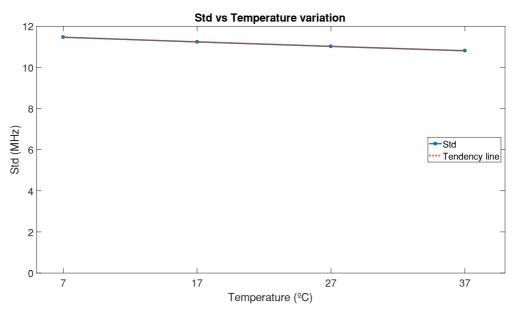

| Figure 5.7 Relaxation Oscillator temperature variation standard variation                  | 63        |

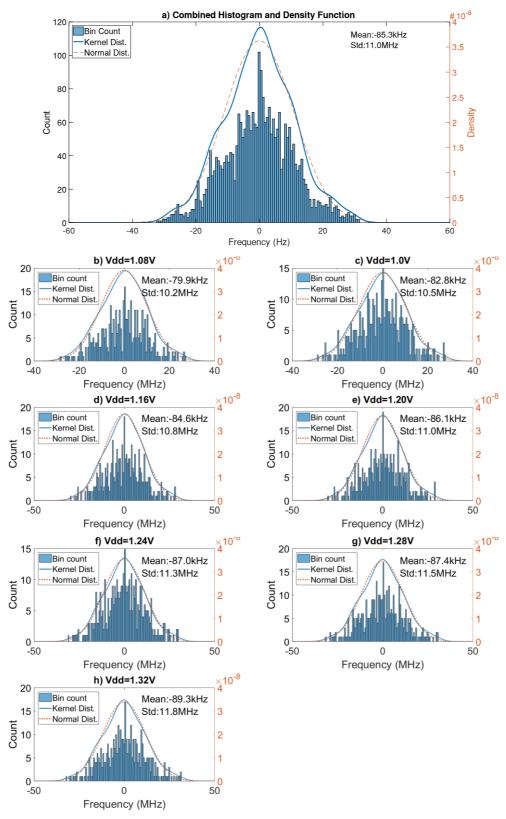

| Figure 5.8 Relaxation Oscillator supply voltage variation mismatch results            | 64 |

|---------------------------------------------------------------------------------------|----|

| Figure 5.9 Relaxation Oscillator supply voltage variation standard variation          | 65 |

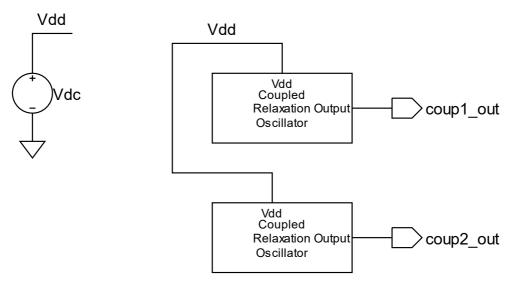

| Figure 5.10 Coupled Relaxation Oscillator entropy source test circuit                 | 66 |

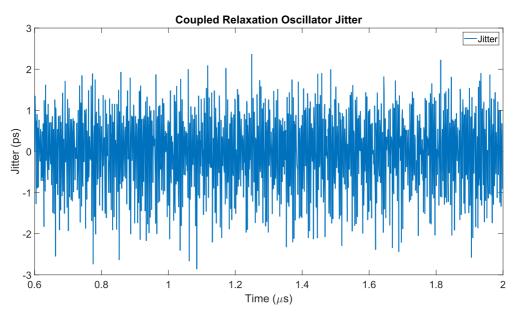

| Figure 5.11 Coupled Relaxation Oscillator period jitter                               | 67 |

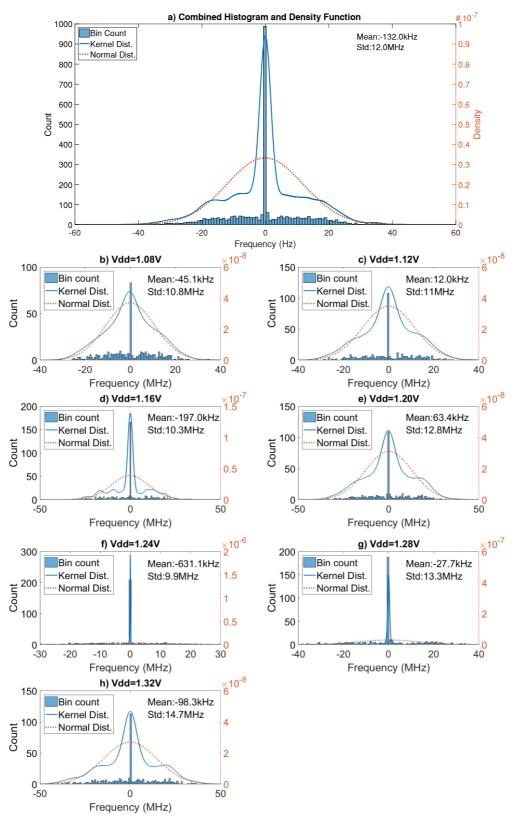

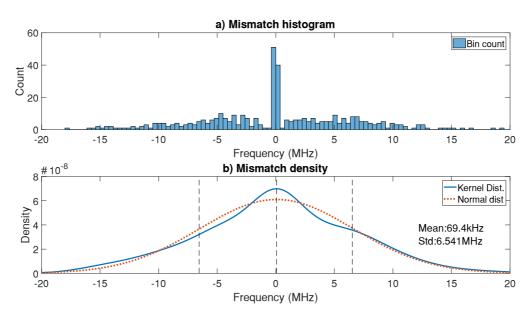

| Figure 5.12 Coupled Relaxation Oscillator a) Mismatch histogram b) Mismatch density   | 68 |

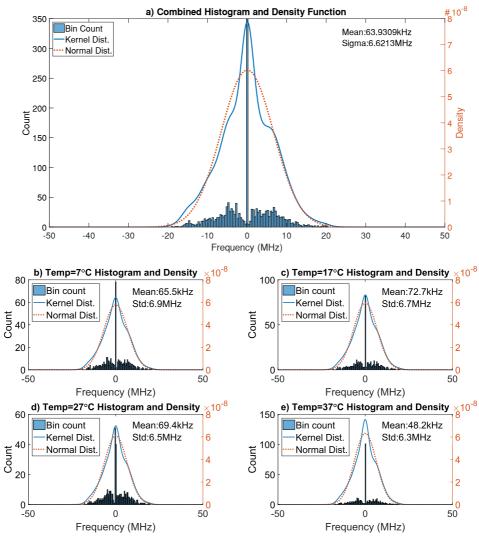

| Figure 5.13 Coupled Relaxation Oscillator temperature variation mismatch results      | 70 |

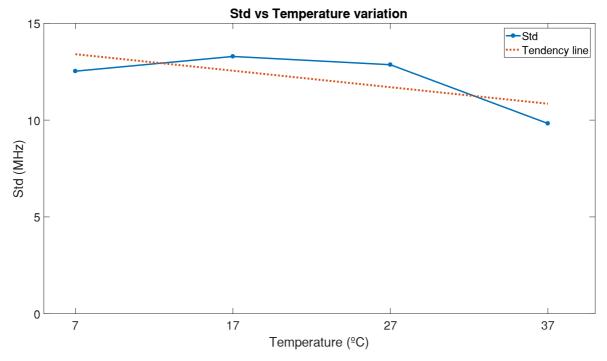

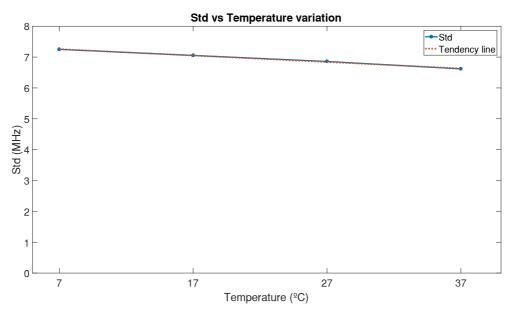

| Figure 5.14 Coupled Relaxation Oscillator temperature variation standard variation    | 71 |

| Figure 5.15 Coupled Relaxation Oscillator supply voltage variation mismatch results   | 72 |

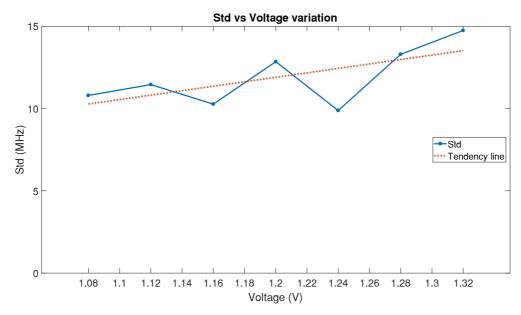

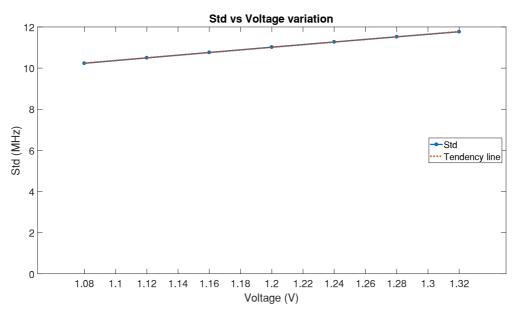

| Figure 5.16 Coupled Relaxation Oscillator supply voltage variation standard variation | 73 |

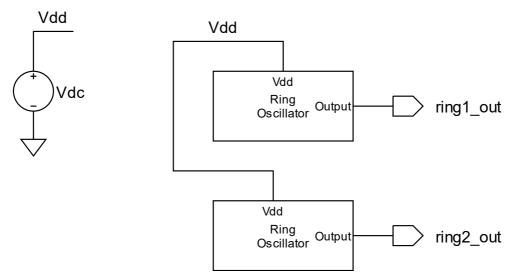

| Figure 5.17 Ring Oscillator entropy source test circuit                               | 74 |

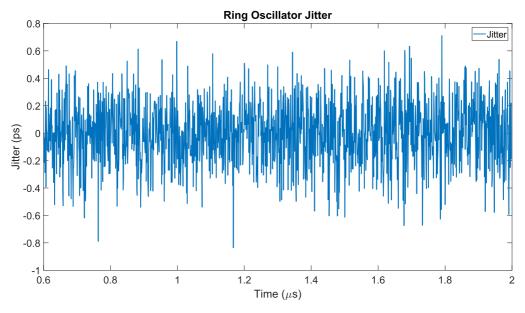

| Figure 5.18 Ring Oscillator period jitter                                             | 75 |

| Figure 5.19 Ring Oscillator a) Mismatch histogram b) Mismatch density                 | 76 |

| Figure 5.20 Ring Oscillator temperature variation mismatch results                    | 77 |

| Figure 5.21 Ring Oscillator temperature variation standard variation                  | 78 |

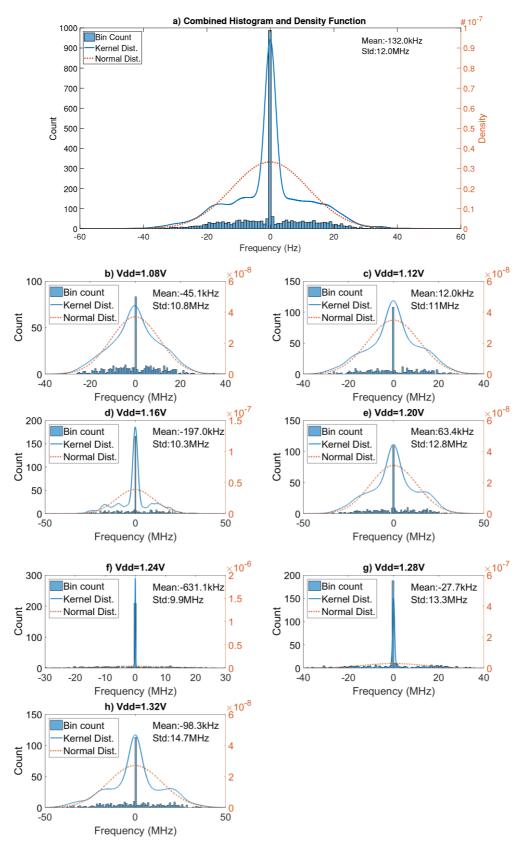

| Figure 5.22 Ring Oscillator supply voltage variation mismatch results                 | 79 |

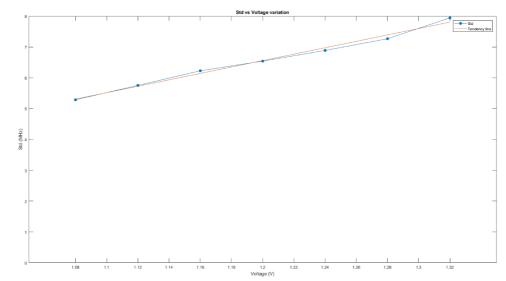

| Figure 5.23 Ring Oscillator supply voltage variation standard variation               | 80 |

# LIST OF TABLES

| Table 3.1 APUF with selecting modules performance [24]                                     | 29   |

|--------------------------------------------------------------------------------------------|------|

| Table 3.2-Relaxation Oscillator results [23]                                               | 33   |

| Table 3.3 Coupled Chaos Oscillator PUF performance [36]                                    | 34   |

| Table 3.4 Wide-Range Variation-Resilient Physically Unclonable Function [37]               | 36   |

| Table 3.5 PL-MRO-PUF performance [40]                                                      | 37   |

| Table 4.1 Relaxation Oscillator dimensioning                                               | 45   |

| Table 4.2 Coupled Relaxation Oscillator dimensioning                                       | 50   |

| Table 4.3 Ring oscillator dimensioning                                                     | 51   |

| Table 5.1 Frequency of the coupled relaxation oscillator and resistance of voltage-control | lled |

| resistance for different values of $V_{\text{res}}$                                        | 54   |

| Table 5.2 Relaxation Oscillator mismatch chi-square goodness-of-fit test results           | 61   |

| Table 5.3 Coupled Relaxation Oscillator mismatch chi-square goodness-of-fit test results.  | 69   |

| Table 5.4 Ring Oscillator mismatch chi-square goodness-of-fit test results                 | 76   |

| Table 5.5 Ring Oscillator mismatch and temperature variation chi-square goodness-of-fit    |      |

| results                                                                                    | 78   |

| Table 5.6 Ring Oscillator supply voltage variation chi-square goodness-of-fit test results | 81   |

| Table 5.7 Area comparison of the oscillators studied                                       | 81   |

| Table 5.8 Power consumption comparison of the oscillators studied                          | 82   |

| Table 5.9 Period jitter comparison of the oscillators studied                              | 83   |

| Table 5.10 Entropy comparison of the oscillators studied                                   | 83   |

| Table 5.11 Temperature variation standard deviation comparison of the oscillators studied  | d84  |

|                                                                                            |      |

# ACRONYMS

| CMOS   | Complementary Metal-Oxide-Semiconductor       |

|--------|-----------------------------------------------|

| CRP    | Challenge-Response Pair                       |

| Cusums | Cumulative Sums                               |

| HD     | Hamming Distance                              |

| loT    | Internet of things                            |

| NBTI   | Negative-Bias-Temperature-Instability         |

| NIST   | National Institute of Standard and Technology |

| NMOS   | N-channel Metal-Oxide-Semiconductor           |

| NVM    | Non-Volatile Memory                           |

| ΡΚΙ    | Public Key Infrastructure                     |

| PMOS   | P-channel Metal-Oxide-Semiconductor           |

| PRNG   | Pseudo Random Number Generator                |

| PUF    | Physical Unclonable Function                  |

| RNG    | Random Number Generator                       |

| RO     | Ring Oscillator                               |

| SRAM   | Static Random-Access Memory                   |

| TRNG   | True Random Number Generator                  |

| VCR    | Voltage Controlled Resistor                   |

VTC Voltage Transfer Characteristics

## INTRODUCTION

#### 1.1 Motivation

Internet of Things (IoT) managed to integrate wireless communication into our daily lives. IoT enables a lot of devices from sensors to automobiles to communicate with each other and share their data. IoT systems are embedded in our daily lives in various forms. The vast areas of application, for example, the transport sector, healthcare, industry, blockchain, and building smart atmospheres are enabling a general digital transformation. While IoT networks certainly improved the quality of our lives allowing for new and enhanced services, exponential growth, power and computing limitations, high mobility, and communication, introduce an unprecedented number of security threats while allowing for attacks to propagate quickly through the network [2].

Several causes constrain the security of IoT devices including limited energy available, limiting computing resources, and the heterogeneous nature of the network [3]. The energy and computing constrain of IoT devices do not allow for the implementation of heavy cryptography and security protocols used on normal networks. The scale of IoT devices opens chances for careless programming which is a gateway for malware and backdoors schemes. The heterogeneous nature of the network results in dissevered security, identification, and authentication standards, which, increases the complexity of the security challenge [4].

The characteristic stated above, and the estimate of 75 billion IoT devices connected by the year 2025 result in the inefficient performance of conventional security mechanisms, leading to crucial information being unsecured [5]. Unsafe data can have major costs to our lives thus, the information must be received and sent to an authenticated user. Also, for example, e-wallets for cryptocurrencies work by storing the private keys that are necessary to manage the cryptocurrency account as proof of public key ownership, allowing the user to do payments and transfers, the economic value such e-wallets may hold is very high thus, need high levels of security.

Security services should ensure confidentiality, only the authorized users can read the data; integrity, the data sent cannot be manipulated; authentication, confirmation of identity; nonrepudiation, no other user have sent the information; digital signature, verify the integrity, perform authentication and nonrepudiation [6].

These services are achieved through cryptographic keys and algorithms used between the sender and the receiver. Encryption by itself does not guarantee security, so does not provide enough integrity. Simply encrypted messages can be decrypted, also, third parties can still transmit encrypted packets in the network. A widely used encryption method is called public key infrastructure (PKI). PKI systems use two types of keys, public and private, as the name suggests, private keys are kept secret while public keys are known by the public where one key is used com encryption and the other for decryption. The private key should be reliable, robust, and perfectly reproducible [5]. Because of those characteristics, the keys are usually stored in the non-volatile memory (NVM) however this kind of memory is vulnerable to physical attacks.

There are two main types of solutions, hardware-based and software-based solutions.

• The software-based solution is the most common solution on traditional networks, they rely on software that is based on mathematical methods to protect the information sent. However, because they are based on mathematical methods (e.g., a discrete logarithmic problem), they require processing and memory power, resources often scarce on IoT which may lead to poorer methods implemented thus, less security [5]. A software-based solution might not be the best option for IoT devices. Also, this kind of procedure is effective as a security measurement because the logarithmic problems are not easily solved using today's computers however with the increase of computing power and quantum computers, these kinds of security mechanisms will become obsolete.

• Hardware-based solutions can be achieved using a dedicated integrated circuit as systems on chip (SoC) to perform cryptography and store keys. Because data is stored and generated by the physical properties of the chip instead of memory and software, this solution can prevent read-and-write access to data and is more resilient against other attacks. [5] Also, since is designed as an integrated circuit, it is possible to reduce power consumption and improve encryption. One of the main disadvantages of hardware-based security solutions is that they are susceptible to physical attacks where if the chip is stolen, attackers can clone the device which means they can clone the key and get access to the information originally secured.

2

However, physically unclonable functions (PUFs) and true random generators (TRNGs) can solve the previously stated problem.

#### 1.2 Proposed goals

The main goal of this work is to implement a static entropy source based on coupled oscillators using CMOS 130nm technology. To study its properties using already established tests, and to compare the results obtained with state-of-the-art architecture. To achieve the main objective of implementing a static entropy, the following goals were set:

- Review the most common PUF configurations

- Review oscillators

- Understand statistical tests to evaluate PUFs

- Implement static entropy source based on coupled oscillators

- Study the implemented static entropy source

- Compare the designed static entropy source with state-of-the-art implementations

### 1.3 Contributions

In this dissertation a static entropy source based on coupled relaxation oscillator was developed using advanced 130nm technology. This static entropy source can be used to be part of a PUF.

Compared to the state-of-the-art implementation, the ring oscillator static entropy source, the coupled relaxation static entropy source, it did not perform up to expectations in terms of area, power consumption and entropy. However, it showed promising results when under temperature and supply voltage variations showing it can be robust under such variations.

Even though the circuit did not perform up to par against the ring oscillator, the results show that that this circuit has potential as a static entropy source. Thus, further study is needed to improve the static entropy source developed.

#### 1.4 Report Structure

This work is divided into six chapters, structures as follows.

Chapter 1 presents the subject being researched as well as the motivation behind the search for a new solution by also listing the goals for the dissertation.

Chapter 2 is theoretical explanation useful for the understanding of the work developed of this dissertation.

Chapter 3 is an overview of the current state-of-the-art. Explores basic concepts of PUFs and statistical tests to evaluate the latter and, shows some previous scientific work.

Chapter 4 is where the work developed is presented, the circuits used and respective dimensioning.

Chapter 5, the results obtained from the work developed in Chapter 4 are revealed, also a discussion and comparison of such results.

Finally, Chapter 6, the final conclusions about the work accomplished are drawn. And some potential future work is discussed.

# 2

## BACKGROUND

#### 2.1 Entropy

The entropy applied to key generation was explained by M. Alioto [6]. Key generation is crucial for secure systems for examples for cryptographic operations or to identify and authenticate devices. The key generation can be generated from static entropy for applications where the secret key only needs to be generated once or generated from dynamic entropy for applications where the secret key needs to be fresh every time the system requires a key.

The secure strength of a determined key can be measured by the number of possible key guesses. Because the key is binary, the number of key guesses and consequently the secure strength is

Strength of the System =

$$2^{keylength \cdot entropy}$$

(2.1)

Entropy is the amount of information held by each bit. A bit represents two values, 0 and 1, so, ideally, for random key generation every bit must have the same probability of being generated. Entropy categorized as a value that ranges from 0 to 1. An entropy of 0 represents no information which translates to a perfectly predictable value which mean the probability generating a bit 0 (Pr[0]) is either 0% or 100%. A perfectly random key has an entropy of 1 which means Pr[0] = 0.5, thus, Pr[1] = 0.5. In practical systems Pr[0] is not exactly 0.5, this means the entropy will be less than 1 thus reducing the effective keylength [*keylength* · *entropy*] consequently degrading the strength of the system as show by equation (2.1).

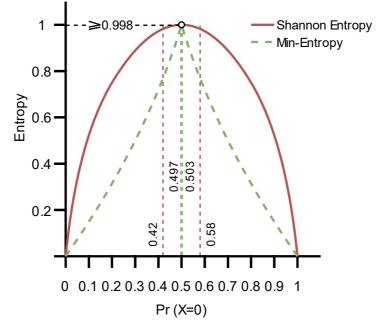

Depending on the application, entropy can be defined in various ways for example by the Shannon entropy and the Min-entropy.

For moderately strict security requirements the Shannon entropy is popularly used. The Shannon entropy was first defined by Shannon [7] and it states that in the case of bit generation where there are only two possibilities with probabilities p and q = 1 - p, the entropy is  $entropy = -(p \log p + q \log q)$

(2.2)

Plotted in Figure 2.1. The entropy is considered adequate when the effective key length is degraded by less than 1bit. For a 256-bit key this means the acceptable entropy is given by  $256 : entropy \ge 255.5 \Leftrightarrow$

$$\Leftrightarrow entropy \ge \frac{255.5}{256} \Leftrightarrow$$

$$entropy \ge 0.998$$

For a 256-bit key, following the Shannon entropy, the minimum acceptable entropy is 0.998, following equation (2.2), this translates to  $0.42 \le \Pr[0] \le 0.58$ .

Figure 2.1 Shannon Entropy and Min-Entropy with the probability of the bit being 0 and their acceptable key length degradation. Extracted from [6].

The Min-entropy is a measure of the key unpredictability, defined by Renner. R and Wolf. S [8]. It is described as the probability of successfully guessing a certain key, a 1-bit key has a 50% chance of guessing the right value. For Min-entropy, the entropy target of 0.998 converts to a more stringent requirement,  $0.497 \le \Pr[0] \le 0.503$ . The Min-entropy is plotted in Figure 2.1.

Both Shannon entropy and Min-entropy dictate the acceptable 0/1 bias of circuit implementations for static and dynamic entropy.

#### 2.1.1 Static Entropy

As explained by Alioto [6]. Static entropy is used to generate fixed keys thus, it is the desired entropy for PUFs. The generation of random fixed keys is essential in hardware security and is mostly used as chip ID to identify a device and for the protection of software intellectual property. Conventionally, static entropy is generated off-chip and then stored in a nonvolatile manner, for example, fuses and flash memories. However, such ways to store the key are vulnerable to a large well-known attack at the software level and as well physical attacks.

To generate the same challenge, the generator needs to be resilient to aging, temperature, and voltage oscillations effect to decrease undesirable variations. Instead, the entropy can be derived from the physical differences between transistors originating from the process and mismatch variations [9].

#### 2.1.2 Dynamic Entropy

By Alioto [6], Dynamic entropy is used by RNGs to generate new random keys whenever a new key is needed. RNGs can be divided into TRNGs and PRNGs. TRNGs use random physical processes to generate a random number and thus are much more secure because there is no correlation between numbers. PRNG uses deterministic systems to generate random numbers, thus, every generated key is correlated and by understanding how the system works, it is possible to predict the next number to be generated.

#### 2.2 Oscillators

An electronic oscillator is a circuit designed to generate a periodic signal out of constants, oscillators can be linear (sinusoidal) or non-linear (non-sinusoidal/relaxation) [10]. This means the oscillator translates energy from the DC power to generate a periodic signal with a certain frequency and amplitude, AC power, determined by the oscillator itself [11].

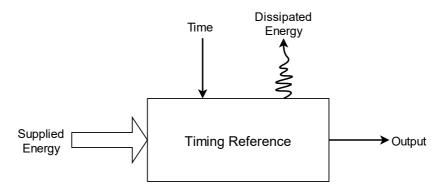

Since the oscillator generates a periodical signal from constants, it needs to have a time reference in its system. A time reference is a system that can generate an output signal through a known time behavior as shown in Figure 2.2.

Figure 2.2 Time Measurement. Extracted from [11].

In the previous figure, time is used to quantify the variation of the system over time. At the input, energy is supplied for the system to operate, in a system with no energy dissipated, energy only must be supplied to start the system, however, if dissipated energy is considered energy needs to be continuously supplied. At the output, the influence of time on the system is measured [11].

Oscillators can be classified by the pole pattern which characterizes their timing reference, this makes it easy to observe the properties of the oscillation.

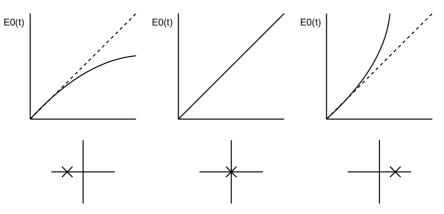

First-order oscillators will have the pole located in the real axis, if this pole is in the origin, the system is an ideal integrator, when a constant is applied to the input of that integrator, the output signal changes linearly with time, thus, a time-variant signal with a well-known time behavior is created. When there is a constant input signal  $\alpha$  in the integrator and  $E_o(t)$  on the output, then:

$$E_0(t) = \int_0^t \alpha \, d\tau$$

For a constant input, the ideal integrator will output a linear time-varying signal. In an electrical circuit, an example of an integrator is the capacitor [12]. However, in a real system, the integrator is not ideal, thus, the pole will not be centered on the origin, and thus there is no longer a linear relationship between the constant input and the output. If the pole is shifted to the right of the origin,  $E_0(t)$  will increase exponentially. If the pole is shifted to the left plane,  $E_0(t)$ , the slope will decrease over time showing the presence of losses in the system and the oscillation is damped [12]. Also, this kind of oscillator needs additional steps to obtain an oscillation because the integrator by itself does not change the signal of the constant meaning it integrates linearly to infinity[12]. The pole interaction with the system in a first-order oscillator can be seen in Figure 2.3.

Figure 2.3 System behavior using one pole [11].

This kind of oscillator, due to its nature is used to create non-sinusoidal signals originating from the relaxation oscillator.

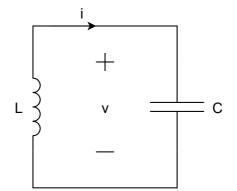

Second-order oscillators have two dominant poles in the imaginary axis, when this pole is in the imaginary axis, the output signal is stable in amplitude and frequency. This kind of oscillator does not need additional steps to generate oscillations, the oscillation happens naturally. The time-varying signal is achieved using a resonator. A resonator is a second-order device that oscillates at a resonant frequency defined by its components. An ideal LC resonant circuit is shown in Figure 2.4.

Figure 2.4 Resonator circuit using a inductor and a capacitor.

Ideally, this kind of circuit functions by connecting a charged capacitor to an inductor. The charged capacitor has an electric field between its plates which will result in a voltage across the capacitor. Since the inductor acts as a load, this voltage will drive current through the inductor increasing its magnetic field. As the voltage across the capacitor reaches close to zero and because magnetic fields oppose current changes, a voltage across the inductor is induced which will induce a current to charge the capacitor. In this kind of circuit, the resonator will oscillate with a frequency given by:

$$f_0 = \frac{\omega_0}{2\pi} = \frac{1}{2\pi\sqrt{LC}}$$

Thus, the values of inductance and capacitance will determine the pole placements.

Because this kind of oscillator oscillates naturally, it creates a sinusoidal signal thus second-order oscillators are used to produce linear oscillators.

Third-order oscillators contain three poles. Two poles on the imaginary axis like the second order oscillator and a third pole in the real axis like the first order oscillator, like in the first oscillator, this pole will usually be on the left side of the plane meaning it has a positive real part which indicates the presence of losses in the system [12].

### 2.2.1 Linear Oscillator

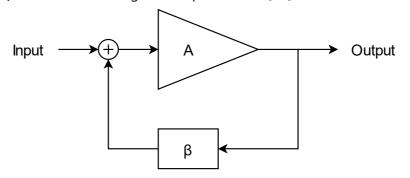

Linear oscillators produce a sinusoidal signal. A conventional block diagram of a linear oscillator is shown in Figure 2.5 which contains an amplifier block of gain A and a frequency selective second-order feedback block with gain  $\beta$ . The feedback block can be composed of an RC circuit or LC circuit. This kind of oscillator can be analyzed using the Barkhausen criteria.

The Barkhausen criterion is a mathematical condition that characterized the region of oscillatory instability of linear oscillators with a feedback loop, it was established by studying the poles of the system and their relation to the oscillator behavior by reducing complex equations into two real variables [13]–[15]. Analyzing the linear oscillator represented by Figure 2.5 using the Barkhausen criteria, the necessary conditions to generate a sinusoidal oscillation, are  $|A\beta| = 1$  and  $\angle A\beta = 2k\pi$ , or an integral multiple of 360° [13].

Figure 2.5 Linear Oscillator block diagram. Extracted from [13].

The following information about the Barkhausen criterion and feedback loop is based on [14]. To achieve the desired phase shift, reactive elements must be used in the feedback loop, since reactive elements have a resonance frequency, the phase shift is dependent on the reactive element's resonance frequency. Meaning the Barkhausen criterion is only satisfied at this natural frequency. If  $|A\beta| < 1$ , the oscillation will decay over time until it perishes. If  $|A\beta| > 1$ , every time the signal goes through the feedback loop it will increase in amplitude, thus the oscillation will be increasingly higher in amplitude, this increase is only limited by the power

supply of the oscillator and can lead to a nonlinear operation. In practical oscillators, the loop gain,  $|A\beta|$ , need to be slightly higher than 1 to compensate for the noise and/or variations in transistor and circuit parameters. The Barkhausen criterion is only applicable to linear oscillators, this means it can only be utilized for sinusoidal oscillators like the Wien Bridge Oscillator, the Colpitts and Hartley Oscillator, these following examples are based on Senani *et.al* [13], and Schubert and Ernest [14] explanations.

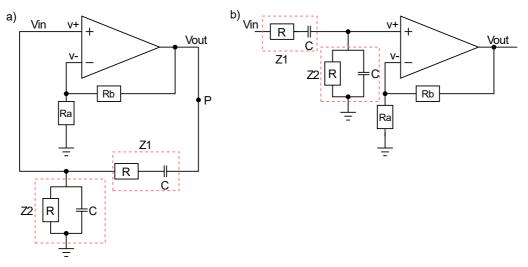

The Wien Bridge Oscillator as shown by the circuit of Figure 2.6 a), is a type of RC oscillator and it uses an op-amp as the non-inverting amplifier and the reactive feedback loop is composed of a series-shunt topology using two resistors and two capacitors forming a secondorder band-pass filter, the resulting center frequency is

$$\omega_0 = \frac{1}{RC} \tag{2.3}$$

The center frequency it's chosen such that the phase shift of the band-pass filter becomes zero. Since the non-inverting amplifier does not have a phase shift, the total phase shift around the loop is zero.

Figure 2.6 Wien Bridge Oscillator. a) Closed loop. Extracted from [13]. b) Open loop.

Because the band-pass filter is passive, it will have a voltage gain smaller than 1, the noninverting amplifier must have a voltage gain equal to  $\frac{1}{band-pass filter \ voltage \ gain}$ .

The open-loop circuit is shown in Figure 2.6 b). Following the ideal op-amp model:

- The infinite input impedance of the op-amp

- Infinite open-loop gain

- Zero offset

- $V_{out} = A.(v^+ v^-)$

The open-loop transfer function can be obtained as a relation between the op-amp loop and the feedback network.

$$\frac{V_{out}}{V_{in}} = \frac{Z_1}{Z_1 + Z_2} \times \left(1 + \frac{R_b}{R_a}\right) \Leftrightarrow$$

$$\Leftrightarrow \frac{V_{out}}{V_{in}} = \frac{sCR \times \left(1 + \frac{R_b}{R_a}\right)}{s^2 C^2 R^2 + 3sCR + 1} = A\beta$$

Following the Barkhausen criteria stated before, the necessary conditions for oscillation are  $|A\beta| = 1$  and  $\angle A\beta = 0$  which results in

$$|A\beta| = \left| \frac{sCR \times \left(1 + \frac{R_b}{R_a}\right)}{s^2 C^2 R^2 + 3sCR + 1} \right| = 1$$

And

$$\phi = \arctan(\infty) - \arctan\left(\frac{3\omega RC}{1 - \omega^2 R^2 C^2}\right) = 0$$

For  $s = j\omega$  and the frequency of oscillation ( $\omega$ ) given by equation (2.3),

$$|A\beta| = \left|\frac{\left(1 + \frac{R_b}{R_a}\right)}{3}\right| = 1$$

Thus,

$$\left(1 + \frac{R_b}{R_a}\right) = 3$$

And the condition of the oscillation is given by

$$\frac{R_b}{R_a} = 2$$

Which is the ration of  $R_b$  and  $R_a$ .

The Colpitts and Hartley Oscillators are the two most used LC Oscillators. This type of oscillator is more suitable for high-frequency applications compared to RC Oscillators. Despite RC Oscillators having more power dissipated compared to LC oscillators, due to the resistance, these are preferred over LC in low frequencies because of the major downside of using inductors in integrated circuits, their size, however, since the frequency and the inductor size is inversely related, in high frequencies the use of inductor becomes acceptable thus LC oscillators are preferred over RC oscillators in high frequencies.

Figure 2.7 Linear Oscillators. Extracted from [13]. a) Colpitts Oscillator. b) Hartley Oscillator.

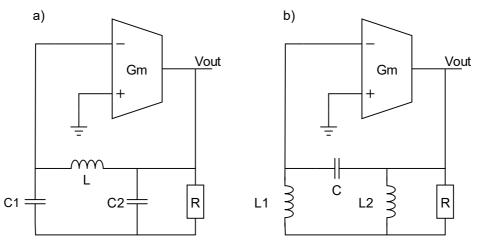

The Colpitts and Hartley Oscillators with an OTA-based implementation are shown in Figure 2.7 a) and Figure 2.7 b) respectively. In this example, it is used an inverting OTA-amplifier with a gain of  $-G_m$ . As reactive feedback loops an LC circuit.

Analyzing the Colpitts Oscillator represented by Figure 2.7 a), the frequency of oscillation is given by

$$f_0 = \frac{1}{2\pi\sqrt{LC_T}}$$

And  $C_T$  is

$$C_T = \frac{C_1 \times C_2}{C_1 + C_2}$$

The condition required to maintain oscillation following the Barkhausen criterion,  $|A\beta| = 1$  and  $\angle A\beta = 0$ , are given by

$$g_m R \ge \frac{C_1}{C_2}$$

For the Hartley oscillator, the capacitors are switched by inductors and vice versa as represented by Figure 2.7 b), the oscillation of frequency is

$$f_0 = \frac{1}{2\pi\sqrt{L_TC}}$$

And  $L_T$  is

$$L_T = L_1 + L_2$$

Finally, the condition of oscillation is

$$g_m R \ge \frac{L_1}{L_2}$$

## 2.2.2 Non-Linear/Relaxation Oscillator

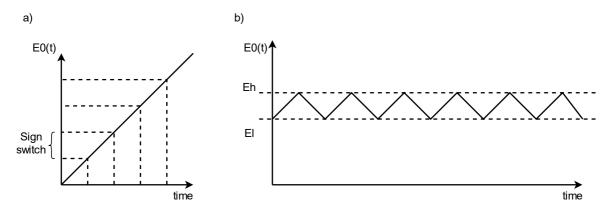

Relaxation oscillators are oscillators that produce a non-sinusoidal signal such as a triangle or square wave. In Relaxation oscillators, only one pole is used in the timing reference. However as discussed before in this Chapter, this is not enough to create a periodical signal with a specific frequency. To counteract this problem additional components are needed to change the signal of the integration constant.

As described by Westra [11] and Verhoeven [12]. To generate a periodic signal, the signal of the integrator is measured, and depending on the sign of the integration constant, the signal will be increasing or decreasing. Then the signal is compared either by a bottom limit ( $E_l$ ) or an upper limit ( $E_h$ ), when the signal reaches either threshold, the sign is changed. To change the sign of the integrator, the system needs feedback, and the sign of integration is stored in a memory. With this procedure it is possible to go from a time-varying signal like the one in Figure 2.8 a) to the periodical signal in Figure 2.8 b).

Figure 2.8 Non-Linear Oscillator. a) Integrator signal. Extracted from [11]. b) Periodic signal. Extracted from [12].

Relaxation oscillators have four crucial functions:

- Integration

- Comparison

- Switching the sign of the integration constant

- Memorization

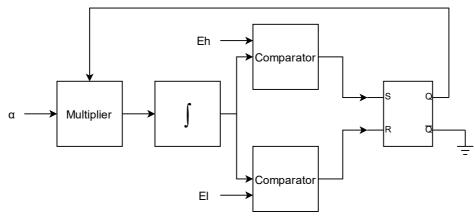

From the functions stated above, using a block diagram, it is possible to model an oscillator where each block represents each function like the one depicted in Figure 2.9.

Figure 2.9 Basic Relaxation Oscillator block diagram. Extracted from [12].

The oscillator represented in Figure 2.9, is the basic regenerative oscillator. As explained by Westra [11], starting from left to right, the multiplier is responsible for switching the sign of the integration constant which will determine which reference  $E_h$  or  $E_l$  the signal,  $E_o(t)$ , is changing to. The two reference levels are constant and define the top and bottom limits of the signal as shown in Figure 2.8 b), level comparison is done by two comparators both connected to a latch. The flip-flop is the memory element, depending on the comparator output, the latch will output either 1 or -1 in other to determine the sign of the constant. The output of the latch is then injected back into the multiplier which will change or not the integration constant.

To reduce the complexity of the oscillator, the number of blocks can be reduced using elements that produce several of the necessary functions. Using fewer blocks simplifies the bias of the circuit the latter may have better speed performances. This reduction can be achieved utilizing a Schmitt trigger.

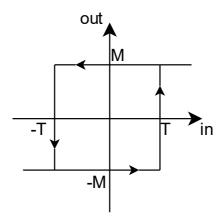

The Schmitt trigger has a hysteresis-like behavior as shown in Figure 2.10. It has two stable states (M and -M) and an internal reference signal with two different values (T and -T), when the input signal is equal to or higher than the reference level, the Schmitt trigger switches state.

Figure 2.10 Schmitt Trigger transfer function. Extracted from [16].

As described by Verhoeven [12]. The Schmitt trigger is also a memory element as when it reaches a certain state, it maintains the output if the input doesn't reach the reference signal respective to the other state. Because the stable states output opposite values, those can be used as the integration constant  $\alpha$  and  $-\alpha$  thus, the multiplier element is no longer needed. The Schmitt trigger can perform the functions of comparison, switching the sign of integration and the memory.

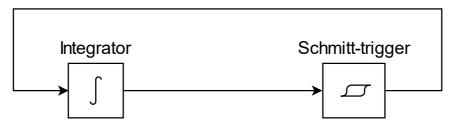

One of the simplest first-order oscillators can be built by only using an integrator and a Schmitt trigger. In Figure 2.11, a high-level model of this relaxation oscillator is depicted using a block diagram.

Figure 2.11 High-level model of relaxation oscillator using a Schmitt-trigger.

The relaxation oscillator in Figure 2.9 is optimized easily since every block can be optimized for the only function it performs and one miss-optimization will have less influence on another component. However, its complexity is a big downside of this oscillator and due to the number of components, it may have speed problems and the bias might be complicated. In the relaxation oscillator in Figure 2.11 the optimization will be more complicated. However, it is a much simpler implementation and easier to bias.

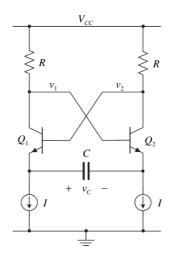

### 2.2.3 Non-Linear/Relaxation Coupled Oscillator

As described by Westra and Verhoeven [11], [12]. When an external signal has a welldefined time behavior it can be used to influence the timing of a first-order oscillator. Then, the timing properties of the external signal will be taken over by the first order oscillator and the periodic signal generated will be related to the external signal. Since oscillators output a signal with a well-defined time behavior, it is possible to synchronize two first-order oscillators to each other. The signal from the first oscillator is used to synchronize the second oscillator and the signal from the second oscillator can be used to synchronize the first oscillator. This is what is called a coupled system.

Coupling oscillators is done to improve the noise behavior. In coupled oscillators, the carriers from both oscillators become strongly correlated and most noise sources remain un-correlated. If all noise sources and uncorrelated, the noise power is reduced by half.

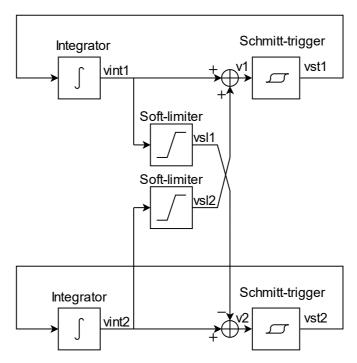

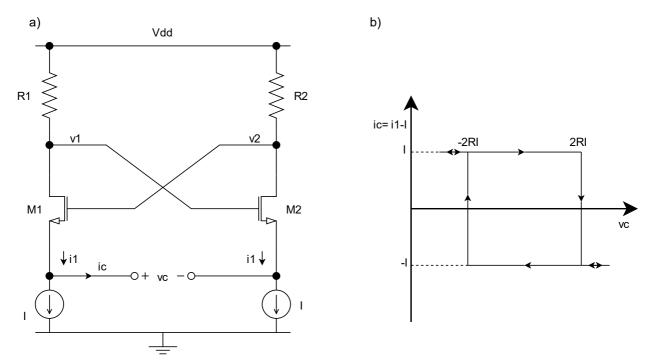

The following coupling explanation is based on the work of Luis Oliveira [17]. By adding a soft limiter after the integrator of the relaxation oscillator depicted in Figure 2.11, a new output with a 90° phase difference compared to the output of the Schmitt trigger is obtained. Represented by Figure 2.12, the soft-limiter output can be used to synchronize a second oscillator and the soft-limiter output of this second oscillator can be used to synchronize the first oscillator. By coupling two oscillators this way, a regenerative cross-coupled quadrature relaxation oscillator is obtained.

Figure 2.12 High-level model of cross-coupled relaxation oscillator using a soft-limiter. Extracted from [17].

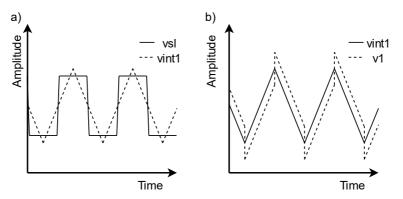

In a cross-coupled oscillator, there is not a master nor a slave oscillator, the balance is achieved by both oscillators. Both oscillators are designed to operate at the same frequency and due to the soft limiter, the output at each Schmitt trigger will be in quadrature. Since the soft limiter is an amplifier with saturation, the input signal gets amplified ( $v_{int}$ ) however, due to the saturation, the output will resemble a square ( $v_{sl}$ ) as shown in Figure 2.13 a). The soft limiter output is added to the integrator output signal of the other oscillator, this will create a stepper slope in the transition region as shown by  $v_1$  in Figure 2.13 b).

Figure 2.13 Cross Coupled Relaxation Oscillator signals. Extracted from [17]. a) Input ( $v_{int1}$ ) and output ( $v_{sl}$ ) of soft limiter. b) Integrator signal ( $v_{int1}$ ) and coupling output ( $v_1$ ).

The signal before the soft limiter is  $v_{int1}$  and after is  $v_1$ . This stepper slope enables the switching time to be less sensitive to noise. Higher soft limiter gain minimizes the influence of noise on the transition time.

## 2.2.4 Ring Oscillator

As described by Silva, Manuel [18] and Charan Sarkar et al.[19] .This oscillator is especially appealing because of its simplicity, it is easily designed in state-of-the-art technologies for example CMOS, it can achieve high-frequency oscillations at a low power cost, and it can provide outputs at different phases.

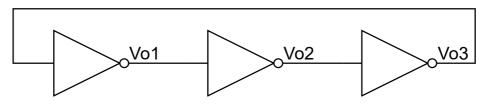

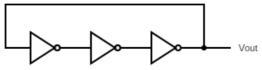

The ring oscillator is composed of n odd number of inverters connected as shown in Figure 2.14.

Figure 2.14 Ring oscillator. Extracted from [18].

Each inverter delivers an output that is phase shifted by  $\frac{\pi}{n}$  compared to the previous inverter output.

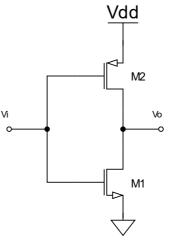

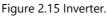

The singled-ended ring oscillator consists of inverters containing a PMOS and an NMOS transistor as shown in Figure 2.15. Both transistors perform switching between ON and OFF.

The transistor  $M_1$  is responsible for the pull-down transition and the transistor  $M_2$  is responsible for the pull-up transition.

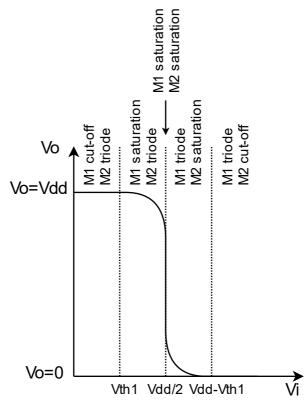

Figure 2.16 Transfer function characteristic of the inverter.

The transfer function characteristic of the inverter is in Figure 2.16. When v<sub>1</sub> goes from low (v<sub>1</sub>=0) to high (v<sub>1</sub>=V<sub>dd</sub>). While v<sub>1</sub><V<sub>th1</sub>, V<sub>th1</sub> is the threshold voltage of the transistor M<sub>1</sub>, M<sub>1</sub> is in the cut-off region and M<sub>2</sub> is in the triode region, v<sub>0</sub>=V<sub>dd</sub>. When v<sub>1</sub>>V<sub>th1</sub>, the transistor M<sub>1</sub> changes to the saturation mode, M<sub>2</sub> keeps in the triode mode and v<sub>0</sub> starts to decrease. At one point, M<sub>2</sub> changes to saturation mode, and both transistors are in saturation, this is when v<sub>0</sub> abruptly decreases. When M<sub>1</sub> reaches the triode region, v<sub>0</sub> starts to decrease at a slower rate. Finally, when v<sub>1</sub>>V<sub>dd</sub>-V<sub>th2</sub>, V<sub>th2</sub> is the threshold voltage of M, M<sub>2</sub> is in the cut-off region, and v<sub>0</sub>=0V.

## 2.3 PUFs

Inspired by the works of Alioto [6], and Shamsoshoara et al. [5]. Traditionally, a key generation used an out-of-chip static entropy generator, and the key was stored in non-volatile memories. However, these types of memories are known to be vulnerable to a wide range of hardware and software attacks. PUFs aim to overcome the limitations associated with such methods, for that, it must ensure that by physical inspection, the secret should not be exposed and that the secret key should only be available only when the ship is powered on, preventing the possibility of a malicious attack to retrieve the key that it is not being required. These properties do not allow hackers to have access to the key since they cannot clone the inherent properties of the device even with physical access.

For an external stimulus called a challenge, the PUF will produce an output called the response. Each challenge and response form a pair called Challenge Response Pair (CRP) and ideally, each challenge will produce a perfectly repeatable output making CRPs independent from each other. There are two classes of PUFs depending on their CRPs. PUFs are classified as weak PUFs when there is a limited number of CRPs and strong PUFs when the number of CRPs increase exponentially with the area of the PUF.

PUFs rely on the unique physical properties introduced in the fabrication of the device to generate static entropy and extract a unique random key. To generate the same key from the process and mismatch variations, PUFs need to emphasize the latter variations and diminish the effects of all other variations by making the response independent of voltage and temperature variations, by maintaining the response consistent throughout the life of the device (aging), and by maintaining the statistical properties of the response from die to die.

### 2.3.1 Weak PUFs

Weak PUFs have a linear relationship with the number of CRPs. The number of responses is a function of the number of components used for the generation of CRPs. The limited number of CRPs results in stable responses robust to environmental conditions. However, it also means less security thus, for this class of PUFs it is crucial not to reveal any CRP and the latter ideally should be encrypted. Weak PUFs are mostly used for secret key generation, for example, chip ID, [20], [21] and lightweight encryption [22].

### 2.3.2 Strong PUFs

In strong PUFs, the number of CRPs increases exponentially with the area of the PUF. The high number of unique CRPs will prevent brute force attacks where all the responses are applied to get access to the system. Also, the high number of CRPs may offer stronger cryptographic strength due to generating longer keys.

### 2.3.3 Architecture

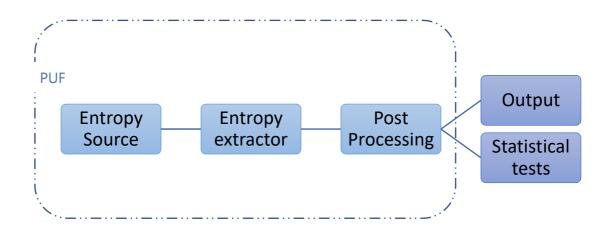

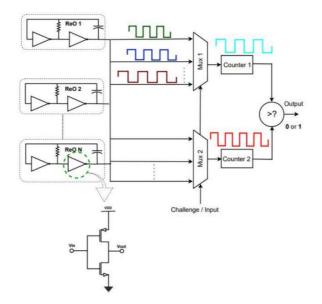

PUFs can be seen as a combination of different blocks with each block having its objective. Typically, PUF is structured as shown in Figure 2.17 which shows that PUFs can be divided

21

mainly into 3 different components: entropy generations, entropy extractor, and post-processing block which is optional [6], [9].

Figure 2.17 Block structure of a typical PUF. Based on [23].

• The first block is responsible for generating the static entropy through the physical properties of the electrical components. This block usually uses oscillators and switching components to produce the entropy in conjunction with a multiplexer commanded by the challenge, to increase randomness and stability, and/or also a counter to count the different pulses generated by the multiplexers. For example, connecting two different ring oscillators to a multiplexer where the challenge chooses which signal passes through followed by a counter.

• The second block will sample the output signal of the entropy source and will extract a discrete sequence of bits. This section has mostly used a comparator, an arbiter, D flip-flop, however, any other component that can perform a selection between two logic gates can be used.

• The Post-processing block is used to reduce the BER restoring some entropy and randomness that may have been lost due to any kind of perturbation. Some techniques include spatial majority vote (SMV), temporal majority vote (TMV), and dark bit masking.

The output of the PUF is formed by a sequence of ones and zeros. To certify the quality of the sequence created, it can be directed to further testing for example statistical tests to evaluate the randomness of the sequence thus confirming its use on security.

22

### 2.3.4 Quality Metrics

PUF quality can be assessed by several metrics to quantify the PUF response, including, stability, uniqueness, reproducibility, identifiability, randomness, sensitivity to variations, area, and energy efficiency Alioto[6], Samsoshoara[5], Podeti, et al.[24], Alioto et al.[25]

Stability is measured by the cumulative sum of unstable bits (flipping bits) over a certain number of iterations. Another method to evaluate stability is using the bit error rate (BER) which corresponds to the average of instability bits over the response of the PUF [6].

Uniqueness is quantified by the difference between the responses of each die of the PUF applying the same challenge (inter-PUF Hamming Distance) [5], [24]. The ideal inter-PUF Hamming Distance (inter-HD) is 50%, which means the response of two dice should vary by 50% if the responses are perfectly random [6].

Reproducibility is quantified by the average bits that differ between responses from different challenges at different conditions, the intra-PUF Hamming Distance (intra HD) [5], [24]. The ideal intra-HD is 0 meaning the same PUF for the same challenge can always reproduce the same key[6].

Identifiability is defined by the ratio between the inter-PUF and intra-PUF HD, the higher the identifiability the more difficult it is to identify the specific PUF [25].

Randomness aims to quantify the unpredictability of a response, for example in a random response the distribution of '1's and '0's should be 50% [6], [24]. Randomness can be assessed using the National Institute of Standards and Technology (NIST) test suite, the 0/1 bias requirement from the NIST test suite is equivalent to the min-entropy discussed in Chapter 2.1 [26]. Another randomness metric is Shannon entropy.

## 2.4 Statistics/Statistical Tests

Statistics is about collecting, analyzing, presenting, and interpreting data which will allow the study of processes to be able to make quantitative and qualitative decisions.

However, statistics are not absolute, in statistical tests is often used a 5% probability that the test is wrong, and the significance level. The larger the sample size, the more likely the results are the right answer.

In this work, statistics and statistical tests were used to assess the behavior of transistors under mismatch variations. Thus, when discussing the results from statistical tests can't take absolute conclusions until a physical test is performed.

### 2.4.1 NIST Test

The National Institute of Standards and Technology (NIST) described and developed a set of statistical tests to standardize the evaluation of the security and randomness of binary sequences [26]. The current NIST Test Suit comprises fifteen different tests. The tests are:

- The Frequency (Monobit) Test

- Frequency Teste within a Block

- The runs Test

- Tests for the Longest-Run-of-Ones in a Block

- The Binary Matrix Rank Test

- The Discrete Fourier Transform (Spectral) Test

- The Non-overlapping Template Matching Test

- Maurer's "Universal Statistical" Test

- The Linear Complexity Test

- The Serial Test

- The Approximate Entropy Test

- The Cumulative Sums (Cusums) Test

- The Random Excursions Test

- The Random Excursions Variant Test

The NIST Test has a few concepts that will quantify the results and so, help to understand the meaning of the test's result. These concepts are the *complementary error function*, the *incomplete gamma function*, the *standard normal and chi-square distribution* and the  $p_{value}$ .

These statistical tests are used to assess the possible randomness of a set of bit strings. If the bit string passes all the tests, the string has a high chance of being random thus, the entropy source has high entropy.

### 2.4.2 Chi-square Goodness of Fit Test

The chi-square Goodness of Fit Test as explained in [27] is used to test if a specific sample of data has a specific distribution. This test used binned data for example data from a histogram. For better results, the test should use the same number of bins as the histogram used to visualize data.

This test is defined by the null hypothesis  $H_0$ , that the data follow a specific distribution. The test statistic is defined as

$$\chi^{2} = \sum_{i=1}^{k} \frac{(O_{i} - E_{i})^{2}}{E_{i}}$$

Where  $O_i$  is the number of observations for bin i and  $E_i$  is the expected frequency for bin i for a significance level,  $\alpha$ .

Test statistics follow the chi-square distribution with n degrees of freedom. Thus, the hypothesis that the data follow a specific distribution is rejected if

$$\chi^2 > Chi - squared value$$

The chi-square value is dependent on the degrees of freedom and the significance level  $\alpha$ . The chi-square values are in Appendix A. The p-value obtained is an indication of the probability to obtain results as extreme as the result observed under the premise that the null hypothesis is correct. The higher the p-value, the less likely the null hypothesis is rejected.

### 2.4.3 Monte Carlo Method

As explained by, Kroese et. al [28], Monte Carlo is the simulation of random processes for several iterations. This method has various uses for example sampling, estimation, and optimization.

The sampling's main objective is to gather information about some random object. For example, mimic the behavior of a real-life system or circuit which is composed of such an object.

Estimation aims to estimate certain numerical quantities related to a certain model. For example, estimating the expected throughput in a production line.

The optimization objective, as the name suggests is to optimize complicated functions. For example, introduce randomness to deterministic functions and this way can be more efficiently solved.

Monte Carlo is universally used due to its simplicity and efficiency which lead to ease of scalability. When dealing with statistics, the more data evaluated, the closer to reality the results are, thus, the above characteristics are what makes the Monte Carlo method so popular.

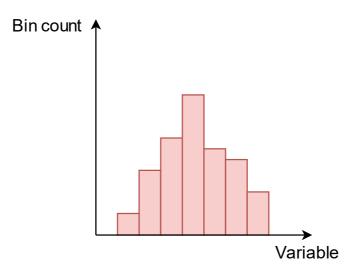

The data obtained from the Monte Carlo method can be graphically expressed using histograms. As noted in [29], histograms split the range of data into equal-sized bins and the number of points from the data obtained from Monte Carlo that fall into the range of a certain bin is counted. So, on the vertical axis it is the count for each bin and on the horizontal axis, the variable being studied. A set of data displayed in the histogram form looks like Figure 2.18.

Figure 2.18 Histogram example.

To understand better the data that is being displayed by the histogram, probability density functions can be used. As explained by Uchechu. H. [30]. For such functions, there are two main types, parametric and non-parametric.

Parametric probability density functions assume that the data come from an already established probability distribution and based on the data, it creates an assumption about the parameters that define such function. An example of this is the normal distribution which assumes the data follows the normality.

Non-parametric probability density functions do not follow assumptions. When the distribution of data is unknown, the non-parametric functions allow for a more correct result about the population. An example is the kernel density distribution.

The kernel density distribution allows having a density distribution that represents the data obtained from the histogram without any assumption thus, better representing the distribution of data for an unknown distribution. By plotting the kernel density distribution against the normal distribution, it is possible to analyze how close the data of the histogram is to the normal distribution from the same data.

The normal distribution is especially important when assessing if a data set is or is not naturally random.

# 3

# STATE OF THE ART

When designing PUFs, there are some characteristics that are desirable, like, minimize noise, power consumption, area of the chip, obtain high entropy e robustness to external variations. Thus, when analyzing and designing PUFs, it is important to have a closer look into those characteristics.

## 3.1 Arbiter PUF

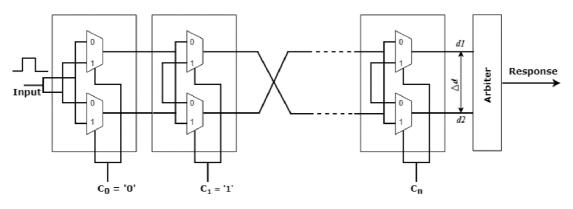

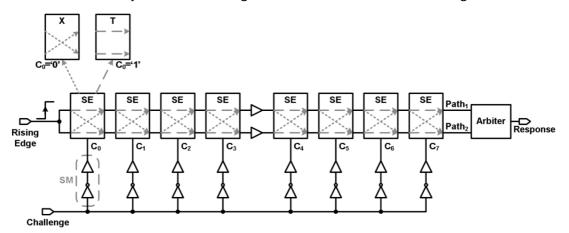

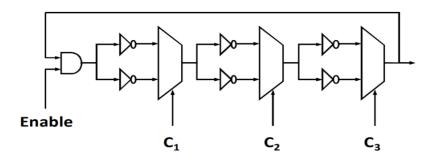

The arbiter PUF is a kind of delay based PUF that is comprised of a switching component and an arbiter block as shown in Figure 3.1. Input and a random challenge are fed into the switching component to produce the necessary delays. The arbiter block will measure the delays and select which channel, the two paths are designed to have the same delay producing the response. The arbiter block can be for example a D flip-flop. [24]

Figure 3.1 Arbitre PUF. Extracted from [24].

The switching component consists of N multiplexers that are fed with an N-bit challenge with each bit on each multiplexer to select the paths. In the end, the Arbiter stage will determine each signal arrived first and based on that, for example, output "1" if signal1 arrived first and output "0" if signal 2 arrived first. Both paths are designed to have the same delay however due to differences in intrinsic physical characteristics of each path/component, there will be a delay that will characterize the entropy of the PUF.

In [31], was proposed an Arbiter PUF (APUF) of 64 single-bit PUF cells using CMOS technology, with the 64 single-bit PUF cells, obtained a 64-bit response. The entropy of the response is obtained by exploiting the imperfections from the fabrication process of the CMOS technology not only on the switching element but also on the selecting module. The architecture of a single-bit PUF cell is illustrated in Figure 3.2.

The switching element is formed by four transmission gates using one NMOS and one PMOS in parallel, this configuration enables the input signal to travel in two possible paths depending on the random challenge determined by the selecting module. Each path has a different-sized transistor to have paths with various delays.

The selecting module is composed of three inverters in series. The first transistor is set so the voltage transfer characteristics (VTC) is  $1/2V_{DD}$  and the other two transistors are used to completely emphasize signal value. A challenge of  $1/2V_{DD}$  is fed into the first inverter, due to the process variations created upon fabrication of the CMOS transistor, the VTC will be slightly different thus, the input challenge will stay below or under the VTC. If the input challenge is lower than the real VTC, the NMOS will be in saturation mode and the PMOS in linear mode thus, the output will tend to  $V_{DD}$ . If the input challenge is higher than the real VTC, the NMOS will be in linear mode and the PMOS in saturation mode thus, the output will tend to zero. Variations occur not only on the switching element but also on the selecting module.

Figure 3.2 Proposed single-bit PUF cell. Extracted from [31].

The APUF with selecting modules showed it can be a good PUF. The results were good in uniqueness and energy consumption tests. However, to get enough entropy, this kind of PUF need a significant number of stages (SE blocks in Figure 3.2) to generate enough delays between the two paths, thus its main drawback is the area used.

| Table 3.1 APUF with selecting modules performance [31]. |             |  |

|---------------------------------------------------------|-------------|--|

| Technology                                              | 45nm MOSFET |  |

| Area (μm²)                                              | 2168        |  |

| V <sub>DD</sub> range (V)                               | 0.9~1.1     |  |

| Temperature Range (°C)                                  | 0~100       |  |

| Energy per bit (pJ/b)                                   | 0.103593    |  |

| BER                                                     | 1.34%       |  |

| Uniqueness                                              | 49.99%      |  |

The performance results are shown in Table 3.1.

# 3.2 Memory Based PUF

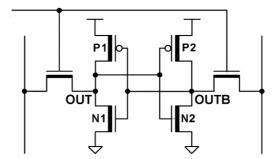

The Memory based PUF uses a memory cell to generate the entropy. An SRAM is a type of NVM which means it only stores data when it is being powered. A commonly used configuration is a 6 transistor SRAM cell, which is formed by two cross-coupled identical inverters, this configuration stores one bit of information, which can be seen in Figure 3.3. The entropy is extracted from process variations present in the inverters. These mismatches are then amplified due to the positive feedback of the cross-coupled inverters. [32] However SRAM cells tend to produce more the number logic "1" than the logic number "0", which greatly reduces the randomness of the challenge produced. Also, the SRAM cell only depends on six transistors, if the mismatches between the transistors is not substantial compared to noise, the reliability of the PUF can be degraded [32]. Compared to other types of PUFs, SRAM-PUF has advantages in stability and reliability [33], [34].

Figure 3.3 SRAM cell Schematic. Extracted from [32].

In [32], is proposed a methodology to solve the above issues of the SRAM-PUF. This is achieved by taking into consideration aging effects, Negative-Bias-Temperature-Instability (NBTI) which mostly affects the threshold voltage. The polarity and aging change the result created by the mismatches in the cross-coupled transistors, since, in fabrication, the data "1" is 70% more likely to appear, aging effects are injected into the SRAM To balance the final "1" and "0"'s output thus increasing uniformity. To improve reliability, the objective is, after reaching the desired uniformity, to introduce more NBTI aging to increase the threshold mismatch on one inverter on each SRAM cell, this increases the mismatch and thus, the reliability. The final robust SRAM-PUF methodology is represented in Figure 3.4. After the introduction of aging effects, results show great improvements in uniformity and reliability, without NBTI injection, the probability of "1" sis 0.7255, after the introduction of the aging effect until  $\Delta V_{th}$ =46, the probability of "1" reaches 0.4957 on the ideal level of 0.50.

Figure 3.4 Methodology for robust SRAM-PUF. Extracted from [32].

# 3.3 Oscillator Based PUF

### 3.3.1 Relaxation Oscillator

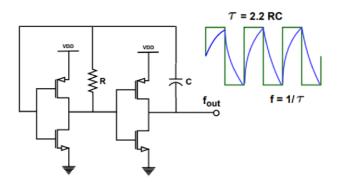

A relaxation oscillator is a non-linear oscillator that generates a periodic non-sinusoidal output signal such as a triangle or square wave, a classical CMOS relaxation oscillator is shown in Figure 3.5. The oscillator generates a signal utilizing the charge and discharge cycles of capacitors or inductors with the frequency of the oscillation dependent on the time constant  $\tau$  of the capacitive or inductive circuit. These kinds of oscillators are easily implemented in CMOS and cost less current and power [24].

Figure 3.5 Classical CMOS Relaxation oscillator schematic. Extracted from [24].

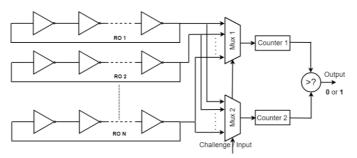

In [24], it is used a relaxation oscillator with the schematic represented by Figure 3.6. This oscillator will have a frequency-dependent on the time constant  $\tau$  of the RC circuit which is f=1/ $\tau$ . This PUF is very similar to the conventional ring oscillator PUF as shown in Figure 3.7, for the entropy source, the relaxation oscillator PUF takes use of the process variations that occurred in the fabrication, two multiplexers are used to select which relaxation oscillator, two counters to count the number of oscillations and finally the comparator to output the response based on the count difference. This PUF was implemented in UMC65nm technology with the use of 32 relaxation oscillators, so a 5-bit challenge was used to select each oscillator.

Figure 3.6 Basic Relaxation Oscillator. Extracted from [24].

Figure 3.7 Relaxation Oscillator PUF. Extracted from [24].

The evaluation of quality metrics indicates that this PUF is not very resilient neither to voltage nor to temperature variations. [24]. The performance results from a relaxation oscillator based on the PUF in Figure 3.7 are shown in Table 3.2.

| 65nm                        |  |  |

|-----------------------------|--|--|

| -                           |  |  |

| -                           |  |  |

| -                           |  |  |

| -                           |  |  |

| 118.42 (one instance)       |  |  |

| -                           |  |  |

| 49.22%                      |  |  |

| 49.53%                      |  |  |

| 45.31%                      |  |  |

| 97.41% (temperature change) |  |  |

| 97.97% (voltage change)     |  |  |

|                             |  |  |

Table 3.2-Relaxation Oscillator results [24].

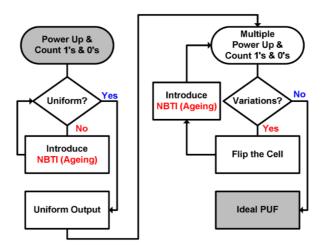

### 3.3.2 Coupled Oscillator

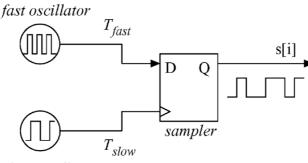

The coupled oscillator has already been used in developing TRNGs as in [35], [36]. In both works, the coupling is achieved using a D flip-flop where a slower oscillator is used to sample a faster oscillator as shown in Figure 3.8. To produce a random bitstream, it is exploited the jitter present in the sampler oscillator, if the standard deviation of the slow oscillator period is greater than the fast oscillator period, two successive sampling times are assumed independent, thus the bitstream generated is random.

slow oscillator

Figure 3.8 Simple Coupled Oscillator. Extracted from [36].

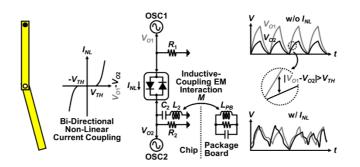

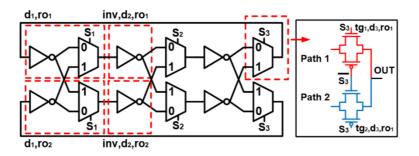

In [37], a coupled chaos oscillator was implemented as shown by the simplified circuit in Figure 3.9. Instead of using a D flip-flop, the coupling is accomplished through a bi-directional non-linear current conduction which can be implemented using two cross-coupled diodes, this results in a nonlinear current which is used to obtain a chaos behavior. Chaos provides a non-periodic deterministic behavior thus it can be used to generate unique ID entropy. Two identical ROs are used to provide a periodic non-chaotic behavior, when C<sub>2</sub> and R<sub>2</sub> are introduced, the voltage swing of the second oscillator decreases, and the difference between the voltage

swings across both oscillators becomes larger than the threshold voltage of the diodes, this activates the nonlinear current from the cross-coupled diodes inducing a chaos behavior in the oscillation.

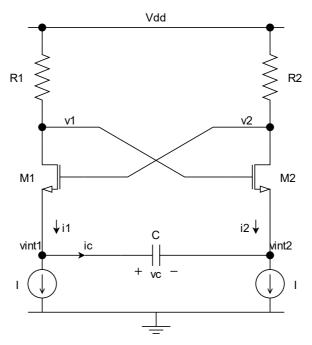

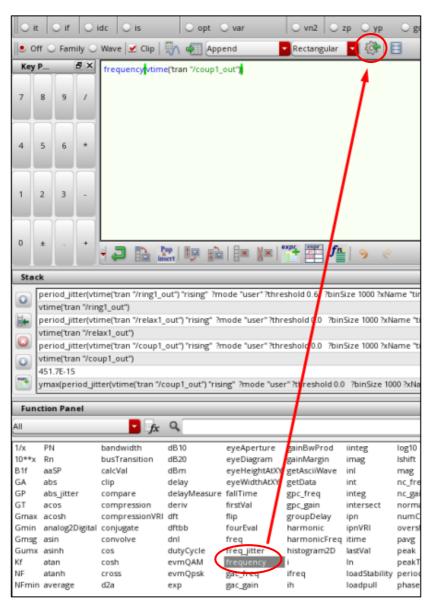

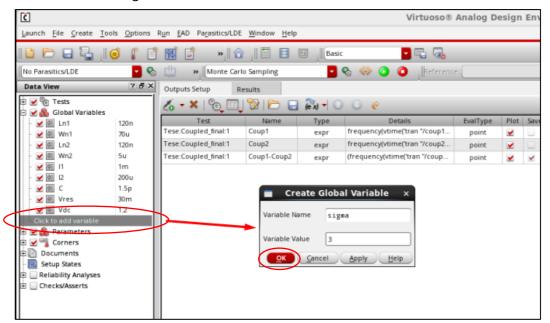

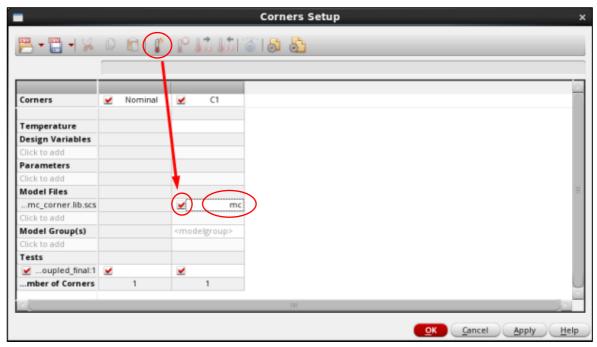

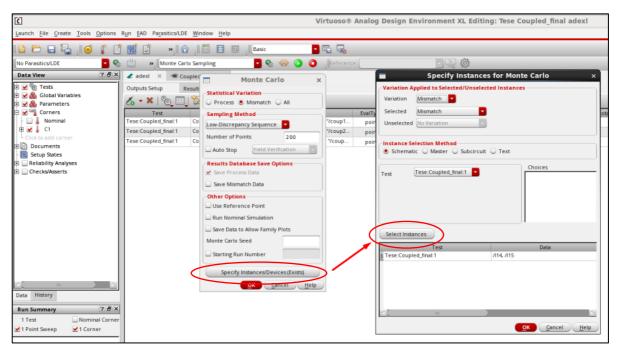

Figure 3.9 Simplified schematic of coupled chaos PUF. Extracted from [37].