#### University of Tennessee, Knoxville

# TRACE: Tennessee Research and Creative Exchange

**Doctoral Dissertations**

**Graduate School**

12-1999

# Theoretical and algorithmic approaches to field-programmable gate array partitioning

Barbara Catherine Plaut

Follow this and additional works at: https://trace.tennessee.edu/utk\_graddiss

#### **Recommended Citation**

Plaut, Barbara Catherine, "Theoretical and algorithmic approaches to field-programmable gate array partitioning." PhD diss., University of Tennessee, 1999. https://trace.tennessee.edu/utk\_graddiss/8900

This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by Barbara Catherine Plaut entitled "Theoretical and algorithmic approaches to field-programmable gate array partitioning." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Computer Science.

Michael A. Langston, Major Professor

We have read this dissertation and recommend its acceptance:

Donald Bouldin, Michael Berry

Accepted for the Council:

Carolyn R. Hodges

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

#### To the Graduate Council:

I am submitting herewith a dissertation written by Barbara C. Plaut entitled "Theoretical and Algorithmic Approaches to Field-Programmable Gate Array Partitioning." I have examined the final copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Computer Science.

Michael. A. Langston, Major Professor

We have read this dissertation and recommend its acceptance:

Michael W. Beny

Accepted for the Council:

Associate Vice Chancellor and Dean of the Graduate School

# Theoretical and Algorithmic Approaches to Field-Programmable Gate Array Partitioning

A Dissertation

Presented for the

Doctor of Philosophy Degree

The University of Tennessee, Knoxville

Barbara C. Plaut December 1999

## Acknowledgements

First and foremost, I thank my advisor, Prof. Michael Langston. I thank him for his guidance and unwavering support, and for the many, many things I have learned under his advisorship.

I am grateful to the Navy for the Augmentation Award for Science and Engineering Technology (AASERT), and to Prof. Langston for awarding me the privilege of being its recipient.

I thank Profs. Berry, Bouldin and Raghavan for serving on my graduate committee, and their efforts in that regard.

I thank all the faculty and staff in the Computer Science Department who have helped me in so many ways.

I thank my family members who have cheered my accomplishments and buoyed me up during the low times.

Last, but not least, I thank my mentor, best friend and husband, Conrad, for having so much faith in me.

## Abstract

Many practical problems dealing with the design of Very Large Scale Integrated (VLSI) circuits can be modeled as graphs in which vertices represent components of the circuit and edges represent a relationship between these components. When expressed as graphs, these problems can then often be solved using graph theoretic methods. Unfortunately, many such problems are  $\mathcal{NP}$ -complete, hence no practical exact solutions are known to exist.

In this dissertation, we study  $\mathcal{NP}$ -complete problems taken from the realm of partitioning for Field-Programmable Gate Arrays (FPGAs). We adopt a two-pronged approach of theory and practice, developing practical heuristics driven by theoretical study.

The theoretical approach is motivated by well-quasi-order (WQO) theory, which can be used to show, among other things, that when some hard problems have fixed parameters, polynomial-time solutions exist. This is of significance in the area of FPGA partitioning, in which practical problems are often characterized by fixed-parameter instances. WQO techniques are not generally practical, however, and we develop new methods to solve several important problems in VLSI that are not even amenable to WQO techniques.

We begin with a representative partitioning problem, Min Degree Graph Partition (MDGP), the fixed-parameter version of which is closed under the immersion order. We show that the obstruction set (set of immersion minimal elements) for this problem is computable; we prove both upper and lower bounds on the obstruction set size; and we completely characterize all fixed-parameter MDGP simple tree obstructions.

WQO theory tells us only that fixed-parameter MDGP is solvable in (high-degree) polynomial time. We attack the problem using what we refer to as kd-candidate subsets, culminating in linear-time decision and search algorithms. The kd-candidate subset method also paves the way for an efficient heuristic for the FPGA Minimization problem.

We then broaden our scope to incorporate delay minimization into FPGA partitioning. We develop, analyze and test a novel method called *critical path compression*, inspired in part by compiler optimization techniques.

We then look at a variety of generalizations of MDGP. Some of these problems are not immersion closed; others are not even defined in a way that WQO theory applies. However, almost all of them are efficiently solvable via the *kd-candidate* subset approach.

Interspersed in these results are many refinements of what is known about the complexity of these problems. We also discuss a few other solution strategies, and present many open problems.

## Contents

| 1 | Int                                                   | roduct                                 | ion and Background                             | 1  |  |

|---|-------------------------------------------------------|----------------------------------------|------------------------------------------------|----|--|

|   | 1.1                                                   | Defini                                 | itions and Mathematical Preliminaries          | 3  |  |

|   | 1.2                                                   | Hardy                                  | ware Technology                                | 8  |  |

| 2 | A F                                                   | undan                                  | nental Partitioning Problem                    | 11 |  |

|   | 2.1                                                   | Proble                                 | em Definition and Prior Results                | 11 |  |

|   | 2.2                                                   | New 1                                  | Results                                        | 15 |  |

|   |                                                       | 2.2.1                                  | Algorithmic Tools                              | 15 |  |

|   |                                                       | 2.2.2                                  | Self-reduction                                 | 21 |  |

|   |                                                       | 2.2.3                                  | More on Decision and Search                    | 24 |  |

|   |                                                       | 2.2.4                                  | Obstruction Sets                               | 25 |  |

|   |                                                       | 2.2.5                                  | Tractability on Restricted Classes of Graphs   | 35 |  |

| 3 | Extending the Fundamental Problem: FPGA Minimization  |                                        |                                                |    |  |

|   | 3.1                                                   | 1 Problem Definition and Prior Results |                                                |    |  |

|   | 3.2 New Results                                       |                                        |                                                |    |  |

|   |                                                       | 3.2.1                                  | Refining the Tractability of FPGA Minimization | 39 |  |

|   |                                                       | 3.2.2                                  | $\mathrm{MDGP}(k,d,p)$ Results                 | 43 |  |

|   |                                                       | 3.2.3                                  | p-way MDGP(k,d): A Practical Heuristic         | 47 |  |

| 4 | Extending the Fundamental Problem: Delay Minimization |                                        |                                                |    |  |

|   | 4 1                                                   | Proble                                 | em Definition                                  | 58 |  |

| 4.2 A Practical Heuristic |       |                        | actical Heuristic                                           | 62  |

|---------------------------|-------|------------------------|-------------------------------------------------------------|-----|

|                           |       | 4.2.1                  | Circuit Characteristics                                     | 62  |

|                           |       | 4.2.2                  | Prior Work                                                  | 64  |

|                           |       | 4.2.3                  | A New Approach - The "Two-Step" Method                      | 66  |

|                           |       | 4.2.4                  | An Iterative Improvement Algorithm for Improving Delay in a |     |

|                           |       |                        | Partitioned Circuit                                         | 68  |

| 5                         | Var   | iations                | s of the Fundamental Problem                                | 103 |

|                           | 5.1   | Hyper                  | graphs                                                      | 103 |

|                           | 5.2   | Partit                 | ioning for Heterogeneous Systems                            | 107 |

|                           | 5.3   | Labell                 | led Graphs                                                  | 113 |

|                           | 5.4   | Balan                  | ced Partitioning                                            | 114 |

| 6                         | Fut   | ure Di                 | rections and Conclusion                                     | 118 |

|                           | 6.1   | Theoretical Directions |                                                             | 118 |

|                           |       | 6.1.1                  | Closure-Preserving Operators                                | 118 |

|                           |       | 6.1.2                  | Other Circuit Partitioning Problems                         | 129 |

|                           |       | 6.1.3                  | Faster Immersion Testing                                    | 133 |

|                           |       | 6.1.4                  | Other Issues                                                | 133 |

|                           | 6.2   | Practi                 | cal Directions                                              | 134 |

|                           | 6.3   | Conclu                 | asion                                                       | 135 |

| Bi                        | bliog | raphy                  |                                                             | 136 |

| Vi                        | ta    |                        |                                                             | 149 |

# List of Figures

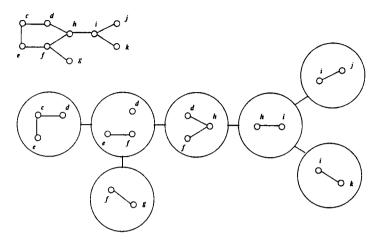

| 1.1 | A graph and its tree-decomposition of width two   | 6  |

|-----|---------------------------------------------------|----|

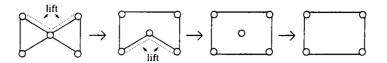

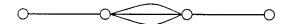

| 1.2 | $C_4 \leq_i K_1 + 2K_2 \ldots \ldots$             | 7  |

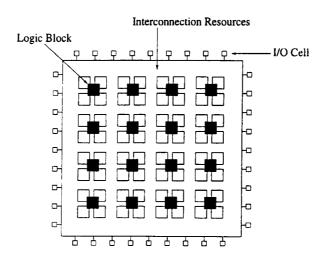

| 1.3 | The FPGA                                          | g  |

| 2.1 | A partitioning problem                            | 12 |

| 2.2 | A star graph with six rays                        | 15 |

| 2.3 | An instance of MDGP(3,2)                          | 17 |

| 2.4 | $C1 = A \cup I, C2 = B \cup I$                    | 18 |

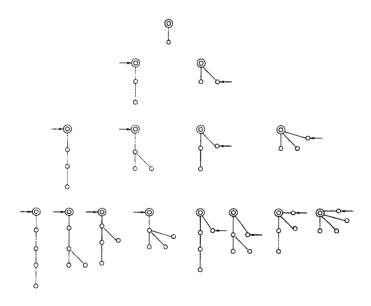

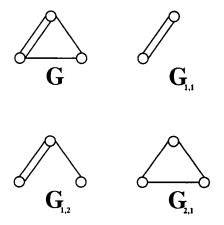

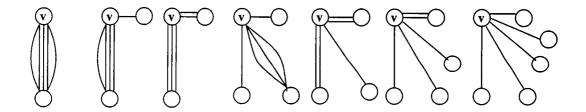

| 2.5 | Some $MDGP(k,d)$ obstructions                     | 27 |

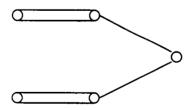

| 2.6 | A $kdq$ -tree $(k = 8, d = 2, q = 2)$             | 29 |

| 2.7 | kdq-trees                                         | 29 |

| 2.8 | A general tree obstruction to $MDGP(k,d)$         | 33 |

| 2.9 | Some nonisomorphic rooted trees                   | 34 |

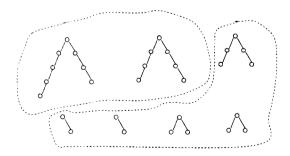

| 3.1 | A disconnected instance of FPGA Minimization      | 40 |

| 3.2 | A tree instance of FPGA Minimization              | 41 |

| 3.3 | Partitioning a tree instance of FPGA Minimization | 42 |

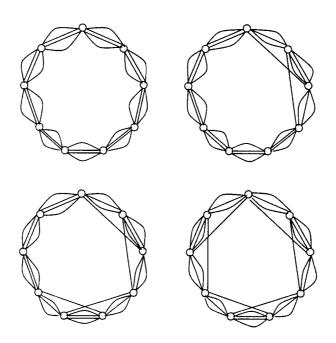

| 3.4 | Some 8-regular, 8-edge-connected 9-components     | 45 |

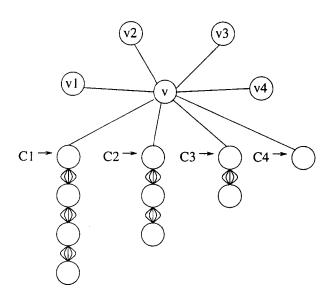

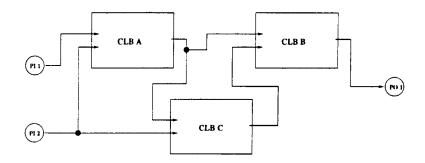

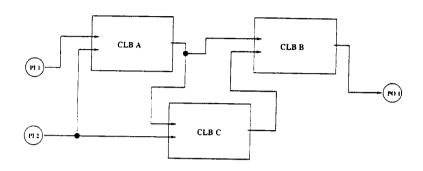

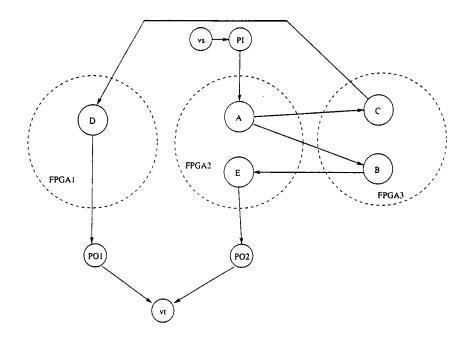

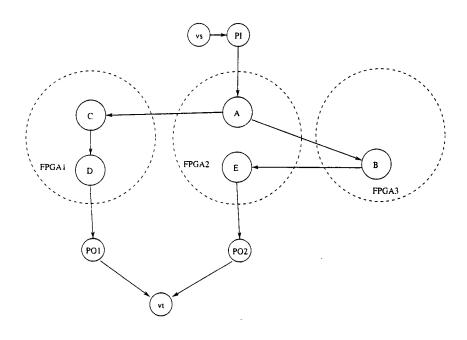

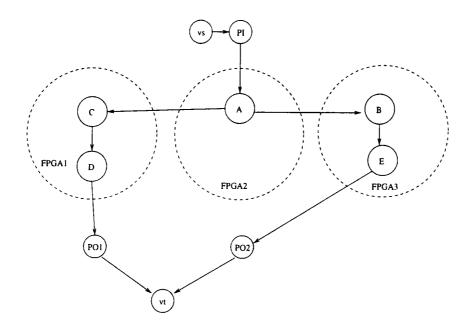

| 3.5 | An example circuit                                | 49 |

| 3.6 | Partitioning a hypergraph and a simple graph      | 50 |

| 3.7 | An instance of FPGA Minimization                  | 52 |

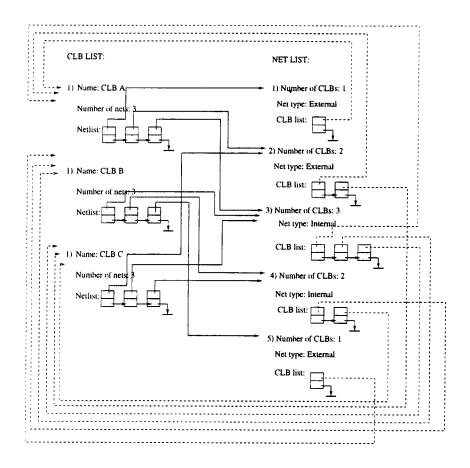

| 3.8 | Data structure for FPGA Minimization              | 54 |

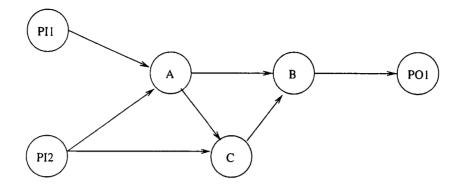

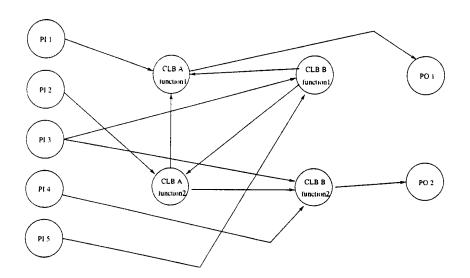

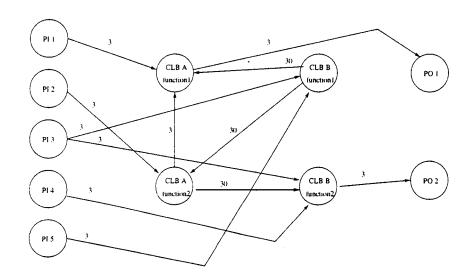

| 4.1  | An example circuit                           | 63 |

|------|----------------------------------------------|----|

| 4.2  | A Delay Minimization example                 | 65 |

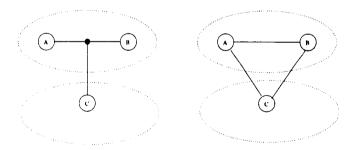

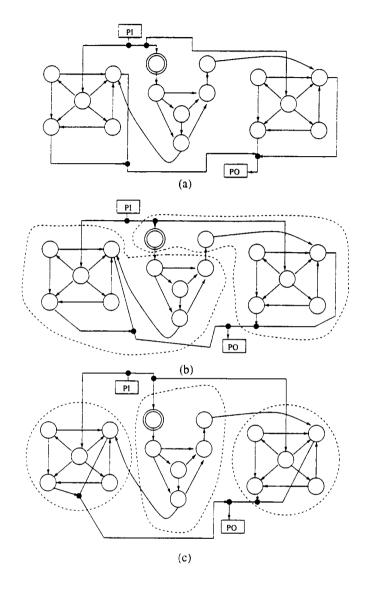

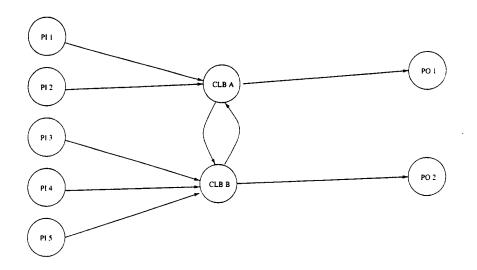

| 4.3  | A connection graph                           | 69 |

| 4.4  | Two-function CLBs                            | 70 |

| 4.5  | A connection graph for two-function CLBs     | 70 |

| 4.6  | A cyclic connection graph                    | 71 |

| 4.7  | A connection graph with edge delays          | 71 |

| 4.8  | A DAG with edge delays                       | 72 |

| 4.9  | Compressing a critical path                  | 74 |

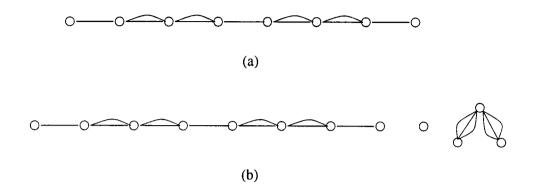

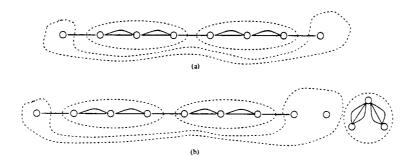

| 4.10 | An extended target sequence                  | 80 |

| 4.11 | A critical path                              | 81 |

| 4.12 | Elimination I example: part 1                | 83 |

| 4.13 | Elimination I example: part 2                | 83 |

| 4.14 | Elimination I example: part 3                | 84 |

| 5.1  | A "yes" instance of Hypergraph MDGP(k,d)     | 05 |

| 5.2  | $MDGP(2,1; 1,2) \neq MDGP(k,d)$              | 08 |

| 5.3  | A "yes" instance of MDGP(2,1; 1,2)           | 09 |

| 5.4  | Instances of p-way MDGP(k,d) and MDGP(k,d,0) | 16 |

| 5.5  | Partitioning the graphs of Figures 5.4(a)    | 17 |

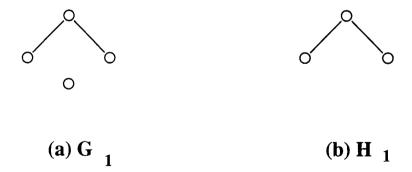

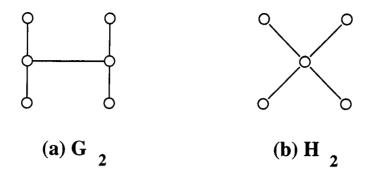

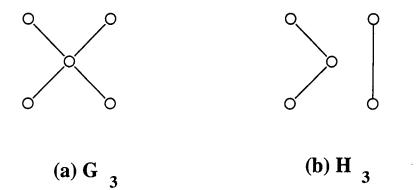

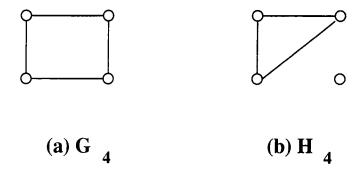

| 6.1  | Graphs $G_1$ and $H_1$                       | 22 |

| 6.2  | Graphs $G_2$ and $H_2$                       | 24 |

| 6.3  | Graphs $G_3$ and $H_3$                       | 26 |

| 6.4  | Graphs $G_4$ and $H_4$                       | 27 |

| 6.5  | Some obstructions to $MDC(4)$                | วา |

## List of Tables

| 1.1  | Summary of main results                                        | 4   |

|------|----------------------------------------------------------------|-----|

| 3.1  | Complexity of MDGP and FPGA Minimization                       | 43  |

| 3.2  | Partitioning results                                           | 57  |

| 4.1  | Possible mappings for circuit 3.5                              | 63  |

| 4.2  | Effect of Elimination I                                        | 85  |

| 4.3  | Effect of Substitution I                                       | 88  |

| 4.4  | Circuit statistics                                             | 93  |

| 4.5  | Hill-climbing experiment: percentage improvement               | 94  |

| 4.6  | Hill-climbing experiment: final delay                          | 95  |

| 4.7  | Hill-climbing experiment: CPU time                             | 96  |

| 4.8  | Topology comparison: percentage improvement                    | 97  |

| 4.9  | Topology comparison: final delay                               | 98  |

| 4.10 | Strategy comparison: percentage improvement                    | 99  |

| 4.11 | Strategy comparison: final delay                               | 100 |

| 4.12 | Strategy comparison: CPU time                                  | 101 |

| 4.13 | Breadth-first search (BFS) vs. topological sort (TS): CPU time | 102 |

| 6.1  | Summary of closure-preserving operators                        | 130 |

## Chapter 1

## Introduction and Background

The technology of VLSI circuit design has progressed rapidly in recent years. The process of transforming an abstract circuit design into a physical entity has become increasingly complex. In order to handle this complexity, the process is broken down into a series of tasks, each of which can be handled relatively independently. Some of these tasks are behavior modelling, functional and logic minimization, logic fitting and simulation, partitioning, placement, routing and fabrication ([SY]). In this work, we focus on the partitioning stage.

Another consideration in circuit design is that of the physical layout style, some of which are full-custom, gate-array, standard-cell, macro-cell, programmable logic array (PLA) and field-programmable gate attay (FPGA) ([SY]). Our interest is in partitioning for FPGA layouts.

This particular aspect of partitioning is itself a broad problem, with numerous specific formulations, many of which have been extensively studied ([AK]). These problems, when translated into graphical terms, are usually  $\mathcal{NP}$ -complete, and ultimately tackled by approximation and heuristic algorithms. However, theoretical results of Robertson and Seymour ([RS1], [RS2], [RS3], [RS4]) can often be used to show that in many cases fixed-parameter versions of the problem are in fact solvable in polynomial time. This is of significance when dealing with FPGA partitioning problems, which

are inherently confined to instances with bounded parameters. Unfortunately, even theoretically efficient algorithms are often not practical. Nevertheless, the theoretical study often paves the way to new and better heuristics.

In this chapter, we give an introduction to the topic, some definitions and background information.

In the second chapter, a representative and fundamental partitioning problem is defined and studied from a theoretical perspective. The fixed-parameter versions of this problem are relevant to FPGA partitioning. They are known to be solvable in (high-degree) polynomial time, because of their closure under the immersion order. In this work, we show that the obstruction sets for these graph families are computable by demonstrating upper bounds on the obstruction set sizes. We also determine lower bounds, and completely characterize the simple tree obstructions. We then show that both the search and decision versions of the problem are solvable in linear time. While this problem does not capture all of the issues important in FPGA partitioning, it serves as a useful starting point for further study.

The fundamental problem is extended to consider FPGA Minimization in the third chapter. Here we strive to partition a circuit into as few chips as possible, in order to minimize cost, and to enable realization of a circuit on a specific system. We delve deeper into the complexity of the problem, and derive a practical heuristic driven by theoretical results.

In the fourth chapter, the fundamental problem is extended in yet another direction. The circuit system is considered in its dynamic state, with electrical current flowing through it. We seek to minimize the maximum time for a signal to flow from any input to any output. Here we must broaden our graphical representation of the circuit from undirected to directed graphs, and the theoretical picture changes significantly. In this chapter, we develop and study a new method for minimizing delay in a partitioned circuit.

The fifth chapter deals with many variations of the fundamental partitioning prob-

lem. Although many of these problems are no longer amenable to WQO techniques, we find that most of them can still be solved efficiently using the techniques of the second chapter. We conclude with some ideas for future study, from both a theoretical and a practical standpoint.

Table 1.1 summarizes the main theoretical and practical results of this work.

## 1.1 Definitions and Mathematical Preliminaries

For our purposes, an undirected graph  $G = (V_G, E_G)$  consists of finite sets of vertices  $V_G$  and undirected edges  $E_G$ . Multiple copies of edges are allowed, but self-loops are ignored, because they have no consequence in any of the algorithms that we develop.

A directed graph  $G = (V_G, E_G)$  is defined similarly, except each edge pair has an ordering.

The simplified notation G = (V, E) is used when G is the only graph under consideration.

If v is a vertex in G, the degree of v (denoted  $\delta_G(v)$ ) is the number of edges in G that are incident on v. When there is no ambiguity about the graph, we simply use  $\delta(v)$  to denote the degree of v. The notation is extended to denote the degree of a set of vertices as follows: for  $S \subseteq V_G, \delta_G(S)$  is the number of edges in G that have exactly one endpoint in S.

Two vertices  $u, v \in V$  are adjacent or neighbors if  $uv \in E$ .  $N(u) = \{v : uv \in E\}$  denote the set of immediate neighbors of u. Note that  $\delta(u) > |N(u)|$  if multiple copies of an edge adjacent to u exist.

The notation  $K_n$  is used to signify a graph containing n vertices, in which every pair of vertices is connected by a single edge.

A subgraph of G induced by some  $V' \subseteq V_G$  consists of vertex set V' and edge set  $\{uv|uv \in E_G, u \in V', v \in V'\}$ .

Table 1.1: Summary of main results

**MDGP:** in  $\mathcal{P}$  when restricted to simple trees;

Fixed-parameter MDGP: solvable in linear time,

obstruction set computable,

upper and lower bounds on obstruction set size,

complete characterization of simple tree obstructions

FPGA Minimization: NP-complete for many classes of graphs,

development of theoretically-based heuristic;

Fixed-parameter FPGA Minimization: exponential obstruction set size

Delay Minimization: NP-complete for many classes of graphs,

development of critical path compression heuristic;

Fixed-k, d Delay Minimization:  $\mathcal{NP}$ -complete

Fixed-parameter Hypergraph MDGP: in  $\mathcal{P}$

Heterogeneous MDGP: in  $\mathcal{P}$  when restricted to simple trees;

Fixed-parameter Heterogeneous MDGP: decision and search solvable in linear time;

obstruction set computable

Balanced MDGP(k,d,0):  $\mathcal{NP}$ -complete

MDC(d): exponential obstruction set size

Sixteen WQO closure-preserving operators: whether closed or not

If, for every two vertices  $x, y \in V_G$ , there exists a series of edges from x to y, we say that G is connected. Each maximally connected subgraph of a graph is referred to as a component. Two vertices  $u, v \in V$  are n-edge-connected if a minimum of n edges must be deleted to disconnect G in such a way that u and v lie in different components.

An n-path is a connected, acyclic graph containing n > 1 vertices, each vertex of which has either 1 or 2 neighbors.

The following two definitions are from [H]. A shortest u - v path is called a geodesic. The diameter of a connected graph is the length of any longest geodesic.

A tree is a connected, acyclic graph. A simple tree is a tree in which there is at most one copy of each edge. A forest (simple forest) is a graph whose components are all trees (simple trees).

Two graphs H and G are said to be isomorphic if there is a bijection  $f: V_H \to V_G$  such that  $uv \in E_H \Leftrightarrow f(u)f(v) \in E_G$ .

A tree-decomposition of G = (V, E) is a pair  $(T = (V_T, E_T), f)$  where T is a tree and f is a function mapping  $V_T$  into a set of subgraphs of G, with f satisfying the following properties:

- 1.  $\bigcup_{t \in V_T} f(t) = G$ ; and

- 2. for  $s, t \in V_T$ , if u is on the path from s to t in T then  $f(s) \cap f(t) \subseteq f(u)$ .

The width of a tree-decomposition (T, f) is  $\max_{t \in V_T} |f(t)| - 1$ . The treewidth of G is the minimum treewidth of all tree-decompositions of G. Figure 1.1 shows a graph and a corresponding tree-decomposition of width two.

It is evident that every tree has treewidth 1. Therefore, the family of all trees is of bounded treewidth. As an example of a family of graphs with unbounded treewidth, consider the family of all  $w \times w$  grids, for all w, each of which has treewidth w ([RS1]).

Given graphs H and G, we say that  $H \leq_i G$ , meaning H is contained in G under the *immersion* order, if and only if a graph isomorphic to H can be obtained from

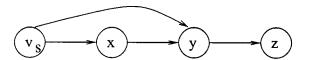

Figure 1.1: A graph and its tree-decomposition of width two

G by a series of the following two operations: taking a subgraph, or lifting a pair of adjacent edges. A pair of adjacent edges uv, vw, with  $u \neq v \neq w$  is lifted by removing uv and vw and adding uw. Figure 1.2 illustrates that  $C_4$  is immersed in  $K_1 + 2K_2$  ([La1]).

The immersion order can also be viewed in terms of edge-disjoint paths: H is immersed in G if and only if there exists an injection from  $V_H$  to  $V_G$  for which the images of adjacent elements of  $V_H$  are connected in G by edge-disjoint paths.

A family F of graphs is said to be immersion closed if  $G \in F$ ,  $H \leq_i G \to H \in F$ . The obstruction set for a family F of graphs is the set of graphs in the complement of F that are minimal in the immersion ordering. Therefore, if F is immersion closed, it has the following characterization: G is in F if and only if there is no H in the obstruction set for F such that  $H \leq_i G$ .

This tells us that there exists a membership algorithm for any immersion-closed family F: simply test for the presence of any immersed obstruction. This will succeed if the obstruction set is finite, which, as we shall soon see, is always the case.

Figure 1.2:  $C_4 \leq_i K_1 + 2K_2$

A quasi-order is a reflexive, transitive relation. A quasi-ordered set  $(X, \leq)$  is well-quasi-ordered if (1) any subset of X has finitely many minimal elements and (2) X contains no infinite descending chain  $x_1 \geq x_2 \geq x_3 \geq \dots$  of distinct elements.

Theorem 1.1 ([RS2]) Graphs are well-quasi-ordered under immersion.

Theorem 1.1 tells us that, given an immersion-closed family of graphs F, a membership algorithm always exists. The following theorem gives us even more: that a polynomial-time algorithm always exists.

**Theorem 1.2** ([FL4]) For every fixed graph H, the problem that takes as input a graph G and determines whether  $H \leq_i G$  is solvable in time  $O(n^{h+3})$ , where h is the order of the largest graph in the obstruction set for F.

Theorems 1.1 and 1.2 together are powerful tools with wide applicability. See [FL1] and [FL2] for many examples. In this work, we focus on problems from the realm of FPGA partitioning, many of which are closed under the immersion order.

Other WQOs are known; one of the most useful in terms of VLSI applications is the *minor* order, under which a graph H is less than or equal to a graph G ( $H \leq_m G$ ) if and only if a graph isomorphic to H can be obtained from G by a series of these two operations: subgraph and edge contraction.

As in the case of the immersion order, there exists a polynomial-time decision algorithm for any minor-closed family of graphs ([RS4]). However, in the case of the

minor order, the running time of the algorithms is much faster. Letting n denote the number of vertices in G, the time to recognize G is  $O(n^3)$  ([RS3]).

Under either the immersion or the minor order, if a family of graphs has treewidth bounded by some constant h, then a linear-time recognition algorithm exists. Given h, and a graph G, it is possible in linear time either to determine whether the treewidth of G exceeds h (in which case G is a "no" instance), or to find a tree-decomposition of G with treewidth at most h ([Bod]). Given such a tree-decomposition, testing for obstruction containment can be done in linear time ([RS3]).

The results just mentioned are *nonconstructive*. They can be used to show the *existence* of polynomial-time *decision* algorithms. They do not address the issue of actual algorithm construction, which depends upon specific knowledge of an obstruction set. They do not give us any information on how to find the obstruction set. They do not give us any information on how to solve the *search* version of the problem; i.e. how to construct positive evidence of a "yes" instance.

While these remarkable theoretical findings give us exciting new tools to cope with previously elusive problems, they also introduce a host of issues that must be resolved for any practical application. Of primary importance are the issues of non-constructivity and high polynomial degree in the case of the immersion order.

## 1.2 Hardware Technology

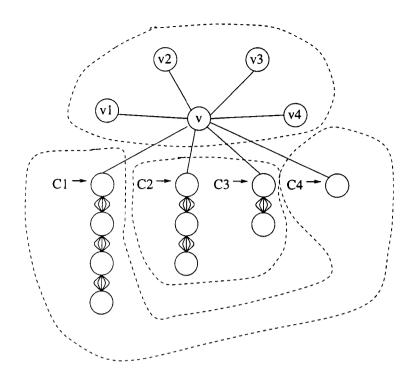

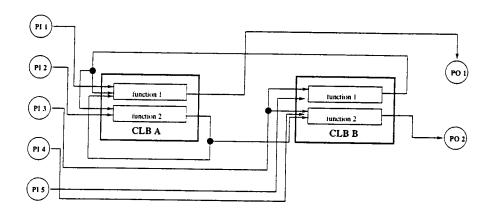

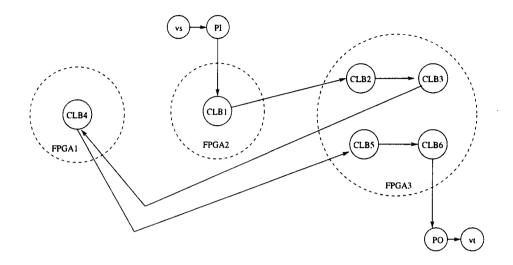

The technology of very-large-scale integrated (VLSI) circuit design continues to progress rapidly. A relatively recent addition to the component library is the field-programmable gate array (FPGA), a collection of functional blocks with programmable connections ([OD]). Figure 1.3 gives a simplified picture of a conceptual FPGA.

The specific function of each block and the connections between blocks are dynamically programmable. This feature enhances affordability and flexibility, and has

Figure 1.3: The FPGA

significant advantages for the development of prototype systems. A given circuit is implemented by partitioning its logic into blocks and connecting the blocks as required. Since circuits are frequently too large to fit on a single chip, they must be partitioned over several FPGAs.

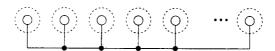

FPGA chips come in a variety of sizes and styles ([X]). Typically, the functional blocks on a chip consist of an array of identical Configurable Logic Blocks (CLBs). Each CLB is a look-up table with a number of inputs (usually two to five), and one or two outputs.

As mentioned earlier, there are many steps involved in taking a circuit from design to physical reality. One of these steps, which can take place either before or after partitioning, is that of technology mapping. Technology mapping refers to the process of transforming a large circuit at the gate level into a system of smaller units that can be realized as a set of communicating CLBs. Although technology mapping can be performed either before or after partitioning, most developers agree that it is more efficient to perform technology mapping first, and then do partitioning on a circuit system of CLBs. The subject of technology mapping will be discussed in more detail

#### in section 3.2.3.

The usual sequence of events, then, is to perform technology mapping first, and then partitioning. The system of CLBs sent to the partitioner can be modelled by a graph, in which a node represents a CLB, and edges represent the connections. Physical connections between CLBs are usually established during a later phase of the design implementation, and are programmable in either direction, so the partitioner may work with an undirected graphical representation of the CLB system. The I/O cells around the periphery of the chip are also programmable in either direction.

In building systems with multiple FPGAs, fabrication technology imposes severe restrictions: limits on pin counts (I/O cells) affect inter-chip connectivity; limits on chip area and density bound FPGA sizes. These physical dimensions give rise to many difficult combinatorial problems, one of which we explore in great detail in the next chapter.

## Chapter 2

## A Fundamental Partitioning Problem

We begin with a very fundamental problem. Although it is actually the simplest of all that we will consider in this work, we find that it is indeed very difficult, and of considerable independent interest.

## 2.1 Problem Definition and Prior Results

A circuit design is usually conceived at a high level, and expressed independently of the hardware in which it will eventually be implemented. Circuit partitioning is the process of dividing a circuit into smaller parts, so that it can be realized by hardware devices. Partitioning a design-level circuit in such a way that it satisfies the physical constraints of a hardware system is a complex problem that has been the subject of extensive study. See [AK], [BKK], [CLCDL], [HK] and [WK] for many examples. In this work, we focus specifically on hardware systems consisting of FPGAs. Within this context, an important question is that of whether a given circuit can be partitioned to fit onto a set of FPGAs such that the size and pin count constraints of each are met. We call this the Min Degree Graph Partition problem (MDGP) ([La1]).

**Instance:** a graph G = (V, E), and two integers k and d.

Question: Is there is a partition of V into disjoint sets  $V_1, \ldots, V_m$  such that  $\forall i : |V_i| \leq k$ , and such that if  $E_i$  is the set of edges with exactly one endpoint in  $V_i$ ,  $\max_{1 \leq i \leq m} |E_i| \leq d$ ?

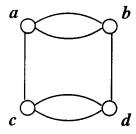

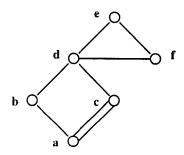

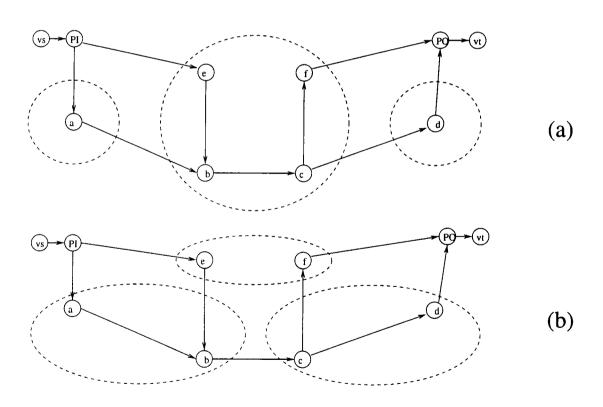

Figure 2.1 shows a "yes" instance of MDGP(k=2,d=2) that has only one satisfying partition:  $V_1 = \{a, b\}, V_2 = \{c, d\}.$

Within this formulation, the parameter k represents the size (in CLBs) of an individual type of FPGA chip, and the parameter d represents the pin-count of a chip. Given a graphical representation of a circuit, with each node representing a CLB and each edge representing a connection between two CLBs, MDGP asks whether the circuit can be realized on a set of FPGAs of a given type.

Note the similarity between this problem and the Graph Partitioning problem of [GJ]. In the latter problem, the goal is to minimize the sum of all edges that have their endpoints in different subsets, and there is no explicit constraint on the number of edges that may emanate from an individual subset. Therefore, Graph Partitioning does not model the situation in which there is a degree constraint on each subset.

There are some important issues in circuit design, such as cost and performance, that are not addressed by this fundamental problem. Nevertheless, MDGP provides a useful starting point for the study of FPGA partitioning from a theoretical perspective. Much of the knowledge gleaned from this basic problem is of benefit in solving broader problems, some of which we will examine more closely in later sections.

Figure 2.1: A partitioning problem

The MDGP problem is very difficult without parameter bounds, via a reduction from Multiway Cut:

**Theorem 2.1** ([Go]) Min Degree Graph Partition is  $\mathcal{NP}$ -complete.

Fortunately, however, the aforementioned fabrication limits can be used to advantage. As long as k and d are bounded, the family of "yes" instances is closed in the immersion order, which leads to the following result.

**Theorem 2.2** ([La1,LP]) For any fixed k and d, MDGP can be decided in polynomial time.

Since the parameters k and d represent actual physical constraints, when partitioning for FPGAs we may assume that these parameters are bounded by the technology at hand. Fixed-parameter MDGP is, therefore, a relevant problem from the perspective of circuit partitioning. To distinguish fixed-parameter MDGP from generalized MDGP, we shall use MDGP(k,d) to denote the former.

In section 1.1 we saw that, for any family of graphs closed under the immersion order and of bounded treewidth, a linear-time recognition algorithm exists. Unfortunately, the family of "yes" instances of MDGP(k,d) is not of bounded treewidth. To see this, consider MDGP(1,4). Even this simple family of graphs contains the  $w \times w$  grid for any w, a graph with treewidth w.

Prior to this time, little more was known about the complexity of MDGP(k,d), and no efficient algorithms, or even brute force algorithms, were known to exist. Not much more could be said other than that MDGP(k,d) was nonconstructively decidable in polynomial time. Whether it was solvable in low-order polynomial time was an open question, as recently as 1995 ([LP]). Many issues remained, including the following:

• WQO-based solutions are inherently nonconstructive. They depend on the existence of finite obstruction sets and, in general, we do not know what these obstruction sets are, or how to find them.

- Although the algorithms are polynomially bounded, the degree of the polynomial is high:  $O(n^{h+3})$ , where h is the order of the largest obstruction. This polynomial presents yet another dimension of nonconstructivity: since we do not know the obstruction set, or even the order of the largest obstruction, we do not know the exact degree of the polynomial. Sometimes efficient algorithms can be devised to test for specific obstructions, but this is a difficult task (BGLR).

- Obstruction sets are very difficult to identify. In some cases, obstruction set isolation has been performed exhaustively as part of a major research effort ([KiL]). Other researchers have developed machinery to generate minor-minimal "no" instances of some graph families of bounded treewidth ([CD]). However, in general, there exists no easy, widely-applicable method of finding obstruction sets.

- WQO-based solutions are *decision* algorithms: they simply tell us whether or not a given graph is a member of a particular graph family. They do not address the corresponding *search* problem by constructing evidence. In most practical problems, knowing that a graph is a "yes" instance is not enough. In the case of graph partitioning, for example, a solution in the form of a satisfying partition is essential.

- WQO-based solutions apply only to ordinary graphs. Practical problems, especially those that model VLSI problems, are often represented more accurately by hypergraphs. Although WQOs are known to exist on hypergraphs ([GGL], [Se]), these orders have not yet been shown to be of practical importance for these types of problems.

In subsequent sections, we will address each of these issues.

## 2.2 New Results

We know by Theorem 2.2 that MDGP(k,d) is solvable in polynomial time. In this section, we present some tools that will ultimately be used to show that MDGP(k,d) is actually solvable in linear time. These tools will also assist in formulating self-reduction strategies, finding MDGP(k,d) obstruction sets, and understanding the complexity of MDGP when it can be assumed that the instance graph has a predefined structure.

#### 2.2.1 Algorithmic Tools

We now present some definitions, observations and lemmas that will be of general use throughout most of this work. (Recall that we refer to fixed-parameter MDGP as MDGP(k,d).)

**Observation 2.1** A star graph (see Figure 2.2) with k + d rays is an obstruction to MDGP(k,d); therefore, no obstruction to MDGP(k,d) contains a vertex with more than k + d neighbors.

Similarly, no "yes" instance of MDGP(k,d) contains a vertex with more than d+k neighbors; hence the "yes" family has bounded degree.

Figure 2.2: A star graph with six rays

**Definition 2.1** Let  $N_p(v)$  denote  $\{v\} \cup \{w : \exists a \text{ path from } v \text{ to } w \text{ of length } \leq p\}$ .

**Definition 2.2** A connected subset of a graph G is a subset  $S \subseteq V_G$  such that the subgraph of G induced by S is connected.

**Lemma 2.1** G is a "yes" instance of MDGP(k,d) iff there exists a solution in which every subset is connected; thus, in this solution, every vertex v is partitioned only with other vertices in  $N_{k-1}(v)$ .

**Proof** If there exists such a solution for G, then G is a "yes" instance.

For the converse, assume that G is a "yes" instance, and that we have a satisfying partitioning. Consider any subset S such that the subgraph G' of G induced by S is not connected. We can then separate S into distinct connected subsets, one for each connected component of G'. Each of these is of size less than k. Additionally, each is of degree no more than d, because there exist no edges between the new subsets. Because every subset is now connected and of size no more than k, each vertex  $v \in S$  is partitioned only with other vertices in  $N_{k-1}(v)$ .  $\square$

**Definition 2.3** Given k and d, let  $c_p$  denote the value  $1 + \sum_{i=1}^{p} (k+d)(k+d-1)^{i-1}$ .

**Lemma 2.2** If G is an obstruction to MDGP(k,d), then  $\forall v \in V, \forall p > 0, |N_p(v)| \leq c_p$ .

**Proof** By Observation 2.1, v has at most k+d immediate neighbors, so  $|N_1(v)| \le 1 + (k+d)$ . Each neighbor at distance q > 0 from v has at most k+d-1 neighbors not contained in  $N_{q-1}(v)$ , so  $|N_p(v)| \le 1 + \sum_{i=1}^p (k+d)(k+d-1)^{i-1}$ .  $\square$

It is useful to observe that, when k+d>2,  $c_p=1+(k+d)\times\frac{(k+d-1)^p-1}{k+d-2}$ .

**Definition 2.4** A "kd-satisfying subset" is a subset of size no more than k and degree no more than d.

**Definition 2.5** A "kd-candidate subset" is a connected kd-satisfying subset. Given k, d and a vertex v, let  $C_v$  denote the set of all kd-candidate subsets containing v.

We note that, because a kd-candidate subset is connected and of size no more than k, its diameter is bounded by k-1. Furthermore, for every v in some kd-candidate subset C, every other vertex in C is in  $N_{k-1}(v)$ .

For example, consider the graph G in Figure 2.3 as an instance of MDGP(3,2). Then  $N_{k-1}(a) = N_2(a) = \{a, b, c, d\}$ , and  $C_a = \{\{a, c\}, \{a, b, c\}\}$ .

**Lemma 2.3** Given kd-satisfying subsets C1 and C2, either C1 - C2 or C2 - C1 is a kd-satisfying subset. <sup>1</sup>

**Proof** Since neither C1 - C2 nor C2 - C1 can have size exceeding k, we need only consider their respective degrees.

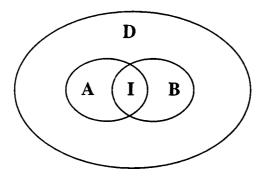

If  $C1 \cap C2 = \emptyset$ , then we are done. Otherwise, let  $I = C1 \cap C2$ , A = C1 - C2, B = C2 - C1, D = V - C1 - C2 (see figure 2.4).

Denote by  $N_{AB}$  the number of edges having an endpoint in A and an endpoint in B.  $N_{AD}$ ,  $N_{AI}$ ,  $N_{BD}$ ,  $N_{BI}$  and  $N_{DI}$  have analogous meanings. The degree of C1 is  $N_{AD} + N_{AB} + N_{DI} + N_{BI}$ , and the degree of C2 is  $N_{AB} + N_{BD} + N_{AI} + N_{DI}$ .

Figure 2.3: An instance of MDGP(3,2)

<sup>&</sup>lt;sup>1</sup>Independently proved in [CLCDL].

Figure 2.4:  $C1 = A \cup I, C2 = B \cup I$

By the definitions above, we have

$$N_{AD} + N_{AB} + N_{DI} + N_{BI} \le d$$

and

$$N_{AB} + N_{BD} + N_{AI} + N_{DI} \le d.$$

Summing yields

$$N_{AD} + 2N_{AB} + 2N_{DI} + N_{BI} + N_{BD} + N_{AI} \le 2d,$$

so

$$N_{AD} + 2N_{AB} + N_{BI} + N_{BD} + N_{AI} \le 2d.$$

Thus either

$$N_{AB} + N_{AI} + N_{AD} < d$$

or

$$N_{AB} + N_{BI} + N_{BD} \le d.$$

The former bounds the degree of C1-C2, the latter the degree of C2-C1.  $\square$

**Lemma 2.4** Given kd-satisfying subsets  $C_1, C_2, ..., C_p$ , a disjoint set of kd-satisfying subsets  $D_1, D_2, ..., D_q$  exists such that  $C_1 \cup C_2 \cup ... \cup C_p = D_1 \cup D_2 \cup ... \cup D_q$ .

**Proof** The proof is by induction on p. For the basis case, p=1, the set of subsets is already disjoint and satisfying. As inductive hypothesis, assume that, given  $C_1, C_2, ..., C_p, p \geq 1$ , an appropriate set of subsets  $D_1 \cup D_2 \cup ... \cup D_q, q \geq 1$ , exists. Given  $C_{p+1}$ , we construct a set of kd-satisfying subsets  $D_1 \cup D_2 \cup ... \cup D_{q'}$  such that  $D_1 \cup D_2 \cup ... \cup D_{q'} = C_1 \cup C_2 \cup ... \cup C_{p+1}$ . Initially  $D_1 \cup D_2 \cup ... \cup D_{q'} = D_1 \cup D_2 \cup ... \cup D_q$ , so  $D_1 \cup D_2 \cup ... \cup D_{q'} = C_1 \cup C_2 \cup ... \cup C_p$ , and the  $D_i$ 's are disjoint and satisfying. Let  $T = C_{p+1}$ . For each  $D_i, 1 \leq i \leq q'$ , we do the following. If  $D_i \cap T = \emptyset$ , do nothing. Otherwise,  $D_i \cap T = I \neq \emptyset$ , with  $I \cap D_j = \emptyset$ ,  $\forall 1 \leq j \leq q', j \neq i$ . By Lemma 2.3, either  $D_i - T$  or  $T - D_i$  is satisfying. If the former, we change  $D_i$  to  $D_i - T$ ; if the latter, we change T to  $T - D_i$ . At the end of consideration of each  $D_i$ , if T is nonempty, q' is incremented by one, and  $D_{q'}$  is set to T. Finally, any empty  $D_i$  may be removed, and q' decremented accordingly.  $\square$

The proof of Lemma 2.4 suggests a subset disjointing algorithm. Such an algorithm is used by [CLCDL] in an FPGA partitioning heuristic. The heuristic first forms subsets to satisfy constraints, and then makes the subsets disjoint in a later step. Our work proceeds further, however, as we shall now describe.

The algorithm suggested by the proof of Lemma 2.4 is of quadratic-time complexity. It can, however, be implemented to run in time linear with respect to |V|, assuming we are given one kd-candidate (rather than mere kd-satisfying) subset for each  $v \in G$ . In the proof described above, T is compared against each  $D_i$ . If we begin with kd-candidate subsets, however, there is only a constant number of  $D_i$ 's with which any T can have a nonempty intersection. Each of T,  $D_i$  is initially formed from a kd-candidate subset, and never made larger. If there exist  $u \in T$ ,  $v \in D_i$  such that  $u \notin N_{2\star(k-1)}(v)$ , the intersection of T,  $D_i$  must be empty, by the following reasoning. Suppose otherwise:  $\exists x \in T \cap D_i$ . Because  $x \in T$  and  $u \in T$ , it must be the case that

<sup>&</sup>lt;sup>2</sup>Independently claimed in [CLCDL].

the distance from u to x is at most k-1. Because  $x \in D_i$  and  $v \in D_i$ , it must be the case that the distance from x to v is also at most k-1. Therefore, the distance from u to v is at most 2 \* (k-1), which contradicts  $u \notin N_{2*(k-1)}(v)$ .

Therefore, each subset can be indexed by the vertex for which it serves as a kd-candidate subset, and no checking need be done of subsets indexed by vertices "too far apart." Specifically, the subset disjointing algorithm proceeds as follows. We are given a set of p = |V| kd-candidate subsets, one for each  $v \in V$ . As the algorithm progresses, and subsets are modified, they may lose their connectivity. They, will, however, always be kd-satisfying. Furthermore, because vertices are never added to subsets, it will always be the case that for any subset  $C, u \in C, v \in C \rightarrow u \in N_{k-1}(v)$ . We will denote the subset indexed by vertex v as  $S_v$ .

Step 1: For each vertex v, compute  $\{x | x \in N_{2*(k-1)}(v)\}$ .

Step 2: This step consists of an outer loop, which executes for each vertex  $v_i$ ,  $2 \le i \le |V|$ . For each  $v_i$ , an inner loop executes for each  $\{v_j|v_j \in N_{2*(k-1)}(v_i), \text{ and } j < i\}$ . The inner loop is as follows:

if

$$S_{v_i} \cap S_{v_j} \neq \emptyset$$

then

if  $S_{v_i} - S_{v_j}$  is of degree no more than  $d$

then

$$S_{v_i} = S_{v_i} - S_{v_j}$$

else

$$S_{v_j} = S_{v_j} - S_{v_j}$$

Step 1 executes in linear time, as does the outer loop of Step 2. The running time of the inner loop of Step 2 is bounded by a constant. Therefore, the complexity of the entire subset disjointing algorithm is linear.

This algorithm is of linear time complexity, does not possess large constants of proportionality, and runs quickly in our experimentation. It does, however, require the availability of |V| kd-candidate subsets, the computation of which is much more costly, as we shall see in Section 2.2.3.

The proposition that follows is an important tool in our subsequent work, and finds many applications within, including the following:

- finding linear-time decision and search algorithms for MDGP(k,d), as well as a host of related problems

- showing that the obstruction set for MDGP(k,d) is computable

- characterizing the simple tree obstructions to MDGP(k,d)

- proving complexity results for MDGP and other problems

Additionally, it has also been used in ([Go]) in which it was dubbed the *Locality* Condition, a term that we will retain here.

Proposition 2.1 The Locality Condition: G is a "yes" instance of MDGP(k,d) iff  $\forall v \in V, C_v \neq \emptyset$ .

**Proof** Suppose  $\forall v \in V, C_v \neq \emptyset$ . Then, by Lemma 2.4, a satisfying partition can be found, ensuring that G is a "yes" instance. For the converse, suppose G is a "yes" instance. Then, by Lemma 2.1 and by the definition of kd-candidate subset,  $\forall v \in V, C_v \neq \emptyset$ .  $\square$

#### 2.2.2 Self-reduction

It is sometimes possible to solve a search problem by reducing it to a related decision problem. For example, one might seek to find a satisfying subset assignment for Min Degree Graph Partition with the aid of a routine that merely tells whether such an assignment exists.

This approach to algorithm design is called *self-reducibility*, and has been formulated in many ways in the literature. In its most limited form, an assortment of restrictions is placed on the decision algorithm, its input and the lexicographic

position of the output produced (see, for example, [Sc]). In more general forms, in-put/output limitations are eliminated and decision algorithms quite distant from the original problem are permitted (see, for example, [FL3]). Additional variations exist, some even incorporating randomness or parallelism (see, for example, [FF], [KUW]).

It is not difficult to see that, for any fixed k and d, MDGP is self-reducible in polynomial time. That is, one can construct a satisfying subset assignment, if any exist, with at most a polynomial number of calls to a decision algorithm, known from the last section also to run in polynomial time. It can in fact be self-reduced with only a linear number of calls.

**Theorem 2.3** The search version of MDGP(k,d) can be solved in O(np(n)) time, where p(n) denotes the time required to solve the decision version of the problem.

**Proof** First, use the decision algorithm to ensure that the graph is a "yes" instance. If the graph is a "yes" instance, we know, by Lemma 2.1 that there exists a solution in which every subset is connected. We now describe an algorithm that constructs such a solution. The algorithm does this by modifying the input graph G. As subsets are constructed, if a vertex v is assigned to a nonempty subset S, this assignment is forced by the placement of at least d+1 copies of an edge between v and some vertex  $w \in S$ . At the end of the algorithm, the subsets in the modified graph are identified as follows. Vertices u and v are in the same subset S iff there exists a path from u to v such that there are at least d+1 copies of each edge in the path.

In what follows, we will refer to a vertex assigned to a subset as a *committed* vertex. Those not yet assigned to a subset are *uncommitted*. Initially, no vertices are committed. An outer loop executes at most once for each vertex.

An arbitrary uncommitted vertex v is selected for this inner loop, and v is now committed to a new subset S. We next show how, in an inner loop, S is constructed in O(p(n)) time.

Every time the inner loop begins, the current version of the graph is known to be a "yes" instance. By Lemma 2.1, we know, therefore, that there exists a solution in which every subset is connected (as the algorithm progresses, it zeroes in on one of perhaps many potential initial solutions). The number of uncommitted immediate neighbors of v is bounded by a constant; these vertices form a "neighbor pool." At all times, the neighbor pool consists of all uncommitted immediate neighbors to vertices in S. Initially all vertices in the neighbor pool are unmarked. A vertex in the neighbor pool will be marked if it can be determined that its addition to S produces a graph that is a "no" instance.

If at any time in the inner loop there are no unmarked vertices in the neighbor pool, then there is no way to expand S while maintaining its connectivity. In that case, by Lemma 2.1, and the fact that the modified graph remains a "yes" instance, it must be that S is a kd-candidate subset, and we exit the inner loop.

We select any unmarked vertex w from the neighbor pool, and any vertex  $y \in S$  for which an edge wy exists. We augment the graph with d additional copies of wy. If the augmented graph is a "no" instance, the added edges are taken back out. Additionally, vertex w is marked, because its commitment to S produces a graph that is a "no" instance. If the augmented graph is still a "yes" instance, then the extra edges are retained. Additionally, w is now committed to S. All uncommitted neighbors of w are added to the neighbor pool. If the size of S is now k, then S cannot be expanded; thus the graph is a "yes" instance, and we discard the neighbor pool and exit the inner loop. If there are no unmarked vertices in the neighbor pool, then S cannot be made larger while preserving connectivity; thus the graph is still a "yes" instance, and we discard the neighbor pool and exit the inner loop. If neither of these conditions occurs, then the inner loop is not exited, and a new unmarked w is selected.

The neighbor pool is always of size bounded by a constant. This is because the number of neighbors of every vertex is bounded, and no more than k vertices are ever in S. The process continues until a subset size of k is reached, or until no neighbor in the neighbor pool can be pulled into the subset. One of the inner loop terminating

#### 2.2.3 More on Decision and Search

**Theorem 2.4** The decision version of MDGP(k,d) can be solved in linear time.

**Proof** In linear time, any graph containing a vertex with at least k + d neighbors can be eliminated as a "no" instance. Otherwise,  $|N_{k-1}(v)|, \forall v \in V$  is bounded by a constant;  $|C_v|$  for each v is of constant size; the set of all kd-candidate subsets can be computed in linear time; and by the Locality Condition, a solution exists iff each set is nonempty.  $\square$

Theorems 2.3 and 2.4 yield a quadratic time search algorithm for MDGP(k,d). However, we can do even better than that.

**Theorem 2.5** The search version of MDGP(k,d) can be solved in linear time.

**Proof** If a solution is known to exist, one can be constructed as follows. Find an arbitrary kd-candidate subset for each vertex. This can be done in linear time, since the complete set of kd-candidate subsets for each vertex can be computed in constant time. Eliminate overlapping as described in the proof of Lemma 2.4. As per the discussion following that proof, this can be done in linear time.  $\square$

It must be pointed out that, although solving MDGP(k,d) is asymptotically efficient, in practice this is not really the case. This is due to the large constants of proportionality introduced by our methods. The search algorithm for MDGP(k,d) consists of two parts: 1) finding kd-candidate subsets for each vertex, and 2) eliminating overlapping. The second part is quite efficient, as discussed following the proof of Lemma 2.4. This is not the case, however, for the first part.

Finding a kd-candidate subset containing some vertex v can be done by examining every possible combination of at most k-1 vertices from  $N_{k-1}(v)$ . Since  $|N_{k-1}(v)| \le c_{k-1}$ , the constant of proportionality for this method is bounded by  $\sum_{i=0}^{k-1} {c_{k-1}-1 \choose i}$

$>\sum_{i=0}^{k-1} {2^k \choose i} > {2^k \choose k-1} > (\frac{2^{k-k+2}}{k-1})^k$ . It may not be necessary to consider all of these combinations, since a kd-candidate subset must be connected. However, the multiplicative constant  $c_{k-1}$  introduced by the size of  $N_{k-1}(v)$  remains, and this is exponential in k.

Although the constants of proportionality of these methods are large and prohibitive, they pale in comparison to those introduced by WQO methods. WQO constants arise from testing for minor containment, which consists of "towers of 2's" functions. See [FL1], [BL], and [RS1] for more on this subject.

### 2.2.4 Obstruction Sets

If the obstruction set for an immersion-closed family of graphs is known, then a constructive decision algorithm automatically exists. Unfortunately, there exist very few examples of immersion- or minor-closed families of graphs for which complete obstruction sets have been isolated. As an example of the difficulty of identifying complete obstruction sets, the reader is referred to [KiL], the major result of which is the identification of the complete 110-element obstruction set for a single instance of a minor-closed family of graphs.

In this section, we show that, given any fixed k and d, the obstruction set for MDGP(k,d) is computable. This enables the generation, in principle, of the obstruction set for any fixed-parameter instance of MDGP. Such a task is formidable in its magnitude, however, as we shall see later.

**Observation 2.2** An obstruction to MDGP(k,d) contains at most d+1 copies of any edge.

**Lemma 2.5** An obstruction to MDGP(k,d) contains at most  $c_k$  vertices.

**Proof** Suppose G is an obstruction to MDGP(k,d), with  $|V| > c_k$ . Because G is a "no" instance, by the Locality Condition there exists some v such that  $C_v = \emptyset$ . By

Lemma 2.2 there exists some  $w \in V$  such that  $w \notin N_k(v)$ . Consider  $G' = G - \{w\}$ . Because every element in  $C_v$  must be drawn from  $N_{k-1}(v)$ ,  $C_v$  for G' is also empty. Thus, by the Locality Condition, G' is a "no" instance, so G was not minimal.  $\square$

**Theorem 2.6** The obstruction set to MDGP(k,d) is computable.

**Proof** By Lemma 2.5 there is a bound on the number of vertices in an obstruction, and by Observation 2.2 the number of copies of any edge in an obstruction is bounded. The obstruction set can be computed by generating and checking the finite number of graphs that satisfy these bounds. □

Although this is a finite number, it is very large. The upper bound on the number of vertices is  $c_k$ , with at most  $\frac{c_k^2-c_k}{2}$  edges, each of multiplicity up to d+1. As a rough upper bound on the number, we consider the number of labelled simple (p,q) graphs (graphs with p vertices and q edges). This number is given by  $\binom{p}{2}$  ([HP]). A better, but still inexact, bound would be  $g_p$ , the number of unlabelled graphs of p vertices, although even this would not take into account edge multiplicity.

Counting unlabelled graphs is difficult (see [HP] for a thorough discussion of this topic). The precise answer for  $g_p$  is known, but cannot be stated simply. An approximate answer of  $g_p \sim \frac{2^{\binom{p}{2}}}{p!}$  is also known ([Wi]). This number is greater than  $2^p$  for  $p \geq 10$ , which can be seen as follows.

We note that  $\frac{2^{(\frac{p^2-p}{2})}}{p!} = \frac{2^{(\frac{p^2-p}{2})}}{p!} = \frac{((\sqrt{2})^{p-1})^p}{p!} > (\frac{(\sqrt{2})^{p-1}}{p})^p$ . This last quantity is larger than  $2^p$  when  $(\sqrt{2})^{p-1} > 2p$ , which is always the case when  $p \ge 10$ .

Figure 2.5 shows some sample MDGP(k,d) obstructions for small values of k and d (note that MDGP(k,d) obstructions must be connected). From these examples, several structural observations are evident. For example,  $C_{k+1}$  is an obstruction for MDGP(k,1); a graph with one vertex v of degree d+1 and no other vertices except for v's immediate neighbors is an obstruction for MDGP(1,d) (which, in the case of simple graphs, is a star graph).

| <b>d</b> | 1              |              | 2             |                                                   | 3 |             |  |

|----------|----------------|--------------|---------------|---------------------------------------------------|---|-------------|--|

| 1        | ٥              |              | •             | $\Lambda$                                         | • | <b>^</b>    |  |

| _        | $\wedge$       |              | <b>○</b>      |                                                   |   | •           |  |

| 2        | Δ              | $\Lambda$    |               | ♠                                                 |   |             |  |

|          | $\hat{\Box}$   |              |               |                                                   | X | $\triangle$ |  |

| 3        | $\diamondsuit$ | $\bigwedge$  | <b>\$ 4 4</b> | <ul><li>♦</li><li>♦</li><li>★</li><li>♦</li></ul> |   | <b>♦</b> *  |  |

|          |                | $ \uparrow $ | *             |                                                   |   |             |  |

Figure 2.5: Some MDGP(k,d) obstructions

We next show that there is an exponential lower bound on the size of this obstruction set. We do this by completely characterizing the simple tree obstructions to MDGP(k,d), and then showing an exponential lower bound on trees satisfying this configuration. Thus, all trees defined and discussed in the remainder of this section are simple.

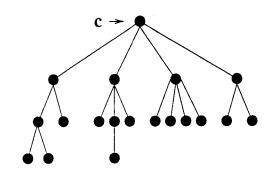

We define a kdq-tree  $T_{kdq}$ , for  $1 \le q \le k$  as follows:

- 1.  $T_{kdq}$  contains a vertex c with  $|N(c)| = \delta(c) = d + q$ .

- 2. Some set of q neighbors of c form the roots of subtrees. These subtrees are of sizes  $s_1, s_2, ..., s_q$ , where  $s_1 + s_2 + ... + s_q = k$ .

- 3. Each of the remaining d neighbors of c forms the root of a subtree of size  $\max(s_i)$ ,  $1 \le i \le q$ .

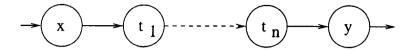

Figure 2.6 shows a sample kdq-tree for k=8, d=2, q=2. Figure 2.7 shows all of the kdq-trees for k and d ranging from 1-3.

For any tree T and vertices  $u, v | \exists uv \in E_T$ , we will denote by  $T_{uv}$  the connected subtree of T - uv with root v. Any such connected subtree, relative to some vertex u, will be referred to as a subtree of u.

Lemma 2.6 Any kdq-tree  $T_{kdq}$  is a "no" instance to MDGP(k,d).

**Proof** Assume some  $T_{kdq}$  is a "yes" instance. Consider any subset S containing c in a satisfying partition of  $T_{kdq}$ . For each subtree  $T_{cy}$  of c, one of the following must hold:

- 1.  $y \notin S$ . The degree of S is at least one for each such y.

- 2.  $y \in S$ , but  $T_{cy}$  not entirely included in S. The degree of S is at least one for each such y.

- 3.  $y \in S$ , and  $T_{cy}$  entirely included in S.

Figure 2.6: A kdq-tree (k = 8, d = 2, q = 2)

| $k \downarrow \frac{d}{}$ | 1        | 2         | 3             |  |

|---------------------------|----------|-----------|---------------|--|

| 1                         | ^        | $\Lambda$ |               |  |

| 2                         | <b>△</b> |           | $\rightarrow$ |  |

| 3                         |          |           |               |  |

Figure 2.7: kdq-trees

Since the size of S is bounded by k, and by the definition of  $T_{kdq}$ , there can be at most q-1 y's of the third type. The total number of y's is d+q, therefore there are at least d+1 y's of the first and second types, each contributing at least one to  $\delta(S)$ . This contradicts the assumption that  $T_{kdq}$  was properly partitioned.  $\square$

Lemma 2.7 Any kdq-tree  $T_{kdq}$  is a minimal "no" instance to MDGP(k,d).

**Proof** To show that  $T_{kdq}$  is minimal, we must consider the graph obtained by any immersion operation, and show that some partition P exists. An immersion operation can be one of 1) edge removal; 2) vertex removal; or 3) lifting a pair of adjacent edges.

Before considering each of these operations in turn, we examine four scenarios:

Scenario 1: Suppose the degree of c is reduced by one of these operations: 1) removal of an edge cx or 2) removal of a vertex x adjacent to c. In either of these cases, at least one edge cx is removed. By the definition of kdq-tree, there exist q-1 subtrees of c, not including  $T_{cx}$ , of total size no more than k-1. A subset S of size no more than k can be formed consisting of these q-1 subtrees along with c. The degree of c was reduced to at most d+q-1 by the immersion operation, and at least q-1 subtrees of c have been included in S, which is therefore of degree no more than d. What remains of  $T_x$  can be partitioned into a subset by itself, as can the other subtrees of c. Each of these subsets is of size no more than k, and degree 1 or 0.

Scenario 2: Suppose two edges uc and cw, both incident on c, are lifted. By the definition of kdq-tree, there exist q-1 subtrees of c, not including  $T_{cu}$ , of total size no more than k-1. A subset S of size no more than k can be formed by taking the union of c with these q-1 subtrees. The degree of c was reduced to at most d+q-2 by the immersion operation, and at least q-1 subtrees of c have been included in S, which is therefore of degree no more than d. All other subtrees of c can be partitioned by themselves into subsets of degree 1.

Scenario 3: Suppose some immersion operation does not reduce the degree of c, but disconnects the graph. There would then exist some set of at least q subtrees of c

of size no more than k-1, along with some disconnected component. The q subtrees could be partitioned along with c into a subset of degree d and size no more than k. The remaining subtrees of c could be partitioned into subsets of size no more than k and degree 1. The disconnected component could be partitioned by itself into a subset of size no more than k and degree 0.

Scenario 4: Suppose some immersion operation does not reduce the degree of c or disconnect the graph, but results in reduction in the size of some subtree of c. This situation is the same as Scenario 2, except that there is no disconnected component.

We now examine each of the three immersion operations in turn.

- 1. Edge removal. If an edge adjacent to c is removed, Scenario 1 results. Otherwise, Scenario 3 results.

- 2. Vertex removal. If the vertex removed is c, each subtree of c fits into a subset of size no more than k and degree 0. If the vertex removed is one adjacent to c, we have Scenario 1. If the vertex is of degree 1, we have Scenario 4. Otherwise, we have Scenario 3.

- 3. Lifting a pair of adjacent edges. If both of the lifted edges were incident on c, we have Scenario 2. Otherwise, the result is Scenario 3.

Lemma 2.8 For any tree T, and any  $v \in V_T$  with  $\delta(v) > d$ , any kd-candidate subset C including v includes at least  $\delta(v) - d$  entire subtrees of v. Additionally, if any set of at least  $\delta(v) - d$  entire subtrees of v is of total size at most k - 1, these subtrees, along with v. form a kd-candidate subset.

**Proof** Suppose C is a kd-candidate subset for v, but includes fewer than  $\delta(v) - d$  entire subtrees of v. Then C excludes part of more than  $\delta(v) - (\delta(v) - d) = d$  subtrees of v, each of which contributes at least 1 to the degree of C, and thus C is not a kd-candidate subset including v, a contradiction.

For the second statement of the lemma, we need only determine the degree of the subset, because its size is at most k, and it is connected. The degree of the subset is exactly 1 for every excluded subtree of v, and this number is no more than  $\delta(v) - (\delta(v) - d) = d$ . Therefore, the subset is of degree no more than d, and satisfies the definition of kd-candidate subset including v.  $\square$

We observe that Lemma 2.8 also holds for forests.

### Lemma 2.9 Any tree obstruction to MDGP(k,d) is a kdq-tree.

**Proof** Suppose we have a tree obstruction T. Because T is a "no" instance, by the Locality Condition there exists some vertex  $v \in V(T)$  that has no kd-candidate subset. Because v has no kd-candidate subset,  $\delta(v) > d$ , and because T is an obstruction, by Observation 2.1  $\delta(v) \leq d + k$ . For  $1 \leq q = \delta(v) - d \leq k$ , we have:

1. T contains a vertex c = v with  $|N(c)| = \delta(c) = d + q$ .

Suppose that, associated with this vertex c, there exists a set of q subtrees of c containing a total of fewer than k vertices. Then, by Lemma 2.8, c would have a kd-candidate subset. Therefore, every such set of q subtrees of c contains at least k vertices.

To see than no such set contains more than k vertices, note that removal of any vertex of degree 1 from any subtree of c would still yield a set of q subtrees of c containing at least k vertices, and by Lemma 2.8, c would still have no kd-candidate subset. Thus such a T would not be minimal.

We conclude that:

2. Some set of q neighbors of c form the roots of subtrees. These subtrees are of sizes  $s_1, s_2, ..., s_q$ , where  $s_1 + s_2 + ... + s_q = k$ .

Now, consider the remaining d neighbors of c, and the subtrees of which they are roots. By reasoning analogous to that above, we note the following: if one of these subtrees is of size less than  $\max(s_i)$ ,  $1 \le i \le q$ , then c has a kd-candidate subset; if one of these subtrees is of size greater than  $\max(s_i)$ ,  $1 \le i \le q$ , then T is not minimal. Thus it must be the case that:

3. Each of the remaining d neighbors of c forms the root of a subtree of size  $\max(s_i)$ ,  $1 \le i \le q$ .

Therefore, by 1, 2, and 3, T satisfies the definition of kdq-tree.  $\Box$

**Theorem 2.7** A tree is an obstruction to MDGP(k,d) iff it is a kdq-tree.

**Proof** Follows from Lemmas 2.7 and 2.9. □

We now address the issue of a lower bound on the size of the MDGP(k,d) obstruction set.

**Theorem 2.8** When k > d + 4, the size of the obstruction set of MDGP(k,d) is at least  $max\{2^{d+1}, 2^{k-3}\}$ .

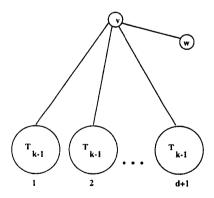

**Proof** Consider any tree consisting of a root vertex with d+2 children: one degree-1 vertex, and d+1 roots of arbitrary  $T_{k-1}$  trees (trees containing k-1 vertices). (See Figure 2.8.) Any such tree is a kdq-tree; specifically it is a kd2-tree. By Theorem 2.7, such a tree is an obstruction to MDGP(k,d).

Figure 2.8: A general tree obstruction to MDGP(k,d)

We begin by examining the number of nonisomorphic rooted trees containing p vertices. (The topic of exactly counting rooted trees is thoroughly discussed in [HP]; here we seek only to show an exponential lower bound.) We show by construction that the number of nonisomorphic rooted trees with p vertices ( $p \ge 2$ ) is at least  $2^{p-2}$ . For p = 2, we observe that there exists only one rooted tree containing 2 vertices. For p > 2, we construct 2 trees with p vertices for each nonisomorphic rooted tree  $T_{p-1}$  containing p-1 vertices. One of these trees consists of a new root vertex with the root of  $T_{p-1}$  as its single child. The other tree is identical to  $T_{p-1}$ , except for the addition of a new vertex of degree 1 incident on the root. Figure 2.9 shows the nonisomorphic rooted trees containing 2-5 vertices constructed by this method. The roots are double-circled in the figure. Arrows indicate the most recently added vertices.

No two of these newly constructed trees are isomorphic. If they were, their roots would have to be of the same degree, hence they were constructed from nonisomorphic subtrees. Removing the most recently added vertex would yield isomorphic subtrees.

Figure 2.9: Some nonisomorphic rooted trees

We observe that, in any graph matching the configuration of Figure 2.8, there is only one vertex that can be designated as c. Any other vertex that has one subtree of size 1 must have at least one other subtree of size exceeding k.

The general obstruction shown in Figure 2.8 contains rooted subtrees with k-1 vertices each; hence even if all of these subtrees had the same configuration, the number of such obstructions is at least  $2^{k-3}$ .

Additionally, this general obstruction contains d+1 of these rooted subtrees. Even if no repetition were allowed in the configuration of these subtrees, the number of obstructions matching this configuration would still be bounded below by  $\binom{2^{k-3}}{d+1} > (\frac{2^{k-3}-d}{d+1})^{d+1} > 2^{d+1}$  when  $2^{k-3} > 3d+2$ . This is always the case when k > d+4.  $\square$  It should be mentioned that the lower bound on MDGP(k,d) obstruction set size established here is quite loose. In addition to the omissions mentioned in the proof above, no attempt has been made to count kdq-trees in the case of  $q \neq 2$ . Furthermore, the MDGP(k,d) obstruction set includes many graphs that are not trees. Even without considering all of these possibilities, however, the MDPG(k,d) obstruction set is seen to be exponential in both k and d.

## 2.2.5 Tractability on Restricted Classes of Graphs

Thus far, we have considered the fundamental problem from a very general perspective. In reality, the graphs that serve as input to real instances of FPGA partitioning might not be so generalized. Circuits may, in fact, have a certain measure of underlying structure. Many circuit graphs are of treewidth at most two, a class of graphs known as series-parallel. In some situations it may even be possible to assume that the input graph is a tree or a forest, or even a simple tree or simple forest. Although the tractability of MDGP on most of these graph families is still an open question, we can show that MDGP, restricted to simple trees (and hence, forests) is efficiently solvable.

**Theorem 2.9** MDGP, restricted to simple trees, is decidable in  $O(n^2 \log n)$  time.

**Proof** Given a simple tree T, first check whether any vertex has degree d+k or more. If so, T is a "no" instance, because it contains an obstruction (the star graph with d+k vertices).

Otherwise, for each  $v \in T$ , do the following. If the degree of v is no more than d, then  $\{v\}$  is a kd-candidate subset for v. If the degree of v is more than d, we perform the following steps:

- 1. Compute the size of each subtree of v. This takes O(n) time.

- 2. Sort the sizes of the subtrees of v. This takes  $O(n \log n)$  time.

- 3. Check the total size t of the smallest  $\delta(v) d$  subtrees of v. This takes O(n) time.

- 4. If t is less than k, then v along with the set of smallest  $\delta(v) d$  subtrees of v form a kd-candidate subset, by Lemma 2.8. Otherwise, by Lemma 2.8, v has no kd-candidate subset.

By the Locality Condition, if any vertex has no kd-candidate subset, then T is a "no" instance, otherwise it is a "yes" instance.

The outer loop executes at most once for every vertex, and the inner loop is in  $O(n \log n)$ . Therefore, the complexity of this procedure is  $O(n^2 \log n)$ .  $\square$

Because each simple tree can be handled independently, Theorem 2.9 generalizes to simple forests.

We conclude this section by noting that the algorithm outlined in the proof of Theorem 2.9 is not designed for efficiency; our primary purpose here is to establish that the problem is in  $\mathcal{P}$ . We conjecture that, by careful use of tree traversals and data structures, the complexity may be  $O(n \log n)$  or even better.

## Chapter 3

# Extending the Fundamental

**Problem: FPGA Minimization**

The fundamental problem has given us a basis for theoretical study of FPGA partitioning. In this chapter, we proceed further to incorporate one of the primary issues in VLSI design, that of cost minimization.

## 3.1 Problem Definition and Prior Results

Although some results have been obtained for MDGP and MDGP(k,d), the problem as stated is not entirely representative of the issues inherent in FPGA partitioning. MDGP is useful as a starting point, however, and can be generalized in ways that address other issues.

A primary consideration in FPGA partitioning is cost. While we have shown algorithms that can decide whether an input graph is a "yes" instance of MDGP(k,d), and while we can even find a feasible partition in linear time, thus far we have ignored the question of minimizing the number of subsets in a partition. Since the number of subsets in a partition represents the number of FPGAs used in the realization of a circuit (hence the cost), it is important that this issue be considered.

It is easy to modify the definition of the problem to accommodate this additional constraint, in a problem that we call FPGA Minimization:

**Instance:** a graph G = (V, E), and three integers k, d and p.

Question: Is there is a partition of V into disjoint sets  $V_1, \ldots, V_m$  such that  $m \leq p, \forall i : |V_i| \leq k$ , and such that if  $E_i$  is the set of edges with exactly one endpoint in  $V_i$ ,  $\max_{1 \leq i \leq m} |E_i| \leq d$ ?

FPGA Minimization is  $\mathcal{NP}$ -complete, since it contains MDGP as a special case in which p = |V|.

However, once again the physical limitations inherent in partitioning for FPGAs allow us to assume constant bounds on some of the parameters. Since the size and pincounts of the devices are constrained by the technology, we consider the variant of FPGA Minimization in which these two parameters are fixed. In this situation, which is more representative of the real problem of partitioning a circuit over the minimum number of FPGAs, we wish to minimize p, the number of subsets in a partition. We will refer to the decision version of this problem as p-way MDGP(k,d). Unfortunately, even this restricted version is very difficult.

Theorem 3.1 ([Go]) p-way MDGP(k,d) is  $\mathcal{NP}$ -complete.

## 3.2 New Results

In this section, we present a theoretical study of FPGA Minimization and p-way MDGP(k,d). We will also look at the version of the problem in which all three parameters are fixed, which will be denoted by MDGP(k,d,p). We find that many of the results for MDGP(k,d) apply in this setting as well, although FPGA Minimization and its variants provide some curiosities of their own. Additionally, we learn that FPGA Minimization remains  $\mathcal{NP}$ -complete even on very restricted graph families.

Since p-way MDGP(k,d) is of potential relevance in real circuit partitioning, in