# University of Tennessee, Knoxville TRACE: Tennessee Research and Creative Exchange

Masters Theses

**Graduate School**

12-1999

# A systematic implementation of image processing algorithms on configurable computing hardware

Benjamin Alexander Levine

Follow this and additional works at: https://trace.tennessee.edu/utk\_gradthes

### **Recommended Citation**

Levine, Benjamin Alexander, "A systematic implementation of image processing algorithms on configurable computing hardware. " Master's Thesis, University of Tennessee, 1999. https://trace.tennessee.edu/utk\_gradthes/9893

This Thesis is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Masters Theses by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a thesis written by Benjamin Alexander Levine entitled "A systematic implementation of image processing algorithms on configurable computing hardware." I have examined the final electronic copy of this thesis for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Master of Science, with a major in Electrical Engineering.

Donald W. Bouldin, Major Professor

We have read this thesis and recommend its acceptance:

Accepted for the Council: Carolyn R. Hodges

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

#### To the Graduate Council:

I am submitting herewith a thesis written by Benjamin Alexander Levine entitled "A System for the Implementation of Image Processing Algorithms on Configurable Computing Hardware." I have examined the final copy of this thesis for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Master of Science, with a major in Electrical Engineering.

Bouldin

Donald W. Bouldin, Major Professor

We have read this thesis and recommend its acceptance:

Next ...

Accepted for the Council:

Associate Vice Chancellor and Dean of the Graduate School

A Systematic Implementation of Image Processing Algorithms on Configurable Computing Hardware

5

A Thesis Presented for the Master of Science Degree The University of Tennessee, Knoxville

> Benjamin Alexander Levine December 1999

## ACKNOWLEDGEMENTS

I would first like to thank my advisor, Dr. Don Bouldin, for his support and guidance in this project. Without him, this work could never have been completed. I would also like to thank him for introducing me to configurable computing, a topic I find very interesting, and an area in which I hope to pursue further research. Finally, I am indebted to Dr. Bouldin for encouraging me to explore opportunities beyond the University of Tennessee.

I have enjoyed working with the rest of the CHAMPION team, especially Dr. Chandra Tan, Dr. Danny Newport, and Mr. Senthil Natarajan. All of their efforts and assistance have contributed greatly to this work and to the CHAMPION project as a whole. I wish them all good fortune in their future endeavors. I would also like to acknowledge the Defense Advanced Research Projects Agency for their support of this research under grant F33615-97-C-1124.

Finally, I would like to thank my wife, Ruth, for her support and encouragement, and for putting up with the long hours I have had to spend on this project. She has, in many ways, enabled me to complete this thesis and my research at the University of Tennessee, and to move on to new challenges.

' ii

## ABSTRACT

Configurable computing hardware has many advantages over both general-purpose processors and application specific hardware. However, the difficulty of using this type of hardware has limited its use. An automated system for implementing imageprocessing applications in configurable hardware, called CHAMPION, is under development at the University of Tennessee. CHAMPION will map applications in the Khoros Cantata graphical programming environment to hardware. A relatively complex automatic target recognition (ATR) application was manually mapped from Cantata to a commercially available configurable computing platform. This manual implementation was done to assist in the development of function libraries and hardware for use in the CHAMPION systems, as well as to develop procedures to perform the application mapping. The mapping techniques used were developed in such a way that they could serve as the basis for the automated system. Many important considerations for the mapping process were identified and included in the mapping algorithms.

The manual mapping was successful, allowing the ATR application to be run on a Wildforce-XL configurable computing board. The successful application implementation validated the basic hardware design and mapping concepts to be used in CHAMPION. Nearly a tenfold performance increase was realized in the hardware implementation and performance bottlenecks were identified which should enable even greater performance improvements to be realized in the automated system. The manual implementation also helped to identify some of the challenges that must be overcome to complete the development of the automated system.

iii

# Table of Contents

| I. INTRODUCTION                             |         |

|---------------------------------------------|---------|

| A. Motivation                               | ••••••• |

| B. Research Objectives                      | ····· I |

| B. Research Objectives                      | 6       |

|                                             |         |

| II. BACKGROUND                              | 10      |

|                                             | 10      |

| 1) Haldwale                                 |         |

| 2) Applications                             | 13      |

| 3) Development Software                     | 15      |

| B. Khoros Cantata                           |         |

| C. CHAMPION                                 |         |

|                                             |         |

| III. PROJECT GOALS                          | 23      |

| A. START Application                        | າ       |

| 1) First Phase                              |         |

| 2) Second Phase                             |         |

| B. Wildforce Board                          |         |

| 1) Xilinx FPGAs                             |         |

|                                             |         |

| 2) Board Architecture                       |         |

|                                             |         |

| IV. IMPLEMENTATION.                         |         |

| A. Cantata Implementations of START         |         |

| 1) Standard Cantata                         |         |

| 2) Hardware Equivalent Cantata              |         |

| B. Glyph Libraries                          |         |

| 1) Khoros Cantata Glyphs                    | 45      |

| 2) Hardware Equivalent Glyphs               | 46      |

| 3) Hardware Glyphs                          |         |

| C. Differences Between Cantata and Hardware |         |

| 1) Data Transfer                            |         |

| 2) Data Synchronization                     |         |

| 3) Data Conversion/Operator Sizing          |         |

|                                             |         |

|                                             |         |

| 1) Workspace Conversion                     |         |

| 2) Data Sizing and Glyph Selection          | 58      |

| 3) Data Synchronization                     | 61      |

| 4) Partitioning                             | 64      |

| a) Background                               | 64      |

| b) Constraints                              |         |

| c) Partitioing Algorithm                    |         |

| 5) Synthesis                                |         |

| 6) Host Code Generation                     | 69      |

|                                             |         |

| V. RESULTS                                  | 70      |

| V. RESULTS<br>A. Configurations             | 70      |

| B. Application Performance                  | 70      |

| 1) Target Recognition                       |         |

| <ul><li>2) Processing Time</li></ul>        |         |

|                                             |         |

| VI. CONCLUSIONS      |                                       |  |

|----------------------|---------------------------------------|--|

| A. Glyph Libraries   | · · · · · · · · · · · · · · · · · · · |  |

| B. Mapping Procedure | •••••••••••                           |  |

| C. Performance       |                                       |  |

| D. Future Work       |                                       |  |

|                      |                                       |  |

| REFERENCES           |                                       |  |

|                      |                                       |  |

**v**

# List of Tables

| Table II-1.  | Comparison of Four Xilinx FPGA-based CCMs.                         | 11     |

|--------------|--------------------------------------------------------------------|--------|

| Table III-1. | Resources Available in FPGAs Used on Wildforce-XL.                 | 36     |

| Table IV-1.  | Glyphs Used in Standard Cantata Implementation of START.           | 40     |

| Table IV-2.  | Glyphs Used in Hardware Equivalent Cantata Implementation of START | 43     |

| Table IV-3.  | Hardware Glyph Control Line Combinations and Meanings              | · 50 ′ |

| Table V-1.   | Hardware Resource Usage for Each FPGA Configuration.               | 74     |

| Table V-2.   | Results from Cantata and Hardware Implementations of START         | 80     |

# List of Figures

| Figure II-1.  | . Khoros Cantata Glyphs and Command Line Equivalent.              |    |  |

|---------------|-------------------------------------------------------------------|----|--|

| Figure III-1. | Sample Images from START Algorithm.                               | 25 |  |

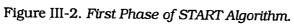

| Figure III-2. | First Phase of START Algorithm.                                   | 28 |  |

| Figure III-3. | Second Phase of START Algorithm.                                  | 31 |  |

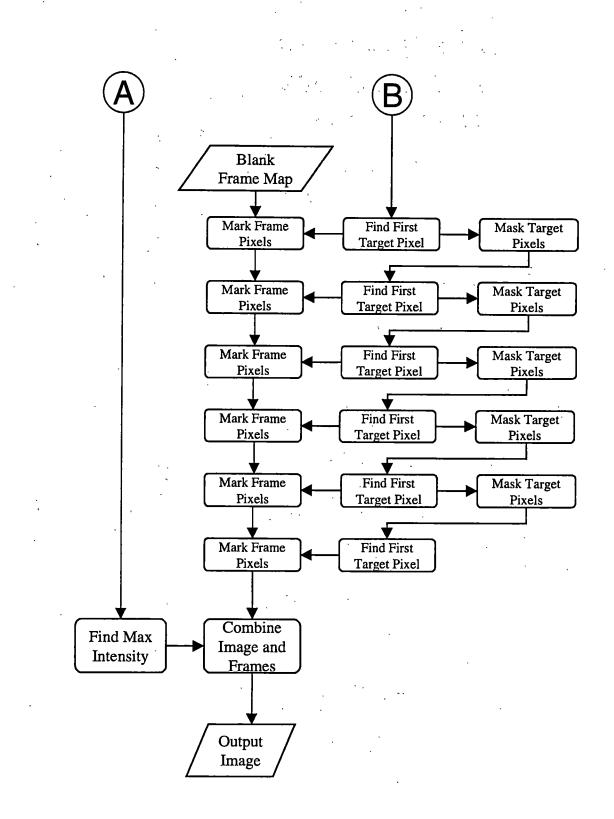

| Figure III-4. | Xilinx 4000 Series FPGA Configurable Logic Block.                 | 33 |  |

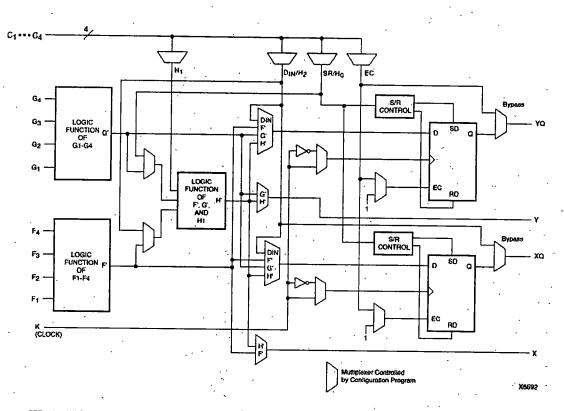

| Figure III-5. | Wildforce-XL Block Diagram.                                       | 37 |  |

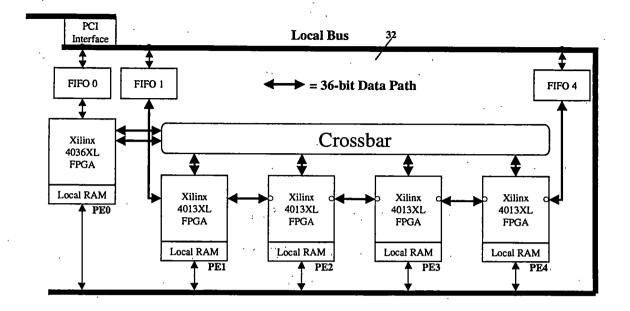

| Figure III-6. | Wildforce-XL Board As Used.                                       | 38 |  |

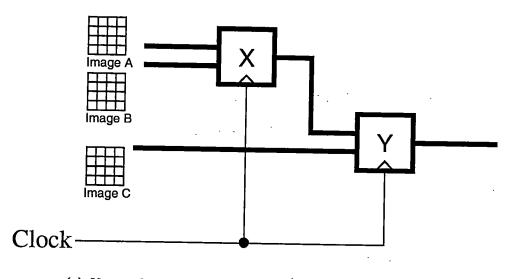

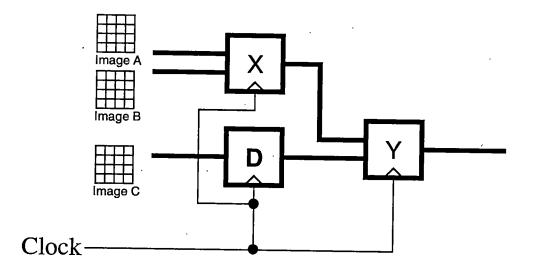

| Figure IV-1.  | Data Synchronization Problem and Solution.                        | 53 |  |

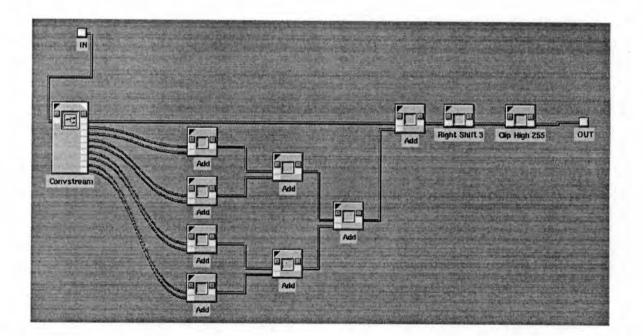

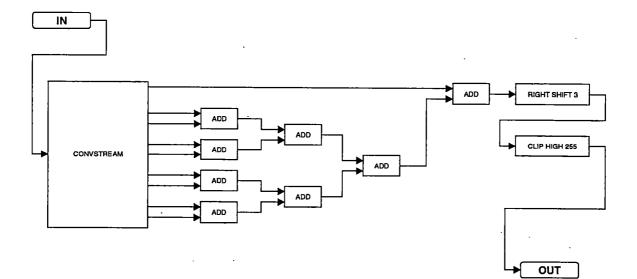

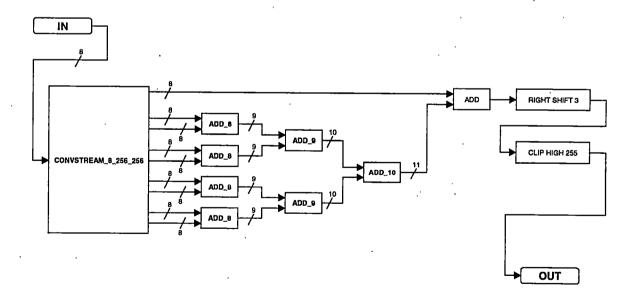

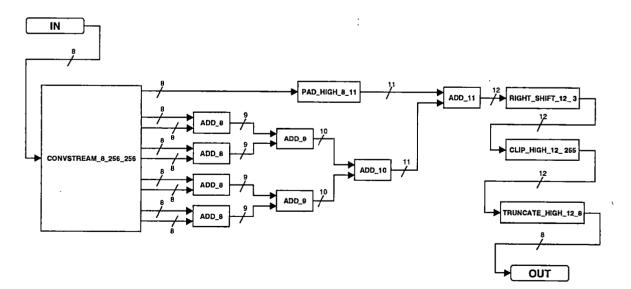

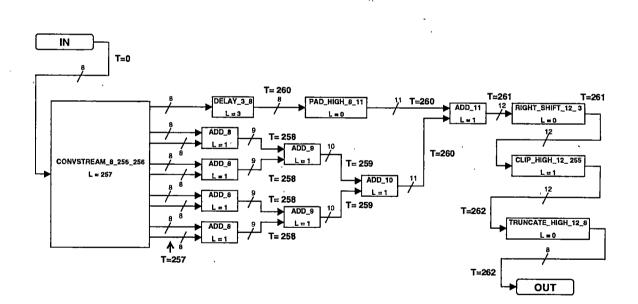

| Figure IV-2.  | Example Hardware Equivalent Cantata Workspace – Low-Pass Filter.  | 56 |  |

| Figure IV-3.  | Graph Form of Low-Pass Filter Workspace.                          | 57 |  |

| Figure IV-4.  | Data Alignment Problem in Low-Pass Filter Graph.                  | 59 |  |

| Figure IV-5.  | Low-Pass Filter Graph with Data Widths and Glyph Types Annotated. | 61 |  |

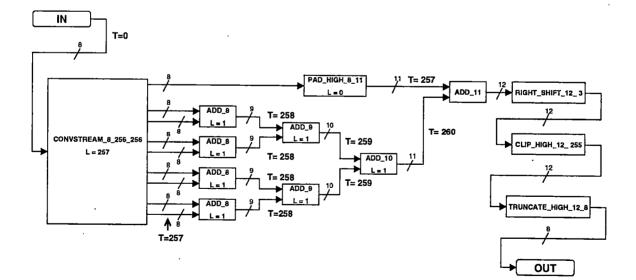

| Figure IV-6.  | Partial Time Annotation for Low-Pass Filter Graph.                | 62 |  |

| Figure IV-7.  | Low-pass Filter Graph with Complete Time Annotation.              | 63 |  |

| Figure IV-8.  | Pseudo-Code for START Host Program.                               | 71 |  |

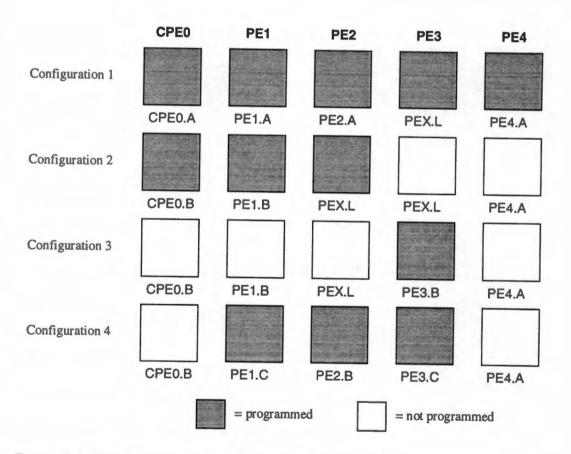

| Figure V-1.   | FPGA Programming for Each Board Configuration.                    | 73 |  |

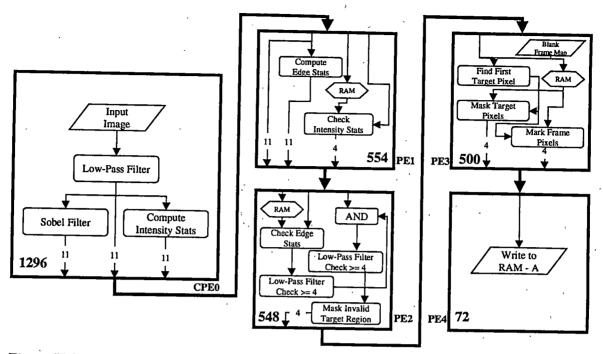

| Figure V-2.   | First Board Configuration.                                        | 76 |  |

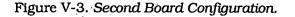

| Figure V-3.   | Second Board Configuration.                                       | 77 |  |

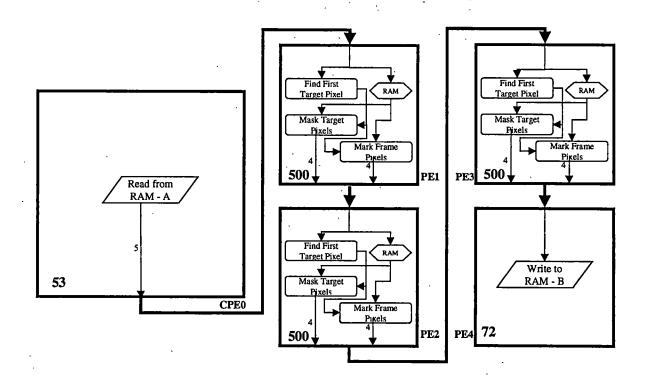

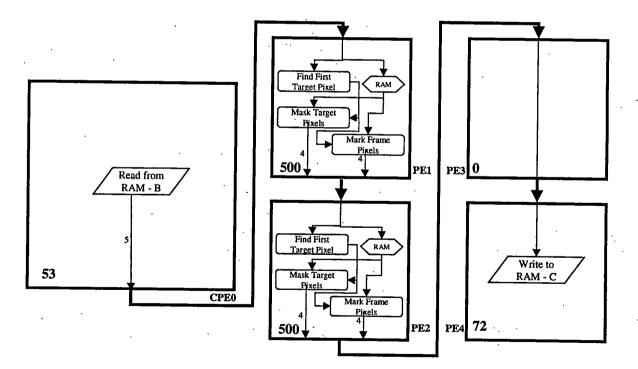

| Figure V-4.   | Third Board Configuration.                                        | 78 |  |

| Figure V-5.   | Fourth Board Configuration.                                       | 79 |  |

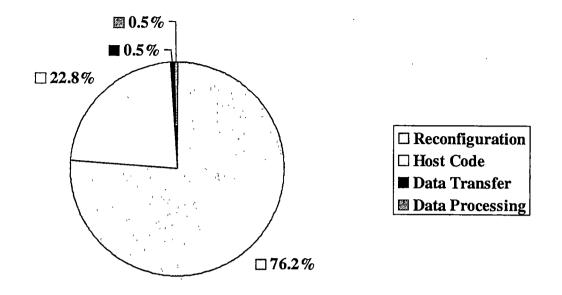

| Figure V-6.   | Breakdown of Image Processing Time for Hardware Implementation    | 82 |  |

# I. INTRODUCTION

## A. Motivation

Since the first electrical computing devices were created in the 1940s, an everincreasing variety of computations has been done by electronic hardware. The earliest computers calculated artillery tables and decrypted codes for the military. There is now virtually no type of computation that is not performed by computer at least some of the time. Clearly, in the intervening years an extremely large number of new applications for computing hardware have been developed. The calculations performed in these applications range from those that were previously done by hand, such as accounting and scientific calculations, to entirely new sorts of computations that can only be done by computer, such as digital image processing and complex simulations. Regardless of the type of computation being done, the same basic operations are used ubiquitously. For example, arithmetic operations, such as addition and multiplication, and logical operations, such as Boolean ANDs and ORs, are used for virtually all types of calculations. While the same operations are used repeatedly, the type of hardware performing these basic operations can vary widely.

For many years, electronic hardware used for computation could be divided into two main types, general purpose, and application specific. General-purpose hardware is exemplified by microprocessors such as the Intel 80x86 family and the Motorola 68000 family, which serve as the main processing unit in most personal computers. The architecture of these devices is fixed and includes specific hardware to implement a limited, pre-defined, set of instructions. These microprocessors run programs, which are lists of instructions to be executed that are stored in external

memory. New programs can be loaded into memory from disk or other storage as needed. The software program determines the computation to be done, not the hardware. Because their instruction sets include very general operations such as arithmetic and logical operators, branching and recursion, and memory access, this type of hardware can be programmed to perform any conceivable function. In fact, as the work of Church and Turing shows, *all* computations can be performed by such a general-purpose computer. However, general-purpose computers can be very slow at performing certain kinds of operations, such as those involving floating-point calculations or complex mathematical functions. For this reason, most modern computers have one or more coprocessors, which are application specific hardware that perform floating-point calculations and other mathematical operations, and graphics coprocessors that perform 3D rendering.

Application-specific computing hardware performs functions very quickly, but the price of this speed is limited flexibility. As their name implies, this type of hardware can only perform one function, or a group of closely related functions. The hardware determines the type of computation to be done. They cannot be reprogrammed to perform entirely new functions that were not anticipated and included in the original design. If application specific hardware is needed to perform a new function, then a new hardware design will have to be created. Since this type of computation hardware is generally implemented as carefully designed Application Specific Integrated Circuits (ASICs), creating a new design takes a great deal of effort and knowledge. Since they are custom ICs, they are also very expensive to fabricate, and it takes week or months to design a new ASIC and have it fabricated. Therefore, application specific hardware is only useful if the functions needed are known in

advance and the requirements of the functions they perform are not expected to change during the useful lifetime of the hardware.

In spite of these drawbacks, application specific hardware is widely used whenever speed is an important design consideration. By structuring the hardware to match the problem, application specific hardware can often achieve computation speeds several orders of magnitude faster than general-purpose hardware. This high level of performance is obtained by utilizing several techniques, including the performance of operations in parallel; the organization of hardware for efficient data transfer, which reduces delays while data is moved from place to place; and the utilization of hardware structures that permit efficient data scheduling, reducing inefficiencies introduced when computation is halted to wait for new data.

In recent years, a new class of computing hardware has been gaining increasing research interest. Configurable computing hardware has some of the advantages of both general-purpose and application-specific hardware. This type of hardware may be based on commercially available Field Programmable Gate Arrays (FPGAs), or on ICs designed specifically for the purpose. In either case, this type of hardware consists of a relatively large number of functional units with programmable interconnections. The functionality of the hardware is determined by how the interconnections between functional units are configured, and in most, but not all, architectures, how the functional units themselves are configured. By changing the configuration, the hardware can be made to perform a completely different function. Since the configuration is specific to the application at hand, it is in effect a custom computer for the particular design. For this reason, computing devices using configurable hardware are often called Custom Computing Machines (CCMs).

З

The functional units in a CCM are usually relatively simple logical functions equivalent to a few gates, or a few tens of gates. Some configurable computing hardware has slightly more complex functional units such as small Arithmetic Logic Units (ALUS). The functional units may be fixed in function, or their functionality may be configurable. For instance, many FPGAs use Look-Up Tables (LUTS), for which the output (or outputs) for every possible input can be programmed. In this way, LUTs can implement any possible logical function of the inputs, giving great flexibility. Most architectures also include flip-flops in each functional unit, to register the outputs and allow for synchronous designs.

The interconnections between functional units provide much of the utility of most configurable computing architectures. Programmable switches can selectively connect tracks wired to the inputs and outputs of the functional blocks, allowing the desired functions to be implemented. These interconnections are internal to the IC; if multiple ICs are used in a CCM, then there are usually programmable interconnections between the ICs as well.

Since the structure of the hardware has effectively been changed for the specific function to be implemented, many types of computations can be performed by CCMs at speeds close to those obtained using application specific hardware. In addition, the configuration can be changed relatively quickly from one function to another, giving some of the same flexibility as general-purpose hardware. In effect, configurable computing allows the benefits of both application-specific and general-purpose computing to be present in the same hardware.

Despite these advantages, configurable computing hardware has not been widely used. Perhaps the main reason is the difficulty involved in configuring this hardware

· 4 ·

to perform a specific function. A typical CCM may consist of several interconnected FPGAs, as well as memory and other components. In order to map an application to this hardware, the designer must first design the hardware configuration needed to perform the necessary functions. This is usually done with either schematic capture, or increasingly with a Hardware Description Language (HDL) such as VHDL or Verilog. In either case, the designer must understand digital design and be able to separate an application into data processing and control elements. The design must then be partitioned spatially, so that the design is spread across the resources available on the FPGAs. If the design does not fit in the available FPGAs, then it must also be partitioned temporally, by allocating functional units to different configurations of the same FPGA. In addition, any configuration of the CCM itself must be determined, and a program to communicate with a host computer must usually also be created. While commercial tools exist to help with parts of this process, it still requires a great deal of skill, knowledge of digital design, time, and effort. These steep requirements have severely limited the potential users of this type of hardware and prevented its widespread acceptance.

The development of methods to allow CCMs to be used more easily will make their advantages available to more users. Ideally, tools will be developed to allow users with no knowledge of digital design to use CCMs, just as users who know nothing about the design of a microprocessor can use computers. The less important knowledge of the underlying hardware is, the larger the pool of potential users of CCMs will be. The current pool of users consists almost exclusively of researchers and digital hardware engineers. If the use of CCMs is to spread beyond this limited group, then much more research into better tools to use them will have to be done.

## B. Research Objectives

Research at the University of Tennessee is currently underway to develop an automated system for mapping image processing applications in a graphical programming environment called Khoros Cantata to configurable computing hardware. It is expected that this system, called CHAMPION, will help make the power of configurable hardware more accessible to users who lack digital design experience. It is also expected that the system will allow new applications to be implemented in much less time than is required now, since many portions of application mapping that must currently be done manually will be automated. The work described in this thesis is a part of the overall research being conducted as part of the CHAMPION project.

The author's research concerns the manual mapping of a complex application running in Khoros Cantata to a commercially available CCM, the Annapolis Micro Systems Wildforce-XL. A systematic method of doing this application mapping was developed. The manual mapping used a library of parameterizable hardware modules developed concurrently for CHAMPION. The entire manual mapping was done with the goals of CHAMPION considered at every step. The resulting implementation was thus quite different from that which would have been developed if the only goal were to implement the application in hardware. However, the goal of the research was not just to simply implement the application in hardware, but to provide information on the requirements of the implementation to the developers of the automated system.

The proposed benefits of performing a manual mapping were fourfold. First, to help develop application-mapping methods that could be used to help design the automated system by determining the requirements of the system and possible

methods by which the mapping could be performed. Second, to help guide the library development process by showing what types of library modules would be needed and what the requirements of those modules should be. Third, to show that the mapping methods and library modules developed could be used to implement a significant application. Fourth, the successful implementation of the application would give researchers measurements of the time required to manually map the application and the performance of a manually mapped implementation.

The process of mapping an application from software to hardware is a complicated one and there are many factors that had to be considered at each step of the process. Some of these were readily apparent, such as ensuring that the hardware chosen implements the same operations as the software application. Others were not considered until the mapping process had begun. By performing a mapping manually, all of the steps needed could be determined, and all of the factors that needed to be considered could be identified. The mapping process was successful, showing that the methods determined in the mapping process were viable, and could be used as the basis for an automated system. The manual mapping also clearly delineated the requirements for an automated system to perform the mapping process.

There are hundreds of functions available in the Khoros Cantata toolboxes and in publicly available extensions. Since not all of these could or should be included in the CHAMPION system, decisions had to be made as to which functions would be needed. Some of the decisions were obvious; simple arithmetic operators such as addition, and the basic Boolean operators should definitely be included in a system such as CHAMPION. Other choices were not as obvious. By determining the types of functions needed to implement a real application, better decisions as to which

functions to include could be made. The implementation process also helped determine the requirements of the hardware implementing these functions. Design details of the hardware modules such as control lines and I/O ports were determined to large extent by what would be necessary to make the initial application work.

In order to evaluate the effectiveness of the automated system, some idea of the time required to do a manual mapping is necessary. Only by having information on the time required for a manual implementation can the productivity gains provided by CHAMPION be measured. The manual implementation also provided information on the performance of the application, in terms of the rate at which data can be processed. While the performance of the applications mapped by the automated system is not a primary goal of the project, it is still valuable to be able to measure any differences in performance between the results obtained by CHAMPION and the results obtained by a human designer.

The manual implementation did provide the type of information that was expected, as discussed above. This information should prove useful in the development of the automated system. However, the development of the automated system is mostly outside of the scope of the author's research and as such, will not be discussed in detail in this paper. It is to be expected that later publications by others working on the CHAMPION system will provide more information on its development.

This chapter presented an introduction to the research covered by this thesis. Chapter II provides background information on configurable computing, Khoros Cantata, and the CHAMPION project. Chapter III discusses the application to be mapped and the CCM used to implement it. Chapter IV discusses the application mapping process, including the libraries and procedures used. Chapter V gives the

results of the hardware implementation, including specific information on the final implementation and its performance, as well as the time taken to complete it. Chapter VI presents overall conclusions about the research.

# II. BACKGROUND

## A. Configurable Computing

To date, most research in configurable computing can be divided into three main areas. The first has been the development of configurable computing hardware. The second has been the implementation of various types of applications on configurable computing hardware. The third has been the creation of software to assist in the implementation of applications on configurable computing hardware. All three of these areas have helped determine which types of applications are best suited to implementation on CCMs, and the benefits of running these applications on this type of hardware as compared to either general-purpose or application-specific hardware. Portions of each of these areas are relevant to the current research and will be discussed in the following sections.

#### 1) Hardware

Numerous configurable computing machines have been built by research groups. More recently, commercial vendors have begun producing CCMs. While some research groups have designed their own ICs for configurable computing, (e.g., PipeRench [1] and RaPiD [2]), most CCMs have been constructed using commercially available FPGAs. A list of dozens of FPGA-based CCMs is given in [3]. Some of the more significant FPGA-based CCMs include Splash 2 [4], DECPeRLe-1 [5], and the Virtual Computer [6]. Versions of these CCMs, and CCMs derived directly from them, are used today by many CCM researchers.

Many different CCMs have been built with the same FPGAs, especially those produced by Xilinx, Inc. of San Jose, California. Despite their use of the same FPGAs, CCMs can vary widely in a number of other specifications. CCMs can vary in the number and size of FPGAs used; the number of interconnections between the FPGAs and whether or not these interconnections are configurable; the topology of the interconnections; whether or not other resources are available in the CCM, such as RAM or DSP chips; and how the CCM connects to an external host computer. Table II-1 shows some of the specifications for several different CCMs that use Xilinx FPGAs and illustrates some of the differences between them.

Much of the research in CCMs has attempted to determine what kinds of CCM architectures are most efficient, fastest, cheapest, and so forth. The answer to these

| FPGA Family<br>Number of<br>FPGAs | Xilinx XC3000 | array boards<br>may be used)<br>Xilinx XC4000    | Computer<br>Xilinx XC4000 | Knoxville)<br>Xilinx<br>XC4000XL<br>4 x XC4013XL |

|-----------------------------------|---------------|--------------------------------------------------|---------------------------|--------------------------------------------------|

| (available for computation)       | 16 x XC3090   | 17 x XC4010                                      | 52 x XC4010               | 1 x XC4036XL                                     |

| Total Gate<br>Equivalents         | 96,000        | 170,000                                          | 520,000                   | 88,000                                           |

| RAM                               | 4 MB          | 8.5 MB                                           | 8 MB                      | 640 KB                                           |

| Interconnection<br>Topology       | 4 x 4 Matrix  | Linear Array<br>with<br>Programmable<br>Crossbar | Spherical                 | Linear Array<br>with<br>Programmable<br>Crossbar |

| Host Interface                    | TurboChannel  | SUN S-Bus                                        | SUN S-Bus                 | PCI Bus                                          |

Table II-1. Comparison of Four Xilinx FPGA-based CCMs.

questions usually varies depending on the characteristics of the applications that are being run. For instance, some applications require the frequent storage of intermediate results in RAM. If these applications were implemented on a hypothetical CCM, denoted CCM-A, which has relatively low RAM access bandwidth, than the performance would be lower than if they were run on another hypothetical CCM, denoted CCM-B, which has higher RAM access bandwidth. However, CCM-B might achieve its higher RAM access bandwidth by devoting more I/O pins on each FPGA to memory interfacing, leaving fewer available pins for interconnection between FPGAs. If CCM-A and CCM-B both have the same number and type of FPGAs, then all else being equal, CCM-B will have less connectivity between FPGAs than CCM-A. Another class of applications might require many interconnections between functional units. These applications would fit better into CCM-A than into CCM-B, using computation resources more efficiently in the former. For these and other obvious reasons, there can be no one CCM architecture that is ideal for all applications.

However, there are CCMs with architectures that seem to work relatively well for a range of problems. CCMs are now available from commercial vendors such as Annapolis Micro Systems and the Virtual Computer Company. These systems offer many of the same features found on research CCMs including: multiple FPGAs on a single board, state readback of processing elements for diagnostic purpose, direct access to RAM from each FPGA, host I/O through a fast interface bus such as PCI or VME, and pre-developed APIs for host interface code and hardware configuration. These commercial CCMs can be used to implement fairly complex and demanding applications.

Missing from these commercial offerings are the powerful tools necessary to make these CCMs easy to use. Once again, the most pressing problem in configurable computing seems to be the development of tools to efficiently use CCMs. Tool development is lagging behind the development of configurable hardware, and seems to be a limiting factor in its adoption, so there is currently somewhat less interest in hardware development than in earlier years. Research does continue in various areas of CCM hardware development. Recent research in architectures often involves the integration of configurable hardware and general-purpose processors [7, 8, 9], or DSP chips [10]. New architectures are also being developed to take advantage of developments in commercial FPGA designs. Xilinx Corporation's new Virtex family, which offers much higher densities than its other FPGAs, faster reconfiguration, and partial reconfiguration, seems to be of particular interest to the CCM community.

## 2) Applications

In addition to studying CCM hardware and the software tools needed to use it, researchers have been investigating the types of applications that are well suited for implementation on CCM hardware. CCM hardware is especially good at applications that require the repeated application of simple operators on large amounts of data. Performing operations in parallel and optimizing them so that the operations can be performed at high speed is one of the primary ways that CCM architectures can achieve good performance. If applications show some exploitable parallelism and use relatively simple operators, then they may be good candidates for implementation using a CCM.

Most configurable computing hardware is very inefficient at performing floating point calculations. These calculations require large amounts of FPGA resources and run relatively slowly. Applications requiring many floating-point calculations are not

usually good candidates for implementation on CCM hardware. In some cases, however, an application originally developed using floating point numbers can be implemented using fixed-point data representation without a significant degradation of its performance. Determining the number of bits necessary to represent data at various stages of an application and the effect of changing floating-point representations to fixed-point can be an important step in determining the suitability of application to CCM implementation, and there has been increasing research on this topic [11, 12].

Several application domains have proved particularly suitable to implementation on CCMs. In particular, applications involving image and video processing [13, 14, 15], communications [16, 17], and CAD applications [18, 19, 20], have been the subject of recent research. Since image-processing applications have been widely implemented on CCM hardware, image processing seemed to be a particularly fruitful application domain for an automated system such as CHAMPION. The availability of a widely used tool for image processing application development, Khoros Cantata, made image processing even more attractive as the focus for CHAMPION and for the initial manual implementation presented in this paper.

Image processing applications are well suited for implementation on configurable computing hardware, for several reasons. They involve relatively large amounts of data. For example, one 640 x 480 image with 256 gray levels represents 300 kilobytes of data. If the images being processed come from a standard real time source at 30 frames/second, nearly 8 megabytes per second must be processed. Many image processing operations require only simple arithmetic and logical operations that are well suited to configurable hardware and avoid more complex mathematical operators and floating point calculations that are more poorly suited. Image-processing applications exhibit a high degree of parallelism, in that the same

operations are often applied to each pixel in an image or portion of an image. In a general-purpose computer, each operation on each pixel must be done sequentially, which can be time consuming for large images. CCM implementations of image processing applications can often be designed so that multiple pixels can be processed simultaneously by arrays of functional units, greatly improving performance. This kind of array processing has been widely used in application specific VLSI designs [21] and much of this experience is transferable to CCM designs.

#### 3) Development Software

Ideally, software should be developed that would allow a user to capture their design at a high level, without any consideration of digital design or the specific CCM architecture being targeted. The high level design would then automatically be converted into an equivalent hardware description and this hardware description partitioned across the available resources. Finally, the software would generate the host code and programming files to run the application on the targeted architecture. This would allow a user to run their application on CCM hardware without having any knowledge of digital electronics and without even being aware of the mapping process taking place. Unfortunately, this is a very difficult task. No one has yet come even close to meeting these specifications. Much research has been done into tools that can perform parts of the application mapping process, however, and it eventually should be possible to approach this hypothetical ideal case.

Much research has been performed recently to make it easier to run applications on CCMs by allowing high level design information to be entered using general purpose programming languages. Many papers [22, 23, 24, 25, 26, 27] have reported work on systems to map programs in C or C++ to various types of configurable hardware.

Since C is a widely used language; the ability to map applications from C to CCMs should greatly increase the number of people with the ability to utilize configurable hardware. Other work has been done mapping applications from other programming languages to CCMs [28, 29, 30]. All of these language-based efforts usually work with subsets of the programming languages and require not only programming ability, but also varying degrees of knowledge of the underlying hardware. These efforts do increase the pool of potential users of CCMs, but mapping applications to hardware with these tools is not completely automated and still requires significant technical expertise.

There have been successful efforts to create tool suites specifically designed for implementing designs on CCM architecture [31, 32]. This type of system provides powerful tools to help the hardware designer create and test designs on CCMs. They are intended for technical users, however, and aim more at increasing the efficiency of the users, rather than widening the pool of potential users. Their primary goal is not to isolate the user from detailed technical information about the hardware, but to make access to that information easier and more useful.

Other systems have attempted to automate portions of the application mapping process. For instance, one style of design for CCMs uses libraries of parameterizable modules that perform standard functions. A design can be created by combining these modules in a design with the necessary interfacing and interconnections. Several systems have been developed that are focused on creating, maintaining, and implementing these libraries of modules [33, 34]. Again, these tools greatly assist the hardware designer, but do not significantly lower the skill requirements for using CCMs.

One system that does make CCMs more accessible to users who are not necessarily experienced hardware designers was developed at Virginia Tech [35]. It allows the implementation of image processing applications by connecting pre-designed modules that perform common operations, such as filtering and thresholding, using a schematic capture tool. These applications are then implemented on a configurable computing engine developed at Virginia Tech, using a set of specific software tools. The system is designed to work only with one specific architecture, however, and many of the steps in the mapping process are manual. Nonetheless, the system does greatly decrease the skill required to create CCM implementations of relatively complex applications.

## B. Khoros Cantata

Khoros is a software system from Khoral Research Incorporated (KRI). At the core of Khoros is a set of toolboxes containing over 300 operators. These operators include arithmetic operators for scalars, vectors, and matrices; image and signal processing functions; data visualization and display operations; and many functions for manipulating and examining sets of data. The operators can be run as stand alone programs from the command line, or as functions called by a C or Fortran program.

In addition to the operators, Khoros defines three robust data structures. The geometry data model allows for representation and storage of complex geometric structures, and allows for easy access to, and manipulation of these structures. The color data model is used for the storage of color maps in a format that allows for easy transformations of the color space. The polymorphic data model is the most flexible data model. It is capable of storing multi-dimensional data including audio signals,

images, video, vector spaces, or virtually any other type of data that can be represented with up to three spatial dimensions and optionally one time dimension.

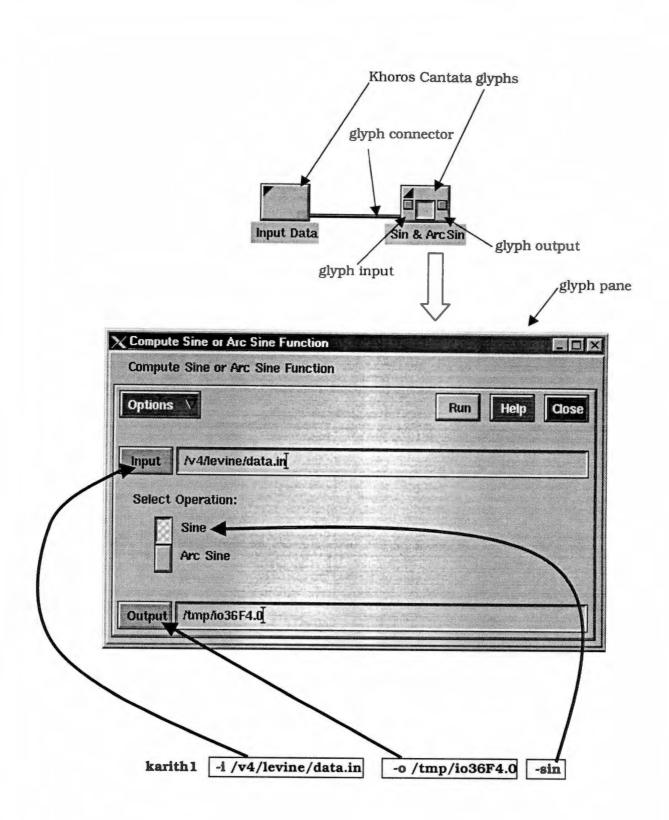

While Khoros can be used by running commands manually, it is perhaps most widely used with its graphical programming environment called Cantata. Cantata allows the user to create an application by drawing a graphical representation of it. Each function in the Khoros toolbox is represented on the screen by a small icon called a glyph. The glyph has an input terminal corresponding to each of the possible inputs to the function and output terminals for each of the outputs. In addition, each glyph has a pane, which is a set of interface objects that allow the user to set options for the operation of the glyph. Each of these objects corresponds directly to a parameter that can be passed to each function on the command line.

Figure II-1 shows a simple Cantata workspace. A glyph for calculating the trigonometric sine is shown, as well as another glyph that reads in the input data. The pane for the sine glyph is shown directly below the glyph itself. It has a text box for the input and output filenames and radio buttons to select whether the sine or arc sine is to be computed. The input filename is set automatically to be the same as the output of the preceding glyph. In this case, the first glyph is set to read in a file called /v4/levine/data.in. This filename is then passed to the sine glyph. The output filename is automatically picked by Cantata, and corresponds to a temporary file. This filename will be passed to any following glyphs, and the data in the file can be further processed, written to another file, or displayed, depending on which glyphs are used. The user does not have to worry about the filenames for the inputs and outputs, as they are chosen by Cantata. The user also does not have to be concerned about the type of data in the files; Cantata will take care of any conversions between types necessary. It does not matter whether the input is one floating-point value or a

Figure II-1. Khoros Cantata Glyphs and Command Line Equivalent.

three-dimensional array of double precision values. In every case, Cantata determines how to handle the data without user intervention.

As mentioned previously, anything in Khoros can be done at the command line as well as in Cantata. The command line equivalent to the two glyphs is shown at the bottom of Figure II-1. Each parameter in the command line has a corresponding user interface object in the glyph pane. On the command line, the user has to type each parameter in manually. In Cantata, the parameters are generated automatically from the settings in the glyph pane. Regardless of whether it is called from the command line or from Cantata, the same software routine performs the desired operation on the data.

The power of Cantata, like other graphical programming environments, is that it allows a user to simply draw a diagram of their application and have it run. They do not have to worry about the details of how data is passed or where it is stored. They do not have to be concerned about converting data from one data type to another. They do not even have to compile their code. This means that users do not even have to be conversant with traditional programming methods to quickly implement and test their algorithms and ideas. Since Cantata can work on such a wide range of data, users can test their applications using real data. The visual nature of Cantata also makes it easy to modify an existing application by simply adding or removing glyphs and changing connections.

Cantata can be used by users who may be skilled in their own area of expertise, but who may not necessarily be able to program well enough to test their ideas. For instance, a mathematician who is adept at creating algorithms for computer vision, but might otherwise be limited by a lack of programming ability, can use Cantata to

implement and test algorithms using real data. Cantata has become widely used partly because of its ability to isolate users from the underlying technology and still let them exploit the power of the computing platforms they are using.

## C. CHAMPION

The goal of research currently being pursued at the University of Tennessee is to produce a system, called CHAMPION, which will automatically map applications implemented in Khoros Cantata to configurable computing hardware. This would greatly increase the number of potential users of CCMs, as little or no knowledge of hardware design would be required. Khoros Cantata was chosen as a front end to CHAMPION due to its widespread use in the image processing community, and also because it isolates the user from the technical details of the hardware doing the computations. This is important because it will allow the same application to run on a workstation or on configurable hardware without visible differences in the application, as long as the CHAMPION libraries are used.

CHAMPION will require the creation of a set of libraries and a set of tools or procedures. The libraries will consist of Cantata glyphs that are compatible with hardware implementation and a corresponding hardware version of each of the Cantata glyphs. As long as the user uses these CHAMPION glyphs to create their Cantata workspace, CHAMPION should be able to convert the Cantata application into a hardware implementation to be run on a CCM. The Cantata glyphs and the corresponding hardware will perform the same operations, so the hardware implementation should perform identically to the Cantata implementation. The determination of the types of glyphs needed and how these will be implemented in hardware is an important part of the development of CHAMPION, and will be guided by the results obtained in the research presented in this paper.

In addition to the two sets of libraries, CHAMPION will require the development of a set of tools to perform the application. Tools will need to be developed for each step of the mapping process. First the Cantata workspace for the application must be read and converted into an intermediate form for use by CHAMPION. Each glyph in the Cantata workspace must be replaced by its hardware equivalent, and then the hardware partitioned to fit the target architecture. The programming files for each FPGA must be generated and the necessary code for the host processor must be generated. Exactly what is required at each step of this process will be determined in large part by the results of the manual implementation presented herein.

l

# III. PROJECT GOALS

The goals of this research project were to manually implement a significant Khoros Cantata application on configurable hardware, using glyph libraries and procedures that will be usable in the context of the larger CHAMPION project. The specific application chosen was an automatic target recognition application called START and the specific CCM was a commercial product called the Wildforce-XL. Details of the application and the hardware it was implemented on are presented in this chapter. Details about the implementation process are presented in Chapter IV, and the results of the implementation are presented in Chapter V.

## A. START Application

A relatively complex image processing application that was well understood by the author was desired for the first manual application implementation. Using a complex application would provide several benefits. It would help identify more useful hardware glyphs than would a simpler algorithm. Using an algorithm large enough to require reconfiguration of the board would test that capability of the board and require the determination of techniques to partition the design temporally as well as spatially. Finally, using a complex algorithm would validate that the libraries and procedures developed were sufficient to complete problems of a significant nature.

An Automatic Target Recognition (ATR) application developed by the author for a digital image processing course was picked as the application to be implemented. The application was named Simple, Two-criterion, Automatic Recognition of Targets, or START. The application was not chosen for its merit as an ATR algorithm; rather it

was chosen because it was sufficiently complex and because it was an existing application developed by the author. This familiarity with the application allowed the efforts of the author to be concentrated on the hardware implementation and not on understanding the application to be implemented, or on devising a new one.

The START application uses a statistical algorithm to find regions in Forward-Looking InfraRed (FLIR) images where a target may exist and draws a box around such regions. Algorithms of this sort are often used for target queuing; that is, they automatically identify areas of possible interest for further examination by human operators. The algorithm does not positively identify a target, nor does it identify the type of target, as a true ATR algorithm does. It simply identifies segments of the image as areas where there is a high probability of there being one or more targets.

The START algorithm was tested with FLIR images from Colorado State University's Fort Carson RSTA Data Collection. This is a freely accessible collection of image data available over the Internet [36]. Forty images were chosen from the entire set of available images. The images chosen had corresponding color visual light images available so that the actual location of targets could be determined more accurately, as identifying targets in the FLIR image can sometimes be difficult for a human observer. The FLIR images were taken of varied, generally hilly terrain, with either no vehicles present, or up to four vehicles present. The vehicles used to represent targets were an M60 main battle tank, an M113 armored personnel carrier, an M901 anti-tank vehicle, and a GMC pickup truck. A representative FLIR image is shown in Figure III-1(a).

Many variables were present in the image set. Vehicles varied in their distance from the sensors and in their orientation, greatly changing their apparent size and shape.

(a) FLIR Image Used as Input to START Algorithm.

(b) Target Pixel Map from First Phase of START Algorithm.

(c) Output image from START Algorithm.

Figure III-1. Sample Images from START Algorithm.

Vehicles were sometimes partially concealed by terrain features, which also introduced variation in size and shape. The overall image contrast was variable, as was the relative background intensity. These variables made the determination of target regions challenging. A straightforward algorithm based on statistical evaluation of two criteria was found to provide reasonably good results, however.

Areas of interest are assumed to have two characteristics. First, they must contain pixels hotter than the surrounding terrain. In a FLIR image, hotter pixels are brighter or higher in numeric value. An area of interest must also contain pixels having a high numerical value after the application of an edge detection filter. A high numerical value indicates large gradient intensity between adjacent pixels, which corresponds to a sharp temperature gradient between adjacent regions. Vehicles are likely to exhibit sharp temperature gradients, either between the vehicle and the surrounding terrain, or between different components of the vehicle, such as an exhaust port and the chassis. An area of interest must satisfy these two different criteria; it must contain hot pixels and it must contain pixels that exhibit large gradients. These are the two criteria in the name Simple, Two-criterion, Automatic Recognition of Targets.

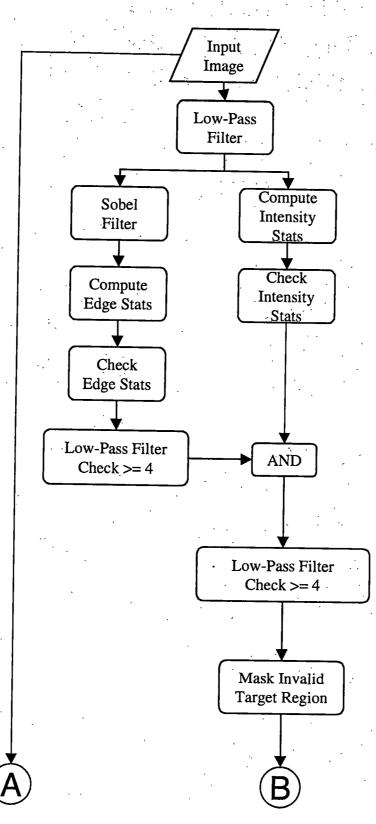

While the core idea of the algorithm is relatively simple, many details of the START algorithm are important to its success. First, the images are low-passed filtered initially to remove noise, as image noise is generally high frequency in nature and produces strong responses in edge detection filters. The threshold values for each of the two criteria are specified as a certain number of standard deviations from the mean. These values are important to the performance of the algorithm and were determined empirically during processing of a large set of input images. The intermediate binary images in the target identification process are low-pass filtered and then thresholded. This favors larger clusters of pixels and eliminates the occasional falsely identified pixel.

#### 1) First Phase

Figure III-2 shows a block diagram of the first part of START algorithm, in which a map of potential target pixels is generated. The input image is first low-pass filtered to remove noise. The unfiltered input image is also passed to the second portion of the algorithm through the connector marked "A". The low-pass filter is implemented by convolving the image with the  $3 \times 3$  mask shown here:

$\begin{bmatrix} 1 & 1 & 1 \\ 1 & 1 & 1 \\ 1 & 1 & 1 \end{bmatrix}$

The resulting image is then divided by 8 to normalize the values. Since the actual maximum multiplier from the mask is 9, dividing by 8 causes some intensity scaling of the low-passed image. Since the relative pixel values remain the same, this has so significant effect on the results. Dividing by 8 can be implemented by a simple right shift, while dividing by 9 is much more expensive in terms of hardware, so the former was chosen.

The filtered image is passed to a block that computes the mean and standard deviation of the intensities of the pixels. These statistics are then used to check for pixels that are more than two standard deviations above the mean. Pixels meeting this criterion are given the value 1 and all others are given the value 0. This produces a map of the pixels that meet the criterion of being relatively hot, since the intensities are linearly proportional to temperature in a FLIR image.

The low-pass-filtered image is also passed to a block that performs edge detection. Edge detection is essentially a high-pass filtering operation, which gives high values to pixels with sharp gradients and low values to pixels with low gradients. The particular edge detection method chosen uses the *Sobel operators* to approximate the gradient. The Sobel operators are two  $3 \times 3$  masks as shown here:

Sobel X operator =

$$\begin{bmatrix} -1 & 0 & 1 \\ -2 & 0 & 2 \\ -1 & 0 & 1 \end{bmatrix}$$

Sobel Y operator =  $\begin{bmatrix} -1 & -2 & -1 \\ 0 & 0 & 0 \\ 1 & 2 & 1 \end{bmatrix}$

The image is convolved separately with each of the two Sobel operators and then the output image is computed as the sum of the absolute values of the responses, which approximates the magnitude of the gradient response [37].

The statistics for the image after edge detection are then computed. The next block then marks all pixels more than four standard deviations above the mean as 1 and the remaining pixels as 0. This produces a pixel map of all pixels meeting the criterion of having a high gradient value and thus being associated with a transition between regions of greatly differing temperatures. This pixel map is then low-pass filtered, without scaling. This gives each output pixel a value from 0 to 9, representing the number of pixels in each 3 x 3 region that had the value 1 in the pixel map. Pixels with values from 0 to 3 are marked as 0 and pixels with values 4 and above are marked as 1. This creates a new pixel map, which indicates where clusters of pixels meeting the gradient criterion were located. This eliminates insignificant temperature changes or changes involving very small objects. The gradient criterion pixel map and the intensity criterion pixel map are then logically AND'ed together. This produces a new pixel map with all pixels that meet both criteria being marked as ones and all other pixels marked as zeros. This map then has the clustering operation described previously applied. Next, regions along the

edges of the image and in the immediate foreground are marked as zeros, since it is known that these are not valid regions for targets to appear in, based on the camera setup and geometry. A final target pixel map is thus generated and output at connector "B" of the flowchart in Figure III-2.

#### 2) Second Phase

In the second phase of the algorithm, the target pixel map is used to identify target regions and draw frames around these regions. A flowchart of the second phase is shown in Figure III-3. The target pixel map enters the second phase flow chart through the connector labeled "B". The next block determines whether there are any pixels in the target map with value 1; and if so, the column and row location of the first such target pixel. This information is passed to two more blocks. The first block marks a square frame centered around the first non-zero pixel found in the previous block. These frame pixels are marked on a blank frame map, which consists of all zeros. The second block masks all target pixels within 30 pixels of the first target is identified for every group of pixels corresponding to a particular vehicle in the FLIR image.

The masked target map is then passed to another block, which repeats the operation of finding the first non-zero pixel. This information is passed to blocks that repeat the frame marking and target masking operations. After six total repetitions of frame marking, the frame mask is complete. The frame is a binary image with pixel values of one everywhere a target frame should appear and pixel values of zero everywhere else. The frame map may contain from zero to six frames, depending on the number of target regions identified. A sample frame map can be seen in Figure III-1(b). This frame map corresponds to the input image shown in Figure III-1(a).

Figure III-3. Second Phase of START Algorithm.

The final step of the START algorithm is to combine the frame map and the original image. The original image enters the flowchart through the connector marked "A". The maximum intensity value in the image is found. This value will be used as the value assigned to the frame pixels. By using the maximum value for the frames, the frame pixels will appear white, but without changing the apparent contrast of the image when displayed. The next block simply replaces every pixel in the original image for which the corresponding frame pixel is one with the maximum intensity value. The pixels in the original image corresponding to zero pixels in the frame map are unchanged. The resulting output image then consists of the original image, with square white frames marked around the identified targets. A sample output image, corresponding to the input image in Figure III-1(a), is shown in Figure III-1(c).

### B. Wildforce Board

A commercially available CCM was chosen to implement the first application. Early research efforts often required the design of a new CCM board to meet the requirements of the research. As the field has matured, however, commercial companies have begun to produce hardware that is flexible enough to be used for a wide range of research topics as well as commercial or industrial applications. The Wildforce-XL board from Annapolis Micro Systems was chosen as the first architecture used in the CHAMPION project and was therefore the board available for the manual implementation presented in this paper. The Wildforce-XL board is based on technology licensed from the developers of Splash-2 [4] and like that CCM, uses Xilinx XC4000 series FPGAs. This section will briefly describe the structure of the Xilinx XC4000 series FPGA, as well as detailing the architecture of the Wildforce board itself.

## 1) Xilinx FPGAs

The Xilinx XC4000 series FPGAs have been widely used for developing CCMs. These FPGAs are in general use throughout the electronics industry, and are thus widely available and relatively inexpensive. There are also many commercial tools available for synthesizing designs for these FPGAs. Xilinx also has an extensive program for supporting university researchers with free or low-cost hardware and software. These facts, combined with their powerful and flexible design, explain the popularity of Xilinx XC4000 series FPGAs with configurable hardware developers.

The basic functional unit of the Xilinx FPGA is the Configurable Logic Block (CLB). A diagram of the CLB is shown in Figure III-4 (Some details relating to RAM functions

Figure III-4. Xilinx 4000 Series FPGA Configurable Logic Block. Source: Xilinx, Inc, The Programmable Logic Data Book 1998. San Jose, CA, 1998. [38]

and carry logic are not included in this diagram). Each CLB has five main components: two four-input function generators, one three-input function generator, and two storage elements. Each of the function generators can be configured to implement any possible function of three or four variables. The function generators can be also combined to produce functions of up to nine variables. The two fourinput function generators receive their inputs from outside the CLB. The three input function generator can use the outputs of the four-input function generators for up to two of its inputs. The remaining input(s) must come from outside of the CLB. The four-input function generators can also be configured to be used as RAM, with up to 32 bits of RAM in each CLB.

In addition to the function generators, there are two configurable storage units in each CLB. These can be configured to act as D-type flip-flops or level sensitive latches. The inputs to the storage units can be configured to come from outside the CLB or from any of the function generators. When used as flip- flops, they can be configured to be clocked on either the rising or falling edges of the clock, and when used as latches they can be configured to be transparent for either high or low clock inputs. The storage elements also have configurable set/reset control and enables.

There are 16 multiplexers in each CLB, six with four inputs and ten with two inputs. These multiplexers are configured to determine the functionality of the CLB. The total functionality of the CLB is determined by the setting for the multiplexers and the settings for the function generators, giving a great deal of flexibility and power in each CLB. The configuration process for the FPGA sets the control inputs to every multiplexer with bits of SRAM. The values in the function generators are also stored in SRAM. This means that the Xilinx FPGA must be reconfigured whenever the power supply to the FPGA is removed and restored.

Every Xilinx 4000 series FPGA contains a square matrix of CLBs, surrounded by a ring of Input/Output Blocks (IOBs). The IOB connect the CLBs to the pins of the FPGA. The IOBs are configurable and can be programmed for different electrical characteristics, use of registers, etc. Each FPGA has an extensive set of internal routing tracks, and many blocks of programmable switches which can form connections between the tracks and the CLBs and IOBs. Different FPGAs in the XC4000 series have different numbers of CLBs, and differ in the exact interconnections available internally and pins available externally.

Each FPGA configuration consists of individual settings for every CLB and IOB, and settings for every programmable interconnection point. The total configuration stream can reach nearly two million bits for the largest Xilinx FPGAs. In CCM applications, the configuration data is usually sent to the FPGA from a host computer. The data can be sent to the FPGA serially or in parallel, at either 1 MHz or 8 MHz clock rates. Even at the faster speed, configuring a large FPGA can take tens or hundreds of milliseconds. The Xilinx XC4000 series FPGA cannot be partially configured; that is, the entire FPGA must be reconfigured to change any of the device settings.

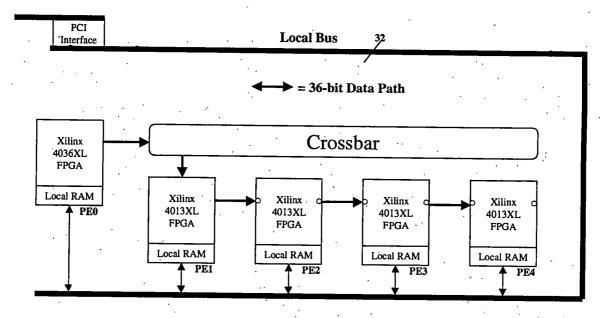

2) Board Architecture

Annapolis Microsystems manufactures several different types of CCM boards. The one used in this project is the Wildforce-XL board. It is a PCI-bus card, which uses five Xilinx XC4000XL FPGAs for processing elements. The specific version of the board used had 1 XC4036XL FPGA and 4 XC4013XL FPGAs available for processing. A comparison of the resources in each FPGA is shown in Table III-1.

| ,<br>    | Logic Cells | CLB Matrix | Total CLBs | Number of<br>Flip-Flops | Equivalent<br>Gate Count |

|----------|-------------|------------|------------|-------------------------|--------------------------|

| XC4013XL | 1368        | 13 x 13    | 576        | 1536                    | 10,000 –<br>30,000       |

| XC4036XL | 3078        | 36 x 36    | 1296       | 3168                    | 22,000 –<br>65,000       |

## Table III-1. Resources Available in FPGAs Used on Wildforce-XL.

Source: Xilinx, Inc, The Programmable Logic Data Book 1998. San Jose, CA, 1998. [38]

Annapolis Microsystems refers to the FPGAs on the Wildforce board as *processing elements*. The XC4036XL FPGA is called a *control processing element* and given the designation CPE0. It differs from the other FPGAs in that it is larger, and also in that it has control lines available for various resources on the board, such as the external I/O interface and crossbar configuration register, that are not available to the other FPGAs. The four XC4013XL FPGAs are given the designations PE1, PE2, PE3, and PE4. These four processing elements are connected together in a linear array by a 36-bit *systolic bus*. All five FPGAs can be connected by the 36-bit *crossbar*, which selectively allows connections between any of the processing elements. CPE0 can only connect to the other processing elements through the crossbar.

Each FPGA on the board has a small daughterboard associated with it, which can be populated with memory or a Digital Signal Processing (DSP) chip. Each of the FPGAs on the board used in this project had 32 KB of 32-bit SRAM on its daughterboard. These daughterboards have a dual-port memory controller such that both the FPGA and the host computer can access the SRAM.

The board also contains a PCI interface for communicating with the host computer, and several FIFO registers to facilitate data transfer across the PCI bus. Figure III-5, shows a simplified block diagram of the Wildforce board. Since there are many

Figure III-5. Wildforce-XL Block Diagram.

resources available on the Wildforce board and many configurations of the crossbar and other components, it was decided to use a constrained configuration of the board for the initial manual and automatic implementations. This reduces the problem complexity to a more manageable level. Eventually the constraints on the board utilization will be relaxed so that all of the power of the Wildforce-XL board will be available in the automated CHAMPION system.

The constrained configuration of the board used in this project did not use any of the FIFOs. All communication with the host was done through the SRAM associated with each processing element. The crossbar was used only to provide a 36-bit path from CPEO to PE1. The connections between processing elements are normally bidirectional. For the constrained implementation, however, it was decided that the direction of all connections between processing elements would be fixed so that all signals would pass in one direction only. The board topology became a linear array,

with all signals starting in CPEO passing to PE1. No signals could run from PE1 back to CPEO. Similarly, all signals from PE1 ran to PE2, with no signals allowed to pass back from PE2 to PE1. A diagram showing the configuration of the Wildforce-XL board as used in this project is shown in Figure III-6.

Figure III-6. Wildforce-XL Board As Used.

# IV. IMPLEMENTATION

## A. Cantata Implementations of START

#### 1) Standard Cantata

The START algorithm was initially developed for a graduate class in digital image processing and was written in the MATLAB language. After the decision was made to adopt the START algorithm for this project, it first had to be implemented in Cantata. The first Cantata version used glyphs from the standard toolboxes supplied with the Khoros software package. It took approximately eight days to successfully implement the application in Cantata using the standard glyphs. The standard Cantata implementation took 57 seconds to process one 256 x 256 image from the set of test images.

Ninety-nine total glyphs were needed to implement the algorithm. Only 20 different glyphs were needed, but many of these glyphs were used repeatedly. A list of the glyphs used is shown in Table IV-1. Upon examination of the Cantata workspace, it was apparent that some of the glyphs used could be implemented directly in hardware and some could not be directly implemented in any practical manner. For instance, the glyphs classified as arithmetic in Table IV-1, addition and absolute value, are standard operators that can be easily implemented in hardware. The glyphs classified as Khoros specific, on the other hand, perform functions that are specific to the data structures used in Khoros. Since these complex data structures are not readily implementable in hardware, functions related to these data structures have no direct hardware equivalent. Determining which glyphs had

| Glyph Name Glyph Type |                  | Hardware Equivalent? | Times Used |

|-----------------------|------------------|----------------------|------------|

| Read File             | File I/O         | Yes                  | 6          |

| Save File             | File I/O         | Yes                  | 1          |

| Right Shift           | Bitwise operator | Yes                  | 1          |

| AND                   | Bitwise operator | Yes                  | 1          |

| OR                    | Bitwise operator | Yes                  | 6          |

| NOT                   | Bitwise operator | Yes                  | 1          |

| >=                    | Comparison       | Yes                  | 4          |

| >                     | Comparison       | Yes                  | 7          |

| Absolute Value        | Arithmetic       | Yes                  | 2          |

| Add                   | Arithmetic       | Yes                  | 8          |

| Inset                 | Geometric        | No                   | 1          |

| Pad                   | Geometric        | No                   | 18         |

| Statistics            | Mathematical     | No                   | 9          |

| Convolve              | Mathematical     | No                   | 5          |

| Convert Type          | Data Handling    | No                   | 5          |

| Switch                | Data Handling    | Yes                  | 6          |

| Constant              | Data Handling    | Yes                  | 15         |

| Copy from Value       | Khoros Specific  | No                   | 1          |

| Insert Segment        | Khoros Specific  | No                   | 1          |

| Unmask                | Khoros Specific  | No                   | 1          |

Table IV-1. Glyphs Used in Standard Cantata Implementation of START.

hardware equivalents and which did not was crucial to the eventual implementation of the START algorithm in hardware.

Besides the addition and absolute value glyphs, other glyphs that were clearly readily implementable in hardware were the comparison operators and the bitwise operators. The file I/O operators would not actually be accessing file structures on a hard drive, but would be accessing data transferred to the CCM hardware by the host, and would thus perform an analogous function. They were therefore also considered to have a hardware equivalent. The switch glyph performed a function identical to that performed by a multiplexer, so it had a clear hardware equivalent. The constant glyph simply generates a constant value, which can be done in hardware by simply fixing wires to logical ones or zeros.

Many other glyphs had no clear hardware equivalent. The pad and inset glyphs performed geometric operations on a two-dimensional image. There was no directly equivalent way to do these two-dimensional operations in a hardware implementation where the images would be streamed through in one dimension. The statistics glyph presented a different problem. This glyph calls a Khoros routine that can perform over 25 different statistical functions, from simple functions such as mean, to much more complex functions such as skew and kurtosis. It would not be efficient to create a hardware module that performed all of these functions if only one or two were used in a given application. Since the START application only needed the mean and standard deviation functions, it made sense to have these be implemented separately, using other hardware glyphs, rather than by a monolithic statistics block capable of performing other operations. The convolve operator had a problem similar to the statistics glyph, in that its functionality was too broad. It could perform a convolution of one image with a mask of any size and with any values. This sort of flexibility can not be implemented efficiently in hardware. An efficient implementation of convolution would have to have a structure specified by the mask to be used, so a general-purpose convolution block had no direct hardware equivalent. The convert type glyph converts data from one data type to another, such as from floating point to integer. Since the data types would have to be managed quite differently in hardware than they are in software, there could be no glyph performing this exact function in hardware. As mentioned previously, the three glyphs that performed Khoros specific functions also had no hardware equivalents.

The implementation of the START algorithm in standard Khoros revealed several problems. As just discussed, many of the glyphs used in standard Khoros have no exact hardware equivalent. The START algorithm would have to be implemented in Cantata again, using only glyphs that had hardware equivalents. However, the

functionality of the glyphs that did not have hardware equivalents would have to be duplicated in some fashion that was compatible with glyphs that could be implemented. This required the creation of glyphs to perform new functions that would map directly to a hardware implementation.

### 2) Hardware Equivalent Cantata

After the problems with the standard Cantata implementation were identified, development of a new Cantata implementation that would be more compatible with hardware implementation was begun. Some portions of the original workspace contained only hardware compatible glyphs and could be retained, but in general, the algorithm had to be re-implemented from scratch. It took more than three weeks to develop the hardware equivalent Cantata workspace, including the time taken to develop the custom glyphs.

The hardware equivalent implementation took 17 minutes and 34 seconds to process one 256 x 256 image from the test image set. This is more than eleven times longer than the standard Cantata version. Not only did the hardware equivalent version have more glyphs than the standard version, but also some of the glyphs in the hardware equivalent were custom glyphs. Due to the way that Cantata integrates custom glyphs with the standard ones, custom glyphs are much slower.

The new implementation was identified as being *hardware equivalent Cantata*. It contained a mix of standard Cantata glyphs and glyphs that were designed especially for this project and were linked to C programs that performed the desired functions. The hardware equivalent Cantata version required a total of 305 glyphs, of 24 different types. The glyphs used are shown in Table IV-2. Many of the glyphs used are in the standard Cantata toolboxes, although not all of these were used in the

| Glyph Name          | Glyph Source | In First Version ? | Times Used |

|---------------------|--------------|--------------------|------------|

| RAM Read            | Custom       | No                 | 1          |

| RAM Write           | Custom       | No                 | <u> </u>   |

| Convolution Stream  | Custom       | No                 | 4          |

| Stream Max          | Custom       | No                 | 7          |

| Stream Sum          | Custom       | No                 | 4          |