#### University of Tennessee, Knoxville

# TRACE: Tennessee Research and Creative Exchange

**Doctoral Dissertations**

**Graduate School**

5-2001

# Automatic mapping of graphical programming applications to microelectronic technologies

Sze-Wei Ong

Follow this and additional works at: https://trace.tennessee.edu/utk\_graddiss

#### **Recommended Citation**

Ong, Sze-Wei, "Automatic mapping of graphical programming applications to microelectronic technologies." PhD diss., University of Tennessee, 2001. https://trace.tennessee.edu/utk\_graddiss/8562

This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by Sze-Wei Ong entitled "Automatic mapping of graphical programming applications to microelectronic technologies." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Electrical Engineering.

Donald W. Bouldin, Major Professor

We have read this dissertation and recommend its acceptance:

Accepted for the Council:

Carolyn R. Hodges

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

#### To the Graduate Council:

I am submitting herewith a dissertation written by Sze-Wei Ong entitled "Automatic Mapping of Graphical Programming Applications to Microelectronic Technologies." I have examined the final copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosopy, with a major in Electrical Engineering.

Smald W. Bouldin

Donald W. Bouldin, Major Professor

We have read this dissertation and recommend its acceptance:

May Val

Darbia Tan

Accepted for the Council:

Interim Vice Provost and (Dean of The Graduate School

# AUTOMATIC MAPPING OF GRAPHICAL PROGRAMMING APPLICATIONS TO MICROELECTRONIC TECHNOLOGIES

A Dissertation

Presented for the

Doctor of Philosophy

Degree

The University of Tennessee, Knoxville

Sze-Wei Ong

May, 2001

#### ACKNOWLEDGEMENT

I would first like to thank my advisor, Professor Donald W. Bouldin, for his support, guidance and encouragement during this research. Professor Bouldin introduced me to the area of VLSI design and provided me many helpful ideas in this research. The encouragement, valuable criticism, and technical advice from Professor Bouldin has sustained my progress in the research. I also thank my other committee members, Dr. Danny Newport, Dr. Michael A. Langston, Dr. Daniel B. Koch and Dr. Chandra Tan, for their guidance and useful suggestions. I would also like to acknowledge the Defense Advanced Research Projects Agency for providing the financial support for this research under grant F33615-97-C-1124. Finally, my sincere thanks go to Ee-Laine Cheong and my parents Yok-Ting Ong and Siew-Sin Chew for their love, patience, understanding, and support.

#### ABSTRACT

Adaptive computing systems (ACSs) and application-specific integrated circuits (ASICs) can serve as flexible hardware accelerators for applications in domains such as image processing and digital signal processing. However, the mapping of applications onto ACSs and ASICs using the traditional methods can take months for a hardware engineer to develop and debug. In this dissertation, a new approach for automatic mapping of software applications onto ACSs and ASICs has been developed, implemented and validated. This dissertation presents the design flow of the software environment called CHAMPION, which is being developed at the University of Tennessee. This environment permits high-level design entry using the Cantata graphical programming software from KRI. Using Cantata as the design entry, CHAMPION hides from the user the low-level details of the hardware architecture and the finer issues of application mapping onto the hardware. Validation of the CHAMPION environment was performed using multiple applications of moderate complexity. In one case, the application mapping time which required six weeks to perform manually took only six minutes for CHAMPION, yet comparable results were produced. Furthermore, the CHAMPION environment was constructed such that retargeting to a new adaptive computing system could be accomplished in just a few hours as opposed to weeks using manual methods. Thus, CHAMPION permits both ACSs and ASICs to be utilized by a wider audience and application development accomplished in less time.

## TABLE OF CONTENTS

| C) | CHAPTER |        |                                              | PA | PAGE |  |

|----|---------|--------|----------------------------------------------|----|------|--|

| 1. | Int     | roduc  | tion                                         |    | 1    |  |

|    | 1.1     | Motiv  | vation                                       |    | 6    |  |

|    | 1.2     | Proble | em Statement                                 |    | 7    |  |

|    | 1.3     | Goals  | and Expected Contributions                   |    | 9    |  |

| 2. | Ba      | ckgrou | ınd                                          |    | 10   |  |

|    | 2.1     | Micro  | electronic Technologies                      |    | 11   |  |

|    | 2.2     | Design | n flows of ACS and ASIC                      |    | 13   |  |

|    |         | 2.2.1  | Design Flow of ACS                           |    | 14   |  |

|    |         | 2.2.2  | Design Flow of ASIC                          |    | 17   |  |

|    |         | 2.2.3  | Comparison between ACS and ASIC Design Flows |    | 20   |  |

|    | 2.3     | Khoro  | os Software Development Environment          |    | 21   |  |

|    |         | 2.3.1  | Cantata Graphical Programming Environment    |    | 22   |  |

|    | 2.4     | Differ | ences between Cantata and Hardware           |    | 25   |  |

|    |         | 2.4.1  | Data Transfer                                |    | 25   |  |

|    |         | 2.4.2  | Data Synchronization                         |    | 27   |  |

|    |         | 2.4.3  | Data Sizing                                  |    | 29   |  |

|    | 2.5     | Relate | ed Work                                      |    | 30   |  |

|    |         | 2.5.1  | CAMERON Project: Colorado State University   |    | 30   |  |

|    | CH. | APTE   | R                                                    | PA | GE |

|----|-----|--------|------------------------------------------------------|----|----|

|    |     | 2.5.2  | MATCH Project: Northwestern University               |    | 37 |

|    |     | 2.5.3  | Commercial Software                                  |    | 42 |

| 3. | Me  | thodol | ogy                                                  |    | 44 |

|    | 3.1 | Overvi | iew of the Design Flow of CHAMPION                   |    | 44 |

|    | 3.2 | Glyph  | Development Flow                                     |    | 48 |

|    |     | 3.2.1  | Glyph Development and Verification                   |    | 49 |

|    |     | 3.2.2  | Glyph Installation                                   |    | 53 |

|    |     | 3.2.3  | Pipelined Glyphs                                     |    | 53 |

|    |     | 3.2.4  | Control Lines in CHAMPION Glyphs                     |    | 56 |

|    | 3.3 | Front- | end Flow                                             |    | 58 |

|    |     | 3.3.1  | Converting Cantata Workspace to CHAMPION Netlist     |    | 58 |

|    |     | 3.3.2  | Data Width Matching                                  |    | 59 |

|    |     | 3.3.3  | Data Synchronization                                 |    | 61 |

|    | 3.4 | ACS E  | Back-end Flow                                        |    | 90 |

|    |     | 3.4.1  | Partitioning                                         |    | 90 |

|    |     | 3.4.2  | Netlist to Structural VHDL, Synthesis, and Placement | &  |    |

|    |     |        | Routing                                              |    | 92 |

|    |     | 3.4.3  | Host Program Generation                              |    | 93 |

|    | 3.5 | ASIC : | Back-end Flow                                        |    | 93 |

|    |     | 3.5.1  | Netlist to Structural VHDL                           |    | 93 |

|    |     | 3.5.2  | Design Compilation and Optimization                  |    | 93 |

|    |     | 3.5.3  | Physical Layout Generation                           |    | 95 |

|    |     | CHA     | PTER                                                   | PA  | GE  |

|----|-----|---------|--------------------------------------------------------|-----|-----|

| 4. | Im  | pleme   | ntation                                                |     | 98  |

|    | 4.1 | Wildfo  | orce Board                                             |     | 100 |

|    | 4.2 | HP260   | G                                                      |     | 103 |

|    | 4.3 | CHAN    | MPION Graphical User Interface and Command Line Us     | er  |     |

|    |     | Interfa | ace                                                    |     | 103 |

|    | 4.4 | Glyph   | Development Flow                                       |     | 106 |

|    |     | 4.4.1   | Glyph Development Tools                                |     | 106 |

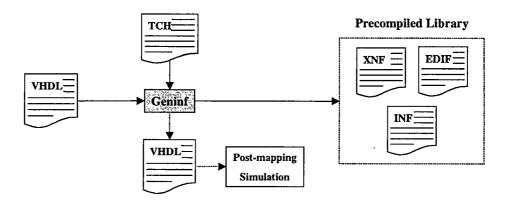

|    |     | 4.4.2   | Glyph Installation Tools                               |     | 107 |

|    | 4.5 | Front-  | End Flow                                               |     | 110 |

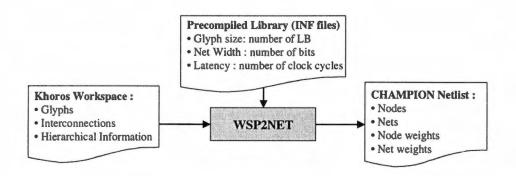

|    |     | 4.5.1   | Conversion of Cantata Workspace to CHAMPION Netlis     | st  | 110 |

|    |     | 4.5.2   | Data Width Matching                                    |     | 111 |

|    |     | 4.5.3   | Data Synchronization                                   |     | 111 |

|    | 4.6 | ACS E   | Back-End Flow                                          |     | 120 |

|    |     | 4.6.1   | Partitioning                                           |     | 120 |

|    |     | 4.6.2   | Netlist to Structural VHDL, Synthesis, and Place & Rou | te. | 120 |

|    |     | 4.6.3   | Host Program Generation                                |     | 121 |

|    | 4.7 | ASIC    | Back-end Flow                                          |     | 121 |

|    |     | 4.7.1   | Netlist to Structural VHDL                             |     | 121 |

|    |     | 4.7.2   | Design Compilation and Optimization                    |     | 122 |

|    |     | 4.7.3   | Physical Layout Generation                             |     | 122 |

| 5. | Exp | erime   | ental Results                                          |     | 123 |

|    |     |         | Pass Filter                                            |     | 194 |

| CHAPTER      | PAG                                                        |     |  |  |  |

|--------------|------------------------------------------------------------|-----|--|--|--|

| 5.1.1        | Overview                                                   | 124 |  |  |  |

| 5.1.2        | Implementation Results                                     | 125 |  |  |  |

| 5.2 IR A     | $\Gamma R$ algorithm from the Army Night Vision Laboratory | 140 |  |  |  |

| 5.2.1        | Overview of the Algorithm                                  | 140 |  |  |  |

| 5.2.2        | Implementation Results                                     | 142 |  |  |  |

| 5.3 Face :   | Detection Algorithm                                        | 148 |  |  |  |

| 5.3.1        | Overview of the Algorithm                                  | 148 |  |  |  |

| 5.3.2        | Implementation Results                                     | 149 |  |  |  |

| 5.4 STAR     | T Algorithm                                                | 161 |  |  |  |

| 5.4.1        | Overview of the Algorithm                                  | 161 |  |  |  |

| 5.4.2        | Implementation Results                                     | 162 |  |  |  |

| 6. Summar    | y and Future Work                                          | 167 |  |  |  |

| BIBLIOGRAPHY |                                                            |     |  |  |  |

| T/T/T A      |                                                            | 172 |  |  |  |

## LIST OF FIGURES

| FIGURE PAGI |                                                                   |    |

|-------------|-------------------------------------------------------------------|----|

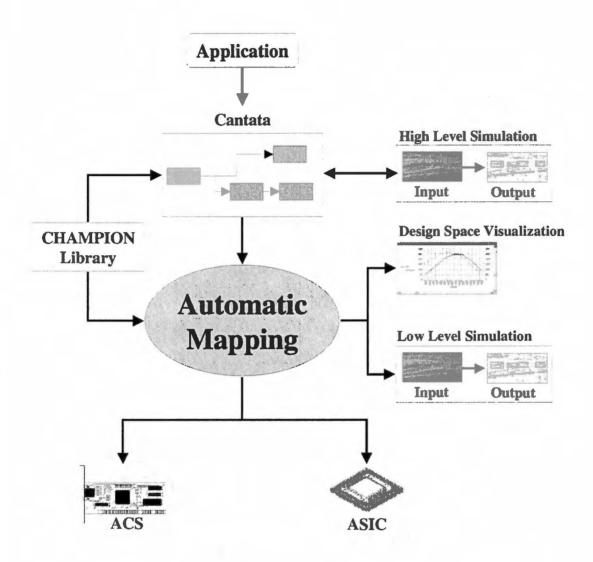

| 1.1         | CHAMPION software design environment                              | 4  |

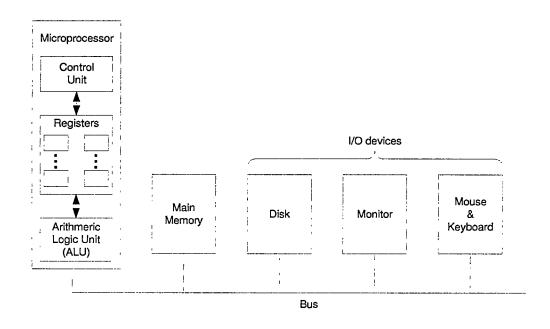

| 2.1         | Organization of a simple bus-oriented microprocessor              | 12 |

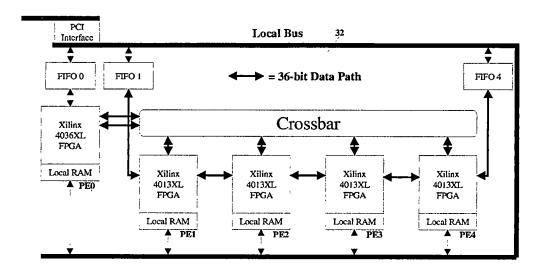

| 2.2         | Architecture of the Wildforce board.                              | 14 |

| 2.3         | ACS design flow                                                   | 15 |

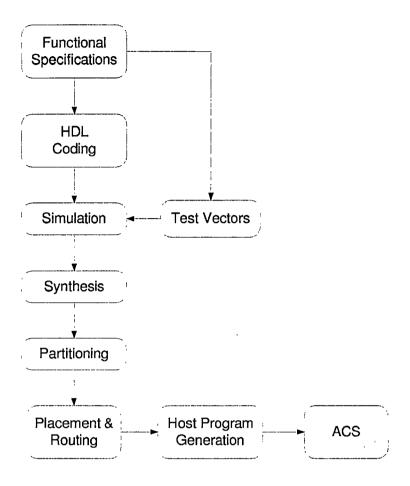

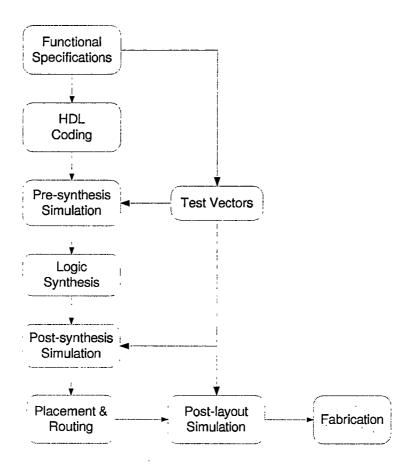

| 2.4         | ASIC design flow                                                  | 18 |

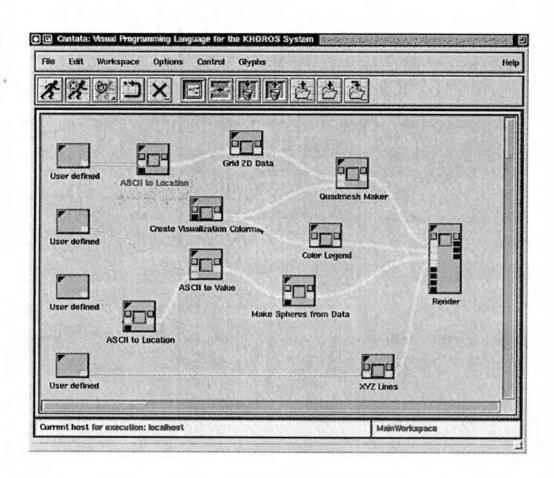

| 2.5         | A sample Cantata workspace                                        | 23 |

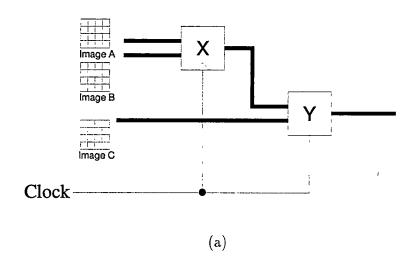

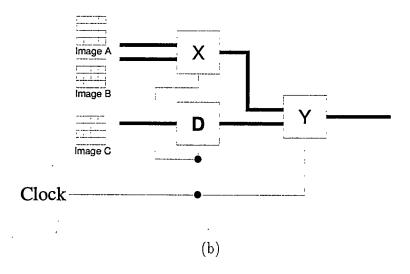

| 2.6         | Synchronization using delay buffers. (a) Unsynchronized glyphs    |    |

|             | and (b) glyphs synchronized by delay insertion                    | 28 |

| 2.7         | Design flow of CAMERON project                                    | 33 |

| 2.8         | The heterogeneous hardware system used in the MATCH project       |    |

|             | [5]                                                               | 38 |

| 2.9         | Match compiler [5]                                                | 40 |

| 3.1         | Design flow of CHAMPION                                           | 45 |

| 3.2         | Four main flows in CHAMPION                                       | 46 |

| 3.3         | Steps for developing a new glyph                                  | 50 |

| 3.4         | Glyph verification methods                                        | 51 |

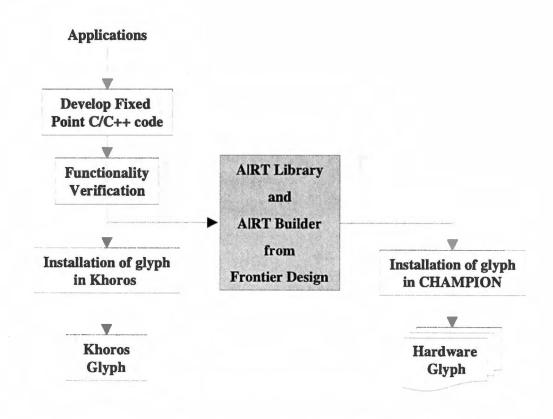

| 3.5         | New glyph development using ART Library and Builder               | 52 |

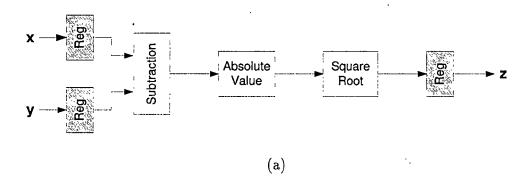

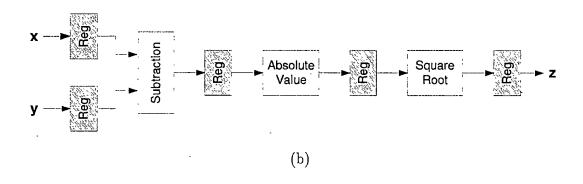

| 3.6         | Datapath structures. (a) Nonpipelined structure and (b) pipelined |    |

|             | structure                                                         | 54 |

| FIG  | PA                                                                   | GE |

|------|----------------------------------------------------------------------|----|

| 3.7  | Structure of CHAMPION glyph                                          | 57 |

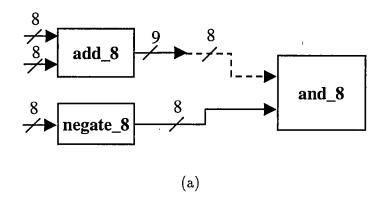

| 3.8  | Positive mismatch. (a) Example of a positively mismatched data       |    |

|      | path and (b) insertion of "truncating" glyph in positively mis-      |    |

|      | match data path                                                      | 60 |

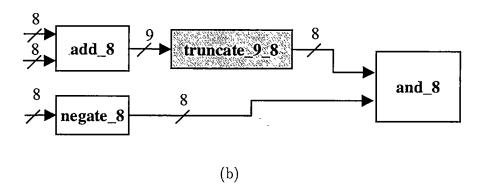

| 3.9  | Negative mismatch. (a) Example of a negatively mismatched data       |    |

|      | path and (b) Insertion of "padding" glyph in positively mismatch     |    |

|      | data path                                                            | 62 |

| 3.10 | An unsynchronized digital system                                     | 63 |

| 3.11 | A digital system which uses clock-triggered registers to synchronize |    |

|      | the data                                                             | 65 |

| 3.12 | Synchronization approaches. (a) The result of synchronizing the      |    |

|      | system using the simple approach and (b) an optimum synchro-         |    |

|      | nization                                                             | 67 |

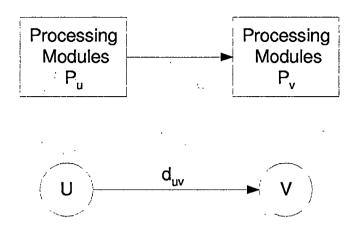

| 3.13 | A block diagram of processing modules with their corresponding       |    |

|      | SFG                                                                  | 70 |

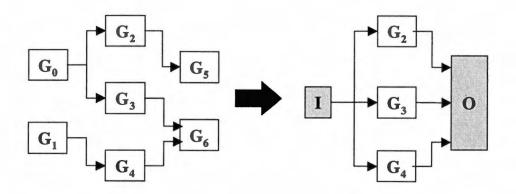

| 3.14 | Insertion of input and output nodes in the SFG                       | 71 |

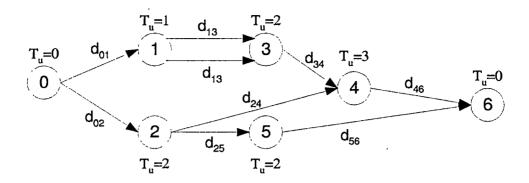

| 3.15 | The SFG representation of the digital system shown in Figure 3.10.   | 72 |

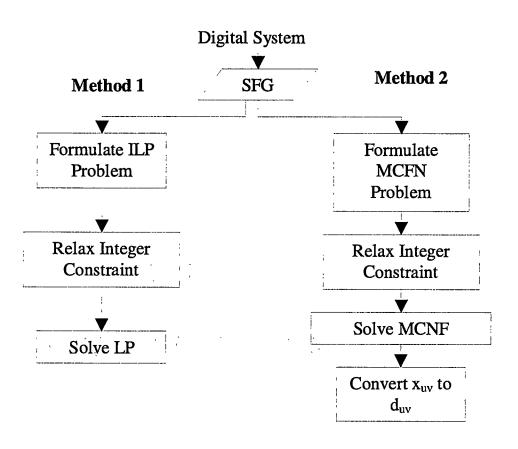

| 3.16 | Two methods for data synchronization                                 | 83 |

| 3.17 | Hyperarc                                                             | 87 |

| 3.18 | Different representations of a hyperarc                              | 88 |

| 3.19 | Delays of the hyperarc                                               | 89 |

| 3.20 | The design flow of Epoch tool                                        | 96 |

| FIG  | URE PAGE                                                        |

|------|-----------------------------------------------------------------|

| 4.1  | Design flow of CHAMPION                                         |

| 4.2  | A simplified block diagram of the Wildforce board 101           |

| 4.3  | Wildforce board as used in CHAMPION                             |

| 4.4  | CHAMPION graphical user interface                               |

| 4.5  | Art Library classes [4]                                         |

| 4.6  | Glyph installation process using Geninf                         |

| 4.7  | Conversion of Cantata workspace to CHAMPION netlist 110         |

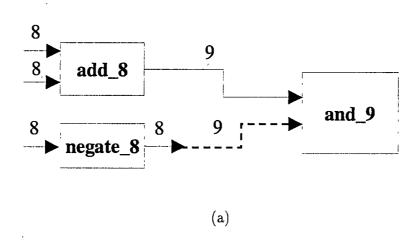

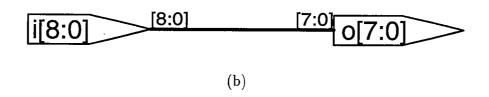

| 4.8  | Example of truncating glyph. (a) VHDL file for a truncate_9_8   |

|      | glyph and (b) the corresponding hardware architecture 112       |

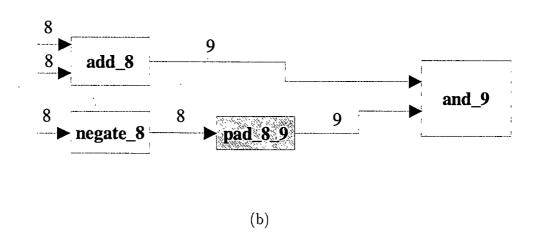

| 4.9  | Example of padding glyph. (a) VHDL file for a pad_8_9 glyph and |

|      | (b) the corresponding hardware architecture                     |

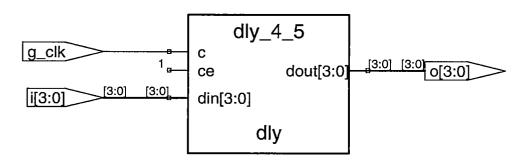

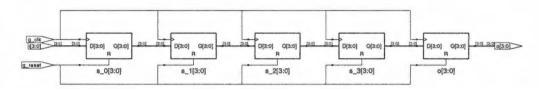

| 4.10 | Delay glyph using components from Xilinx Core Generator 116     |

| 4.11 | Hardware architecture of the VHDL file in Figure 4.10 117       |

| 4.12 | Delay glyph for ASIC implementation                             |

| 4.13 | Hardware architecture of the VHDL file in Figure 4.12 119       |

| 4.14 | Data Synchronization process                                    |

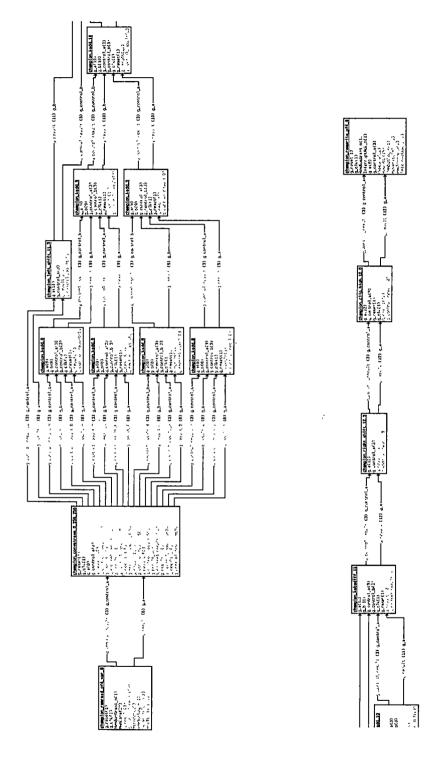

| 5.1  | Cantata Workspace for the high-pass filter                      |

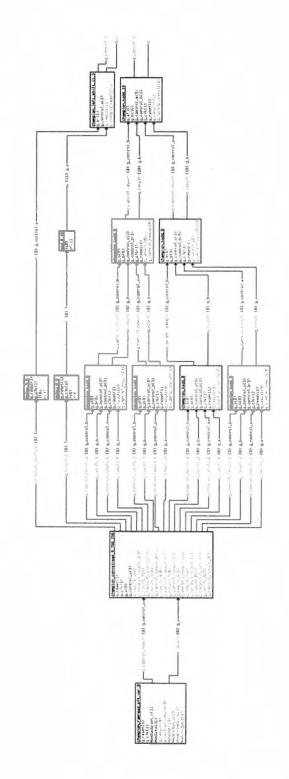

| 5.2  | High-pass filter in CHAMPION netlist                            |

| 5.3  | High-pass filter in after data width matching                   |

| 5.4  | High-pass filter after data synchronization                     |

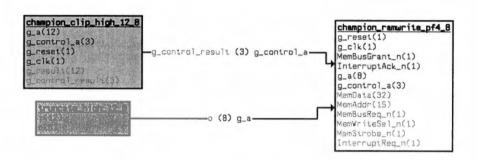

| 5.5  | First partition of high-pass filter                             |

| 5.6  | Second partition of the high-pass filter                        |

FIGURE PAGE

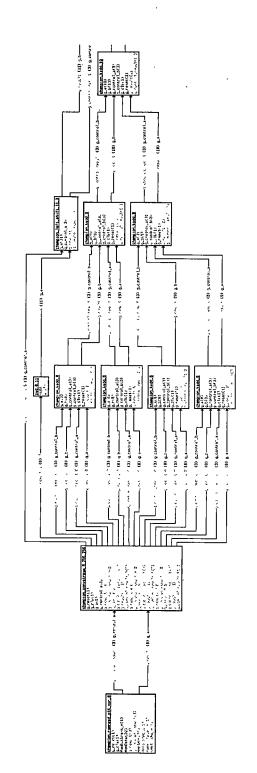

| 5.7  | The core of the high-pass filter generated using the top-down ap-   |

|------|---------------------------------------------------------------------|

|      | proach                                                              |

| 5.8  | The core of the high-pass filter generated using the bottom-up      |

|      | approach                                                            |

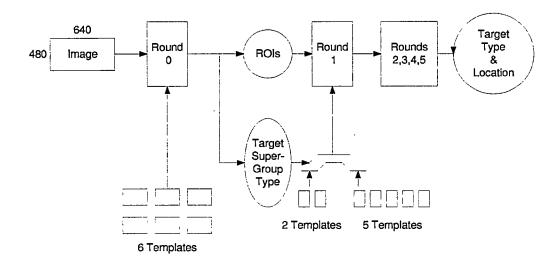

| 5.9  | The IR ATR algorithm                                                |

| 5.10 | The core of the Round 0 generated using the top-down approach. 14   |

| 5.11 | The core of the Round 0 generated using the bottom-up approach. 14  |

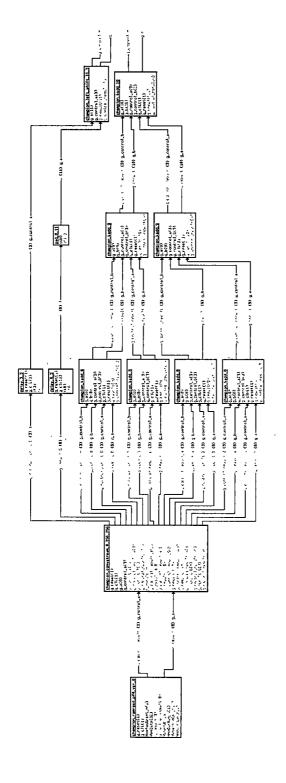

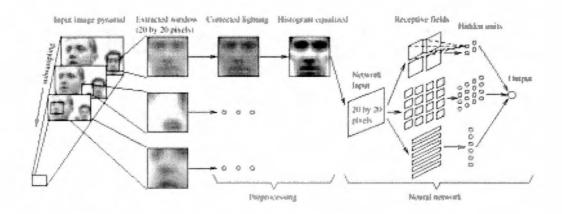

| 5.12 | The basic algorithm used for face detection [27]                    |

| 5.13 | The core of Umec Layer 1 generated using the top-down approach. 15  |

| 5.14 | The core of Umec Layer 1 generated using the bottom-up approach.152 |

| 5.15 | The core of Umec Layer 2 generated using the top-down approach. 154 |

| 5.16 | The core of Umec Layer 2 generated using the bottom-up approach 155 |

| 5.17 | The core of Face17c generated using the top-down approach 150       |

| 5.18 | The core of Face17c generated using the bottom-up approach 15       |

| 5.19 | The core of Face18c generated using the top-down approach 158       |

| 5.20 | The core of Face18c generated using the bottom-up approach 159      |

| 5.21 | The core of START generated using the top-down approach 164         |

| 5.22 | The core of START generated using the bottom-up approach 168        |

### LIST OF TABLES

| TABLE |                                                     | PA | GE  |

|-------|-----------------------------------------------------|----|-----|

| 3.1   | Pipelined computations                              |    | 56  |

| 3.2   | Equation 3.6 in matrix form                         |    | 76  |

| 3.3   | Dual of the ILP expressed by Equation 3.6           |    | 77  |

| 3.4   | The MCNF problem in matrix from                     |    | 80  |

| 4.1   | Resources on XC4013XL and XC4036XL FPGAs            |    | 100 |

| 4.2   | Comparison of execution time of Simplex algorithm   |    | 114 |

| 5.1   | Sizes of the four applications implemented          |    | 124 |

| 5.2   | Partitions of high-pass filter                      |    | 133 |

| 5.3   | ACS mapping time of high-pass filter                |    | 135 |

| 5.4   | Execution time of high-pass filter                  |    | 136 |

| 5.5   | ASIC implementation results of the high-pass filter |    | 139 |

| 5.6   | Partitions of Round 0                               |    | 143 |

| 5.7   | ACS mapping time of Round 0                         |    | 143 |

| 5.8   | Execution time of Round 0                           |    | 144 |

| 5.9   | ASIC implementation results of Round 0              |    | 146 |

| 5.10  | ACS mapping time of Round 0                         |    | 150 |

| 5.11  | ASIC implementation results of the neural networks  |    | 153 |

| 5.12  | Execution time of START [12]                        |    | 163 |

| 5.13  | ASIC implementation results of the START algorithm  |    | 166 |

#### CHAPTER 1

#### Introduction

Graphical programming environments such as Khoros [25, 31] from KRI, Lab-VIEW from National Instruments, and Simulink from MathWorks, allow applications to be graphically represented as a set of functional blocks connected by signal paths. By insulating the application programmer from low-level or machine-dependent programming details, these environments allow faster and easier development of complex applications. Although complex applications can be easily developed with the help of these graphical programming environments, the execution times are often long due to large input data or computationally intensive operators in the applications. For many types of commercial and military applications, which require high throughput, these long execution times are simply unacceptable.

With advances in microelectronic technology, these complex applications, which are traditionally implemented in software, can now be implemented in hardware. Two main types of integrated circuits can be used to implement these applications. The first type of integrated circuit is the programmable logic devices such as Field Programmable Gate Array (FPGA) and Complex Programmable Logic Device (CPLD). Programmable logic devices contain circuitry that can be

configured by the user to implement a wide range of logic circuits. These chips include a collection of programmable switches that allow the internal cells to be reconfigured in many different ways. The switches are programmed by the end user, rather than during the fabrication of the chip. The programmable logic devices can dramatically reduce manufacturing turn-around time and cost of low volume manufacturing.

The programmable logic devices have a major drawback. The programmable switches in these devices consume valuable chip area and limit the speed of operation of the implemented circuits. To improve the circuit performance or reduce the chip area, the circuit can be implemented in a custom-designed chip. Such chips are intended for use in specific applications and therefore, are often called application-specific integrated circuits (ASICs). The main advantage of a custom-designed chip is that it usually leads to better performance since its design can be optimized for a specific task. However, the cost of designing such chips is usually much higher than that of programmable logic devices. But if the chips are used in a product that is sold in large quantities, the design cost is amortized over the large number of copies manufactured. Therefore, the cost per chip would be lower than that of programmable logic devices.

Although hardware can be used to improve the performance of complex applications, the lack of supportive design environments results in an unacceptably long turn-around time for leveraging the benefits of hardware technology. To reduce the design time significantly, it is necessary to develop mapping tools that

allow the designers to reduce the time required to move from specifications to hardware implementation.

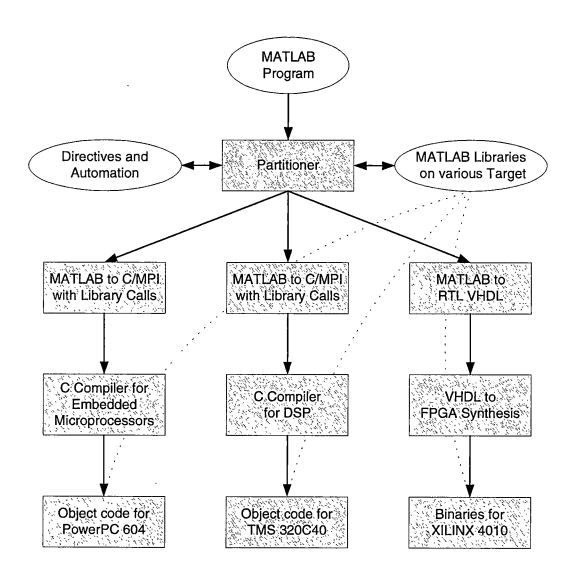

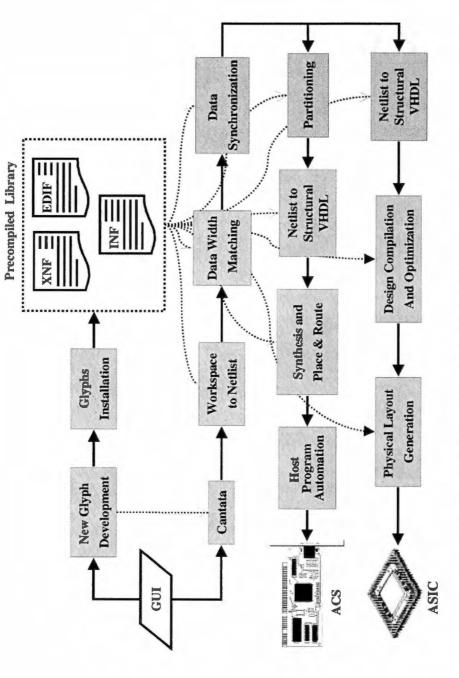

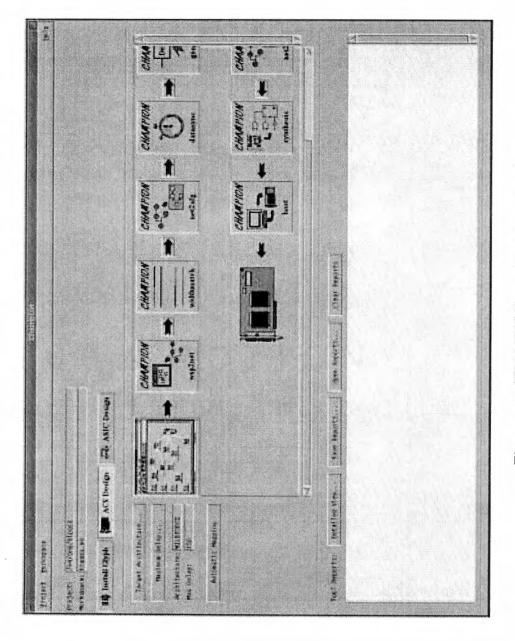

In this dissertation, a new approach for automatic mapping of software applications onto ACSs and ASICs has been developed, implemented and validated. This dissertation presents the design flow of the software environment called CHAMPION, which is developed by the Microelectronic Systems Research Laboratory at the University of Tennessee. This software design environment takes graphical programming applications, and automatically map them onto ACS and ASIC (as shown in Figure 1.1). The graphical programming environment used in the CHAMPION project is Cantata by KRI. The target hardware architectures of the CHAMPION project are the programmable logic devices based computing system known as Adaptive Computing System (ACS) and Application-Specific Integrated Circuit (ASIC). Using CHAMPION, application designers can develop their applications using Cantata and implement them on an ACS or ASIC.

In this dissertation, the design flow of the software to hardware mapping in the CHAMPION project is presented. Relative to contemporary technology, the design flow developed and implemented in this dissertation:

- allows the functionality to be captured faster and more accurately using precompiled functions,

- produces synchronous circuit by synchronizing the design using delay buffers,

- uses linear programming to minimize the number of delay buffers used for

Figure 1.1: CHAMPION software design environment.

synchronizing the design

- partitions the design early instead of late to shorten the hardware mapping time

- allows the automatic mapping to be targeted to both ACS and ASIC.

This dissertation presents the algorithms, approaches, and mathematical techniques used in the design flow of the CHAMPION project. The main emphasis of the mechanisms used in this research is to shorten the mapping time while producing an implementation with performance which is compatible to the contemporary technology.

Several relatively complicated algorithms have been implemented using CHAMPION. A two criteria automatic target recognition algorithm was first implemented to validate the design flow. This algorithm was automatically as well as manually mapped onto ACS. It serves as a benchmark for determining the improvement in the designer productivity using CHAMPION. Three other algorithms have also been implemented to validate the design flow of CHAMPION. They are the neural network-based face detection algorithm [28] from the Carnegie Melon University (CMU), the Infrared Automatic Target Recognition (IR ATR) algorithm from the Army Night Vision Laboratory and a high pass filter for image processing applications.

#### 1.1 Motivation

The designing process of ACS and ASIC presents many problems to the application programmers. The task of developing applications for ACS and ASIC requires considerable knowledge in digital logic, which is very different from the kind of algorithmic expression that arises in application programming. In addition, for ACS design, a sound knowledge of the programmable logic devices and the control and interfacing circuits on the board is required in order to take advantage of the ACS. Therefore, it remains a significant obstacle to the widespread adoption of ACS and ASIC by application programmers, who are generally unfamiliar with digital circuit design. Without supportive design tools such as CHAMPION to assist the hardware development, ACS and ASIC will go unused in many application domains.

In addition to the lack of hardware knowledge, the long and tedious process of developing ACS and ASIC also keeps application programmer from utilizing them. For instance, the implementation of an application on ACS requires considerable effort in generating, synchronizing, partitioning, and synthesizing the digital circuit. Significant effort is also required to resolve the issue of the intricate interactions between the hardware (ACS) and the software (host machine). Currently, the entire process of mapping an application onto an ACS requires months for a hardware engineer to complete. With the automatic mapping, more application designers will be able to achieve higher quality implementations in less time.

The market for consumer electronics is characterized by rapidly growing technology of hardware and rather short market windows. A key concept for coping with such requirements is the retargeting of system components on different hardware technologies. In the CHAMPION project, the design flow streamlines the process of implementing applications for new hardware technologies for designers who are concerned about their competitive position in adopting new hardware technology quickly.

#### 1.2 Problem Statement

The problem of automatic mapping of graphical programming applications to ACS and ASIC involves translating a software application into a form that can be executed on both hardware technologies. Currently, there is a missing link between the graphical programming application and both technologies. The graphical programming applications are often developed by application programmers who lack the knowledge of hardware design while the hardware systems are often designed by engineers who are unfamiliar with the specific application domain.

A software environment which automatically maps graphical programming applications to ACS and ASIC will complete this missing link. This software environment allows application designers to perform hardware designs at a software level. To create a software design environment that provides an easier and faster way for application programmers to implement their applications on ACS and

#### ASIC, several issues have to be resolved:

- 1. How can the mapping be automated as much as possible?

- 2. How to shorten the mapping time while producing a high performance circuit?

- 3. What mechanisms should be used to handle the differences in data transfers and data sizes between the graphical programming applications and hardware circuits?

- 4. Which synchronization algorithms should be used to synchronize the circuit in the shortest possible time and to minimize the number of delay buffers used?

- 5. For ACS implementation, what partitioning method should be used to yield fast and optimized results?

- 6. For ASIC implementation, what compilation strategies should be used to shorten the time required to synthesize, optimize and generate the layout of the circuit?

- 7. What feedback estimates should be given to the user during the mapping process?

- 8. How can the design flow be as hardware independent as possible?

- 9. What is required to target a new technology?

#### 1.3 Goals and Expected Contributions

In general, the main objective of this dissertation is to create an easier and faster way for application programmers to develop their applications for ACS and ASIC. A software design environment has been developed to map graphical programming applications automatically onto ACS or ASIC. This software design environment allows application programmers who lack the knowledge of hardware design to implement their applications onto ACS and ASIC. It also allows the designers to achieve higher quality implementations in less time. As a result, with the help of this design environment, both ACS and ASIC can be utilized by a wider audience and application development will be accomplished in less time.

#### CHAPTER 2

#### **Background**

A considerable body of literature exists on ACS, ASIC and their design flows. This chapter provides a brief description of ACS and ASIC, and covers the relevant aspects of the traditional design flows of ACS and ASIC.

The focus of the dissertation is upon improving hardware designer productivity by automating the mapping of graphical programming applications (GPAs) onto ACS and ASIC. Many of the tools that will be used to automate the mapping process involve handling the differences between the GPA and hardware implementation. Included in this chapter are sections containing material on the GPA used in this dissertation and the major differences between the GPA and hardware.

This chapter also includes a section describing the commercial software and other research programs that perform the mapping automation similar to that in this dissertation. The major differences between the approach taken by CHAM-PION and that of commercial software and research programs are discussed.

#### 2.1 Microelectronic Technologies

Historically, digital hardware has been divided into two main groups, general purpose processor and application specific hardware. General-purpose processor is a fixed architecture device which implements a pre-defined set of instructions. General-purpose processors commonly fall in one of two categories: microprocessors and digital signal processing (DSP) processors. Examples of microprocessors are Intel's Pentium family, SUN's UltraSparc family and Motorola/IBM's PowerPC family. DSP processors, on the other hand, include Texas Instruments' TMS320C6xxx family, Motorola's DSP560xx family and Analog Devices' Tiger-SHARC family. These processors execute programs stored in some internal or external memories by fetching their instructions, examining them and then executing them one after another. An organization of a simple bus-oriented microprocessor is shown in Figure 2.1. New programs can easily be loaded into memory as needed. The computation of any algorithm is determined by the software program, not the hardware. Because their instruction sets include very general operations such as arithmetic and logical operators, general-purpose processors can be programmed to perform any conceivable function. However, general-purpose processors are very slow at performing computational intensive functions. Execution of these functions requires the functions to be translated into the general-purpose instructions that are executed by the processors.

For application-specific hardware, an engineer designs all of the circuits specifically for an application. These hardware, which are often referred to as

Figure 2.1: Organization of a simple bus-oriented microprocessor.

application-specific integrated circuits (ASICs), usually lead to better performance since they can be optimized for the specific application. However, an ASIC can only be designed to perform one particular application. If they are needed to perform a new function, then a new ASIC will have to be created. Another disadvantage of ASIC is its labor-intensive nature. It typically takes months for hardware engineers to design a new ASIC and have it fabricated. This labor-intensive nature of ASIC also translates it into a high cost and long time-to-market hardware. In spite of these drawbacks, application specific hardware is widely used whenever performance is of primary importance. By optimizing the hardware for a particular task, ASIC can often achieve computation speeds several orders of magnitude faster than general-purpose hardware.

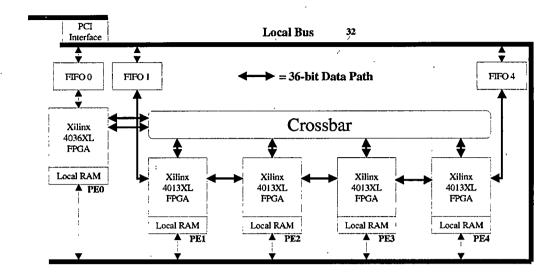

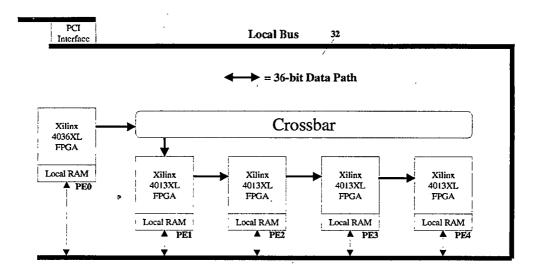

In recent years, a new class of computing hardware, called adaptive computing system (ACS), has been increasingly gaining research interest. ACS has some of the advantages of both general-purpose and application-specific hardware. A typical ACS is composed of multiple programmable logic devices, memory elements and circuits for control and interface with a host computer. The architecture of the ACS board used in this research project is shown in Figure 2.2. The programmable logic devices, which are also known as processing elements (PEs), found in the ACS are commercially available Field Programmable Gate Arrays (FPGAs) or Complex Programmable Logic Devices (CPLDs). These PEs provide a relatively large number of programmable functional units and programmable interconnections. The functionality of the hardware is determined by how the functional units and interconnections are configured. By changing the configuration, the hardware can be made to perform a completely different function. Since the configuration is specific to the application at hand, it is in effect a custom computer for the particular design. Different types of application can be implemented at speeds close to those obtained using application specific hardware. In addition, the configuration can be changed relatively quickly from one function to another, giving some of the same flexibility as general-purpose hardware.

#### 2.2 Design flows of ACS and ASIC

In this section, the entire synthesis-based ACS and ASIC design flows and methodologies are discussed. The main function of this section is to bring to the

Figure 2.2: Architecture of the Wildforce board.

forefront different stages involved in ACS and ASIC design. It will provide the necessary background for understanding the design flow of CHAMPION.

#### 2.2.1 Design Flow of ACS

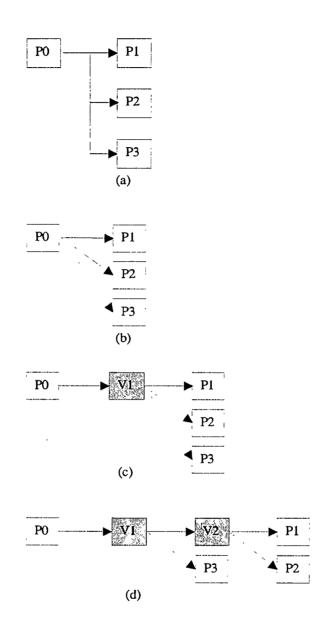

The design flow for an ACS is depicted in Figure 2.3. To map an application to ACS, the designer must first define the hardware structure for the application. In the past, this was done using schematic capture, where the designer manually draws the schematics of the design using the components of a cell library. This process was time consuming and impractical for design reuse. To overcome this problem, schematic capture is increasingly being replaced with hardware description language (HDL). The two main HDLs in use today are VHDL and Verilog. For both schematic capture and HDL coding, a sound knowledge of the digital

Figure 2.3: ACS design flow.

logic design is required.

After the design has been captured in schematic or HDL, it is essential to verify that the schematic or HDL code matches the required functionality, prior to synthesis. This step is commonly known as pre-synthesis behavioral simulation. If errors are found during the simulation, appropriate changes need to be made and the verification of the new design is repeated through simulation.

When the simulation results indicate that the design functions correctly, the design is then partitioned spatially. The spatial partitioning of the design is required to allow the design to be mapped onto multiple FPGAs available on the ACS. The partitioning process considers many factors such as, the size of the PEs, number of interconnections between partitions and number of memory elements in a partition. If the design does not fit in all the PEs available in the ACS board, then it must also be partitioned temporally, by allocating functional units to different configurations of the same PE.

Once the design is partitioned, pin assignment has to be performed on each partition to assign the I/O pins on each PEs to the schematic or HDL description of the partition. This is a long and tedious process since the designer has to manually assign all the input and output signals of each partition to the I/O pins on the corresponding PE. Each partition is then individually synthesized into a technology-dependent netlist. This netlist is specified in terms of the basic logic cell of the PE. For example, if the Xilinx XC4000 series FPGAs are used as the PEs on the ACS board, the netlist is specified in terms of Configurable Logic Block (CLB).

After the technology-dependent netlists for each partition has been generated, each logic cell specified in the netlists can be arranged on a layout surface of the PE. For ACS design, the main goal of the placement process is to arrange all the logic cells in such a way that the routing is feasible and all the critical nets are minimized. In ACS design, area minimization is normally not as important as it is

in the ASIC design. After placing the logic cells in that particular arrangement, the interconnections between logic cells are routed according to the specified netlist.

The placement and routing processes produce physical implementations for each partition of the design. These physical implementations are then translated into binary streams (commonly known as configuration file), which are used to program the PEs. A software program, which is normally written in C or C++, has to be generated to give instructions to the host computer on when and how to download the configuration file and data for the application to the ACS.

While commercial tools exist to help with parts of this design flow of ACS, it still requires a great deal of skill, knowledge of hardware design, time, and effort to design. These steep requirements have severely limited the potential users of this type of ACS and prevented its widespread acceptance.

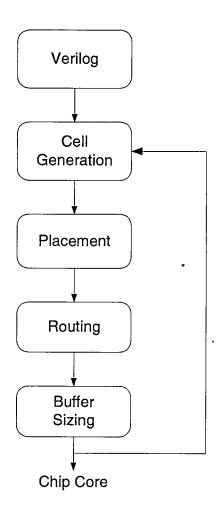

#### 2.2.2 Design Flow of ASIC

Figure 2.4 shows the sequence of steps to design an ASIC. The design process starts with the development of a hardware definition for the application. This is usually done with HDL. The functionality of the HDL is then verified against the initial specification. This can be done by assigning specific values to the input signals, performing simulation runs and viewing the output waveforms in a graphical simulation tool. An alternative is to write a testbench, which is an HDL block whose outputs provide the stimuli for the design to be simulated. In

Figure 2.4: ASIC design flow.

ASIC design, testbench simulation is more commonly used compared to waveform simulation. Simulation using testbench simplifies the post-synthesis and post-layout simulation steps. The same testbench can be used for post-synthesis and post-layout simulation and the results can be compared. As a result, the testbench is used as the golden model for verifying the design at every level of abstraction

After the initial simulation, the HDL description of the design is then synthe-

sized into a netlist consisting of logic gates and their interconnections. The logic gates used in the netlist are obtained form a technology library provided by the ASIC manufacturer. The library defines the delay models, models for variations of temperature, voltage and manufacturing processes as well as the functionality of each gate. Notice that in the ACS design flow, the netlist obtained through the synthesis process is specified in terms of the basic logic block of the PE. But for ASIC design, the netlist is specified in terms of logic gates provided by the manufacturer.

This gate-level netlist is then simulated to verify the functionality of the design. This post-synthesis simulation is performed using the same specifications used during the pre-synthesis simulation. After verifying the design, the logic gates are placed on the layout of the chip. The main goal of placement in ASIC design is to find a minimum area arrangement for the gates that allows completion of interconnections between the gates, while meeting the performance constraints. This is typically done in two phases. In the first phase, an initial placement is generated. In the second phase, iterative improvements are made to the initial placement until the layout has a minimum area or best performance and conforms to design specifications. After placing the logic gates, the interconnections between logic gates are routed according to the specified netlist.

Another round of simulation can be performed after the placement and routing processes. The simulation at this level is commonly known as post-layout simulation. Post-layout simulation is performed mainly to verify that the design

meets the specified timing constraints. Once the design is verified, pin assignment is performed to connect the input and output signals of the design to the I/O pins of a chosen frame. After pin assignment, the physical layout of the design is ready to be sent off for fabrication.

#### 2.2.3 Comparison between ACS and ASIC Design Flows

Comparing the ACS and ASIC design flows shown in Figure 2.3 and Figure 2.4, it can seen that the main difference between the two design processes is that ACS design requires the design to be partitioned before synthesis. To map a design onto ACS, the design has to be partitioned into smaller sub-designs, which can be fitted into the PEs. The partitioning process is performed based on constraints such as the size of the PE, the number of I/O pins on the PE, and the number of memory elements allowed in each partition. For ASIC design, no partitioning is required. The complete design is mapped onto a single chip.

The partitioning process in the ACS flow has caused simulation to be omitted at lower levels of abstraction. In ASIC design, simulations are performed at three different levels: pre-synthesis, post-synthesis and post-layout. The same set of specifications can used to simulate the design at these three levels since the design does not have to be partitioned into sub-designs. Once the design is partitioned, as in the case of ACS design, the initial specifications cannot be used to verify the design since each partition implements different functionality. In fact, it is almost impossible to simulate each partition since the functionality of each partition is

not known due to the fact that each partition is performed based on constraints, not according to the functionality of the partition.

The ACS design flows also requires the designer to generate a host program responsible for communications between the host system and the ACS board. To generate this host program, knowledge on the control and interface circuitry of the ACS board is required. The designer needs to understand how the control and interface circuitry on the ACS board works as well as the set of commands provided by the ACS manufacturer for using the circuitry.

#### 2.3 Khoros Software Development Environment

Khoros is a software integration and development environment developed by Khoral Research Incorporated (KRI). It includes a suite of software development tools and a set of toolboxes containing over 300 functions. These functions include arithmetic operators for scalars, vectors, and matrices, image and signal processing functions, data visualization and display operations, and many functions for manipulating and examining sets of data [31]. The functions can be used as stand alone programs from the command line, or as functions called by a C/C++ program.

All the functions in Khoros operate on data defined in three robust data models. The geometry data model allows for representation and storage of complex geometric structures. It also allows easy access and manipulation of the geometric structures. The color data model is designed for the storage of color maps in a format that allows for easy transformation of the color space. The polymorphic data model is the most flexible data model. It is capable of storing multi-dimensional data including audio signals, images, video, vector spaces, or virtually any other type of data that can be represented with up to three spatial dimensions and optionally one time dimension [25, 26].

# 2.3.1 Cantata Graphical Programming Environment

While Khoros functions can be used as standalone commands, they are most widely used with the Khoros graphical programming environment called Cantata. Cantata allows users to develop their applications easily using the collection of functions in Khoros. Each function in the Khoros toolbox is represented on the screen by a small icon called a glyph. Graphical programs can be created by interconnecting these glyphs with data paths (as shown in Figure 2.5). Each glyph has an input terminal corresponding to each of the possible inputs to the function and output terminals for each of the outputs. In addition, each glyph has a pane, which is a set of interface objects that allows the user to set options for the operation of the glyph. Each of these objects corresponds directly to a parameter that can be passed on to each function on the command line.

Designed to act as an integrated software development environment, Khoros allows users to add new operators or functions to its collection of toolboxes. These new functions can be generated using C or C++ and installed in Cantata with the help of Khoros tools. Complex software wrappers that provide sophisticated

Figure 2.5: A sample Cantata workspace.

data handling are added to the glyph during the installation process.

Like most of the graphical programming environments, Cantata allows users to develop their application programs by simply interconnecting functional blocks. Once the applications are created, they can be executed in Cantata without having to compile their code. In addition, in Cantata, users do not have to worry about the details of how data is passed or where it is stored. Since Cantata uses the polymorphic data model, users do not have to be concerned about converting data from one data type to another. All these features allow users who may not be familiar with traditional programming methods to quickly implement and test their algorithms and ideas. Since Cantata can work on such wide ranges of data, users can test their applications using real data. The visual nature of Cantata also makes it easy to modify an existing application by simply adding or removing glyphs and changing connections.

Cantata can be used by users who may be skilled in their own area of expertise, but who may not necessarily be able to program well enough to test their ideas. For instance, a physician who would like to apply an image processing algorithm onto a computed tomography (CT) scan image, but might otherwise be limited by a lack of programming ability, can use Cantata to apply the algorithm using real data. Cantata has become widely used partly because of its ability to isolate users from the underlying technology while still allowing them to exploit the power of the computing platforms they are using. By providing a high-level design environment for problem solving, Cantata increases the productivity of

both researchers and application developers, regardless of their programming experience.

### 2.4 Differences between Cantata and Hardware

At first glance, an application in Khoros Cantata may seem to be similar to a schematic of a hardware design. Each glyph in Cantata seems to be equivalent to a hardware cell and the connections between glyphs seem to be equivalent to the wires connecting the hardware cells. Unfortunately, upon closer examination things are not quite that simple. The Cantata programming environment handles many details that are not apparent from the graphical workspace. Operations such as converting between different data types, synchronizing data, and transferring blocks of data between glyphs are handled by Cantata at the background during the execution of the program. In a hardware design, specific hardware modules have to be created to handle these operations. Three different types of operations that were handled significantly differently in Cantata and in hardware implementation of an application were found. The next three sections describe these operations and the way they are handled.

## 2.4.1 Data Transfer

In a Cantata implementation, data is transferred between glyphs through the use of temporarily files. The data output by one glyph is written out to a temporary file. Cantata will pass the filename of this temporarily file to any succeeding glyphs that will use that data as their inputs. In other words, the input filename of any particular glyph is set automatically to be the same as the output of the preceding glyph. The succeeding glyphs can then read in the data for further processing. The user does not have to worry about the filenames for the inputs and outputs as they are chosen by Cantata. The actual transfer method involves storage on a hard drive, where the entire file is transferred all at once time. The data is stored in one of the three Khoros data structures.

In hardware implementation, data is transferred between hardware glyphs one value at a time rather than an entire block of data. Instead of transferring an entire image, as in Cantata, only a certain number of bits are transferred at each clock cycle in hardware, depending on the bus width. In addition, the hardware requires registers to hold the data values as they are being transferred between the hardware glyphs.

In order to map a Cantata application to hardware, this difference in data transfer must be accounted for. This data transfer difference will not affect the operation of a glyph if the Cantata glyph operates on the data one value at a time. For instance, a Cantata glyph that adds a constant to each value in a stream only needs to work with one value at a time. The corresponding hardware glyph can work with one data value at a time as well and the mapping of it will be simple. If a Cantata glyph performs some accumulation of operations in a stream before it produces a valid output, it will not map easily to hardware. An example of such glyph is an accumulator that finds the sum of all the pixels in an image.

To map this type of glyph to hardware, the differences in data transfer methods must be taken into account.

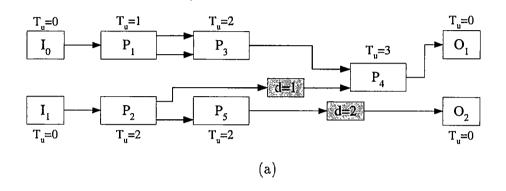

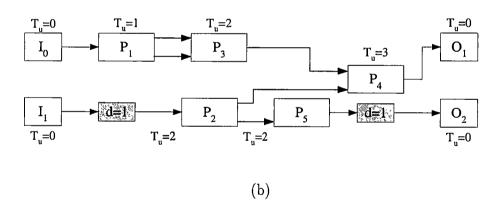

#### 2.4.2 Data Synchronization

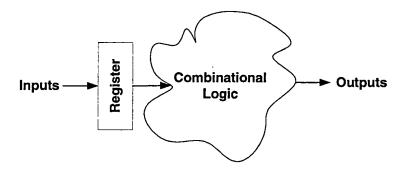

In a Cantata, executions of the programs are data driven. That is, each Cantata glyph will begin execution only when all its input data is available. With this, there are never any data synchronization errors in Cantata. However, hardware systems are clock driven. At each clock cycle, each hardware glyph will process whatever data is presented at its inputs.

Due to the difference in the processing time of each hardware glyph, data traveling over different concurrent paths may arrive at the inputs of a multi-input glyph at different times. To insure that each glyph generates the correct time-sequenced output, it is necessary that each glyph receive all its input data precisely at the same time.

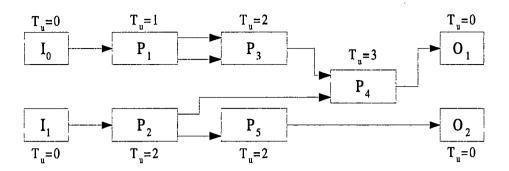

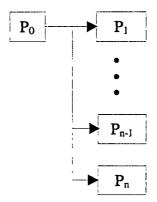

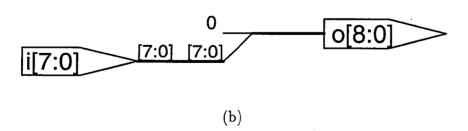

In Figure 2.6 (a), a simple network for adding three images A, B and C, is shown. The two hardware glyphs, designated X and Y, are triggered by the same clock signal. Assuming that images A, B, and C all become available at the same time. In the first clock cycle, glyph X will add its two inputs, which are the first pixel from image A and the first pixel from image B. At the same time, glyph Y will also add its two inputs, which are the first pixel from image C and an invalid output from glyph X since glyph X is in the process of adding the its inputs. This causes the inputs to glyph Y to be out of sync, resulting in hardware results

Figure 2.6: Synchronization using delay buffers. (a) Unsynchronized glyphs and (b) glyphs synchronized by delay insertion.

that are different from those obtained in Cantata.

To fix this problem, a delay buffer, D, needs to be inserted at the input of glyph Y, as shown in Figure 2.6 (b). Now image C is delayed by one clock cycle before it reaches glyph Y, synchronizing it with the output of glyph X. The data synchronization for all glyphs with more than one input must be checked and fixed throughout the entire application. It is important to note that the delay glyphs inserted for data synchronization do not appear in the original Cantata workspace. Instead, they are identified and inserted during the mapping process.

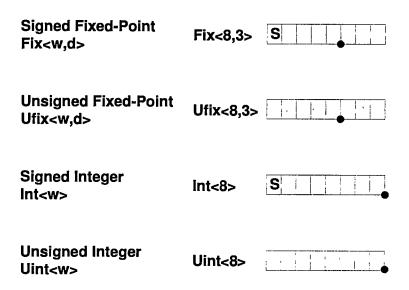

## 2.4.3 Data Sizing

In Cantata, data size conversion is handled automatically by the glyphs. The polymorphic data model adopted by Cantata frees users from having worry about converting data from one size to another.

In hardware, the inputs of each glyph have fixed data width. Therefore, two unsigned five-bit numbers can be added together, but a five-bit number cannot be added to a six-bit number. If an input and an output of different sizes are connected together, one of them must be converted to match the other. Since there are so many different possible combinations of input and output sizes, it is impossible for the glyph to do this automatically. Part of the mapping process must therefore include a way of finding and fixing all the mismatches. To fix the mismatched data path, a hardware glyph can be inserted to perform the correct conversion. These conversion glyphs do not appear in the Cantata workspace.

Just like the delay glyphs inserted for data synchronization, they are identified and inserted during the mapping process.

#### 2.5 Related Work

Several research projects and commercial software that perform similar mapping automation are being developed. In this section these research projects and commercial software are presented. The major differences between the approach taken by CHAMPION and that of the commercial software and research programs are discussed.

## 2.5.1 CAMERON Project: Colorado State University

### **Project Overview**

At Colorado State University (CSU), a research project called CAMERON [7] is being developed. The CAMERON project develops compilers for mapping image-processing applications developed using Khoros onto ACS boards. New image processing operators in CAMERON are written in a high-level programming language called single-assignment C (SA-C). SA-C is a programming language based on C that has been developed at CSU and integrated in the Khoros graphical programming environment. It is created as a language well suited for image processing and amenable to compiler analysis and optimization.

SA-C is a subset of C with extensions for image processing. These extensions include parallel loops, true n-dimensional arrays of variable precision scalars,

and access mechanisms such as windowing. These extensions make it easy to implement image-processing algorithms [20].

SA-C is designed to exploit both coarse-grain and fine-grain parallelism as appropriate for ACS. SA-C eliminates recursion and pointers manipulation, and allows each variable to be assigned only once. The existence of recursion and pointers in a program complicates the analysis of data dependencies at compiletime. By eliminating recursion and pointers, SA-C makes data dependencies and access patterns clearer and therefore, allows the compiler to easily identify loop-level (coarse-grain) and instruction-level (fine-grain) parallelism. The reason for the single assignment restriction is that it establishes a one-to-one correspondence between variables in the program and wires in the resulting circuit. By allowing each variable to be assigned only once, the value of the variables will not change. Therefore, they do not need to be associated with memory. Instead, every operator is a sub-circuit, and the variables it operates on are the input wires. This will make the generation of VHDL circuits from SA-C easier. It will also make it easier for programmers to understand this mapping and to write SA-C programs that translate into efficient circuits [7].

The main goal of the CAMERON project is to allow low-level image processing algorithms to be written using SA-C inside the Khoros software development environment. These programs can then be manipulated as glyphs inside Cantata. The application generated using these SA-C glyphs can then be mapped onto on parallel architectures for execution in ACS.

The technology underlying the mapping approach taken by CAMERON project is dataflow analysis. The image processing glyphs written in SA-C can be directly translated into dataflow graphs (DFG). Once the program is transformed into a dataflow graph, dataflow optimizations such as loop merging, loop unrolling, and data blocking can be applied. Since SA-C is single assignment, a direct correspondence exists between dataflow graph components and FPGA hardware components. Therefore, optimized dataflow graphs can easily be mapped onto FPGA configurations.

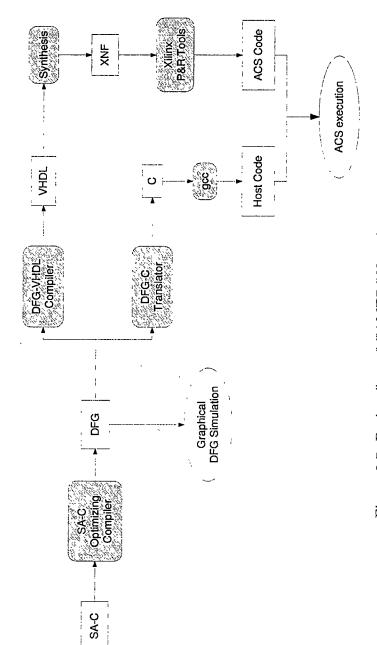

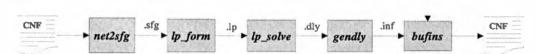

The design flow of the mapping process of CAMERON project is shown in Figure 2.7. Image processing applications can be implemented in Cantata by interconnecting the SA-C glyphs. Once the application is developed using Cantata, all the glyphs are merged into a single SA-C program. The SA-C compiler is then used to optimize the SA-C program. The compiler first converts the entire SA-C program to an internal data flow form called Data Dependence and Control Flow (DDCF) graphs. Optimizations are then performed on the DDCF graphs. The optimizations performed includes traditional optimizations such as Common Subexpression Elimination, Constant Folding and Dead Code Elimination, and optimizations specifically designed for the FPGA such as Loop Unrolling, Function Inlining and Loop Nextification [6].

After the optimization process, the compiler translates the DDFG graph to DFG graph. The DFG graph is then partitioned into DFG for the FPGA and DFG for the host. The parallelizable loops in the DFG are assigned to the FPGA.

Figure 2.7: Design flow of CAMERON project.

The sequential code not inside a loop is assigned to the host code. Using these partition criteria, the main computational circuit that will be implemented in the FPGA is entirely combinational. As a result, pipelining cannot be used in the main computational circuit [6].

After partitioning, the DFG for the hardware is translated to VHDL. The process of translating the DFG to VHDL is divided into two main parts. The DFG is translated by converting each node into VHDL. For DFG nodes implementing simple operations, such as arithmetic or logical operations, there is a one-to-one correspondence between the nodes and VHDL statements. Therefore these nodes are directly translated into VHDL statements. For more complicated operations, such as array sum, the translator generates a connection to a predefined VHDL component. A library of such components allows the SA-C compiler to directly access hardware implementations for many complex operations.

The translated VHDL code is then processed by a commercial VHDL compiler and place and route tools. These tools produce the final FPGA configuration files that can be downloaded onto the ACS and executed. The DFG for the host is translated into C code and compiled using a C compiler into the host program. The host program is used to control the downloading of the FPGA configuration, the process of sending data to the ACS and the results reading process.

## Comparison Between CHAMPION and CAMERON

Our research shares a "system-level" perspective with the CAMERON project. Both projects use Cantata as the entry point for application development and ACS as the hardware for application implementation. However, our research extends to support ASIC as an alternative hardware implementation since it provides some advantages over ACS.

CAMERON is more strongly oriented towards compilation-based approaches for implementing applications than our work. Most efforts are in the development of the SA-C language to support the programming for image processing and reconfigurable hardware, and the development of a SA-C compiler to optimize the code. The SA-C language is a subset of C with restrictions such as single assignment and the elimination of recursion and pointers manipulation. It is a language well suited for image processing application.

In our research work, we allow the user to use both fixed point C and C++ during glyph development. The fixed-point C and C++ are not restricted to image processing domain. They are well suited for more application domains. In addition, C++ also provides an object-oriented feature for programming. The only restriction that we imposed on C and C++ is the use of fixed-point number as opposed to floating point number. The only disadvantage of using fixed-point number is that a fixed-point number requires more data bits than a floating number to achieve the same degree of accuracy.

In the CAMERON project, the compiler exploits both coarse-grain and fine-

grain parallelism. The compiler identifies loop-level and instruction-level parallelism to increase the throughput of the application implemented in the ACS. However, the main computational circuit implemented in the FPGA is entirely combinational. This restricts the pipelining in the main computational circuit. Our research work improves the hardware throughput by mapping the Cantata application to sequential logic circuit instead of combinational circuit. Therefore, pipelining of the input data is possible in the entire circuit.

Perhaps the main difference between our research work and CAMERON is the time required to map a Cantata application to ACS. In our research, we perform synthesis and place/route on our library cells in advance. Thus, we have accurate information on the size and delay of each cell and only have to re-synthesize small net-lists that represent the collection of cells that fit in each FPGA. The CAMERON approach merges the VHDL code into a single, large file that must be fully re-synthesized and then partitioned at a finer grain than our approach. Hence, CHAMPION is presented with a smaller netlist and can be expected to execute in less time. Since the circuits produced by CHAMPION allow pipelining, the performance of the circuits is expected to be compatible to that of CAMERON, even though no optimization is performed on the circuit.

## 2.5.2 MATCH Project: Northwestern University

## **Project Overview**

The objective of the MATCH (MATlab Compiler for Heterogeneous computing systems) [5] project at Northwestern University is to make it easier for users to develop efficient codes for heterogeneous computing systems. They are implementing and evaluating an experimental prototype of a software system that will take MATLAB descriptions of various embedded systems applications, and automatically map them onto a heterogeneous computing environment consisting FPGA arrays, embedded processors and DSP processors.

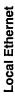

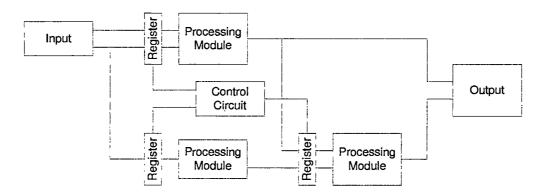

The prototype heterogeneous hardware system (shown in Figure 2.8) designed to work in the MATCH project consists of a controller (microprocessor running Solaris Operating system) and three types of computing resources: an ACS board, embedded processors, and DSP processors. A VME bus is used as the communication backbone for these computing resources.

This heterogeneous system combines the advantages of microprocessor based embedded systems, DSP processors and FPGA resources. The microprocessors and DSP processors are used to support the computations, which are not ideally suited for the FPGAs and the bulk of the functionality required to implement an algorithm. Example of functions implemented by these processors are control intensive algorithms, complex floating-point applications and computing tasks with large amount of code that is rarely executed. The reconfigurable logic is used to accelerate only the most critical computation kernels of the program.

Figure 2.8: The heterogeneous hardware system used in the MATCH project [5].

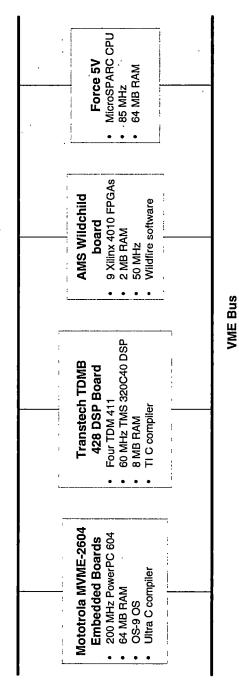

The key issue that needs to be addressed in the MATCH project is how to map a MATLAB program on such a heterogeneous architecture without expecting the application programmer to get into the low level details of the architecture. A compiler is being developed to generate efficient code automatically for the heterogeneous target. An overview of the compiler is shown in Figure 2.9. The compiler parses the input MATLAB program based on a formal grammar and builds an abstract syntax tree (AST) [5]. The AST is then partitioned among the various components based on the set of predefined library functions. The nodes corresponding to the predefined library functions are assigned to the respective targets.

The ASTs for the FPGAs are then converted to register transfer level VHDL. Each user function is translated into a process in VHDL. Each scalar variable in MATLAB is translated into a variable in VHDL. Each array variable in MATLAB is stored in a RAM adjacent to the FPGA. The read or write functions of the memory corresponding the array variable are then generated. Control statements such as IF-THEN-ELSE constructs in MATLAB are translated into corresponding IF-THEN-ELSE constructs in VHDL. Assignment statements in MATLAB are translated into variable assignment statements in VHDL. Loop control statements are translated into a finite state machine. Once the translation is completed, logic synthesis and place and route tools will then be used to generate the FPGA binaries. The ASTs corresponding to the ACS host, embedded microprocessors and DSP processors are translated into equivalent C code.

Figure 2.9: Match compiler [5].

Finally, these generated codes are compiled using the respective target compilers to generate the object codes for the processors. A main thread of control is automatically generated for the controller. The controller is used to make remote procedure calls to the microprocessors, DSP processors, and ACS.

#### Comparison Between CHAMPION and MATCH

The MATCH project uses MATLAB for application development. Similar to Cantata, MATLAB is a function-oriented language where most of the programs can be written using predefined functions. However, MATLAB programs are normally implemented as sequential codes since the language is designed to be executed on a single conventional processor. To take advantage of the hardware implementation, the parallelism within the MATLAB code must be exploited.

For graphical programming such as Cantata, application can easily be implemented in a parallel manner since the application is created in a form of data flow graph. The user can increase the "amount" of parallelism by interconnecting the glyphs in parallel. This will make the application highly parallel at the function-block level. The only remaining sequential part is the instruction-level code within the glyph. This instruction-level parallelism can be exploited similar to what is being done in the CAMERON project. However, this will require a more restricted language, such as SA-C, to enable the compiler to analyze the data dependency and therefore, extract the parallelism in the code.

The MATCH project uses a more complicated hardware architecture for the

mapping of application. A heterogeneous system consisting of FPGAs, microprocessors and DSP processors is used. The MATCH compiler is required to partition the MATLAB code to based on the type of computations. For example, control intensive algorithms, complex floating-point applications are not ideally suited for the FPGAs and should be implemented in the microprocessors or DSP processors. On the other hand, critical kernels which require fast computations should be implemented in FPGAs.

Similar to the CAMERON project, the main difference between our research work and MATCH will be the time required to map an application to hardware. In our research, we perform synthesis, placement and routing on our library cells in advance. Thus, we only need to re-synthesize small netlists that represent the interconnections of high level cells. The MATCH approach, however, translates the MATLAB code to VHDL code. The VHDL code must then be fully resynthesized and then partitioned at a finer grain than our approach. Hence, CHAMPION is presented with a smaller netlist and can be expected to execute in less time.

#### 2.5.3 Commercial Software

There have been several major commercial efforts to automatically map high-level applications to hardware. The COSSAP tool from Synopsys allows application to be developed using a block diagram graphical language. The developed application is then translated into VHDL or Verilog and synthesized into hardware.

The Signal Processing Workbench (SPW) from Cadence also takes an application developed using a block diagram language and translates it to VHDL. The Renoir tool from Mentor Graphics Corporation allows an application to be developed in different graphical ways. The users can enter the design as either block diagrams, flow charts or state diagrams. The Renoir tool will then generates the corresponding behavioral VHDL or Verilog automatically. The Monet tool can then be used to convert the behavioral VHDL into register transfer level VHDL. The register transfer level VHDL can be synthesized using the Leonardo logic synthesis tool.

The CHAMPION software differs from all of the commercial tools above in that we perform synthesis, placement and routing on our library cells in advance. Thus, we only have to re-synthesize small netlists that represent the interconnections of high level cells and can be expected to execute in less time.

## CHAPTER 3

# Methodology

In order to automatically map a Cantata application onto ACS and ASIC, all the steps shown in the ACS and ASIC design flows (Figure 2.3 and 2.4 respectively) have to be automated. In addition, the different types of operations such as data transfer, synchronization and sizing that are handled differently in Cantata and in hardware have to be resolved. This chapter presents the algorithms, approaches, and mathematical techniques used in CHAMPION to automate the design flows and to handle the hardware and software differences.

# 3.1 Overview of the Design Flow of CHAMPION

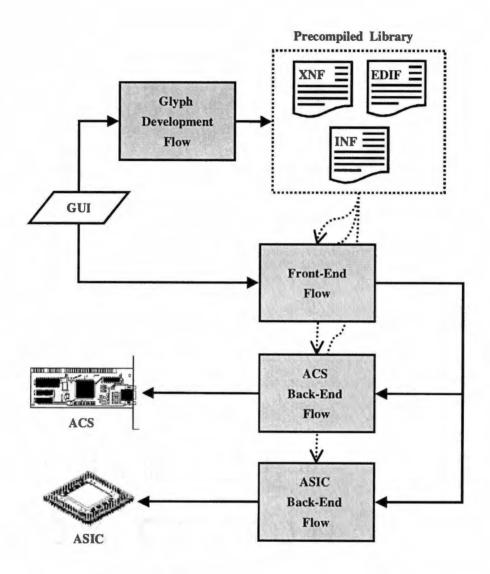

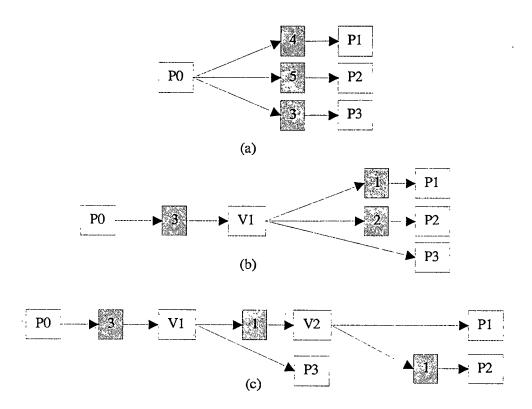

The design flow of CHAMPION is illustrated in Figure 3.1. The entire design flow can be divided into four sub-flows (as shown in Figure 3.2):

- Glyph development flow

- Front-end flow

- ACS back-end flow

- ASIC back-end flow

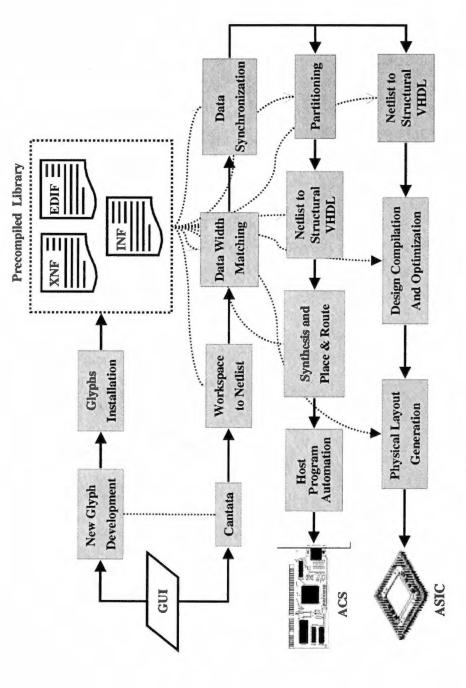

Figure 3.1: Design flow of CHAMPION.

Figure 3.2: Four main flows in CHAMPION.

In CHAMPION, Cantata is used as a function-oriented programming environment where all the application programs are developed using predefined functions or modules called glyphs. Currently, a set of library glyphs has been developed in the CHAMPION project. New library glyphs can be developed and added to the existing precompiled library if needed. A set of tools has been developed to automate the process of developing, verifying and installing the new glyphs in the CHAMPION library. This set of tools constitutes the glyph development flow.

Once the designer has all the required glyphs, the application can be generated by interconnecting these glyphs. The front-end flow is then used to transform the Cantata program into more of a hardware-like netlist. The Cantata program is first translated into a more graph-oriented database, preserving the original glyphs and their interconnections. Each interconnection is then checked to verify that the bit-widths of the connecting ports are the same. After matching the width of all the interconnections, data synchronization is performed. In CHAMPION, data synchronization is achieved by introducing delay buffers into the system. The synchronization software determines the lengths and locations of the delay buffers necessary to balance the various data paths. An optimization algorithm is employed to calculate a set of buffer lengths and insertion points that maximizes the amount of buffer sharing which therefore, minimizes the total number of delay buffers.

If the design is being mapped to ACS, the ACS back-end flow will be used. The ACS back-end flow first partitions the synchronized netlist at the glyph-level. After partitioning, the internal data structure or format is translated into a structural VHDL representation. The required I/O ports for each of the sub-netlists are then added to the VHDL files. Next, the VHDL files are synthesized and merged with the pre-compiled VHDL components corresponding to the Cantata glyphs. Each sub-netlist is then placed and routed. A host program is generated to download the resulting configuration files to the corresponding programmable logic component on the ACS board.

If the design is being mapped to ASIC, the ASIC back-end flow will be used. No partitioning is required for the ASIC implementation. The synchronized netlist is translated into a VHDL representation. Next, the VHDL representation of the circuit is synthesized to a target technology selected by the user. A layout tool is then used to automatically generate the final layout of the ASIC based on the synthesized netlist.

#### 3.2 Glyph Development Flow

Application programs can be constructed by interconnecting the glyphs contained in the CHAMPION library using Cantata. If certain glyphs needed for the application cannot be found in the CHAMPION library, the user can go through the glyph development flow to generate, verify and install these glyphs to the library.

## 3.2.1 Glyph Development and Verification

To incorporate a new glyph into the CHAMPION library, the designer must first develop the fixed-point C/C++ program for the glyph. The reason for using fixed-point arithmetic is to allow the C/C++ program to mimic hardware operations. For complex functions, the C/C++ program can be formed as a macro of lower-level functions.

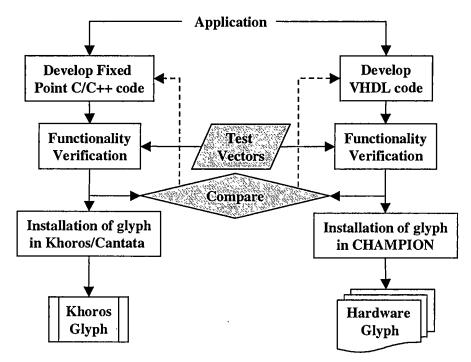

For each of the C/C++ program developed, a corresponding VHDL code must be developed. The functionality of the VHDL code must be identical to that of the C/C++ program. A set of test vectors is used to simulate both the C/C++ and VHDL code. The simulation results are compared to verify that bitwise identical behavior is achieved. The steps for developing the new glyph are shown in Figure 3.3.

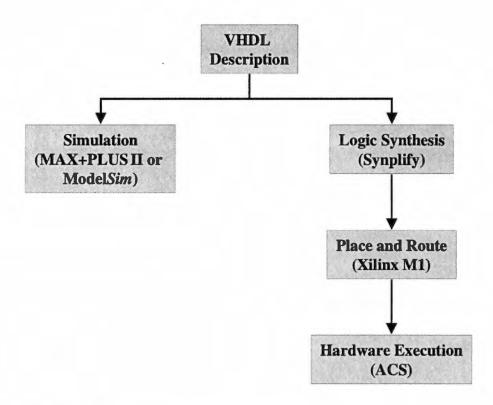

For the VHDL description, the functionality can be verified by:

- simulating the VHDL code using the commercial software such as Model

Technology's ModelSim, or

- executing the synthesized VHDL code in the ACS.

Both the VHDL verification methods are shown in Figure 3.4.

To accelerate the glyph development process, the commercial software, A|RT Library and Builder [11] from the Frontier Design was integrated to the glyph development flow. The A|RT Library and Builder provide the ability to generate the VHDL description of the hardware directly from a C-code specification. The

Khoros Glyph + Hardware Glyph = CHAMPION Glyph

Figure 3.3: Steps for developing a new glyph.