# BACHELOR'S DEGREE THESIS

# Accelerating Zero Knowledge Proofs

Author Laia Pujol Ventosa

Supervisor (MIT)

Daniel Sánchez

Tutor (UPC)

Antonio González

In partial fulfillment of the requirements for the Bachelor's degree in Mathematics Bachelor's degree in Informatics Engineering

October 2023

### Abstract

Zero-knowledge proofs represent a highly promising cryptographic tool that enables the validation of a statement's correctness without revealing any supplementary information. These proofs find utility in applications demanding both computational integrity and privacy, such as validating outsourced computation results, where confidential input values may be involved. However, a significant challenge hinders their practical adoption: the potentially time-consuming process of generating proofs. Consequently, this project investigates the feasibility of accelerating zero-knowledge proofs using hardware, aiming to overcome this critical hurdle.

$\textbf{Keywords:} \ \ \text{verifiable computation, zero-knowledge proofs, zk-SNARKs, learning}$

with errors, lattice-based cryptography, accelerator

MSC2020: 94A60

### Resum

Les proves de coneixement zero són una eina criptogràfica altament prometedora que permet demostrar que un predicat és correcte sense revelar informació addicional sobre aquest. Aquestes tipus de proves són útils en aplicacions que requereixen tant integritat computacional com privadesa, com ara verificar la correcció dels resultats d'una computació delegada a una altra entitat, on hi poden haver involucrats valors d'entrada confidencials. Tanmateix, té un impediment que obstaculitza la seva adopció pràctica: el procés potencialment lent de generació de les proves. Així doncs, aquest projecte explora la viabilitat d'accelerar les proves de coneixement zero mitjançant hardware, amb l'objectiu de superar aquest obstacle crític.

Paraules clau: computació verificable, proves the coneixement zero, zk-SNARKs, aprenentatge amb errors, criptografia basada en reticles, accelerador

MSC2020: 94A60

### Resumen

Las pruebas de conocimiento cero representan una herramienta criptográfica altamente prometedora que permite demostrar la corrección de un predicado sin revelar información adicional. Estas pruebas son útiles en aplicaciones que requieren tanto integridad computacional como privacidad, como por ejemplo la validación de los resultados de una computación delegada a otra entidad, donde pueden estar involucrados valores de entrada confidenciales. Sin embargo, existe un desafío significativo que obstaculiza su adopción práctica: el proceso potencialmente lento de generación de pruebas. Como resultado, este proyecto explora la viabilidad de acelerar las pruebas de conocimiento cero utilizando hardware, con el objetivo de superar este obstáculo crítico.

Palabras clave: computación verificable, pruebas de conocimiento cero, zk-SNARKs, aprendizaje con errores, criptografía basada en retículos, acelerador

MSC2020: 94A60

First and foremost, I would like to thank Nikola Samardzic and Simon Langowski for their help and patience answering all my doubts and guiding me through the intricacies of this project. Your advice and support has been instrumental and deeply appreciated.

I would also like to express my sincere thanks to Professor Daniel Sanchez for hosting me over these recent months and welcoming me into his group. Being part of it and participating in its meetings has proved to be a truly enriching experience.

I want to thank Professor Antonio González for helping me get this opportunity and offering invaluable feedback on this project.

I am also grateful to the program Centre de Formació Interdisciplinària Superior (CFIS) for all their support during these last years. Moreover, this experience has been possible thanks to the funding provided by Fundació Privada Cellex and Fundació Ciutat de Valls. Thank you all for your contributions.

Lastly, thanks to my family and friends for being there throughout all these years. This journey would not have been possible without you.

# Contents

| 1. | Intr | roduction                                                   |        | 1  |  |  |  |  |  |  |

|----|------|-------------------------------------------------------------|--------|----|--|--|--|--|--|--|

| 2. | Bac  | ckground and motivation                                     |        | 3  |  |  |  |  |  |  |

|    | 2.1. | Verifiable Computation (VC)                                 |        | 3  |  |  |  |  |  |  |

|    |      | 2.1.1. Definition                                           |        | 3  |  |  |  |  |  |  |

|    |      | 2.1.2. Public and designated verifier                       |        | 4  |  |  |  |  |  |  |

|    | 2.2. | Zero Knowledge Proofs                                       |        | 5  |  |  |  |  |  |  |

|    |      | 2.2.1. Definition                                           |        | 5  |  |  |  |  |  |  |

|    |      | 2.2.2. Examples                                             |        | 6  |  |  |  |  |  |  |

|    |      | 2.2.3. Interactivity of a proof                             |        | 9  |  |  |  |  |  |  |

|    |      | 2.2.4. Applications                                         |        | 10 |  |  |  |  |  |  |

| 3. | Imp  | plementing Zero Knowledge with zk-SNARKs                    |        | 13 |  |  |  |  |  |  |

|    | 3.1. | Overview                                                    |        | 13 |  |  |  |  |  |  |

|    | 3.2. | Intuition of a proof's structure                            |        | 14 |  |  |  |  |  |  |

|    |      | 3.2.1. Arithmetic circuit setup                             |        | 14 |  |  |  |  |  |  |

|    |      | 3.2.2. Selector polynomials                                 |        | 15 |  |  |  |  |  |  |

|    |      | 3.2.3. Master and vanishing polynomial                      |        | 17 |  |  |  |  |  |  |

|    |      | 3.2.4. Quadratic Arithmetic Program                         |        | 18 |  |  |  |  |  |  |

|    |      | 3.2.5. Rank-1 Constraint Satisfiability                     |        | 19 |  |  |  |  |  |  |

|    |      | 3.2.6. Linear PCPs                                          |        | 20 |  |  |  |  |  |  |

|    | 3.3. |                                                             |        |    |  |  |  |  |  |  |

|    |      | 3.3.1. Benefits and drawbacks                               |        | 21 |  |  |  |  |  |  |

|    |      | 3.3.2. Implementation                                       |        | 22 |  |  |  |  |  |  |

| 4. | Har  | rdware design                                               |        | 24 |  |  |  |  |  |  |

|    | 4.1. | Description of the problem                                  |        | 24 |  |  |  |  |  |  |

|    |      | 4.1.1. Computing H polynomial                               |        | 24 |  |  |  |  |  |  |

|    |      | 4.1.2. Matrix vector multiplication                         |        | 25 |  |  |  |  |  |  |

|    | 4.2. | 4.2. Number Theoretic Transform                             |        |    |  |  |  |  |  |  |

|    |      | 4.2.1. Improving polynomial multiplication                  |        | 26 |  |  |  |  |  |  |

|    |      | 4.2.2. Evaluation and interpolation using the Vandermonde 1 | natrix | 27 |  |  |  |  |  |  |

|    |      | 4.2.3. The radix-2 DIT algorithm                            |        | 28 |  |  |  |  |  |  |

|    |      | 4.2.4. Generic algorithm                                    |        | 29 |  |  |  |  |  |  |

|    |      | 125 Hardware design                                         |        | 21 |  |  |  |  |  |  |

### Contents

|           | 4.3.  | 4.3.1.  | vector multiplication | 34<br>34<br>35 |

|-----------|-------|---------|-----------------------|----------------|

| <b>5.</b> | Eval  | uation  | l                     | 38             |

|           | 5.1.  | Arbitra | ary input circuits    | 38             |

|           |       |         | Circuit description   | 39             |

|           |       | 5.1.2.  | Explaining the code   | 39             |

|           |       |         | Workloads             | 41             |

|           | 5.2.  | Integra | ating jsnark          | 43             |

|           | 5.3.  | Estima  | ated hardware results | 44             |

|           |       | 5.3.1.  | Memory bandwidth      | 46             |

|           | 5.4.  | Final c | considerations        | 46             |

| 6.        | Con   | clusion | ns                    | 48             |

| 7.        | Futu  | ire woi | rk                    | 50             |

| Bi        | bliog | raphy   |                       | 52             |

# Chapter 1

# Introduction

In the ever-changing world of communication technologies, the need for trust and security has never been more paramount. In the past few years, individuals and organizations are increasingly relying on digital platforms for sensitive transactions or data processing. Therefore, the need to ensure the integrity, privacy and efficiency of these operations has become a major concern. This is where the world of verifiable computation and zero-knowledge proofs enters the stage.

Verifiable computation looks to address the challenge of efficiently validating computations that have been outsourced to another party. Furthermore, it also seeks to enable the verification of those computations without the need to reveal sensitive or private input data provided by the party in charge of the computation.

The cryptographic primitives that provide the tools for its implementation are zero-knowledge proofs. Succintly, they allow one party, the prover, to demonstrate the validity of a statement to another party, the verifier, without revealing any specific details about the statement itself. The main drawback for using them in practice is that the proof generation is very time-consuming. Therefore, in this project we want to study if a specific protocol that provides an implementation for verifiable computation can be accelerated through hardware.

In summary, the main goal of this work is to learn what Zero Knowledge Proofs are and to understand the basic concepts on how to implement them practically. Then, we want to investigate if it is possible to accelerate the generation of the proof using hardware design.

In the following chapters we will explore the concepts explained previously. Our journey will be divided into the following sections:

■ In Chapter 2, we will dive into the basics of Verifiable Computation and Zero Knowledge Proofs. We will use examples to make these ideas clear and also look at real-life situations where researchers have suggested using them.

- Chapter 3 will introduce zk-SNARKs, a group of protocols that are widely used to implement Zero Knowledge Proofs. There will also be a practical explanation on how to generate a proof for an arithmetic circuit as well as a description of the characteristics of the protocol mainly used in this project.

- In Chapter 4 we will focus on the design of some units needed to accelerate the proof generation in a zk-SNARK.

- In Chapter 5 we will explain the code made with the purpose of executing workloads to be used as baselines. We will also do a back-of-the-envelope calculation of the time and area needed when using the hardware explained in the previous chapter.

- Chapter 6 and 7 will provide the conclusions of the project as well as some proposals on how this work could continue in the future.

# Chapter 2

# Background and motivation

The purpose of this chapter is to provide an understanding of essential concepts outlined in this thesis. Additionally, it aims to present compelling examples of their applications to the real world.

# 2.1. Verifiable Computation (VC)

Due to the uneven distribution of computational power, there is an increasing demand to outsource computation from a **weak client** (such as mobile phones) to one or more **powerful workers** (like an external server). This leads to the need to verify that the results obtained have been computed correctly. This verification serves the purpose of protecting the client against malfunctioning workers or malicious ones that are able to return plausible results without performing the computation.

### 2.1.1. Definition

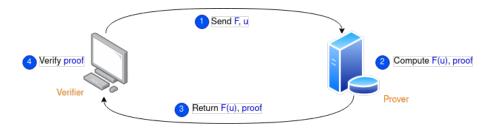

In a nutshell, a **public verifiable computation scheme** allows a client to outsource the computation of a function F on an input u to one or more workers. The workers, who we shall call **provers**, will generate a proof of the correctness of the computation that the client, also known as **verifier**, can later check. The verification should require less work than would be needed for the evaluation of F.

Figure 2.1: Verifiable Computation diagram.

We can find a more formal definition in [1] and [2]:

**Definition 2.1.1** (Public Verifiable Computation Scheme): A Public Verifiable Computation Scheme  $\mathcal{VC}$  consists on the set of three polynomial-time algorithms defined below:

- 1. **KeyGen** $(F, 1^{\lambda}) \to (EK_F, VK_F)$ : Given the security parameter  $\lambda$  (see definition 2.1.2), the randomized *key generation algorithm* generates a public evaluation key  $EK_F$  that encodes the target function F and a public verification key  $VK_F$ .

- 2. Compute  $(EK_F, u) \to (y, \pi_y)$ : In a deterministic algorithm, the worker uses the public evaluation key  $EK_F$  and input u to compute  $F(u) \to y$  and the proof of y's correctness  $\pi_y$ .

- 3. Verify $(VK_F, u, y, \pi_y) \to \{0, 1\}$ : The deterministic verification algorithm uses the verification key  $VK_F$  to output 1 if F(u) = y and 0 otherwise.

In the field of cryptography, the security parameter measures the difficulty for adversaries to break a chryptographic scheme. In our definition the security parameter  $\lambda$  sets an upper limit on the probability that an adversary can successfully forge a proof using the  $EK_F$  and  $VK_F$ . It is usually expressed as a string of  $\lambda$  1s, conventionally  $1^{\lambda}$ . Its formal definition is given in [1]:

**Definition 2.1.2** (Security parameter): For any function F and any probabilistic polynomial-time adversary A:

$$\Pr\left[\begin{array}{c} F(\hat{u}) \neq \hat{y} \\ (\hat{u}, \hat{y}, \hat{\pi}_y) \leftarrow \mathcal{A}(EK_F, VK_F) : \text{ and } \\ \mathbf{Verify}(VK_F, \hat{u}, \hat{y}, \hat{\pi}_y) = 1 \end{array}\right] \leq \mathbf{negl}(\lambda)$$

# 2.1.2. Public and designated verifier

In the definition above, the entity that checks the correctness of the proof is called a **public verifier**. The main characteristic of this scheme is that the verifier can be any third party that is willing to participate in the verification process, i.e., with a single proof, everyone can be convinced of the correctness of the computation.

In contrast, we could also have a VC scheme that is **designated verifier**, where only this individual will be convinced of the proof. In this case, the verification key  $VK_F$  and the output of the verification function (i.e., if the proof provided by the prover is correct or not) need to be kept a secret in order to maintain the scheme secure against attacks.

# 2.2. Zero Knowledge Proofs

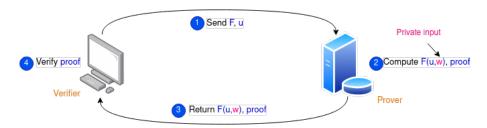

Until now, we have considered all the computation's inputs u to be known by the verifier. However, in some situations, the prover might have a private input w (also known as witness) they do not want to share with the verifier.

Figure 2.2: VC diagram with private inputs.

This leads to the need to make the  $\mathcal{VC}$  scheme **zero-knowledge**, which essentially means that the verifier learns nothing about the prover's private input beyond the output of the computation.

### 2.2.1. Definition

Zero Knowledge Proofs were first conceived by Shafi Goldwasser, Silvio Micali and Charles Rackoff in 1985 ([3]). Since then, they have become more popular due to its multiple applications in fields such as verifiable computing, authentication or privacy.

Essentially, a **Zero Knowledge Proof (ZKP)** is a proof that yields nothing beyond the validity of the assertion ([4]). In other words, ZKP systems allow one party (the **prover**) to convince the other parties (the **verifiers**) that a **statement** is true without revealing any other information about it. A ZKP system should satisfy three properties ([5],[6]):

- Completeness: if a statement is true and both the prover and the verifier follow the protocol, then the prover can convince the verifier to accept the statement.

- Soundness: if a statement is false and the verifier follows the protocol, the verifier will not be convinced to accept it.

- **Zero-knowledge**: if a statement is true and the prover follows the protocol, the interaction will not reveal any additional information beyond its truth to the verifier.

## 2.2.2. Examples

To better understand the concept of Zero Knowledge Proofs, in this section we will provide illustrative examples to facilitate the reader's comprehension of the subject.

### Red and green balls

In this example, suppose there are two balls: one red and one green. Alice (the prover) wants to prove to his color-blind friend Bob (the verifier) that these balls have different colors. To do so they follow these steps:

- 1. Bob takes the two balls, apparently identical to him, and shows Alice the initial position of the balls.

- 2. Then, in private, Bob tosses a coin and exchanges the balls if it lands on heads.

- 3. Bob shows the balls to Alice and asks her if he exchanged the balls.

If Alice is indeed able to tell apart the color of the two balls she will always know if Bob switched the balls. Hence, after repeating the steps enough times, Bob will be convinced that the colors of the two balls are different (completeness). It is worth noting that if Alice could not distinguish the balls she would have a 50% chance of guessing correctly each time. After repeating the test 20 times she would have a 1 in 1,048,576 chance of (luckily) answering right every time.

If Alice is also color-blind and the experiment is repeated enough times, at some point she will be "unlucky" and give a wrong answer. Thus, Bob will not be convinced that she is saying the truth (soundness).

Finally, Bob never discovers which is the color of each ball and therefore we achieve the zero-knowledge property.

### Graph isomorphism

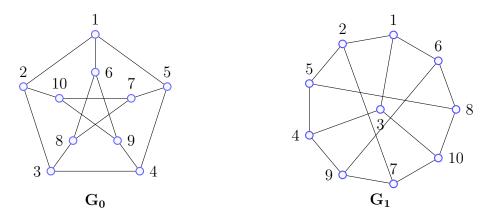

The following example is a more mathematical one and first we will recall the definition of graph isomorphism:

**Definition 2.2.1** (Graph isomorphism): A graph  $G_0$  is isomorphic to  $G_1$  if  $\exists$  and isomorphism  $\pi : [N] \to [N]$  such that  $\forall i, j$ :

$$(\pi(i), \pi(j)) \in E_1 \iff (i, j) \in E_0$$

where N is the number of nodes and  $E_0$ ,  $E_1$  are the sets of edges of  $G_0$ ,  $G_1$  respectively.

Note that saying that there is an isomorphism between two graphs is equivalent to the concept of being able to obtain one graph pattern from the other just by "moving the nodes". In Figure 2.3 we can see an example of two isomorphic graphs. In this case an isomorphism would be:

$$(1,2,3,4,5,6,7,8,9,10) \xrightarrow{\pi} (5,4,9,7,2,8,1,6,10,3)$$

Figure 2.3: Isomorphic graphs.

In this example, Alice (our prover) wants to convince Bob (the verifier) that she knows an isomorphism for two graphs  $G_0$  and  $G_1$ .

Before starting the interaction, Alice defines a new graph  $\mathbf{H}$  that is isomorphic to  $\mathbf{G_0}$  (and  $\mathbf{G_1}$ ). She can do this by applying some random permutation  $\gamma:[N]\to[N]$  to the nodes of  $\mathbf{G_0}$  (it would be analogous for  $\mathbf{G_1}$ ):  $\mathbf{H}=\gamma(\mathbf{G_0})$ . Then, the steps for the proof would be:

- 1. Alice creates and sends graph **H** to Bob.

- 2. Bob flips a coin and sends the result to Alice.

- 3. If the result was heads, Alice needs to return an isomorphism to  $G_0$ . Otherwise, she has to send an isomorphism to  $G_1$ .

If Alice knows an isomorphism  $\pi$  such that  $\mathbf{G_0}$  and  $\mathbf{G_1}$  are isomorphic, she will always be able to return an isomorphism to  $\mathbf{H}$  to the prover. If it landed on heads, she will just return  $\gamma$ . In the other case, she can return  $\gamma \circ \pi^{-1}$  because  $\mathbf{H} = \gamma(\mathbf{G_0}) = \gamma(\pi^{-1}(\mathbf{G_1}))$ . Thus, we have completeness.

We also have soundness after repeating the experience multiple times. If the prover does not truly know the isomorphism between both graphs, they can try to fake a proof by guessing which isomorphism will be required by the verifier and constructing **H** from  $G_0$  or  $G_1$ . The probability of having a lucky guess once is 1/2 so after k repetitions  $Pr[Accepting\ a\ false\ proof] = <math>1/2^k$ .

The zero-knowledge property is also achieved because the verifier never learns what the isomorphism between both graphs is.

### Ali-Baba Cave

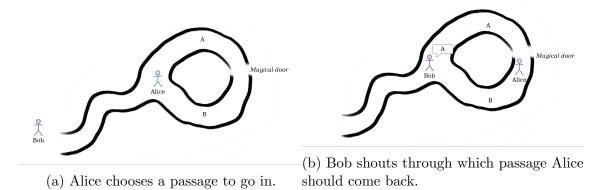

Another well-known example of a ZKP is the one proposed by Jean-Jacques Quisquater and others in [7].

Suppose there is a cave with exactly one entrance from the outside. Inside, the cave forks into two passages (which we will call A and B) in an intersection that cannot be seen from outside the cave (see Figure 2.4). In this case Alice (prover) wants to show Bob (verifier) that she knows the password to a secret door that connects both passages.

The procedure to prove this statement is the following:

- 1. Alice goes inside the cave and chooses one of the two passages while Bob stands outside the cave. This means that Bob is unable to see which of both passages Alice has chosen.

- 2. Bob goes into the cave and stops at the intersection. Then he shouts which of the two passages (A or B) he wants Alice to come out from.

- 3. Alice comes back through the passage Bob asked her, using the secret door if needed.

Figure 2.4: Ali-Baba cave example.

After repeating this procedure enough times (similarly to the previous examples), Bob will be convinced that Alice's statement was true.

One important remark that needs to be made is the fact that a third party would not be convinced by this proof because Bob and Alice could have colluded to fake the results by agreeing beforehand which passage would be chosen each time. This means that Alice is just disclosing this knowledge to Bob and not to the rest of the world. One way to convince a third party would be to flip a coin (or some other random algorithm) to decide which passage should Alice come back from. Then, the observer would be reassured that Alice and Bob have not colluded.

## 2.2.3. Interactivity of a proof

All the examples we have seen until now in 2.2.2 have been **interactive proofs**. This means that the prover and the verifier can interact back and forth in order to complete the proof. In the following paragraphs we will explain a way to change them into **non-interactive proofs**. This will be useful because it will allow us to directly generate a proof that will convince the verifier without needing to exchange so many messages.

This procedure was first explained in [8] and it is commonly known as the **Fiat-Shamir heuristic**. Essentially, it takes a **public coin** interactive protocol<sup>1</sup> and turns it into a non-interactive one. The practical way to do this is making the prover generate the "coins" given by the verifier with a hash function.

In a public coin protocol, the interaction could be something like what is shown on the left of Figure 2.5. Firstly, the prover sends a message  $m_1$ , then the verifier sends back the result of one or more coin tosses and finally the prover replies back with  $m_2$ . Afterwards, the verifier checks that the result is correct using the public input x (if there is one), the result of the coin toss and the messages  $m_1$  and  $m_2$ . In the graph isomorphism example 2.2.2,  $m_1$  would be the graph  $\mathbf{H}$  and  $m_2$  would be the isomorphism to  $\mathbf{G_0}$  or  $\mathbf{G_1}$  depending on the result of the coin toss.

Figure 2.5: Fiat-Shamir heuristic. On the left we can see the public coin protocol and on the right we have the modified one so that it is non-interactive.

Let  $H: \{0,1\}^* \to \{0,1\}^k$  be a cryptographic hash function<sup>2</sup>. The way to remove the interactivity is to apply the hash function H to the first message  $m_1$  and the public input x. As the results of the hash function are supposed to be random, we

<sup>&</sup>lt;sup>1</sup>In this setting, the random choices made by the verifier are made public.

<sup>&</sup>lt;sup>2</sup>Informally, they are functions that map a string of arbitrary length to one with a fixed length k. They have many useful properties that can be applied to cryptography, for instance, it is unfeasible to retrieve an input from its hash under certain conditions or to find other inputs with the same hash value.

will replace the random value that comes from the verifier's coin toss by  $H(x, m_1)$  and generate  $m_2$  using that value. The verification is made using x,  $m_1$ ,  $H(x, m_1)$  and  $m_2$  (right side of Figure 2.5).

Note that this procedure can be used for our previous examples in 2.2.2 because they all could use a coin to simulate the behaviour of the verifier. Therefore, we can transform them into non-interactive proofs using the Fiat-Shamir heuristic. Beware that this does not mean that every interactive zero-knowledge proof can be transformed so that they are not interactive. Firstly, they need to be converted into public-coin protocols. Also, for Fiat-Shamir heuristic to work, we need the prover to be computationally bounded so that they are not able to invert H. Nonetheless, it is used in many implementations of zero-knowledge proofs ([9]).

There is one last comment on this heuristic. Suppose that we consider H to be a random-oracle i.e. a theoretical "black box" that responds to every unique query with a truly random string and that gives the same response if the query is repeated. Then, completeness and soundness hold ([9]). However, there are still some questions about the security of the new protocol due, in part, to the fact that a random-oracle is often used as an idealised version of a hash function. More work on this can be found in [10] and [11].

# 2.2.4. Applications

Having explored some "toy examples" in section 2.2.2, let's now delve into some real-world applications.

### Preventing identity theft

One of the first application ideas that were devised right after the conception of zero-knowledge proofs was a way to prevent identity theft ([8]). Essentially, if a user wants to prove their identity to some server, the user should create a zero-knowledge proof stating that they know the answer to a hard theorem such as factoring or graph isomorphism (as seen in 2.2.2). This method provides a way to avoid the use of passwords, which can be stolen from the server and even if they are encrypted, said encryption could be broken if it is not secure enough.

### Nuclear disarmament

Another idea that was proposed and is rather interesting is using it in the context of nuclear disarmament, which has the aim of reducing or completely eliminating nuclear weapons from the world in order to avoid a potential nuclear catastrophe, both accidental or caused by wars. One of the reasons it is not being done faster is that countries need reassurance that the others are doing it as well, an that is when zero-knowledge proofs come in. Their privacy-preserving characteristics would allow to prove that certain operations regarding the elimination of nuclear weapons have

been performed without needing to disclose sensitive information. Work on this was done by Boaz Barak among others and is shown in papers such as [12].

### **Forensics**

Zero-knowledge proofs could also be used in forensics. This field consists in applying scientific methods to investigate and analyze evidence from crime scenes and other incidents, and can be used to aid in legal investigations and proceedings. In this case, we could prove that and individual's DNA is different from the one found in a crime scene without disclosing the DNA of the person. This application was explored in [13] by Ben Fisch, Daniel Freund and Moni Naor.

### Cryptocurrencies with privacy and anonymity

One of the fields where zero-knowledge that has had the most success are cryptocurrencies. In this area, the motivation of zero-knowledge proofs was maintaining the privacy of the transactions the users make. There was work on this in [14] and there are some digital currencies such as Zcash that already use it.

### Verification dilemmas in the law

There are other cases where we want to avoid exposing personal or proprietary information. For instance, when applying for a loan it is necessary to disclose personal data such as the salary to the bank, when for example it should only be necessary to prove that it is above a certain quantity. Also, in deal-making negotiations between firms, they might need to disclose some proprietary information that could be used by the competitor if the deal falls through. Additionally, litigants in court proceedings might have to reveal trade secrets in order to prove their claim. In [15], they explore these and other cases and present zero-knowledge proofs as a way to keep the sensitive data private.

### Electronic voting

The possibility of voting electronically opens many possibilities like the option of having completely transparent vote counting. Then, zero-knowledge proofs can be used here to ensure voter's privacy. Some work on this is explained by Jens Groth in [16].

### Fight disinformation

Lastly, a very peculiar example is the one presented in [17] on how to fight disinformation. The main idea is to be able to generate proofs that the images in some articles come from the place and time the article is talking about. To do so, the camera has an embedded certified signing key that cannot be extracted from it. There is a standard for it called C2PA but there is a problem with post-processing

because these images might be cropped or manipulated. The solution for it is generating a proof that the new image comes from the original. That is where we can use zk-SNARKs, an implementation of all we have been talking about in this chapter and that we will discuss in the following chapter (3).

# Chapter 3

# Implementing Zero Knowledge with zk-SNARKs

Among the most promising and widely used candidates for a practical implementation of non-interactive zero-knowledge proofs we can find **zk-SNARKs**<sup>1</sup>. They encompass a group of protocols that enable the prover to generate a proof for a computation without revealing the values used in such computation.

In this chapter we will find a brief description of zk-SNARKs as well as an intuition on how to create a proof for a specific arithmetic circuit. Later we will also describe the specific protocol we will be working with and discuss some of its advantages and drawbacks with respect to other state-of-the-art protocols. Finally, we will provide a brief analysis of the algorithm we will want to accelerate in later chapters.

## 3.1. Overview

zk-SNARKs are a type of VC (2.1) schemes that allow the prover to generate ZKP. The acronym zk-SNARK stands for zero knowledge succint non-interactive argument of knowledge:

- **Zero-Kownledge**: the verifier of the statement cannot acquire any new information through the process, they only learn whether the statement is true or false.

- Succint: the proof of the statement is short and can be efficiently verified without the need to perform the full computation. In practice, this means that the length of the proof and the verification complexity should be sublinear in the size of the circuit computing F we are generating the proof for ([18]).

<sup>&</sup>lt;sup>1</sup>There are also other type of protocols such as zk-STARKs (Zero-knowledge Scalable Transparent Argument of Knowledge) or Bulletproofs which we will not see in this project.

- Non-interactive: it does not require any back-and-forth interaction between the prover and verifier, the prover just needs to send a single message with the proof to the verifier.

- ARgument of Knowledge: the proof system provides evidence that the prover knows certain information required to complete the proof. It is worth noting that this is an argument and not a proof, though they are often used interchangeably. If a proof system only satisfies the soundness condition with respect to polynomial-time provers, then it is called an argument system.

# 3.2. Intuition of a proof's structure

At this point we have seen the definitions of Zero Knowledge Proofs and zk-SNARKS but we have not yet learned how to create a proof for a given function. In this section we are going to try to give an intuition on that. It is meant to be an introductory explanation based on the ones given in [19] and the lectures found in [9]. For a more complete one it can be useful to refer to some articles explaining their respective protocol in more detail ([1], [6] and [18]).

## 3.2.1. Arithmetic circuit setup

Suppose that we are given an arithmetic circuit C over a finite field  $\mathbb{F}$  that computes the function we are generating the proof for<sup>2</sup>. The prover claims to know a secret witness w such that C(x, w) = y, where x is the public input of the circuit and y is its output.

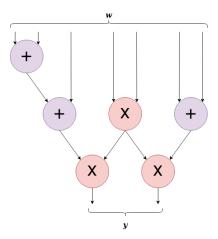

Figure 3.1: Circuit description. It is composed by 3 addition gates (purple) and 3 multiplication gates (red). The arrows at the top of the picture represent the secret input w and the ones at the bottom are part of the output y.

<sup>&</sup>lt;sup>2</sup>In the example shown in Figure 3.1 the function would be  $F(w_1, w_2, w_3, w_4, w_5, w_6, w_7) = ((w_1 + w_2) + w_3)(w_4, w_5), (w_4w_5)(w_6 + w_7).$

The circuit we will use for this example is shown in Figure 3.1 and for the sake of simplicity, we will take the public input x to be empty.

In our example, the output (known by the verifier) will be the vector

$$y = (132, 108)$$

which we can get with the secret input (which the prover wants to prove they know)

$$w = (2, 5, 4, 3, 4, 7, 2)$$

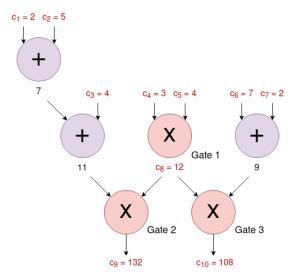

To generate the proof, we will also numerate the multiplication gates (as can be seen in Figure 3.2) and define a vector with the inputs/outputs of the multiplication gates. If there is an addition gate before a multiplication one, we will add the inputs of the addition gate to the vector instead of the output value of the addition gate. For clarity, these values are shown in red in Figure 3.2.

Figure 3.2: Circuit with values specified. The inputs/outputs of the multiplication gates are shown in red and each multiplication gate is numbered.

This will give us the following vector

$$c = (c_1, c_2, c_3, c_4, c_5, c_6, c_7, c_8, c_9, c_{10}) = (2, 5, 4, 3, 4, 7, 2, 12, 132, 108)$$

# 3.2.2. Selector polynomials

We are now able to start constructing the proof. For each value in vector c we will first define three **selector polynomials** which will encode if they are the left input, right input or output of a multiplication gate  $^3$ . Each gate will have a

<sup>&</sup>lt;sup>3</sup>As we will see, the addition gates will be implicit in the procedure.

distinct evaluation point assigned, i.e. when evaluating each selector polynomial at this point, we will get if it is the left input, right input or output of that gate. In this example we will choose these points as roots of the unity  $\{\omega, \omega^2, \omega^3\}$  in  $\mathbb{F}$ . This is done to make polynomial manipulation faster as we will use a variation of a Fast Fourier Transform for finite fields<sup>4</sup>.

For example, the selector polynomials assigned to the 1<sup>st</sup> element of c:  $l_1(x)$ ,  $r_1(x)$ and  $o_1(x)$ . They would be defined as:

- $l_1(x): l_1(\omega)=0, l_1(\omega^2)=1, l_1(\omega^3)=0$  because it is a left input to the second multiplication gate (through the additions in between) but that is not the case for the first and third multiplication gates.

- $r_1(x): r_1(\omega)=0, r_1(\omega^2)=0, r_1(\omega^3)=0$  as it is not a right input to any of the gates.

- $o_1(x): o_1(\omega)=0, o_1(\omega^2)=0, o_1(\omega^3)=0$  as it is not an output to any of the gates.

As it can be seen in Figure 3.2, these polynomials will be identical for the 2<sup>nd</sup> and  $3^{\rm rd}$  element in c because even though they are inputs to different addition gates, they all end up being left inputs to the second multiplication gate. The 4<sup>th</sup> and 5<sup>th</sup> element are just a left and right input to the first gate respectively. The  $6^{\rm th}$  and  $7^{\rm th}$ one are both right inputs to the third gate.

In the case of the 8<sup>th</sup> element the polynomials would be defined as:

- $l_8(x): l_8(\omega) = 0, l_8(\omega^2) = 0, l_8(\omega^3) = 1$  as it is a left input to the third multiplication gate.

- $r_8(x): r_8(\omega) = 0, r_8(\omega^2) = 1, r_8(\omega^3) = 0$  because it is also a right input to the second gate.

- $\bullet$   $o_8(x): o_8(\omega) = 1$ ,  $o_8(\omega^2) = 0$ ,  $o_8(\omega^3) = 0$  as it is the output of the first gate.

And finally the 9<sup>th</sup> and 10<sup>th</sup> elements are outputs of the second and third gate respectively.

The value of the three selector polynomials assigned to every element of vector c at  $\omega$ ,  $\omega^2$  and  $\omega^3$  can be found on Table 3.1. Once we have all the selector polynomials, we will use them to define three polynomials for the whole circuit that will encode all the operations in it:

- $L(x) = \sum_{i=1}^{10} c_i \times l_i(x)$

- $R(x) = \sum_{i=1}^{10} c_i \times r_i(x)$   $O(x) = \sum_{i=1}^{10} c_i \times o_i(x)$

<sup>&</sup>lt;sup>4</sup>More information on that can be found in section 4.2.

|             | ω | $\omega^2$ | $\omega^3$ |             | $\omega$ | $\omega^2$ | $\omega^3$ |             | ω | $\omega^2$ | $\omega^3$ |

|-------------|---|------------|------------|-------------|----------|------------|------------|-------------|---|------------|------------|

| $l_1(x)$    | 0 | 1          | 0          | $r_1(x)$    | 0        | 0          | 0          | $o_1(x)$    | 0 | 0          | 0          |

| $l_2(x)$    | 0 | 1          | 0          | $r_2(x)$    | 0        | 0          | 0          | $o_2(x)$    | 0 | 0          | 0          |

| $l_3(x)$    | 0 | 1          | 0          | $r_3(x)$    | 0        | 0          | 0          | $o_3(x)$    | 0 | 0          | 0          |

| $l_4(x)$    | 1 | 0          | 0          | $r_4(x)$    | 0        | 0          | 0          | $o_4(x)$    | 0 | 0          | 0          |

| $l_5(x)$    | 0 | 0          | 0          | $r_5(x)$    | 1        | 0          | 0          | $o_5(x)$    | 0 | 0          | 0          |

| $l_6(x)$    | 0 | 0          | 0          | $r_6(x)$    | 0        | 0          | 1          | $o_6(x)$    | 0 | 0          | 0          |

| $l_7(x)$    | 0 | 0          | 0          | $r_7(x)$    | 0        | 0          | 1          | $o_7(x)$    | 0 | 0          | 0          |

| $l_8(x)$    | 0 | 0          | 1          | $r_8(x)$    | 0        | 1          | 0          | $o_8(x)$    | 1 | 0          | 0          |

| $l_9(x)$    | 0 | 0          | 0          | $r_9(x)$    | 0        | 0          | 0          | $o_9(x)$    | 0 | 1          | 0          |

| $l_{10}(x)$ | 0 | 0          | 0          | $r_{10}(x)$ | 0        | 0          | 0          | $o_{10}(x)$ | 0 | 0          | 1          |

Table 3.1: Selector polynomials.

It can be easily seen that when evaluating any of the polynomials at the point corresponding to any of the multiplication gates, we will get the expected value for it. For instance, if we evaluate the polynomials at  $\omega^2$ :

$$L(\omega^2) = \sum_{i=1}^{10} c_i \times l_i(\omega^2) = c_1 + c_2 + c_3 = 2 + 5 + 4 = 11$$

$$R(\omega^2) = \sum_{i=1}^{10} c_i \times r_i(\omega^2) = c_8 = 12$$

$$O(\omega^2) = \sum_{i=1}^{10} c_i \times o_i(\omega^2) = c_9 = 132$$

which are the values expected for the 2<sup>nd</sup> gate.

# 3.2.3. Master and vanishing polynomial

Once we have all the selector polynomials and their coefficients, we define the **master polynomial** as

$$p(x) := L(x)R(x) - O(x) = (\sum_{i=1}^{m} c_i \times l_i(x)) \times (\sum_{i=1}^{m} c_i \times r_i(x)) - (\sum_{i=1}^{m} c_i \times o_i(x))$$

where m is the number of inputs and outputs of all the multiplication gates (the size of vector c), in our case m = 10. The key fact of defining this polynomial is that

$$p(\omega^i) = 0, \quad \forall i \in \{1, \dots, n\}$$

where n is the number of multiplication gates, in the example n = 3. This is true owing to the fact that in these points p(x) is essentially multiplying the inputs and

subtracting the gate output. Therefore, the *n* powers of  $\omega$  will be roots of p(x) which will lead us to define a **target** or **vanishing polynomial**:

$$t(x) = (x - \omega) \cdots (x - \omega^n)$$

that exactly divides p(x) i.e. p(x) = t(x)h(x) for some h(x).

## 3.2.4. Quadratic Arithmetic Program

The last piece of the puzzle is the following claim which roughly states that:

The prover claims to know a witness w such that C(x, w) = y.

The prover claims to know a vector c such that p(x) = t(x)h(x).

The simple idea of the proof would be to do something like this:

- 1. The verifier samples a random point  $\gamma$ , calculates  $t = t(\gamma)$  and gives  $\gamma$  to the verifier.

- 2. The prover calculates  $h(x) = \frac{p(x)}{t(x)}$ , computes  $p = p(\gamma)$ ,  $h = h(\gamma)$  and sends p and h to the verifier.

- 3. The verifier checks that  $p = t \cdot h$  and accepts if the equality holds.

This approach is based on the **Schwartz-Zippel lemma** which for our problem states that given a value  $\gamma$  chosen at random uniformly from  $\mathbb{F}$ , the probability that  $t(\gamma) = \alpha$  is  $\frac{d}{|\mathbb{F}|}$  (where d is the degree of the polynomial).

*Remark.* Obviously, this construction has multiple issues, among them:

- 1. The prover could easily fake a proof because they can compute t. Hence they can take a random value h and compute  $p = t \cdot h$ , which will be accepted by the verifier because the equality holds.

- 2. Additionally, even if the prover had a p(x) that truly satisfied the equality, it could be obtained from sampling a random h(x) and computing p(x) = t(x)h(x). This means that there is no enforcement that p(x) represents the function we are computing.

In practice, these issues are solved by encrypting the polynomials and other values used in the protocol. For the sake of brevity, we will refrain from delving into it. Nonetheless, the construction used in [1] is thoroughly explained in [19] and even though it is not the protocol we will use in this project, its reading can be very useful to further understand the different issues that can emerge from this kind of protocols.

This construction we have explained is a Quadratic Arithmetic Program (QAP), whose definition was first implicitly found in [20] and is expressed in [1]:

**Definition 3.2.1** (Quadratic Arithmetic Program): A Quadratic Arithmetic Program (QAP)  $\mathcal{Q}$  over field  $\mathbb{F}$  contains three sets of m+1 polynomials  $\mathcal{L} = \{l_k(x)\}, \ \mathcal{R} = \{r_k(x)\}, \ \mathcal{O} = \{o_k(x)\}$  for  $k \in \{0...m\}$ , and a target polynomial t(x). Suppose f is a function that takes n elements of  $\mathbb{F}$  as input and outputs n' elements of the same field, where N = n + n' is the total of I/O elements. Then, we say that  $\mathcal{Q}$  computes f if:

$(c_1, \dots, c_N) \in \mathbb{F}^N$  is a valid assignment of F's inputs and outputs.

$\updownarrow$

There exist coefficients  $(c_{N+1}, \cdots, c_m)$  such that t(x) divides p(x), where

$$p(x) = \left(l_0(x) + \sum_{k=1}^{m} c_k \cdot l_k(x)\right) \cdot \left(r_0(x) + \sum_{k=1}^{m} c_k \cdot r_k(x)\right) - \left(o_0(x) + \sum_{k=1}^{m} c_k \cdot o_k(x)\right)$$

In other words, there must exist some polynomial h(x) such that  $p(x) = h(x) \cdot t(x)$ . The size of Q is m. The degree of Q is deg(t(x)).

Observe that in the definition there are  $l_0(x)$ ,  $r_0(x)$ ,  $o_0(x)$  polynomials which allow us to have additive constants in the problem. See also that if we allow the selector polynomials to evaluate to constants different from  $\{0,1\}$  in the evaluation points chosen for each gate, the system can also have multiplicative constants.

# 3.2.5. Rank-1 Constraint Satisfiability

There is another construction that is more suited for expressing the different constraints for the function and that can be easily transformed into a QAP. It is called **Rank-1 Constrain Satisfiability (R1CS) system** and its definition is the following (found in [18]):

**Definition 3.2.2** (Rank-1 Constraint Satisfiability): An R1CS system over a finite field  $\mathbb{F}$  is specified by a tuple  $\mathcal{CS} = (n, N_g, N_w, \{\mathbf{a}_i, \mathbf{b}_i, \mathbf{c}_i\}_{i \in [N_g]})$  where  $n, N_g, N_w \in \mathbb{N}$ ,  $n \leq N_w$  and  $a_i, b_i, c_i \in \mathbb{F}^{N_w+1}$ . The system  $\mathcal{CS}$  is satisfiable for a statement  $\mathbf{x} \in \mathbb{F}^n$  if there exists a witness  $\mathbf{w} \in \mathbb{F}^{N_w}$  such that

- $\mathbf{x} = (w_1, \dots, w_n)$  and

We express this concept as  $CS(\mathbf{x}, \mathbf{w}) = 1$  and we refer to n as the statement size,  $N_w$  as the number of variables and  $N_g$  as the number of constraints.

Observe that there is a 1 appended to the witness ( $[1 | \mathbf{w^T}]$ ) in the last equation in the definition. It has the purpose of allowing additive constants in the system, just as the polynomials  $l_0(x), r_0(x), o_0(x)$  did for the QAP.

Before creating the R1CS for the example, see that in our circuit 3.2 the computation can be summarized with:

$$c_4 \times c_5 = c_8$$

$(c_1 + c_2 + c_3) \times c_8 = c_9$

$(c_6 + c_7) \times c_8 = c_{10}$

In this case  $n = N_w = 10$  and  $N_g = 3$  and the vectors from the R1CS system will be:

The reason we have expressed the vectors in matrices is because checking that the system is satisfiable will be equivalent to cheking that the following equality holds:

$$A \cdot \begin{bmatrix} 1 \\ w \end{bmatrix} * B \cdot \begin{bmatrix} 1 \\ w \end{bmatrix} - C \cdot \begin{bmatrix} 1 \\ w \end{bmatrix} = \mathbf{0}$$

### 3.2.6. Linear PCPs

The kind of SNARKs that use the proof that we have described during this section are based on **Linear Probabilistic Checkable Proofs (PCPs)**. Informally, this is the kind of proof that can be verified by checking just a few random bits of it. The way to do this is by granting the verifier access to a linear oracle<sup>5</sup>  $\pi : \mathbb{F}^l \to \mathbb{F}$  so that they can submit several queries and decide to accept or reject a statement on an input x ([18]).

<sup>&</sup>lt;sup>5</sup>An oracle can be thought of a "black box" capable of providing a solution given an instance of a computational problem.

For instance, it is possible to transform the QAP into a 4-query linear PCP. Recall that in the original problem we have:

$$p(x) = (\sum_{i=1}^{m} c_i \times l_i(x)) \times (\sum_{i=1}^{m} c_i \times r_i(x)) - (\sum_{i=1}^{m} c_i \times o_i(x)) = t(x)h(x)$$

To perform the verification of the proof, we choose a random value  $\gamma$  and define the following vectors:

$$l_{\gamma} = [l_1(\gamma), \dots, l_m(\gamma)]^T$$

$$r_{\gamma} = [r_1(\gamma), \dots, r_m(\gamma)]^T$$

$$o_{\gamma} = [o_1(\gamma), \dots, o_m(\gamma)]^T$$

$$\Gamma = [1, \gamma, \dots, \gamma^{m-1}]^T$$

Then, we can check the proof by making the following queries (shown in blue in the equation) to the oracle:

$$(c \cdot l_{\gamma}) \times (c \cdot r_{\gamma}) - (c \cdot o_{\gamma}) = t(\gamma)(h \cdot \Gamma)$$

Note that the dot product between two vectors is a linear function and that the verifier can easily compute  $t(\gamma)$ .

Besides that, as it was said before, it is a bit more difficult to implement it so that the prover can not fake a proof. To understand each implementation it is better to check the original papers ([1], [6],[18]).

# 3.3. The protocol

Now that we have covered the fundamentals of zk-SNARKs, our attention will be directed towards the protocol featured in the paper "Shorter and Faster Post-Quantum Designated-Verifier zkSNARKs from Lattices" by Yuval Ishai, Hang Su adn David J. Wu ([18]). Firstly, we will explain some of the protocol's advantages and drawbacks in comparison to other state-of-the-art protocols. Subsequently, we will provide an overview of the three primary functions within the protocol.

### 3.3.1. Benefits and drawbacks

In recent years, there has been a substantial amount of research dedicated to exploring constructions based on various assumptions and optimizing both the asymptotic and practical efficiency of zkSNARKs. A potential concern for the future for a significant portion of these new zk-SNARKs is that they rely on group-based or pairing-based assumptions. Thus, they are insecure against quantum adversaries<sup>6</sup>.

<sup>&</sup>lt;sup>6</sup>For example, Shor's algorithm can be used to break some of these cryptographic schemes.

The protocol we are exploring is based on the problem of Learning With Errors (LWE) which essentially encrypts some secret values by adding some noise to them. This problem comes from lattice-based cryptography and it is thought to be quantum secure ([18]).

Another advantageous side of the protocol is the fact that it uses fields that use modular arithmetic. This is an improvement with respect to other kinds of protocols because for instance, multiplications on elliptic curves (used in [6] for example) are more expensive.

This protocol is designated verifier, therefore, a proof can only convince the intended party and not the general public. This can be seen as both a benefit and a drawback depending on the applications. For blockchain applications, it would not work because not everyone could verify the proof. But for e-mail signatures, the prover might only want to convince the person they are sending the e-mail to, so that if anyone else finds it, they will not be able to know that it was truly written by them.

Lattice-based protocols are relatively new and have not been as explored as others. Thus, they are still slower than the ones based on pairing-based assumptions for example. We think that they can be accelerated to become equal or better. In the next section we will explain the algorithm and focus on the part we want to accelerate.

# 3.3.2. Implementation

In the implementation of this SNARK there are three main parts: key generation, proof generation and verification of the proof. As we will see, these will follow the scheme explained in section 2.1.

### **Key generation**

This is the part of the proof that is in charge of the setup. Note that it only needs to happen once and then we can just execute the other two algorithms without needing to run this one as well. Therefore, it will not be important to accelerate it. We can see that the algorithm:

$$\mathtt{Setup}(1^{\lambda},1^{\kappa}) \to (\mathtt{crs},\mathtt{st})$$

takes a security parameter  $\lambda$  and the system index  $\kappa$  as inputs. It outputs the common reference string crs and the verification state st. The crs is generated using a trusted setup and it is later used in the proof generation algorithm. The st is used to verify the proof and it should be secret to the designated verifier.

### Proof generation

The proof generation algorithm:

## Proof generation(crs, x, w) $\to \pi$

is the one that takes as inputs the public input x, the witness w and the common reference string and then generates a proof. It is the costly step that we want to accelerate, as it has some characteristics that make it ideal for it. We will see more of this in the next chapter.

### Verification

Finally, the verification step needs to output zero or one depending on the correctness of the proof:

$$Verify(st, x, \pi) \rightarrow \{0, 1\}$$

The function takes the verification step, the public input and the proof as parameters and outputs a bit that is 0 or 1.

# Chapter 4

# Hardware design

The purpose of this chapter will be to outline the problem we aim to address and to present potential hardware solutions to tackle it.

# 4.1. Description of the problem

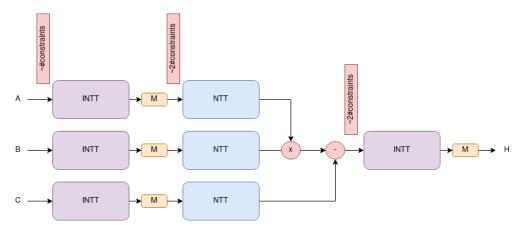

As it has been hinted throughout previous chapters, the problem we will focus on is *improving the proof generation time for zk-SNARKs* and more concretely, doing it for the protocol shown in [18]. To do so, in this chapter we will describe some strategies to design the hardware for the critical parts of the proof generation algorithm which collectively contribute to around 80% of the computation time for the proof. The parts that we will study are the computation of the H polynomial and a matrix vector multiplication.

# 4.1.1. Computing H polynomial

As we have seen in previous sections, computing the polynomial H(x) is one of the fundamental parts of the proof. This is because the essence of the proof relies on a simple divisibility check (see Section 3.2). To compute this polynomial and comply with the protocol requirements it is needed to perform some polynomial operations such as interpolation or evaluation.

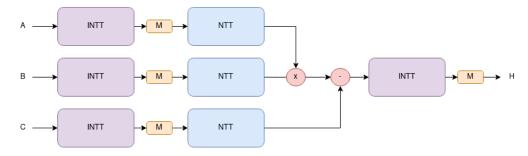

In Figure 4.1 we can see how H is computed based on the representation coming from R1CS. The most costly parts of this computation are the 7 NTTs (Number Theoretic Transform) and INTTs (Inverse Number Theoretic Transform) which are in charge of evaluating or interpolating a polynomial in an adequate set of points. In Section 4.2 we will see how to implement them in hardware to make them efficient. The other operations shown in the picture are scalar multiplications (M orange

blocks), an element-wise product<sup>1</sup> (x) and element-wise subtraction (-).

Figure 4.1: Diagram for the computation of the polynomial H during the proof generation algorithm.

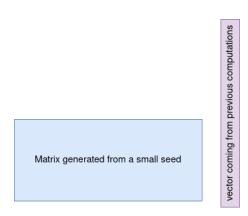

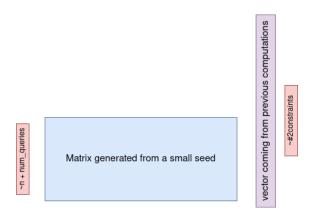

# 4.1.2. Matrix vector multiplication

Later on, in the code there is also another time-consuming step which mainly consists on multiplying a matrix that is generated from a small seed with a vector that comes from previous computations. This part is the one that might take longer to compute in the algorithm with about 70% of running time.

Figure 4.2: Matrix-vector multiplication used in the proof generation algorithm.

# 4.2. Number Theoretic Transform

As we have seen in previous sections, the evaluation and interpolation of polynomials are crucial steps in the algorithm. In this section we will introduce the **Number Theoretic Transform (NTT)**, which is a variant of the Fast Fourier Transform in finite fields. It will allow us to compute costly polynomial operations in a more efficient way. Later we will also introduce a way of accelerating it through hardware.

<sup>&</sup>lt;sup>1</sup>Also called Hadamard product.

## 4.2.1. Improving polynomial multiplication

Let  $\mathbb{F} = \mathbb{Z}/p\mathbb{Z}$  be the field of the integers modulo a prime  $p, a = (a_0, \dots, a_{n-1}) \in \mathbb{F}^n$  and  $b = (b_0, \dots, b_{n-1}) \in \mathbb{F}^n$ . Then, we define the convolution of these two vectors as<sup>2</sup>:

**Definition 4.2.1** (Vector convolution): The convolution of two vectors a and b is given by:

$$a \otimes b := (c_0, \dots, c_{2n-2})$$

where  $c_k = \sum_{i=0}^k a_i b_{k-i}, \quad a_j, b_j = 0$  for  $j < 0$  or  $j \ge n$ .

Note that one of the most direct applications of the convolution is polynomial multiplication. Let  $A(x) := \sum_{i=0}^{n-1} a_i x^i$  and  $B(x) := \sum_{i=0}^{n-1} b_i x^i$ . Then

$$A(x)B(x) = \left(\sum_{i=0}^{n-1} a_i x^i\right) \left(\sum_{i=0}^{n-1} b_i x^i\right) = \sum_{i=0}^{n-1} \sum_{j=0}^{n-1} a_i b_j x^{i+j} =$$

$$= \sum_{k=0}^{2n-2} \left(\sum_{i=0}^{k} a_i b_{k-i}\right) x^k = \sum_{k=0}^{2n-2} c_k x^k =: C(x)$$

As shown above, the coefficients of the resulting polynomial are the elements of  $a \otimes b$ . The problem of using the convolution for polynomial multiplication is that the algorithm is  $O(n^2)$  which is too slow.

Before seeing how we can improve it, we will introduce some notation regarding polynomial representation:

Coefficient representation It is the one we have been using until now, where the polynomial is defined by the values that multiply the powers of x. To simplify matters later, we will extend the coefficients with 0s until we have  $N = 2^t$  coefficients such that  $n \leq N$ :

$$A(x) = \sum_{i=0}^{N-1} a_i x^i, \ B(x) = \sum_{i=0}^{N-1} b_i x^i \qquad a_i, b_i = 0 \ \forall i \ge n$$

**Point-value representation** We can also use the evaluation of the polynomials at N points to represent them. Given  $\alpha = (\alpha_0, \dots, \alpha_{N-1}) \in \mathbb{F}^N$ , the values  $A(\alpha_0), \dots, A(\alpha_{N-1})$  represent the polynomial A(x).

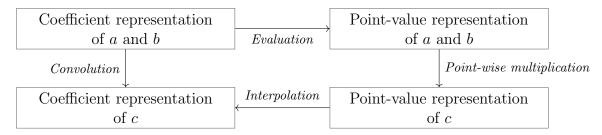

In Figure 4.3 we can see a diagram for polynomial multiplication. As we have said before, the convolution has a complexity of  $O(N^2)$  and it is trivial that the pointwise multiplication is O(N). The interesting part comes with the evaluation and

<sup>&</sup>lt;sup>2</sup>It comes from the definition of convolution for discrete functions.

interpolation operations. They both can be computed in  $O(N \log N)$  when choosing adequate values for the point-value representation.

Figure 4.3: Polynomial multiplication diagram.

# 4.2.2. Evaluation and interpolation using the Vandermonde matrix

As we have hinted in previous sections, the evaluation points we will choose<sup>3</sup> will be powers of the primitive Nth root of unity in the corresponding field. In this case, it is an  $\omega \in \mathbb{F}$  such that  $\omega^N \equiv 1 \mod p$ . Therefore, we will take the evaluation points defined as  $\alpha_i := \omega^i \quad \forall i \in 0, \ldots, N-1$ .

Now we can define the **Vandermonde matrix for**  $\omega$ :

$$M_{N,\omega} = \begin{bmatrix} 1 & \alpha_0 & \cdots & \alpha_0^{N-1} \\ 1 & \alpha_1 & \cdots & \alpha_1^{N-1} \\ \vdots & \vdots & \ddots & \vdots \\ 1 & \alpha_{N-1} & \cdots & \alpha_{N-1}^{N-1} \end{bmatrix} = \begin{bmatrix} 1 & 1 & \cdots & 1 \\ 1 & \omega & \cdots & \omega^{N-1} \\ \vdots & \vdots & \ddots & \vdots \\ 1 & \omega^{N-1} & \cdots & \omega^{(N-1)(N-1)} \end{bmatrix}$$

We can evaluate the polynomial at N points by applying the matrix to the vector of coefficients and similarly, we can also obtain the coefficients from applying the inverse of the matrix to the vector of evaluated points:

Evaluation:  $(M_{N,\omega} \cdot a)_i = A(\alpha_i) = A(\omega^i)$

Interpolation:  $(M_{N,\omega}^{-1} \cdot C(\alpha))_i = c_i$

An interesting observation regarding the matrix is the following:

Proposition 1.  $M_{N,\omega}^{-1} = \frac{1}{N} M_{N,\omega^{N-1}}$

<sup>&</sup>lt;sup>3</sup>Note that when doing multiplication through the alternative path instead of doing the convolution means that we can choose whichever evaluation points we want because the final coefficient representation will be independent of this choice.

*Proof.* We want to prove that the equality  $\frac{1}{N}M_{N,\omega^{N-1}} \cdot M_{N,\omega} = \mathbf{I}_N$  holds.

$$\left(\frac{1}{N}M_{N,\omega^{N-1}} \cdot M_{N,\omega}\right)_{i,j} = \frac{1}{N} \sum_{k=0}^{N-1} (\omega^{N-1})^{ik} \omega^{jk} = \frac{1}{N} \sum_{k=0}^{N-1} (\omega^{ikN}) \omega^{k(j-i)} =$$

$$= \frac{1}{N} \sum_{k=0}^{N-1} \omega^{k(j-i)} = \begin{cases} 1, & \text{if } i = j \\ 0, & \text{otherwise} \end{cases}$$

where in the case  $i \neq j$  we are using the geometric sum property:

$$\frac{1}{N} \sum_{k=0}^{N-1} \omega^{k(j-i)} = \frac{1}{N} \cdot \frac{\omega^{N(j-i)} - 1}{\omega^{j-i} - 1} = \frac{1}{N} \cdot \frac{1-1}{\omega^{j-i} - 1} = 0$$

This property will make the inverse matrix easy to compute and will allow the algorithms for interpolation and evaluation to be very similar.

# 4.2.3. The radix-2 DIT algorithm

Let's now think about the algorithm for the evaluation. See that we can decompose the step of evaluating a polynomial into:

$$\begin{vmatrix}

A^{[0]}(x) \coloneqq a_0 + a_2 x + a_4 x^2 + \dots + a_{N-2} x^{\frac{N}{2}-1} \\

A^{[1]}(x) \coloneqq a_1 + a_3 x + a_5 x^2 + \dots + a_{N-1} x^{\frac{N}{2}-1}

\end{vmatrix} \implies A(x) = A^{[0]}(x^2) + x A^{[1]}(x^2)$$

which basically gives us a recursive case we can use in our program.

The algorithm given by this recursion is expressed in pseudo-code in Listing 4.1. The function NTT takes as inputs the vector of N coefficients a and a value  $\omega$  and computes the evaluation of a at the powers of  $\omega$ . As we have said, in this case  $\omega$  will be the Nth root of unity in  $\mathbb{F}$ .

The steps of the algorithm are:

- 1. Base case: if N (which is equal to the size of a) is 1, the algorithm returns a because the polynomial is just the constant term.

- 2. Otherwise we store the even coefficients of a into vector  $a^{[0]}$  and the odd ones into  $a^{[1]}$ .

- 3. Then, we call the NTT with vectors  $a^{[0]}$  and  $a^{[1]}$  with a value of  $\omega^2$  and we store it into  $c^{[0]}$  and  $c^{[1]}$  respectively. This means that  $c^{[i]} = A^i(\omega^2)$   $i \in \{0,1\}$ .

- 4. We create a new vector c of N elements which will hold the result of the function i.e.  $c_i = A(\omega^i)$   $i \in \{0, ..., N-1\}$ . Each element is obtained with

linear combinations of  $c^{[0]}$  and  $c^{[1]}$  and some powers of  $\omega$  which we will call **twiddle factors**. More concretely, the code is using the following equalities:

$$\begin{split} &A(\omega^k) = A^{[0]}(\omega^{2k}) + \omega^k A^{[1]}(\omega^{2k}) \\ &A(\omega^{k+\frac{N}{2}}) = A^{[0]}(\omega^{2k}\omega^N) + \omega^{k+\frac{N}{2}}A^{[1]}(\omega^{2k}\omega^N) = A^{[0]}(\omega^{2k}) + \omega^{k+\frac{N}{2}}A^{[1]}(\omega^{2k}) \end{split}$$

This last step is performed inside the for shown in the pseudocode.

Listing 4.1: Pseudo-code for evaluating a at N powers of  $\omega$ .

Therefore, we have an algorithm that allows us to evaluate a polynomial in adequate points with a complexity of  $O(N \log N)^4$ . The algorithm for interpolation is very similar to the one we have seen here (see Proposition 1). Thus, by looking at diagram 4.3 we now can do evaluation, interpolation and multiplication in  $O(N \log N)$ .

# 4.2.4. Generic algorithm

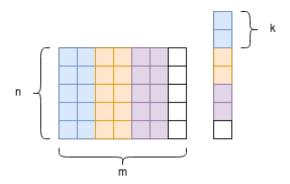

The algorithm described above corresponds to the simplest case of the **Cooley-Tukey algorithm**[21], where in each recursive call we divide the NTT in two smaller NTTs with half the size of the original one<sup>5</sup>. The more general case considers splitting  $N = N_1 N_2$  and doing the following steps (see Figure 4.4):

- 1. Reorganize the elements of the coefficient vector into a  $N_2 \times N_1$  matrix.

- 2. Perform  $N_1$  simultaneous NTTs with a vector size of  $N_2$  (input data considered as a  $N_2 \times N_1$  matrix).

- 3. Multiply the resulting data, considered as a  $N_2 \times N_1$  matrix, by the corresponding twiddle factors and transpose the resulting matrix into a  $N_2 \times N_1$  matrix.

<sup>&</sup>lt;sup>4</sup>We will not see it here but it can be easily obtained by applying the master theorem for analysis of algorithms.

<sup>&</sup>lt;sup>5</sup>This is the reason we took N to be a power of 2.

4. Perform  $N_2$  simultaneous  $N_1$ -point NTTs on the resulting  $N_1 \times N_2$  matrix.

Usually,  $N_1$  or  $N_2$  are a small value which we will call the **radix**. If  $N_1$  is the radix we are performing a **Decimation In Time (DIT)** and otherwise, it is a **Decimation In Frequency (DIF)**. For example, in the previous code 4.1 we were doing a **radix-2 DIT**.

$$a = [a_0, a_1, \dots, a_{N_1 N_2 - 1}] \xrightarrow{\text{Reorganize elements}} \begin{bmatrix} \downarrow & \downarrow & \downarrow \\ a_0 & \dots & a_{N_1 - 1} \\ a_{N_1} & \dots & a_{2N_1 - 1} \end{bmatrix}$$

$$\vdots & \ddots & \vdots \\ a_{(N_2 - 1)N_1} & \dots & a_{N_2 N_1 - 1} \end{bmatrix}$$

$$\xrightarrow{N_1 \text{ NTTs with } \omega^{N_1}} \begin{bmatrix} c_0^{[0]} & \dots & c_1^{[N_1 - 1]} \\ c_1^{[0]} & \dots & c_1^{[N_1 - 1]} \\ \vdots & \ddots & \vdots \\ c_{N_2 - 1}^{[0]} & \dots & c_{N_2 - 1}^{[N_1 - 1]} \end{bmatrix}$$

$$\xrightarrow{\text{Transpose} +} \xrightarrow{\text{Twiddle factors}} \begin{bmatrix} \downarrow & \downarrow & \downarrow \\ c_0^{[0]} & c_1^{[0]} & \dots & c_{N_2 - 1}^{[0]} \\ c_0^{[1]} & \omega^{N_1 - 1} c_1^{[1]} & \dots & \omega^{N_2 - 1} c_{N_2 - 1}^{[1]} \\ \vdots & \vdots & \ddots & \vdots \\ c_0^{[N_1 - 1]} & \omega^{N_1 - 1} c_1^{[N_1 - 1]} & \dots & \omega^{(N_1 - 1)(N_2 - 1)} c_{N_2 - 1}^{[N_1 - 1]} \end{bmatrix}$$

$$\xrightarrow{N_2 \text{ NTTs with } \omega^{N_2}} \begin{bmatrix} c_0 & \dots & c_{N_2 - 1} \\ c_{N_2} & \dots & c_{2N_2 - 1} \\ \vdots & \ddots & \vdots \\ c_{(N_1 - 1)N_2} & \dots & c_{N_1 N_2 - 1} \end{bmatrix}$$

Figure 4.4: Diagram for the NTT with an input vector of  $N = N_1 N_2$  elements.

For completeness, we are going to show the correctness of the twiddle factors found in Figure 4.4 for the NTT:

**Proposition 2.** The twiddle factor that multiplies  $c_j^{[k]}$  after performing the first NTT is  $\omega^{jk}$ .

*Proof.* We want to see that after performing the second NTT (which evaluates vectors on powers of  $\omega^{N_2}$ ) on  $\omega^{jk}c_j^{[k]}$ , coefficient  $c_{iN_2+j}$  will have the evaluation of

A in  $\omega^{iN_2+j}$ . We will also use the fact that  $c_j^{[k]}$  is the result of performing an NTT with  $\omega^{N_1}$  on the vector of coefficients a:

$$c_{iN_2+j} \stackrel{?}{=} \sum_{k=0}^{N_1-1} \omega^{iN_2k} (\omega^{jk} c_j^{[k]}) = \sum_{k=0}^{N_1-1} \omega^{(iN_2+j)k} \sum_{l=0}^{N_2-1} \omega^{jlN_1} a_{k+lN_1}$$

Now, we use the fact that in  $\mathbb{F}$  we have the identity  $\omega^N = \omega^{N_1 N_2} \equiv 1 \mod p$  to add some powers of  $\omega^{N_1 N_2}$  that do not alter the value of the previous equation:

$$\begin{split} \sum_{k=0}^{N_1-1} \omega^{(iN_2+j)k} \sum_{l=0}^{N_2-1} \omega^{jlN_1+liN_1N_2} a_{k+lN1} &= \sum_{k=0}^{N_1-1} \sum_{l=0}^{N_2-1} \omega^{(iN_2+j)(k+lN_1)} a_{k+lN1} \\ &= \sum_{l=0}^{N_2-1} \sum_{k=0}^{N_1-1} \omega^{(iN_2+j)(k+lN_1)} a_{k+lN1} \end{split}$$

And we finally do the following change of variable  $s = k + lN_1$  that gives us the result we were looking for:

$$\sum_{s=0}^{N_1 N_2 - 1} \omega^{(iN_2 + j)s} a_s = A(\omega^{iN_2 + j})$$

Therefore, we have seen that:

$$A(\omega^{iN_2+j}) =: c_{iN_2+j} = \sum_{k=0}^{N_1-1} \omega^{(iN_2+j)k} c_j^{[k]}$$

where

$$i = 0, ..., N_1 - 1$$

and  $j = 0, ..., N_2 - 1$ .

## 4.2.5. Hardware design

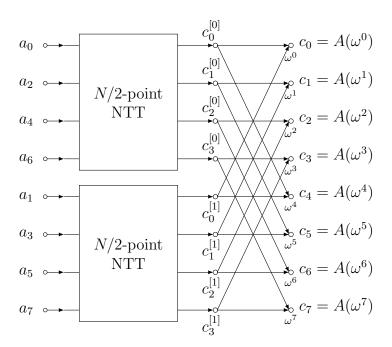

After giving all the mathematical background, we are now ready to design the hardware implementation. The initial idea would be to just translate the code given in Listing 4.1 into its hardware equivalent. This is the idea that is used in the butterfly diagram<sup>6</sup> shown in Figure 4.5.

In the picture we can see an 8-input NTT that uses the 2-radix recursive algorithm by decomposing the problem into two  $\frac{N}{2} = 4$  NTTs. In hardware, the lines in the figure would be translated into wires and on the ones that have a power of  $\omega$  next to them, we would add a multiplier to perform the operation. Then, we would follow the exact same strategy to do the 4-point NTT, then the one with 2 elements and finally the one with just 1 (the base case of the recursion).

<sup>&</sup>lt;sup>6</sup>It is called butterfly diagram because its shape is thought to resemble a butterfly.

Figure 4.5: Butterfly diagram for an 8-point NTT. Adapted from [22].

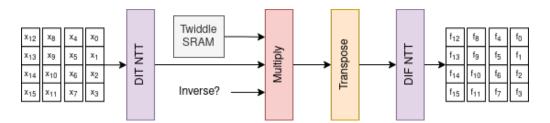

This is a very common implementation of the NTT. However, if the input size gets too large, it is no longer feasible to implement it like this. One answer to this problem was proposed in the paper FFTs in External or Hierarchical Memory by David H. Bailey ([23]). It essentially consists on using the generic case of the algorithm we showed in the previous section where instead of directly computing the NTT it is split into 4 steps: perform  $N_1$   $N_2$ -point NTTs, multiply the results by the corresponding twiddle factors, transpose it and compute  $N_2$   $N_1$ -point NTTs.

This implementation of the NTT was done in F1: A Fast and Programmable Accelerator for Fully Homomorphic Encryption [24]. In the paper, the idea is to implement an N-point NTT as a composition of smaller E element NTTs, where E is the number of vector lanes in the accelerator. In Figure 4.6 there is an example on how to implement a 16-point NTT by using 4-point NTTs (E = 4 and it is analogous to using  $N_1 = N_2 = 4$  in the previous section).

Figure 4.6: Four-step NTT datapath that uses 4-point NTTs to implement 16-point NTTs. Adapted from [24].

Even though this implementation of the NTT adds a multiplication (in red in Figure 4.6) to the algorithm, it has other advantages besides allowing bigger NTT sizes. For one, it produces an ordered NTT but it also grants the option of performing an INTT using the same pipeline by modifying the contents in the Twiddle SRAM as explained in [24].

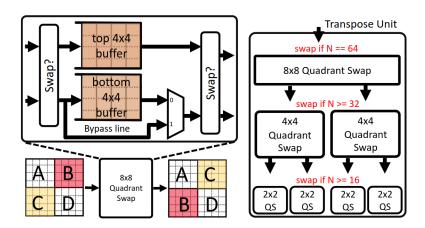

Another important unit in this pipeline is the one that is used for transposing a matrix of size  $E \times E$ . This unit can be implemented by using the identity:

$$\left[\begin{array}{c|c} A & B \\ \hline C & D \end{array}\right]^T = \left[\begin{array}{c|c} A^T & C^T \\ \hline B^T & D^T \end{array}\right]$$

Then the idea is to have a *quadrant-swap* unit (left of Figure 4.7) of size  $K \times K$  that follows three steps, where each of them takes K/2 cycles. In cycle i:

- 1. First step: read A[i] and C[i] and store them in top[i] and bottom[i], respectively.

- 2. Second step: read B[i] and D[i]. Activate the first swap MUX so that D[i] is stored in top[i] and A[i] is outputed. Activate also the bypass line to output B[i] as well.

- 3. Third step: output D[i] from top[i] and C[i] and activate the second swap MUX so that they are correctly ordered (C[i] on top).

The benefits of using this design is that it is fully pipelined because steps 1 and 3 can be done in parallel and it can be used for all values of N by bypassing some of the initial quadrant swaps (where  $N = G \times E$  and with power-of-2 G < E). The structure of the full unit for E = 8 can be found in Figure 4.7.

Figure 4.7: Transpose unit for an  $8 \times 8$  matrix (right) and its component quadrant-swap unit (left). From [24].

## 4.3. Matrix vector multiplication

The other costly step in the computation is a dense matrix vector multiplication. One of the key facts is that the matrix is generated from a seed and, therefore, we do not need to load it from memory. First we will explain the naïve way to do a matrix-vector multiplication and then we are going to explain how to make it more memory-friendly.

## 4.3.1. Naïve algorithm

Suppose we want to multiply a matrix A with size  $n \times m$  by a vector b with length m to obtain a new vector c of length n:

$$A \cdot b = \begin{bmatrix} a_{0,0} & \cdots & a_{0,m-1} \\ \vdots & \ddots & \vdots \\ a_{n-1,0} & \cdots & a_{n-1,m-1} \end{bmatrix} \cdot \begin{bmatrix} b_0 \\ \vdots \\ b_{m-1} \end{bmatrix} = \begin{bmatrix} a_{0,0}b_0 + \cdots + a_{0,m-1}b_{m-1} \\ \vdots \\ a_{n-1,0}b_0 + \cdots + a_{n-1,m-1}b_{m-1} \end{bmatrix} =: c$$

The coefficients of c can be computed as

$$c_i = \sum_{j=0}^{m-1} a_{i,k} b_j$$

and that means that the intuitive algorithm to implement it would be the one expressed in Listing 4.2.

```

MVM(A,b) {

n = nrows(A);

m = nrows(b);

vector c(n,0);

for (i = 0; i < n; ++i) {

for (j = 0; j < m; ++j) {

c[i] += A[i][j]*b[j];

}

}

return c;

}</pre>

```

Listing 4.2: Intuitive pseudo-code for computing a matrix vector multiplication.

Though this algorithm might be fine if n and m are small, it becomes a problem with bigger computations. The reason for that is that the contents of the vector and the matrix loaded from memory can be spilled if they occupy more space than the one supplied by the registers or the cache used to hold these values. It also does not benefit from the possibilities of having more than one core in the processor. Therefore, the computation can be improved when taking the underlying hardware into account.

## 4.3.2. Tiling

To improve the performance of the pseudo-code seen before, we will rely on these concepts:

- Data reuse: it consists on efficiently using data that is already in a fast-access level of the memory hierarchy (for example, the registers or the cache). The issue with this kind of memories is that often they are not big enough to hold all date necessary for the computation. Thus, the objective is to be able to use the data as much as possible (following the code guidelines) before returning it to memory to make space for other elements.

- Data locality: data is typically retrieved from memory in groups or blocks of elements. Hence, it is important to consider how is the data stored in memory and strive to access consecutively the elements that are in the same block (which is similar to element-wise data reuse but on a block level). This approach minimizes the need to repeatedly retrieve the entire block from memory.

- Exploiting parallelism: in a processor there are often different cores or functional units that can be used in parallel. To improve performance it is key to have an adequate data distribution and load balancing among them.

In our case, the computation we are performing is a matrix vector where the *matrix* is randomly generated from a seed. Therefore, the data we will need for the computation are the elements from the vector and the seed to generate the matrix. We will also need space to store the temporary multiplication results before returning them to memory.

Observe that each element of the matrix only needs to be used once. Thus it is not necessary to store the randomly generated value after its initial use. This is not the case for the vector elements, as each one multiplies each value in a matrix column. Consequently, the idea is to compute partial results of the resulting vector c by computing the multiplication of a block or tile of k elements of vector b and its corresponding A columns. This idea is conveyed in Figure 4.8, where the program should first compute the result of multiplying the first k=2 elements of vector b by the first two columns of matrix a. Then, it should load the next a0 elements of a1 (overwriting the previous ones if necessary, as they are no longer needed) and accumulate the results of the new multiplication. By executing the program this way, we would avoid unnecessarily reading the vector more than once.

Note also that by doing this it is also possible to distribute the computation between several different cores/units. Each one would receive the computation of one or more tiles and the only thing that it is needed to do at the end is to sum the results coming from the different cores.

Figure 4.8: Example of tiling in a matrix vector multiplication.

By doing these steps we would achieve a much better use of the resources available because we would avoid unnecessary loads from memory and use all the cores/units available.

As a curiosity, an example on how a program is coded influences the performance of it is brought up in the article *There's plenty of room at the Top: What will drive computer performance after Moore's law?* ([25]).In the article they compare the performances obtained from running a code that computes a the multiplication of two 4096-by-4096 matrices. First they show that by changing the programming language used (Python, Java or C) we can get an execution time that is 47 times faster. And not only that, an even more impressive gain can be obtained from tailoring the code to the specific features of the hardware by using its 18 cores (version 4), exploiting the memory hierarchy (version 5), vectorizing the code (version 6) and using the Intel's special intructions (version 7). As it can be seen the absolute speedup is incredible!

| Version | Implementation              | Running time (s) | GFLOPS  | Absolute speedup | Relative speedup | Fraction of peak (%) |

|---------|-----------------------------|------------------|---------|------------------|------------------|----------------------|

| 1       | Python                      | 25,552.48        | 0.005   | 1                | _                | 0.00                 |

| 2       | Java                        | 2,372.68         | 0.058   | 11               | 10.8             | 0.01                 |

| 3       | С                           | 542.67           | 0.253   | 47               | 4.4              | 0.03                 |

| 4       | Parallel loops              | 69.80            | 1.969   | 366              | 7.8              | 0.24                 |

| 5       | Parallel divide and conquer | 3.80             | 36.180  | 6,727            | 18.4             | 4.33                 |

| 6       | plus vectorization          | 1.10             | 124.914 | 23,224           | 3.5              | 14.96                |

| 7       | plus AVX intrinsics         | 0.41             | 337.812 | 62,806           | 2.7              | 40.45                |

Figure 4.9: Speedups from performance engineering a program that multiplies two 4096-by-4096 matrices. Absolute speedup is time relative to Python, and relative speedup, which is shown with an additional digit of precision, is time relative to the preceding line. Fraction of peak is GFLOPS relative to the computer's peak 835 GFLOPS. From [25].