# Heterogeneous Programming Using OpenMP and CUDA/HIP for Hybrid CPU-GPU Scientific Applications

Journal Title

XX(X):1–18

©The Author(s) 0000

Reprints and permission:

sagepub.co.uk/journalsPermissions.nav

DOI: 10.1177/ToBeAssigned

www.sagepub.com/

SAGE

#### Marc González and Enric Morancho

#### Abstract

Hybrid computer systems combine compute units (CUs) of different nature like CPUs, GPUs and FPGAs. Simultaneously exploiting the computing power of these CUs requires a careful decomposition of the applications into balanced parallel tasks according to both the performance of each CU type and the communication costs among them. This paper describes the design and implementation of runtime support for OpenMP hybrid GPU-CPU applications, when mixed with GPU-oriented programming models (e.g.: CUDA/HIP). The paper describes the case for a hybrid multi-level parallelization of the NPB-MZ benchmark suite. The implementation exploits both coarse-grain and fine-grain parallelism, mapped to compute units of different nature (GPUs and CPUs). The paper describes the implementation of runtime support to bridge OpenMP and HIP, introducing the abstractions of *Computing Unit* and *Data Placement*. We compare hybrid and non-hybrid executions under state-of-the-art schedulers for OpenMP: static and dynamic task schedulings. Then, we improve the set of schedulers with two additional variants: a memorizing-dynamic task scheduling and a profile-based static task scheduling. On a computing node composed of one AMD EPYC 7742 @ 2.250GHz (64 cores and 2 threads/core, totalling 128 threads per node) and 2 x GPU AMD Radeon Instinct MI50 with 32GB, hybrid executions present speedups from 1.10x up to 3.5x with respect to a non-hybrid GPU implementation, depending on the number of activated CUs.

#### Keywords

Heterogeneous Programming, Hybrid CPU-GPU, OpenMP, CUDA, HIP

#### Introduction

Hybrid computing systems have become the widest spread solution within the High Performance Computing (HPC) domain. Hybrid systems combine computing units (CUs) of different nature and computational power, for instance CPUs, GPUs and FPGAs. Given the impressive computing power delivered by these architectures, significant efforts have been devoted to port applications from many computing domains to this type of HPC systems. Machine Learning, BioInformatics, Scientific Computing and many more have clear examples of representative applications like TensorFlow (Abadi et al. 2015), Caffe (NVIDIA 2020), Smith-Waterman (Manavski and Valle 2008), Alya (Giuntoli et al. 2019) that recently developed the support for GPU-based systems.

Hybrid systems are programmed with language extensions to general-purpose programming languages such as C/C++ and Fortran. Nvidia's CUDA, AMD's HIP, OpenCL, OpenACC and OpenMP are reference programming models for heterogeneous computing that follow this approach. In general, all these programming frameworks focus on the essential actions for porting an application to a hybrid architecture: memory allocation, data transfers between CUs that now operate within a distributed memory address space, and the specification of those computations to be offloaded to GPU-based CUs and those to be executed by CPU-based CUs. OpenMP includes many language constructs to guide all these aspects.

Hybrid applications simultaneously exploit fine and coarse levels of parallelism. This requires the definition of memoryallocation strategies per each device, work-distribution schemes aware of the different nature of the CUs to balance the work execution, and communication phases whenever is necessary to exchange values between the CUs that reside in different memory spaces. In particular, OpenMP has evolved with new features so that all of these aspects are reasonably supported through specific constructs and practices. Nevertheless, most of this support focuses on the sole utilization of the OpenMP programming model, not addressing the fact that many applications now have been ported to GPU-based systems using other programming models such as CUDA or HIP. OpenMP has to be able to reasonably support too the interoperability with these defacto heterogeneous programming standards. Both CUDA/HIP runtime systems define very similar interfaces to operate with GPU devices. The main functionalities that need to be addressed are how computations are offloaded to the devices, how memory is allocated into devices and mirrored with host memory, and how data is transferred from/to devices and host. All of these aspects are supported by a set of runtime primitives included in CUDA/HIP that require

Computer Architecture Department, Universitat Politècnica de Catalunya-BarcelonaTECH, Barcelona, Spain

# Corresponding author:

Marc González, marc@ac.upc.edu

the specification of how to interoperate with the OpenMP execution model.

Mixing CUDA/HIP and OpenMP is a common practice (Yang et al. 2011, 2021; Corni et al. 2016; Jacobsen and Senocak 2013; Guan et al. 2013). In this context, the threading level is utilized to activate several devices, having one or more threads responsible for: device memory allocation, data transfers and kernel offloading. But if this approach is extended to simultaneously activate both the CPU and GPU cores, then programmers have to face significant programming limitations. Essentially, programmers have to manually introduce code responsible for an appropriate work distribution that adapts to the inherent differences of CPU/GPU compute power, and to distribute data among the host and device memory spaces according to the work distribution. All of this has been observed in previous works where specific work-distribution mechanisms are described for hybrid architectures (Mittal and Vetter 2015; Belviranli et al. 2013; Choi et al. 2013; Zhong et al. 2012; Zhang et al. 2021; Gowanlock 2021).

In this context, the challenge of simultaneously activating both CPUs and GPUs is essentially limited by the interoperability of OpenMP with CUDA/HIP. The main contribution of this paper is the design and implementation of a runtime system support to improve the interoperabilty of OpenMP and CUDA/HIP. We introduce two main abstractions build on top of the OpenMP programming model: Computing Unit and Data Placement. Using the proposed runtime system, we describe how to effectively mix OpenMP and AMD's HIP to achieve a multi-level parallelization of the NPB-MZ benchmark suite where both the CPU an GPU cores execute simultaneously. We evaluate its performance in a computing node composed of one AMD EPYC 7742 @ 2.250GHz (64 cores and 2 threads/core, totalling 128 threads per node) and 2 x GPU AMD Radeon Instinct MI50 with 32GB. Hybrid configurations present speedups from 1.08x up to 3.18x with respect to a non-hybrid GPU configuration, depending on the number of activated CUs.

This paper is organized as follows: Section describes the NPB-MZ benchmark suite and points out its sources of parallelism. Section details the design and implementation of the runtime support for OpenMP hybrid applications. Section depicts how the runtime support is used to achieve a hybrid implementation of the NPB-MZ benchmark suite. Section evaluates the performance of our hybrid implementation. Section discusses related works and, finally, Section concludes the paper.

# Benchmark characterization

#### NAS Parallel Benchmarks

The NAS Parallel Benchmark (NPB) (Bailey et al. 1991) suite provides the implementation of different benchmarks for several programming languages (Fortran, C, ...) and parallel paradigms (OpenMP, MPI, ...). The suite defines several input classes for each benchmark; classes S, W, A, B,... determine a sequence of increasing input sizes. Finally, to verify the result of the benchmarks, NPB gives the expected result for each class. The original NPB benchmark suite consisted of eight benchmarks: five kernels and three

pseudo-applications. In this work we focus just on the three pseudo applications: BT (Block Tri-diagonal solver), LU (Lower-Upper Gauss-Seidel solver) and SP (Scalar Pentadiagonal solver).

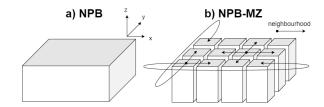

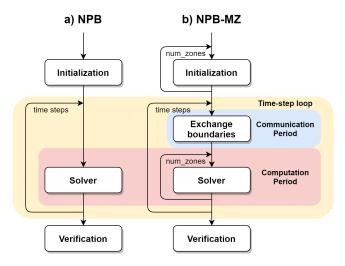

BT, LU and SP traverse a 3D volume (Figure 1-a) to compute discrete solutions of the Navier-Stokes equations. Figure 2-a shows the flow graph of NPB benchmarks. The main loop, the time-step loop, applies a benchmark-specific solver on every iteration.

**Figure 1.** 3D Volume: a) NPB, b) NPB-MZ, example  $4 \times 3$  tiling into 12 zones and neighbourhood relation between zones.

Figure 2. Flow graphs: a) NPB and b) NPB-MZ.

The Multi-Zone NPB (NPB-MZ) (der Wijngaart and Jin 2003) re-implement NPB to expose a coarse level of parallelism. To that end, the 3D input volume is tiled through both x and y dimensions producing a grid of prisms (known as *zones*, Figure 1-b) that can be processed in parallel.

However, the correct values of the border faces of each zone also depend on the values of the border faces of its neighbour zones. So, between two iterations of the timestep loop, an *exchange-boundaries* procedure must update the border faces of all zones.

Figure 2-b shows the flow graph of NPB-MZ benchmarks. Each time-step iteration must call the exchange-boundary procedure before applying the solver to all zones (potentially in parallel).

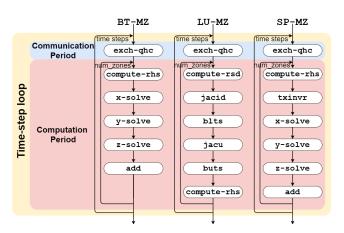

Consequently, each time-step iteration can be divided into two periods: the *Communication Period*, devoted to transfer zone faces, and the *Computation Period*, devoted to update zones. Figure 3 details the sequence of high-level procedures called at each iteration.

Table 1 depicts the characterization of NPB-MZ benchmarks. For each input class, the table details the overall size, the number of zones, the zone size and the number of time steps of each benchmark. Notice some differences

| Input | 3D volume                      | Memory        | Num. 2       | zones $(x \times y)$ | Zone size (points per zone) |         |                          | Time steps |     |     |

|-------|--------------------------------|---------------|--------------|----------------------|-----------------------------|---------|--------------------------|------------|-----|-----|

| Class | $x \times y \times z$ (points) | (GB)          | LU           | SP & BT              | LU                          | SP      | BT                       | LU         | SP  | BT  |

| В     | $304 \times 208 \times 17$     | $\approx 0.2$ | $4 \times 4$ | $8 \times 8$         | 67 184                      | 16 786  | from 2 992 to 59 976     | 250        | 400 | 200 |

| C     | $480 \times 320 \times 28$     | $\approx 0.8$ | $4 \times 4$ | $16 \times 16$       | 268 800                     | 16 800  | from 2 912 to 60 648     | 250        | 400 | 200 |

| D     | $1632 \times 1216 \times 34$   | ≈ 13          | $4 \times 4$ | $32 \times 32$       | 4 217 088                   | 65 892  | from 11 968 to 243 236   | 300        | 500 | 250 |

| Е     | $4224 \times 3456 \times 92$   | $\approx 250$ | $4 \times 4$ | $64 \times 64$       | 83 939 328                  | 327 888 | from 59 248 to 1 203 452 | 300        | 500 | 250 |

**Table 1.** Characterization of NPB-MZ benchmarks: overall size (number of points and memory requirements) and, for each benchmark, number of zones, zone size and number of time steps.

among the benchmarks that will be relevant in order to understand the performance of the hybrid implementations of the benchmarks:

- In LU, the number of zones is always 16, independently on the input class. For each input class, zone sizes are uniform.

- In SP, the larger the input class, the larger the number of zones. Like in LU, zone sizes are uniform at each input class; however, SP zones are smaller than LU zones.

- In BT, like in SP, the larger the input class, the larger the number of zones. However, zone sizes are not uniform; for each input class, the ratio between the size of the biggest zone and the size of the smallest zone is about 20×.

**Figure 3.** Time-step loop of NPB-MZ benchmarks. Sequence of procedures called at each iteration of the time-step loop.

# Sources of parallelism

The NPB-MZ suite exposes several levels of parallelism. Its main difference with respect to NPB is the exposure of a new parallelism level, the *inter-zone* parallelism. It can be exploited in the *Computation Period* by the parallel processing of zones through several Computing Units (i.e., CPU's and GPU's). Moreover, NPB-MZ also exposes an *intra-zone* parallelism in both periods while processing each individual zone. It can be exploited by several parallelization techniques (i.e., multi-threading, vectorization and porting to GPU). The following subsections describe these parallelism levels.

#### Computation period: Inter-zone Parallelism

Figure 4 shows the skeleton of the time-step loop of the NPB-MZ applications. The *Computation Period* is implemented by a loop that traverses the zones and processes

```

for (step=0; step < num_steps; step++) {</pre>

/* BORDER EXCHANGE */

exch qbc(...);

/* ZONE PROCESSING */

for (zone=0 ; zone < num_zones; zone++) {</pre>

comp_phase_1 (...);

comp_phase_2 (...);

comp_phase_N (...);

} /* zone loop */

} /* Time step loop */

void comp_phase_N(...) {

/* Loop NEST 1 */

for (k=0; k < zdim; k++)

for (j=0; j < ydim; j++)</pre>

for (i=0; i < xdim; i++) {</pre>

/* MATRIX BASED COMPUTATION */

/* Loop NEST 2 */

for (k=0; k < zdim; k++)

for (j=0; j < ydim; j++)</pre>

for (i=0; i < xdim; i++) {</pre>

/* MATRIX BASED COMPUTATION */

}

```

**Figure 4.** Time step loop for the NPB-MZ benchmark suite. Border elements of zones are computed in function *exch-qbc*. Zones are processed sequentially by means of a series of computational phases where each one contains several loop nests that perform matrix-based computations.

them. As processing a zone is independent of processing the other zones, the exploitation of *inter-zone* parallelism implies the parallelization of this loop.

# Computation period: Intra-zone Parallelism

Figure 4 depicts that each computational phase calls a subroutine with several loop nests that implement the computation for one zone and a computational phase. The *intra-zone* parallelism corresponds to the exploitation of the parallelism exposed by these loop nests. These loops can be annotated with OpenMP directives or transformed to device kernels.

# Communication period: Intra-zone Parallelism

Figure 5 shows the code skeleton for the exchange of boundary values. In this period, zones are processed sequentially, so no inter-zone parallelism exists. However, processing each zone exposes some *intra-zone* parallelism. The computations are organized in the form of *memcpy* operations that pack/unpack border elements into temporary buffers (copy\_face function) and then these are exchanged

```

/* EXCH OBC */

for (zone=0; zone < num_zones; zone++) {</pre>

east = adjacency east[zone];

north = adjacency_north[zone];

copy_face(tmpEast, mesh[east], "IN",...);

copy_face(tmpNorth, mesh[north], "IN",...);

compute_border(mesh[zone], tmpEast, tmpNorth,...);

copy_face(tmpEast, mesh[east], "OUT" ...);

copy_face(tmpNorth, mesh[north],"OUT",...);

} /* zone loop */

void copy face(...) {

for (k=0; k < dim; k++)

for (j=0; j < dim; j++) {</pre>

/* MATRIX BASED COMPUTATION */

}

void compute_border(...) {

for (k=0: k < dim: k++)

for (j=0; j < dim; j++) {</pre>

/* MATRIX BASED COMPUTATION */

}

```

Figure 5. Computation of border elements for each zone. Zones are processed sequentially by means of a sequence of memcpy operations (copy\_face function) that pack/unpack border elements to temporary buffers. The buffers are exchanged between adjacent zones (compute\_border function).

between adjacent zones (compute\_border function). These computations are implemented as parallelizable loop nests that can be annotated with OpenMP directives or transformed into device kernels.

# Hybrid parallelization

Figures 6 and 7 depicts the parallel host and device code schemes for the NPB-MZ benchmark suite. The inter-zone parallelism is easily exploited by annotating the loop that traverses zones with an OpenMP *parallel for* directive. Exploiting intra-zone parallelism depends on the nature of the CUs: for CPU-based CUs, by means of additional OpenMP directives that parallelize loop nests within the different phases of zone processing; for GPU-based CUs, these loop nests must be transformed into kernel functions.

To simultaneously activate both devices and host, the codes in Figures 6 and 7 need additional support to identify whether an OpenMP thread corresponds to a CPU-based or to a GPU-based CU. In the context of hybrid executions, nested parallelism requires associating threads in an outer level of parallelism to a subset of the computational resources (i.e. a compute unit). Therefore, when these threads generate the inner level of parallelism, a decision has to be taken regarding whether this parallelism has to be mapped to device or host cores. We define that a thread diverges to a host compute unit if it deploys the inner level of parallelism to a host compute unit. Similarly, a thread diverges to a device compute unit if it offloads the inner level of parallelism to a device. This support is not available in

the current specification of OpenMP 5.2 and neither exists in Nvidia's CUDA nor AMD's HIP runtime specifications. One main contribution of this paper is the design and implementation of the missing runtime support to effectively merge OpenMP with CUDA or HIP. Notice that new features in OpenMP like contexts, traits and meta-directives could be used to parallelize the loop nests using solely OpenMP directives. But these do not solve the problem of determining if a thread in the outermost level of parallelism (e.g.: inter-zone parallelism) has to be diverged to a GPU or CPU version for the innermost parallelism (e.g.:intrazone parallelism). Even with meta-directives, OpenMP does not define what should be the association between threads and devices. Only a manual solution performed by the programmer can solve this limitation. Notice too that this association is essential for the work distribution to be applied between threads executing the outermost parallelism. In addition, if the application already is coded using CUDA or HIP primitives (e.g.: memory allocation, data transfers and kernel offloading), the programmer might want to utilize this version of the code but combined with OpenMP.

```

for (step=0; step < num_steps; step++) {</pre>

/* BORDER EXCHANGE */

exch_qbc(...);

/* ZONE PROCESSING */

#pragma omp parallel for /* Inter-zone parallelism */

for (zone=0; zone < num_zones; zone++) {</pre>

comp_phase_1 (...);

comp_phase_2 (...);

comp_phase_N (...);

} /* zone loop */

} /* Time step loop */

void comp_phase_N(...) {

#pragma omp parallel for /* Intra-zone parallelism */

for (k=0; k < zdim; k++)

for (j=0; j < ydim; j++)

for (i=0; i < xdim; i++) {</pre>

/* MATRIX BASED COMPUTATION */

#pragma omp parallel for /* Intra-zone parallelism */

for (k=0; k < zdim; k++)

for (j=0; j < ydim; j++)</pre>

for (i=0; i < xdim; i++) {</pre>

/* MATRIX BASED COMPUTATION */

}

```

**Figure 6.** Multi-level OpenMP parallel code. Outermost level of parallelism (inter-zone) is exploited by means of an OpenMP directive that parallelizes the loop that traverses the zones. Innermost level of parallelism (intra-zones) is exploited by means of OpenMP annotations for the loop nests that implement the compute phases of zone processing.

Hybrid execution requires to manage different memory spaces, so memory allocation and placement requires some guidance from the programmer. Consequently, at the programming model level, the programmer needs some explicit support to indicate when to allocate memory, where to allocate and, if necessary, to change the placement of that

```

__global__ kernel_1_comp_phase_N(...) {

k = f_k(block grid);

j = f_j(block grid);

i = f_i(block grid);

/* MATRIX BASED COMPUTATION */

...

}

__global__ kernel_2_comp_phase_N(...) {

k = f_k(block grid);

j = f_j(block grid);

i = f_i(block grid);

/* MATRIX BASED COMPUTATION */

...

}

void comp_phase_N(...) {

kernel_1_comp_phase_N<<<grid, block, ... >>> (...);

kernel_2_comp_phase_N<<<grid, block, ... >>> (...);

}

```

**Figure 7.** Device code for exploiting innermost parallelism (intra-zone). Loop nests corresponding to compute phases of zone processing have been transformed into device kernels.

memory. In the context of Figures 6 and 7, the programmer must ensure that memory allocation and placement has happened prior any work is assigned to the OpenMP threads that will be diverged to CPU or GPU execution. But this is highly entangled with the work distribution applied among the hybrid execution flows. Similarly as with the computing unit abstraction, we need additional runtime support to make possible the appropriate policies for memory placement according to the work-distribution schemes.

Given the inherent difference in compute power between host and devices, new scheduling schemes are necessary. Current specification of OpenMP supports static and dynamic schedulers. In this paper we implement variants of those to address the eventual unbalance caused by the different compute power of CPU and GPU cores.

# Runtime support for OpenMP hybrid applications

This section describes the design of a runtime support that allows the programmer to develop hybrid OpenMP applications with CUDA/HIP. The design is divided into three runtime subsystems: a) *libCU-rtl* implements the necessary support to introduce the computing unit abstraction, b) *libPLACEMENT-rtl* implements the necessary support to manage with different address spaces, c) *libSCHEDULING-rtl* includes the implementation of additional scheduling schemes for hybrid applications.

The content of this section contributes to identify runtime primitives that can improve the overall programmability of hybrid OpenMP applications. It should be understood as a case of study for improvements in the OpenMP runtime support regarding the interoperability with GPU-oriented programming frameworks such as CUDA or HIP.

#### libCU-rtl

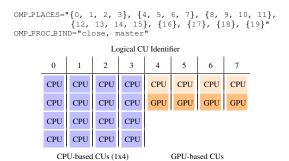

Computing units can be either CPU-based or GPU-based. For CPU-based CUs, they correspond to an aggregation of one or more CPUs. For instance, a CU can be formed with a pair of CPUs giving an organization that we identify as 1x2: 1 stands for one CU, the 2 identifies the number of CPUs in the CU. Similarly, CUs can be defined in the form of 1x4, 1x8 or whatever the CPU aggregation.

GPU-based CUs are defined only in the form of K+1 configuration where K CPUs are bounded to one GPU in order to orchestrate all actions over the GPU: memory allocation, data transfers and computation offloading. For this work, the most common usage cases have been covered with hybrid configurations in the following form: (N x M + G) CPUs where N stands for the number of CPU-based CUs executing with M CPUs, and G stands for the number of GPU-based CUs. All CPU-based CUs are composed of the same number of CPUs and GPU-based CUs are managed by solely one thread per GPU (e.g.: K=1). For these cases, a total number of NxM + G threads are necessary for execution.

Threads are created using the OpenMP programming directives. For thread-CU association, we rely on the thread affinity support already existing in OpenMP. The environment variables *OMP\_PROC\_BIND* and *OMP\_PLACES* control the thread affinity to the actual CPUs. Our CU runtime support relies on correctly setting these variables to ensure the particular thread-CU association that will allow the simultaneous activation of CPUs and GPUs.

**Figure 8.** Example of an 8 CUs organization: 4 CPU-based CUs composed each one of 4 CPUs, 4 GPU-based CUs composed of 1 CPU and 1 GPU. This configuration needs 20 physical CPUs. OpenMP thread binding is used to configure the thread-CU association. OpenMP variables *OMP\_PLACES* and *OMP\_PROC\_BIND* are set to achieve the desired configuration.

Figure 8 shows an 8-CU hybrid system, with 4 CPU-based CUs composed each one of 4 CPUs and 4 GPU-based CUs composed of 1 CPU and 1 GPU. This configuration needs a total number of 20 physical CPUs. Besides, the CPU aggregation is achieved by setting the two OpenMP environment variables that control affinity and thread binding to CPUs. OMP\_PLACES lists aggregation of physical CPU identifiers where threads are bounded to. These aggregations are named *places*. OMP\_PROC\_BIND describes how to interpret the content of OMP\_PLACES across nested levels of parallelism. Table 3 shows the appropriate values for these variables in a OpenMP compact form for some particular CU configurations.

| Signature    |               | Description                                                                             |

|--------------|---------------|-----------------------------------------------------------------------------------------|

| unsigned int | nCUS()        | Get the current number of active CUs.                                                   |

| unsigned int | nGPUS()       | Get the number of GPU-based CUs.                                                        |

| unsigned int | nCPUS()       | Get the number of CPU-based CUs.                                                        |

| ungigned int | nInnerCPUs()  | Get the number of CPUs contained in the CPU-based CU associated to the invoking thread. |

| unsigned inc |               | Returns 0 if thread corresponds to a GPU-based CU.                                      |

| bool         | isGPU(()      | Check if invoking thread is associated to a GPU-based CU.                               |

| bool         | isCPU()       | Check if invoking thread is associated to a CPU-based CU.                               |

| ungigned int | getGPUid()    | Get the device ID for the CU associated to the invoking thread.                         |

| unsigned inc |               | Returns error (-1) if the invoking thread is not associated to a GPU-based CU.          |

| unsigned int | co+CDII;d()   | Get the OpenMP thread ID for the CU associated to the invoking thread.                  |

| unsigned inc | gettroid()    | Returns (-1 limits::max) if the invoking thread is not associated to a CPU-based CU.    |

| unsigned int | getCUid()     | Get the CU ID, from 0 up to the number of CUs minus one.                                |

| void         |               | Synchronize with the device corresponding to the CU associated to the invoking thread.  |

| VOIG         | synchronize() | In case the CU corresponds to a CPU, no synchronization happens.                        |

Table 2. Runtime primitives of libCU-rtl

|                             | Configuration | OMP_PLACES            |

|-----------------------------|---------------|-----------------------|

| OpenMP<br>Thread<br>Binding | 1x2 + 4       | "{0:2}:1:1, {2}:4:1"  |

|                             | 1x4 + 1       | "{0:3}:1:1, {4}:1:1"  |

|                             | 4x2 + 1       | "{0:2}:4:2, {8}:1:1"  |

|                             | 7x2 + 2       | "{0:2}:7:2, {14}:2:1" |

|                             | 3x4 + 4       | "{0:4}:3:4, {12}:4:1" |

**Table 3.** Examples for OMP\_PLACES variable and thread binding control in hybrid execution using the OpenMP programming model.

Within the libCU-rtl, CUs are identified with integer numbers that range from 0 up to NCUS-1, where the NCUS correspond to the number of executing CUs. This is totally in accordance with how OpenMP identifies the threads that execute within the same parallel region. The OpenMP thread name space matches exactly the CU name space. Within the libCU-rtl, CPU-based CUs are identified from 0 up to NCPUS-1 where NCPUs is the number of of CPU-based CUs. GPU-based CUs are identified by numbers in the range [NCPUS, NCUS-1]. The CU name space is used to implement work-distribution schemes similarly to the OpenMP programming model.

Table 2 lists the runtime primitives implemented to operate with the CU abstraction within the OpenMP programming model. The primitives give support to the programmer to query the runtime system about the parameters of the hybrid execution: how many CUs are executing, how many of them correspond to CPU-based CUs, and how many of them correspond to GPU-based CUs. Also, there are primitives to get and set the CU identifier, and to translate from the CU identifier to the device identifier the thread is assigned to, and from the CU identifier to the OpenMP thread identifier in the case of CPU-based CUs. For GPU-based CUs there is a specific primitive to synchronize with the associated device. Section describes in detail how all these primitives have been used to code a hybrid version of the NPB-MZ benchmark suite.

# libPLACEMENT-rtl

OpenMP hybrid applications require additional runtime support to control the data sharing between the host and device address spaces e.g.: data sharing happens at system memory page level). Memory allocation and placement, and eventual data transfers have to be guided by the programmer in order to achieve satisfactory levels of performance.

For instance, CUDA runtime primitives to manage unified virtual memory allow programmers to provide hints for data placement and usage in computational kernels (González and Morancho 2021; NVIDIA 2023). For hybrid OpenMP applications, similar support is needed and should be available in accordance to the OpenMP conventions for parallelism exploitation. The role of the *libPLACEMENT-rtl* is to bridge the OpenMP programming model with the existing support to control the memory allocation, placement and if necessary, migration.

Guidance from the programmer is needed so that when a computation is assigned to a CU, the data associated to the computation is placed on the corresponding CU memory space. This requires memory allocation and, potentially, data migration prior the actual computation is executed. Usually, for hybrid applications, programmers introduce a pre-computed work distribution and memory allocation before any computation takes place. This happens in the initialization phases of the application. In contrast, the lib-PLACEMENT-rtl includes the necessary runtime support so that memory allocation, placement and migration can happen at any time of the execution.

Within the libPLACEMENT-rtl, memory spaces are identified with an integer value that ranges from 0 up to NAS-1, where NAS stands for the total number of memory spaces in use. Host address space is identified with value 0, and the devices' memory spaces are numbered from 1 up to the number of GPU-based CUs.

The main data structure for the libPLACEMENT-rtl is a map between key values and actual memory addresses belonging to any of the different address spaces. A key corresponds to a host memory address that identifies uniquely a memory region. Programmers can register memory regions using the primitive registerMem. Along the application execution, programmers can allocate, deallocate, copy and migrate memory regions using key values and CU identifiers that identify memory regions in a particular CU. The libPLACEMENT-rtl strictly gives support for this functionalities and no memory consistency mechanisms are supported. The replicas and actual state of data is totally under the programmer responsibility. The runtime distinguishes between memory placement and memory allocation. Memory regions only have one active placement, although they might have been allocated in several memory spaces. Only migration actions change the placement, while allocation or copy do not. Besides,

| Primitive      |                                           | Description                                                               |

|----------------|-------------------------------------------|---------------------------------------------------------------------------|

| unsigned int   | registerMem(void* key, unsigned int size) | Register within the runtime a memory region identified by key             |

| unsigned inc   | registermen(void* key, unsigned int size) | of size bytes.                                                            |

| unsigned int   | getPlacement(void* key)                   | Get the memory space ID for the input key,                                |

| andighea inc   | goer racement (vorax key)                 | from 0 up to the number of active memory spaces for the application.      |

|                |                                           | Perform memory allocation on the given CU memory space for a memory       |

| void*          | alloc(void* key, unsigned int CU)         | chunk. Size is determined by the previous registration of the key value   |

| VOIU.          | arroc(void, key, unsigned inc co)         | associated to the memory region. Return value corresponds to the pointer  |

|                |                                           | to memory region.                                                         |

| void*          | dealloc(void* key, unsigned int CU)       | Perform memory deallocation on the given CU memory space for a memory     |

| 1014"          | dearroe (voia key, andighed inc co,       | chunk.                                                                    |

| void*          | mem_addr(void* key, unsigned int CU)      | Get base address of the registered memory region associated to key within |

|                | monitadar (voran noj) anorgnod inc oo,    | the $CU$ memory space.                                                    |

| unsigned int   | migrate(void* key, unsigned int to)       | Perform memory migration from the current placement of data (key) to the  |

| unbighed inc   | migrace (voia key, unbighed inc co,       | destination memory space.                                                 |

| unsigned int   | copy(void* key, unsigned int from,        | Perform a memory copy from the origin memory space to the                 |

| anorginea riic | unsigned int to)                          | destination memory space.                                                 |

| bool           | isGPU(unsigned int AS)                    | Check if the memory space AS corresponds to a device memory space.        |

| bool           | isCPU(unsigned int AS)                    | Check if the memory space AS corresponds to host memory space.            |

| unsigned int   | getGPUid(unsigned iny AS)                 | Get the device ID for the AS.                                             |

| unbighed inc   | gecorora (anorghea ing Ab)                | Returns error (-1) if the AS is not associated to a GPU-based CU.         |

Table 4. Runtime primitives of libPLACEMENT-rtl

primitives that involve data transfers between CUs are not optimized regarding the overlapping of communication and computation. In general, the primitives in libPLACEMENT-rtl expect that once memory regions have been allocated, then the application rarely will require memory migration due to changes in the work distribution among the CUs. But if this were the case, the runtime supports this feature. Section describes the hybrid implementation of the NPB-MZ benchmark suite and shows that this has not represented a limitation for the hybrid parallelization and execution.

Table 4 describes the runtime primitives that introduce the placement abstraction within the OpenMP programming model. The primitives give support to the programmer to query the runtime system about the parameters of the hybrid execution: how many address spaces are in use and check if an address space identifier corresponds to a host or device address space. For managing the memory allocation, the runtime support includes primitives to alloc and copy. In this regard, the alloc and de-alloc operations are mapped on the already existing primitives in the native OpenMP runtime support, but execute additional control code to monitor the allocated memory regions. For placement management, the runtime supports one main primitive to migrate memory regions. Section describes in detail how all these primitives have been used to code a hybrid version of the NPB-MZ benchmark suite.

# libSCHEDULING-rtl

Hybrid applications require work distribution schemes that adapt to the different computing power of the CUs. We have implemented a runtime library with generic support to implement different schedulers. The implementation follows an object-oriented paradigm, with virtualization of methods that need to be redefined by the programmer to implement new schedulings.

Within the libSCHEDULING-rtl, the input parameters for the scheduler are the number of tasks, the number of CPU-based CUs and the number of GPU-based CUs. All schedulers assume that the tasks are identified by an integer value ranging from 0 up to NTASKS-1, where NTASKS stands for the total number of tasks to be executed.

Table 5 describes the runtime primitives that allow the programmer to define and operate with the schedulers. The primitives also give support to the programmer to monitor execution times for tasks and also for CUs. Section describes in detail how these primitives have been used to code a hybrid version of the NPB-MZ benchmark suite.

Table 6 describes the main data structures that have been used to implement the scheduling support. The runtime system records how many tasks have to be scheduled, how many CUs are available, how many of them correspond to CPU-based CUs and how many correspond to GPUbased CUs. The runtime has the ability to memorize the task assignment between the CUs, so that if a computation is repeated several times, the scheduling is only applied once and later reused across the computation instances. For this purpose, the runtime uses several vectors to retain the task-CU assignment (e.g.: vectors mTaskCU, mTaskHowmany). Along the execution of the application, CUs require tasks to be executed (e.g.: getTask). This corresponds to the main virtual method. A programmer can redefine this method to implement dynamic workdistributions schemes. CUs notify that a task starts execution (executeTask) and communicate to the runtime system that a task has been completed (commitTask). These primitives are used to monitor task execution time and total CU execution time (vectors mTimersPerCU and mTimersPerTask).

Within libSCHEDULING-rtl we have implemented variants of two state-of-the-art schedulers: Static and Dynamic Task scheduling. The following subsections describe each scheduling in detail. In the context of this work, these schedulers represent a case of study to evaluate the support that the *libSCHEDULING-rtl* offers to enable user-defined schedulers. Hence, this section should not be understood as comprehensive study on work scheduling for heterogeneous systems.

# SCHEDULING::Static

This scheduling assigns the set of tasks evenly among the CUs: the total number of tasks is divided by the number of CUs. The same number of consecutive tasks (according to the tasks numbering) is assigned to each CU. If the number of CUs does not evenly divide the number of tasks, then

| Signature    |                                            | Description                                                                                                     |

|--------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| void         | commitTask(unsigned int task)              | Commit the task executed by the CU associated to the invoking thread.                                           |

| unsigned int | getTask()                                  | Get a task assigned to the CU associated to the invoking thread. Returns NOTASK when runs out of pending tasks. |

| void         | executeTask(unsigned int task)             | Start execution of the task assigned to                                                                         |

| VOIG         | executerask (unsigned int task)            | the CU associated to the invoking thread.                                                                       |

| unsigned int | getCUid(int Task)                          | Get the CU identifier that executes the task.                                                                   |

| void         | setTaskTime(unsigned int task, float Time) | Set the time sample for a task.                                                                                 |

| void         | getTaskTime(unsigned int task)             | Get the time sample for a task.                                                                                 |

| void         | setCUTime(int CU, float Time)              | Set the time sample for a CU.                                                                                   |

| void         | getCUTime(int CU, float Time)              | Get the time sample for a CU.                                                                                   |

| bool         | isDynamic()                                | Check if scheduling is a variant of a dynamic scheduling.                                                       |

| bool         | isStatic()                                 | Check if scheduling is a variant of a static scheduling.                                                        |

| void         | printScheduling()                          | Output the assignment between CUs and tasks.                                                                    |

| void         | <pre>printTaskTimers()</pre>               | Output the time samples for tasks.                                                                              |

| void         | printCUTimers()                            | Output the time samples for CUs.                                                                                |

Table 5. Runtime primitives of libSCHEDULING-rtl

| Туре                                                   | Name            | Description                                                                                                                                                                   |

|--------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| unsigned int                                           | mNtasks         | Number of tasks to be scheduled.                                                                                                                                              |

| unsigned int                                           | mNcpus          | Number of CPU-based CUs.                                                                                                                                                      |

| unsigned int                                           | mNgpus          | Number of GPU-based CUs.                                                                                                                                                      |

| std::vector <int></int>                                | mTaskCU         | Vector of size <i>mTasks</i> containing the CU identifier that executes each task.                                                                                            |

| std::vector <int></int>                                | mTaskHowmany    | Vector of size mNcpus+mNgpus containing the number of tasks assigned to each CU.                                                                                              |

| <pre>std::vector&lt; std::vector<int> &gt;</int></pre> | mCUTasks        | Vector of size <i>mNcpus+mNgpus</i> . Each element is a vector containing the sequence of tasks assigned to a CU.                                                             |

| std::vector <bool></bool>                              | mCommitTasks    | Vector of size <i>mNtasks</i> that indicates if a task has been completed.                                                                                                    |

| std::vector <unsigned int=""></unsigned>               | mIndexTask      | Vector of size mNcpus+mNgpus containing an index value for the task being executed by a CU. This value is used to access the corresponding vector within the mCUTasks vector. |

| omp_lock_t                                             | mLock           | Mutex used for mutual exclusion to support dynamic schedulers.                                                                                                                |

| unsigned int                                           | mChunk          | Chunk parameter applied to the dynamic scheduler.                                                                                                                             |

| std::vector <float></float>                            | mTimersPerCU    | Vector of size mNcpus+mNgpus to store the execution time for a CU.                                                                                                            |

| std::vector <float></float>                            | mTimersPerTask  | Vector of size <i>mTasks</i> to store the execution time for a task.                                                                                                          |

| std::vector <unsigned int=""></unsigned>               | mIndexFirstTask | Vector of size mNcpus+mNgpus to store first task assigned to a CU. The scheduler assumes a sequence of consecutive tasks being assigned to each CU.                           |

| std::vector <unsigned int=""></unsigned>               | mIndexLastTask  | Vector of size mNcpus+mNgpus to store last task assigned to a CU. The scheduler assumes a sequence of consecutive tasks being assigned to each CU.                            |

Table 6. Data structures of libSCHEDULING-rtl

an additional task is assigned to CUs with identifiers in the range [0, NREMAIN-1] where NREMAIN is the number of remaining tasks. This scheduler behaves exactly as the STATIC scheduling included in the OpenMP specification for loop level parallelism.

#### SCHEDULING::STATIC-hybrid

This scheduler is a variant of the Static scheduler. According to a pre-computed parameter, the Performance Conversion Factor (PCF), the scheduler divides the set of the tasks into two subsets: one for the CPU-based CUs, the other for the GPU-based CUs. Then the scheduler applies a Static scheduling per each subset, separately assigning tasks to CPU-based CUs and GPU-based CUs. The PCF is the ratio between the execution time needed to process a task by a CPU-based CU and by a GPU-based CU according to the hybrid configuration. For instance, a  $PCF_{1x2}$  equal to 2.5 indicates that the execution time needed by a CU composed by 2 CPUs to process a task is equal to 2.5 multiply by the time needed by one GPU-based CU (e.g.: one GPU). Similarly,  $PCF_{1x4}$  is the ratio between the execution times of a CU composed by 4 CPUs and a GPU-based CU. In general, this scheduler needs the PCF values to be pre-computed; in our implementation, through profiling techniques.

Given T tasks, this scheduler assigns to the set of GPU-based CUs the number of tasks:  $T_{gpu} = T / (G \times PCF + C)$ , where C corresponds to the number of CPU-based CUs, G

corresponds to the number of GPUs. If the division generates a remaining of tasks, these are grouped in GxPCF groups and assigned to the GPUs. The number of tasks assigned to the CPU-based CUs is  $T_{cpu} = T - T_{gpu}$ . Once the  $T_{gpu}$  and  $T_{cpu}$  values are computed, then the scheduler applies a Static scheduling to each set according to the number of CPU-based and GPU-based CUs. The reasoning behind this arithmetic is the following: dividing the number of tasks by the value (G x PCF + C), defines the number of groups that can be formed with sufficient work to distribute among CPU-based and GPU-based CUs in a uniform, balanced way. The balancing occurs because of the PCF parameter in the expression. For instance, if T=10, G=1, C=1 and PCF=3, then we want to form groups of 4 tasks (4=GxPCF+C), because 3 of them will be mapped to a GPU, one will be mapped to a CPUbased CU. This results in balanced distribution, according to the PCF value. We count how many of these groups can be formed by computing  $T / (G \times PCF + C)$ .

This STATIC-hybrid scheduling has several similarities with previous heterogeneous work-schedulings in Scogland et al. (2012, 2014). In these works, performance models are introduced to estimate the execution time of a task on the available computing resources (e.g.: CPUs/GPUs). The estimates are generated dynamically, through regression techniques. The STATIC-hybrid is very similar to that of the heterogeneous work-scheduling in Scogland et al. (2012,

2014). Given the estimates, the tasks are assigned to the compute units in a similar fashion. The essential difference is that the STATIC-hybrid scheduler needs of an off-line profiling step to generate samples of execution times for tasks and compute units. The performance comparison factor is derived from these samples, which is the key element in the STATIC-hybrid scheduling to decide where to place a particular task. In general, this approach is less general that those based on dynamic techniques, but in the context of scientific applications it is yet a feasible and effective technique. The impact of the profiling step is evaluated in Section where we describe how much time is needed and what are the programming efforts that it requires.

#### SCHEDULING::Dynamic

This scheduler assigns tasks to CUs dynamically. It divides the set of tasks into chunks of *chunk* consecutive tasks according to the task numbering; where *chunk* is a parameter of the scheduler. A chunk is assigned to each CU and as soon as a CU finishes processing its chunk, the scheduler assigns a new chunk to the CU. This scheduling behaves as a task scheduler where the chunk parameter determines the task granularity.

The chunk parameter can smooth the effect of CU synchronizations to acquire chunks of work. Besides, this scheduler is able to memorize the task-CU assignment. The runtime system keeps track of which tasks executed each CU. From one execution of the scheduled computation, to the next instance of the same computation, the scheduler ensures that the same task scheduling is applied. Thus, no data migration occurs when the parallelism execution is repeated. Only the first instance of the work execution suffers from overheads related to memory registering, allocation and/or data transfers associated to the data communication between the CUs. This data locality preservation is only effective if no other computation under a different scheduling moves data between host and devices. This scheduler behaves exactly as the DYNAMIC scheduling included in the OpenMP specification for loop level parallelism, but with the additional property of memorizing the task assignment from one execution to the next one.

# Design and Implementation of Hybrid NPB-MZ

This section describes the hybrid design and implementation of the NPB-MZ benchmark suite using the runtime support described in the previous section.

# Multi-Level Hybrid Parallelization

The mulit-level parallelization is described in terms of the *inter* and *intra* zone parallelism exposed in both the *Computation Period* and *Communication Period* of each benchmark in the suite.

#### Computation Period

Figure 9 shows the OpenMP implementation for a hybrid parallel strategy for the *inter-zone* parallelism. The original loop responsible for traversing the zones (Figure 4) has been substituted by a parallel region. The parallel region is executed with as many threads as CUs are used for the hybrid execution. The code executed by all threads corresponds to

a *while* loop where the primitives for acquiring, executing and committing tasks are inserted. Notice the usage of the *migrate* primitive to ensure that the memory allocation is performed prior any attempt is done to process a zone (e.g.: task). In this case, the task identifier coincides with the zone index to be processed at each iteration of the *while* loop. For threads associated to a GPU-based CU, after the zone is processed, a synchronization primitive is invoked. The different computation phases are executed by a host CU or device CU according to the nature of the thread. Notice that this code structure is independent from the applied scheduling. In Figure 9 a static scheduling is used, but it could be substituted by a dynamic or hybrid scheduling.

Figure 10 depicts the code for one stage. Notice the usage of the corresponding primitives to check whether the executing thread is associated to a host or to a device CU. For host CUs, the execution is diverged to loop nests annotated with OpenMP directives. These inner parallelism is exploited by as many threads as the output of the primitive nInnerCPUs. Thus, this innermost parallelism is deployed over the CPUs associated to the host CU. This is ensured because OpenMP thread affinity is set so that appropriate places are described through OMP\_PLACES and OMP\_PROC\_BIND environment variables. If the thread corresponds to a device CU, then the execution is diverged to the invocation of the kernels that codify the device versions of the original loop nests. Notice the translation from the device CU identifier to the actual device identifier (e.g.: call to the getGPUid primitive).

```

Static(num_zones, CU::nGPUS(), CU:nCPUS());

#pragma omp parallel num_threads(CU::GPUS()+CU:CPUS())

task = Static::getTask();

while (task != NO_TASK) {

PLACEMENT::migrate(mesh[zone],...);

Static::executeTask(task);

/* ZONE PROCESSING */

zone = task;

comp_phase_1 (...);

comp phase 2 (...);

comp_phase_N (...);

if (CU::isGPU()) CU::synchronize();

Static::commitTask(task);

task = Static::getTask();

}// while

} // parallel

```

**Figure 9.** Code transformation for exploiting inter-zone parallelism. Original parallel loop is transformed into a parallel region containing a *while* loop. Threads iterate and invoke the runtime primitives to acquire tasks and execute them. The scheduling to be applied is determined by the call to the primitive *Static*.

#### Communication Period

Within the *Communication Period* there is no *inter-zone* parallelism. All zones are processed one after the other, exchanging and updating border values. Process a zone

```

void comp_phase_N(...)

if (CU::isCPU()) {

NT = CU::nInnerCPUs();

#pragma parallel for num_threads(NT)

for (k=0; k < zdim; k++)

for (j=0; j < ydim; j++)

for (i=; i < xdim; i++) {

/* MATRIX BASED COMPUTATION */

...

}

} // if

else if (CU::isGPU()) {

HipSetDevice(CU::getGPUid());

kernel_l_comp_stage_N<<<grid, block, ... >>> (...);

} // else

...

}

```

**Figure 10.** Code transformation for exploting intra-zone paralellism. Host CUs are diverged to loop nests annotated with loop level parallelism directives. This innermost level of parallelism is executed by the CPUs associated to the host CU; the number of threads is determined by the call to *nInnerCPUs*. Device CUs are diverged to kernel invocations.

```

for (zone=0; zone<NUM_ZONES; zone++) {</pre>

east_zone = adjacency_east[zone]

north_zone = adjacency_north[zone];

zonePlacement = PLACEMENT::getPlacement(mesh[zone]);

copy_face(tmpEast[zonePlacement], mesh[east_zone],

"IN", ...);

copy_face(tmpNorth[zonePlacement], mesh[north_zone],

"IN", ...);

if (PLACEMENT::isGPU(zonePlacement)) {

HipSetDevice(PLACEMENT::getGPUid(zonePLacement));

apu compute-border (mesh[zone],

tmpEast[zonePlacement],

tmpNorth[zonePlacement]);

else if (PLACEMENT::isCPU(zonePLacement)) {

cpu compute border(mesh[zone], tmpEast[zonePlacement]

tmpNorth[zonePlacement]);

copy_face(tmpEast[zonePlacement], mesh[east_zone],

"OUT", ...);

copy_face(tmpNorth[zonePlacement], mesh[north_zone],

"OUT", ...);

```

**Figure 11.** Hybrid implementation of the exchange boundary computation. Host and device versions of the compute border computation are introduced. Zone placement is checked and border computation happens where the zone resides.

exposes some amount of parallelism that can be exploited through fine-grain parallelism.

Figure 11 depicts the code scheme for the *Communication Period*. Zone faces containing border elements are copied to temporary buffers (e.g.: calls to *copy-face procedure*). Then, zone placement is checked to perform the border exchange computation on a device or host accordingly.

The implementation of the *copy-face* procedure now is more complex because buffering of border elements is conditioned by the fact that buffers and adjacent zones can

```

void copy_face(void* Buffer, void* Zone, string Dir, ...) {

zonePlacement = PLACEMENT::getPlacement(Zone);

bufferPlacement = PLACEMENT::getPlacement(Buffer);

if (Dir == "IN") {

if (PLACEMENT::isGPU(zonePlacement) &&

PLACEMENT::isGPU(bufferPlacement)) {

HipSetDevice(PLACEMENT::GPU(zonePlacement));

gpu_copy_face<<<grid, block, ...>>>(...);

HipMemCpyPeer(Buffer, ...,);

if (PLACEMENT::isGPU(zonePlacement) &&

PLACEMENT::isCPU(bufferPlacement)) {

HipSetDevice(PLACEMENT::GPU(zonePlacement));

gpu_copy_face<<<grid, block, ...>>>(...);

HipMemCpy(Buffer, ..., HipDeviceToHost);

if (PLACEMENT::isCPU(zonePlacement) &&

PLACEMENT::isGPU(bufferPlacement)) {

cpu_copy_face(...);

HipSetDevice(PLACEMENT::GPU(bufferPlacement));

HipMemCpy(Buffer, ..., HipHostToDevice);

if (PLACEMENT::isCPU(zonePlacement) &&

PLACEMENT::isCPU(bufferPlacement)) {

cpu_copy_face(...);

} // if Dir == "IN"

else if (Dir == "OUT") {

} //if Dir == "OUT"

```

**Figure 12.** Hybrid implementation of the copy\_face computation. Placement checks are introduced for buffers and and zones. Host and device versions of the copy\_face procedure are needed to cover all 4 possibilities: buffer resides on host/device, zone resides on host/device.

reside on different address spaces. Figure 12 shows the code skeleton for this procedure. Notice the structure of *if* statements that cover the 4 possibilities: buffer resides on host/device, zone resides on host/device. Notice that, for data transfer, AMD's HIP primitives appear to move the data acrros the host and devices. This communication arises according to the memory footprint determined by the applications, which in turn is totally conditioned by the scheduling applied during the *Computation Period*. The effect of this communication is evaluated in Section .

#### Programmability Assessment

The runtime support described in this section has made possible the deployment of a methodology to enable hybrid executions mixing OpenMP and CUDA/HIP. In terms of programmability, we have introduced the abstractions of the Computing Unit, Data Placement and Scheduling within the OpenMP programming model in a transparent fashion and in accordance to the current specification of the OpenMP programming paradigm. In addition, we have provided with a code transformation to enable task parallelism accompanied with a set of placement and scheduling primitives that make possible the simultaneous activation of host and device computing units.

The following subsections compare our proposal versus existing solutions that achieve similar levels of programmability mixing different programming models with CUD-A/HIP.

#### Comparing with MPI + CUDA/HIP

As different devices in a compute node might or might not share their memory spaces, several works have tried to achieve a hybrid parallelization mixing distributed memory paradigms such as MPI and CUDA/HIP (Karunadasa and Ranasinghe 2009; Peña et al. 2020; Kraus 2013; Awan et al. 2019; Jacobsen et al.). These solutions require similar runtime primitives as those explored in this work. In MPI (Message Passing Interface Forum 1994), work distribution would happen manually across the different MPI ranks. And within each of the ranks, the simultaneous activation of the host cores and the device cores would also happen through manual re-coding of the application. One immediate drawback of this approach corresponds to the mapping of host cores to MPI ranks for locality purposes. OpenMP includes support to guide the thread affinity to hardware resources. Though for MPI it is also possible to use tools like numactl or cpusets, this complicates the task of the programmer, compared to the current OpenMP solution, fully integrated in the specification with the definition of places and thread binding (i.e., usage of environment variables OMP\_PLACES and OMP\_PROC\_BIND).

#### Comparing with OpenMP/OmpSS

OmpSS (Elangovan et al. 2013; Duran et al. 2011; Bueno et al. 2012) is a task-based programming model that can effectively support the hybrid parallel strategy described for the NPB-MZ benchmark suite. The inter-zone parallelism can be supported through task definition directives, and data associated to tasks can be specified through the usage of *in*, *out* clauses to describe producer consumer relations. The entanglement between the task scheduling and the data placement is solved using this information. Compared to our proposal, both require the programmer to identify which data is associated to each task, however the programming efforts are simpler in OmpSS than in our proposal.

For OpenMP, the similarities and limitations are the same. OpenMP supports task-level parallelism. The common usage of a parallel directive combined with a single directive for task definition can be used for the inter-zone parallelization. But OpenMP does not allow the programmer to control how tasks have to be mapped to compute units. This combination can not be accompanied with the specification of a particular scheduling. Therefore, similar runtime functionalities as those proposed in this paper would be necessary to deploy a reasonable interoperability between OpenMP and CUDA/HIP. Specially for data placement and work scheduling. Notice that using target and metadirectives to offload computations to devices does not solve the problem of whether at the inter-zone level of parallelism, decide where to execute a task. The *target* support just solves the device code generation, not the scheduling and data placement problems.

The CoreTSAR proposal (Scogland et al. 2014) addresses the limitations of these programming models. In particular, it identifies the missing runtime functionalities to simultaneously deploy task-based parallelizations with appropriate task scheduling, including a reasonable programming level regarding the data placement guidance. Both CoreTSAR and the runtime described in this paper share some functionalities, being the main difference the fact that CoreTSAR

does not target the interoperability for OpenMP and CUD-A/HIP. CoreTSAR complements the OpenMP standard to enable OpenMP strategies for heterogeneous programming. Besides, CoreTSAR scheduling is based on dynamic techniques, in contrast we explore offline profiling techniques to define an appropriate task scheduling.

#### **Evaluation**

This section evaluates the overall performance of our hybrid implementation of the NPB-MZ benchmark suite. Applications have been coded and compiled within the ROCm-3.5.0 framework and *llvm 12* compiler suite. The CPU code has been compiled combining a C++ NPB-MZ implementation (Dümmler and Rünger 2013) and the original NPB-MZ Fortran implementation (der Wijngaart and Jin 2003) to generate a version compatible with the ROCm implementation of the applications. All experiments have been performed in a system composed of AMD EPYC 7742 @ 2.250GHz (64 cores and 2 threads/core, totalling 128 threads per node) and 2 x GPU AMD Radeon Instinct MI50 with 32GB. We run class D NPB-MZ benchmarks (Table 1), so the input mesh is composed by 16 zones (LU-MZ) or 1024 zones (BT-MZ and SP-MZ); memory usage is 13 GB.

#### Overall Performance

The basis for the performance evaluation is the comparison between four versions of the benchmarks in the suite: GPU-based and CPU-based non-hybrid versions already studied in previous studies for the NPB-MZ benchmark suite (Duran et al. 2005; Gonzalez and Morancho 2020; González and Morancho 2021) and two hybrid executions under two work-distribution schemes. On one hand, a static scheduling that corresponds to the default and only supported scheduling for hybrid executions in the latest OpenMP specification (OpenMP 5.2). On the other hand, we include a dynamic task scheduling with the ability of memorizing the task-CU assignment across different instances of the scheduled computation. The comparison between the static and dynamic hybrid versions exposes the current performance limitations in OpenMP for hybrid executions.

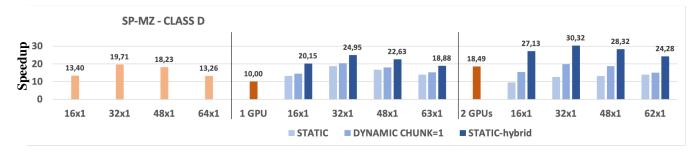

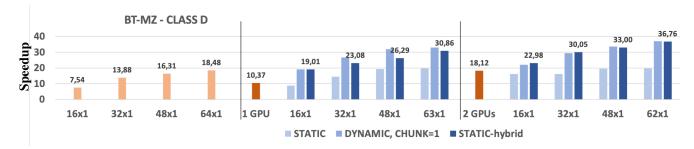

# SP-MZ benchmark:

Figure 13 shows the speedup achieved by several parallel configurations with respect to the single CPU configuration in benchmark SP-MZ. Leftmost bars correspond to executions under a STATIC scheduling. We take the performance of this scheduler as a performance reference. From left to right, first CPU-based configurations range from 16 to 64 threads exploiting the *inter-zone* parallelism (e.g.: for 64x1 configuration, each thread processes 16 zones). Maximum speedup is observed with 32 threads: 19.71x. Then, with 48 and 64 threads, the performance drops significantly (up to 18.23x and 13.26x respectively). This trend will also appear in the hybrid configurations. Table 7 shows average execution time per zone under different configurations. For SP-MZ, the first thing to notice is that for 1-GPU, processing one task (e.g. zone) takes 0.83ms on average. In contrast, with 1-CPU, it takes 8.70ms. When

**Figure 13.** Benchmark SP-MZ with input CLASS D. Overall speedup for different configurations: from left to right, CPU only configurations, 1 GPU configurations and 2 GPU configurations. CPU-based CUs are defined as BxT, where B corresponds to CPU-based CUs executing with T CPUs each. Speedup is measured with respect to single CPU configuration.

more CPUs are added, the time for processing one tasks increases. Notice how for a non hybrid 32x1 configuration the average task processing time is 11.25ms, but for 64x1 is 36.38ms: more than 3x of slowdown. Consequently, CPU-based versions do not scale well with the increment of CUs. The time it takes to compute one zone when executing with 16, 32 48 and 64 CUs is not constant. The main reason for this is that last level cache memory has a small capacity compared to the input data size: 256 MB in contrast to 13GB (see Table 1). The pressure over the memory subsystem is different in each configuration, making executions with a higher count of CUs process one zone with higher execution times. This aspect is essential to explain the performance of hybrid configurations.

| Conf. | SP-MZ | BT-MZ  | Conf. | LU-MZ   |

|-------|-------|--------|-------|---------|

| 1-GPU | 0.83  | 2.96   | 1-GPU | 38.44   |

| 1x1   | 8.70  | 31.11  | 1x1   | 1653.38 |

| 16x1  | 9.00  | 64.75  | 1x16  | 258.94  |

| 32x1  | 11.25 | 69.19  | 1x32  | 98.13   |

| 48x1  | 18.61 | 87.66  | 1x48  | 88.44   |

| 64x1  | 36.38 | 102.50 | 1x64  | 38.44   |

**Table 7.** Average task time (ms) for all NPB-MZ applications with different CU configurations: BxT where B stands for the number of CUs and T stands for the number of threads in each CU, non hybrid 1-GPU and 2-GPU (B=0).

| Conf. | SP-MZ | BT-MZ | Conf. | LU-MZ |

|-------|-------|-------|-------|-------|

| 1-GPU | 1     | 1     | 1-GPU | 1     |

| 16x1  | 10.89 | 21.91 | 1x16  | 6.74  |

| 32x1  | 13.62 | 23.41 | 1x32  | 2.55  |

| 48x1  | 22.52 | 29.66 | 1x48  | 2.30  |

| 64x1  | 44.03 | 34.69 | 1x64  | 2.16  |

**Table 8.** PFC values used per each application and configuration. Values are obtained from the relation between task execution times in 1 GPU and B x T CPUs configurations (BxT where B stands for the number of CUs and T stands for the number of threads in each CU).

Hybrid configurations with 1 GPU show a similar trend. 1-GPU configuration speeds-up by 10x. Hybrid configurations under the STATIC scheduling do not outperform CPU-based configurations. For instance, 32x1+1 configuration speeds-up by 18.72x, below the performance of the 32x1 configuration (19.71x). This is due to the way the 1024 zones are distributed among CU's. For 32x1 configuration, there are 32 CU's and the scheduler assigns 32 zones to each one. For the 32x1+1 configuration, there are 33 CUs, so

the largest piece of work still is a 32-zone work unit. For hybrid configurations with higher count of CPU-based CUs, adding one or two GPUs does not significantly reduce the work assignment per each CU. The STATIC scheduler does not take into account the differences between the CUs respect their compute power.

Figure 13 shows the performance of hybrid configurations under a DYNAMIC scheduler with CHUNK=1. Notice that now configurations 32x1+1 and 32x1+2 speedup by 20.38x and 19.88x respectively. Both outperform the maximum performance observed for CPU-based configurations. But we have observed that the speedup for hybrid configurations under the DYNAMIC scheduler is limited by the Communication Period. For the SP-MZ, the input working set is composed of many and very small zones where the ratio between the number of boundary elements and the total number of zone elements makes that a very high count of elements are processed within the border computation. This becomes even worse when we combine the memory spaces for host and devices, slowing down its execution time. Zones are dynamically distributed among the CUs. This makes that adjacent zones now are placed in different memory spaces. Therefore, data transfers are necessary to compute the exchange of boundary values. In particular we have observed execution times for the Communication Period that change from 97ms for CPU-based configurations to 140ms for hybrid configurations with 1 GPU, and 200ms with 2 GPUs. The Computation Period ranges from 576ms to 280ms depending on the number of active CUs in the configuration. Therefore, speedups for the Computation Period are considerably higher than those observed for the overall performance. For instance, for hybrid configurations with 2 GPUs, we have observed speedups that range between 21x and 31x. But the increments in the execution times for the Communication Period limit the overall performance of the application. In this regard, one particular aspect of the DYNAMIC scheduling is that of memorizing the task-CU assignment from one execution instance to the next one. In the context of hybrid architectures with different physical memory spaces, this aspect becomes essential to ensure that in phases where data is interchanged between tasks, the communication overheads do not become a performance bottleneck. We have checked that if the same scheduling is applied but removing the memorizing ability (e.g., each instance of the Computation Period remaps the task-CU

assignment), then both the *Computation Period* and the *Communication Period* suffers from slowdown factors between 10x-15x.

The STATIC-hybrid scheduler is based on a performance conversion factor (PCF) between the GPUs and the CPUs. In this case, the PCF value for each configuration has been obtained from the data in Table 7. We divide the average task execution under a CPU and non hybrid configuration by the average task execution time when executed in one GPU. This should describe how faster a GPU is computing one task compared to CPU-based execution with 16, 32, 48 and 64 CPUs. Table 8 exposes the PCFs values for each configuration, directly computed from Table 7. In general, collecting the data in Tables 7 and 8 requires the execution of several iterations of the benchmarks. In our case, 5 iterations were sufficient to observe steady execution times per task on both the GPU case and the CPU case. Overall this corresponded to experiments that needed less than 10 minutes for all 3 benchmarks in the NPB-MZ suite.

For the STATIC-hybrid scheduling, we observe that the work imbalance caused by the different nature of the CUs is solved. Even more, the scheduler tends to assign adjacent zones to the same CU. Therefore, this scheduling balances the execution without incurring in communication overheads related to the boundary values exchange. This explains the observed performance levels: speedup values range between 20x and 30x, outperforming the single GPU configurations by factors ranging from 1.75x and 2.5x. Although these improvements, both the 1-GPU and 2-GPU hybrid configurations expose a performance degradation with more than 32 CPUs. This fact is explained by the data in Table 7. As it was described previously, the zone processing time is not constant, with increments of more that 3x of slowdown when doubling the number of available CPUbased CUs. This explains that for hybrid configurations with more than 32 CPUs the STATIC-hybrid scheduling is not able to perform a zone-CU assignment that keeps improving the performance as the total count of CUs is increased. In the context of heterogeneous computing, the STATIC-hybrid corresponds to a a state-of-the-art scheduling aligned to most recent advances in heterogeneous scheduling. The reference works (Scogland et al. 2012, 2014; Elangovan et al. 2013; Duran et al. 2011) explore similar approaches based on estimates for the execution time in different types of compute units. In particular, the proposal Scogland et al. (2014) is based on dynamic techniques that implement a regression based on architectural parameters. In contrast, the STATIChybrid is based on offline data obtained through profiling techniques. In this regard, we consider a the STATIChybrid scheduling as a variant for a reference scheduling in heterogeneous computing.

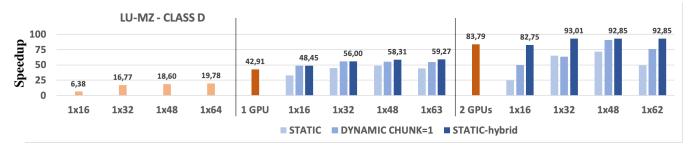

LU-MZ benchmark: Figure 14 shows the speedup achieved by several parallel configurations with respect to the single CPU configuration in benchmark LU-MZ. From left to right, the performance of CPU-based configurations are shown using from 1 to 64 threads exploiting the *intrazone* parallelism (e.g.:for a 1x32 configuration, each zone is processed by 32 threads, one zone after the other). Maximum speedup is observed with 64 threads: 19.78x. In general, from 16 CPU to 64 CPU configurations, there

is poor scalability, although speedup increases with the increment of CPUs. This trend will also appear in the hybrid configurations. As it has been observed in the previous subsection, the main reason for this is that last level cache memory has a small capacity compared to the input data size: 256 MB in contrast to 13GB (see Table 1). This makes that the CPU-based versions do not scale well with the increment of CUs. The time it takes to compute one zone when executing with 16, 32 48 and 64 CUs is not constant (see Table 7). The pressure over the memory subsystem is different in each configuration, diminishing the effect of the utilization of high counts of CUs.

Hybrid configurations show a very different range of speedups. Single GPU configurations delivers an impressive speedup of 42.91x. Configurations under the STATIC scheduling improve the speedup as the number of CPU-based CUS increases, reaching a maximum speedup of 48.80 for the 1x48+1 configuration. The STATIC distribution does not take into account the differences in compute power of the CUs. The LU-MZ operates over a mesh of 16 zones. In all 1-GPU hybrid configurations the number of CUs are 2. This means that 8 zones are assigned to 1 GPU, 8 zones are assigned to 1 CPU-based CU composed of 16, 32, 48 or 64 CPUs depending on the configuration. For 2 GPUs, the initial speedup is 83.79x. But the STATIC scheduling is not able to adapt the work distribution now for 3 CUs. Dividing the 16 zones among 3 CUs defines the largest piece of work to be composed of 6 zones that are assigned to the CPU-based CU.

The DYNAMIC scheduling improves the performance significantly. For this scheduling the maximum speedup corresponds to 55.89x for 1-GPU and 90.47x for 2-GPU configurations. In this case, faster CUs (the GPUs) take more work to execute. In contrast to the SP-MZ benchmark, the LU-MZ input mesh is organized in very few and very large zones. This implies that the ratio between border elements and zone elements is very small. As a result, we do not observe a significant increment in the Communication Period, as happened with the SP-MZ benchmark. Despite that, we have observed that the memorizing ability of the DYNAMIC scheduling still is essential in this case as we have checked that if the same scheduling is applied but removing the memorizing ability (e.g.: each instance of the Computation Period remaps the task-CU assignment), then both the Computation Period and the Communication Period suffers from slowdown factors between 15x-20x.

The STATIC-hybrid achieves the maximum performance in all hybrid configurations. For 1-GPU, speedups range from 48x to 59x, with an increment of performance as the number of CUs is increased. For 2-GPU observed speedups range from 82x to 93x. This scheduling succeeds on identifying the differences in compute power among the available CUs, and distribute tasks (e.g.: zones) accordingly to balance the work distribution. As has been described previously for the SP-MZ application, for the LU-MZ application Tables 7 and 8 expose the PCF values used for the STATIC-hybrid scheduling.