## Locality analysis and its hardware implications for Graph Pattern Mining

Ana Arduengo García

Advisors: Miquel Moretó (UPC) Arvind (MIT CSAIL)

Tutor: Miquel Moretó Planas

A thesis submitted in partial fulfillment of the requirements for the: Bachelor's Degree in Informatics Engineering Bachelor's Degree in Mathematics

May, 2023

# Abstract

Graphs have numerous applications since they are simple yet effective to model real-life phenomenon. The strength of graph formalism is found in its generality and emphasis on relationships between points rather than the characteristics of individual points. Hence, there is a demand for proficient querying techniques on large data graphs.

Graph Pattern Mining (GPM) are the methods to find relationship over actual graphs. There are two major difficulties to computing GPM algorithms: (a) They have poor locality as a result of erratic accesses when traversing the nearby vertices; and (b) They require a lot of memory bandwidth. In other words, it is challenging to conceal the latency because the computation time following the retrieval of a piece of data from the memory hierarchy is brief. The memory bandwidth waste is another side effect of the poor locality.

Near-data processing (NDP) architecture is a promising solution to improve the performance of GPM applications. It is possible to integrate computation units in/or close to the memory module using NDP architecture, and we can reduce the amount of data that is moved back and forth between the CPU and memory module to achieve high performance and energy-efficient computation. To face these challenges, a system-level simulator, capable of simulating multi-threaded applications in a full-system environment with a complete operating system on a heterogeneous multi-core system, can be required.

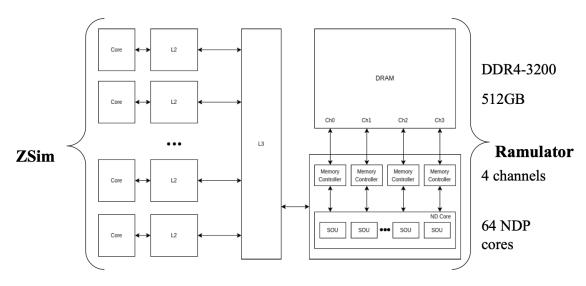

In this work, we have addressed the acceleration of GPM applications from the perspective offered by the NDP architecture. We have developed a new simulation tool, based on the integration of two well-known simulators: ZSim (for the cores and the caches) and Ramulator (for the memory). The need to carry out this integration arises from the fact that the implementation available for the joint use of both simulators does not take advantage of the techniques that ZSim uses to reduce the loss of precision. We have implemented in simulation a state-of-the-art GPM accelerator based on the NDP architecture (NDMiner). The new simulation tool allows a detailed NDMiner profiling to identify its weak points. Therefore, it helps to design strategies that alleviate those bottlenecks and improve their performance. Consequently, after realizing experiments with the new simulator, we have elaborated a series of concrete proposals to solve some of the problems detected and to improve NDMiner.

**Keywords:** Graph Pattern Mining (GPM), Near-Data Processing (NDP), Graph Mining Acceleration, Locality, Hardware Simulation, ZSim, Ramulator

Mathematics Subject Classification (MSC): 68R10

# Resumen

Los grafos tienen numerosas aplicaciones porque permiten modelizar fenómenos reales de forma sencilla y efectiva. El punto fuerte de la representación en grafos reside en su generalidad y en que el foco se dirige hacia la relación entre nodos más que hacia las características individuales de cada nodo. Por ello, existe una demanda creciente de técnicas especializadas para el reconocimiento de patrones representativos en grafos.

El reconocimiento de patrones en grafos (GPM) agrupa un conjunto de métodos para buscar relaciones entre sus nodos. La computación de los algoritmos GPM presenta dos grandes problemas: (a) Enfrentan una baja localidad, debido a los accesos erráticos al recorrer vértices cercanos:, y (b) Requieren un gran ancho de banda de memoria. En otras palabras, es difícil ocultar la latencia porque el tiempo de computación después de la recuperación de un grupo de datos de la memoria es corto. Otro inconveniente derivado de la baja localidad es el desperdicio de ancho de banda de memoria.

La arquitectura del procesamiento cerca de la memoria (NDP) es una prometedora solución para mejorar el rendimiento de las aplicaciones GPM. La arquitectura NDP permite integrar unidades de computación en/o cerca del módulo de memoria, reduciendo el movimiento de datos entre la memoria y la CPU y mejorando la eficiencia y el consumo de energía. Para avanzar en este desafío se precisa un simulador capaz de realizar aplicaciones paralelizadas en un sistema heterogéneo con múltiples cores.

En este trabajo, hemos abordado la aceleración de aplicaciones GPM desde la perspectiva ofrecida por la arquitectura NDP. Hemos desarrollado una nueva herramienta de simulación, basada en la integración de dos conocidos simuladores: ZSim (para los cores y las caches) y Ramulator (para la memoria). Hemos tenido que diseñar específicamente esta integración porque la implementación disponible para la utilización conjunta de ambos simuladores no aprovecha las técnicas que usa ZSim para reducir la pérdida de precisión. Luego hemos implementado en el simulador un acelerador GPM que utiliza la arquitectura NDP (NDMiner), entendemos que representa el estado-del-arte al respecto. La herramienta de simulación permite realizar un detallado "profiling" de NDMiner, muy útil para identificar sus puntos débiles. De esta forma, el simulador facilita el diseño de estrategias para mejorar el rendimiento del acelerador. Mediante una serie de experimentos en simulación, hemos elaborado una serie de propuestas concretas para solucionar los problemas detectados y mejorar NDMiner.

**Palabras clave:** Graph Pattern Mining (GPM), Near-Data Processing (NDP), Graph Mining Acceleration, Locality, Hardware Simulation, ZSim, Ramulator

Mathematics Subject Classification (MSC): 68R10

# Resum

Els grafs tenen nombroses aplicacions perquè permeten modelitzar fenòmens reals de manera senzilla i efectiva. El punt fort de la representació en grafs resideix en la seva generalitat i en què el focus es dirigeix cap a la relació entre nodes més que no pas cap a les característiques individuals de cada node. Per això, hi ha una demanda creixent de tècniques especialitzades per al reconeixement de patrons representatius en grafs.

El reconeixement de patrons en grafs (GPM) agrupa un conjunt de mètodes per cercar relacions entre els nodes. La computació dels algorismes GPM presenta dos grans problemes: (a) Enfronten una baixa localitat, a causa dels accessos erràtics en recórrer vèrtexs propers:, i (b) Requereixen un gran ample de banda de memòria. En altres paraules, és difícil amagar la latència perquè el temps de computació després de la recuperació dun grup de dades de la memòria és curt. Un altre inconvenient derivat de la baixa localitat és el malbaratament d'amplada de banda de memòria.

L'arquitectura del processament a prop de la memòria (NDP) és una solució prometedora per millorar el rendiment de les aplicacions GPM. L'arquitectura NDP permet integrar unitats de computació a/o prop del mòdul de memòria, reduint el moviment de dades entre la memòria i la CPU i millorant l'eficiència i el consum d'energia. Per afrontar aquest desafiu cal un simulador capaç de realitzar aplicacions paral·lelitzades en un sistema heterogeni amb múltiples cores.

En aquest treball hem abordat l'acceleració d'aplicacions GPM des de la perspectiva oferta per l'arquitectura NDP. Hem desenvolupat una nova eina de simulació, basada en la integració de dos coneguts simuladors: ZSim (per als cores i les caches) i Ramulator (per a la memòria). Hem hagut de dissenyar específicament aquesta integració perquè la implementació disponible per a la utilització conjunta de tots dos simuladors no aprofita les tècniques que fa servir ZSim per reduir la pèrdua de precisió. Després hem implementat al simulador un accelerador GPM que utilitza l'arquitectura NDP (NDMiner), que representa l'estat de l'art. L'eina de simulació permet realitzar un detallat "profiling" de NDMiner, molt útil per identificar els seus punts febles. D'aquesta manera, el simulador facilita el disseny d'estratègies per millorar el rendiment de l'accelerador. Mitjançant una sèrie dexperiments en simulació, hem elaborat una sèrie de propostes concretes per solucionar els problemes detectats i millorar NDMiner.

**Paraules clau:** Graph Pattern Mining (GPM), Near-Data Processing (NDP), Graph Mining Acceleration, Locality, Hardware Simulation, ZSim, Ramulator

#### Mathematics Subject Classification (MSC): 68R10

# Contents

| $\mathbf{A}$  | bstra                            | let                                                                                                                                                                                                       | i                                                                                  |

|---------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| $\mathbf{Li}$ | st of                            | Figures                                                                                                                                                                                                   | vi                                                                                 |

| $\mathbf{Li}$ | st of                            | Tables                                                                                                                                                                                                    | vii                                                                                |

| 1             | <b>Intr</b><br>1.1<br>1.2<br>1.3 | roduction         Motivation                                                                                                                                                                              | <b>1</b><br>3<br>3<br>4                                                            |

| Ι             | Ba                               | ackground                                                                                                                                                                                                 | 6                                                                                  |

| 2             | <b>Gra</b><br>2.1<br>2.2         | <b>ph Structures</b> What is a graph (data structure)?         Databases and real-world graphs                                                                                                            | <b>7</b><br>7<br>10                                                                |

| 3             | Gra<br>3.1<br>3.2<br>3.3         | Apph Pattern Mining         Mathematical terminolgy         Execution model         Programming example                                                                                                   | <b>11</b><br>13<br>15<br>16                                                        |

| 4             | <b>Rela</b><br>4.1<br>4.2        | ated Work         GPM acceleration problems         4.1.1 Parallelism         4.1.2 Specialized computation units         4.1.3 Optimized memory hierarchy         Previous works         4.2.1 FlexMiner | <ol> <li>17</li> <li>17</li> <li>18</li> <li>18</li> <li>22</li> <li>23</li> </ol> |

| 11            | I                                | 4.2.2 NDMiner                                                                                                                                                                                             | 25<br>28                                                                           |

| 5             | Imp<br>5.1<br>5.2<br>5.3<br>5.4  | Dementation         ZSim         Ramulator         Ramulator         Integrating ZSim and Ramulator         Implementation of NDMiner         5.4.1                                                       | <ul> <li>29</li> <li>32</li> <li>33</li> <li>34</li> <li>34</li> </ul>             |

|               |                                  | 5.4.2 Load Ellision Unit                                                                                                                                                                                  | 34                                                                                 |

|            |              | 5.4.3   | Chain of events of a NDRequest                                 | 35        |

|------------|--------------|---------|----------------------------------------------------------------|-----------|

| 6          | ND           | Miner   | workload analysis                                              | 37        |

|            | 6.1          |         | imental setup                                                  | 37        |

|            | 6.2          | -       | ,<br>S                                                         | 38        |

| 7          | Pro          | nosed   | solutions                                                      | 43        |

| '          | 7.1          | -       | ting reuse                                                     | <b>43</b> |

|            | 1.1          | 7.1.1   | Choosing the right $k$                                         | 44        |

|            |              | 7.1.2   | Using locality to balance the workload                         | 46        |

|            |              | 7.1.3   | Overlapping computation and memory accesses to hide latency    | 47        |

|            |              | 11110   |                                                                |           |

| тт         | . <b>т</b> . | п •     |                                                                | 40        |

| Π          | .1.          | Proje   | ect Management, Budget, and Sustainability                     | 49        |

| 8          | Pro          | ject M  | Ianagement                                                     | 50        |

|            | 8.1          | Task d  | lefinition                                                     | 50        |

|            |              | 8.1.1   | Project management tasks                                       | 50        |

|            |              | 8.1.2   | Research                                                       | 52        |

|            |              | 8.1.3   | Implementation                                                 | 53        |

|            |              | 8.1.4   | Experimentation                                                | 53        |

|            |              | 8.1.5   | Memory writing and oral defense                                | 54        |

|            | 8.2          | Resour  | rces                                                           | 54        |

|            |              | 8.2.1   | Human resources                                                | 54        |

|            |              | 8.2.2   | Software resources                                             | 55        |

|            |              | 8.2.3   | Hardware resources                                             | 55        |

|            |              | 8.2.4   | Information resources                                          | 55        |

|            | 8.3          | Risk n  | nanagement: overcoming obstacles                               | 55        |

| 9          | Buc          | lget ar | nd Sustainability                                              | 57        |

| Ū          | 9.1          | 0       |                                                                | 57        |

|            | -            | 9.1.1   |                                                                | 57        |

|            |              | 9.1.2   | Generic costs                                                  | 58        |

|            |              | 9.1.3   | Extra costs                                                    | 59        |

|            |              | 9.1.4   | Total cost                                                     | 59        |

|            | 9.2          | Sustai  | nability $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 59        |

|            |              | 9.2.1   | Environmental dimension                                        | 60        |

|            |              | 9.2.2   | Economic dimension                                             | 60        |

|            |              | 9.2.3   | Social dimension                                               | 61        |

| 10         | Con          | clusio  | ns and Future Work                                             | 62        |

| -0         |              |         | usions                                                         | 62        |

|            |              |         | e work                                                         | 62        |

| <b>D</b> ' |              |         |                                                                |           |

| Bi         | bliog        | graphy  |                                                                | 64        |

# List of Figures

| 2.1<br>2.2<br>2.3                                                                          | Different networks, same graph                                                                                                                                                                                                                                                                                                                                                                        | 8<br>8<br>9                                  |

|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5                                                            | Example of the embeddings of a triangle found in the graph $G$<br>Matching a tailed triangle pattern with a search tree                                                                                                                                                                                                                                                                               | 12<br>13<br>13<br>14<br>14                   |

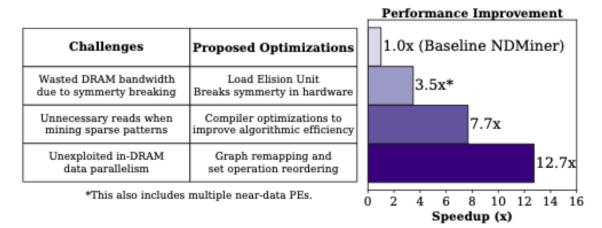

| $\begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \\ 4.7 \\ 4.8 \\ 4.9 \end{array}$ | Set operations are the majority of the workloadLong memory latency is the biggests bottleneckA von Neumann architecture schemeConcept of NDP computing architectureFlexMiner architectureLot of operations can be reused by associative property of set intersectionHardware design overview of NDMinerRedundant operations for the diamond patternNDMiner optimizations and performance improvements | 18<br>19<br>20<br>23<br>24<br>25<br>26<br>26 |

| $5.1 \\ 5.2 \\ 5.3$                                                                        | Example of how the chain of events is created in a memory acces High-level overview of Ramulator                                                                                                                                                                                                                                                                                                      | 31<br>32<br>35                               |

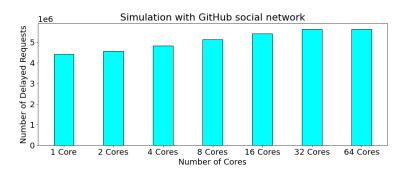

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5                                                            | NDMiner experimental setup                                                                                                                                                                                                                                                                                                                                                                            | 37<br>39<br>40<br>40<br>41                   |

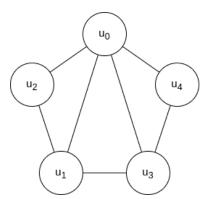

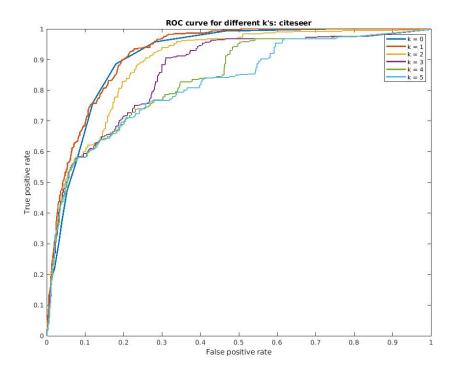

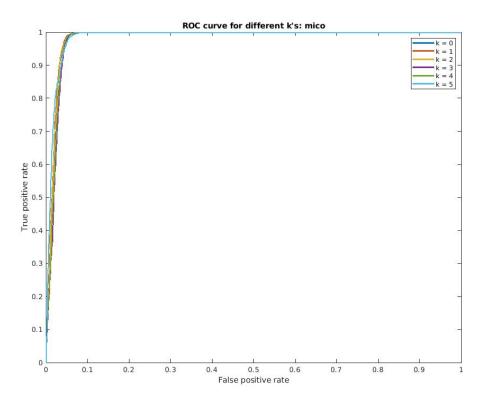

| <ol> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> </ol>                             | Pentagon pattern          ROC curve for the citeseer dataset          ROC curve for the mico dataset          No need to wait for the full result to continue with the execution                                                                                                                                                                                                                      | $45 \\ 45 \\ 46 \\ 47$                       |

| 8.1                                                                                        | Summary of project tasks                                                                                                                                                                                                                                                                                                                                                                              | 51                                           |

# List of Tables

| 2.1 | Datasets used in this work                                                            | 10 |

|-----|---------------------------------------------------------------------------------------|----|

| 4.1 | FlexMiner - NDMiner comparisson                                                       | 27 |

| 7.1 | Area under the curve for the different datasets and $k$ 's $\ldots$ $\ldots$ $\ldots$ | 46 |

| 7.2 | Trade-off of bringing data to the cache                                               | 47 |

| 7.3 | Trade-off of doing an operation in the ND-engine                                      | 47 |

# Chapter 1

# Introduction

To understand a complex system, we must first understand how its components interact between them. To put it another way, a map of its wiring diagram is needed. A graph is a catalog of a system components, which are often referred to as nodes or vertices, as well as the direct interactions between them, which are referred to as links or edges. This graph representation provides a common language for studying systems that may be vastly different in appearance, nature, or scope [1]. Thus, graphs are mathematical structures that are used for describing relations between entities and are used almost everywhere.

Graph Mining is a collection of tools and techniques that are used to: (a) investigate the characteristics of real-world graphs; (b) predict how the properties and structure of a graph may affect a given application; and (c) create models capable of producing graphs that match the patterns that appear in real-world graphs.

Graph pattern mining (GPM) has emerged as a new class of data-intensive applications that has aroused interest in the architecture [2, 3, 4] and system [5, 6, 7] fields. GPM has a wide range of real-world applications, including pattern search over semantic data and motif extraction from gene networks. GPM differs fundamentally from general graph processing applications in some ways: (a) the computation uses more complicated iterations that could lead to load imbalance; and (b) there are numerous data accesses during the computation. As a result, using traditional hardware (such as a CPU or GPU) to speed up the computation is difficult.

Due to these challenges, graph mining algorithms have recently evolved and hardware has accelerated. The architectural paradigm known as Near-Data Processing (NDP), also referred to as Processing-in-Memory (PIM), has shown promise in overcoming the memory wall issue for data-intensive applications. The latency and energy overheads associated with data movements can be significantly reduced by moving the computations closer to the data locations in the main memory. Additionally, we can make better use of the memory device limited internal access paths and data bandwidth.

Increasing the data access bandwidth is the key to optimizing the performance of large-scale graph processing. However, there are five difficulties in achieving high bandwidth on conventional architectures [8, 9]:

- Intensive Data Access: On the one hand, graph applications typically result in a lot of requests for data access. Graph processing, on the other hand, has a high data-access-to-computation ratio, meaning that the majority of its operations are connected to data accesses.

- Irregular Computation: The power-law distribution causes a wide range in the computation workloads for various vertices. This will result in a serious problem with workload imbalance and communication overhead.

- Poor locality: For a straightforward operation on one vertex, access to all of its neighbors may be necessary. Such poor locality causes inefficient bandwidth utilization on multi-processing unit architecture and erratic access to global data.

- Redundant set intersection operations: GPM is defined as a search tree exploration process starting from each vertex in the graph, and then the following potential vertex is used to extend on the partially matched subgraph using set intersection and subtraction operations. The set intersection operation becomes the bottleneck due to the frequent computation of the candidate vertices and can consume the majority of the execution time. However, most of set intersection operations are unnecessary, i.e., the same set of vertices is being encountered, and the same set intersection operation is done.

- High Data Dependency: The graph vertices connections nature is what leads to the data dependency. It is challenging to investigate the parallelism in graph processing due to heavy dependencies. Data conflicts may appear.

The overall result is that memory has become a bottleneck and current frameworks are not suitable for this type of applications.

To face these challenges, a system-level simulator, capable of simulating multithreaded applications in a full-system environment with a complete operating system on a heterogeneous multi-core system, can be required. Furthermore, the simulator should also be capable of a detailed system-level profiling to identify the bottlenecks, therefore, helping in designing strategies and architectures to alleviate these bottlenecks.

In this work, we develop a new simulation tool, based on ZSim+Ramulator, capable to replicate the operation of a state-of-the-art graph pattern mining accelerator

using near-data processing (NDMiner), analyzing their workload and identifying their bottlenecks.

In Section 1.1, we give a summary of the major issues and research issues that this work addresses. The main contributions of this work are then discussed in Section 1.2. Finally, we describe its structure in Section 1.3.

## 1.1 Motivation

Near-Data Processing (NDP) is an architectural paradigm to address the challenges for GPM applications. Typical 3D stacked memory based NDP systems contain massively parallel processing units, each of which can access its local memory as well as other remote memory regions in the system. In such an architecture, minimizing remote data access and achieving compute load balancing presents a critical tradeoff, where existing solutions can only enhance one but sacrifice the other.

However, NDP systems provide an opportunity for emerging data-intensive applications. Currently, there are several research works on the integration of the computation unit with the logic layer of 3D-stacked DRAM. To develop these techniques, a system-level simulator, capable of simulating multi-threaded applications in a full-system environment with a complete operating system on a heterogeneous multi-core system, can be required.

The motivation for this work is to simulate the architecture of the-state-of-the-art NDP GPM accelerator. For this, we have to design a new simulation tool, which has used to analyze the workload of the NDMiner framework, detect their bottlenecks and propose strategies to solve the problems derived from the trade-off between data access optimization and load balancing. Consequently, we have elaborated a series of concrete proposals to solve some of the problems detected.

## 1.2 Contributions

On this thesis, we focus on a state-of-the-art architecture for GPM acceleration that moved the computation closer to the memory: NDMiner.

In order to be able to analyse its weak points and address possible solutions, we will go over the following steps:

• Development of a new simulation tool based on ZSim+Ramulator. We join two simulators: ZSim for the cores and the caches and Ramulator for the memory. The need to carry out this integration arises from the fact that the available implementation does not leverage the techniques ZSim uses to reduce the loss of accuracy.

- Implementation in simulation of NDMiner. The NDMiner framework have been implemented in the simulator, and the results published by the authors have been reproduced, as verification of the correct installation and operation of the simulator.

- **NDMiner workload analysis.** Using the simulation tool, we have analyze the NDMiner workload, performing a detailed profiling identifying their main bottlenecks.

- Solution proposals. Using the analysis done in NDMiner we will propose solutions to alleviate the bottlenecks found.

## 1.3 Thesis Outline

Here, we provide a reader's guide and a summary of the material covered in the chapters. Most of the chapters stand alone to make them easier to read. The three major sections of the thesis are as follows:

### Part I: Background

The objective of this part is to provide a context to the work. This part contains the justification of the research, a description of the main aspects addressed in it, the work itself, and a review of previous relevant studies.

#### Part II: Implementation and Results

This part describes the essential aspects of the work and therefore brings together the most relevant content. This part includes (a) the description of the simulation tool that we have developed, based on the integration of ZSim and Ramulator; (b) the implementation in simulation of NDMiner graph mining accelerator, which we have used as a reference for the state-of-the-art with NDP architecture; (c) the reproduction of the results published by the authors, as verification of the correct installation and operation of the simulator; (d) the NDMiner workoad analysis, identifying weak points; and (e) the proposal of concrete strategies that alleviate them and, therefore, improve the NDMiner performance.

### Part III: Project Management, Budget, and Sustainability

This part describes the planning required by the project, the resources used for the work, and the management of difficulties encountered during its development. This part also covers the project budget and the three main elements of its sustainability: economic, social and environmental.

# Part I

# Background

## Chapter 2

## Graph Structures

### 2.1 What is a graph (data structure)?

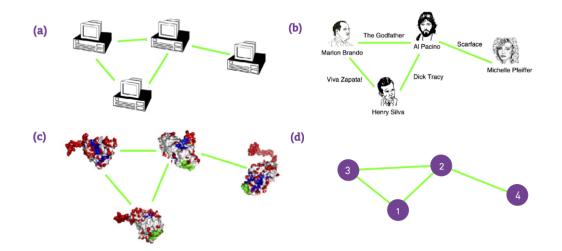

Graph structures are a very natural way of representing natural links in our world. They are comprised of a set of vertices and the links between one another. An object such as a protein as part of a biological network or an individual in a social network is represented by a vertex in a graph. An interaction, like a friendship in a social network, or a biochemical relation between two proteins within a cell [10] corresponds to an edge in such a network. A common language to study systems that may be very different in scope, appearance, or nature is provided by this network representation. The network representation is the same for three distinctly different systems as seen in Figure 2.1.

This concept can conveniently be applied to real-world situations like human relationships or molecular interactions. Therefore there has been high interest in this type of structures in the last decades as a way to understand interactions between entities. Some of its most common applications can be found in social networks, cyber-security and e-commerce (Figure 2.2).

Mathematically, a graph G is defined as an ordered pair (V(G), E(G)) where V(G) refers to the set of vertices and E(G) to the set of edges. All elements in E are a pair of vertices of V(G). Then, we say that u is connected to  $v \in V(G)$  if  $(u, v) \in E(G)$ . We differentiate between directed and undirected graphs depending on if the pairs in E(G) are ordered or not. In other words, depending on if (u, v) is equivalent to (v, u). If they are equivalent, then the graph is undirected. In this case the neighborhood of  $v \in V(G)$ , N(v) is all u such that (u, v) or  $(v, u) \in E(G)$ . If they are not equivalent then the graph is directed and we separate the nodes linked to v in outward and inward neighbors depending on the order in the pair. In this thesis, we will focus on undirected graphs.

Figure 2.1: The same graph for different networks. (a) routers in the Internet; (b) actors that played in the same movie; and (c) proteins that can bind to each other in the cell. While the links and the nodes are different, the representation is the same, consisting of N = 4 nodes and L = 4 links, as shown in (d) [1].

Figure 2.2: Graph usage in different fields.

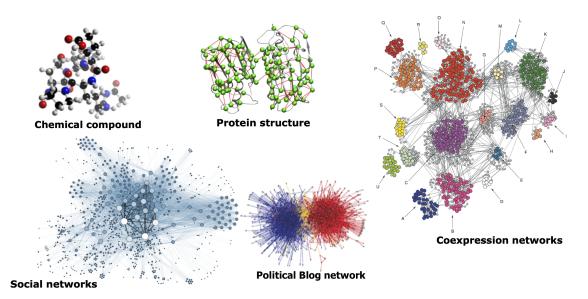

Figure 2.3: (a) An example graph; (c) An adjacency list for the example graph; (d) An adjacency matrix for the example graph; (e) CSR representation of example graph [11].

One of two common data structures is typically used to represent graphs: adjacency matrices (Figure 2.3(c)) and adjacency lists (Figure 2.3(d)). Both data structures are essentially arrays with vertices as their indices; In order to achieve this, each vertex must have a distinct integer identifier between 1 and V.

The adjacency list is the most typical data structure for storing graphs. An adjacency list is an array of lists, each of which contains the neighbors of a particular vertex (or, in the case of a directed graph, the out-neighbors).

For graph analysis applications in which the graph itself is not modified, Compressed Spares Row (CSR) representation (Figure 2.3(e)) is more frequently used. This representation consists of two arrays. One of them is the concatenated neighborhood lists of each vertex in the graph. The other is a pointer to the start of the neighborhood list itself. It is more compact, but it is not easy to modify any of the neighborhood lists. Therefore it is only suitable for static graphs and applications that do not apply transformations.

|                   | V         | E               | Max degree |

|-------------------|-----------|-----------------|------------|

| wiki              | 8 298     | $103 \ 689$     | 893        |

| Citeseer          | $3 \ 312$ | 4536            | 99         |

| $\mathbf{Github}$ | 37  700   | $289\ 003$      | $6\ 809$   |

| Mico              | 100  000  | $1 \ 080 \ 156$ | $1 \ 359$  |

Table 2.1: Datasets used in this work

## 2.2 Databases and real-world graphs

Real-world graphs also typically have the following characteristics [12]:

- Power law A power law vertex degree distribution is a characteristic of many real-world graphs. The power law degree distribution has the effect that most vertices have low degrees, but a small number of vertices will have very high degrees. When processing a scale-free graph in parallel, this property, known as scale-free in literature, can result in a significant load imbalance.

- Small diameter or small world property Despite being sparse, many graphs are linked together to form enormous connected components with tiny diameters. The longest shortest path between any two graph vertices is the diameter of the graph.

- Community Structure Communities are the collective nodes that connect to form interconnected clusters. There are more connected edges than outgoing edges in a cluster. This characteristic causes some clusters to be highly interconnected while having few connections to other clusters.

The graph databases that we used and their key features are listed in the table in Table 2.1

## Chapter 3

# Graph Pattern Mining

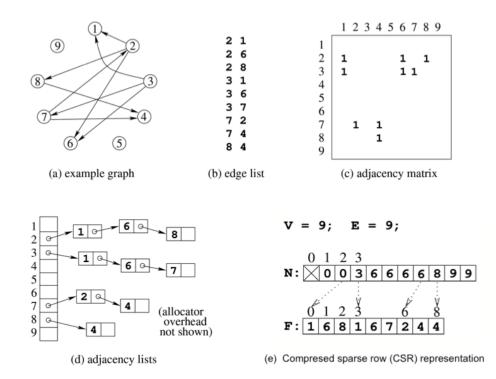

The main goal of Graph Pattern Mining is, given a graph data set G and a set of graph patterns  $\mathcal{P} = \{P_1, P_2, ..., P_n\}$  find all embeddings of P in G. An example is shown in Figure 3.1.  $\mathcal{P}$  is only one graph, a triangle and there are three different embeddings of it in G.

The study of patterns in actual graphs is relevant because it is important: [13]:

- Comprehending human (also protein, machine) behavior: By identifying patterns of connectivity, domain experts (biologists, sociologists) may be able to create hypotheses that explain when and how humans (proteins, machines), or their parts, interact with one another.

- Anomaly detection: neither anomaly nor "normal" can be perfectly defined but we can say that an anomaly is an event (node, subgraph), whose characteristics are very infrequent, and thus very different from most of the other population. We also search for local anomalies, that is, very particular edges, subgraphs, or nodes. They should differ from the "normal" patterns, so knowing the patterns that appear most commonly in graphs is necessary for the detection of such outliers.

- Graph compression: Data regularities that can be used to compress the data are represented by graph patterns. Keeping and compressing historical data is crucial for internet-scale graphs like Facebook, which at the time of writing this has "more than 950 million active users".

A naive approach to find the embeddings would be to enumerate all subgraphs of G with the same number of vertices as each  $P \in \mathcal{P}$  and check if they are equivalent to G. Nevertheless, we work under the premise that  $\mathcal{P}$  is known. In other words, we

Figure 3.1: Example of the embeddings of a triangle found in the graph G

know how the topology of each  $P \in \mathcal{P}$ . We can take advantage of that information to narrow the search.

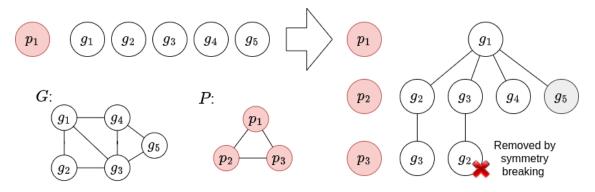

To illustrate how this can be done we walk through the example shown in Figure 3.1. Each step will be illustrated in Figure 3.2. We will map each vertex of P to possible candidates in G one by one. First, we start with node  $p_1$  in P. We could map it to any other vertex in G, so we add all of them as possible candidates. Let's focus on the case where  $g_1$  in G is mapped to  $p_1$ . Now, we decide we are matching  $p_2$  in P. We know that  $p_1$  and  $p_2$  are connected, therefore, because we want to maintain the structure of the pattern, we also require the same thing from their correspondent mapping in G. In other words, the candidates to be mapped to  $p_2$ will need to be connected to  $q_1$ . The same reasoning is followed for the mapping of  $p_3$ . As we can see, we have arrived to two possible mappings. Nonetheless, they are both the same. That is because the pattern P is symmetric. We could for example interchange any two nodes and we would still end up with the same pattern. To remove those symmetries we "block" those changes by imposing an order over the vertex in P. We not only consider the connectivity between the nodes in P but also the order we impose. In this case, we impose that if f is the mapping, then  $f(p_1) > f(p_2) > f(p_3)$ , where the relationship ">" is decided using the ids of the vertices.

Now, we will proceed to introduce the mathematical terminology to formally define GPM queries.

Figure 3.2: Matching the triangle to the Graph G. At each step, we extend the mapping by adding new vertices that comply with the topology of the pattern P we are searching for.

Figure 3.3: Example of an isomorphism between G and H. Every  $u_i$  is mapped to  $v_i$ .

## 3.1 Mathematical terminolgy

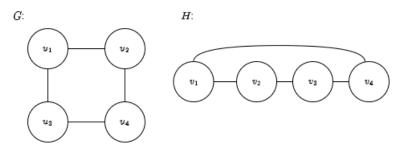

**Definition 3.1.1** (Graph isomorphism). Given G and H two graph structures.  $f: G \to H$  is a **graph isomorphism** if it is a bijection between the vertex sets and if  $(u, v) \in E(G)$  if and only if  $(f(u), f(v)) \in E(H)$ . In other words, it is a bijection between the vertex sets that preserves the topology of the graph. If such f exists then we say that G and H are **isomorphic** and we denote it with  $G \cong H$ .

If we ignore differences between individual nodes, isomorphism captures the idea that two networks have the same edge structure, that is, the same topology. This concept is illustrated in Figure 3.3. The graph structure is the same, and they are isomorphic, despite their apparent differences.

**Definition 3.1.2** (Graph automorphism). A **graph automorphism** is an isomorphism from the graph onto itself. It is a form of symmetry of the graph.

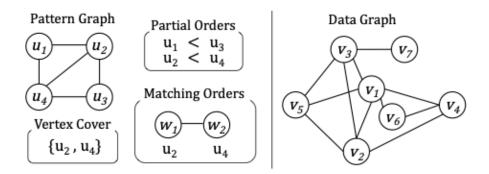

**Definition 3.1.3** (Partial order). The **Partial order** is a set of order rules we impose over the identifiers of the vertex to eliminate the possibility of an automorphism (Figure 3.4). That is, to avoid non-canonical matches we break the symmetries of a

Figure 3.4: Data graph, Pattern graph, and partial and matching orders definition [14]

Figure 3.5: Projection of G over  $S = u_1, u_2$ .

pattern p by enforcing a partial ordering on matched vertices [15]. For this, we must enumerate all automorphisms of the pattern p to find symmetries, and iteratively sorting pairs of symmetric vertices until the only automorphism that matches the ordering is the one mapping each vertex to itself [14]. The partial ordering for the Figure 3.4 example pattern is u1 < u3 and u2 < u4. From now on, we will refer to the partial order as  $\mathcal{PO}$

**Definition 3.1.4** (Connected graph). Given G a graph structure. We say it is a **connected graph** if and only if  $\forall u \in V(G), \exists v \in V(G)$  such that  $(u, v) \in E(G)$ .

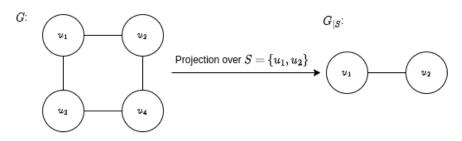

**Definition 3.1.5** (Projection of a graph). Let  $S \subseteq V(G)$ . The **projection** of V(G) over S is the graph H such that V(H) = S and  $(u, v) \in E(H)$  if and only if  $u, v \in S$  and  $(u, v) \in E(G)$  (Figure 3.5).

**Definition 3.1.6** (Matching order). It is the order in which we will be mapping the vertex of P to G (Figure 3.4. Let  $N_P$  be the set of natural numbers smaller or equal than |V(P)|. The **matching order** of the subgraph P is a bijection  $\pi : V(P) \to N_P$  such that  $\forall i \in N_P$ , the projection of P over  $\pi^{-1}([1..i])$  is a connected subgraph of P. From now on we will also refer to  $\pi(u)$  as the **matching order** of u and we will denote the projection of P over  $\pi^{-1}([1..i])$  as  $M_i^{\pi}$ .

The connectivity requirement is not usually included in the matching order definition, but it is employed in the most common algorithms because it allows to cut down in the number of iterations executed in the search.

Notation 1. We will denote the projection of P over  $\pi^{-1}([1.i])$  as  $M_i^{\pi}$ . This will be the subgraph of P that has already been mapped at step i.

Notation 2. For clarity, unless indicated otherwise, we will use  $u_i$  to refer to  $\pi(i)$ .

**Definition 3.1.7** (i-partial match). Let  $0 < i \leq |V(P)|$  and  $\pi$  a matching order of P. An **i-partial match** of P is an isomorphism  $f : M_i^{\pi} \to G$ . We will denote the space of these isomorphisms as  $R_i^{\pi}$ . We will refer to  $f(M_i^{\pi}) = A_i^f$  or **i-antecesors** of f. This is the subgraph of G that has been mapped to  $M_i^{\pi}$  at step i.

**Definition 3.1.8** (Backwards neighbors). Let  $u \in V(P)$  such that  $\pi(u) = i$ . The **backwards neighbors** of u is the set  $N^{\pi}_{+}(u) = \{w \in N(u) | \pi(w) < i\}$ , i.e, they are the neighbors of u that have smaller matching order.

**Definition 3.1.9** (Candidate set). Let  $\pi$  be a matching order of P. Let i < |V(P)|. Given f an i-partial match, the (i+1)th **candidate set**  $C(f|i+1) = \{v \in G | \forall u \in N^{\pi}_{+}(u_{i+1}), (f(u), v) \in E(G)\} = \bigcap_{v \in A^{f}_{i} | f(u) = v, u \in N^{\pi}_{+}(u_{i+1})} N(v).$

**Definition 3.1.10** (Result set). At step i+1 the result set is  $Z_{i+1} = C(f|i+1) \setminus A_i^f$ . It is those candidates vertices that have not been yet mapped to a  $u_j, j < i+1$ . If  $f = \{(u_1, v_1), ..., (u_i, v_i)\}$ , it is the set of vertices  $v \in V(G)$  such that  $f' = f \cup (u_{i+1}, v) \in R_{i+1}^{\pi}$ .

## 3.2 Execution model

Using the terminology presented, the search model for one P is shown in Algorithm 1. At each i-step, we take all i-partial matchings and try to expand them with the mapping of 1 more vertex. In line 6, we impose the connections pattern P have. In line 7 we remove redundancies, in other words, we avoid a vertex appearing more than once. Finally, we apply the partial order rules to avoid automorphisms in the final mapping. This gives us the set with the vertices that are candidates to be mapped to the i + 1 vertex in P. This algorithm finds all embeddings because at each step we guarantee that all vertex that maintain the initial topology of the pattern are added as candidates. At the same time, we also guarantee that vertex that do not maintain it are added.

As we had seen in the example in Figure 3.2, at each step we were extending a tree. From now on, we will refer to it as **Search Tree**. In Algorithm 1 we are expanding said tree in a BFS manner. Still, a DFS execution in which we complete each whole isomorphism one by one is more beneficial for hardware as it better exploits temporal reuse in the data. In line 6, we do the intersection of neighborhood lists of nodes previously matched. If we go branch by branch, there is a higher chance the neighborhood lists of the ancestors will still be present in the cache.

Algorithm 1: GPM search in BFS

Data:  $G, P, \pi, \mathcal{PO}$ **Result:**  $R_n^{\pi}$  where n = |V(P)| $\mathbf{1} \ R_1 \leftarrow \{f \mid \overset{\sim}{f} = \{(u_1, v)\} \quad \forall v \in V(G)\};$  $\mathbf{2} \ i \leftarrow 1;$ **3 while**  $R_i \neq \emptyset$  and  $i \leq n$  do  $R_{i+1} \leftarrow \emptyset;$  $\mathbf{4}$ for each  $f \in R_i \in do$  $\mathbf{5}$  $C(f|i+1) \leftarrow \bigcap_{v \in A_i^f|f(u)=v, u \in N_+^\pi(u_{i+1})} N(v) ;$ 6  $Z_{i+1} \leftarrow C(f|i+1) \setminus A_i^f;$  $\mathbf{7}$  $\widetilde{Z_{i+1}} \leftarrow ApplyPO(\mathcal{PO}, A_i^f, Z_{i+1});$ 8  $R_{i+1} \leftarrow R_{i+1} \cup \{f \cup (u_{i+1}, v), \forall v \in \widetilde{Z_{i+1}}\}$ 9  $i \leftarrow i + 1;$ 10

## 3.3 Programming example

In this section, we present how the algorithm already presented looks when it goes over the Search Tree in a DFS manner for the triangle (Algorithm 2). The final result in this case is the set of vertices of G in the order they have been mapped to the triangle.

```

Algorithm 2: Triangle search in DFS

Data: G

```

**Result:** F1  $F \leftarrow \emptyset$ ; 2 foreach  $v0 \in G$  do foreach  $v1 \in N(v0)$  do 3 if v1 > v0 then  $\mathbf{4}$ break;  $\mathbf{5}$ foreach  $v2 \in N(v_0) \cap N(v1)$  do 6 if v2 > v1 then 7 break; 8  $F \leftarrow F \cup \{(v0, v1, v2)\}$ 9

# Chapter 4

## **Related Work**

### 4.1 GPM acceleration problems

General purpose processors are not designed to deal with this type of workloads. There have been numerous proposals to design hardware accelerators that better address their main necessities. In this chapter, we will go over the opportunities to accelerate GPM with hardware and describe some proposals from the literature.

#### 4.1.1 Parallelism

In Chapter 3 we saw that, in a pattern aware search, we build several Search Trees that we extend at each step to find the embeddings of the pattern in the graph data set. These Search Trees are independent from one another, and they unfold an opportunity for parallelism. Each of them can be fully extended without any need for synchronization. In order to exploit it, processors can take advantage of already existing parallel environments such as hybrid clusters, multicores, and GPUs [16]. There are some challenges a high parallel system needs to overcome [17, 12]. First, the workload is difficult to distribute due to the power-law distribution in graphs. The threads/cores that take the Search Trees with highly connected root nodes will have a much higher workload. In order to address this issue work stealing paradigms have been proposed [18]. Then, it becomes a problem of data transfer. If a core wants to steal the work a different core started, it will also need to take the current progress (Search Tree) as it is a crucial part for finishing the computation.

#### 4.1.2 Specialized computation units

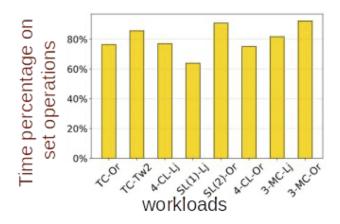

Normal processors are equipped with an arithmetical logic unit (ALU). The capabilities they offer do not align with the necessities of set operations. Figure 4.1 is an analysis of the weight of set operations in GPM workloads for GPUs. For every application, it is over 60%. Amdahl Law is a very common concept in computer science. It states how much speedup we can gain if we only improve a part of the workload. A clear and very intuitive conclusion is that to obtain the best improvements we should focus on the part of the computation that takes up most of the execution. If we apply Amdahl Law to figure 4.1 we can conclude that we can improve performance a lot if we optimize set operations. Several hardware accelerators have implemented special set operation units [19, 20].

Figure 4.1: Set operations are the majority of the workload [19].

#### 4.1.3 Optimized memory hierarchy

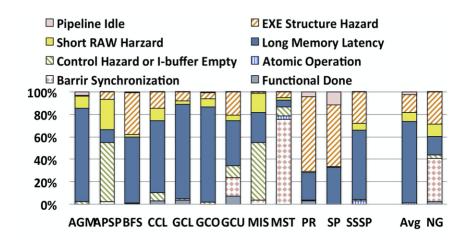

Graphs suffer from very irregular memory access patterns due to their connection focus nature. For this reason, typical solutions to optimize memory accesses do not work here. Prefechers are based on identifying a pattern in the access addresses. Caches, optimize the memory accesses based on the observation that data has spacial and temporal locality. Because of how randomized accesses are in these workloads, spacial locality does not apply. The only thing left is temporal locality, in other words, reusing the same data. What ends up happening is that, in graph applications, accesses typically end up relying on main memory as we can see in Figure 4.2.

Some proposals focus on ways to pre-process so it is stored in memory in a way that better aligns with current memory access optimizations. One of the simplest pre-processing strategies is ordering vertex by degree. If the graph is saved in CSR

Figure 4.2: On average, long memory latency is the biggest bottleneck that causes over 70% of all pipeline stalls in graph applications [21].

format that will mean that the neighborhood lists of all of the highest connected nodes will be together. There is a very high chance that we will constantly move between them, as these nodes are also likely connected with one another. By sorting the vertices by degrees we aim at putting together the main cluster (collection of highly interconnected nodes). Other proposals try and define more fine-grained clusters to improve the same concept.

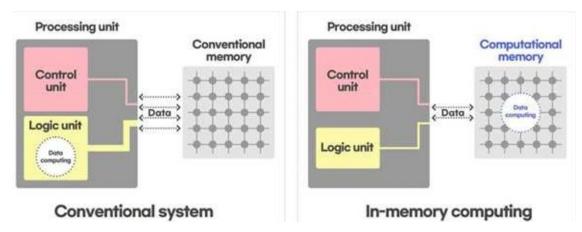

Other proposals change the whole processor architecture to a more memory focused approach. They put computation closer to the memory. If the computation takes place inside the memory, it is called **Processing-in-Memory (PIM)** and **Near-Data-Processing (NDP)** if it is close to it.

#### Near-Data Processing (NDP)

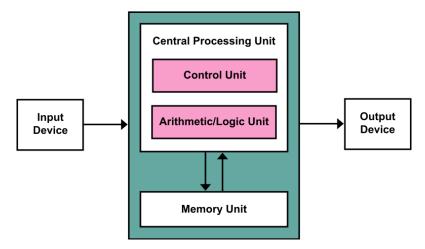

Processors usually follow the Von-Neumann arquitecture model (Figure 4.3). The computation is fully relegated to the cores and the only task of the memory is storing the data. Near-Data-Processing and Processing-In-Memory aims at breaking that separation by putting computation closer or inside it, respectively (Figure 4.4). Some new memories like HBM (High Bandwith Memory) or HCM (Hybrid Memory Cube) have already been designed with a logic layer that can support small computation components.

One of the key properties these systems try to exploit is the difference in bandwidth. The amount of data that can move from the memory to the NDP logic per time unit is much bigger than to the cores. The main execution is still taken care of by the cores. Therefore, the main goal is pre-process the data in NDP to reduce it and then later send it to the cores to continue their execution.

Figure 4.3: A von Neumann architecture scheme.

Figure 4.4: Concept of NDP computing architecture.

NDP also comes with some limitations, the most important for us being:

- Simple logic: The logic we are able to put so near to the memory has to be simple, as there is not a lot of area. Also, we need to take into account that the memory goes at a different frequency compared to the cores, making the computation slower.

- Coherence with the caches cannot be broken: Data can also be copied in the caches along the processor. Caches have protocols to ensure that different copies along the caches are consistent with one another. MESI (Modified-Exclusive-Shared-Invalid) is one of the most spread. It keeps track of how the current state of a cache line and makes the necessary changes when a core issues a request. The same coherence protocol cannot be extended to main memory given that it would be unfeasable to keep track of the state of all the data we have. Therefore, if the NDP logic is allowed to modify the data in main memory, there needs to be a system in place to notify the caches, or the data itself is marked as non-cacheable.

#### Why NDP for GPM?

We now list the properties of GPM that make them suitable for Near-Data (NDP) architectures:

- Read only data and a static structure: The range of GPM problems we are considering work with static graphs, in other words, they do not change their structure as the execution progresses. At the same time, GPM only aims at searching for embeddings, it does not modify the data structure at any point. Therefore, if the data is only going to be read, all copies will be consistent with one another.

- Early reduction of data: In GPM, we have two opportunities to reduce the read amount of data and only move to the core what is necessary to continue with the execution.

- Symmetry breaking: Part of the neighborhood lists are discarded while applying the symmetry imposed in the pattern to avoid automorphisms.

- Set difference and intersection: In GPM, for every operation we want to do (set intersection or difference), we have to load both inputs into the cores. However, we only use the result to continue the execution of the program, and it takes a much less space. For these two operations, the result is the subset of both or one of the inputs.

$$X \cap Y = Z, \quad Z \subseteq X, Y \tag{4.1}$$

$$X \setminus Y = Z, \quad Z \subseteq X \tag{4.2}$$

If they are computed in the memory, we can see a high reduction in the data movement between the core and main memory.

• Simple arithmetic operations: Symmetry breaking can be implemented with comparator logic. When the data read surpasses a threshold, it is stopped. The intersection of sets can be simply done with adder and comparator logic. The same goes for the difference.

For these reasons, it might be beneficial offloading some of the set operations and symmetry breaking to NDP engines to try and obtain a better performance.

### 4.2 Previous works

The development of Graph Pattern Mining accelerators always goes in hand with the latest software developments. The algorithm presented in this thesis, commonly referred to as "think-like-an-embedding", was already being used early in frameworks like Arabesque traversing the search tree in BFS [6]. Then, several other proposals started adding more optimizations. G-Miner [22] introduced task-based asynchronous execution, Fractal [18] suggested using DFS to reduce the memory footprint, and aDFS [23] used an almost-DFS exploration that combined the advantages of both DFS and BFS. Using this programming paradigm, Gramer [4] was the first hardware accelerator for graph pattern mining, and it achieved a significant improvement compared to software approaches.

AutoMine [5] was the first to represent graph pattern mining tasks as set intersect and substract operations, and used a custom compiler to create optimized plans for each pattern. Such pattern-aware paradigm was able to match the performance of highly optimized algorithms, with additional optimizations like symmetric breaking and search order scheduling in: GraphPi [24], Pangolin [25], GraphZero [26], and Sandslash [27]. These optimizations exploit locality, reduce memory consumption, and mitigate the overheads of dynamic memory allocation and synchronization [28].

This improvement on the algorithm leads to a new generation of accelerators, including FlexMiner [19] (a standalone accelerator), IntersectX [3] (an ISA extension for general-purpose processors), and SISA [2] (a design for processing in memory). This new methods expose a high level of parallelism. Instances of more recent methods are: Fingers [29], which computes the set operations in parallel with vectorized units and uses a pseudo-DFS order to expose enough independent tasks to effectively utilize resources; and ABNDP [30], which uses a distributed DRAM cache, where the computation load can be distributed and balanced, without significantly increasing remote accesses [28].

In this section we will focus on two of the last proposed architectures to analyze how to tackle the different improvement opportunities.

#### 4.2.1 FlexMiner

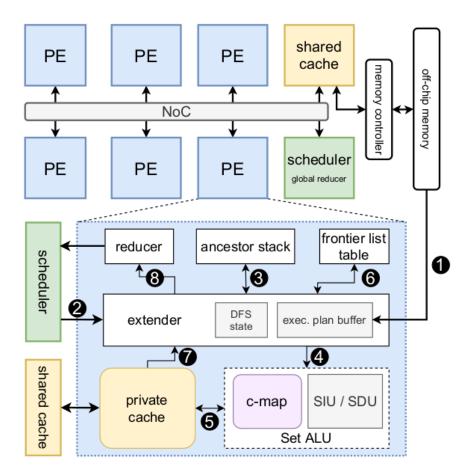

FlexMiner is a hardware accelerator developed by researchers at MIT [19]. It has several DFS walkers that traverse the Search Trees with specialized units for set operation units. Each Processing Element works independently from another, as a Search Tree is always completed by only one Processing Element. By doing so it is able to exploit the opportunities for parallelism as well as optimizing set operations. In Figure 4.5 we can see how a single PE is built.

Figure 4.5: FlexMiner architecture [19]

The step required to complete each pattern is loaded by an off-chip memory into the extender. Then, the workload is distributed by the scheduler. It assigns a vertex v of the graph to each PE. Then, the PE starts creating and extending the Search Tree with v as root. The ancestor stack saves the vertices of G that have been mapped to the pattern so far in the branch we are traversing (partial match). The frontier list table saves the information necessary to access the candidate sets that we progressively compute at each extension step. At each extension, we only take one vertex of the candidate set to add to the stack because we are following a DFS model. The rest of the candidate set will be used when we traverse back.

At each extension step, the set operation unit loads the neighborhood lists necessary to compute the candidate set. The generated result set is loaded into the cache and its information is saved into the frontier list table. Then, the extender takes one vertex and loads it into the ancestor stack. The same steps are repeated until the mapping from graph to pattern is completed. Then, we traverse back in a DFS manner to obtain the next embedding. The same process is repeated over and over until the Search Tree is complete.

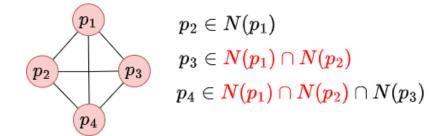

In the traverse of the search tree, there are a lot of redundant operations due to the associative property of set intersections. In Figure 4.6 there is an example of a pattern in which we will be able to reuse the intersection done to compute the candidate vertices for  $p_3$  in the computation of the candidate vertices for  $p_4$ . This type of reuses is easier to exploit if we are traversing the Search Tree in a DFS manner. We need to keep fewer results in memory because we are tackling the Search Tree branch by branch. FlexMiner takes advantage of what DFS walk is doing and adds another element to automate these reuses: the c-map. We will not go into the design. Still, it is worth mentioning it is another optimization on the DFS walk.

Figure 4.6: In the same branch of the search tree, a lot of operations can be reused if we apply the associative property of set intersection.

By optimizing the two first points (parallelism and specialized computation units) and the DFS walk (and the computation reuses that come with it) in hardware, FlexMiner significantly improved the performance obtained by state-of-the-art software optimization (GraphZero).

Figure 4.7: Main hardware components of NDMiner [20].

#### 4.2.2 NDMiner

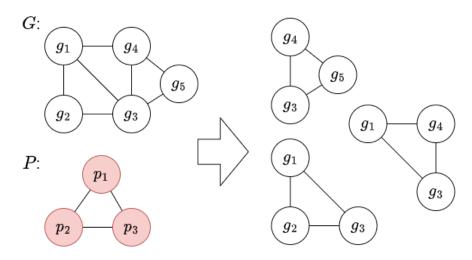

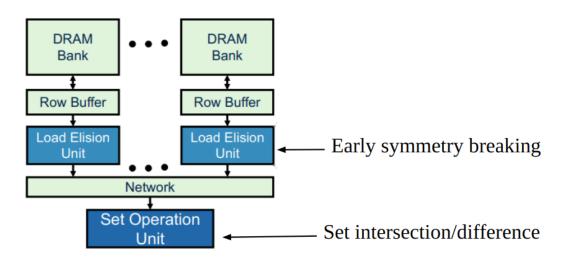

FlexMiner improved GPM performance by mainly focusing on the computation of the workload. NDMiner [31] is a different proposal developed at the University of Michigan that focuses on the memory side. They move the set operation units closer to the memory (outside the network) and apply the symmetry breaking at bank level in the Load Ellision unit. An overview of the components can be seen in Figure 4.7.

To understand why each of these components is in those places we need to look into how sets are being saved in the memory. Each neighborhood list is saved only in one bank. Then, we interleave the neighborhood lists between banks. The neighborhood list of vertex 0 will be in the first bank, the list of vertex 1 in the next bank, and so on.

The Load Ellision Unit works under the premise that neighborhood lists are ordered. This is a common assumption in GPM because it makes it easier to perform the set operations. To apply the symmetry breaking, we put an upper bound to the ids of the vertices of the set. Once that upper bound is surpassed, we cut off the reading of the set. Because the set is all in the same bank this can be done at that level.

The set operation unit needs to be able to access all neighborhood lists. Because they are distributed among all channels, ranks, and banks it needs to be able to access all the memory. Therefore, it needs to be put after the network. This will mean that the main memory bandwidth set operation units see is the same as the cores. We observe that the actual position of these components will highly depend on how the graph is mapped to the memory. If neighborhood lists were distributed among different banks and at each bank we could perform a part of each operation,

Figure 4.8: Redundant operations for the diamond pattern.

then we could move the set operation unit to bank level. The NDP engine issues requests for the sets it needs to the main memory. To allow ND cores to finish their computation as early as possible, it avoids having concurrent operations that access the same banks. It does so by reordering the requests that arrive at the ND engine.

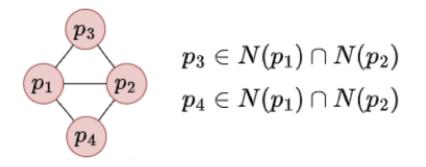

These hardware solutions are also combined with software optimizations. If two candidate sets are computed with the same operation only one request is sent to the memory and it is attached to both candidate set. This happens for instance, for the diamond pattern as we can see in Figure 4.8. Both  $p_3$  and  $p_4$  have the same connectivity, and therefore their candidates will be computed in the same way in a branch of the Search Tree. For both, only one request for a set operation is sent to the NDP engine.

How much each of these modifications increases NDMiner performance is shown in Figure 4.9.

Figure 4.9: The difficulties of accelerating GPM workloads led to NDMiner optimizations and corresponding performance gains. Optimizations build up as the bars descend [31].

There are several questions we raise with this design:

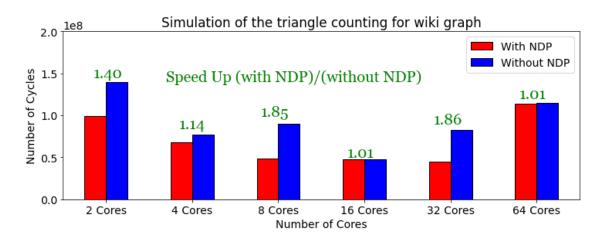

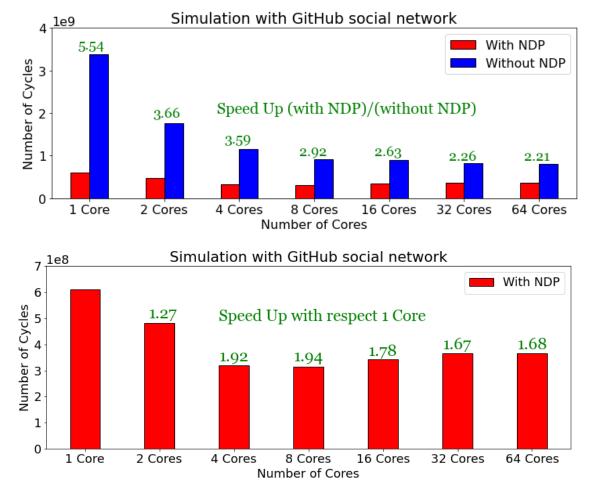

- How are cores leveraged? All of the computation is relegated to the NDP engine in this design. Therefore, if we introduce more cores to leverage the parallelism, do we bottleneck by the NDP engine?

- Do we exploit any of the reuse? Every time we do an operation the request is sent to the memory. Still, there where no mechanisms put in place to reduce redundant operations.

- Are we able to get results faster? The bandwidth the NDP core is experiencing from main memory is the same as the core because it is outside the network. Therefore, it is not taking advantage of the higher bandwidth of the internal memory.

The main goal of this thesis will be implementing the NDM iner design in a complete simulation framework to address these questions.

As a summary of these two accelerators we present Table 4.1 to represent the different points each of them exploits.

|           | Parallelism    | Specialized set<br>operation units | Reduce<br>redundant operations | Specialized<br>memory |

|-----------|----------------|------------------------------------|--------------------------------|-----------------------|

| FlexMiner | $\checkmark$   | $\checkmark$                       | $\checkmark$                   | ×                     |

| NDMiner   | $\checkmark$ 1 | $\checkmark$                       | ×                              | $\checkmark$          |

Table 4.1: FlexMiner - NDMiner comparisson

<sup>&</sup>lt;sup>1</sup>Potentially several threads could work in parallel and send requests to the NDP engine

# Part II

# Implementation and Results

## Chapter 5

## Implementation

The main goal of this work is to implement the architecture proposed in NDMiner in simulation. NDMiner focuses only on what happens in main memory while leaving the rest of the processor out of the picture. In order to be able to have detailed control over the memory we use a Ramulator [32], a popular main memory simulator that implements different memory models. Then, for the processors and caches we use ZSim[33], a simulator developed in Standford and MIT.

The amount of memories ZSim offers is pretty limited and their configuration is not standarized. Therefore there is value in joining it with Ramulator, as it allows us to try more memory configurations and have a finer control. There have been previous proposals to join them both [34, 35]. Still, the execution was not integrated, as ZSim was used only to generate cache traces that were later fed to Ramulator. If we analysie how ZSim actual works, we loose the accuracy of the thread contention simulation. We make a static and very rough estimation of when main memory will serve our request and continue. Ideally, there should be an event created for the main memory access that would be part of the chain of events.

First, we will look at the internal mechanisms ZSim and Ramulator use for its simulation so we can later integrate them together.

#### 5.1 ZSim

The main contribution ZSim has made is allowing the simulation of multicore systems in a scalable way. In order to fulfill that goal, they divide the simulation in two phases they later parallelise.

• Bound phase. The contention between threads is not taken into account.

For each instrumented instruction we record the path it needs to do in order to finish. Essentially, it is a path discovery phase.

• Weave phase. We adjust the timing taking into account thread contention. The elements in the processor are divided into domains whose simulation executes in parallel. The only moment threads will have to synchronize is when there is a path that crosses domains.

We periodically change between those two phases only simulating a small number of cycles each time. One of the main observations that allow ZSim to follow this execution model is that path-altering interaction between threads is rare in a small number of cycles. Thus, there is only a very small loss of accuracy.

The instances when a path crosses domain are marked during the bound phase. Therefore, the workload during the weave phase is reduced as it will only need to take care of thread synchronization in those points. Previous frameworks used parallel discrete event simulator (PDES). Events generated during the simulation are distributed among the different host cores. If they are pessimistic then threads will synchronize every time a conflict might happen. If they are optimistic then they will continue with the execution and rollback later if needed. As the amount of cores increases so do the interaction between events, difficulting scaling this system.

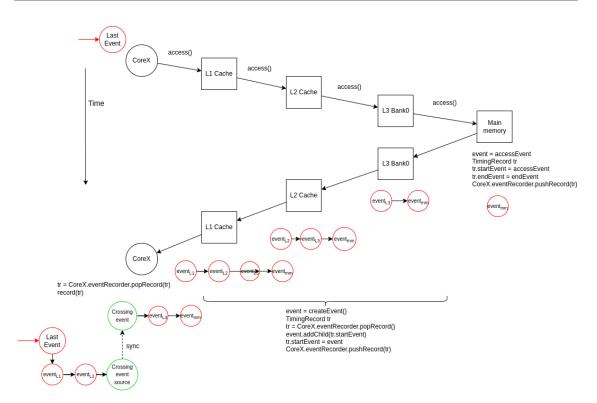

When incorporating our own objects in ZSim, we need to make sure we are creating a valid chain of events during the bound phase. There are different core models. SimpleCore and NullCore do not register the chain of events they generate when executing instructions such as loads or stores. That is because they do not model contention: SimpleCore has a fixed latency (it does not consider thread contention) and NullCore does not perform simulation of the instructions. Therefore, if we want our chain of events to be registered and simulated we need to use TimingCore or OOOCore.

When a core issues a request to the memory hierarchy the objects it needs to access will add events to the chain if necessary. This is done with the TimingRecord object which is later pushed to the EventRecorder of the core. The chain will later be taken by the core and linked to any previuos event if necessary.

To simulate dependencies between events we use "parental relationships". They are not one to one, as an event can have multiple children. This would happen, for instance, if an access to a cache later provokes a write back and another access, both of which might generate new events. Therefore, the writeback and the new access will have the same "parent" event. An event cannot start simulation during the weave phase until all its parents have finished. Only then, the event will be queued on its domain queue to wait for simulation. Inserting the domain crosses is not our responsibility, as it will be done by the **CoreRecorder** when the full chain has returned to the core.

Figure 5.1: Example of how the chain of events is created in a memory access.

In Figure 5.1 is an example of how the chain of events is created and returned to the core for a memory access. Every miss in a cache triggers an access to a lower level memory. When we arrive to the level where data is found we create a TimingRecord and push it to the EventRecorder. Then we recursively go back and we extend the chain of events as necessary. Finally, the core records the access by linking the chain to any previous event and introducing any CrossingEvent if the path chained domain at any point.

Finally all of this events will be simulated during the weave phase to adjust the timing skewes caused by thread contention and main memory access latency.

To do the simulation in parallel, ZSim creates several processes and threads. Therefore, objects used for the simulation have to be saved in shared space, in the global heap. To do so, they can inherit from GlobalAlloc, an object already provided by ZSim.

Summarizing, when extending ZSim as programmers our responsability is:

- Creating a coherent chain of events that reflects the dependencies between actions.

- Saving objects in shared memory.

Figure 5.2: High-level overview of Ramulator [36].

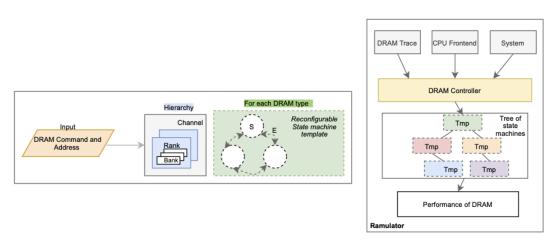

### 5.2 Ramulator

Ramulator is a well known main memory simulator. It implements a variaty of DRAM models and standars such us LPDDR3/4, DDR3/4, GDDR5, HBM, WIO1/2, SALP, TL-DRAM, ALDRAM, RowClone and SARP. A high level design is as shown in the Figure 5.2 which employs a re-configurable tree of state machines for modelling the hierarchy of a DRAM type.

The underline simulation is much simpler than in ZSim, as it is cycle driven. It ticks every cycle and checks the necessary changes that have to made to update the memory.

The way Ramulator is modeled, each of the levels of the main memory hierarchy (for instance, channel, rank, bank group, bank) is represented under the same object: DRAM. To be able to issue requests along the hierarchy we only need 3 main lookup functions for all levels.

- decode(): Returns the prerequisite command for the request

- check(): Returns if the command can be issued

- update(): Changes the state of the level according to the command that has just been issued.

Each of this functions is defined as a vector of lambda functions in the spec. If a certain level does not have enough information then the request keeps going down.

All memory controllers in Ramulator are centralized in a Memory object that takes care of performing the mapping from address to memory and forwarding the request to the correct controller.

#### 5.3 Integrating ZSim and Ramulator

The approach taken introduces new objects in ZSim that will become the bridge between the two simulators. Essentially, we will have one bridge for every channel or controller as they work independently from one another. Every time there is a request for the memory we create a new Event and push a TimingRecord. This event will follow the same flow as shown in the previous example in Figure 5.1. Ramulator is cycle driven, that meaning that it ticks every cycle and tries to schedule something. In order to emulate that behaviour we can also create a new Event that is triggered every memory cycle. When it simulates it ticks the controllers in Ramulator and gets reintroduced to be simulated in the next memory cycle. Because of the difference in frequencies between main memory and the system, we might not be able to tick exactly with the memory cycles. Therefore we tick as close as possible to them.

When the request is sent to Ramulator we attach a callback that will take care of finishing the event so the events attached as children can keep being simulated. Every time a request finishes in Ramulator (sending the response back to the core for read requests and issuing the memory writes for write requests) we will need to execute said callback.

A simple solution to integrate Ramulator while keeping the custom mappings from address to memory it offers, is centralizing all requests in one place, as Ramulator does. By doing so, the last level caches would only have to forward their requests to this centralized point and they would later redistribute. Nevertheless, we would be adding more synchronization points, as the arrival and redistribution of requests will incur in a lot of domain crossing. Thus, we eliminate the centralized memory for all controllers and we keep them independent. For that, we put in a separate object the mapping from address to memory and we link the last level caches to it, so they can know which channel/controller they have to forward their requests to.

In total, three new objects were created to bridge both simulators.

- RamulatorMemoryManager: Objects in Ramulator are heavily templated by the specification of the memory. This object just takes care of removing those templates in order to keep the ZSim code as undisturbed as possible.

- RamulatorMapper: Implements all of the functionality necessary to use custom mappings from address to memory.

- RamulatorMemory: It takes care of the events related to serving requests in main memory (access event, tick event).

We are introducing in ZSim a cycle driven object, which slows down the execution. Still we are able to combine the multicore scalability of ZSim with the flexibility and portability of Ramulator memory models. This model will allow us to keep trying different configurations and distributions of the NDP logic in the future with different memory models.

#### 5.4 Implementation of NDMiner

In NDMiner they store each neighborhood list in one bank and they interleave the sets by vertex id. Therefore, the NDP engines need to be able to access every bank and hence every channel. That puts the NDP engines on the ZSim side, as we do not have any elements in Ramulator that currently centralizes all memory controllers.

A NDP request is currently formed by the input neighborhoods, a filter and the type of operation. The input sets are marked with the vertex who owns the neighborhood list.

Now, we will go over how the main hardware proposals of NDMiner were implemented:

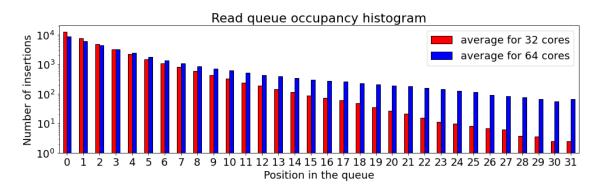

#### 5.4.1 Reordering the NDP operations

NDMiner proposed implementing a reordering of set operations to leverage bank, rank and channel parallelism. These reorderings were done in windows of 1024 ND requests. To maximize the parallelism the main goal is trying to avoid having concurrent accesses that take sets from the same bank.

Our implementation takes a more dynamic approach. When a NDP request arrives to the PIM engine we queue it. Then, when we are trying to schedule a new NDP request we search for the one that interferes less with the NDP operations that are currently in-flight. In case of a match we use the criteria First Come First Served. In the initial configuration we set the queue size to 32 NDP requests.

Now, in the NDP engine, we would need to have a table that keeps track of how many ND cores are accessing each bank. Later, we have set up Ramulator so it prioritizes those accesses that incur a row hit. Still, there is an upper bound to how many times we can prioritize those accesses that access the same bank. By doing so, we avoid request starvation in the controller.

#### 5.4.2 Load Ellision Unit

The actual data of the application does not exist in the simulation. Therefore, the best solution we found was already encoding in the request how many cache lines

we would have to read before getting to the threshold imposed by the symmetry breaking. We recognize that actually implementing the Load Ellision Unit incurs an extra delay not modeled in this simulation.

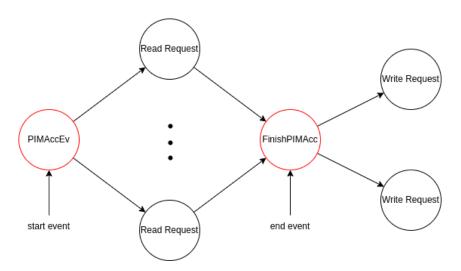

#### 5.4.3 Chain of events of a NDRequest

Going back, our responsibility when implementing a ZSim object is creating a coherent chain of events that can later be returned to the core. For that, we need to find which stages a request needs to go through to be fullfilled and what are the dependencies between them. The steps a NDP request does before ending are the following:

- Enqueue: Put it in the NDP request queue so we can later decide the most convenient request to schedule.

- **Dequeue and schedule:** The NDP request is chosen for execution. We assign a NDP core.

- **Issue reads:** Start issuing read requests to main memory to read both inputs.