# From Multiphase to Novel Single-Phase Multichannel Shift-Clock Fast Counter Time-to-Digital Converter

Nicola Lusardi<sup>®</sup>, *Graduate Student Member, IEEE*, Fabio Garzetti<sup>®</sup>, *Member, IEEE*, Andrea Costa<sup>®</sup>, *Graduate Student Member, IEEE*, Enrico Ronconi<sup>®</sup>, *Member, IEEE*, and Angelo Geraci<sup>®</sup>, *Senior Member, IEEE*

Abstract-With countless applications, time measurements are among industrial electronics' current most important challenges. This is not a matter of precision, which by now standard architectures have brought in the order of picoseconds and therefore at the physical limits of most common detection systems, but to the number of channels in continuous enormous growth. Just think about time-offlight (TOF)-based applications like 3-D-imaging, time-ofarrival real-time locating systems, TOF positron emission tomography, and so on. This addresses the research on the design of new time-to-digital converters characterized by a huge number of channels and precision compliant with detectors' time resolution. In this context, field programmable gate array architectures provide fully digital and completely programmable solutions meeting the demands for flexible setups and speedy prototyping. The innovative contribution provided by the new counter architecture proposed consists of the reduction of the area required for implementation (only 110 SLICEs), with a consequent increase in the number of channels (up to hundreds in a tiny Aritx-7), much higher than the state-of-the-art multiphase solutions available today and of the new complete generation of the time estimates in real time, all while maintaining a state-ofthe-art low power consumption and high resolution (up to 150 ps) and precision (up to 68.4 ps r.m.s.).

*Index Terms*—Field-programmable gate array (FPGA), Nutt-interpolation, shift-clock fast-counter (SCFC), tapped delay-line (TDL), time-to-digital converter (TDC).

#### I. INTRODUCTION

T HANKS to recent developments in electronics, time interval measurements have advanced quickly, finding use in a wide range of time-of-flight (TOF)-based applications where time and space are connected by the constant speed of light. Just consider, to cite the most disruptive ones, 3-D-imaging in

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TIE.2023.3322007.

Digital Object Identifier 10.1109/TIE.2023.3322007

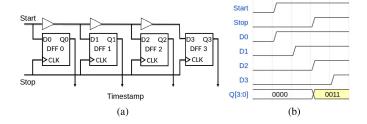

industry 4.0 for quality inspection and volumetric detection [1], automotive LiDAR scanners for self-driving [2], time-of-arrival real-time locating systems to automatically identify and track objects and people [3], and TOF positron emission tomography (TOF-PET) in diagnostics imaging [4]. This means that precisions of hundreds of picoseconds in time must be offered in order to guarantee the precision in space required for the majority of the applications previously stated. For this reason, time resolutions of used detectors are modest and limited to necessary for production cost restraint [5]. The time-to-digital converter (TDC), a fully digital type of time interval meter (TIM), is increasingly successful since it offers all the benefits of digital designs [6]. Complex mixed signaling is not necessary in this sense, to cite one of the most obvious advantages, principally simplifying the design in terms of engineering and production costs. The TDC can be implemented in an application-specific integrated circuit (ASIC) or, because of its fully digital structure, in a field programmable gate array (FPGA), which is currently a key resource due to its adaptability and extremely low nonrecurring engineering (NRE) costs, both in the R&D and production phases [7]. The TDC is most frequently implemented in FPGAs using delay lines or counter systems. The principal architecture of the first type is known as tapped delay-line (TDL) TDC (that is TDL-TDC), while for the other category the shift-clock fast-counter TDC (SCFC-TDC) is the most common one [8]. Of course, TDL and SCFC TDCs respond to different needs. In short, SCFC-TDCs accomplish lower resolution but require much less space for implementation than TDL-TDCs, which offer the maximum resolution at the tradeoff of a large area occupied. Therefore, TDL-TDCs are suited for applications needing very high performance in terms of resolution, while SCFC-TDCs for multichannel applications. In TDL-TDCs, the TDLs (Fig. 1) consist of chains of buffers, referred as bins or taps, each one being the unit of time quantization. As a consequence, TDL-TDCs provide resolutions, in first approximation, equal (or bigger) to the minimum propagation delay of the buffers in the technological node of the host device (e.g.,  $\sim 34$  ps in 65-nm FPGAs,  $\sim 25$  ps in 40-nm FPGAs,  $\sim 16$  ps in 28-nm FPGAs) [9]. The TDL-TDC structure involves the use of considerable resources. First of all, the buffer chains of TDLs are intrinsically highly hardware-consuming, and the presence of

© 2023 The Authors. This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see http://creativecommons.org/licenses/by/4.0/

Manuscript received 8 February 2023; revised 19 May 2023 and 26 July 2023; accepted 28 September 2023. (*Corresponding author: Nicola Lusardi.*)

The authors are with the Department of Electronics Information and Bioengineering (DEIB), Politecnico of Milano, 20133 Milan, Italy (email: nicola.lusardi@polimi.it; fabio.garzetti@polimi.it; andrea1.costa@ polimi.it; enrico.ronconi@polimi.it; angelo.geraci@polimi.it).

IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS

Fig. 1. Principle diagram of the TDL-TDC. (a) Architecture. (b) Waveforms.

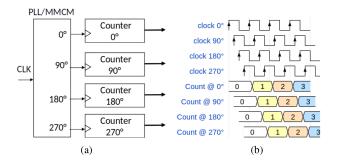

process and voltage-temperature fluctuations (PVT) determine mismatches among buffer delays that call for the implementation of a calibration mechanism (that consume hardware) in order to maintain high both resolution and and linearity [10]. Furthermore, in order to extend the full-scale range (FSR) and to get resolutions orders of magnitude below the minimum buffers delay value, two additional stages must be added to the basic structure, which are the Nutt-interpolator [11] to cope the former item and the subinterpolator [9], [12], [13] the latter one. Consequently, few channels can only be implemented in a single device due to the complexity of the entire resulting design, i.e., some units in small-size FPGAs (e.g., Xilinx 28-nm Artix7 family [14], [15]) up to few tens in medium-size FPGAs (e.g., Xilinx 28-nm Kintex-7 [16]). However, in high-size FPGAs (e.g., Kintex-7 [17] and Virtex-7 [18]) we can achieve hundreds of channels only if the processing, in order to save hardware and power, is done outside the FPGA. Last but not least, we must take into consideration that the purely asynchronous structure is affected by significant metastability issues on the sampling D-type flip-flops (DFFs) due to setup-and-hold time violations. Indeed, as can be seen from Fig. 1, the D inputs of the DFFs are connected directly, without any synchronization mechanism, to the Start signal and its delayed versions, which are completely asynchronous with respect to the Stop signal present at the CLK inputs. However, the structure does not present any critical issues regarding the skew between signals. In fact, the distribution structure of the clock signal (Stop in Fig. 1) within the FPGA ensures a skew lower than the minimum propagation delay of the buffers [19]. Furthermore, the topology of TDL itself prevents the output of the *i*th tap from being delayed compared to the output of tap i - 1. On the other hand, the SCFC-TDC is a pure synchronous TDC built using several low hardware-consuming counters characterized by a resolution corresponding to the minimum clock period achievable in the technological node of the host device. Therefore, the counters can be driven (Fig. 2) by the same clock period but moved by an offset equivalent to the desired resolution, even though always orders of magnitude below TDL-TDC [20]. When it comes to area occupancy, SCFC-TDCs utilize a lot less space than TDL-TDCs, allowing for the implementation of more channels in a single FPGA device, even if small (e.g., Xilinx 6-Series 40-nm Spartan-6 and 28-nm 7-Series Artix-7 families). An evidence of this at different technological nodes (i.e., 65, 40, and 28 nm) and different FPGA's families (i.e., Spartan, Artix, Kintex, and Virtex) is reported in Table I. Scientific literature reports many examples of

Fig. 2. Principle diagram of the SCFC-TDC. (a) Architecture. (b) Waveforms.

#### TABLE I

OVERVIEW OF TIMING PERFORMANCE (I.E., LSB AND PRECISION) AND AREA OCCUPANCY (I.E., NUMBER OF CHANNELS IMPLEMENTED) IN TDL AND SCFC TDCS AT DIFFERENT TECHNOLOGICAL NODES AND FPGA FAMILIES (I.E., SLICE REPRESENTS THE TOTAL AVAILABLE UNITS IN THE DEVICE TO PROVIDE A COMPARATIVE METRIC)

| Ref. | Туре | LSB [ps] | Prec. [ps r.m.s.] | Num. Ch. | SLICE  |

|------|------|----------|-------------------|----------|--------|

| [21] | TDL  | 45       | 18                | 2        | N.A.   |

| [22] | TDL  | 16.3     | -                 | 4        | 8,160  |

| [23] | SCFC | 138      | -                 | 64       | 11,200 |

| [24] | SCFC | 160      | 89.6              | 128      | 14,720 |

| [25] | SCFC | 625      | 255               | 32       | 11,200 |

(a) 65-nm 5-Series Virtex-5 FPGA family.

| Ref. | Туре | LSB [ps] | Prec. [ps r.m.s.] | Num. Ch. | SLICE  |

|------|------|----------|-------------------|----------|--------|

| [26] | TDL  | 25.6     | 37                | 2        | 2,278  |

| [27] | TDL  | 0.92     | 6                 | 2        | N.A.   |

| [28] | TDL  | 7.7      | 8.9               | 8        | 23,038 |

| [29] | SCFC | 1000     | 500               | 17       | 11,662 |

| [30] | SCFC | 1000     | 430               | 4        | 11,662 |

(b) 40-nm 6-Series Spartan-6 FPGA family.

| Ref. | Туре | LSB [ps] | Prec. [ps r.m.s.] | Num. Ch. | SLICE  |

|------|------|----------|-------------------|----------|--------|

| [31] | TDL  | 10       | 12.8              | 2        | 37,680 |

| [32] | TDL  | 1.7      | 4.2               | 2        | N.A.   |

| [33] | SCFC | 173.6    | 94.8              | 32       | 37,680 |

| [34] | SCFC | 312.5    | 184.7             | 32       | 37,680 |

(c) 40-nm 6-Series Virtex-6 FPGA Family.

| Ref. | Туре | LSB [ps] | Prec. [ps r.m.s.] | Num. Ch. | SLICE  |

|------|------|----------|-------------------|----------|--------|

| [14] | TDL  | 22.3     | 26.04             | 2        | 33,650 |

| [15] | TDL  | 2        | 12.5              | 16       | 33,650 |

| [35] | SCFC | 156      | 78                | 36       | 15,850 |

| [36] | SCFC | 138      | 73.6              | 64       | 28,000 |

|      |      |          |                   |          |        |

(d) 28-nm 7-Series Artix-7 FPGA family.

| Ref. | Туре | LSB [ps] | Prec. [ps r.m.s.] | Num. Ch. | SLICE   |

|------|------|----------|-------------------|----------|---------|

| [18] | TDL  | 10.54    | 14.59             | 96       | 108,300 |

| [16] | TDL  | 10.6     | 8.13              | 64       | 50,950  |

| [17] | TDL  | 9.4      | 9.5               | 128      | 50,950  |

| [37] | SCFC | 280      | 130               | 8        | 50,950  |

| [38] | SCFC | 89.9     | 56.2              | 256      | 50,950  |

(e) 28-nm 7-Series Kintex-7 and Virtex-7 FPGA family.

the so-called multiphase SCFC-TDCs (MP-SCFC-TDC), [20], [23], [25], [29], [30], [36], [37], [39], [40] in which the clock shifting is obtained by means of one or more phase-locked-loops (PPLs) or mixed-mode clock managers (MMCMs) [19]. So, the resolution corresponds to the clock period (e.g., bigger than 1.0 ns in Xilinx 28-nm 7-Series [37]) divided by the maximum number of clock nets that the FPGA can manage (e.g., Xilinx 28-nm 7-Series FPGAs offer 32 clocks nets with at maximum 16 clocks routed in the same clock zone). The high number of clock signals (also known as phases) with relative time skews [41] that must be controlled to maintain the resolution is the weak point of MP-SCFC-TDCs, which increases the system's complexity and portability between various configurations and FPGA types [24], [33], [34], [35], [38], [42]. A new single-phase SCFC-TDC (SP-SCFC-TDC) design is introduced to get around this restriction. The proposed SP-SCFC-TDC combine the absence of skew issues of TDL-TDC (due by the presence of the TDL and the distribution structure of the clock signal inside the FPGA) with the synchronous architecture of the MP-SCFC-TDC that, at difference with respect to the classical asynchronous TDL-TDC, minimize the metastability due to the setup-and-hold violations of the flip-flop. The rest of this article is organized as follows: In Section II, an MP-SCFC-TDC used as a reference is presented, and the novel SP-SCFC-TDC is presented in Section III. The experimental validations of the proposed architecture in 28-nm Xilinx 7-Series Artix-7 35 T (i.e., XC7A35T-1CPG236 C hosted in a Basys3 evaluation board [43]) and in Artix-7 100 T (i.e., XC7A100T-1CSG324C hosted in a Nexys4 evaluation board [44]) FPGAs are discussed in Section IV, demonstrating the possibility of implementing up to 64, 32, and 32 channels in the Artix-7 35 T (5,200 SLICE) and 128, 120, and 112 ones in the Artix-7 100 T (15,850 SLICEs) with resolutions of 625.5, 317.25, and 156.125 ps, respectively, using only 84, 108, and 110 SLICEs per channels and only one clock phase. Both MP

and SP SCFC-TDC presented are organized as IP-Cores with an intuitive graphical user interface (GUI) that easily allows the user to set operating parameters, in particular the number of channels and the resolution.

# II. PAST REFERENCE MULTIPHASE SCFC-TDC ARCHITECTURE

We have designed the MP-SCFC-TDC, taken as a reference, suitable for 28-nm Xilinx 7-Series FPGAs and organized as a tunable IP-Core [20], [23], [25], [29], [30], [36], [37], [39], [40]. Section II-A describes the design, and Section II-B reports implementation details and relative critical issues.

## A. Design

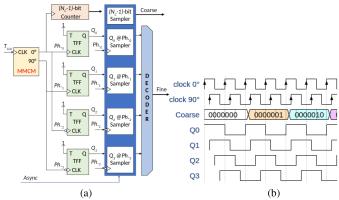

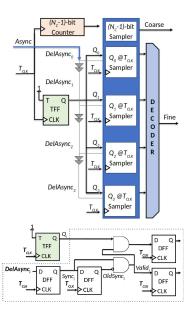

According to [20], [23], [25], [29], [30], [36], [37], [39], [40], for hardware saving purpose, the MP-SCFC has not been implemented using the scheme of one  $N_C$ -bit wide counter per phase (Fig. 2) but, referring to the Nutt-interpolation, we have used only one ( $N_C - 1$ )-bit wide counter placed side-by-side to  $N_{PH}$  (i.e., number of phases) toggle-type flip-flops (TFFs) that are simple 1-bit wide counters. The ( $N_C - 1$ )-bit wide counter is the coarse counter, while the  $N_{PH}$  TFFs are the fine counters.

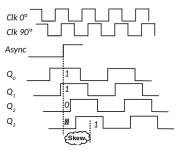

Fig. 3. MP-SCFC with one 8-bit coarse counter and 4 fine 1-bit TFF counters;  $N_{PH} = 4$  and  $N_C - 1 = 8 - 1$ . (a) Architecture. (b) Waveforms.

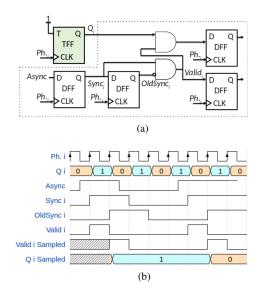

Fig. 4. Sampling of the fine part of a MP-SCFC. (a) In the box, the architecture of the generic sampler. (b) Waveforms considering only the generic phase ith.

Moreover, to maximize  $N_{PH}$  by lowering the number of the clock nets ( $N_{\text{CLK}}$ ), we drive the stage of fine counters in doubledata-rate (DDR) mode. In this way, we have  $N_{PH} = 2 \cdot N_{\text{CLK}}$  (i.e.,  $N_{\text{CLK}}$  is an even number) and the first  $N_{PH}/2$  TFFs (from the 0 to the  $N_{PH}/2 - 1$ ) work on the rising edge of the  $N_{\text{CLK}}$  clocks and the other  $N_{PH}/2$  TFFs (from the  $N_{PH}/2$  to the  $N_{PH} - 1$ ) on the falling edge. Clock signals have the same period  $T_{\text{CLK}}$  and are generated using an MCMM at  $N_{\text{CLK}}$  outputs with a shift of  $\Delta \varphi = 180^{\circ}/N_{\text{CLK}}$  between phases. In this way, the  $N_{PH}$  TFFs explore  $2 \cdot N_{PH}$  thermometric codes in  $2 \cdot T_{\text{CLK}}$ . Concerning the ( $N_C-1$ )-bit wide counter, it is connected to a clock signal with 0° phase shift and period of  $2 \cdot T_{\text{CLK}}$ . Fig. 3 shows the architecture and waveforms of main signals of the MP-SCFC in case  $N_C = 8$  and  $N_{PH} = 4$ .

In this way, in a single-channel MP-SCFC-TDC the outputs  $(N_{PH} \text{ outputs of the TFFs and the } N_C - 1 \text{ bits of the coarse counter})$  are sampled by D-type flip-flops (DFFs), when the asynchronous physical event (Async) occurs. As shown in Fig. 4,

unlike what happens in TDL-TDCs, to avoid setup-and-hold violations in the flip-flops that constitute the sampler, the Async signal is synchronized by a DFF, one per phase, fed with the corresponding clock. By doing so, we have  $N_{PH}$  replicas (named  $Sync_0, Sync_1, \ldots, Sync_{N_{PH}-1}$ ) synchronized to each of the  $N_{PH}$  phases. After that, each Sync<sub>i</sub> (where  $i \in [0; N_{PH}]$  and *i* represents the generic phase) is resampled by the same phase in order to generate  $OldSync_i$  (one per phase, i.e.,  $OldSync_0$ ,  $OldSync_1, \ldots, OldSync_{N_{PH}-1}$ ). So, for each phase, the sampling process is concluded with the assertion of  $Valid_i$  (one per phase, i.e., Valid<sub>0</sub>, Valid<sub>1</sub>, ..., Valid<sub>NPH</sub><sup>-1</sup>) when Sync<sub>i</sub> = 1 and  $OldSync_i = 0$  and the storage of the status of the *i*th TFF. After that, for avoiding to operate with multiple phases, all the sampled values are moved from the generic phase *i*th to phase 0 (a.k.a. master-phase) by means of a clock domain crossing (CDC). The coarse counter, synchronous with the master-phase, is sampled by  $N_C - 1$  DFFs when Valid<sub>0</sub> = 1. Finally, the timestamp is constructed by combining coarse and fine measurements once data has been translated from thermometric to binary code, having FSR equal to  $2^{N_C} \cdot T_{\text{CLK}}$  and resolution (LSB) equal to  $T_{CLK}/N_{PH}$ . Now, a multichannel MP-SCFC-TDC can be easily obtained by replicating the MP-SCFC and sampling circuit as many times as inputs are sharing the same MCMM. In addition, the system is set up as a configurable IP-Core enabling its simple usage.

## B. Implementation Details

Having selected for implementation a 28-nm Xilinx 7-Series FPGA device, at maximum 16 clock nets can be routed in the same clock zone and 8 clocks can be managed by the MCMM [19]. In fact, MMCMs have eight outputs, which would require the use of three of them to get 16 channels, weakening the architecture efficiency due to consequent strong clock jitter. Due to this, 8  $N_{\text{CLK}}$  is the maximum allowed (i.e., 16 for  $N_{PH}$ ). Moreover, the timing analysis returns 2.5 ns as minimum clock period corresponding to 156.26 ps (i.e., 2.5 ns/16) of resolution. And here the first drawback of this architecture emerges: the technology of the selected host device, in terms of the amount of clock lines and MCMM resources, limits the achievable resolution.

In order to better focus MP-SCFC-TDC features and performance, thanks to the flexibility of the IP-Core, three different implementations have been considered (Table II), which are #1-MP with  $N_{\text{CLK}} = 2$  ( $N_{PH} = 4$ ) and 625-ps resolution, #2-MP with  $N_{\text{CLK}} = 4$  ( $N_{PH} = 8$ ) and 312.5-ps resolution, and #3-MP with  $N_{\text{CLK}} = 8$  ( $N_{PH} = 16$ ) and 156.26-ps resolution. In all implementations, the same FSR equal to 640 ns (i.e.,  $N_C = 8$ ) has been set. However, because the resolution value can only go as high as 500 ps, implementations with  $N_{\text{CLK}} > 2$  are worthless. This is due to the second drawback of the MP-SCFC-TDC architecture: the time position of the asynchronous Async input with respect to the  $N_{\text{CLK}}$  clocks cannot be fixed with precision better than hundreds of picoseconds. For example, as shown in Fig. 5, if the skew of the time paths ( $\Delta$ Skew) between two consecutive phases i and i + 1 is greater than the LSB (i.e.,  $\Delta$ Skew<sub>*i*+1,*i*</sub> > LSB), the signal for that particular phase will

TABLE II MP-SCFC-TDC DIFFERENT IMPLEMENTATIONS FEATURES

IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS

| Figures                  | #1-MP | #2-MP | #3-MP  |

|--------------------------|-------|-------|--------|

| N <sub>CLK</sub>         | 2     | 4     | 8      |

| NPH                      | 4     | 8     | 16     |

| $T_{\rm CLK}$ [ns]       | 2.5   | 2.5   | 2.5    |

| Expected LSB [ps]        | 625   | 312.5 | 156.25 |

| Measured LSB [ps]        | 625   | 500   | 500    |

| $N_C - 1$                | 8-1   | 8-1   | 8-1    |

| FSR [ns]                 | 640   | 640   | 640    |

| Num. LUTs/Ch             | 212   | 238   | 295    |

| Num. FFs/Ch              | 336   | 431   | 446    |

| Num. Ch. in Artix-7 35T  | 64    | 32    | 32     |

| Num. Ch. in Artix-7 100T | 128   | 120   | 112    |

Fig. 5. Example of skew error in the MC-SCFC-TDC considering  $N_{\text{CLK}} = 2$  ( $N_{PH} = 4$ ). This results in the error of sampling "1100" instead of "1101" due to the skew of Async with respect to the last phase. For simplicity, the sampler has been omitted and Async directly samples the phases.

always be sampled at the next clock edge corrupting the fine part of the measure. This second main drawback could be be effectively addressed by utilizing the "ones counter method" [45] and the "phase resort" technique [46], originally designed to resolve similar issues, such as bubble errors, in high-resolution (picoseconds) TDL-TDCs. Both solutions are also feasible for MP-SCFC-TDC; although, due to their high-resolution target, they would result in an excessively complex system for the required resolution (i.e., tens of picoseconds). The ones counter method entails analyzing data for each channel and compensating for nonidealities using an additional module, which could pose challenges when dealing with numerous channels or limited FPGA resources. On the other hand, employing the phase resort technique would necessitate intricate manual routing and/or comprehensive knowledge of implementation delays, potentially leading to a time-consuming process, particularly for multichannel implementations.

## III. NOVEL SINGLE-PHASE SCFC-TDC ARCHITECTURE

To overcome the drawbacks of the MP-SCFC-TDC architecture (i.e., the limited number of  $N_{\text{CLK}}$  and the problem of the skew), we propose a single clock architecture using a chain of buffers that makes up a TDL, one per channel, instead of the MCMM that is common to all channels in the MP-SCFC-TDC. It is possible to observe that SP-SCFC-TDC combine the absence of skew issues of TDL-TDC (intrinsically due by the presence of the delay-line and the distribution structure of the clock signal into FPGA) with the synchronous architecture

Fig. 6. Novel SP-SCFC-TDC architecture, single-channel, with  $N_{PH} = 4$  (top) with highlighted the sampler (bottom).

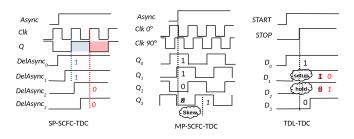

Fig. 7. Novel SP-SCFC-TDC waveforms (synchronous without skew) are compared with the MP-SCFC-TDC (synchronous with skew) and TDL-TDC (asynchronous with metastability issues but without skew).

offered by the MP-SCFC-TDC. As can be seen from Fig. 6, the output of each individual TFF (green) is sampled by the samplers (identical to those in Fig. 4), both driven by the same clock  $T_{\text{CLK}}$ . However, the asynchronous signals  $\text{DelAsync}_i$ , unlike in the TDL-TDC, are appropriately synchronized before being sampled by DFFs (white). In this way, SP-SCFC-TDC minimizes the metastability due to the setup-and-hold violations of the flip-flop. Fig. 6 depicts the developed architecture. The Async input is transmitted to the  $N_{PH}$  samplers, which are the same as in the MP-SCFC-TDC architecture, using a TDL, while the  $(N_C - 1)$ -bit coarse counter and only one TFF are supplied with the same clock with period  $T_{\text{CLK}}$  and phase  $0^{\circ}$  (i.e., the master-clock of the MP-SCFC-TDC solution). Fig. 7 presents the waveforms of the main nodes of the proposed architecture (SP-SCFC-TDC), which are not affected by skew, metastability, and are synchronized to the clock, comparing them with those of the MP-SCFC-TDC (synchronous but subject to skew) and the TDL-TDC (asynchronous, hence subject to metastability, setup, and hold time violations). In case of 28-nm Xilinx 7-Series FPGAs, the carry-chain resources (i.e., CARRY4) on the device are used to implement the TDL. Precisely, a proper number

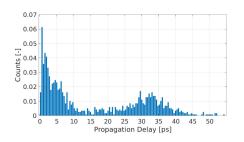

Fig. 8. Experimental measurement of the distribution of the propagation delays in a TDL ( $N_{\text{TAP}} = 256$ ) implemented in 28-nm Xilinx 7-Series device.

of CARRY4 resources ( $N_{\text{CARRY4}}$ ) are cascaded to give a TDL composed by  $N_{\text{TAP}}$  taps (i.e.,  $N_{\text{TAP}} = 4 \cdot N_{\text{CARRY4}}$ ) with total delay a bit bigger than  $T_{\text{CLK}}$ . So, considering that each tap has a propagation delay  $t_p$  comparable to the minimum one offered by the technological node (i.e., 16 ps in 28-nm devices), it is possible to choose at which step  $\Delta N_{\text{TAP}}$  to extract the  $N_{PH}$  delayed Async, called DelAsync<sub>i</sub> (one per phase: DelAsync<sub>0</sub>, DelAsync<sub>1</sub>, ..., DelAsync<sub>N\_{PH}-1</sub>) to be sent to the samplers. Thus, considering that  $\Delta N_{TAP}$  taps must introduce a delay equal to the desired LSB, we have to set  $\Delta N_{\text{TAP}} = \text{LSB}/t_p$  and, obviously,  $N_{\text{TAP}} \ge T_{\text{CLK}}/t_p$ . In this design, the choice of  $N_{\text{TAP}} = 256$  (i.e.,  $256 > 2.5 \text{ ns}/16 \text{ ps} \simeq 157$ ) corresponds to  $N_{\text{CARRY4}} = 64$ .

However, because it was not intended to be a specific timing resource, the CARRY4 primitive displays PVT fluctuations (as predicted in Section I) in the time delay between the four taps inside the same CARRY4 and to other CARRY4 stages. The propagation delay for the 28-nm Xilinx 7-Series, shown in Fig. 8, can vary by nearly 300% from the mean value (i.e.,  $\sim 16$  ps), corresponding to a maximum of  $\sim 50$  ps (i.e., ultrabin) and a minimum of  $\sim 1$  ps. The temporal length of  $\Delta N_{\text{TAP}}$ , a consequence of the central limit theorem, remains almost constant and numerically tends to  $\Delta N_{\mathrm{TAP}} \cdot t_p$ , even in the presence of considerable dispersion in propagation delays, provided that  $\Delta N_{\text{TAP}}$  is sufficiently large. In Section IV, this claim will be experimentally confirmed. We would like to highlight that the proposed SP-SCFC-TDC employs a merging method for the taps. Similar but more hardware-intensive methods, designed for achieving high-resolution (picoseconds) in TDL-TDCs, are proposed in [47] and [48]. However, our proposed solution offers a simpler and more resource-efficient implementation, making it suitable for multichannel applications on smaller FPGAs with resolutions in the tens of picoseconds. In analogy with the MP-SCFC-TDC IP-Core introduced in Section II, the  $\Delta N_{\text{TAP}}$  and not the  $N_{\text{CLK}}$  fixes the resolution, the FSR is equal to  $N_C \cdot T_{\text{CLK}}$  and the LSB is equal  $\Delta N_{\text{TAP}} \cdot t_p$ . In this way, the resolution of the proposed SP-SCFC-TDC is no more constrained by the clock resources (i.e.,  $LSB_{MP} = T_{CLK}/N_{PH}$ ) but only depends on the taps propagation delay (i.e.,  $LSB_{SP} = \Delta N_{TAP} \cdot t_p$ ). Second, the problem of the skew is also eliminated, since the sampling is performed along the sequence of buffers and the skew between two samplers is negligible thanks to the structure of the CARRY4 stage.

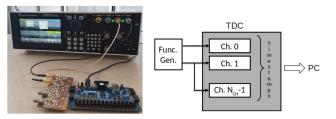

Fig. 9. Block diagram (rigth) of the experimental setup photo with Basys3 (left). To minimize the number of connectors, the channel 0 is directly connected to the function generator and all the other  $N_{CH} - 1$  channels to a delayed replica.

## **IV. MEASUREMENTS**

Experimental comparisons are made between the proposed SP-SCFC-TDC and systems that are currently available in literature, and with the reference MP-SCFC-TDC. In particular, Section IV-B compares the three implementations of MP-SCFC-TDC, i.e., #1-MP, #2-MP, and, #3-MP (Section II-B and Table II) with the correspondent SP-SCFC-TDC implementations named #1-SP, #2-SP, and #3-SP. All the TDCs have the same  $T_{\rm CLK}$  equal to 2.5 ns and FSR equal to 640 ns (i.e.,  $N_C - 1 = 8 - 1$ ). Finally, Section IV-C compares MP-SCFC-TDC and SP-SCFC-TDC architectures with systems available in literature at the state of the art. While Section IV-A reports the measurement setup and the methods used to calculate the figure of merits.

## A. Measurement Setup

A host computer processes the timestamps from the MP-SCFC-TDC and SPSCFC-TDC multichannel  $(N_{CH})$  implementations in order to determine the resolutions, precisions, and respective differential and integral nonlinearity (DNL/INL). The clock signals necessary to the TDCs are provided by the oscillator available on the Basys3 and Nexys4 boards used as support hardware, while the Async signals are created by an external function generator. The setup layout is graphically represented in Fig. 9. The standard deviation ( $\sigma_{i0}$ ) of the distribution of the differences between timestamps of the *i*th channel and of channel 0 is referred as channel-to-channel precision, i.e.,  $\sigma_{i0} = \sqrt{\sigma_i^2 + \sigma_0^2}$ ; it mathematically correspond to the contribution of the single-shot precision of channel *i*th ( $\sigma_i$ ) and channel 0  $(\sigma_0)$ ; i.e.,  $\sigma_{i0} = \sqrt{\sigma_i^2 + \sigma_0^2}$ . To determine the DNL and INL of the generic *i*th channel, a code-density-test (CDT), i.e., the histogram of the occurrence, over the fine part of timestamps is performed [49]. In this manner, an estimation of the propagation delay of the  $N_{PH}$  phases is performed normalizing the histogram by the dynamic-range of 2.5 ns offered by the fine part (i.e.,  $T_{\text{CLK}}$ ). The average of the time duration of bins of the CDT is assumed as index of resolution. While bin-by-bin relative DNL and INL curves are derived by differentiation of the CDT, for the DNL, and successive integration, for the INL. Furthermore, according to measure theory, the generic *i*th channel precision is  $LSB_i/\sqrt{12}$  if jitters and linearity errors are negligible (i.e., the ENOB of the system coincides with the LSB), which means that  $\sigma_{i0} = \sqrt{\text{LSB}_i^2/12 + \text{LSB}_0^2/12}$ , where  $LSB_0$  and  $LSB_i$  represent the resolutions of channels 0 and *i*th.

TABLE III MP-SCFC-TDC VERSUS SP-SCFC-TDC HARDWARE OCCUPANCY

| #1<br>MP | #2<br>MP                                                                    | #3<br>MP                                                                                                                                                                                                                                                                       | #1<br>SP                                                                                                                                                                                                                                                                                                                                                                                                                                               | #2<br>SP                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | #3<br>SP                                              |

|----------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| 4        | 8                                                                           | 16                                                                                                                                                                                                                                                                             | -                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                                                     |

| -        | -                                                                           | -                                                                                                                                                                                                                                                                              | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10                                                    |

| 8-1      | 8-1                                                                         | 8-1                                                                                                                                                                                                                                                                            | 8-1                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8-1                                                   |

| 212      | 238                                                                         | 295                                                                                                                                                                                                                                                                            | 212                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 238                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 295                                                   |

| 336      | 431                                                                         | 446                                                                                                                                                                                                                                                                            | 333                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 424                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 431                                                   |

| 1 for    | all Cha                                                                     | nnels                                                                                                                                                                                                                                                                          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                                     |

| 0        | 0                                                                           | 0                                                                                                                                                                                                                                                                              | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 64                                                    |

| 84       | 108                                                                         | 110                                                                                                                                                                                                                                                                            | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 108                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 110                                                   |

| 1.61     | 2.07                                                                        | 2.11                                                                                                                                                                                                                                                                           | 1.61                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2.07                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.11                                                  |

| 0.53     | 0.68                                                                        | 0.69                                                                                                                                                                                                                                                                           | 0.53                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0.68                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0.69                                                  |

| 64       | 32                                                                          | 32                                                                                                                                                                                                                                                                             | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 32                                                    |

| 128      | 120                                                                         | 112                                                                                                                                                                                                                                                                            | 128                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 120                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 112                                                   |

|          | MP<br>4<br>-<br>8-1<br>212<br>336<br>1 for<br>0<br>84<br>1.61<br>0.53<br>64 | MP         MP           4         8           -         -           8-1         212           336         431           1 for all Cha         0           0         0           84         108           1.61         2.07           0.53         0.68           64         32 | MP         MP         MP           4         8         16           -         -         -           8-1         8-1         212           212         238         295           336         431         446           1 for all Channels         0         0           0         0         0           84         108         110           1.61         2.07         2.11           0.53         0.68         0.69           64         32         32 | MP         MP         MP         SP           4         8         16         -           -         -         39         8-1         8-1         8-1           212         238         295         212         336         431         446         333           1 for all Channels         0         0         64         84         108         110         84           1.61         2.07         2.11         1.61         0.53         0.64         32         32         64 | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

TABLE IV SP-SCFC-TDCs NONLINEARITY ERRORS

|                           | #1 SP   | #2 SP     | #3 SP     |

|---------------------------|---------|-----------|-----------|

| $\Delta N_{\mathrm{TAP}}$ | 39      | 20        | 10        |

| Exp.LSB [ps]              | 624     | 320       | 160       |

| Meas.LSB [ps]             | 625.5   | 317.25    | 156.125   |

| DNL/INL [% LSB]           | 4.5/4.5 | 26.4/20.3 | 23.3/26.4 |

In light of the fact that all channels, roughly speaking, have the same resolution LSB (i.e.,  $\text{LSB}_i \simeq \text{LSB}_0$ ), we can assume  $\sigma_{i0} = \sqrt{\text{LSB}^2/6}$  as channel-to-channel precision.

## B. MP-SCFC-TDC versus SP-SCFC-TDC

We must set the  $\Delta N_{TAP}$  value of the SP-SCFC-TDC to have nearly identical LSB values in order to compare MP- and SP-SCFC-TDCs fairly. By setting  $\Delta N_{TAP} = 39$ , the LSB value for #1-SP is in theory  $39 \cdot 16 \text{ ps} = 624 \text{ ps}$  and 625.5 ps measured, which is compatible with the #1-MP LSB equal to 625 ps. Similarly,  $\Delta N_{TAP} = 20$  in #2-SP corresponds to theoretical LSB equal to  $20 \cdot 16 \text{ ps} = 320 \text{ ps}$  and 317.25 -ps measured as compared to 312.5 ps of #2-MP LSB. Finally,  $\Delta N_{TAP} = 10$  in #3-SP determines theoretical LSB equal to  $10 \cdot 16 \text{ ps} = 160 \text{ ps}$ and 156.125 ps measured as compared to 156.25 ps of #3-MP LSB.

1) Hardware Occupancy: First of all, we have investigated the hardware occupancy of MP-SCFC-TDCs and SP-SCFC-TDCs, which differ, as Figs. 4 and 6 show, by  $N_{PH} - 1$  TFFs per channel and for the presence of one MCMM in MP-SCFC-TDCs replaced by 64 CARRYs per channel in SP-SCFC-TDCs. Table III displays the resources used by the two architectures in the selected target device and in some others belonging to different families.

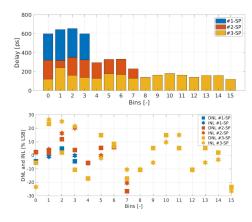

2) Linearity and Resolution: Linearity and resolution of #1-SP, #2-SP, and #3-SP have been investigated through the CDTb etween the  $N_{PH}$  phases composed by  $\Delta N_{TAP}$  taps. Measured CDTs and bin-by-bin relative DNL and INL curves are shown in Fig. 10. Table IV summarize the measured resolution or LSB (Meas. LSB), the expected one (Exp. LSB) and, the DNL/INL errors (i.e., the maximum magnitude of the bin-by-bin curves). The conclusion in Section III, which states that if the

#### LUSARDI et al.: FROM MULTIPHASE TO NOVEL SINGLE-PHASE MULTICHANNEL SHIFT-CLOCK FAST COUNTER TDC

Fig. 10. CDT (top) and bin-by-bin DNL and INL curves (bottom) over #1-SP (blue), #2-SP (red), and #3-SP (orange).

TABLE V MP-SCFC-TDC VERSUS SP-SCFC-TDC PRECISIONS

| Ch-Ch Prec.<br>[ps r.m.s.] | #1<br>MP | #2<br>MP | #3<br>MP | #1<br>SP | #2<br>SP | #3<br>SP |

|----------------------------|----------|----------|----------|----------|----------|----------|

| σ                          | 180      | 144      | 144      | 180      | 92.3     | 68.4     |

| $\sigma_{i0}$ _            | 255      | 204      | 198      | 255.5    | 130.5    | 96.8     |

| (Exp. LSB)/√6              | 255.5    | 127.6    | 63.8     | 254.7    | 130.6    | 65.3     |

| (Meas. LSB )/ $\sqrt{6}$   | 255.5    | 204      | 204      | 255.4    | 129.5    | 63.7     |

dispersion of propagation delays is high and  $\Delta N_{\text{TAP}}$  is sufficiently great,  $\Delta N_{\text{TAP}}$ , as a consequence of the central limit theorem, the time duration of  $\Delta N_{\text{TAP}}$  (i.e., the Meas. LSB) remains almost constant approximating the Exp. LSB to  $\Delta N_{\text{TAP}} \cdot t_p$ , is supported by the data in Fig. 10. Because the propagation delay demonstrates a maximum dispersion (ultra-bin) that is negligible compared to the LSB, it is feasible to operate in a hardware-saving mode without calibration while maintaining low relative DNL and INL.

3) Precision: Considering both expected and measured LSBs, i.e., Exp. LSB and Meas. LSB, respectively, (with  $LSB_{MP} = T_{CLK}/N_{PH}$  and  $LSB_{SP} = \Delta N_{TAP} \cdot t_p$ ), Table V displays the average values of the singe-shot ( $\sigma$ ) and channel-to-channel precisions ( $\sigma_{i0}$ ) measured in the various implementations and the related LSBs. The proposed SP-SCFC-TDC's advantage to the MP-SCFC-TDC is thus made clear. In fact, the observed LSB value of 500 ps corresponds to the measured accuracy limit of 204 ps r.m.s. in MP-SCFC-TDC implementations (see Section II-B).

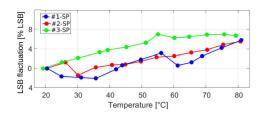

4) Temperature Fluctuation: Unlike the MP-SCFC-TDC, where the MCMM/PLL generating the phases incorporates analog temperature compensation mechanisms, the delay-line of the SP-SCFC-TDC is uncalibrated and uncompensated. As a result, the various taps are subject to fluctuations induced by temperature variations, leading to an LSB dispersion. Consequently, the percentage dispersion of the LSB for #1-SP, #2-SP, and #3-SP was characterized by varying the FPGA temperature between 20 °C and 80 °C with 5 °C steps using a climatic chamber. The results, depicted in Fig. 11, reveal that #1-SP and #2-SP exhibit a dispersion lower than 6% (i.e., 37.5 and 19 ps in absolute value over an Meas. LSB of 625.5 and 317.25 ps respectively), while

TABLE VI COMPARISON BETWEEN STATE-OF-THE-ART MP-SCFC-TDC ARCHITECTURES IN LITERATURE AND THE #1-MP IMPLEMENTATION

| Ref.  | $\frac{T_{\text{CLK}}}{N_{PH}}$ [ns] | LSB<br>[ps] | DNL/INL<br>[%] | Prec<br>[ps] | Num.<br>Ch. | FPGA<br>(SLICEs)      |

|-------|--------------------------------------|-------------|----------------|--------------|-------------|-----------------------|

| [23]  | 2.22/16                              | 138         | 28.9/-         | -            | -           | Virtex-5<br>(11,200)  |

| [20]  | 5.04/4                               | 1400        | 40/-           | 700          | -           | N.A.                  |

| [25]  | 2.5/4                                | 625         | 7/7            | 255          | 32          | Virtex-5 (11,200)     |

| [29]  | 4.0/4                                | 1000        | 52/39          | 500          | 17          | Spartan-6<br>(11,662) |

| [39]  | 3.13/4                               | 780         | 40/5           | 280          | 24          | Kintex-7<br>(N.A.)    |

| [30]  | 4.0/4                                | 1000        | N.A.           | 430          | 4           | Spartan-6<br>(11.662) |

| [40]  | 3.13/4                               | 780         | N.A.           | 250          | 24          | M2GL010T<br>(12,084)  |

| [36]  | 3.33/24                              | 138         | N.A.           | 73.6         | 64          | Artix-7<br>(28,000)   |

| [37]  | 1.13/4                               | 780         | 53/280         | 280          | 8           | Kintex-7<br>(50,950)  |

| #1-MP | 2.5/4                                | 625         | N.A.           | 255          | 103         | Artix-7<br>(15,850)   |

SLICE represents the total available units in the device to provide a comparative metric.

#3-SP shows a dispersion lower than 8% (i.e., 12.5 ps in absolute value over an Meas. LSB of 156.125 ps). These values can be considered negligible concerning the resolution, the precision, and DNL/INL errors.

## C. State of the Art

Table VI compares available MP-SCFC-TDC implementations at state of the art and the #1-MP in Artix-7 100 T, which represents the best compromise between timing performance (i.e., LSB, DNL/INL, and precision) and area occupancy (i.e., number of channels and number of slices available in the FPGA). Table VII compares the proposed SP-SCFC-TDC with available SCFC-based TDC architectures, in which the drawbacks of the SCFC are solved using custom routing [34], [38] (first block of elements in the table), constraints [24], [33] (second block), and use of SERDES [35], [42] (third block). Moreover, hardwareconsuming but high-resolution (picoseconds) subinterpolating architectures, e.g., PLL delay-matrix TDC [50] (997 SLICEs, LSB of 17.73 ps in a medium-size Virtex-6 FPGA), can be adopted in order to increase the resolution of the SCFC-based TDC up to few picoseconds. However, these subinterpolating techniques make it possible to implement hundreds of channels only in medium/high-size FPGAs.

8

IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS

TABLE VII COMPARISON BETWEEN STATE-OF-THE-ART SCFC-BASED TDC ARCHITECTURES IN LITERATURE AND THE #1-SP, #2-SP, AND #3-SP IMPLEMENTATIONS OF THE PROPOSED SOLUTION

| Ref.  | $\frac{T_{\rm CLK}}{N_{PH}}$ [ns] | LSB<br>[ps] | DNL/INL<br>[%] | Prec<br>[ps] | Num.<br>Ch. | FPGA<br>(SLICEs)      |

|-------|-----------------------------------|-------------|----------------|--------------|-------------|-----------------------|

| [38]  | 1.43/16                           | 89.9        | 87/82          | 56.2         | 256         | Kintex-7<br>(50,950)  |

| [34]  | 5.00/16                           | 312.5       | 4.5/4.5        | 184.7        | 32          | Virtex-6<br>(37,680)  |

| [24]  | 2.57/16                           | 160         | 20/-           | 89.6         | 128         | Virtex-5<br>(14,720)  |

| [33]  | 2.78/16                           | 173.6       | 3.5/3.5        | 94.8         | 32          | Virtex-6<br>(37,680)  |

| [35]  | 1.25/8                            | 156         | 32/100         | 78           | 2           | Artix-7<br>(15,850)   |

| [42]  | 4.76/4                            | 1190        | N.A.           | 500          | 32          | Cyclone III<br>(N.A.) |

| #1-SP | -                                 | 625         | 4.5/4.5        | 255.5        | 103         | Artix-7<br>(15,850)   |

| #2-SP | -                                 | 317         | 26/20          | 130.5        | 93          | Artix-7<br>(15,850)   |

| #3-SP | -                                 | 156         | 23/26          | 96.8         | 64          | Artix-7<br>(15,850)   |

SLICE represents the total available units in the device to provide a comparative metric.

## V. CONCLUSION

The performance requirements for time interval meters are continuously increasing, both in terms of precision and the ability to integrate numerous channels (up to hundreds) on a single device. The MP-SCFC-TDC architecture excellently meets these requests, but having structural issues (i.e., the limited phases  $N_{PH}$  and the problem of the skew) that limit the resolution at 500 ps if no hardware-consuming architectures (e.g., the ones counter method, the phase resort, and the PLL delay-matrix, just to cite the most effective) are introduced. This was the motivation that led to develop and propose the novel architecture SP-SCFC-TDC, which overcomes all drawbacks of the MP-SCFC-TDC by granting both high performance and low area occupancy. The proposed SP-SCFC-TDC, similar to TDL-TDCs, utilizes a delay-line and a single clock distributed through the clock resources of the FPGA to quantize the temporal events for digitization, thereby limiting the effects of skews. However, unlike the purely asynchronous nature of TDL-TDCs, it adopts the sampling techniques of MP-SCFC-TDC, which is a synchronous structure. This design choice minimizes metastability issues that may arise from violations of setup-and-hold times. For validation purpose, three implementations (i.e., #1-SP, #2-SP, and #3-SP) in 28-nm Xilinx 7-Series Artix-7 FPGAs (i.e., Artix-7 35 T and Artix-7 100 T) have been performed, having, respectively, resolutions of 625.5, 317.25, 156.125 ps and single-shot precision of 180, 92.3, and 68.3 ps r.m.s. In addition, the suggested architecture's relatively low resource usage (84 SLICEs for #1-SP, 108 SLICEs for #2-SP, and 110 SLICEs for #3-SP) enables the implementation of up to 32/64 channels in Artix-7 35 T (5 k SLICEs) and 112/128 channels in Artix-7 100 T (15 k SLICEs). Last but not least, DNL and INL are always lower than the 26.4% of the LSB. The suggested TDC is also designed as an IP-Core, making it simple for the user to modify each operating parameter separately."

#### REFERENCES

- J. Molleda et al., "An improved 3D imaging system for dimensional quality inspection of rolled products in the metal industry," *Comput. Ind.*, vol. 64, pp. 1186–1200, Dec. 2013.

- [2] M. E. Warren, "Automotive LIDAR technology," in *Proc. Symp. VLSI Circuits*, 2019, pp. C254–C255.

- [3] H.-S. Lee et al., "RFID-Based real-time locating system for construction safety management," J. Comput. Civil Eng., vol. 26, pp. 366–377, May 2012.

- [4] D. R. Schaart, "Physics and technology of time-of-flight PET detectors," *Phys. Med. Biol.*, vol. 66, 2021, Art. no. 09TR01.

- [5] F. Villa et al., "SPADs and SiPMs arrays for long-range high-speed light detection and ranging (LiDAR)," Sensors, vol. 21, Jan. 2021, Art. no. 3839.

- [6] Y. Fei, "CMOS Time-Mode Circuits and Systems: Fundamentals and Applications." Baco Raton, FL, USA: CRC, 2020.

- [7] R. Machado, J. Cabral, and F. S. Alves, "Recent developments and challenges in FPGA-Based time-to-digital converters," *IEEE Trans. Instrum. Meas.*, vol. 68, no. 11, pp. 4205–4221, Nov. 2019.

- [8] S. Henzler, *Time-to-Digital Converters*, vol. 29, Berlin, Germany: Springer, 2012.

- [9] N. Lusardi et al., "The role of sub-interpolation for delay-line timeto-digital converters in FPGA devices," *NIM A*, vol. 916, pp. 204–214, Feb. 2019.

- [10] Y.-H. Chen, "A high resolution FPGA-based merged delay line TDC with nonlinearity calibration," in *Proc. IEEE Int. Symp. Circuits Syst.*, 2013, pp. 2432–2435.

- [11] R. Nutt, "Digital time intervalometer," *Rev. Sci. Instrum.*, vol. 39, pp. 1342–1345, Sep. 1968.

- [12] D. Chaberski et al., "Comparison of interpolators used for time-interval measurement systems based on multiple-tapped delay line," *Metrol. Meas. Syst.*, vol. 24, pp. 401–412, 2017.

- [13] Y. Wang, X. Zhou, Z. Song, J. Kuang, and Q. Cao, "A 3.0-ps rms precision 277-MSamples/s throughput time-to-digital converter using multi-edge encoding scheme in a Kintex-7 FPGA," *IEEE Trans. Nucl. Sci.*, vol. 66, no. 10, pp. 2275–2281, Oct. 2019.

- [14] M. Parsakordasiabi et al., "A low-resources TDC for multi-channel direct ToF readout based on a 28-nm FPGA," *Sensors*, vol. 21, Jan. 2021, Art. no. 308.

- [15] N. Lusardi et al., "Digital instrument with configurable hardware and firmware for multi-channel time measures," *Rev. Sci. Instrum.*, vol. 90, 2019, Art. no. 055113.

- [16] J. Y. Won and J. S. Lee, "Time-to-digital converter using a tuned-delay line evaluated in 28-, 40-, and 45-nm FPGAs," *IEEE Trans. Instrum. Meas.*, vol. 65, no. 7, pp. 1678–1689, Jul. 2016.

- [17] C. Liu and Y. Wang, "A 128-Channel, 710 M samples/second, and less than 10 ps RMS resolution time-to-digital converter implemented in a Kintex-7 FPGA," *IEEE Trans. Nucl. Sci.*, vol. 62, no. 3, pp. 773–783, Jun. 2015.

- [18] H. Chen and D. D. -U. Li, "Multichannel, low nonlinearity time-to-digital converters based on 20 and 28 nm FPGAs," *IEEE Trans. Ind. Electron.*, vol. 66, no. 4, pp. 3265–3274, Apr. 2019.

- [19] Xilinx, San Jose, CA, USA, "7 series FPGAs clocking resources user guide (UG472)," Jul. 2018.

- [20] M. Fries and J. J. Williams, "High-precision TDC in an FPGA using a 192 MHz quadrature clock," in *Proc. IEEE Nucl. Sci. Symp. Conf. Rec.*, 2002, pp. 580–584.

- [21] G. Cao et al., "An 18-ps TDC using timing adjustment and bin realignment methods in a Cyclone-IV FPGA," *Rev. Sci. Instrum.*, vol. 89, 2018, Art. no. 054707.

- [22] N. Dutton et al., "Multiple-event direct to histogram TDC in 65 nm FPGA technology," in *Proc. 10th Conf. Ph.D. Res. Microelectronics Electron.*, 2014, pp. 1–5.

- [23] W. Yonggang, L. Chong, and Z. Wensong, "Two novel designs of multiphase clocked ultra-high speed time counter on FPGA for TDC implementation," in *Proc. IEEE Nucl. Sci. Symp. Med. Imag. Conf.*, 2013, pp. 1–4.

- [24] M. Büchele et al., "The GANDALF 128-Channel time-to-digital converter," *Phys. Procedia*, vol. 37, pp. 1827–1834, Jan. 2012.

- [25] A. Balla et al., "The characterization and application of a low resource FPGA-based time to digital converter," *Nucl. Instrum. Methods Phys. Res. Sect. A: Accel. Spectrometers Detect. Assoc. Equip.*, vol. 739, pp. 75–82, Mar. 2014.

- [26] A. Tontini, L. Gasparini, L. Pancheri, and R. Passerone, "Design and characterization of a low-cost FPGA-Based TDC," *IEEE Trans. Nucl. Sci.*, vol. 65, no. 2, pp. 680–690, Feb. 2018.

- [27] R. Szplet, D. Sondej, and G. Grzęda, "High-precision time digitizer based on multiedge coding in independent coding lines," *IEEE Trans. Instrum. Meas.*, vol. 65, no. 8, pp. 1884–1894, Aug. 2016.

#### LUSARDI et al.: FROM MULTIPHASE TO NOVEL SINGLE-PHASE MULTICHANNEL SHIFT-CLOCK FAST COUNTER TDC

- [28] E. Arabul, S. Paesani, S. Tancock, J. Rarity, and N. Dahnoun, "A precise high count-rate FPGA based multi-channel coincidence counting system for quantum photonics applications," *IEEE Photon. J.*, vol. 12, no. 4, Apr. 2020, Art. no. 7500114.

- [29] T. Suwada et al., "Wide dynamic range FPGA-based TDC for monitoring a trigger timing distribution system in linear accelerators," *Nucl. Instrum. Methods Phys. Res. Sect. A: Accelerators Spectrometers Detectors Assoc. Equip.*, vol. 786, pp. 83–90, Jun. 2015.

- [30] Z. Li et al., "Development of an integrated four-channel fast avalanchephotodiode detector system with nanosecond time resolution," *Nucl. Instrum. Methods Phys. Res. Sect. A: Accelerators Spectrometers Detectors Assoc. Equip.*, vol. 870, pp. 43–49, Oct. 2017.

- [31] J. Y. Won, S. I. Kwon, H. S. Yoon, G. B. Ko, J. -W. Son, and J. S. Lee, "Dual-phase tapped-delay-line time-to-digital converter with on-the-fly calibration implemented in 40 nm FPGA," *IEEE Trans. Biomed. Circuits Syst.*, vol. 10, no. 2, pp. 231–242, Feb. 2016.

- [32] Q. Shen et al., "A 1.7 ps equivalent bin size and 4.2 ps RMS FPGA TDC based on multichain measurements averaging method," *IEEE Trans. Nucl. Sci.*, vol. 62, no. 6, pp. 947–954, Jun. 2015.

- [33] Z. Xue et al., "A 32-channel FPGA-based multi-phase sampling TDC for RPC detector," in *Proc. Int. Conf. Automat. Electron. Elect. Eng.*, 2020, pp. 14–18.

- [34] F. S. Deng et al., "Design of a 32-channel NIM TDC module based on single FPGA for the μSR spectrometer prototype at the China spallation neutron source," *J. Instrum.*, vol. 14, Jun. 2019, Art. no. T06002.

[35] T. Xiang et al., "A 56-ps multi-phase clock time-to-digital convertor based

- [35] T. Xiang et al., "A 56-ps multi-phase clock time-to-digital convertor based on Artix-7 FPGA," in *Proc. 19th IEEE-NPSS Real Time Conf.*, 2014, pp. 1–4.

- [36] Y. Jia, C. Wang, H. Shi, and X. Liu, "Multi-channel high precision time digital converter system based on equivalent pulse counting," in *Proc. Chin. Control Decis. Conf.*, 2018, pp. 5933–5938.

- [37] Y. Sano et al., "Subnanosecond time-to-digital converter implemented in a Kintex-7 FPGA," Nucl. Instrum. Methods Phys. Res. Sect. A: Accelerators Spectrometers Detected Assoc. Equip., vol. 874, pp. 50–56, Dec. 2017.

- [38] Y. Wang, P. Kuang, and C. Liu, "A 256-channel multi-phase clock sampling-based time-to-digital converter implemented in a Kintex-7 FPGA," in Proc. IEEE Int. Instrum. Meas. Technol. Conf., 2016, pp. 1–5.

- [39] Y. Sano et al., "Development of a sub-nanosecond time-to-digital converter based on a field-programmable gate array," J. Instrum., vol. 11, 2016, Art. no. C03053.

- [40] Y. Sano et al., "Performances of typical high energy physics applications in flash-based field-programmable gate array under gamma irradiation," J. Instrum., vol. 12, Apr. 2017, Art. no. C04002.

- [41] P. Kwiatkowski and R. Szplet, "Efficient implementation of multiple time coding lines-based TDC in an FPGA device," *IEEE Trans. Instrum. Meas.*, vol. 69, no. 10, pp. 7353–7364, Oct. 2020.

- [42] D. N. Grigoriev et al., "A 32-channel 840Msps TDC based on Altera Cyclone III FPGA," J. Instrum., vol. 12, Aug. 2017, Art. no. C08025.

- [43] "Basys 3 digilent reference". [Online]. Available: https://digilent.com/ reference/programmable-logic/basys-3/start

- [44] "Nexys 4 digilent reference". [Online]. Available: https://digilent.com/ reference/programmable-logic/nexys-4/start

- [45] Y. Wang, J. Kuang, C. Liu, and Q. Cao, "A 3.9-ps RMS precision timeto-digital converter using ones-counter encoding scheme in a Kintex-7 FPGA," *IEEE Trans. Nucl. Sci.*, vol. 64, no. 10, pp. 2713–2718, Oct. 2017.

- [46] T. Sui et al., "A 2.3-ps RMS resolution time-to-digital converter implemented in a low-cost cyclone v FPGA," *IEEE Trans. Instrum. Meas.*, vol. 68, no. 10, pp. 3647–3660, Oct. 2019.

- [47] Y. Wang and C. Liu, "A nonlinearity minimization-oriented resourcesaving time-to-digital converter implemented in a 28 nm xilinx FPGA," *IEEE Trans. Nucl. Sci.*, vol. 62, no. 10, pp. 2003–2009, Oct. 2015.

- [48] W. Xie, Y. Wang, H. Chen, and D. D. -U. Li,, "128-Channel high-linearity resolution-adjustable time-to-digital converters for LiDAR applications: Software predictions and hardware implementations," *IEEE Trans. Ind. Electron.*, vol. 69, no. 4, pp. 4264–4274, Apr. 2022.

- [49] N. Lusardi, N. Corna, F. Garzetti, S. Salgaro, and A. Geraci, "Cross-talk issues in time measurements," *IEEE Access*, vol. 9, pp. 129303–129318, 2021.

- [50] P. Chen et al., "High-precision PLL delay matrix with overclocking and double data rate for accurate FPGA time-to-digital converters," *IEEE Trans. VLSI Syst.*, vol. 28, no. 4, pp. 904–913, Apr. 2020.

Nicola Lusardi (Member, IEEE) received the Ph.D. degree in electronics from the Digital Electronics Lab, DEIB, Politecnico di Milano, Milan, Italy, in 2018. His thesis was on a topic regarding high-resolution time-to-digital converters in field programmable gate arrays. He is currently a temporary Researcher with DEIB, Politecnico di Milano, where he is also a Professor of Electronics. He is an Associated Member of the Italian National Nuclear Physics Institute, Rome, Italy.

Fabio Garzetti (Member, IEEE) received the Ph.D. (cum laude) degree in electronics from the Digital Electronics Lab, DEIB, Politecnico di Milano, Milan, Italy, in 2022. His thesis work was on a topic regarding innovative solutions for calibration and triggering of asynchronous signals for time-to-digital converters in field programmable gate arrays.

He is currently a temporary Researcher with DEIB, Politecnico di Milano.

Andrea Costa (Graduate Student Member, IEEE) was born in Piacenza in 1995. He received the B.Sc. degree in biomedical engineering and the M.Sc. degree in electronics engineering from Politecnico di Milano, Milan, Italy, in 2017 and 2020, respectively.

His research interests include innovative hardware architectures for data processing in the field of FPGA time-domain devices and FPGA DAQ for high data rate environments.

Enrico Ronconi (Member, IEEE) received the master's degree in electronic engineering from Politecnico di Milano, Milan, Italy, in 2020.

His research interests include advanced programmable logic and software architectures for data processing and transfer in field programmable gate arrays implemented scientific equipment, currently used and developed together with the time-to-digital and digital-to-time converters developed in the same laboratory.

Angelo Geraci (Senior Member, IEEE) received the Ph.D. (cum laude) degree in electronics from Politecnico di Milano, Milan, Italy, in 1996.

He has been an Associate Professor with the Department of Electronics, Information and Bioengineering (DEIB), Politecnico di Milano, since 2004. His research interests inlcude digital electronics based on microcontrollers, DSP and FPGA devices, specifically in the areas of radiation detection, and medical imaging.

Open Access provided by Politecnico di Milano within the CRUI-CARE Agreement.