# DESIGN OF THE ELECTRONICS SUBSYSTEM FOR A HIGH-RESOLUTION ELECTRO-OPTICAL PAYLOAD USING SYSTEMS ENGINEERING APPROACH

## Nasir Mehmood

Dissertation submitted in partial fulfilment of the requirements for the degree of Master of Philosophy in Space Studies Supervisor: Professor Peter Martinez

October 2022

The copyright of this thesis vests in the author. No quotation from it or information derived from it is to be published without full acknowledgement of the source. The thesis is to be used for private study or non-commercial research purposes only.

Published by the University of Cape Town (UCT) in terms of the non-exclusive license granted to UCT by the author.

# **DECLARATION**

#### I, Nasir Mehmood, hereby declare that

- i. I know the meaning of plagiarism and declare that all the work in the document, save for that which is properly acknowledged, is my own.

- ii. This dissertation has been submitted to the Turnitin module and I confirm that my supervisor has seen my report and any concerns revealed by such have been resolved with my supervisor

This dissertation is presented for examination in partial fulfilment of the requirements for the degree of Master of Philosophy in Space Studies.

## Signed by candidate

Nasir Mehmood 30<sup>th</sup> March 2020

# **ABSTRACT**

Satellite imagers, in contrast to commercial imagers, demand exceptional performance and operate under harsh conditions. The camera is an essential part of an Earth Observation Electro-Optical (EO) payload that is designed in response to needs such as military demands, changes in world politics, inception of new technologies, operational requirements and experiments. As one of the key subsystems, the Imager Electronics Subsystem of a high-resolution EO payload plays very important role in the accomplishment of mission objectives and payload goals. Hence, these Electronics Subsystems require a special design approach optimised for their needs and meticulous characterizations of high-resolution space applications.

This dissertation puts forward the argument that the system being studied is a subsystem of a larger system and that systems engineering principles can be applied to the subsystem design process also. The aim of this dissertation is to design the Imager Electronics Subsystem of a high-resolution Electro Optical Payload using a systems engineering approach to represent a logical integration and test flow using the space industry guidelines.

The Imager Electronics Subsystem consists of group of elements forming the functional chain from the Image Sensors on the Focal Plane down to electrical interface to the Data Handling Unit and power interface of the satellite. This subsystem is responsible for collecting light in different spectral bands, converting this light to data of different spectral bands from image sensors for high-resolution imaging, performing operations for aligning, tagging and multiplexing along with incorporating internal and external interfaces.

## **ACKNOWLEDGEMENTS**

I am grateful to almighty Allah, for all His blessings that enabled me to complete my dissertation.

I present my sincere gratitude to Professor Peter Martinez of SpaceLab who provided invaluable guidance and encouragement to complete this dissertation for which I am grateful. I am also very much thankful to Prof. Rene Laufer who taught us the systems engineering so well that guided me at every step of this dissertation.

I extend my warmest gratitude to my parents who encouraged me to take-up this master program. They motivated me to think space from my childhood and shaped my career. I am grateful for their support.

I am particularly grateful to my wife Zainab and children for their prayers and the cooperation and understanding they showed during this time.

I am thankful to all my colleagues at SpaceLab; it has been a great privilege to complete this difficult and challenging but fruitful journey with all of them.

# TABLE OF CONTENTS

| 1   | INTR                        | ODUCTION                                                 | 15 |  |  |  |

|-----|-----------------------------|----------------------------------------------------------|----|--|--|--|

| 1.1 | Мотіу                       | ATION                                                    | 15 |  |  |  |

| 1.2 | OBJEC                       | TIVES                                                    | 17 |  |  |  |

| 1.3 | SCOPE                       | OF THIS DISSERTATION                                     | 17 |  |  |  |

| 1.4 | ORGA                        | NISATION OF DISSERTATION                                 | 18 |  |  |  |

| 2   | SYST                        | EMS ENGINEERING APPROACH IN DESIGN                       | 20 |  |  |  |

| 2.1 | INTRO                       | DUCTION                                                  | 20 |  |  |  |

| 2.2 | SYSTE                       | MS ENGINEERING PROCESS                                   | 21 |  |  |  |

| 2.3 | PROBL                       | EM STATEMENT                                             | 22 |  |  |  |

| 2.4 | REQUI                       | REMENTS DEFINITION, ANALYSIS AND CONCEPT REFINEMENT      | 24 |  |  |  |

| 2.5 | FUNCT                       | TIONAL ANALYSIS, DECOMPOSITION AND ALLOCATION            | 25 |  |  |  |

| 2.6 | SEARC                       | CH FOR ALTERNATIVES                                      | 26 |  |  |  |

| 2.7 | DESIG                       | N BASELINE                                               | 27 |  |  |  |

| 2.8 | INTERI                      | FACE MANAGEMENT                                          | 27 |  |  |  |

| 2.9 | VALID                       | ATION AND VERIFICATION                                   | 27 |  |  |  |

| 3   | Validation and Verification |                                                          |    |  |  |  |

| 3.1 | SYSTE                       | M OVERVIEW                                               | 28 |  |  |  |

|     | 3.1.1                       | System Hierarchy                                         | 29 |  |  |  |

|     | 3.1.2                       | System Requirements                                      | 30 |  |  |  |

| 3.2 | SUBSY                       | STEM PRELIMINARY REQUIREMENT DEFINITIONS                 | 31 |  |  |  |

| 3.3 | REQUI                       | REMENTS ANALYSIS                                         | 32 |  |  |  |

|     | 3.3.1                       | Subsystem Operation and Environment Analysis             | 32 |  |  |  |

|     | 3.3.2                       | Identify Functional Requirements                         | 34 |  |  |  |

|     | 3.3.3                       | Identify Performance Requirements and design constraints | 35 |  |  |  |

|     | 3.3.4                       | Identify design constraints                              | 35 |  |  |  |

|     | 3.3.5                       | Tasks Performed                                          | 37 |  |  |  |

|     | 3.3.6                       | Define and Refine Requirements                           | 43 |  |  |  |

|     | 3.3.7                       | Requirements Baseline                                    | 47 |  |  |  |

|     | 3.3.8                       | Requirements Traceability                                | 49 |  |  |  |

| 3.4 | FUNCT                       | TIONAL ANALYSIS AND ALLOCATION                           | 51 |  |  |  |

|     | 3.4.1                       | Identify Subsystem Functions                             | 51 |  |  |  |

|     | 3.4.2                       | Decompose Each Function to Lower-Level Functions         | 51 |  |  |  |

|     | 3.4.3                       | Allocate Requirements to All Functional Levels           | 52 |  |  |  |

|     | 3.4.4 | Define/Refine Functional Interfaces (Internal and External)       | 52        |

|-----|-------|-------------------------------------------------------------------|-----------|

|     | 3.4.5 | Functional Baseline                                               | 52        |

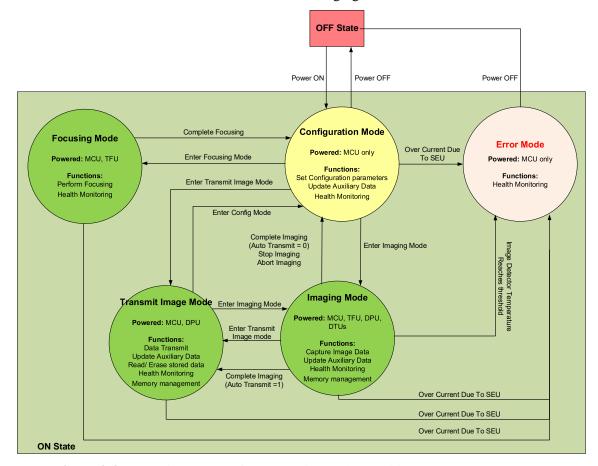

| 3.5 | Mode  | S OF OPERATION                                                    | 52        |

|     | 3.5.1 | Configuration Mode                                                | 53        |

|     | 3.5.2 | Imaging Mode                                                      | 53        |

|     | 3.5.3 | Playback Mode                                                     | 55        |

|     | 3.5.4 | Focusing Mode                                                     | 55        |

|     | 3.5.5 | Error Mode                                                        | 55        |

| 4   | DESIG | GN SYNTHESIS, ALTERNATE-CONCEPTS AND EVALUATION                   | 57        |

| 4.1 | INTRO | DUCTION                                                           | 57        |

| 4.2 | ALTER | NATES FOR PROCESSING ELECTRONICS ASSEMBLY                         | 60        |

|     | 4.2.1 | Alternate-1                                                       | 60        |

|     | 4.2.2 | Alternate-2                                                       | 62        |

|     | 4.2.3 | Alternate-3                                                       | 64        |

|     | 4.2.4 | Alternate-4                                                       | 66        |

|     | 4.2.5 | Trede-off Criteria and weighting                                  | 67        |

| 4.3 | ALTER | NATIVES FOR THE FOCAL PLANE ASSEMBLY                              | 72        |

|     | 4.3.1 | Alternate-A                                                       | 74        |

|     | 4.3.2 | Alternate-B                                                       | 75        |

|     | 4.3.3 | Alternate-C                                                       | <i>78</i> |

|     | 4.3.4 | Alternate-D                                                       | 80        |

|     | 4.3.5 | Trade-off Critera and Weighting                                   | 82        |

| 4.4 | Conci | USION                                                             | 84        |

| 5   | BASE  | LINE DESIGN                                                       | 85        |

| 5.1 | INTRO | DUCTION                                                           | 85        |

| 5.2 | ELECT | RONICS DESIGN DESCRIPTION                                         | 85        |

|     | 5.2.1 | Overview                                                          | 85        |

|     | 5.2.2 | Focal Plane Assembly: Detector Unit (DTU)                         | 88        |

|     | 5.2.3 | Processing Electronics Assembly: Image Data Processing Unit (DPU) | 89        |

|     | 5.2.4 | Processing Electronics Assembly: Management Controller Unit (MCU) | 92        |

|     | 5.2.5 | Processing Electronics Assembly: Thermal Controller Unit (TCU)    | 95        |

|     | 5.2.6 | Front Plane Unit (FPU)                                            | 97        |

| 5.3 | Сомро | ONENTS SELECTION                                                  | 97        |

| 5.4 | Engin | EERING BUDGETS                                                    | 98        |

|     | 5.4.1 | Power Budgets                                                     | 98        |

|     | 5.4.2 | Data Budget                                                       | 99        |

|     | 5.4.3                                 | SNR Performance                                               | 99  |  |  |  |  |

|-----|---------------------------------------|---------------------------------------------------------------|-----|--|--|--|--|

| 6   | ASSE                                  | MBLY INTEGRATION AND VERIFICATION PLANNING                    | 101 |  |  |  |  |

| 6.1 | Introi                                | DUCTION                                                       | 101 |  |  |  |  |

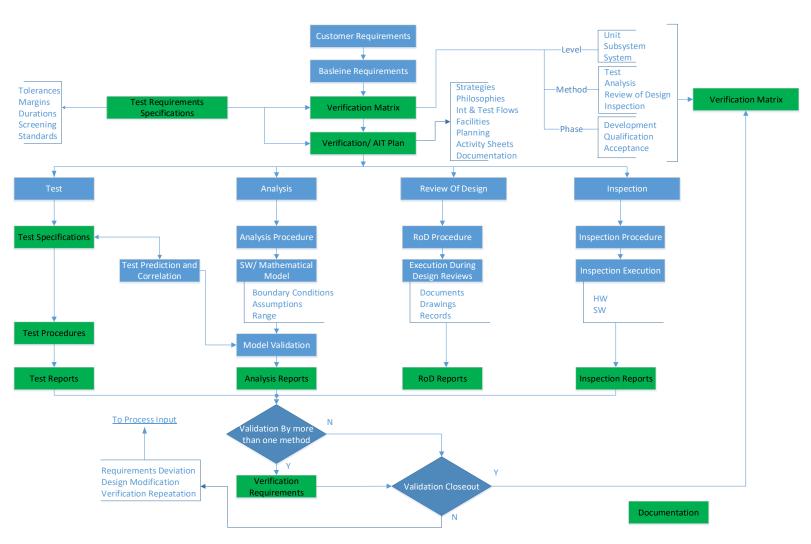

| 6.2 | VERIFI                                | ICATION OF THE IES                                            | 101 |  |  |  |  |

|     | 6.2.1                                 | Verification Methods                                          | 102 |  |  |  |  |

|     | 6.2.2                                 | Verification Levels                                           | 103 |  |  |  |  |

|     | 6.2.3                                 | Verification Stages                                           | 103 |  |  |  |  |

| 6.3 | Model                                 | L PHILOSOPHY                                                  | 103 |  |  |  |  |

|     | 6.3.1                                 | Units and Subsystems Model Philosophy                         | 104 |  |  |  |  |

|     | 6.3.2                                 | Development Plan                                              | 105 |  |  |  |  |

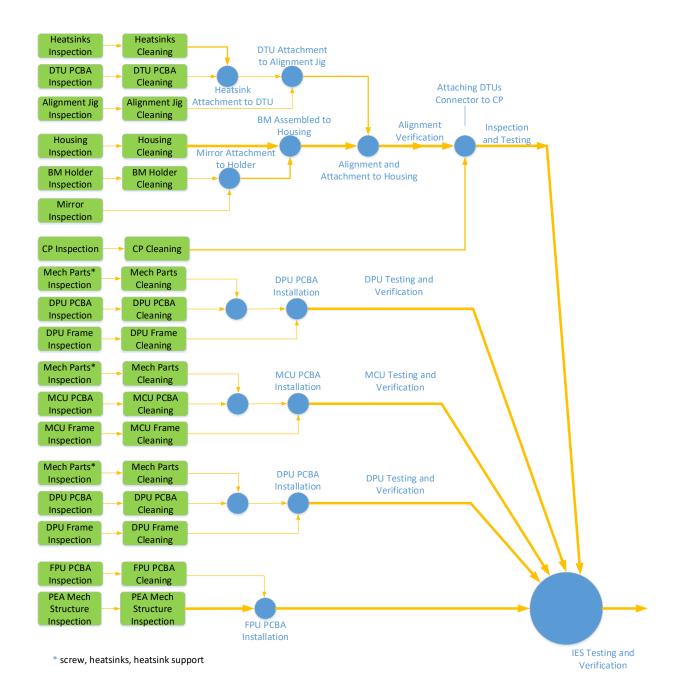

| 6.4 | ASSEM                                 | IBLY, INTEGRATION AND TEST FLOW                               | 110 |  |  |  |  |

| 6.5 | ELECT                                 | RICAL GROUND SUPPORT EQUIPMENT                                | 111 |  |  |  |  |

| 6.6 | FACILI                                | TIES                                                          | 112 |  |  |  |  |

| 6.7 | Docun                                 | MENTATION                                                     | 112 |  |  |  |  |

| 7   | CONC                                  | CLUSION                                                       | 115 |  |  |  |  |

| 7.1 | SUMMA                                 | ARY                                                           | 115 |  |  |  |  |

| 7.2 | FUTUR                                 | E WORK                                                        | 115 |  |  |  |  |

| REF | FEREN                                 | CES                                                           | 117 |  |  |  |  |

| APP | PENDIC                                | CES                                                           | 121 |  |  |  |  |

| APP | ENDIX A                               | A - CALCULATION FOR OVERLAP PIXELS                            | 122 |  |  |  |  |

| APP | endix B                               | B – ESTIMATION FOR REQUIRED NUMBER OF DETECTORS AFTER OVERLAP | 123 |  |  |  |  |

| APP | PENDIX C – IES TECHNICAL REQUIREMENTS |                                                               |     |  |  |  |  |

# **LIST OF FIGURES**

| FIGU   | <b>RE 2-1</b> : | Systems 1  | Engineering P   | ROCESS [9].  |           |             |            |            | 22      |

|--------|-----------------|------------|-----------------|--------------|-----------|-------------|------------|------------|---------|

| FIGU   | RE 2-2:         | PROBLEM    | STATEMENT FO    | R THE PROJE  | CT DISSE  | RTATION V   | WORK       |            | 23      |

| FIGU   | RE 2-3:         | THE EFFEC  | CTIVE NEED AN   | D STATEMEN   | T FOR TH  | IIS PROJEC  | т          |            | 23      |

| FIGU   | RE 3-1:         | EO PAYL    | OAD SYSTEM I    | HIERARCHY    | AND LEV   | EL NAME     | CONVENT    | TIONS. THE | LOWER-  |

|        | LEVELS          | OF IMAGE   | R ELECTRONICS   | S SUBSYSTEM  | I ARE ELA | ABORATEI    | ) IN THE H | IERARCHY.  | 30      |

| FIGU   | RE 3-2:         | CONTEXT    | Γ ANALYSIS OF   | THE SUBSY    | STEM S    | HOWING 7    | THE ENVI   | RONMENTS   | OF THE  |

|        | SUBSYS          | TEM IN WE  | HICH IT HAS TO  | OPERATE AN   | D POTEN   | TIAL INTE   | RACTION V  | WITH EACH  | TYPE OF |

|        | ENVIRO          | NMENTS     |                 |              |           |             |            |            | 33      |

| FIGU   | RE 3-3:         | SUBSYSTE   | M SPECIFICATION | ON TREE      |           |             |            |            | 36      |

| FIGU   | RE <b>3-4</b> : | TASKS PEI  | RFORMED OF TH   | HE REQUIREM  | IENTS AN  | NALYSIS O   | F THE IES  | . THESE TA | SKS ARE |

|        | NOT PE          | RFORMED    | IN THE SEQUE    | ENCE SHOWN   | I, RATHE  | ER THERE    | WERE M.    | ANY JUMPI  | ING AND |

|        | ITERATI         | ONS BETW   | EEN THESE TAS   | KS           |           |             |            |            | 37      |

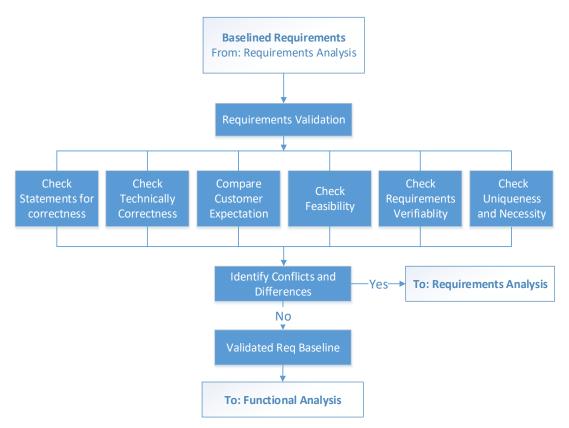

| FIGU   | RE 3-5:         | THE PROC   | CESS OF REQUIR  | EMENTS VAI   | LIDATION  | I. IT IS AN | ITERATIV   | E PROCESS  | THAT IS |

|        | BASED           | ON THE     | RESULTS OF T    | THE FUNCTION | NAL AN    | NALYSIS A   | AND ANY    | CHANGES    | IN THE  |

|        | REQUIR          | EMENTS OF  | R ANALYSIS RES  | SULTS        |           |             |            |            | 48      |

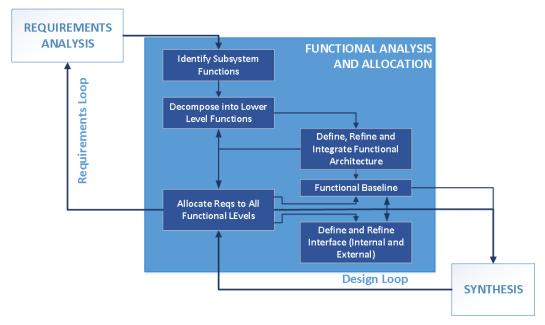

| FIGU   | RE 3-6:         | : FUNCTIO  | NAL ANALYSIS    | S AND ALLO   | CATIONS   | -WITH TH    | E REQUIR   | REMENTS A  | JDS THE |

|        | SYNTHE          | ESIS PROCE | SS THROUGH TH   | HE DESIGN LO | OP        |             |            |            | 51      |

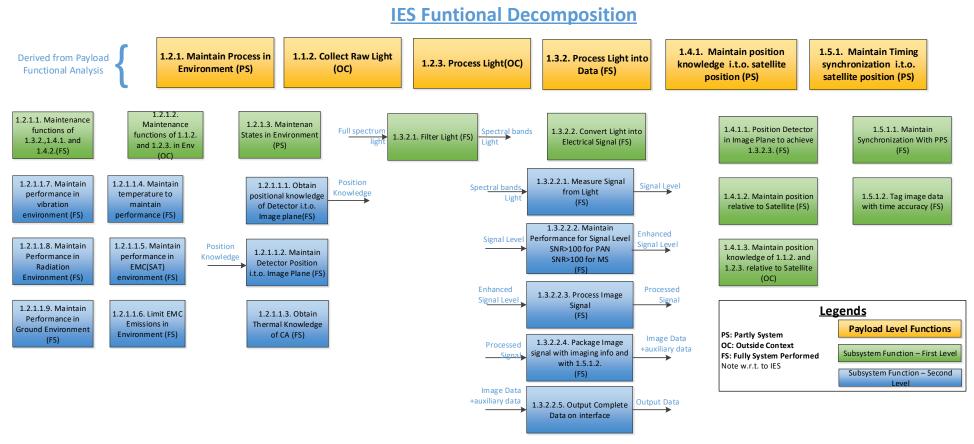

| FIGU   | RE 3-7:         | FUNCTION   | NS OF DIFFEREN  | NT LEVELS ID | ENTIFIEI  | FOR THE     | E IES THR  | OUGH FUN   | CTIONAL |

|        | ANALY           | SIS.       |                 | •••••        |           |             |            |            | 54      |

| FIGU   | RE              | 3-8:       | Operating       | modes        | of        | the         | IES        | with       | mode    |

| transi | tions           |            |                 | 5            | 5         |             |            |            |         |

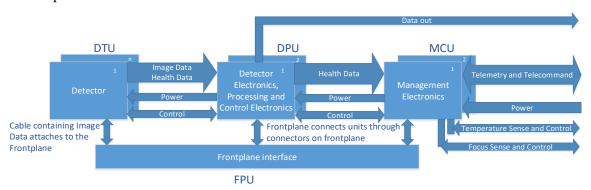

| FIGU   | RE 4-1:         | BLOCK LE   | EVEL REPRESEN   | TATION OF A  | ALTERNA   | TE-1. FOR   | SIMPLIFIC  | CATION ON  | LY MAIN |

|        | INTERFA         | ACES ARE   | SHOWN. THE I    | DATA OUTPU   | T INTERF  | FACE HAS    | TWO CHA    | ANNELS (M. | AIN AND |

|        | REDUNI          | DANT) FRO  | M EACH DPU      | . TMTC ANI   | O POWE    | R INTERFA   | ACES ARE   | ALSO RED   | UNDANT  |

|        | INTERFA         | ACES FOR E | EACH MCU        |              |           |             |            |            | 61      |

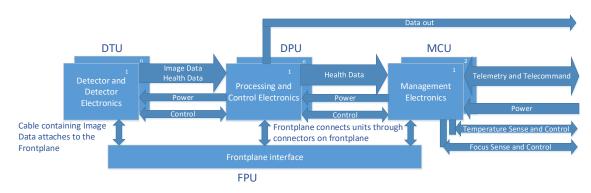

| FIGU   | RE 4-2:         | BLOCK LE   | EVEL REPRESEN   | TATION OF A  | ALTERNA   | TE-2. FOR   | SIMPLIFIC  | CATION ON  | LY MAIN |

|        | INTERFA         | ACES ARE S | SHOWN. THE DE   | ESIGN ALTERN | NATE HAS  | S EQUAL N   | UMBER OI   | f DTUs an  | D DPUs, |

|        | I.E. ONE        | E DPU FOR  | R EACH DTU. 7   | THE DATA OU  | JT INTER  | FACE HAS    | TWO CHA    | ANNELS (M  | AIN AND |

|        | REDUNI          | DANT) FRO  | OM EACH DPU     | . TMTC ANI   | ) Power   | R INTERFA   | ACES ARE   | ALSO RED   | UNDANT  |

|        | INTERFA         | ACES FOR E | EACH OF THE M   | CU           |           |             |            |            | 63      |

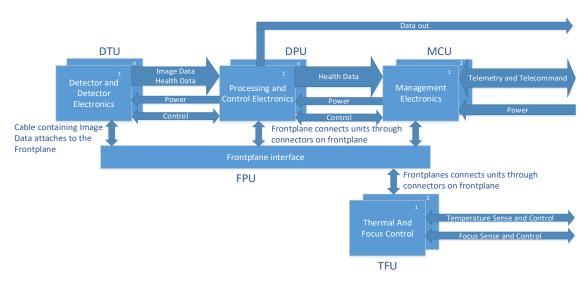

| FIGURE 4-3: BLOCK LEVEL REPRESENTATION OF ALTERNATE-3. FOR SIMPLIFICATION ONLY MAIN |

|-------------------------------------------------------------------------------------|

| INTERFACES ARE SHOWN. THE DESIGN ALTERNATE HAS EQUAL NUMBER OF DTUS AND DPUS,       |

| I.E. ONE DPU FOR EACH DTU. THE MCU AND TFU ARE DUAL REDUNDANT. THE DATA OUT         |

| INTERFACE HAS TWO CHANNELS (MAIN AND REDUNDANT) FROM EACH DPU. TMTC AND             |

| POWER INTERFACES ARE ALSO REDUNDANT INTERFACES FOR EACH OF THE MCU65                |

| FIGURE 4-4: BLOCK LEVEL REPRESENTATION OF ALTERNATE-4. FOR SIMPLIFICATION ONLY MAIN |

| INTERFACES ARE SHOWN. THE DESIGN ALTERNATE HAS EQUAL NUMBER OF DTUS AND DPUS,       |

| I.E. ONE DPU FOR EACH DTU. THE DATA OUT INTERFACE HAS TWO CHANNELS (MAIN AND        |

| REDUNDANT) FROM EACH MCU. TMTC AND POWER INTERFACES ARE ALSO REDUNDANT              |

| INTERFACES FOR EACH OF THE MCU. EACH OF THE MCU AND TFU HAS STANDBY                 |

| (REDUNDANT) UNIT66                                                                  |

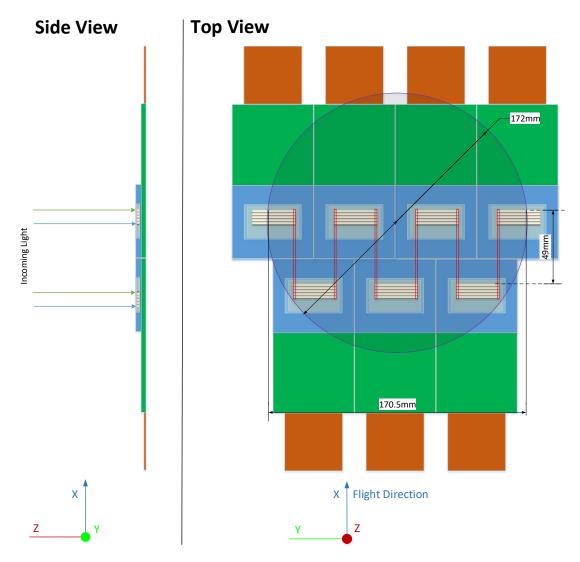

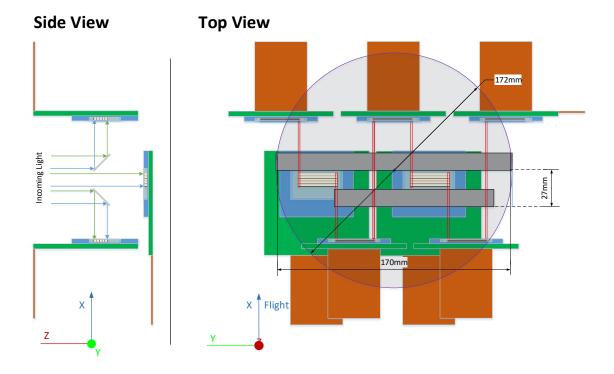

| FIGURE 4-5: ALTERNATE-A-THE FLATPLANE ARRANGEMENT DETECTOR UNIT IN FOCAL PLANE      |

| Assembly75                                                                          |

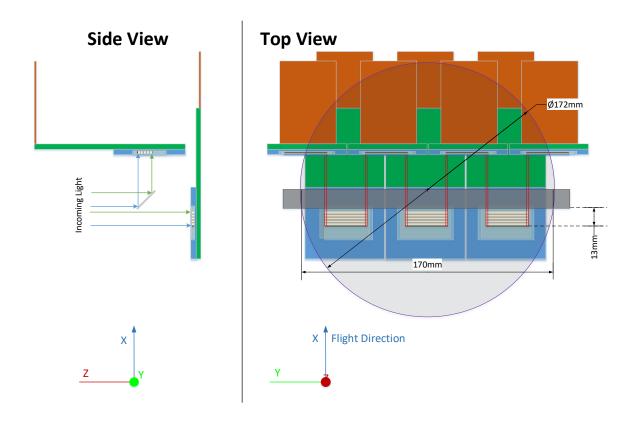

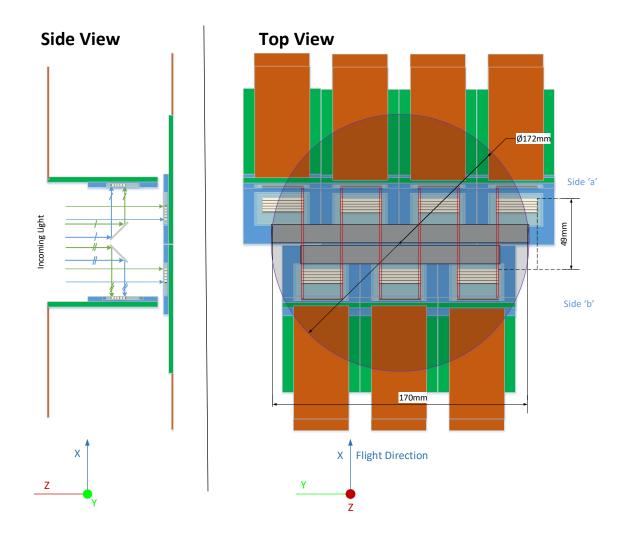

| FIGURE 4-6: ALTERNATE-B, VARIANT-1- FOCAL PLANE ASSEMBLY WITH MIRROR AND            |

| ARRANGEMENT DETECTORS IN TWO PLANES                                                 |

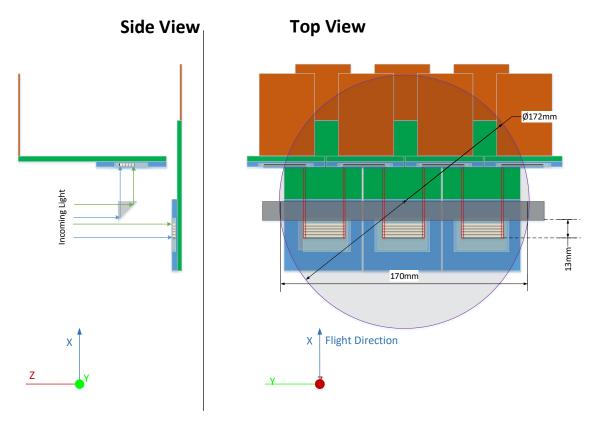

| FIGURE 4-7: ALTERNATE-B VARIANT-2-FPA WITH PRISM AND ARRANGEMENT DETECTORS IN TWO   |

| PLANES                                                                              |

| FIGURE 4-8: ALTERNATE-C-THE ARRANGEMENT DETECTORS IN TWO YZ PLANES AND ONE XY       |

| PLANE OF FOCAL PLANE ASSEMBLY79                                                     |

| FIGURE 4-9: ALTERNATE-D-THE ARRANGEMENT DETECTORS FOR SUPER-RESOLUTION IN TWO YZ    |

| PLANES AND ONE XY PLANE OF FOCAL PLANE ASSEMBLY                                     |

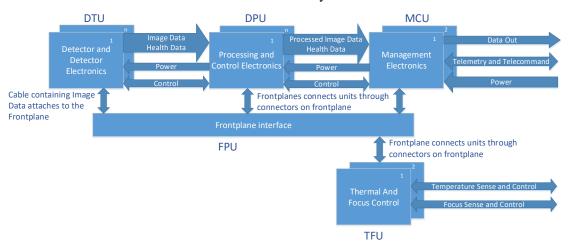

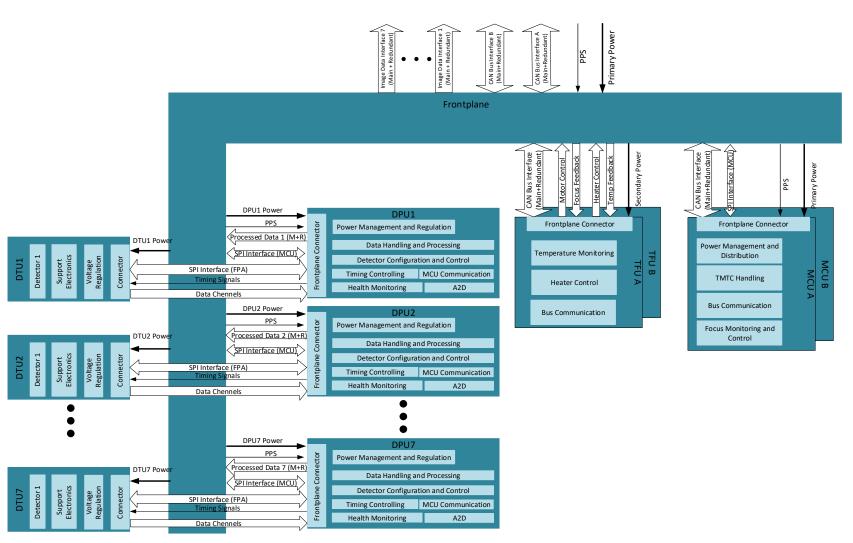

| FIGURE 5-1: DETAILED BLOCK DIAGRAM OF THE IMAGER ELECTRONICS SUBSYSTEM SHOWING      |

| THE INTERNAL AND EXTERNAL INTERFACES87                                              |

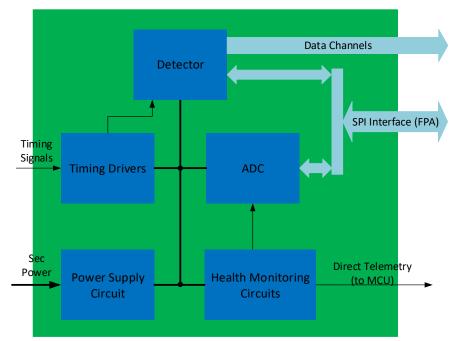

| FIGURE 5-2: BLOCK DIAGRAM OF DETECTOR UNIT                                          |

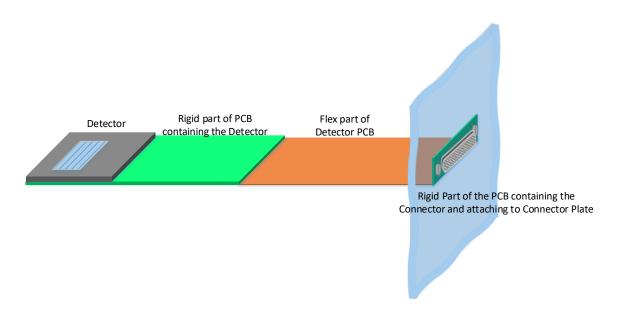

| FIGURE 5-3: RIGID-FLEX-RIGID CONSTRUCTION OF THE DTU AND ATTACHMENT TO THE          |

| CONNECTOR PLATE89                                                                   |

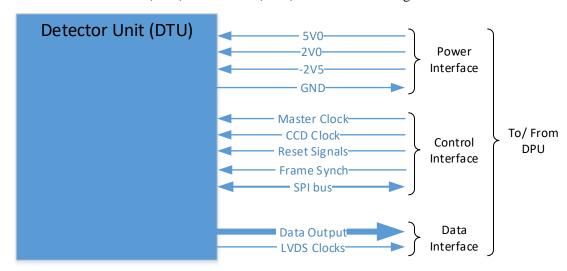

| FIGURE 5-4: INTERFACES OF THE DTU WITH RESPECTIVE DTU                               |

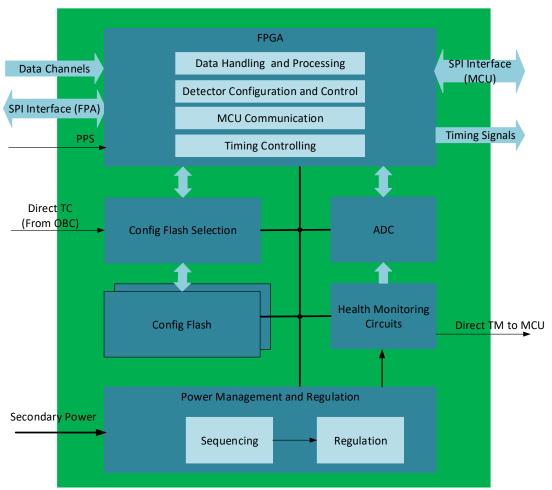

| FIGURE 5-5: FUNCTIONAL BLOCK DIAGRAM OF DPU. 90                                     |

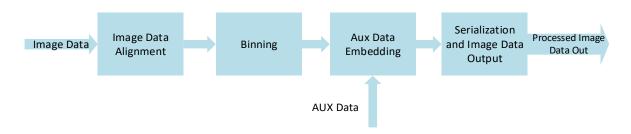

| FIGURE 5-6: DATA PROCESSING CHAIN OF THE FPGA                                       |

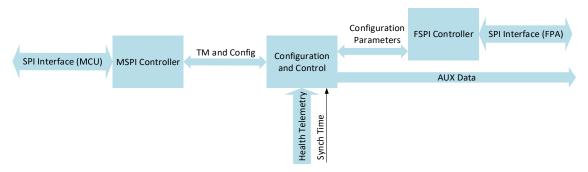

| FIGURE 5-7: THE DETECTOR CONFIGURATION AND CONTROL CHAIN OF THE DPU FPGA91          |

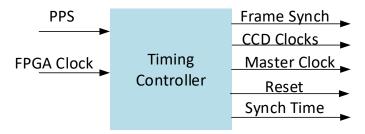

| FIGURE 5-8: INPUTS AND OUTPUTS OF THE TIMING CONTROLLER OF FPGA                     |

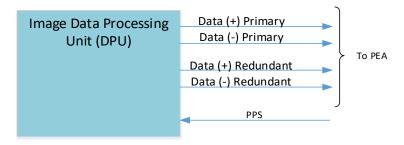

| FIGURE 5-9: DPU TO PEA INTERFACE FOR DATA OUTPUT                                    |

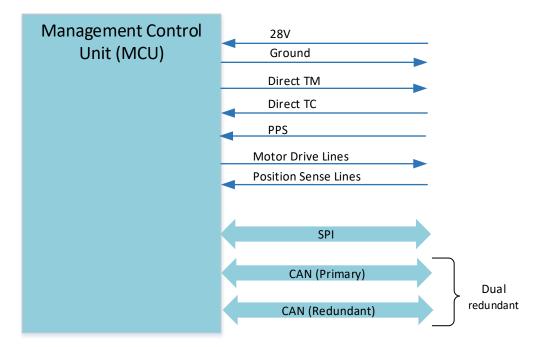

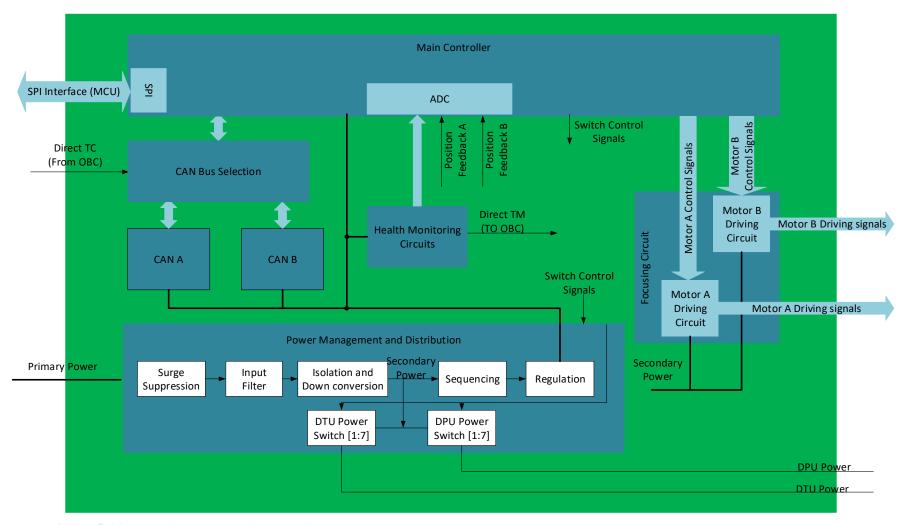

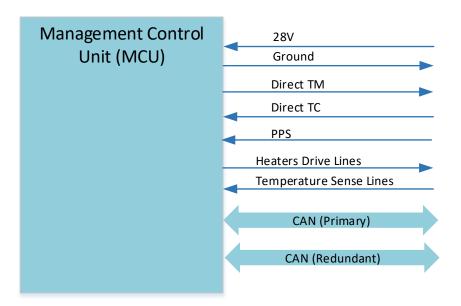

| FIGURE 5-10: MCU INTERFACES.                                                        |

| FIGURE 5-11: FUNCTIONAL BLOCK DIAGRAM OF MCU                                      | 94    |

|-----------------------------------------------------------------------------------|-------|

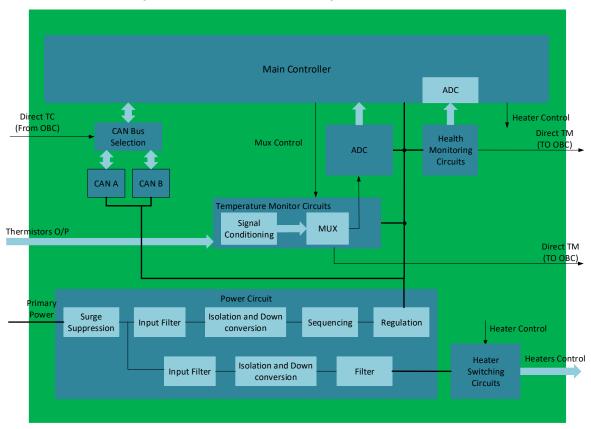

| FIGURE 5-12: TCU INTERFACES.                                                      | 96    |

| FIGURE 5-13: FUNCTIONAL BLOCK DIAGRAM OF THE TCU.                                 | 96    |

| FIGURE 6-1: COMPLETE VERIFICATION FLOW OF IES SUBSYSTEM.                          | 101   |

| FIGURE 6-2: ASSEMBLY AND INTEGRATION FLOW FOR THE ASSEMBLIES AND UNITS OF THE IES | . 110 |

| FIGURE 6-3: BLOCK DIAGRAM OF THE EGSE FOR IES TESTING.                            | 111   |

| FIGURE 6-4: RELATIONSHIP BETWEEN AIT ACTIVITIES AND DOCUMENTATION [39]            | 114   |

# LIST OF TABLES

| TABLE 2-1: PRINCIPLES OF SYSTEMS ENGINEERING APPROACH                         | 21         |

|-------------------------------------------------------------------------------|------------|

| TABLE 3-1: SYSTEM OVERVIEW, SHOWING THE SUBSYSTEMS AND THEIR DESIGN RESPONSIB | ILITIES.29 |

| TABLE 3-2: TASKS PERFORMED FOR REQUIREMENTS ANALYSIS WITH THE INQUIRY FOR EA  | CH TASK    |

| AND THE RESOLUTIONS                                                           | 38         |

| TABLE 3-3: TEMPLATE FOR RECORDING THE SUBSYSTEM REQUIREMENTS.                 | 46         |

| TABLE 3-4: EXAMPLE OF THE TRACEABILITY OF THE SYSTEM REQUIREMENTS TO THE SU   | BSYSTEM    |

| REQUIREMENTS                                                                  | 49         |

| TABLE 3-5: EXAMPLE OF THE TRACEABILITY OF THE SUBSYSTEM REQUIREMENTS TO T     | THE UNIT   |

| REQUIREMENTS                                                                  | 50         |

| TABLE 4-1: PARAMETERS OF THE DETECTOR FOR THE IES.                            | 60         |

| TABLE 4-2: THE COMPARISON OF ALTERNATES FOR PEA USING WEIGHTED CRITERIA       | 71         |

| TABLE 4-3: TRADE-OFF AMONG FPA CANDIDATE DESIGNS.                             | 84         |

| TABLE 5-1: PARAMETERS OF MANAGEMENT CONTROLLER UNIT.                          | 95         |

| TABLE 5-2: PARAMETERS OF THE TCU.                                             | 97         |

| TABLE 5-3: CRITICAL COMPONENTS OF THE IES DESIGN.                             | 98         |

| TABLE 5-4: POWER CONSUMPTION OF IES UNITS IN DIFFERENT MODES OF EO PAYLOAD.   | 99         |

| TABLE 5-5: DATA RATE OF THE IES.                                              | 99         |

| TABLE 5-6: SNR PERFORMANCE ESTIMATES.                                         | 100        |

| TABLE 6-1: TEST PER UNITS AND SUB-SYSTEM.                                     | 104        |

| TABLE 6-2: ACTIVITIES FOR EM, QM AND FM.                                      | 105        |

| TABLE 6-3: ELECTRONIC ENGINEERING VERIFICATION.                               | 106        |

| TABLE 6-4: EMI EMC AND ESD VERIFICATION.                                      | 107        |

| TABLE 6-5: RADIATION EXPOSURE VERIFICATION.                                   | 108        |

| TABLE 6-6: MECHANICAL/ STRUCTURAL TESTING.                                    | 109        |

| TABLE 6-7: AIT FACILITIES.                                                    | 113        |

# LIST OF ACRONYMS

| ADC            | Analog-to-Digital Converter                    |

|----------------|------------------------------------------------|

| AIT            | Assembly, Integration and Test                 |

| AIV            | , ,                                            |

| '              | Assembly, Integration and Verification         |

| AOCS           | Attitude and Orbital Control System            |

| AR             | Anti-reflective                                |

| CAD            | Computer Aided Design                          |

| CAN            | Controller Area Network                        |

| CCD            | Charge Coupled Device                          |

| CE             | Conductive Emission                            |

| CMOS           | Complementary Metal Oxide Semiconductor        |

| COTS           | Commercial Off The Shelf                       |

| CS             | Conductive Susceptibility                      |

| DC             | Direct Current                                 |

| DPU            | Data Processing Unit                           |

| DTU            | Detector Unit                                  |

| ECSS           | European Cooperation for Space Standardization |

| EGSE           | Electrical Ground Support Equipment (EGSE)     |

| EM             | Electromagnetic                                |

| EM             | Engineering Model                              |

| EMC            | Electromagnetic Compatibility                  |

| EMI            | Electromagnetic Interference                   |

| ЕО             | Electro Optical                                |

| ESA            | European Space Agency                          |

| ESD            | Electrostatic Discharge                        |

| FE             | Finite Element                                 |

| FM             | Flight Model                                   |

| FPA            | Focal Plane Assembly                           |

| FPGA           | Field Programmable Grid Array                  |

| FMS            | Focal Plane Assembly - Mechanical Structure    |

| FPU            | Front Plane Unit                               |

| FS             | Fully System                                   |

| GigE           | Gigabit Ethernet                               |

| GSD            | Ground Sampling Distance                       |

| GSE            | Ground Support Equipment                       |

| · <del>-</del> | ···rr····r··r·························         |

| I/O    | Input/ Output                                 |

|--------|-----------------------------------------------|

| IC     | Integrated Circuit                            |

| IES    | Imager Electronics Subsystem                  |

| INCOSE | International Council on Systems Engineering  |

| ITAR   | International Traffic in Arms Regulations     |

| LEO    | Low Earth Orbit                               |

| LVDS   | Low Voltage Differential Signaling            |

| MCU    | Management Controller Unit                    |

| MOE    | Measure of Effectiveness                      |

| MOP    | Measure of Performance                        |

| MS     | Multispectral                                 |

| MTF    | Modulation Transfer Function                  |

| MUX    | Multiplexer                                   |

| NASA   | National Aeronautics and Space Administration |

| NGO    | Needs Goals and Objectives                    |

| NUC    | Nonuniformity Correction                      |

| OBC    | Onboard Computer                              |

| OC     | Out of Context                                |

| OPS    | Optical Subsystem                             |

| PBS    | Product Breakdown Structure                   |

| PC     | Personal Computer                             |

| PCB    | Printed Circuit Board                         |

| PCBA   | PCB Assembly                                  |

| PEA    | Payload Electronics Assembly                  |

| PLS    | Payload Electronics Subsystem                 |

| PHY    | Physical Layer                                |

| PI     | Power Integrity                               |

| PPS    | Pulse Per Second                              |

| PS     | Partially System                              |

| QM     | Qualification Model                           |

| QPL    | Qualified Part List                           |

| RE     | Radiative Emission                            |

| RS     | Radiative Susceptibility                      |

| SE     | Systems Engineering                           |

| SEE    | Single Event Effect                           |

| SEP    | Systems Engineering Process                   |

| SI   | Signal Integrity                  |

|------|-----------------------------------|

| SNR  | Signal to Noise Ratio             |

| SPI  | Serial Peripheral Interface       |

| TBC  | To Be Confirmed                   |

| TBD  | To Be Determined                  |

| TFU  | Thermal and Focus Controller Unit |

| TID  | Total Ionization Dose             |

| TMTC | Telemetry and Telecommand         |

| TRL  | Technology Readiness Level        |

| WBS  | Work Breakdown Structure          |

# 1 Introduction

#### 1.1 Motivation

During the last two decades, the worldwide demand for mid-to-high resolution Earth images taken from LEO satellites has constantly increased for a widespread range of applications from the defense and security, to environmental, agricultural, and geophysics applications to more recent general public demand [1]. Starting with the launch of the IKONOS satellite in 1999, space-based imaging systems have achieved sub-meter ground resolution for commercial applications and the quality and amount of information provided by these optical payloads is continually increasing. High-Resolution (HR) Electro-optical satellite imagery offers sub-meter resolution that is regarded as the highest quality images currently available from commercial remote sensing. These satellites are generally characterized by large dimensions, heavy weight and typically high cost. This implies that considerable effort is required for the design of the payload for these high-resolution satellites to make the mission successful.

As one of the key subsystems, the Electronics Subsystem of a high-resolution payload plays very important role in the accomplishment of mission objectives and payload goals. Hence, these electronics subsystems require a special design approach optimised for their needs and the meticulous characterizations of high-resolution space applications. The design of cameras for satellites is different from normal terrestrial commercial cameras, where the former demand exceptional performance, operate under harsh conditions and are designed in response to needs such as experimentation, inception of new technologies, operational requirements, and military demands and changes in world politics also.

Although the term 'System Engineering' dates back to 1940's in the Bell Telephone Laboratories, the major application of the subject gained the eminence during the Second World War. [2] Systems Engineering started to evolve as a branch of engineering during the late 1950's, when the race to get into space and to develop nuclear warhead missiles was considered absolutely essential for national security and reputation, and extreme political pressures were placed on the military services and their civilian contractors to develop, test, and place in operation nuclear missiles and the Earth orbiting satellites. During that tense period of time and

the competitive situation, the military services and their contractors sought the techniques and tools that would help them stand out at system performance (mission success), and project management (technical performance, delivery schedule, and cost control). During that time period and after that, many lessons were learned from difficulties and failures that revolutionised the practices for the development of high technology products, including all disciplines of engineering, manufacturing, procurement, testing, and quality control with the motivation of accomplishment of high system reliability. Today, systems engineering is regarded as an all-embracing discipline, providing the trade-offs and integration between system elements to achieve the best overall product. [3]

For space missions, systems engineering provides the required method and approach to design and develop space missions. Methods, processes and techniques in space systems engineering are designed to ensure that the end result of the space missions conforms to what was expected in the initial conception. The systems engineering principles, with defined scope, are also applicable at system and subsystem levels.

This dissertation puts forward the argument that the system being studied is always a subsystem of a larger system and the systems engineering principles can be applied, with the defined scope, to the subsystem design process as well. The aim of this dissertation is to apply a systems engineering approach for the design of an electronics subsystem of a High-Resolution Electro-Optical payload and to represent a logical integration and test flow using the system engineering guidelines. There are comprehensive resources available which provide insight and practical knowledge of using systems engineering approach and these are readily followed in this dissertation. [4]

The most influential phase of the systems engineering process is the definition of requirements, and entire fields of study have arisen addressing requirements, with their own conferences, journals and methods. This is all to ensure that there is agreement between the designers, those responsible for its construction and eventual deployment, and those paying for it. [5]

It is important that every requirement for a subsystem harmonises with the overall system and it is a function of systems engineering that these requirements are fulfilled. For this, each subsystem has its own set of requirements, derived from the system requirements, and based on these requirements different sets of configuration to be evaluated using the design methodology to develop satisfactory conceptual designs. Through comprehensive and iterative problem-solving process [6], a baseline solution is developed. In order to successfully satisfy all the desired requirements and specifications of a physically realisable subsystem, it is necessary to identify interfaces and develop an adequate, assembly and verification plan during the design

process. The process completes with verification that the need is met, including interfaces, form, fit, and completeness. The application of systems engineering to a project is tailored to the project's needs. [7]

## 1.2 Objectives

This dissertation is centred on the 'high level' design of an Imager Electronics Subsystem. During this design phase, there are general stakeholders' needs (e.g., operational requirements) [6] of the subsystem. While this design stage has many different feasible design solutions, it is important that the designer delve into all the issues that could potentially drive the overall complexities of the subsystem.

The main objective of this work is to propose a systems engineering approach to assist the designer of the subsystem understand the stakeholders' needs, evaluate various design alternatives, and eventually reach a realisable design solution.

The mission objective and goals are given as a reference mission. The insights gained from this study would be used in real mission for high resolution imaging mission in future.

## 1.3 Scope of This Dissertation

The intent of this work is to advance the knowledge and the understanding of the subsystem design according to the systems engineering practices and the solution of design issues in the acquisition of advanced systems. This dissertation does not focus the systems engineering discipline itself as it is not just about the systems engineering principles, rather it is more focused on the application of systems engineering principles and processes that would be used in the designing of a subsystem for a payload.

The 'Imager Electronics Subsystem' is regarded as a subsystem of the 'High-Resolution EO Payload' system. The Imager subsystem consists of group of elements forming the functional chain from the image sensors on the Focal Plane down to the electrical interface, to the Data Handling Unit, Telemetry and Telecommand (TMTC) and power interface of the satellite. This subsystem is responsible for capturing light from telescope, producing image data with the help of image sensors in different spectral bands, performing operations for sending this data to Satellite after aligning, tagging and multiplexing. Architecture and design of the telescope and compression, packetization and mass memory modules are not included in the scope of this dissertation.

The scope of the work includes studying and analysing the payload's scientific needs and requirements to define the Imager Electronics subsystem requirements and to create the functional architecture for the subsystem. The functional architecture is mapped to the physical architecture. Physical decomposition is performed, and the subsystem is broken down (e.g. units and modules). This decomposition leads to development of alternative conceptual designs (i.e. architectures). Based on a trade-off of the concepts, along with determining the interfaces with other subsystems, a preferred architecture is presented as a recommended baseline solution. The Assembly Integration and Verification (AIV) activity is performed to provide an assembly and integration flow and a verification plan with the selected verification and test philosophy. In the establishment of the AIV plan no software is adopted.

It is understood that generally there is a distinction between the mission designers (engineers) and those who have commissioned the mission and desire its end results (client). Construction of a satellite or its subsystems, launch and operations are to be performed by different entities, and therefore documentation and commonly understood processes are critical to successful alignment and outcomes of the various mission phases. [5] But these documents are not in the scope of this dissertation work.

## 1.4 Organisation of Dissertation

This dissertation is structured as follows:

Chapter 2 addresses the needs identification and gives an introduction to the systems engineering process in the light of guidelines from different sources and standards of systems engineering and a system engineering approach that will be followed in this dissertation for the design.

Chapter 3 addresses the requirements definition, functional analysis, allocation and functional architecture of the Imager Electronics Subsystem.

Chapter 4 presents the search for alternatives. This chapter addresses the iterative process carried out and the thought through approach taken into account for viable alternatives that could perform the required functions and fulfil the requirements.

Chapter 5 introduces the baseline design. Preferred alternatives resulting from the selection process becomes the technical baseline for the design project. Once the design baseline has been selected, it becomes the basis for control of the 'iterative refinement' processes, which adds details to the design and eventually yields the end product that has been verified to perform the functions and meet the requirements. This includes identifying system interfaces, both the

internal and the external interface, at the beginning of the design and continually managed throughout the life of the task to reduce unnecessary redesign resulting from incompatible system designs.

Chapter 6 introduces the Assembly, Integration and Verification (AIV) plan. The AIV plan is a plan of activities that are logical and interrelated sequence of events. The main objective is to achieve a high degree of confidence that the subsystem complies with its specified performance parameters. In order to achieve the objective, it emphasises having not only a very good test infrastructure (i.e. facilities) and an adequate AIV plan but also a qualified and efficient test team. This process is devised to provide confidence that the subsystem will achieve its operational objectives, survive in the launch environment, and perform its functions adequately during the designed lifetime. [8]

Chapter 7 presents the conclusion of the overall design and recommendations for future work.

# 2 SYSTEMS ENGINEERING APPROACH

# IN DESIGN

#### 2.1 Introduction

Design of the Imager Electronics Subsystem (IES) is completed following the systems engineering guidelines. In a broad perspective, systems engineering is about viewing the system holistically to consider every aspect of a program or product in its entirety over the lifecycle encompassing the concept, design synthesis, verification and validation, operation, and disposal at the end-of-life. It ensures the implementation of processes that assure that the needs, goals and objectives of a product are met throughout the lifecycle. To achieve this, many standards have evolved over time that are followed by organisations for their projects. One important aspect in this is that no standard is cast in stone in practicing the systems engineering approach. Although the systems engineering standards of NASA, ESA, INCOSE and others provide a comprehensive set of guidelines, these standards are most often customized to match the organisations' needs in their operations, for their products and services, as well as to fulfil the agreements in a contract [6].

The whole process of systems engineering can be considered to based on two sister processes, i.e. a technical process that is focused on technical efforts to produce the system with required capability and performance, and a management process that is focused on organized technical management efforts to monitor the progress, risk, and effectiveness as well as to manage complexity [9]. The Systems Engineering Process (SEP) presented in this chapter is a customised SEP that describes the technical process of the systems engineering for the achievement of the design of the IES subsystem in fulfilling the objective and goals.

The systems engineering approach, in essence, is a hierarchy of steps that begins with defining a need, advances to a technical baseline and ends with verification that the need has been met. The principles of this hierarchy are presented in Table 2-1:

**Table 2-1**: Principles of systems engineering approach.

| Need                      | Why and what the system is required for?                            |  |  |  |  |  |

|---------------------------|---------------------------------------------------------------------|--|--|--|--|--|

| Functions                 | What functions the system is required to perform?                   |  |  |  |  |  |

| Requirements              | What are the set of requirements (functional requirements,          |  |  |  |  |  |

|                           | performance requirements, derived requirements, interface           |  |  |  |  |  |

|                           | requirements) the system is required to fulfil and under what       |  |  |  |  |  |

|                           | conditions and constraints?                                         |  |  |  |  |  |

| Alternatives              | What different design solutions are available to meet the           |  |  |  |  |  |

|                           | requirements and to perform the functions?                          |  |  |  |  |  |

| Criteria                  | What should be the criteria for selection amongst the alternatives? |  |  |  |  |  |

| <b>Technical Baseline</b> | What is the best suitable or the preferred alternative?             |  |  |  |  |  |

| Verification              | The proof that the preferred alternative performs the functions and |  |  |  |  |  |

|                           | meets the requirements                                              |  |  |  |  |  |

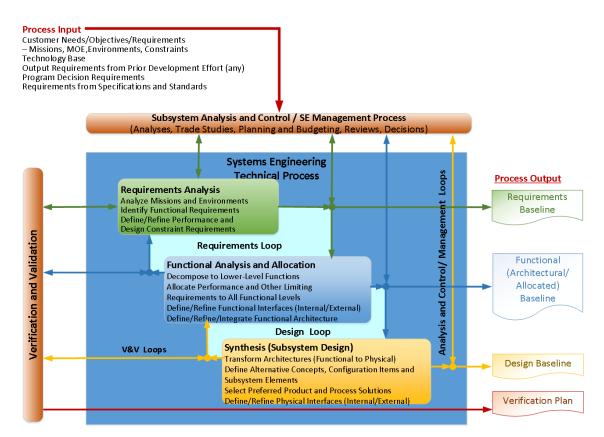

# 2.2 Systems Engineering Process

The primary goal of the systems engineering process is to lead the designer(s) to transform the requirements into system architecture, performance parameters, and design details. The Systems Engineering Process (SEP) presented in Figure 2-1 is applied in this dissertation for the design process of the Imager Electronics Subsystem for a high resolution EO payload of a satellite to provide a desirable and satisfactory outcome. The SEP is an iterative process that provides comprehensive problem solving by defining the problem, determining the effective needs, and then developing a solution though an iterative problem-solving approach [6].

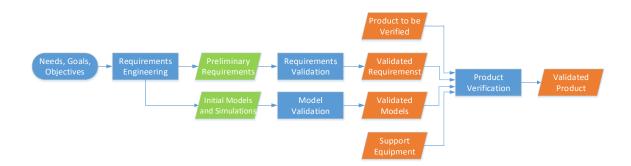

Figure 2-1: Systems Engineering Process [9].

It is the responsibility of management (program and project managers) to implement the SEP when planning a project that in general, takes into account the following factors:

- Project team's mix of experience and skills

- Documentation of the selected engineering methodology (and tools)

- Access to a technical expert about the end product

- Determine action of how the selected methodology is approved [7]

However, the system engineer is responsible for the execution of the SE process.

#### 2.3 Problem Statement

A good system engineering approach requires a clear understanding of all the stakeholders of the problem and the boundaries of the system. [6]The client identifies and determines the problem, and all the stakeholders need to discuss and agree on the understanding of the problem and the solution. The system dynamics, such as the scope, constraints, assumptions and, the interactions with stakeholders are first studied and logically reasoned to provide the system with an effective need. The problem statement for this project dissertation work is identified in Figure 2-2.

As the Remote Sensing industry is growing, more missions are being flown carrying variou payloads for different applications. Beside dedicated missions, the general purpose of RS industry is also growing with users in all kinds of applications. To deliver high quality an very high-resolution images of the Earth to meet specific applications in the remote sensing industry, it is required to a design an electronics subsystem that will constitute a part of the high resolution EO payload of the satellite.

Figure 2-2: Problem Statement for the project dissertation work.

Stakeholder analysis consists of the following components:

- a. Identifying the relevant stakeholders and their roles in the system hierarchy, development and use;

- Examining the stakeholders' documents to analyse their needs and desires with respect to the problem; and

- c. Engaging in bidirectional communications about the requirements. [6]

The stakeholders can be classified as the customer, project manager, chief systems engineer, manufacturer, or designer of another subsystem who shares common interests and responsibilities in the project [10]. The stakeholders can possess different perspectives of the system and can affect or change the system's requirements.

Analysis of stakeholders is carried out to understand the effective needs and wants of the stakeholders with regard to the problem. It is also important that the stakeholders understand and effectively communicate the end user's needs. The system dynamics, such as the boundaries, stakeholder interactions, constraints, assumptions, limitations, and project scope, are first examined and reflected to provide an effective need for the subsystem [6]. The problem statement is then revised to meet the effective need, as shown in Figure 2-3.

To provide a high-quality imaging design for an Imager Electronics Subsystem that i intended to be used as a subsystem of the high resolution multispectral EO payload of th satellite, operating in low Earth orbit for a specified life. The subsystem will be switched Of during the non-eclipse period of the orbit and will image the surface of the Earth and transmithe captured image data to the satellite.

Figure 2-3: The Effective Need and statement for this project.

The subsystem can be considered as a system in its own domain and the systems engineering principles can be applied to the subsystem design process.

# 2.4 Requirements Definition, Analysis and Concept Refinement

The operational needs and requirements must exist for the subsystem or be derived from the systems requirements that are identified by the stakeholders [6].

Prof. Olivier de Weck [11] describes the importance of the process of technical requirements definition that:

- Sets up the basis for mutual understanding between stakeholders and developers on what the product is intended to do.

- Reduces the development effort by:

- motivating the relevant stakeholders to consider rigorously all of the requirements before design starts

- carefully reviewing for oversights, missings, misunderstandings, and inconsistencies early in the development cycle

- Provides a basis for estimating costs and schedules by providing true description of the product to be developed for a realistic estimation of costs and efforts

- Provides a baseline for verification by;

- help developing effective validation and verification plans

- providing a baseline for compliance measurement.

- establishing a baseline for stakeholders for product acceptance

- Facilitates transfer of the product to new users

- Serves as a basis for future-upgrades or modifications of the products.

For requirements definition, requirement analysis is performed with the clearly defined effective need to analyse the subsystem's projected needs, determine what the operational goals are, determine the end user's Concept of Operations (CONOPs), interfaces, and project and design constraints. Depending on the complexity of the project, it becomes more beneficial to include the system engineers of the subsystems to make the requirement definition step effective by defining more realistic requirements and thereby reducing the iterative process of performing requirement analysis.

CONOPs' primary goal is to ensure the operational goals and requirements to all the stakeholders. The CONOPs should therefore be discussed with all the stakeholders in order to clarify the operational scenario envisaged by the CONOPs and to highlight the issues that may arise if certain components fail. The subsystem should be adequately prepared for the scenarios that are highly possible once the subsystem has been set up. These scenarios are developed to help stakeholders understand what possible functions are essential for the operation of the subsystem and allow alternative solutions to be considered later during the design phase. [6]

The requirements analysis converts the needs into baseline system technical or engineering requirements that are related to the characteristics or attributes of the architectural design concept and of the technologies needed for its implementation. The baseline technical requirements are specified at every level, for every component that make up the system/subsystem. These requirements must be traceable and verifiable to confirm the compliance of the design. Completeness and accuracy of all the requirements are deemed necessary to avoid costly (time and money) changes later in the development process [9].

## 2.5 Functional Analysis, Decomposition and Allocation

After discernment of the stakeholders' needs, CONOPs and constraints, a functional analysis is carried out to translate the system's operational objectives into the desired functions. The functional analysis phase allows individual component functions of a concept to be determined and then further developed into the means of performing functions in an operating environment [6].

Functional breakdown is performed to decompose the functions into sub-function forms [6]. The resulting functional architecture of the subsystem serves the following purposes [6]:

- a. Defines all the relevant high-level functions;

- Decomposes the functions and organize them into logical grouping of "high-level" and "derived" functions;

- Organizes the functions into the functional diagrams with the logical ordering or relation amongst the functions;

- d. Performs analysis to understand what is needed to be accomplished to make the concept valid.

When the subsystem's functional hierarchy is developed, the functions are implemented to determine the functional sequencing in the operational scenario [6]. A number of methods, techniques and tools are available to perform functional analysis and allocation. These include [9]:

- Functional Flow Block Diagrams (FFBD)

- Integrated Definition for Function Modelling (IDEF0)

- System Modelling Language (SysML<sup>TM</sup>)

- Unified Modelling Language (UML)

- N<sup>2</sup> Diagrams

- Work Breakdown Structure (WBS)

Many relevant features of the subsystem are derived by decomposing the functions and these insights can be used to generate accurate system requirements. This provides a good framework for the subsystem where it is possible to build other sub-functions. Further decomposition of the functions gives more insight into the plausible ways to solve the problem [6].

#### 2.6 Search for Alternatives

Once the requirements and functions are established, an essential step in the SEP is to search for realizable alternatives that will perform the functions and fulfil the requirements. The SEP encourages the innovation and creativity in this regard. Beside this, the SEP also places great emphasis on delving into the testing and quantitative measures to show that the alternatives, which although they can be very creative and innovative, are viable ways to perform the functions and meet the requirements. The search for alternatives should follow an iterative process with the functions and requirements steps of the SEP involved. [7]

Selection amongst the viable alternatives should be based on predetermined criteria that should, in turn, be based on the objectives, goals and the values identified as the result of the mission analysis.

In most of the cases, the selection process considers cost, time, performance, and risk as more obvious criteria. However, it is also necessary to consider other less noticeable criteria e.g. organizational and stakeholder values, in the selection process as well. [7]

The iteration process should be kept under control and knowing when and where to stop the iterative processes is the key. Some of the indications when this process should be stopped are:

- a well-bounded end product has been identified and found affordable

- decomposition of functions is complete, and no more practical functional allocations exist

- an existing technology can be used to provide the end product

- enough information is available to make the right decisions for the future activities (e.g. continue to the next phase or stop project work)

- the level of complexity has reached a point that one team or organization cannot manage the information or work effectively (for example, discrete components are broken out to be worked on by different smaller teams or to outsource to other organization)

- the organization has reached to a level at which it performs a "make or buy" analysis.

If a make decision is made, the requirements are included in the specifications and drawings. On the other hand, if a buy decision is made, the requirements are included in the contract. [7]

## 2.7 Design Baseline

Preferred alternatives resulting from the selection process become the design baseline that serves as the basis for the control of the iterative processes. Iterative refinement and fine-tuning of this technical baseline adds details and eventually brings in the end product that is verified to perform the functions and fulfil the requirements. [7]

## 2.8 Interface Management

Interface management is an activity in the Systems Engineering Process that ensures the compatibility, proper operation and interoperability between the subsystems that interface with each other. This activity that begins with the concept definition includes identifying system interfaces, defining the interface requirements at each interface boundary, and continues by managing the interfaces during all steps of the SEP. The structure of an interface control is influenced by the system and subsystem Work Breakdown Structure (WBS), contracts and interoperability with other subsystems.

#### 2.9 Validation and Verification

The design validation and verification activities are important for the system designers, the systems engineer, the project and program manager, and the customer [7]. These activities are carried out to ensure that the design fulfils the functions and requirements identified for the system. These efforts confirm the progress towards eventually fulfilling the customer's needs and the results assure that the end product would pass the customer's criteria. These activities not only provide proof that the end product performs as per the specifications, but also an indication of how well the system satisfies its operational requirements [9]. To carry out these activities a plan is formulated that:

- a. Provides a verification and test plan describing the selected tests and procedures;

- b. Serves as an input to the lower level verification.

In order to achieve a satisfactory outcome of the validation and verification process, it is planned early in the task timeline. These verification plans are established to provide satisfactory direction to complete the process for a verifiable design. Eventually, when the verification is completed for each requirement, the individual plan links each requirement to the results or test data that satisfies that requirement. This is a well thought and a very good approach to ensure that all the requirements are met.

# 3 REQUIREMENTS ANALYSIS,

# FUNCTIONAL ANALYSIS AND

# ALLOCATION

In this Chapter, an overview of the system and system requirements is given and the requirement analysis and the functional analysis for the Imager Electronics Subsystem is performed. Requirements are the prime focus because the main purpose of the SEP is to transform the requirements into designs.

The requirements analysis functions as an interface between the internal activities and the inputs fed by the external sources to the SEP by examining, evaluating, and translating the inputs into functional and performance requirements that become the basis for the Functional Analysis and Allocation [9]. The requirements analysis is performed to identify all the necessary and sufficient set of performance requirements, interface requirements, and design constraints for each identified function. Functional Analysis is performed to identify the functions needed for the IES subsystem to fulfil required goals and objectives. This provides an insightful physical realization and clarifies the understanding of what the product is supposed to do for the next step of the SE design process.

The outcome of the requirements and functional analyses establish the basis for the functional and physical architectures for the successful design definition. The requirements analysis and the functional analysis performed in this chapter provide guidance for the conceptual designs to be considered in Chapter 4 and also serve as a check list for the design phase.

# 3.1 System overview

The complete EO Payload system is defined to base on the following subsystems:

- Optical Subsystem (OPS)

- Imager Electronics Subsystem (IES)

- Payload Electronics Subsystem (PLS)

The OPS and the IES are to be designed, developed, manufactured and tested in the same organization (the contractor), and the PLS is to be designed, developed and tested at the customer site. The OPS and IES are to be integrated at the contractor site for testing and performance verification before handing over to the customer. The complete payload is to be assembled, integrated and tested at the customer site.

Each top-level system requirement is analyzed with all the systems engineers (of the system and subsystems). Top level system requirements are presented in section

**Table 3-1**: System Overview, showing the subsystems and their design responsibilities.

| Subsystem | <b>Activities on</b> | <b>Customer Site</b> |          | <b>Activities on Contractor Site</b> |               |          |

|-----------|----------------------|----------------------|----------|--------------------------------------|---------------|----------|

|           | Design and           | Manufacturing        | Testing  | Design and                           | Manufacturing | Testing  |

|           | Development          | and Assembly         |          | Development                          | and Assembly  |          |

| OPS       |                      |                      |          | ✓                                    | ✓             | <b>√</b> |

| IES       |                      |                      |          | ✓                                    | ✓             | ✓        |

| PLS       | ✓                    | ✓                    | <b>√</b> |                                      |               |          |

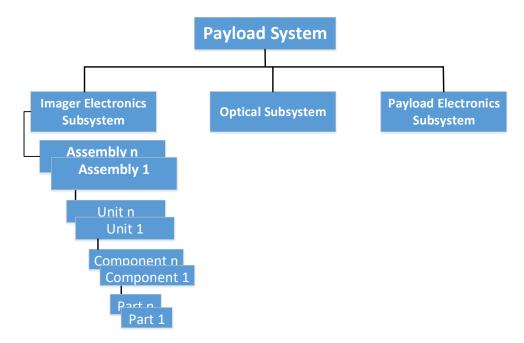

#### 3.1.1 System Hierarchy

It is essential to establish common definitions and understandings among different teams of the project regarding general methods and terminology for effective communication, understanding and productivity [3]. The following definitions are used to define the lower-levels of the EO payload hierarchy.

- System: An integrated set of subsystems that accomplish a defined objective (Payload System).

- **Subsystem**: An integrated set of assemblies, units, components, and parts which performs a clearly separated function (OPS, IES, PLS)

- Assembly: An integrated set of units and/or components that make a defined part of a subsystem

- Unit: An integrated set of components and/or parts that comprise a well-defined portion of an assembly

- Component: a set of multiple parts; a cleanly identified

- **Part**: The lowest level of separately identifiable items (discrete components, resistors, capacitors, inductors, nuts, bolts).

**Figure 3-1**: EO Payload System Hierarchy and level name conventions. The lower-levels of Imager Electronics Subsystem are elaborated in the hierarchy.

## 3.1.2 System Requirements

The Payload has top-level requirements for the design, that include the following:

#### 3.1.2.1 Functional and Performance Requirements

- 1. The payload shall collect EM radiation from the Earth within the following spectral bands:

- Pan 450-800nm

- Blue 440-510nm

- Green 510-580nm

- Red 630-690nm

- NIR 770-900nm

- 2. The Payload level MTF for the Panchromatic band shall be greater than 0.08 as a threshold with a goal of 0.1 at the Nyquist Frequency.

- 3. The Payload level MTF for the Panchromatic band shall be greater than 0.16 as a threshold with a goal of 0.2 at the Nyquist Frequency.

- 4. The total imaging swath width when nadir pointing at any location in the mission orbit, at an orbital height of 600km, shall be continuous and greater than or equal to 10km as a threshold with a goal of 11km.

- 5. The payload shall be able to support image acquisition time of 6 minutes per orbit over the complete design life.

- 6. The GSD for Panchromatic images when Nadir pointing at an orbital height of 600km, shall be 0.5m as a threshold with a goal of 0.4m when measured in along-track and cross-track direction.

- 7. The GSD for Multispectral images when Nadir pointing at an orbital height of 600km, shall be 4 times the GSD of panchromatic images when measured in nadir direction.

- 8. The SNR of the Payload for the Panchromatic band, averaged over a line of pixels, shall be at least 100 for the top-of-atmosphere spectral radiance of 100W/m2.sr.μm

- 9. The SNR of the Payload for the Multispectral bands, averaged over a line of pixel, shall be at least 100 for the top-of-atmosphere spectral radiance of 100W/m2.sr.μm.

#### 3.1.2.2 Physical Requirements

- 10. The Payload shall have a longitudinal (Z-axis) natural frequency greater than 85Hz and less than 105Hz constrained at the Payload Mounting interface.

- 11. The Payload shall have a longitudinal (XY-axis) natural frequency greater than 45Hz and less than 60Hz constrained at the Payload Mounting interface.

- 12. The Payload mass shall not exceed 150kg as a threshold and 120kg as goal.

- 13. The dimensions of the payload shall be less than or equal to 2000x800x800mm3 as threshold and 1800x800x800mm3, as goal.

#### 3.1.2.3 Design Life

14. The Payload shall have a design life of 7yrs comprising 5yrs in the mission orbit at an orbital height of 600km, and 2 years in the ground stage.

#### 3.1.2.4 Reliability

15. The Payload shall be designed to ensure a reliability value better than 0.7 at end of life.

#### 3.1.2.5 Manufacturability

16. All Payload parts shall be manufacturable within the specified tolerances and specifications.

These requirements are discussed among the system engineers, i.e. the chief system engineer of the EO Payload, and the system engineers of Optical Subsystem, Payload Electronics Subsystem and the Imager Electronics Subsystem for clarity, distribution and subsystem level requirements definition.

# 3.2 Subsystem Preliminary requirement definitions

The high-level requirements specification for the IES is based on the notion that the design is seeking a high-resolution, high quality imaging subsystem that:

- Can be used in outer space environment (Low Earth Orbit) as a part of Electro-Optical payload of a satellite;

- Will be able to be designed, developed and tested as a separate subsystem;

- Will be interfaced to the other subsystems to get the required functionality and performance at Payload i.e. system level.

The primary source of the requirements for the IES is the Payload system-level requirements as presented in the preceding section.

## 3.3 Requirements Analysis

Requirements analysis of the IES is performed to:

- Establish what the subsystem must have the capability of accomplishing;

- Identify the various environments in which the subsystem will operate;

- Quantify how well the subsystem must perform in measurable terms;

- Define the constraints which will affect design solutions.

Mainly the requirements, and constraints are derived from customer and stakeholder expectations, higher-level system requirements, project and enterprise constraints, and external constraints [3]. Requirements analysis is performed for the IES as explained in the following sections.

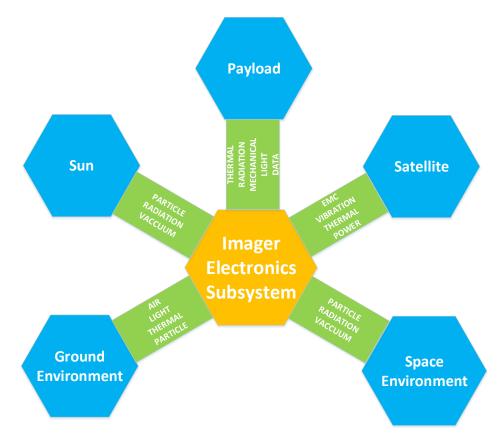

#### 3.3.1 Subsystem Operation and Environment Analysis

A context analysis of the subsystem is performed to identify the environments of the subsystem in which it has to operate. Each environment is carefully analysed and different conditions and interfaces are thought through. This context analysis also highlights the interfaces that the subsystem has different environments throughout its life (on ground, during and after launch).

Analysis has been performed at broader level keeping in view the needs and objectives of the mission. The customer is also provided help to refine the needs, objectives, and MOEs considering the initial and evolving results of the requirements loop [9].

Various difficulties that arise because of conflicting requirements were resolved, for example, the operating time (minimum and maximum) required to accomplish the mission and its implications on the power/ thermal requirements and designs, and alternate technologies as upgrade path for future design. The customer wanted to have this imaging subsystem with full redundancy also on detector level. This customer desirement was analysed thoroughly, but the associated design complexities were analysed to be very high for thermal and electronics design and thus found not feasible with the agreement of the customer.

**Figure 3-2**: Context analysis of the subsystem showing the environments of the subsystem in which it has to operate and potential interaction with each type of environments.

The customer characterized as *mandatory* performance requirements in the form of "thresholds", and *desirable* performance in the form of "goals". Constraints that limit solutions are identified, analysed, and defined in detail, for example, technology limitations options, utilization environments (extremes of hot and cold cases, continuous imaging operation, etc.), or adverse effects in the space environments (e.g. direct sun pointing effects). While this analysis is performed early in the process, it is not a complete and finalized activity [9] and revisited a few times during the process and next phases of design.

For the requirements with "thresholds" and "goals", thresholds are minimum requirements that are needed to perform for the success of the mission and the customer has indicated that the mission may not be performed without these thresholds are met. Goals are beyond-threshold, good-to-have qualities that provide added benefit. It is agreed that achievement of a threshold is of utmost importance, whereas the goals are less critical to achieve, and the customer was made fully aware of any implications (cost, schedule, performance, and risks) involved in their accomplishment before proceeding. For example, the customer mentioned as a goal to have 0.4m GSD that was after the detailed brainstorming and concepts evaluation process (and regular discussions with chief system engineer and OPS system engineer) found that it would only be

possible if super-resolution techniques be used. Although it would have fulfilled the redundancy requirement as stated earlier, this would have made the thermal design extremely challenging and the overall design complexity and AIT effort would increase significantly. All the results were presented to the customer to see if the customer was still willing to accept the associated penalty. For this case, it is agreed to put the goal on hold for implementation at later stages, if possible (e.g. with the availability of suitable detectors for this, and better manufacturing experience to design and manufacture a larger aperture telescope). This was the customer's choice, but it was an obligation of the systems engineering to provide all the information necessary for the customers to make that decision [9].

This is understood that the validity of mission and environmental requirements are to be analyzed and assessed for mission deficiencies throughout the life of the program and are revisited [9] with the customer and the stakeholders whenever they have design alteration or exhibit adverse impact on cost, schedule, performance, or risk [9].

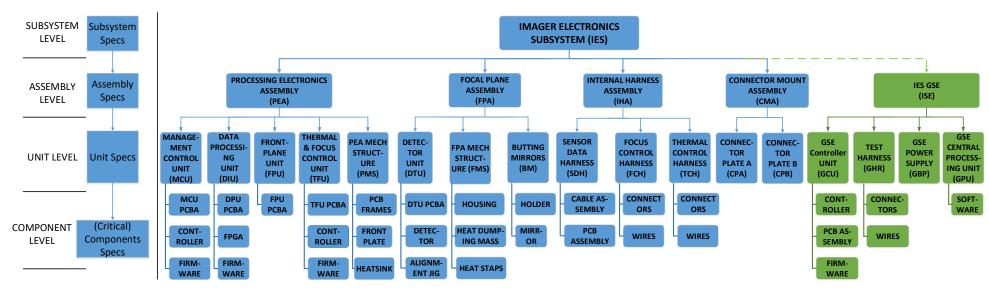

#### 3.3.2 Identify Functional Requirements

The functions (presented in Section 3.4 Functional Analysis and Allocation) that the subsystem needs to perform are identified and the applicable subsystem-level attributes (requirements) are assigned to them. In this step, a subsystem hierarchy is established, and a subsystem-level specification tree developed [9]. Technical control is achieved by decomposing the subsystem level specifications into successively lower-level product specifications resulting in a specification tree in which the specifications for all the products are ultimately traceable to the subsystem specification. For this, the Product-structured WBS for the subsystem is created that has all the derived products of the subsystem (down to the components level for critical components) and that their hierarchical position in the WBS matches the hierarchical position in the build structure of the subsystem. The specification tree is shown in Figure 3-3 with the relationship between the specification tree and the PBS [12].

There are functions that involve more than one requirement. For example, the function to Process Light into raw data is primarily influenced by subsystem allocated power, spectral filtering, thermal ranges, and data interface. Further allocations of each such requirements are therefore necessary. For such requirements a derived set of attributes is assigned to a function because the subsystem-level attribute is not suitable to allocate directly, and it is assured that the assembly of functional requirements (derived or allocated) must equate to the originating specific and overall subsystem requirements. Re-assessment and balancing of functional requirements is necessary when:

a. system or subsystem requirements change; or

b. when analyses indicate that requirements assigned to a specific function might be more advantageously met in another function [9].

The traceability of functions-to-subsystem requirements is also recorded and maintained. The functional requirements become the starting point of the functional analysis and allocation. [9]

#### 3.3.3 Identify Performance Requirements and design constraints

Measurable parameters are established by the means of preliminary level simulations, Excel worksheets and different software (Python 3.7) models to assign performance requirements to the functions/ subfunctions.

## 3.3.4 Identify design constraints

Functional requirements are used to initiate design requirements. The performance requirements, design requirements and constraints become the starting point of the overall subsystem analysis [9].

Figure 3-3: Subsystem Specification Tree.

The specifications tree is the representation of the extent to which the requirements are specified for the hierarchy. This level-of-details and organization of the specification tree is not just achieved in one go only, rather it took many iterations of requirements loop and design loop to reach this level of detailed organization. Level 4 contains the specifications of critical components only, like controllers, FPGAs, PCB etc. the PCBA represents the assembled PCB with parts and components (not just the bare Printed Circuit Board). The specification tree also highlights the importance of testability and verification of the subsystem by including the GSE specifications.

### 3.3.5 Tasks Performed

Following tasks are performed for the requirement analysis activity:

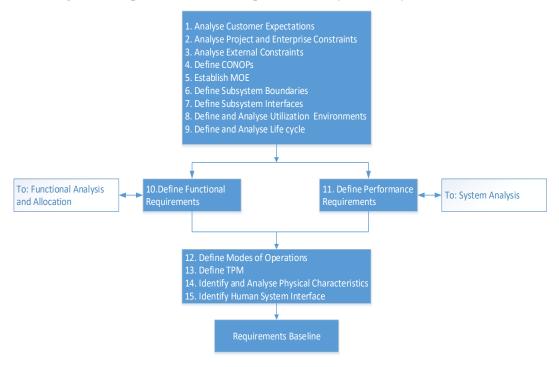

**Figure 3-4**: Tasks performed of the requirements analysis of the IES. These tasks are not performed in the sequence shown, rather there were many jumping and iterations between these tasks.

Table 3-2 explains the tasks performed for the requirements analysis of the IES, with the questions considered for the examination (inquiries) and the outcome (resolution) for each of the for each of the tasks.

**Table 3-2**: Tasks performed for requirements analysis with the inquiry for each task and the resolutions

| Task               | Inquiry                            | Resolution                            |  |  |  |  |

|--------------------|------------------------------------|---------------------------------------|--|--|--|--|

| 1.Analyse          | - What are the customer/           | - Baselined Expectations:             |  |  |  |  |

| Customer/          | stakeholders expectations?         | - The subsystem when integrated with  |  |  |  |  |

| Stakeholders       | - What are the reasons behind      | the Telescope as a part of Payload    |  |  |  |  |

| Expectation        | the system development?            | shall be able to provide the GSD of   |  |  |  |  |

|                    | - Who are the end-users and        | better than or equal to 0.5m          |  |  |  |  |

|                    | their intension to use the         | -The subsystem shall be able to image |  |  |  |  |

|                    | product?                           | continuously for up to 300 seconds.   |  |  |  |  |

|                    | - What is their level of expertise | - High performance with 5 years in-   |  |  |  |  |

|                    | of the customer/ user?             | orbit life                            |  |  |  |  |

|                    |                                    | - All electronic parts shall be COTS  |  |  |  |  |