# THE DESIGN AND IMPLEMENTATION OF A WIDEBAND DIGITAL RADIO RECEIVER

Dissertation for the Degree of Master of Science in Engineering

Clifford Leonard van Dyk

A dissertation submitted to the Department of Electrical Engineering, University of Cape Town, in fulfilment of the requirements for the degree of Master of Science in Engineering

Cape Town, 28 March 2002

The copyright of this thesis vests in the author. No quotation from it or information derived from it is to be published without full acknowledgement of the source. The thesis is to be used for private study or non-commercial research purposes only.

Published by the University of Cape Town (UCT) in terms of the non-exclusive license granted to UCT by the author.

# **Declaration**

I declare that this dissertation is my own, unaided work. It is being submitted for the degree of Master of Science in Engineering at the University of Cape Town. It has not been submitted before for any degree or examination at any other university.

Signature of Author .....

Cape Town 28 March 2002

# **Abstract**

Historically radio has been implemented using largely analogue circuitry. Improvements in mixed signal and digital signal processing technology are rapidly leading towards a largely digital approach, with down-conversion and filtering moving to the digital signal processing domain. Advantages of this technology include increased performance and functionality, as well as reduced cost.

Wideband receivers place the heaviest demands on both mixed signal and digital signal processing technology, requiring high spurious free dynamic range (SFDR) and signal processing bandwidths. This dissertation investigates the extent to which current digital technology is able to meet these demands and compete with the proven architectures of analogue receivers. A scalable generalised digital radio receiver capable of operating in the HF and VHF bands was designed, implemented and tested, yielding instantaneous bandwidths in excess of 10 MHz with a spurious-free dynamic range exceeding 80 decibels below carrier (dBc).

The results achieved reflect favourably on the digital receiver architecture. While the necessity for minimal analogue circuitry will possibly always exist, digital radio architectures are currently able to compete with analogue counterparts. The digital receiver is simple to manufacture, based on the use of largely commercial off-the-shelf (COTS) components, and exhibits extreme flexibility and high performance when compared with comparably priced analogue receivers.

# Acknowledgements

I wish to acknowledge and thank Peralex Electronics (Pty) Ltd. for the opportunity of presenting this project as a dissertation. In particular, the contributions of Glen Thiele, who has offered unparalleled guidance, support and expertise are appreciated. I would also like to thank Per Karlsen and Alex Bassios for their support and encouragement.

I would like to thank Mark Cammidge for his assistance in proof-reading this dissertation.

Finally, I wish to thank my supervisor, Associate Professor Michael Inggs, for his guidance and support.

# **Contents**

| De | eclara  | tion                                                        | i    |

|----|---------|-------------------------------------------------------------|------|

| Al | bstrac  | t                                                           | ii   |

| A  | know    | ledgements                                                  | iii  |

| Co | ontent  | S                                                           | iv   |

| Li | st of I | figures                                                     | viii |

| Li | st of 7 | <b>Tables</b>                                               | хi   |

| Li | st of A | Abbreviations                                               | xii  |

| Ne | omeno   | elature                                                     | xiv  |

| 1  | Intro   | oduction                                                    | 1    |

|    | 1.1     | Background                                                  | 2    |

|    | 1.2     | Scope                                                       | 2    |

|    | 1.3     | System Specification                                        | 4    |

|    | 1.4     | System Architecture                                         | 5    |

|    | 1.5     | Related Work                                                | 6    |

|    | 1.6     | Document Overview                                           | 7    |

| 2  | Wid     | eband Signal Digitisation                                   | 8    |

|    | 2.1     | Dynamic Range Restrictions in Wideband Digitisation         | 8    |

|    | 2.2     | Bandpass Sampling Theory                                    | 11   |

|    |         | 2.2.1 Nyquist's Criterion                                   | 11   |

|    |         | 2.2.2 Bandpass Sampling                                     | 11   |

|    |         | 2.2.3 Spectral Inversion in Bandpass Sampling               | 14   |

|    |         | 2.2.4 Applying Bandpass Sampling to Wideband Reception      | 14   |

|    |         | 2.2.5 Quadrature Sampling and Complex Signal Representation | 15   |

|   | 2.3 | Sources of Error in Wideband Digitisation                           | 16 |

|---|-----|---------------------------------------------------------------------|----|

|   |     | 2.3.1 Quantisation Error                                            | 17 |

|   |     | 2.3.2 Static Errors in the A-D Transfer Function                    | 17 |

|   |     | 2.3.3 Sampling Jitter                                               | 19 |

|   |     | 2.3.4 Relative Noise Contributions in Wideband Digitisation         | 21 |

|   | 2.4 | Oversampling                                                        | 22 |

|   |     | 2.4.1 Relaxation of Anti-aliasing Filter Requirements               | 23 |

|   |     | 2.4.2 Signal-to-Noise Ratio Improvement Through Oversampling.       | 23 |

|   |     | 2.4.3 Spurious Harmonic Placement                                   | 24 |

|   | 2.5 | Signal Dithering                                                    | 24 |

|   |     | 2.5.1 Subtractive and Non-subtractive Dithering Techniques          | 25 |

|   |     | 2.5.2 Small- and Large-scale Dithering                              | 27 |

|   | 2.6 | A-D Converter Input Level Matching                                  | 29 |

|   |     | 2.6.1 Characteristics of an Analogue Receiver Chain                 | 29 |

|   |     | 2.6.2 Combined Analogue and A-D Converter Noise Figure              | 31 |

|   |     | 2.6.3 Optimal Analogue and A-D Converter Interfacing                | 31 |

|   | 2.7 | Selection of a Wideband A-D Converter                               | 32 |

|   |     | 2.7.1 A-D Converter Architectures                                   | 33 |

|   |     | 2.7.2 Survey of Commercially Available Wideband A-D Converters      | 33 |

|   |     | 2.7.3 Comparison of AD6644 and CLC5958                              | 34 |

| _ |     |                                                                     |    |

| 3 | _   | tal Down-conversion and Multirate Signal Processing                 | 37 |

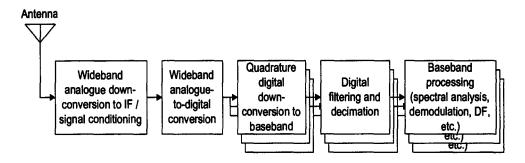

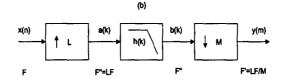

|   | 3.1 | A Generalised IF Sampling Receiver Architecture                     | 38 |

|   | 3.2 | Spectral Translation of IFs to Baseband                             | 38 |

|   |     | 3.2.1 Spectral translation through quadrature digital mixing        | 39 |

|   |     | 3.2.2 Hardware-Efficient Frequency Translation                      | 40 |

|   |     | 3.2.3 Performance Advantages of Digital Spectral Translation        | 40 |

|   | 3.3 | Digital Resampling and Multirate Signal Processing                  | 41 |

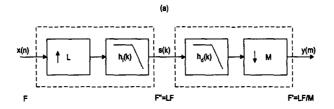

|   |     | 3.3.1 Decimation by Integer Factors                                 | 41 |

|   |     | 3.3.2 Interpolation by Integer Factors                              | 42 |

|   |     | 3.3.3 Resampling by Non-Integer Factors                             | 43 |

|   |     | 3.3.4 Efficient Architectures for Integer Decimation                | 44 |

|   | 2.4 | 3.3.5 Enhanced Signal-to-Noise Ratio through Decimation Filtering   | 48 |

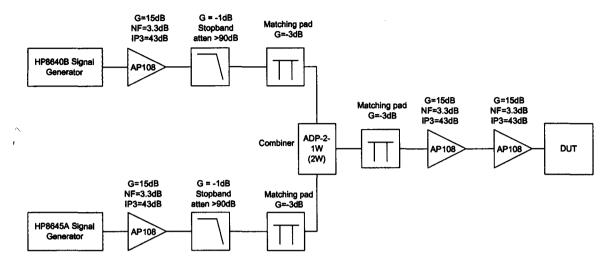

|   | 3.4 | Enhanced Signal-to-Noise Ratio using the Discrete Fourier Transform | 48 |

| 4 | Wid | eband Digital Receiver Architecture and Design                      | 50 |

|   | 4.1 | Overview of System Architecture                                     | 50 |

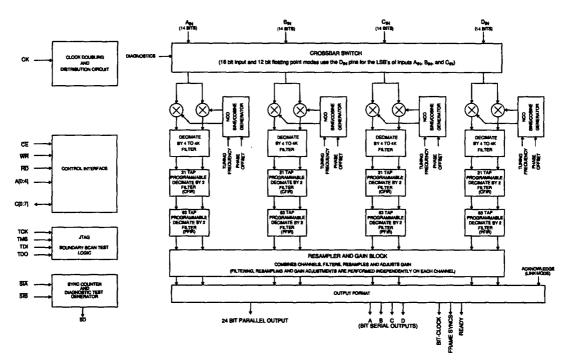

|   | 4.2 | Digital Receiver Channel Architecture                               | 51 |

|   |     | 4.2.1 A Review of the Digital Receiver Requirements                 | 52 |

|   |     | 4.2.2 Commercially Available Digital Down-conversion Hardware.      | 53 |

|   |     | 4.2.3 A Scalable Digital Receiver based on COTS components          | 55 |

|   |     |                                                                     |    |

|   |     | v                                                                   |    |

|   |     | Y                                                                   |    |

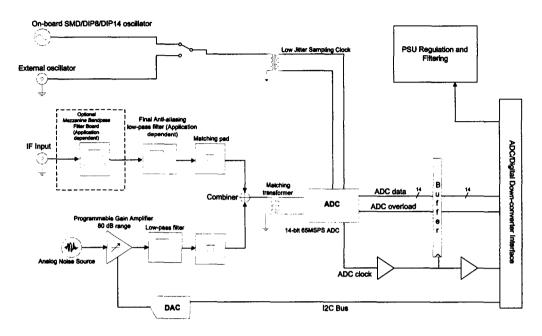

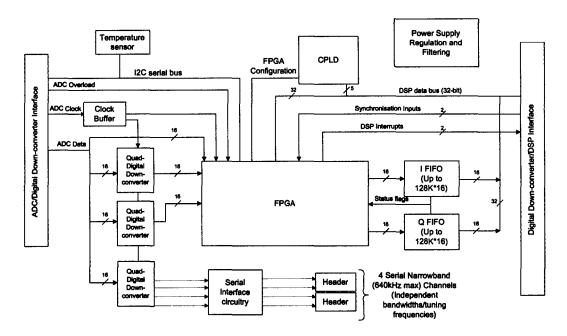

|     |        | 4.2.4           | A Description of the ADC-DDC Board Architecture                | 59  |

|-----|--------|-----------------|----------------------------------------------------------------|-----|

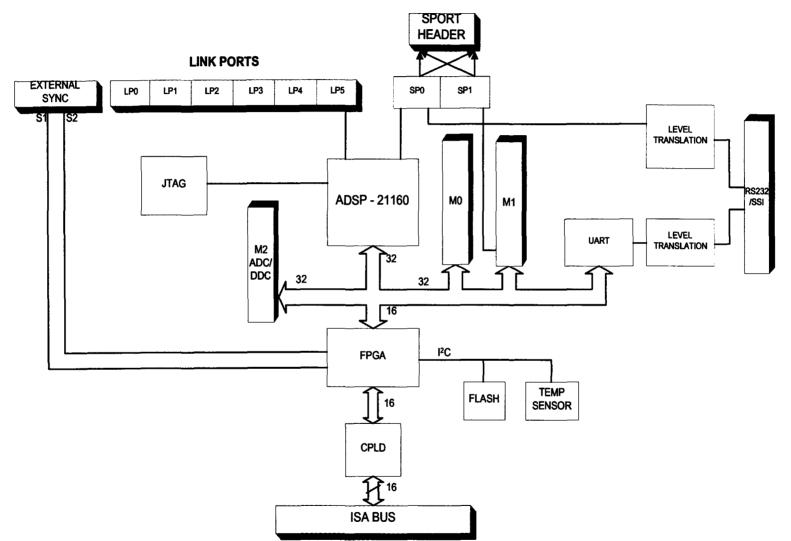

|     |        | 4.2.5           | A Description of the ISA DSP Board Architecture                | 64  |

| 5   | Digi   | tal Reco        | eiver Implementation                                           | 67  |

| •   | 5.1    |                 | onverter Input Level Matching                                  | 67  |

|     | 5.2    |                 | Converter Input Signal Dithering                               | 68  |

|     | 5.3    |                 | ion of a Sampling Oscillator                                   | 69  |

|     | 5.4    |                 | gue Power Supply Filtering                                     | 70  |

|     | 5.5    |                 | ding                                                           | 71  |

|     | 5.6    |                 | hielding                                                       | 71  |

|     | 5.7    | GC401           | 16 Decimating Filter Coefficients                              | 72  |

|     | 5.8    | Proble          | ms Encountered during Receiver Design                          | 73  |

|     |        | 5.8.1           | Insufficient EMI Suppression                                   | 73  |

|     |        | 5.8.2           | Problems due to Faulty Silicon                                 | 74  |

| 6   | Perf   | ormano          | ee Measurements                                                | 75  |

|     | 6.1    |                 | ical Testing of A-D Converter and Analogue Front-End Circuitry | 75  |

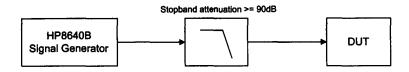

|     |        | 6.1.1           | Non-harmonic Spurious Free Dynamic Range                       | 75  |

|     |        | 6.1.2           | Harmonic Spurious Free Dynamic Range                           | 76  |

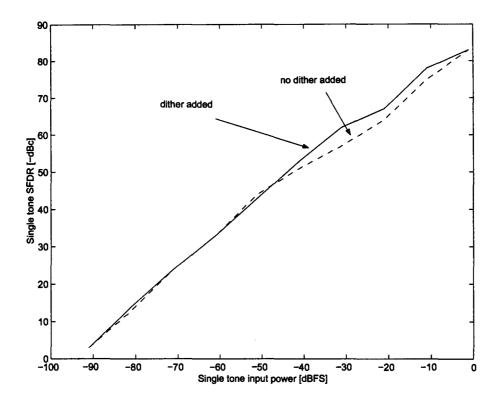

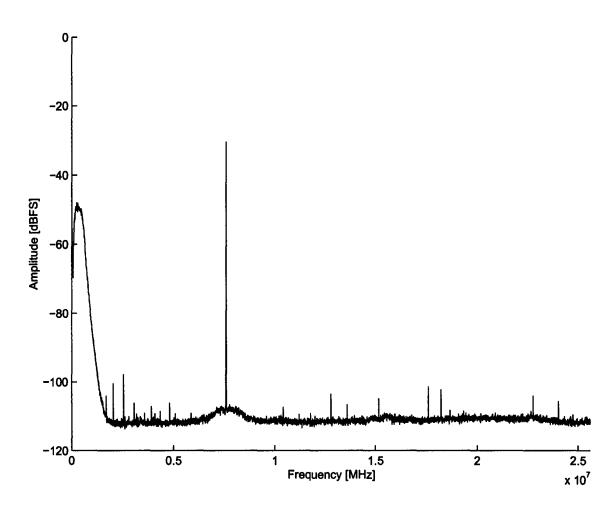

|     |        | 6.1.3           | Effect of Band-limited Dither Noise on A-D Converter Linearity | 77  |

|     | 6.2    | Empir           | ical Testing of the Digital Receiver at 5 MHz IF               | 77  |

|     |        | 6.2.1           | Non-harmonic Spurious-free Dynamic Range                       | 78  |

|     |        | 6.2.2           | Harmonic Spurious-free Dynamic Range                           | 78  |

|     |        | 6.2.3           | Two-tone Third-order Intermodulation Distortion Measurement    | 78  |

|     | 6.3    | Empir           | ical Testing of the Digital Receiver at 12.8 MHz IF            | 80  |

|     |        | 6.3.1           | Non-Harmonic Spurious-free Dynamic Range                       | 80  |

|     |        | 6.3.2           | Harmonic Spurious-free Dynamic Range                           | 81  |

|     |        | 6.3.3           | Two-tone Third-order Intermodulation Distortion Measurement    | 82  |

| 7   | Con    | clusion         |                                                                | 84  |

| Bil | bliogı | raphy           |                                                                | 87  |

| A   | Deri   | vations         | •                                                              | 90  |

|     | A.1    | Signal          | -to-Noise Ratio resulting from Encode Jitter                   | 90  |

| В   | GC4    | <b>1016 W</b> i | ideband Decimation Filtering Frequency Response                | 92  |

| C   | Digi   | tal Rec         | eiver Performance Plots                                        | 99  |

|     | C.1    | AD66            | 44 A-D Converter Output Plots                                  | 99  |

|     | C.2    |                 | and 5 MHz IF 800 kHz Bandwidth Receiver Output Plots           | 99  |

|     | C3     | Wideh           | and 12 8 MHz IF 10 MHz Randwidth Receiver Output Plots         | 100 |

D System and Board Physical Construction and Layout

114

# **List of Figures**

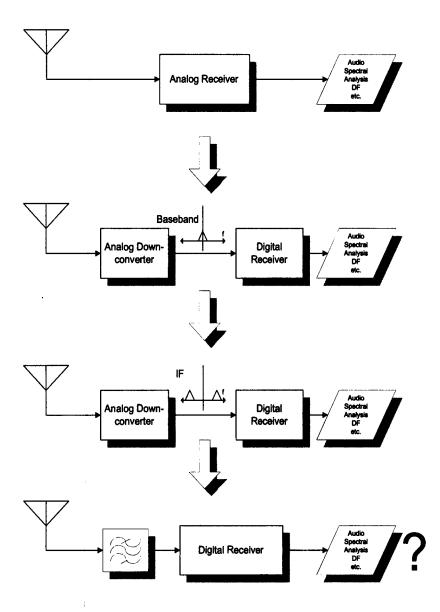

| 1.1 | The progression of receivers from analogue to digital                      | 3  |

|-----|----------------------------------------------------------------------------|----|

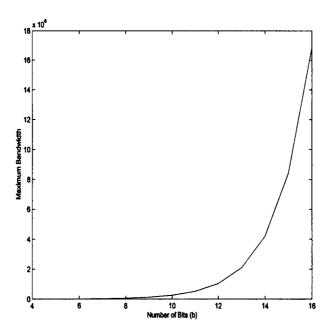

| 2.1 | An example plot of maximum bandwidth versus number of bits                 | 10 |

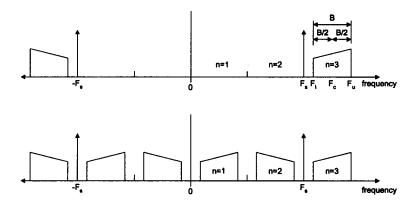

| 2.2 | A typical bandpass sampling scheme                                         | 12 |

| 2.3 | The allowed regions for bandpass sampling                                  | 13 |

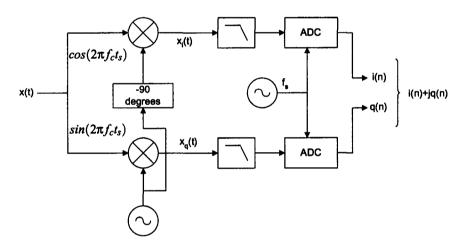

| 2.4 | Illustration of quadrature sampling scheme                                 | 15 |

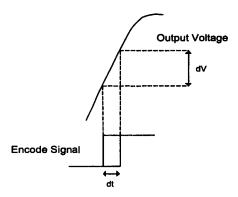

| 2.5 | The voltage error resulting from encode signal jitter                      | 20 |

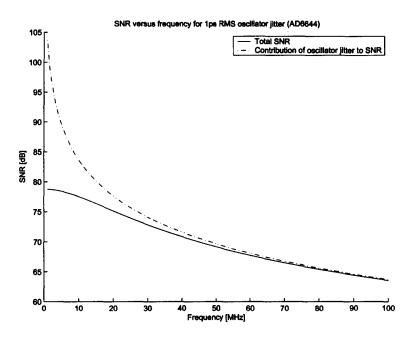

| 2.6 | Signal-to-noise ratio versus analogue input frequency for the AD6644.      | 22 |

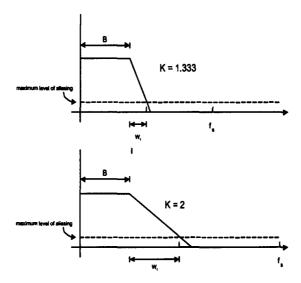

| 2.7 | Anti-aliasing filter transition width requirements                         | 23 |

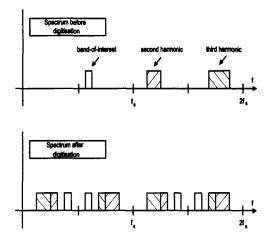

| 2.8 | Band placement such that harmonics do not fall in-band after digitisation. | 24 |

| 2.9 | Subtractive and non-subtractive dithering schemes                          | 26 |

| 3.1 | A generalised IF-sampling digital receiver                                 | 38 |

| 3.2 | The quadrature digital mixing process                                      | 39 |

| 3.3 | Decimation by an integer factor M=4                                        | 42 |

| 3.4 | Interpolation by an integer factor M=4                                     | 44 |

| 3.5 | Resampling by a rational factor $\frac{L}{M}$                              | 45 |

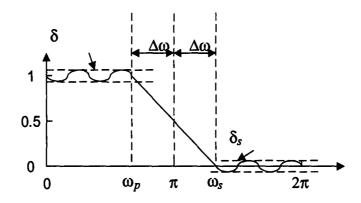

| 3.6 | Halfband filter frequency response                                         | 45 |

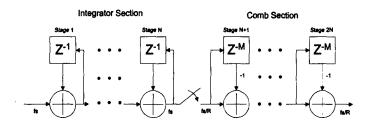

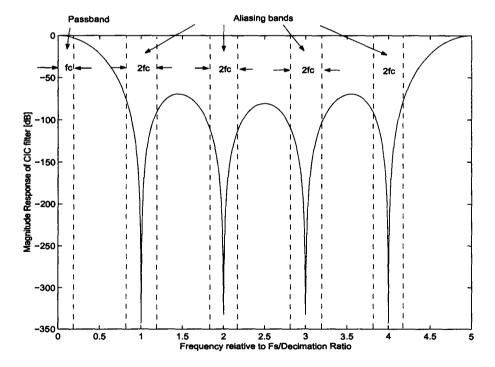

| 3.7 | Structure of a CIC decimating filter                                       | 46 |

| 3.8 | Structure of a CIC decimating filter                                       | 47 |

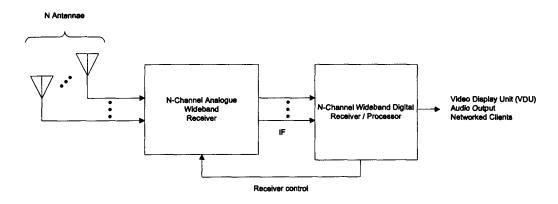

| 4.1 | Typical wideband surveillance receiver system configuration                     | 50  |

|-----|---------------------------------------------------------------------------------|-----|

| 4.2 | Block diagram of the GC4016 quad digital down-converter                         | 55  |

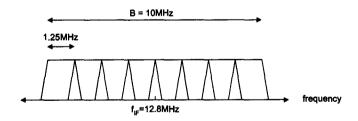

| 4.3 | Adjacent narrowband channels used to form a wideband output                     | 58  |

| 4.4 | Block diagram of the A-D Converter board                                        | 60  |

| 4.5 | Block diagram of the digital down-converter board                               | 61  |

| 4.6 | Block diagram of the general purpose ISA-based DSP card                         | 66  |

| 6.1 | Test setup for harmonic spurious performance measurement                        | 77  |

| 6.2 | Intermodulation distortion test setup                                           | 80  |

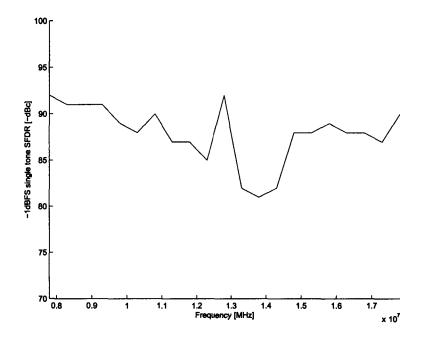

| 6.3 | Single-tone harmonic spurious-free dynamic range versus frequency               | 81  |

| 6.4 | Single-tone harmonic spurious-free dynamic range versus input amplitude.        | 82  |

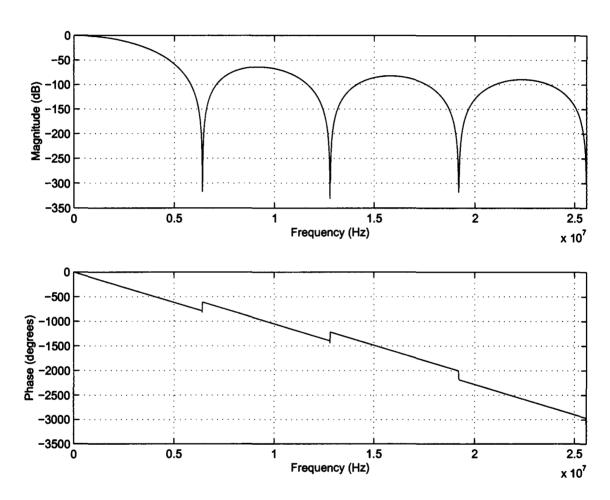

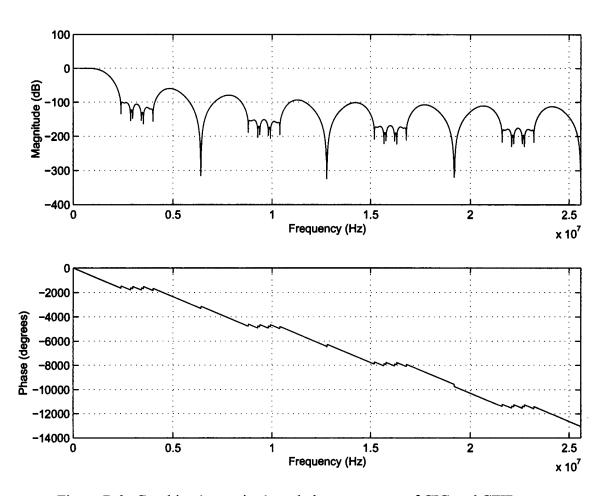

| B.1 | Magnitude and phase response of 5th order CIC decimation filter (decimate by 8) | 93  |

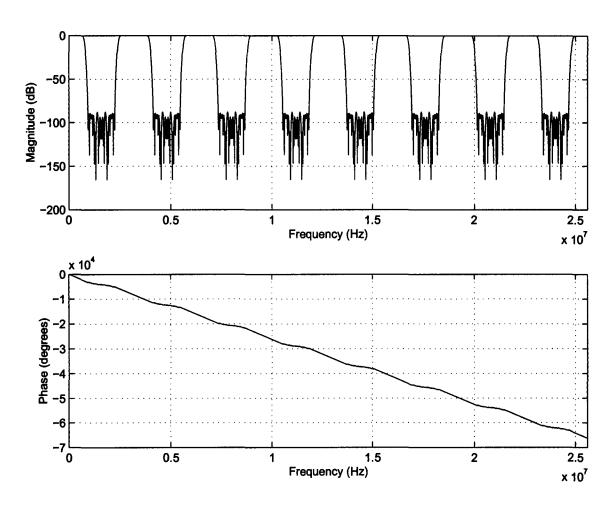

| B.2 | Magnitude and phase response of 21-tap CFIR FIR filter                          | 94  |

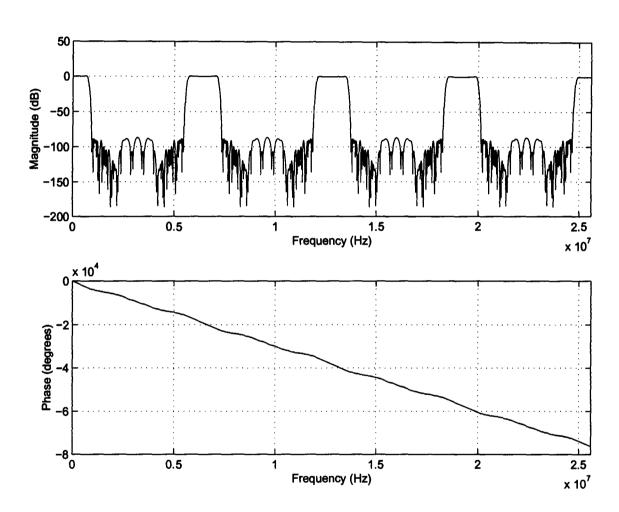

| B.3 | Combined magnitude and phase response of CIC and CFIR                           | 95  |

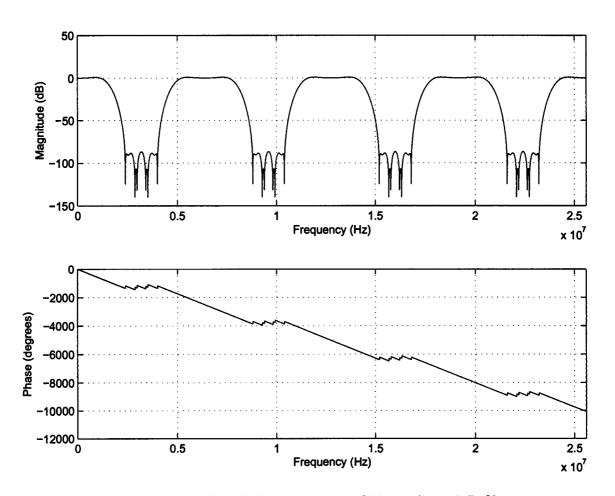

| B.4 | Magnitude and phase response of 63-tap PFIR FIR filter                          | 96  |

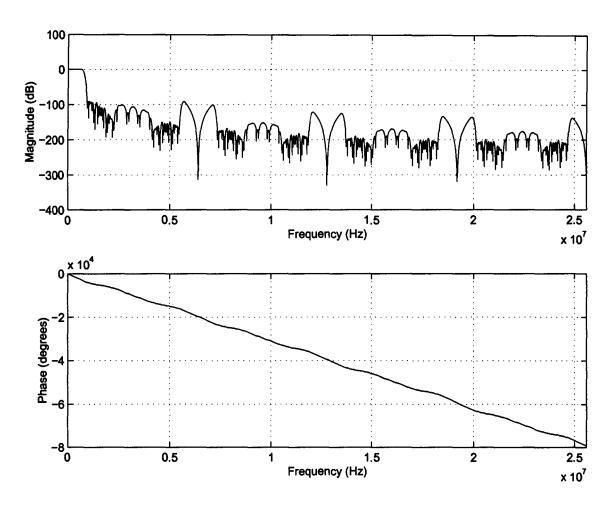

| B.5 | Combined magnitude and phase response of CFIR and PFIR filters                  | 97  |

| B.6 | Combined magnitude and phase response of CIC, CFIR and PFIR filters.            | 98  |

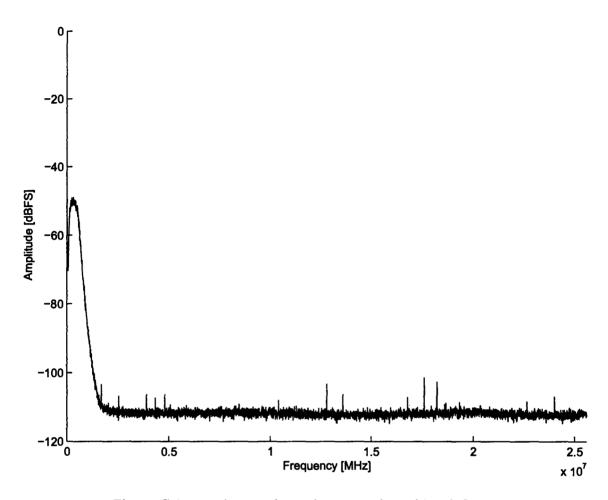

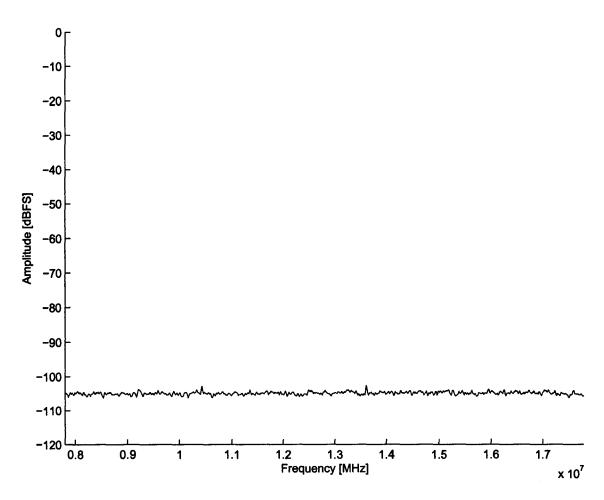

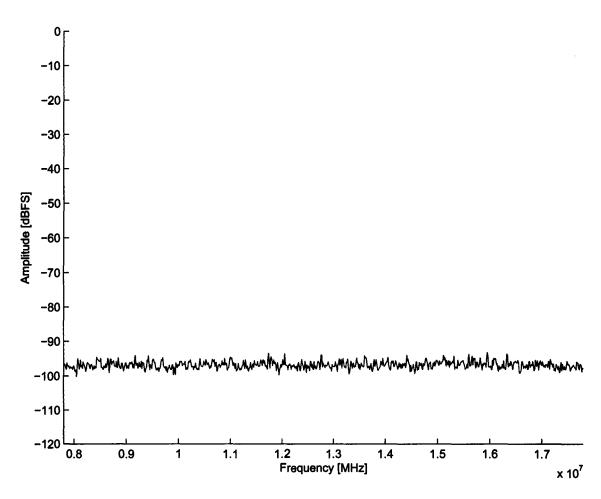

| C.1 | Receiver analogue input terminated in 50 $\Omega$                               | 100 |

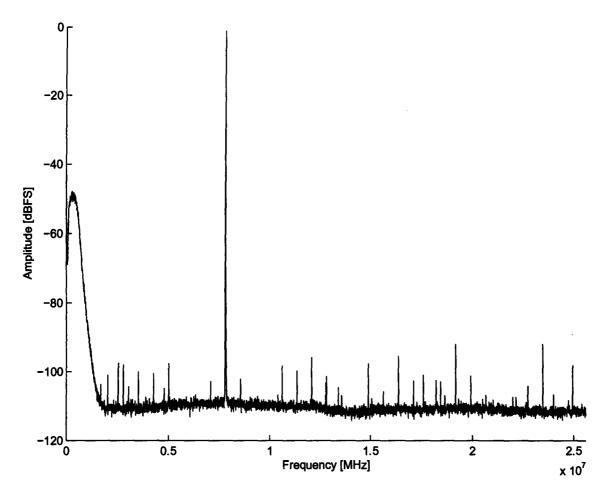

| C.2 | 7.6 MHz, -1 dBFS tone at receiver analogue input                                | 101 |

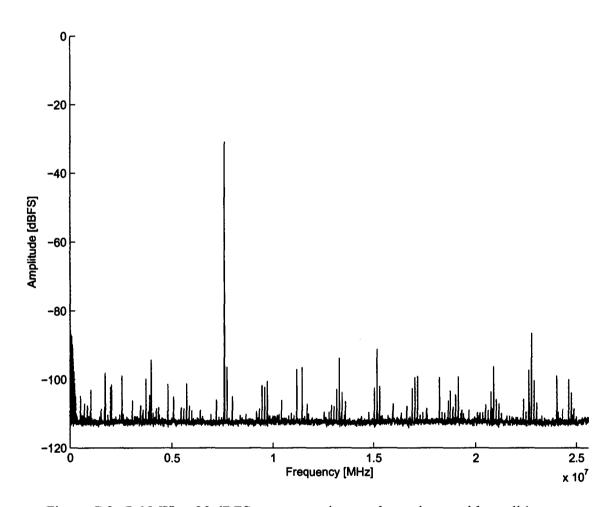

| C.3 | 7.6 MHz, -30 dBFS tone at receiver analogue input with no dither                | 102 |

| C.4 | 7.6 MHz, -30 dBFS tone at receiver analogue input with dither                   | 103 |

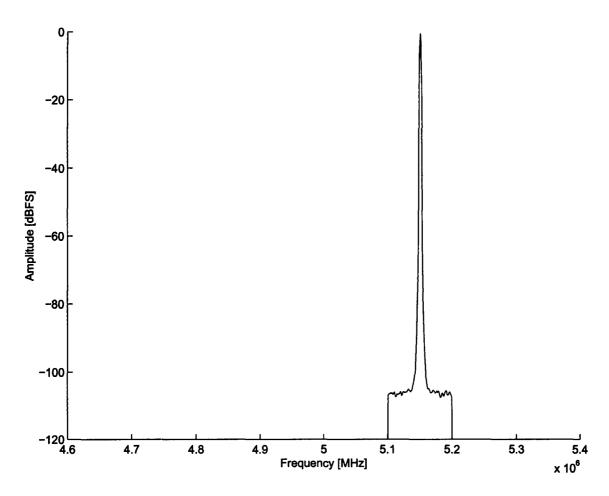

| C.5 | Single tone at 5.15 MHz of amplitude -1 dBFS (averaged)                         | 104 |

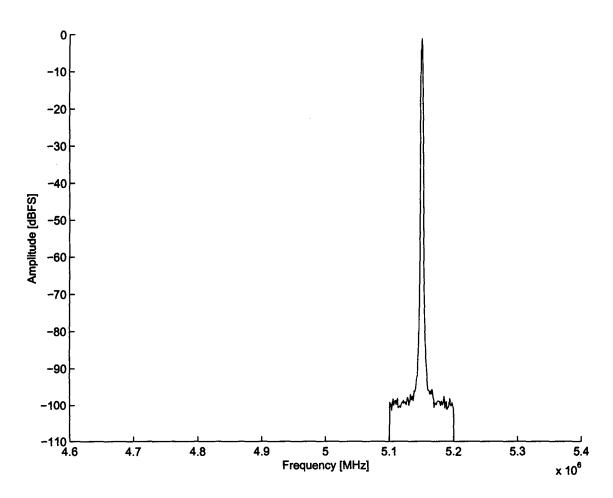

| C.6 | Single tone at 5.15 MHz of amplitude -1 dBFS (peak hold)                        | 105 |

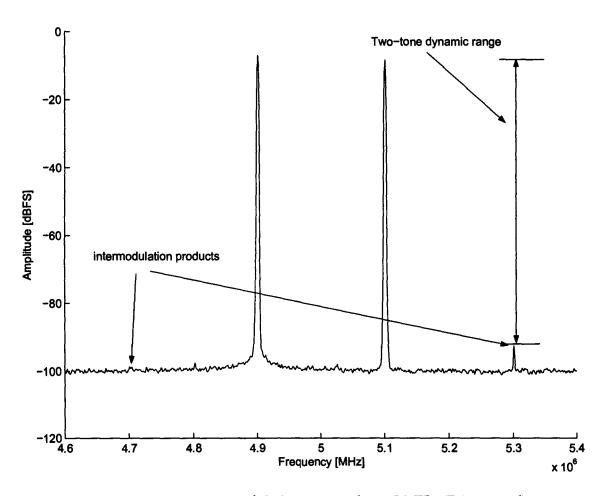

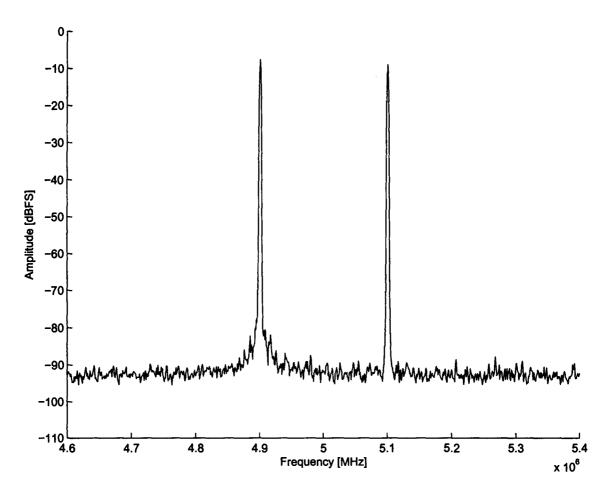

| C.7 | Two-tone intermodulation test results at 5 MHz IF (averaged)                    | 106 |

| C.8          | Two-tone intermodulation test results at 5 MHz IF(peak hold)                                     | 107 |

|--------------|--------------------------------------------------------------------------------------------------|-----|

| C.9          | Receiver input terminated in 50 $\Omega$ (averaged)                                              | 108 |

| C.10         | Receiver input terminated in 50 $\Omega$ (peak hold).<br>$\   \ldots   \ldots   \ldots   \ldots$ | 109 |

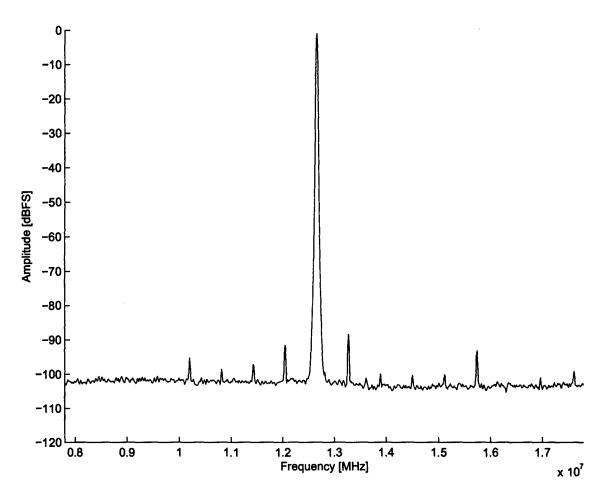

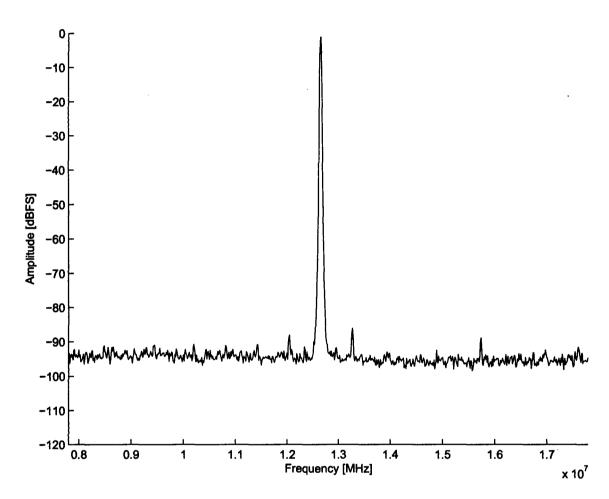

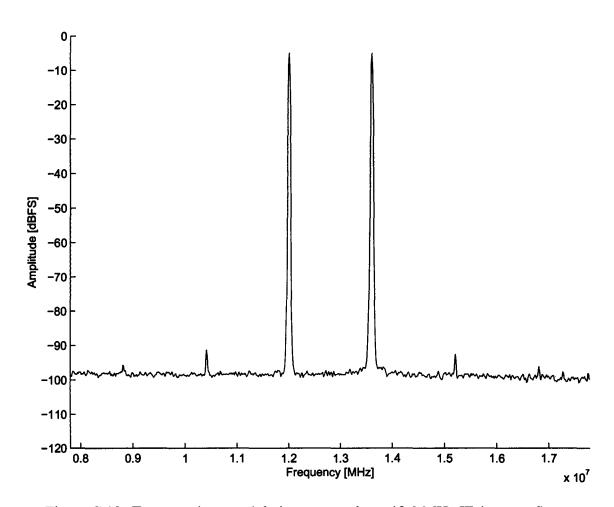

| <b>C</b> .11 | Single tone at 12.64 MHz, -1 dBFS (averaged)                                                     | 110 |

| C.12         | Single tone at 12.64 MHz, -1 dBFS (peak hold)                                                    | 111 |

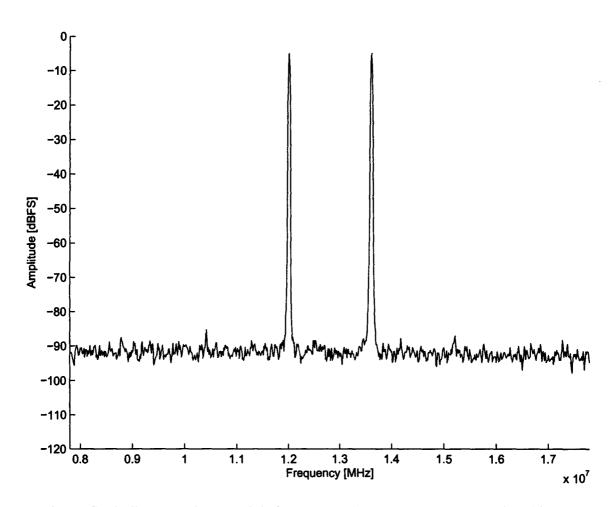

| C.13         | Two-tone intermodulation test results at 12.8 MHz IF (averaged)                                  | 112 |

| C.14         | Two-tone intermodulation test results at 12.8 MHz IF (peak hold)                                 | 113 |

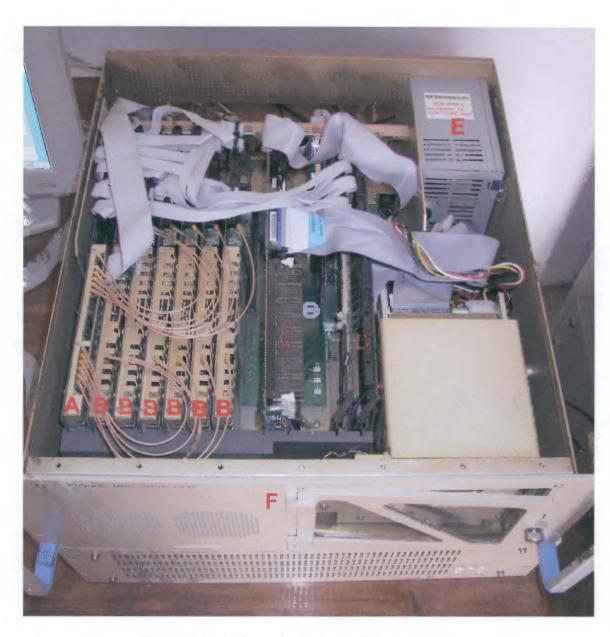

| D.1          | 6-Antenna wideband receiver incorporating the digital receiver                                   | 114 |

| D.2          | 6-Channel wideband digital receiver                                                              | 116 |

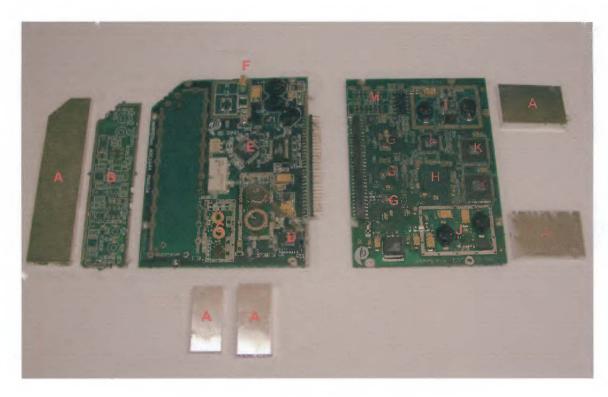

| D.3          | Physical layout of the digital receiver adapter card and mezzanine module                        | 117 |

|              |                                                                                                  |     |

| D.4          | Physical layout of the ADC and DDC boards                                                        | 118 |

| D.5          | Assembled digital receiver card (no shielding cover)                                             | 118 |

# **List of Tables**

| 1.1 | Wideband receiver operating mode requirements                     | 5  |

|-----|-------------------------------------------------------------------|----|

| 2.1 | Parameters used in the calculation of maximum sampled bandwidth . | 10 |

| 2.2 | A comparison of the AD6644 and CLC5958 A-D converters             | 36 |

| 4.1 | Commercially available ASICs for digital down-conversion          | 54 |

| 5.1 | Parameters used in the calculation of oscillator jitter           | 70 |

| D.1 | Key for figure D.1                                                | 15 |

| D.2 | Key for figure D.2                                                | 15 |

| D.3 | Key for figure D.3                                                | 15 |

| D.4 | Key for figure D.4                                                | 17 |

# List of Abbreviations

ADC— Analogue-to-digital converter

AGC— Automatic gain control

ASIC — Application-specific integrated circuit

cf— Characteristic function

CIC — Cascaded integrator-comb

COTS—Commercial off-the-shelf

CPLD— Complex programmable logic device

DAC — Digital-to-analogue converter

dBc- Decibels relative to carrier

dBFS-Decibels relative to full-scale

**DDC**— Digital down-converter

DDS - Digital signal synthesis

**DF**— Direction finding

**DFT**— Discrete Fourier Transform

**DMA**— Direct memory access

**DNL**—Differential non-linearity

**DUT**— Device under test

FFT—Fast Fourier Transform

FIR— Finite impulse response

FPGA— Field-programmable gate array

FSR— Full-scale range

IF—Intermediate frequency

IM3— Third-order intermodulation products

INL—Integral non-linearity

IP3— Third-order intercept point

ISA— Industrial Standard Architecture

LO—Local oscillator

LSB— Least significant bit

MDS— Minimum discernable signal

MGC— Manual gain control

MSB— Most significant bit

NCO— Numerically controlled oscillator

NSD- Non-subtractive dither

**pdf**— Probability density function

**RPDF**— Rectangular probability density function

SBC—Single board computer

**SD**— Subtractive dither

SDR-Software defined radio

SIMD—Single instruction multiple data

SINAD— Signal-to-noise-and-distortion

SFDR—Spurious-free dynamic range

SNR—Signal-to-noise ratio

SSB—Single side band

TDOA— Time difference of arrival

# **Nomenclature**

**Band Occupancy**— The band occupancy is usually expressed as a percentage and is defined as the ratio of the number of signals present within a particular band-of-interest to the number of available channels allocated to the band.

Noise Factor— The noise factor (NF) provides a measure of the contribution of inherent (internal) device noise on total system noise. It is defined as the ratio of the signal-to-noise ratio (SNR) measured at the device output and the SNR ratio measured at the device input under normal operating conditions. By convention, it is expressed in a dB scale.

Selectivity—The property of a receiver that allows it to distinguish between signals at different frequencies.

Sensitivity—For sufficiently high levels of receiver gain, the weakest signal power that may be acceptably processed is limited by noise. This signal level is referred to as the sensitivity of the system and varies with external noise level.

**Spurious Free Dynamic Range (SFDR)**—The ratio of the peak RMS signal amplitude to the RMS value of the peak spurious spectral component. This may or may not be a harmonic. It is usually expressed in decibels relative to carrier (dBc) or decibels relative to full scale (dBFS), and it is therefore important to pay attention to the units of measurement.

# Chapter 1

# Introduction

Digital radio implementations are increasingly being adopted. Analogue circuitry is rapidly being replaced by digital signal processing (DSP), analogue-to-digital (A-D) and digital-to-analogue (D-A) conversion. Advantages of this technology include increased performance and functionality, and reduced cost. Dedicated analogue circuitry may be replaced by flexible, robust DSP application-specific integrated circuits (ASICs) and software.

Analogue-to-digital conversion technology currently limits the instantaneous energy that may be received, as a result of limited A-D converter dynamic range. If the received energy is widely distributed over the received spectrum (usually a valid assumption given the typical energy spread in the bands of interest), the bandwidth that may be received at any given level of available dynamic range is limited. Continuous technological advances move closer to the ideal of connecting an A-D converter (ADC) directly to a bandwidth-limited antenna, and directly sampling wide RF spectra with sufficient dynamic range to permit the demodulation of narrowband channels using digital signal processing hardware and software. Digitisation of the entire HF spectrum (2-30 MHz) has recently become feasible, with state-of-the-art A-D converters currently capable of sampling rates of up to 105 MSPS at 14 bit resolution. Digital signal processing hardware and algorithm speeds, once considered an impediment to the digitisation of wideband data, continue to advance and are currently capable of performing advanced signal processing tasks, such as adaptive equalisation, which are difficult or impossible to implement in the analogue domain.

This dissertation explores the digitisation and frontend digital signal processing of the HF and VHF spectra for the purposes of wideband radio reception.

### 1.1 Background

A well-documented history of communications receivers can be found in Rohde et al. [23]. The development of the superheterodyne-type receivers revolutionised receiver design, relegating previous receiver architectures to occasional, special-purpose use. The superheterodyne architecture is not without problems, however. The use of mixers to perform frequency translation introduces the associated problems of image frequency rejection, IF leak-through and high order non-linearities. Local oscillator (LO) noise sidebands may be translated to the IF by a strong out-of-band signal (usually a strong adjacent channel), a process termed reciprocal mixing[23]. Phase imbalance between in-phase and quadrature channels significantly limits performance in analogue quadrature channel conversion[27].

The advantages of a digital receiver solution are significant, and include reduced system cost, increased temperature stability, finer tuning resolution, faster tuning speed, excellent quadrature channel phase balance, increased filter selectivity, robustness in terms of both hardware and software signal processing algorithms, reconfigurability, advanced signal processing techniques and the ability to store signals for subsequent off-line processing.

These benefits have resulted in the digitisation process moving closer to the RF frontend, with the ultimate goal of directly digitising the antenna output. The "Software Defined Radio" (SDR) has recently been realised, allowing reconfiguration of signal processing functions through software, and resulting in reconfigurable radios capable of operating over multiple air interfaces.

Figure 1.1 illustrates the progression of receivers in recent years. Initially, the limited sample rates of A-D converters and limited digital signal processing power precluded the use of digital hardware beyond baseband signals. With recent improvements in A-D conversion and digital signal processing hardware, sampling and processing of wideband IF signals has become a reality. Digital down-conversion has facilitated the elimination of analogue down-conversion and quadrature conversion stages. It is likely that future digital and mixed signal technology will soon supersede the superheterodyne architecture completely, directly sampling bandlimited RF signals.

### 1.2 Scope

This dissertation is an investigation and evaluation of state-of-the-art wideband digital radio receiver hardware through the design, implementation and qualification of a scalable multi-channel IF-input wideband digital radio receiver. A survey of digital

Figure 1.1: The progression of receivers from analogue to digital

radio receiver architectures and relevant theory is conducted. Simulations and empirical investigations are performed. A general-purpose wideband digital receiver capable of operating in the HF and VHF bands is proposed and implemented. The receiver is quantitatively evaluated, after which conclusions on receiver performance and future trends in wideband digital radio architectures are drawn.

The design, implementation and qualification of the general-purpose receiver spans a two-year period during which the author was solely responsible for the design, testing and integration of digital receiver hardware and driver-level software in numerous systems.

# 1.3 System Specification

The design goal for the system is to realise a highly reconfigurable digital receiver using commercial-off-the-shelf (COTS) components where possible.

- The receiver should be capable of functioning as a backend to wideband and narrowband analogue down-converters.

- It should be capable of digitising the intermediate frequency (IF) output of analogue down-converters with output bandwidths of up to 10 MHz, at IF's in the HF and VHF bands.

- The receiver should accept full scale single-ended analogue input signal levels of ca. 0 dBm, with allowance for fixed amplification of 20 dB. It is presumed that any dynamic analogue receiver gain (manual or automatic gain control) that may exist is included in the analogue down-converter.

- The receiver is required to support wideband down-conversion, baseband filtering and rate reduction in hardware.

- It should further support the extraction of narrowband signals from the wideband input for the purpose of real-time demodulation.

- The system should be scalable, supporting multiple receiver channels.

- It should contain flexible sampling and synchronisation circuitry to support phase-synchronous data acquisition on multiple channels, a prerequisite in applications such as wideband direction finding (DF) and beamforming.

The required modes of operation are presented in table 1.1.

| Sampling  | IF       | Input     | Output    | SFDR   | Maximum       |

|-----------|----------|-----------|-----------|--------|---------------|

| Frequency |          | Bandwidth | Bandwidth |        | Channel Count |

| 51.2 MSPS | 5.0 MHz  | 800 kHz   | 800 kHz   | 80 dBc | 5 (synch)     |

| 51.2 MSPS | 12.8 MHz | 10 MHz    | 10 MHz    | 75 dBc | 6 (synch)     |

| 51.2 MSPS | 5.0 MHz  | 500 kHz   | 11 kHz    | 80 dBc | 12 (asynch)   |

Table 1.1: Wideband receiver operating mode requirements

### 1.4 System Architecture

The receiver implementation consists of one (single antenna) or more (multiple antenna) wideband receiver channels implemented on full-length PC ISA adapter cards and mezzanine modules and mounted in a ruggedised industrial computing rack. A commercially available industrial Single Board Computer (SBC) housing single or dual Intel Pentium processors with 100 Mbit ethernet support forms the main system controller and high-performance back-end processor for the system. It further allows the system to act as a networked data server sub-system on larger systems, supporting system growth. The implemented hardware facilitates multi-channel phase-synchronous data acquisition.

Each wideband receiver (ISA adapter card and mezzanine boards) contains minimal analogue signal conditioning circuitry, a wideband 14 bit 65/80 MSPS A-D converter, dedicated digital down-conversion (DDC) signal processing hardware, extensive FIFO buffering and an Analog Devices ADSP-21160 Super Harvard Architecture floating-point digital signal processor (DSP). The SBC communicates directly with the DSP via the DSP's host processor interface which is accessible to the SBC on the ISA bus. Sample timing and synchronisation circuitry may be implemented on-board (asynchronous/stand-alone receivers) or generated externally (synchronous multi-channel receivers).

An important design decision is the approach taken to realise wide instantaneous bandwidths necessary for fast scanning receivers and wideband DF applications. A wide instantaneous bandwidth is formed from multiple digital down-conversion channels tuned to adjacent bands. This approach provides a scalable solution to achieving both narrow and wide output bandwidths while maintaining efficient down-conversion structures and increased signal processing gain. A limitation of this approach is that the wideband data is channelised, making subsequent narrowband time domain processing of the wideband data difficult.

Each digital receiver board may form the back-end to a wideband analogue receiver or may be configured to sample a bandwidth-limited antenna input directly. The re-

ceiver's analogue input bandwidth may extend to 250 MHz (sub-Nyquist sampling), allowing the receiver to operate in the HF and VHF bands, while supporting instantaneous output bandwidths in excess of 10 MHz.

Much consideration was given to the qualification of receiver boards during system design. Test modes were incorporated into the hardware design, such that the receiver performance could be fully evaluated.

Firmware was written in VHDL and was compiled using Altera Max+Plus II software. Test software operating on the ADSP-21160 DSP was developed using the Analog Devices Inc. VisualDSP++ C/C++ V1.0 compiler and development suite. Host CPU software was developed using the Microsoft Visual C++ 6.0 compiler and development platform. WinDK DDK Development Library V2.7 was used in conjunction with the Windows Platform SDK and Windows NT4.0 DDK in the development of device driver software for communicating with the ISA adapter cards. Simulations were performed under MATLAB 5.2.

### 1.5 Related Work

Current research efforts focus on improving both converter speed and linearity.

Velazquez[29] decribes a technique that may improve the speed of conversion of high-speed, high resolution analog-to-digital converters in RF receiver applications by up to six times the state-of-the-art using a filter bank architecture.

Sigma-delta techniques promise to provide high-resolution A-D converters capable of sampling narrowband signals at a sampling frequency range that extends to gigahertz[14].

Post-digitisation error correction schemes aim to reduce the non-linearities in the digitisation process by modelling the error mechanisms inherent in A-D conversion. A-D conversion error has been shown to be related to analogue input frequency, and static error correction is giving way to dynamic correction schemes such as phase-plane compensation[9], sinewave histogram compensation [15] and adaptive compensation [18]. A-D converter non-linearities have been reduced by as much as 10 to 20 dB using these techniques.

#### 1.6 Document Overview

Chapter 1 provides an overview of this dissertation, motivating the digitisation of wideband spectra and describing the aim of the dissertation. The layout of the dissertation is also described.

Chapter 2 explores the digitisation of wide spectral bandwidths at RF frequencies. An ad hoc estimation of the requirements necessary for the digitisation of wide bandwidths is performed. A-D converter architectures are discussed in light of the requirements for wideband digitisation of RF signals. Dynamic range requirements lay the foundation for a discussion of noise and distortion introduced in the digitisation process. It is shown that sampling aperture jitter may be a significant contributor to noise introduced in the digitisation process, leading to stringent requirements on sampling oscillator jitter performance. Distortion mechanisms are analysed, and methods of distortion reduction are reviewed. Dithering is introduced as an efficient method of improving average A-D converter linearity by reducing input dependent errors. The optimal interfacing of an analogue receiver frontend and an A-D converter is discussed.

Chapter 3 investigates digital signal processing algorithms that may be used to perform down-conversion, rate reduction, bandwidth limiting and spectral estimation. Efficient down-conversion, filtering and rate reduction hardware architectures are examined. The FFT is introduced as an efficient method of spectral analysis. The signal-to-noise ratio improvements inherent to decimation filtering and FFT averaging are explored.

Chapter 4 presents the architecture of the generalised wideband digital receiver. The theory presented in chapters 2 and 3 is applied to the design and specification of the digital receiver. The channelised filter bank approach used to realise wide output bandwidths is described and justified.

Chapter 5 discusses parts of the implementation of the digital receiver in further detail. The problems encountered in the receiver design are described.

Chapter 6 characterises the performance of the digital receiver. Signal-to-noise ratio and receiver linearity measurements are performed. The effect of adding band-limited dither noise is quantified.

Chapter 7 concludes that the requirement of designing a wideband digital receiver that satisfies the requirements stipulated in section 1.3 was satisfied. The resulting receiver is shown to be flexible and scalable, using predominantly COTS components and standard assembly methods. The use of dither to improve receiver dynamic range is found to be justified, both theoretically and empirically. Suggestions on possible improvements to the receiver are discussed.

# Chapter 2

# Wideband Signal Digitisation

Two requirements are paramount in the digitisation of wideband signals, namely high sampling rates and high instantaneous dynamic range. Bandpass sampling theory places a restriction on the minimum sampling rate that may be used to unambiguously represent a band-limited signal using discrete samples. This in turn places strict demands on A-D converters in terms of sampling rates. A high instantaneous dynamic range is required to reliably receive a weak signal in the presence of larger signals.

# 2.1 Dynamic Range Restrictions in Wideband Digitisation

The maximum signal that may be presented to the input of an A-D converter may be considered to be a sinusoidal waveform with a peak-to-peak amplitude that maps to the full range of A-D output codes. A larger amplitude would result in output waveform clipping, while a smaller amplitude does not take full advantage of the resolution available in the converter. This waveform is therefore used to set an upper limit on dynamic range. Assuming no noise is present, the minimum signal is one which would result in a change of the least significant bit (LSB) of the converter. Subject to these criteria, the dynamic range of an ideal A-D converter may be defined

as the logarithmic ratio of the powers of these signals [27]:

$$DR_{ADC} = 10 \cdot log_{10} \left(\frac{P_{max}}{P_{min}}\right)$$

$$= 10 \cdot log_{10} \left(\frac{\frac{2^{2b}Q^{2}}{8}}{\frac{Q^{2}}{8}}\right)$$

$$= 20 \cdot b \cdot log_{10}(2)$$

$$\approx 6 \cdot b$$

(2.1)

where b refers to the number of bits and Q refers to the voltage per quantisation level. Equation 2.1 is the basis on which the familiar rule-of-thumb that the dynamic range of an A-D converter is "6 dB per bit" is formed. It will later be demonstrated that this measure of dynamic range is not applicable to dithered quantisation schemes, but it provides a useful approximation for the discussion to follow  $^1$ :

If the full-scale sinusoid waveform mentioned above were replaced by two equal amplitude sinusoidal waveforms of uncorrelated phase and frequency, the maximum amplitude of each waveform would have to be halved in order to prevent constructive interference of the signals from overloading the A-D converter. In general, for every doubling of the number of equal-amplitude sinusoids, their amplitudes should be reduced by a factor of 2. This may be viewed as the dynamic range available to each of the sinusoidal signals in the presence of the other signals, and may be expressed in logarithmic form as:

$$DR_{avail} = 20 \cdot b \cdot log_{10}(2) - 6 \cdot log_2(N)[dB]$$

(2.2)

where b refers to the number of bits in the A-D converter and N refers to the number of channels. The number of channels, N, may be expressed as:

$$N = \frac{B \cdot O_b}{S_{ch}} \tag{2.3}$$

where B refers to the bandwidth [Hz],  $O_b$  the band occupancy and  $S_{ch}$  the channel separation [Hz].

Equations 2.2 and 2.3 are combined to formulate an expression for B, the maximum bandwidth that may be sampled:

$$B = \frac{2^{\frac{20 \cdot b \cdot log_{10}(2) - DR_{qyail}}{6} \cdot S_{ch}}}{O_b}$$

(2.4)

<sup>&</sup>lt;sup>1</sup>This discussion should be viewed as an *ad hoc* estimation of the dynamic range required of a converter in order to digitise a given bandwidth. It aims to give the reader an impression of the impact of converter resolution on maximum sampled bandwidth, as well as a method of broadly measuring the usability of a wideband receiver in a given environment.

Figure 2.1: An example plot of maximum bandwidth versus number of bits.

By way of example, the assumptions listed in table 2.1 are made.

| Parameter           | Value        |

|---------------------|--------------|

| b                   | 4 to 16 bits |

| DR <sub>avail</sub> | 50 dB        |

| $S_ch$              | 8 <i>kHz</i> |

| $O_b$               | 0.1          |

Table 2.1: Parameters used in the calculation of maximum sampled bandwidth

It is further noted that the above discussion is only a rough approximation, since it was based on equal-amplitude sinusoidal signals as opposed to modulated signals.

The values stated in table 2.1 are substituted into equation 2.4 and plotted in figure 2.1. From this plot it is evident that converter resolution plays a dominant role in determining a maximum bandwidth that may be sampled for any level of desired usable dynamic range.

It should be noted that the probability of all N signals constructively interfering to a given level in a given timespan decreases as N increases, assuming each signal has random phase and frequency. With this in mind, the above may be considered an analysis of the worst-case.

## 2.2 Bandpass Sampling Theory

This section reviews the theory related to the sampling of wideband signals. For practical purposes, the sampling discussion is restricted to uniform sampling intervals (periodic sampling). The fundamental sampling criterion, credited to Harry Nyquist, forms the basis for the discussion on bandpass sampling theory.

#### 2.2.1 Nyquist's Criterion

Nyquist's criterion stipulates the requirements for perfect reconstruction of a uniformly sampled bandlimited signal [25]:

$$T < \frac{1}{2B} \tag{2.5}$$

where B refers to the upper frequency limit on the spectral components present in the signal and T refers to the uniform sampling interval. Restated in terms of sampling frequency  $F_s$ , this can be expressed as:

$$F_s > 2B \tag{2.6}$$

Equations 2.5 and 2.6 can be understood as a necessary condition to prevent overlap of spectral replications, periodically spaced by  $F_s$ , that are inherent to the periodic sampling process [17]. This overlap causes ambiguity in signal reconstruction, and is commonly referred to as aliasing. In practice, some level of aliasing does occur, and it is the function of an analogue anti-aliasing filter to reduce the aliasing to acceptable levels. Due to the finite transition band slope that may be realised in practical analogue filtering, it is conventional to restrict the anti-aliasing filter passband to slightly less than that given by equation 2.5. This topic is covered in more detail in sections 2.2.2 and 2.4.

It is conventional to assume that analogue filtering is low-pass, sufficiently attenuating signals above  $\frac{F_4}{2}$  to prevent unacceptable aliasing.

### 2.2.2 Bandpass Sampling

For a variety of applications, including digital receivers, bandpass sampling techniques may be preferable. Bandpass sampling reduces the speed requirement of A-D converters below that necessary with traditional low-pass sampling. The reduced

Figure 2.2: A typical bandpass sampling scheme

bandwidth of the converter output reduces the memory required to store the signal in a digital form and reduces the demand placed on subsequent processing.

Figure 2.2 demonstrates the technique of bandpass sampling, also referred to as IF sampling, harmonic sampling, sub-Nyquist sampling and undersampling. The sampling rate is expressed as  $F_s$ , and the sampled band, of bandwidth B, is located at  $(F_l, F_u)$ . The sampling process results in the periodic replication of signals within the sampled spectrum, with period  $F_s$ . The spectral replication is used to advantage in bandpass sampling, where it may be viewed as a sampling process with inherent frequency translation into the region  $\left(-\frac{F_s}{2}, \frac{F_s}{2}\right)$ , commonly referred to as sampling translation[17].

#### 2.2.2.1 Precluding Ambiguities in Bandpass Sampling

A bandpass signal may be sampled at an arbitrary frequency  $F_s$  without introducing aliasing ambiguities, provided that the following criteria are met:

- The Nyquist criterion, as expressed in equation 2.5 is met. The definition of B should be redefined as the sampled bandwidth in the bandpass sampling case.

- The passband does not cross an  $\frac{NF_s}{2}$  boundary, where N is integer-valued.

These requirements have been stated mathematically as [28]:

$$\frac{2F_u}{n} \le F_s \le \frac{2F_l}{n-1} \tag{2.7}$$

Figure 2.3: The allowed regions for bandpass sampling

where n is an integer given by

$$1 \le n \le I_g \left[ \frac{F_u}{B} \right] \tag{2.8}$$

and  $I_g[x]$  denotes the largest integer within x. Equations 2.7 is depicted graphically in figure 2.3 [28]. With reference to figure 2.3, the abscissa represents the band position  $F_u$ , while the ordinate contains the sampling frequency  $F_s$ . Both quantities are normalised by B. The band is located at  $(F_l, F_u)$ . The areas within the wedges are the allowed zones for sampling without aliasing, while the shaded area represents those areas in which aliasing will occur. The lowpass case  $F_s \geq 2F_u$ , resulting from n=1, corresponds to the large wedge to the left in figure 2.3. Each adjacent wedge corresponds to a successive value of n, and may be referred to as  $n_{th}$  zone Nyquist sampling. Vaughan  $et\ al.$  [28] propose the inclusion of "guard-bands" in practical bandpass sampling schemes. These assist in eliminating the pathological cases where the edge of the band lies infinitesimally close to an  $\frac{F_s}{2}$  boundary (depicted as the wedge borders in figure 2.3). In such pathological cases, minimal deviations in sampling frequency and non-ideal filtering give rise to aliasing. The total guard band, given by  $B_{GT} = F_s - 2B$ ,

is expressed on the right-hand ordinate in figure 2.3.

#### 2.2.2.2 Sampling Frequency Precision

Vaughan et al. [28] demonstrates that, to prevent aliasing, the relative precision required of the sampling frequency  $F_s$  may be expressed as

$$\frac{\Delta F_s}{2B} = \frac{1}{n(n-1)} \left( \frac{F_u}{B} - n \right)

\approx O\left( \frac{1}{n^2} \right)$$

(2.9)

Equation 2.9 demonstrates that the relative precision required of the sampling frequency  $F_s$  increases with separation from the origin, and is approximately related to the inverse square of the separation of the band from the origin. This further demonstrates the necessity for adequate guard-bands as the bandwidth of interest moves up in frequency relative to the sampling frequency.

### 2.2.3 Spectral Inversion in Bandpass Sampling

Spectral inversion in the baseband alias of the band-of-interest occurs when n is even-valued [28]. This may be seen by examining the aliasing pattern in figure 2.2 When the positive spectral bandpass components are symmetrical about  $F_c$ , spectral inversion presents no problem. Spectral inversion should be avoided when signals are asymmetrical with respect to  $F_c$ , as is the case in single sideband (SSB) signals. This can be achieved by restricting n to being odd-valued.

It is possible to reverse the spectral inversion with minimal signal processing overhead, so as to avoid this restriction on n. This is achieved by modulating the sample sequence with the sequence  $1, -1, 1, -1, \dots$  or  $(-1)^n$  [17]. This effectively translates the sampled spectrum by  $\frac{F_s}{2}$ . It should further be noted that the DC component will be translated to both  $\frac{+F_s}{2}$  and  $\frac{-F_s}{2}$ .

### 2.2.4 Applying Bandpass Sampling to Wideband Reception

Bandpass sampling techniques may be used to advantage in wideband digital radio. As mentioned previously, A-D converter output rates may be lowered, reducing the burden on subsequent processing stages.

Furthermore, when undersampling is employed, the signals of interest are aliased into the region  $(\frac{-F_3}{2}, \frac{F_2}{2})$ . Restated, this inherent down-conversion may be used to translate bandwidths at higher IFs into the aforementioned region. The resulting spectrum, located in the first Nyquist zone, may be translated down to baseband through a variety of digital down-conversion schemes, as detailed in chapter 3. The use of either or both of these techniques may result in a reduction in the number of analogue down-conversion stages and the associated analogue circuitry (LO, mixer etc.).

### 2.2.5 Quadrature Sampling and Complex Signal Representation

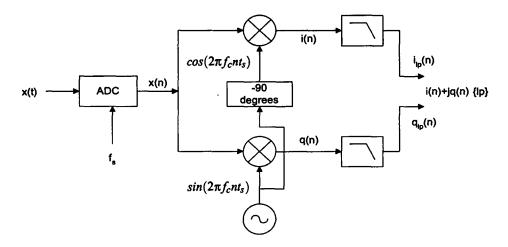

It is common for digital signal processing applications to use a complex data representation with real ("in-phase" or "I") and imaginary ("quadrature-phase" or "Q") parts. A quadrature sampling scheme, as depicted in figure 2.4, may be used to achieve complex or quadrature signal representation at baseband.

Figure 2.4: Illustration of quadrature sampling scheme.

It may be shown that the multiplication of a signal with a complex exponential  $e^{j2\pi f_c t}$  results in a translation or shift of the spectral content of the signal by  $f_c$  Hz. The quadrature sampling scheme implements this frequency translation through Euler's identity:

$$e^{\pm j\theta} = \cos(\theta) \pm j \sin(\theta)$$

(2.10)

The analogue input signal is mixed by means of analogue mixers with the constituent sinusoidal components of the complex exponential  $e^{j2\pi f_c t}$ , resulting in a complex-valued representation of the input signal that is translated in frequency by  $f_c$  Hz and is

separated into its in-phase (real) and quadrature-phase (imaginary) components. The value of  $f_c$  is conventionally chosen such that the input signal is translated to DC ("baseband"). A detailed mathematical account may be found in [16] or [17]. The complex data format is useful in many applications for the following reasons:

- 1. Each A-D converter may sample at half the rate of conventional sampling, while achieving the same output bandwidth. Restated, the digitised bandwidth may be extended from the theoretical  $\frac{f_s}{2}$  imposed by Nyquist's criterion to  $f_s$ , the sampling rate of the A-D converter.

- 2. Quadrature sequences are easily described and manipulated mathematically.

- 3. Quadrature sequences make Fast Fourier Transform (FFT) processing efficient, covering a wider frequency range than a conventional real FFT. Methods for increasing real FFT efficiency are known, but the complex FFT is usually simpler to use.

- 4. Phase and amplitude information is easily extracted from the complex representation, facilitating efficient algorithms for demodulating amplitude or frequency modulated signals.

The phase preservation characteristic is particularly useful, and it is for this reason that complex signal representation has been widely adopted in high data rate digital communications systems, radar systems, time difference of arrival (TDOA) processing in radio direction-finding schemes, coherent pulse measurement systems, antenna beamforming applications and single-sideband (SSB) modulators.

Despite the usefulness of quadrature sampling, imbalance in the I and Q channels resulting from amplitude or phase mismatch, mixer DC offsets and  $\frac{1}{f}$  noise introduced by active components often limits the dynamic range of a receiver [17] [27]. Complex calibration may be used to improve the dynamic range, but this is undesirable due to increased system cost and complexity. Methods of realising complex basebanded signals which do not suffer from these problems will be presented in chapter 3.

### 2.3 Sources of Error in Wideband Digitisation

It is conventional in receiver design to characterise the receiver performance in terms of noise and distortion measures. These performance measures dictate the ability of a receiver to detect small signals in the presence of larger signals, and place a limit on the minimum discernable signal (MDS)[23].

In this section, the sources of error in A-D conversion are identified and analysed. It will be shown that many of the errors result in noise or distortion of the digitised signal, which impact negatively on the sensitivity of a digital receiver.

### 2.3.1 Quantisation Error

The quantisation of a signal into one of l discrete levels, uniformly spaced with spacing q, results in a quantisation error  $\varepsilon$ , the difference between the signal level and the nearest quantisation level.

Under the assumption that all values of  $\varepsilon$  in the range  $\frac{-q}{2} \le \varepsilon < \frac{q}{2}$  are equally probable, it may be shown that the quantisation error manifests itself as wideband noise, uniformly distributed within the Nyquist band  $\left(\frac{-F_s}{2}, \frac{F_s}{2}\right)$ . The mean-square quantisation noise power of an ideal n bit uniform quantiser may then be expressed as [25]:

$$\overline{\varepsilon^2} = \frac{q^2}{12} \tag{2.11}$$

The quantisation of a full scale sinusoid then results in a signal-to-noise ratio of [27]:

$$\left(\frac{S}{N}\right)_{dB} = 1.76 + 6.02n\tag{2.12}$$

The assumption that quantisation error is uniformly distributed within a quantum is generally only true for complex (non-trivial) signals that are large in comparison to the quantisation level [30], and uncorrelated to the sampling frequency [27]. When this assumption fails, error manifests itself as spurious signals within the A-D converter output bandwidth, which may limit the spurious-free dynamic range of a digital receiver. The spurious level may be reduced by sufficiently decorrelating the signal from the sampling frequency. This topic will be explored further in section 2.5.

#### 2.3.2 Static Errors in the A-D Transfer Function

The transfer function of a practical A-D converter differs from the ideal n bit uniform quantiser. The significant errors include gain error, offset error and integral and differential non-linearity. The definitions of the errors, as well as their manifestations, may be briefly summarised as follows:

#### 2.3.2.1 Gain and Offset Error

Gain error refers to an error in the slope of the A-D transfer function, after offset errors have been eliminated. It is defined as [24]:

$$E_{gain} = (V_{FS} - 2 \cdot LSB) - (V_{11} - V_{sz})$$

(2.13)

where  $V_{11}$  is the last transition voltage (most positive signal),  $V_{sz}$  is the first transition voltage (most negative signal) and  $(V_{FS} - 2LSB)$  is the full-scale range minus 2 ideal LSBs. It is expressed as a percentage of full scale range (% FSR) or in least-significant-bits (LSBs).

Offset error may be defined as a common deviation in transition voltage from the ideal transition voltage. It is conventionally measured as the deviation of the first transition from the ideal, after any gain or linearity error has been subtracted, and it is conventionally expressed in mV.

Gain and offset errors manifest themselves as DC offsets in the digitised output, a (minimal) reduction to converter dynamic range (increased noise floor) and a frequency-independent gain error in the digitised signal.

DC offsets are not of severe consequence in IF sampling converters, since the band of interest is located at an IF, and DC offsets are typically filtered out in subsequent digital signal processing stages. Gain errors in the digitised signal may be calibrated out by multiplying each sample with the inverse of the gain error. Gain correction usually does not place increased demand on digital signal processing, since it may be factored into subsequent digital filtering or gain stages. The reduction in A-D converter dynamic range as a result of gain or offset error is small. Gain and offset errors are therefore of minimal impact on the performance of a wideband digital receiver employing an IF sampling architecture.

#### 2.3.2.2 Differential and Integral Non-Linearity

The differential non-linearity (DNL) of an A-D converter may be defined as the difference between an actual code width and the ideal value of one LSB. If the DNL exceeds 1 LSB, the resulting transfer function may become non-monotonic, or missing codes may result.

Differential non-linearity typically manifests itself as higher order non-linearity in the transfer function of an A-D converter [10]. This results in higher order harmonics and mixed products being present in the digital spectrum, which may fall in-band due to aliasing, limiting the spurious-free dynamic range of a digital receiver. The location

and nature of higher-order harmonics are difficult to predict, and it is therefore not possible to place them out-of-band.

The effects of differential non-linearity may be partially eliminated through dithering, as discussed in section 2.5.

Integral non-linearity (INL) may be defined as the deviation of the A-D transfer function from an ideal straight line. End-point INL is specified in terms of the deviation from a straight line between the end-points of the transfer function, in terms of either the transition points or ideal code midpoints. *Best-straight-line* INL is defined as the deviation of a code from a line calculated to minimize the worst-case INL in a mean-squared sense.

INL results in low-order non-linearity in the A-D transfer function. Lower order harmonics and mixed products may result from signals placed at the A-D input, resulting in reduced spurious-free dynamic range. The nature of the non-linearities may vary with differing input power levels, as the integral non-linearities are exercised to different extents.

The effects of integral non-linearity may be reduced through dithering, as discussed in section 2.5.

Although DNL and INL contribute substantially to the degree of linearity of a converter, these measures are generally not sufficient to categorise an A-D converter for communications applications [7], since the position of these errors in the transfer function of the A-D converter may lead to them rarely being exercised. An example of this may be a large DNL error at close to full-scale range. It is unlikely that this would substantially degrade the linearity, since it would rarely be exercised. It is therefore often more beneficial to consider dynamic error measurements, such as spurious-free dynamic range (SFDR) and signal-to-noise-and-distortion (SINAD).

### 2.3.3 Sampling Jitter

The process of sampling an analogue signal at a given instant in time occurs as follows [24]:

- 1. An input buffer amplifier tracks the analogue signal. The amplifier output is used to place charge on an energy storage device, and requires a *settling time* in order to track the signal to within a specified accuracy.

- 2. The output of the amplifier is rapidly disconnected from the energy storage device in response to an encode command (sampling clock transition). The time

Figure 2.5: The voltage error resulting from encode signal jitter

taken to disconnect is referred to as the aperture time and is critical to sampling accuracy.

3. The charge held on the energy storage device is measured and used to determine the quantised output code.

Noise in the A-D converter encode circuitry results in a variance in the exact instant at which the aperture occurs. This time variance is referred to as aperture uncertainty or aperture jitter, and is usually expressed in seconds RMS. Jitter on the sampling clock adds further variance to the aperture delay. The complete jitter contribution may be found by taking the square root of the sum of the squares of the individual contributions:

$$T_{jitter} = \sqrt{T_a^2 + T_{clk}^2} (2.14)$$

where  $T_a$  refers to the aperture uncertainty and  $T_{clk}$  refers to the encode clock jitter. The error in sampling time results in a voltage error that is proportional to the slope (slew rate) of the signal at the sampling instant. This is illustrated in figure 2.5. The error contribution for a sinusoidal input may be shown to result in a signal-to-noise ratio of<sup>2</sup>:

$$\left(\frac{S}{N}\right)_{dB} = 20 \cdot log_{10} \left(\frac{1}{2\pi f_a T_{jitter}}\right) \tag{2.15}$$

where  $f_a$  refers to the frequency, in Hz, of the input sinusoid and  $T_{jitter}$  refers to the total jitter in the encode process, in seconds RMS.

<sup>&</sup>lt;sup>2</sup>A complete derivation of equation 2.15 may be found in appendix A

#### 2.3.3.1 The Relationship between Oscillator Phase Noise and Jitter

The time-domain jitter content in an oscillator can be related to its frequency-domain characteristic of phase noise. The relationship is explored in [22], a valuable reference on oscillator phase noise. This relationship may be useful, since many oscillator manufacturers do not measure the oscillator jitter<sup>3</sup>, but instead specify their oscillators according to phase noise requirements. It is possible to estimate the time-domain jitter in an oscillator source through its reciprocal relationship to phase noise, as demonstrated by [2]. It should be noted that this estimate is usually an under-estimate, unless oscillator harmonics and sub-harmonics are included in the estimate.

#### 2.3.3.2 Thermal Noise

Noise is generated in the analogue input circuitry of an A-D converter, resulting in an increase in the total receiver noise, and a subsequent reduction in the signal-to-noise ratio. The noise generated in analogue input circuitry (sample-and-hold and amplifiers) can be translated into an equivalent noise temperature, referred to the analogue input. This provides a means by which A-D thermal noise can be factored into total analogue receiver noise.

#### 2.3.4 Relative Noise Contributions in Wideband Digitisation

Wideband noise has been shown to be introduced into the digitisation process in the form of quantisation noise, thermal noise and noise as a result of encode clock jitter. The relative contributions of each of these terms may be found by summing the mean-squared contributions of each of the terms. The following formula, given in [5], provides a reasonable indication of the full-scale (maximum) signal-to-noise ratio that may be expected in a wideband A-D converter:

$$SNR_{dB} = -20 \cdot log_{10} \left[ \sqrt{\left(2\pi f_a t_j\right)^2 + \left(\frac{1+\epsilon}{2^N}\right)^2 + \left(\frac{V_n}{2^N}\right)^2} \right]$$

(2.16)

where  $f_a$  is the analogue input frequency,  $t_j$  the RMS encode jitter,  $\varepsilon$  the average differential non-linearity normalised to 1 LSB,  $V_n$  the rms thermal noise normalised to 1 LSB and N the number of bits. The contributions from encode jitter, static transfer function errors (quantisation noise and differential non-linearity) and thermal noise

<sup>&</sup>lt;sup>3</sup>The specification of time-domain jitter is becoming more popular, as it is becoming increasingly important in high-frequency applications.

in the A-D analogue input circuitry may be seen as each of the three terms within the square root respectively. Figure 2.6 plots the predicted signal-to-noise ratio versus the analogue input frequency for the AD6644 65 MSPS 14-bit A-D converter, for 1 pica-second RMS oscillator jitter. From this figure, it may be seen that oscillator

Figure 2.6: Signal-to-noise ratio versus analogue input frequency for the AD6644.

jitter dominates the SNR at high frequencies, for very small levels of oscillator jitter. Since the jitter contribution to SNR is related to the analogue input frequency, undersampling applications impose strict demands on oscillator jitter performance.

# 2.4 Oversampling

Oversampling is the term used to describe sampling schemes where the Nyquist frequency is greater than the signal bandwidth:

$$\frac{F_s}{2} > B \tag{2.17}$$

The ratio  $K = \frac{F_s}{2B}$  is commonly referred to as the *oversampling ratio*. Oversampling may be used to relax the requirements on anti-aliasing filters, as well as to improve the signal-to-noise ratio of a sampled signal. Harmonic spurious may be placed out-of

band through oversampling and appropriate placement of the IF. Oversampling may be used in conjunction with bandpass sampling, realising the benefits of both techniques simultaneously.

#### 2.4.1 Relaxation of Anti-aliasing Filter Requirements

Since analogue filters with infinitely narrow transition regions are not realisable in practice, some degree of oversampling is necessary. By increasing the oversampling ratio, the width of the transition region may be increased, reducing the order of filtering required to meet aliasing requirements. This is illustrated in figure 2.7.

Figure 2.7: Anti-aliasing filter transition width requirements for oversampling ratios of 1.333 and 2 respectively.

# 2.4.2 Signal-to-Noise Ratio Improvement Through Oversampling

For a given bandwidth B, increasing the oversampling ratio results in a uniform spreading of the quantisation noise power over the wider Nyquist bandwidth  $(0, \frac{F_{s new}}{2})$ . Digital filtering may be employed subsequent to digitisation to filter out noise that falls outside of the bandwidth B, thereby reducing the quantisation noise power, and any other noise falling outside of the bandwidth B, resulting in an improved signal-to-noise ratio. The signal-to-noise ratio improvement due to quantisation noise spreading and

subsequent filtering may be computed using equation 2.18

$$\Delta SNR = 10 \cdot log_{10}(K) \tag{2.18}$$

where K refers to the oversampling ratio. It is noted that the signal-to-noise ratio improvement is limited by the resolution at which the digital filtering is performed. For a reduction in quantisation noise, the digital filtering resolution should exceed the resolution of the A-D converter.

#### 2.4.3 Spurious Harmonic Placement

Lower order harmonics often impose a restriction on the spurious-free dynamic range due to lower order non-linearity within both the analogue receiver sections and the A-D converter. Through correct placement of the band-of-interest B relative to the sampling frequency, lower order harmonics may be constrained to fall outside of the bandwidth-of-interest. Figure 2.8 illustrates a placement of a band-of-interest in the second nyquist zone, such that the second and third harmonics do not fall in-band after digitisation.

Figure 2.8: Band placement such that harmonics do not fall in-band after digitisation.

# 2.5 Signal Dithering

Signal dithering is a technique that may be used to improve the dynamic range of an A-D converter. Dithering achieves this by controlling the statistical properties of the

errors introduced in the quantisation process [30]. The input signal is summed with an uncorrelated dither signal which has suitable statistical properties prior to A-D conversion, such that the resulting conversion error is uniformly distributed.

A common misconception is that the level of a sampled signal that may be detected is limited by the converter resolution. In dithered architectures, it is usually possible to extract signals well below the level of a quantum [10]. This is achieved by dithering the signal prior to sampling (which ensures that quantisation noise is sufficiently decorrelated), and using post-conversion digital filtering to reduce the level of quantisation noise. Dithering ensures that the noise is randomly spread across the A-D converter output bandwidth. By sufficiently reducing the A-D output bandwidth through digital filtering, large signal-to-noise ratio improvements may be achieved. This is analogous to analogue receiver band limiting, where received noise is proportional to the receiver bandwidth. The digital filtering should be performed at a higher resolution than the converter resolution, such that quantisation noise may be reduced below the LSB of the converter through band limiting.

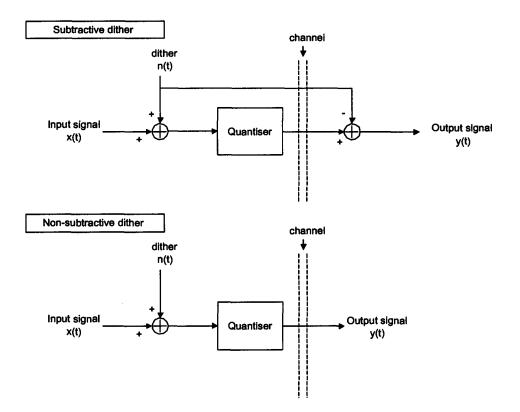

#### 2.5.1 Subtractive and Non-subtractive Dithering Techniques

Dithering may be classified as subtractive dither (SD) or non-subtractive dither (NSD). The two techniques are detailed in figure 2.9.

In SD, the dither signal is added prior to quantisation, and subtracted prior to the output. The dither noise does not reduce the signal-to-noise ratio on the output, since it is subtracted. In NSD, the dither signal is not subtracted, and therefore results in an undesirable reduction of the output signal-to-noise ratio.

#### 2.5.1.1 Subtractive Dithering

The characteristic function (cf) of a random variable is defined as [30]:

$$P_x(u) = E[e^{-j2\pi ux}]$$

$$= \int_{-\infty}^{\infty} F(x)e^{-j2\pi ux} dx$$

(2.19)

In SD of an ideal converter, the total error can be rendered uniformly distributed and statistically independent of the system input by choosing a dither such that the *cf* of the dither satisfies the condition [30]:

$$P_{\nu}\left(\frac{k}{\Lambda}\right) = 0 \quad \forall \ k \in \mathbb{Z}_0 \tag{2.20}$$

Figure 2.9: Subtractive and non-subtractive dithering schemes

where  $\Delta$  is the quantisation level and  $\mathbb{Z}_0$  is defined as the set of all integers excluding 0. A function that satisfies this condition is a function with a probability density function or *pdf* of the form:

$$p(x) = \Pi_{\Delta}(x) \tag{2.21}$$

where the rectangular window function of width  $\Gamma$ ,  $\Pi_{\Gamma}$ , is defined as

$$\Pi_{\Gamma}(x) = \begin{cases} \frac{1}{\Gamma}, & |x| < \frac{\Gamma}{2}, \\ \frac{1}{2\Gamma}, & |x| = \frac{\Gamma}{2}, \\ 0, & \text{otherwise.} \end{cases}$$

(2.22)

The cf of this pdf may be expressed as

$$P_x(u) = \frac{\sin(\pi \Delta u)}{\pi \Delta u} \tag{2.23}$$

This results in the nulls in the cf that satisfy the requirements of equation 2.20.

Wannamaker [30] refers to this uniformly distributed dither of peak-to-peak amplitude  $\Delta$  as rectangular pdf dither or RPDF dither. He further defines the summation of n such dithers as rectangular pdf dither of order n or nRPDF dither. The pdf of the sum of n random variables may be found by convolving the n individual pdfs, while the cf is found by multiplying the n cfs. Thus, the pdf of 2RPDF dither is triangular, of peak-to-peak amplitude  $2\Delta$ .

Furthermore, the values of total error separated in time can be rendered statistically independent of one another by ensuring that the dither values are statistically independent of one another.

#### 2.5.1.2 Non-subtractive Dithering

While subtractive dither may be considered an optimal dither, due to its statistical properties, its implementation may be prohibitively expensive (since the analogue dither needs to be digitally subtracted after digitisation). Non-subtractive dither is therefore given consideration, due to its ease of implementation:

Wannamaker demonstrates that in a non-subtractive dither quantising system it is not possible to render the total error statistically independent of the system input or uniformly distributed for system inputs of arbitrary distribution. An nRPDF dither does, however, render the first n moments of the total error process independent of the distribution of the system input, and results in a total error variance of  $\frac{(n+1)\Delta^2}{12}$ . Higher moments of the error signal will, however, remain input dependent. He further proves that the choice of zero-mean non-subtractive dither pdf which renders the first and second moments of the total error independent of the input, such that the first moment is zero and the second moment (the variance) is minimized, is unique and is 2RPDF (triangular) dither.

Non-subtractive dithering cannot render total error values separated in time statistically independent of each other, but it can regulate the joint moments of such errors. Importantly, it can therefore render the power spectrum of the total error white [30].

# 2.5.2 Small- and Large-scale Dithering

Dither may be categorised as either small-scale (of the order of a quantisation level in amplitude) or large-scale (in the order of full scale in amplitude)[10]. The discussion on dither will be broken down according to these categories, demonstrating the usefulness of each of them.

#### 2.5.2.1 Small-scale Dithering

The aim in small-scale dither (the dithers described above fall into this category) is to reduce the level of fixed-frequency spurious content that is introduced to a signal in the A-D conversion process through quantisation error.

Small-scale dithers aim to ensure that the quantisation error in an otherwise ideal quantisation process results in white noise spread across the sampled spectrum, rather than concentrated at specific frequencies.

#### 2.5.2.2 Large-scale Dithering

The aim of large-scale dither is to average the high-order integral non-linearities in an A-D transfer function, through the addition of large-scale (usually no more than half of full-scale amplitude) noise followed by averaging. This imposes restrictions on the usable dynamic range of the A-D converter [7], but may substantially improve the average linearity of the converter [10]. A subtractive dither scheme is used to eliminate the high degradation in signal-to-noise ratio that results from the addition of high levels of noise prior to sampling.

#### 2.5.2.3 Mid-scale Dithering in Multi-Stage Converters

Practical converter non-linearities, such as DNL and INL discussed above will occur to various extents in regions of the transfer function. This is especially true of multistage A-D converters, as is described below.

The total error resulting from DNL may be found by integrating the product of the *pdf* of the input signal and the DNL errors over the input signal range. The amount of non-linearity introduced by the conversion is therefore dependant on the likelihood of samples occurring in code regions with poor differential or integral non-linearity.

In multi-stage sub-ranging converters, the conversion is subdivided into successive conversion stages. A two-stage sub-ranging converter, for example, uses two A-D converter stages. The first A-D converter performs a course conversion. The resulting digitised sample is converted back to an analogue voltage and subtracted from the original signal. The difference signal is scaled and fed into the second A-D converter which performs a finer-resolution conversion. The two A-D conversions are combined to form the total output resolution of the A-D converter. Since the range of the second A-D converter is used many times in the overall range of the A-D converter, any DNL errors in the transfer function of the second A-D converter repeat at intervals of  $2^N$ ,

where N is the number of bits in the first-stage A-D converter. Since these errors are repetitive, their likelihood of occurrence is increased, resulting in a drastic decrease the average linearity of the device[7].

Adding dither noise of sufficient amplitude (of the order of the period of the repetitive DNL errors in the transfer function) results in the error being sufficiently decorrelated from the input signal. The reduction in correlation between the input signal and the DNL errors results in a reduction of the spurious harmonics of signals present at the converter input.

# 2.6 A-D Converter Input Level Matching

In wideband digital receivers it is necessary to precede the A-D converter with analogue signal conditioning.

Analogue filtering is necessary to limit the input bandwidth and reduce aliasing to acceptable levels. Only energy within the input bandwidth is passed to the A-D converter, reducing the input noise power and more importantly the signal energy at the A-D converter input. In section 2.1 the relationship of signal energy to instantaneous dynamic range was demonstrated.

Analogue signal conditioning must also ensure that the received signal level is optimally matched to the A-D converter input voltage range. An optimal match is defined as a match that achieves an optimal combination of desired sensitivity and dynamic range, within the limits of analogue signal conditioning and A-D converter performance. This section discusses the optimal matching of the analogue signal conditioning (in the form of an analogue wideband receiver) and A-D converter interface. The discussion is based on a similar discussion presented in [27].

The following section presents basic analogue receiver design theory which will be required for the discussion that follows.

# 2.6.1 Characteristics of an Analogue Receiver Chain

For the purposes of gain, noise and distortion analysis, a cascaded chain of analogue components may be modelled as a single component, where:

The overall gain of the cascaded chain is defined as [27]:

$$G = G_1 G_2 \dots G_n \tag{2.24}$$

or

$$G = G_1 + G_2 + \ldots + G_n[dB] \tag{2.25}$$

where  $G_1, G_2, \ldots$  are the gains of the individual cascaded components.

The overall noise figure F of the cascaded chain is defined as [27]:

$$F = F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_1 G_2} + \dots + \frac{F_n - 1}{G_2 G_2 \dots G_{n-1}}$$

(2.26)

where  $F_1, F_2, \ldots$  are the noise figures of the individual cascaded components.

The overall output third-order intercept point of the cascade chain is defined as [27]:

$$Q_3 = \frac{G}{\frac{G_1}{Q_{3,1}} + \frac{G_1 G_2}{Q_{3,2}} + \ldots + \frac{G_1 G_2 \ldots G_n}{Q_{3,n}}}$$

(2.27)

where  $Q_{3,1}, Q_{3,2}, \ldots$  are the output third-order intercept points of each individual component.

The intercept point may be used to determine the amplitude of the two-tone third-order intermodulation products by means of the following equation [27]:

$$P_3 = 3\left(P_o - \frac{2}{3}Q_3\right)[dB] \tag{2.28}$$

where  $P_o$  refers to the output power of the two signals.