### CLOUD-BASED FPGA CUSTOM COMPUTING MACHINES

BY

### AMRAN ABDULRAHMAN AL-AGHBARI

A Dissertation Presented to the **DEANSHIP OF GRADUATE STUDIES**

### **KING FAHD UNIVERSITY OF PETROLEUM & MINERALS**

DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

# **DOCTOR OF PHILOSOPHY**

In

COMPUTER SCIENCE AND ENGINEERING

**DECEMBER 2018**

### KING FAHD UNIVERSITY OF PETROLEUM & MINERALS DHAHRAN- 31261, SAUDI ARABIA

### DEANSHIP OF GRADUATE STUDIES

This thesis, written by **Amran Abdulrahman Al-Aghbari** under the direction of his thesis advisor and approved by his thesis committee, has been presented and accepted by the Dean of Graduate Studies, in partial fulfillment of the requirements for the degree of **DOCTOR OF PHILOSOPHY IN COMPUTER SCIENCE AND ENGINEERING.**

The 13/2/2019

Dr. Mohamed Elrabaa (Advisor)

- 13/2/2019

كادا ا

Dr. Adel Fadhl Ahmed Department Chairman

DE Dr. Salam A. Zummo Dean of Graduate Studies 3

19/2/19

Date

Prof. Aiman El-Maleh (Member)

21/112018

Dr. Mohammad Alshayeb (Member)

Dr. Marwan Abu-Amara (Member)

Dr. Ashraf S. Hasan Mahmoud (Member)

© Amran Abdulrahman Al-Aghbari

2018

Dedication

To my wife, children, and our parents, brothers, sisters and their children.

### ACKNOWLEDGMENTS

Full thanks to my advisor Dr. Mohamed Elrabaa who guided me along my graduate studies at KFUPM University and taught me VLSI from scratch until fabricating a real chip. Thanks to Prof. Mayez Al-Mohamed who taught me most of the valuable principles I know about computing architectures and parallel computing which were helpful in this work. Thanks to all professors who taught me different courses during my graduate studies which were valuable guidance to accomplish this work. Thanks to KFUPM University which provides those expensive devices and licenses that helps a lot to do real and valuable experiments. Thanks to Saudi Arabia for financial support for their students and foreign students. Thanks to Taiz University, my home university in my home country for sending me to KFUPM University to do graduate studies and supporting me financially.

## **TABLE OF CONTENTS**

| ACK  | KNOWLEDGMENTS                                   | V    |

|------|-------------------------------------------------|------|

| TAE  | BLE OF CONTENTS                                 | VI   |

| LIST | T OF TABLES                                     | X    |

| LIST | T OF FIGURES                                    | XII  |

| LIST | T OF ABBREVIATIONS                              | XVII |

| DIS  | SERTATION ABSTRACT                              | XIX  |

| رجةُ | الدكتوراةِ في الفلسفةِ ملخَّصُ بحث در           | XXI  |

| CHA  | APTER 1 INTRODUCTION                            | 1    |

| 1.1  | Motivation                                      | 1    |

| 1.2  | Thesis statement and contributions              | 5    |

| 1.3  | Overview of the thesis                          | 6    |

| CHA  | APTER 2 CLOUD COMPUTING                         |      |

| 2.1  | Data center                                     |      |

| 2.2  | Virtualization                                  |      |

| 2.   | .2.1 Hardware virtualization                    |      |

| 2.   | .2.2 Application virtualization                 |      |

| 2.   | .2.3 Desktop virtualization                     |      |

|      | .2.4 Network virtualization                     |      |

| 2.   | .2.5 Storage virtualization                     | 14   |

| 2.3  | OpenStack: open source cloud computing platform | 15   |

| CHA  | APTER 3 DESIGN WITH FPGAS                       | 17   |

| 3.1  | FPGA architecture                               |      |

| 3.2  | Design flow                                     |      |

| 3.3                                                                  | Partial Reconfiguration                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 21                                                                                           |  |  |  |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|--|

| 3.4                                                                  | High-level synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23                                                                                           |  |  |  |

| 3.5                                                                  | FPGA strengths and weaknesses25                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                              |  |  |  |

| CH                                                                   | APTER 4 LITERATURE REVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 28                                                                                           |  |  |  |

| 4.1                                                                  | Overlay architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 28                                                                                           |  |  |  |

| 4.2                                                                  | Virtualization using abstraction layer (AL)                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                              |  |  |  |

|                                                                      | I.2.1 Interfacing the abstraction layer (AL) with vFPGAs                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                              |  |  |  |

| 4                                                                    | I.2.2 OpenCL and the CPU-FPGAs interface abstraction                                                                                                                                                                                                                                                                                                                                                                                                                                          | 33                                                                                           |  |  |  |

| 4.3                                                                  | FPGA attachment interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 35                                                                                           |  |  |  |

| 4.4                                                                  | FPGA in the cloud and data center                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                              |  |  |  |

|                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                              |  |  |  |

| 4.5                                                                  | ASIC Clouds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                              |  |  |  |

| 4.6                                                                  | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 40                                                                                           |  |  |  |

| СЦ                                                                   | APTER 5 OVERVIEW OF THE CLOUD-BASED FPGA CUSTOM COMF                                                                                                                                                                                                                                                                                                                                                                                                                                          | μτικά                                                                                        |  |  |  |

| CU1/                                                                 | APTER 5 OVERVIEW OF THE CLOUD-DASED FPGA COSTOM COMP                                                                                                                                                                                                                                                                                                                                                                                                                                          | UTING                                                                                        |  |  |  |

| MA                                                                   | CHINES PLATFORM                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                              |  |  |  |

| MA                                                                   | CHINES PLATFORM                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 43                                                                                           |  |  |  |

| MA<br>5.1                                                            | CHINES PLATFORM                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                              |  |  |  |

|                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 44                                                                                           |  |  |  |

| 5.1<br>5.2                                                           | FPGA Virtualization                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                              |  |  |  |

| 5.1<br>5.2<br>5.3                                                    | FPGA Virtualization                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 44<br>47<br>48                                                                               |  |  |  |

| 5.1<br>5.2<br>5.3                                                    | FPGA Virtualization<br>FPGA Cloud Architecture<br>FPGA hypervisor                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                              |  |  |  |

| <b>5.1</b><br><b>5.2</b><br><b>5.3</b>                               | FPGA Virtualization         FPGA Cloud Architecture         FPGA hypervisor         5.3.1       User-to-CCM API functions                                                                                                                                                                                                                                                                                                                                                                     |                                                                                              |  |  |  |

| <b>5.1</b><br><b>5.2</b><br><b>5.3</b>                               | FPGA Virtualization         FPGA Cloud Architecture         FPGA hypervisor         5.3.1       User-to-CCM API functions         5.3.2       User-to-Hypervisor API functions                                                                                                                                                                                                                                                                                                                | 44<br>47<br>48<br>50<br>51<br>52                                                             |  |  |  |

| <b>5.1</b><br><b>5.2</b><br><b>5.3</b><br>5<br>5                     | FPGA Virtualization         FPGA Cloud Architecture         FPGA hypervisor         5.3.1       User-to-CCM API functions         5.3.2       User-to-Hypervisor API functions         5.3.3       Hypervisor-to-Hypervisor back-end API functions                                                                                                                                                                                                                                            | 44<br>47<br>48<br>50<br>51<br>52<br>53                                                       |  |  |  |

| 5.1<br>5.2<br>5.3<br>5<br>5<br>5<br>5.4                              | FPGA Virtualization         FPGA Cloud Architecture         FPGA hypervisor         5.3.1       User-to-CCM API functions         5.3.2       User-to-Hypervisor API functions         5.3.3       Hypervisor-to-Hypervisor back-end API functions         A scenario of Launching, Using and Terminating a CCM                                                                                                                                                                               | 44<br>47<br>48<br>50<br>51<br>52<br>53<br>53                                                 |  |  |  |

| 5.1<br>5.2<br>5.3<br>5<br>5<br>5.4<br>5.5<br>5.6                     | FPGA Virtualization         FPGA Cloud Architecture         FPGA hypervisor         5.3.1       User-to-CCM API functions         5.3.2       User-to-Hypervisor API functions         5.3.3       Hypervisor-to-Hypervisor back-end API functions         A scenario of Launching, Using and Terminating a CCM         CCM Creation                                                                                                                                                          | 44<br>47<br>48<br>50<br>51<br>52<br>53<br>53<br>55<br>56                                     |  |  |  |

| 5.1<br>5.2<br>5.3<br>5<br>5<br>5.4<br>5.5<br>5.6                     | FPGA Virtualization         FPGA Cloud Architecture         FPGA hypervisor         5.3.1       User-to-CCM API functions         5.3.2       User-to-Hypervisor API functions         5.3.3       Hypervisor-to-Hypervisor back-end API functions         A scenario of Launching, Using and Terminating a CCM         CCM Creation         Properties of the Platform                                                                                                                       | 44<br>47<br>48<br>50<br>51<br>52<br>53<br>53<br>55<br>55<br>56                               |  |  |  |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.4<br>5.5<br>5.6                        | FPGA Virtualization         FPGA Cloud Architecture         FPGA hypervisor         53.1       User-to-CCM API functions         5.3.2       User-to-Hypervisor API functions         5.3.3       Hypervisor-to-Hypervisor back-end API functions         A scenario of Launching, Using and Terminating a CCM         CCM Creation         Froperties of the Platform         5.6.1                                                                                                          | 44<br>47<br>48<br>50<br>51<br>52<br>53<br>53<br>55<br>56<br>56<br>57                         |  |  |  |

| 5.1<br>5.2<br>5.3<br>5<br>5.4<br>5.5<br>5.6<br>5<br>5<br>5           | FPGA Virtualization         FPGA Cloud Architecture         FPGA hypervisor         5.3.1       User-to-CCM API functions         5.3.2       User-to-Hypervisor API functions         5.3.3       Hypervisor-to-Hypervisor back-end API functions         A scenario of Launching, Using and Terminating a CCM         CCM Creation         5.6.1         The platform computing model         5.6.2                                                                                         |                                                                                              |  |  |  |

| 5.1<br>5.2<br>5.3<br>5<br>5<br>5.4<br>5.5<br>5.6<br>5<br>5<br>5<br>5 | FPGA Virtualization         FPGA Cloud Architecture         5.3.1       User-to-CCM API functions         5.3.2       User-to-Hypervisor API functions         5.3.3       Hypervisor-to-Hypervisor back-end API functions         5.3.3       Hypervisor-to-Hypervisor back-end API functions         A scenario of Launching, Using and Terminating a CCM         CCM Creation         5.6.1       The platform computing model         5.6.2       Abstraction         5.6.3       Sharing | 44<br>47<br>48<br>50<br>51<br>52<br>53<br>53<br>55<br>55<br>56<br>56<br>57<br>58<br>58<br>58 |  |  |  |

### vii

| 6.1 Dat  | a Communications                                               | 61  |

|----------|----------------------------------------------------------------|-----|

| 6.2 Net  | work Controller                                                | 64  |

| 6.3 Stat | tic logic                                                      |     |

| 6.3.1    | Data routing                                                   |     |

| 6.3.2    | Reconfiguration management unit (RM)                           |     |

| 6.3.3    | Clock management unit (CM)                                     |     |

| 6.4 The  | wrapper's design                                               |     |

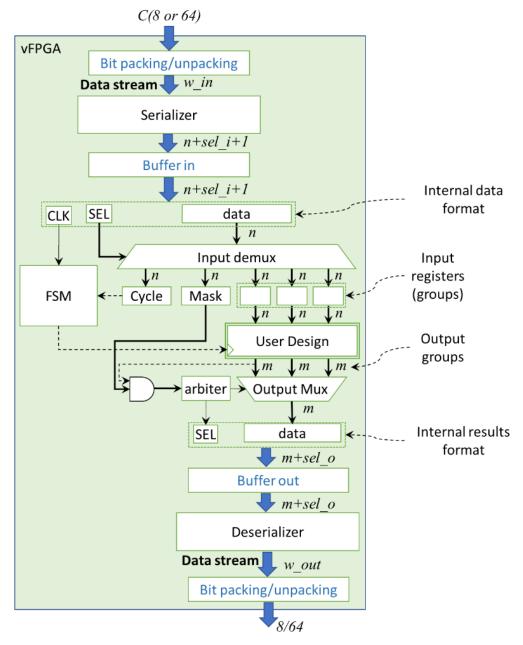

| 6.4.1    | Conceptual design of the wrapper                               | 70  |

| 6.4.2    | Wrapper components                                             | 71  |

| 6.5 Wra  | apper generation                                               | 77  |

| 6.5.1    | Parsing the XML/JSON specification file                        | 79  |

| 6.5.2    | Parsing the Vera specification file                            | 84  |

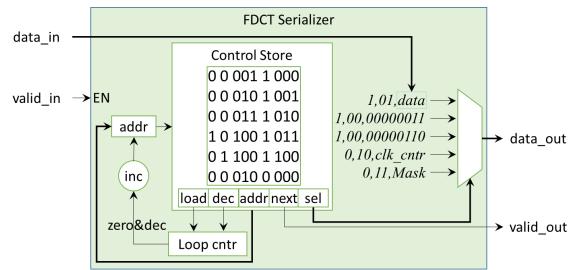

| 6.5.3    | An example for generating a serializer from a Vera description | 85  |

| 6.5.4    | Wrapper generation software                                    | 88  |

| СНАРТ    | ER 7 RESULTS AND COMPARISON                                    |     |

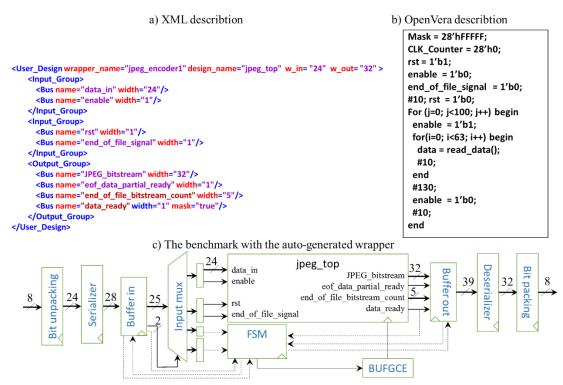

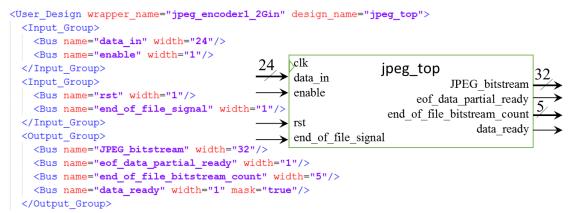

| 7.1 Ger  | nerating a wrapper for the JPEG Encode core                    | 90  |

| 7.1.1    | Preparing the XML Description File                             |     |

| 7.1.2    | User's Vera Data Specifications                                |     |

| 7.1.2    | JPEG Encoder implementation on a vFPGA                         |     |

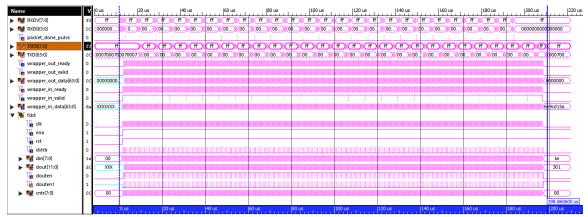

| 7.2 Sim  | ulation methodology                                            | 96  |

| 7.3 Virt | ualization Overhead Evaluation                                 |     |

| 7.4 Con  | nparisons with other platforms                                 |     |

| 7.5 vFP  | GAs versus SW-based virtual machines                           |     |

| 7.6 CCN  | ۸ platform Evaluation                                          |     |

| 7.6.1    | Experiment setup                                               |     |

| 7.6.2    | Performance Evaluation                                         |     |

| 7.6.3    | The impact of adding the AES encryption/decryption             |     |

| 7.6.4    | The impact of having multiple vFPGAs within the same FPGA      | 117 |

| 7.7 Boo  | ot time analysis                                               |     |

| СНАРТ    | ER 8 CONCLUSION                                                | 120 |

| 8.1 Plat | form Limitations                                               |     |

| 8.2 Fut  | ure work                                                       |     |

| AP  | PEN         | IDICES                                                             | 125 |

|-----|-------------|--------------------------------------------------------------------|-----|

| Α.  | De          | scription of the used Benchmarks                                   |     |

| A   | <b>.</b> 1. | JPEG Encoder Core                                                  |     |

| A   | <b>.</b> 2. | AES Core                                                           |     |

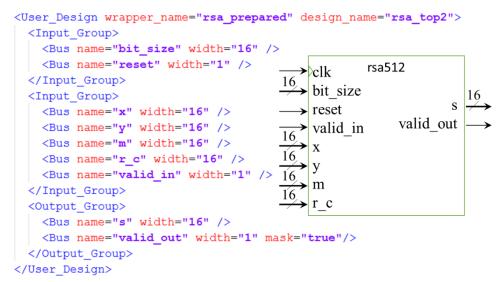

| A   | <b>.</b> 3. | RSA512 Core                                                        |     |

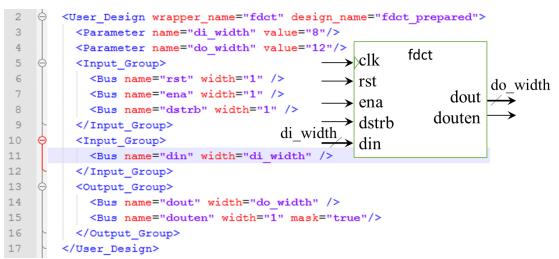

| A   | <b>.</b> 4. | FDCT Core                                                          | 130 |

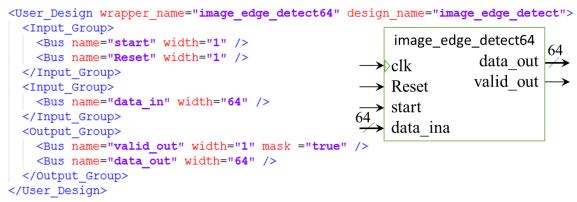

| A   | ۸.5.        | JPEG Images Edge Detection                                         | 132 |

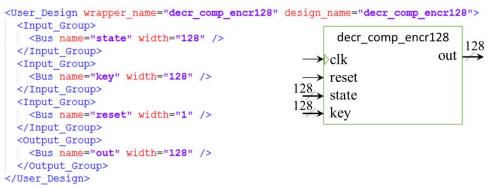

| А   | .6.         | Decrypt-Compute-Encrypt                                            | 133 |

| в.  | So          | ftware tool for Ethernet packet generation and platform test bench |     |

| C.  | Αc          | lescription of the implemented Verilog code                        | 137 |

| RE  | FER         | ENCES                                                              | 139 |

| VIT | <b>FAE</b>  |                                                                    |     |

## LIST OF TABLES

| Table 4-1: | List of notable platforms of FPGA-based processing for clouds or datacenters                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Table 5-1: | Main API function in the software library50                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| Table 6-1: | A description of the XML tags and their attributes used to describe the user hardware I/Os and their groups                                                                                                                                                                                                                                                                                                  |  |  |  |

| Table 6.2: | FDCT benchmark verification code written on OpenVera and its translation to microcode microinstructions                                                                                                                                                                                                                                                                                                      |  |  |  |

| Table 7.1: | Formatting and applying the JPEG Encoder's input data by the wrapper.<br>Four control bits are added with each input. The last column represents<br>the complete output of the serializer which is applied to the input FIFO93                                                                                                                                                                               |  |  |  |

| Table 7.2: | Virtualization overhead compared to direct implementation on an FPGA for 4 benchmarks. For the vFPGAs, the wrapper's I/O widths are 64/64 bits for all designs                                                                                                                                                                                                                                               |  |  |  |

| Table 7.3: | Comparison with notable platforms for attaching FPGAs to DCs105                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| Table 7.4: | Resource utilization of the virtualization platform on FPGA112                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| Table 7.5: | Computation time comparison for three implementations of the secure<br>image edge detection application. a) The application on a virtual<br>machine, b) The application on a server, c) The application is a CCM115                                                                                                                                                                                          |  |  |  |

| Table 7.6: | Estimation of the CCM area overhead in our platform117                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| Table 7.7: | Boot time delay components for vFPGA-CCMs with various image (bitstream) sizes. Internal configuration access port's speed is ~400MB/s                                                                                                                                                                                                                                                                       |  |  |  |

| Table 8.1: | Snapshot of the serializer's output for the JPEG encoder. Each row in the table represents one input group. The CLK column indicates whether to apply a clocking at that input or not. The SEL column represents the input group index. The table starts by setting values to the mask register and the clock counter. Then it sets values to the least frequently used signals. After that, the data starts |  |  |  |

| Table 8.2: | Snapshot of the serializer's output for the AES128. Each row in the table represents one input group. The CLK column indicates whether to apply a clocking at that input or not. The SEL column represents the input group index. The table starts by setting values to the mask register and the clock counter. Then it sets the key. After that, the data starts                                           |  |  |  |

| Table 8.3: | Snapshot of the serializer's output for the RSA512. Each row in the table represents one input group. The CLK column indicates whether to apply a clocking at that input or not. The SEL column represents the input group index. The table starts by setting values to the mask register. It then set the value of the modulus <i>m</i> . Then, it sets the <i>bit_size</i> constants. After                |  |  |  |

## LIST OF FIGURES

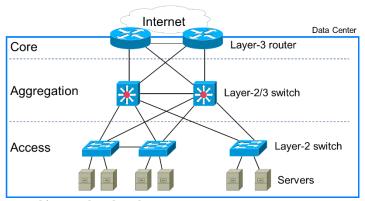

| Figure 2.1: | Data center architecture has three layers.                                                                                                                                                                                                                                                                               | .11 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

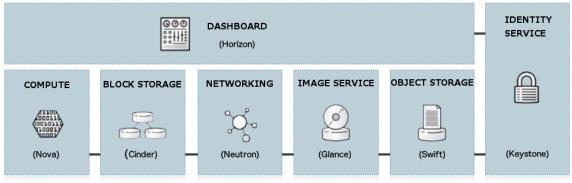

| Figure 2.2: | OpenStack core components [13].                                                                                                                                                                                                                                                                                          | .15 |

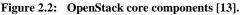

| Figure 3.1: | FPGA Architecture is a two-dimensional array of reconfigurable resources. Components on FPGA are programmable: control logic blocks (CLBs), SRAMs, DSP blocks, and interconnects [14]                                                                                                                                    | .18 |

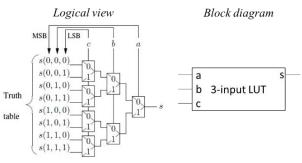

| Figure 3.2: | 3-input LUT implementations                                                                                                                                                                                                                                                                                              | .19 |

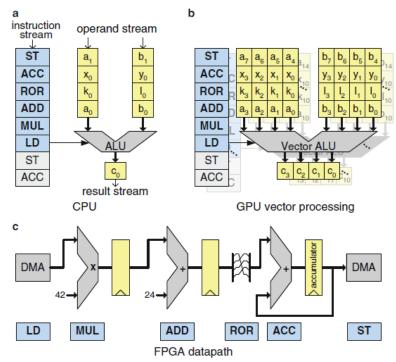

| Figure 3.3: | Compute paradigms comparison [28]. a) CPU represents the Von<br>Neumann model. b) GPU represents the vector processing model. c)<br>FPGA represents spatial computing.                                                                                                                                                   | .26 |

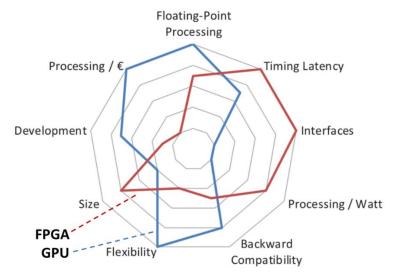

| Figure 3.4: | GPU vs FPGA qualitative comparison [5].                                                                                                                                                                                                                                                                                  | .27 |

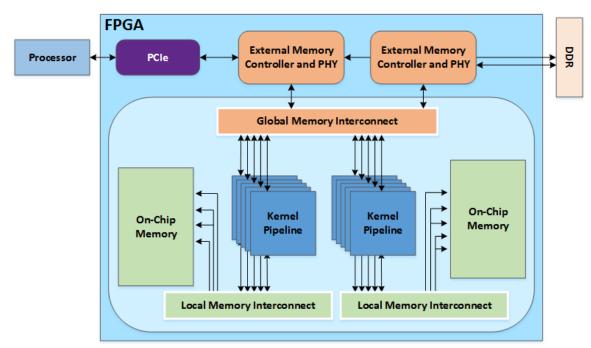

| Figure 4.1: | The architecture and design components in Intel OpenCL for FPGAs [14]                                                                                                                                                                                                                                                    | .35 |

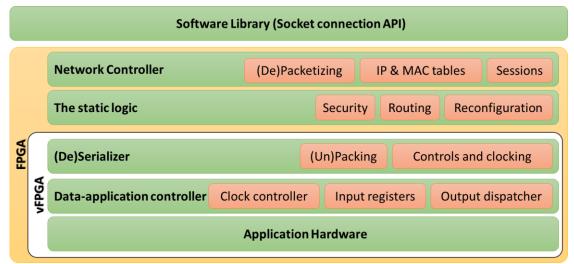

| Figure 5.1: | FPGA virtualization is based on several abstraction layers                                                                                                                                                                                                                                                               | .44 |

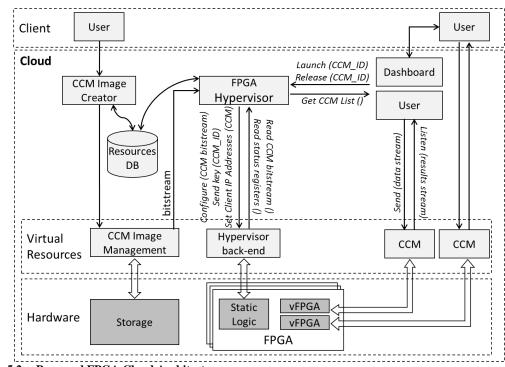

| Figure 5.2: | Proposed FPGA Cloud Architecture                                                                                                                                                                                                                                                                                         | .47 |

| Figure 5.3: | Python implementations for the functions "Send (data stream)" and "Listen_to_results (data stream)". Both functions use TCP stream socket and require the CCM IP address and port number                                                                                                                                 | .51 |

| Figure 5.4: | Hypervisor to hypervisor's backend functions uses UDP socket<br>connection. The UDP payload contains a sequence of CMD and value<br>pairs. Several commands can be sent on one UDP packet. Hypervisor<br>sends a UDP packet and hypervisor's back end reply with a UDP packet.                                           | .53 |

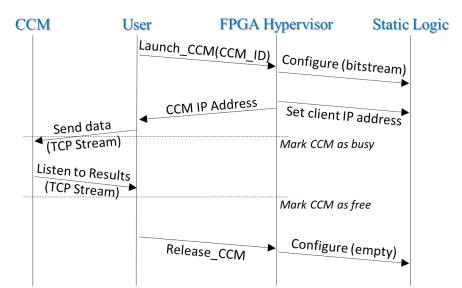

| Figure 5.5: | Scenario of using a CCM on a cloud computing system. The user issues four commands to launch, send data, receives results, and terminate CCM.                                                                                                                                                                            |     |

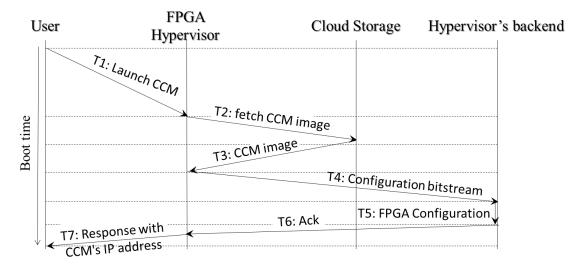

| Figure 5.6: | Scenario of using a CCM on a cloud computing system. First, the user requests to launch a CCM. The FPGA hypervisor configures a vFPGA with the CCM bitstream and returns the CCM IP address back to the user. The user interacts with the CCM by sending data and receiving results. Finally, the user releases the CCM. | .55 |

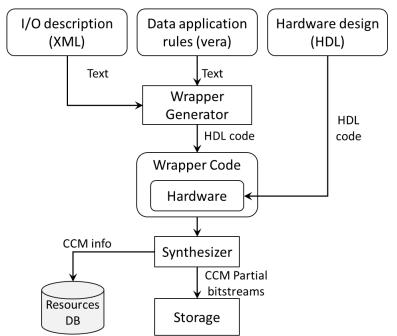

| Figure 5.7: | CCM creator receives hardware design (HLS/HDL), XML file describes<br>hardware I/Os, and Vera file describes how data is applied. Then, it and<br>creates a CCM, synthesized and generates partial bitstreams. Finally, it<br>saves the bitstreams in the cloud storage and their info in the Resources<br>database.     | .56 |

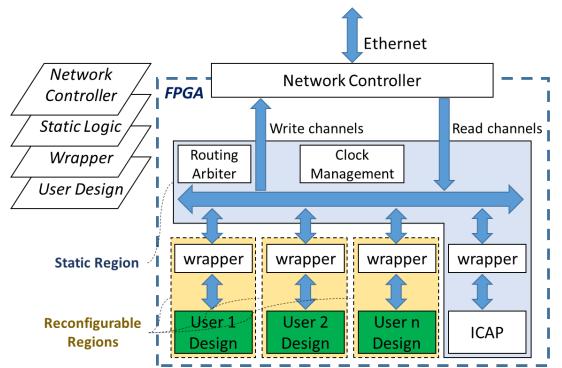

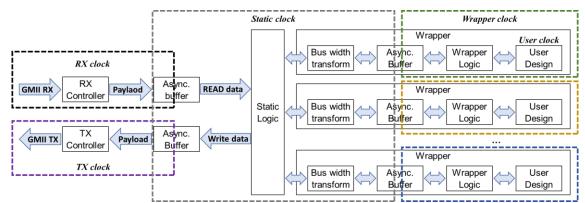

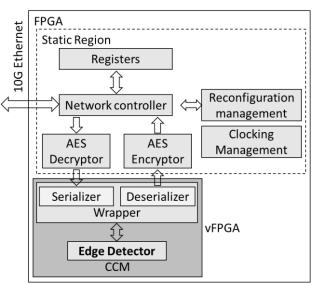

| Figure 6.1: | Virtualization platform overview. FPGA is partitioned into a static region<br>and several reconfigurable regions to be used as virtual FPGAs                                                                                                                                                                             | .61 |

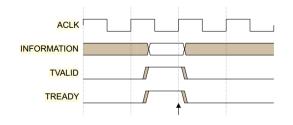

| Figure 6.2: | Timing diagram of the two-way handshaking process [48]                                                                                                                                                                                                                                                                   | .62 |

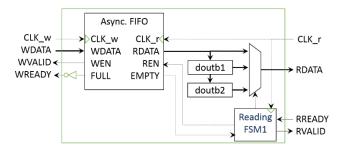

| Figure 6.3:  | BRAM-based asynchronous FIFO for transferring data across unrelated clock domains using the AXI interface                                                                                                                                                                                                                                                                                                                     |     |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

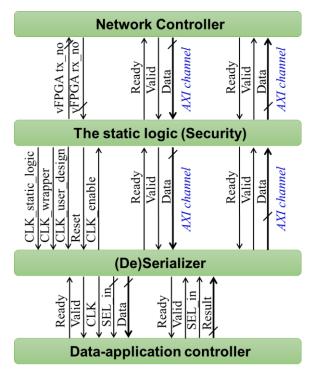

| Figure 6.4:  | Inter-layer interfaces. The interface between L1 and L2 consists of two AXI interfaces and the virtual FPGA indices. The interface between L2 and L3 consists of two AXI interfaces and clocking signals. The interface between L3 and L4 consists of two AXI interfaces whose data have the internal wrapper formats.                                                                                                        | .63 |  |  |

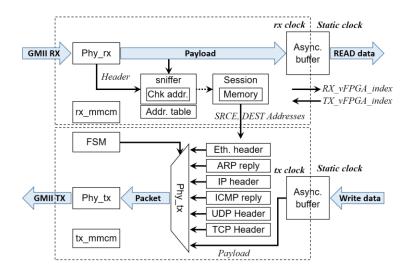

| Figure 6.5:  | The implementation of the Ethernet controller                                                                                                                                                                                                                                                                                                                                                                                 | .66 |  |  |

| Figure 6.6:  | The platform's different clock domains and the use of asynchronous<br>buffers to move data across these domains                                                                                                                                                                                                                                                                                                               | .68 |  |  |

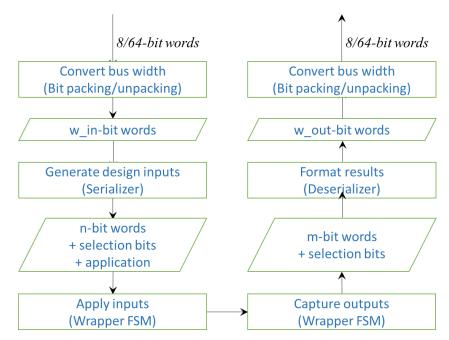

| Figure 6.7:  | A flow chart illustrating the data flow from/to the design through the wrapper. The left-hand side shows the data input flow starting from receiving a payload of a user's network packet till its application to the design. The right-hand side shows formatting and sending the results starting from capturing the outputs till generating the payload for the network packet to be sent back to the user.                | .71 |  |  |

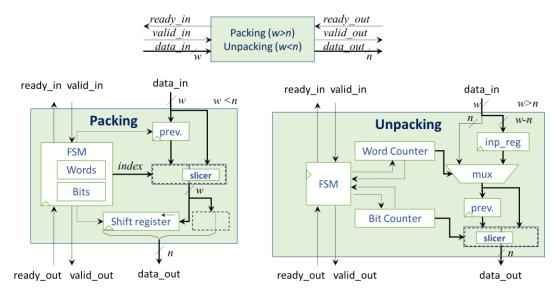

| Figure 6.8:  | Our implementation of the Packing/unpacking circuitry. If the input data width is greater than the output data width, the packing circuitry is used. If it is less, the unpacking circuitry is used. If they are equal, the packing/unpacking part is removed.                                                                                                                                                                | .72 |  |  |

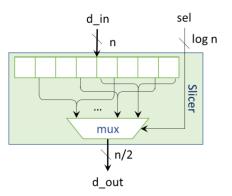

| Figure 6.9:  | Slicer is a combinational circuit that selects n/2 consecutive bits from an n-bit input                                                                                                                                                                                                                                                                                                                                       | .73 |  |  |

| Figure 6.10: | The wrapper's conceptual design                                                                                                                                                                                                                                                                                                                                                                                               | .74 |  |  |

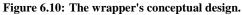

| Figure 6.11: | Diagram shows the complexity of building the wrapper state machine. If<br>the hardware has one output group, then an input can be applied while<br>capturing the output s. If the hardware has several outputs, then the<br>controller should flush out outputs before accepting new inputs. For some<br>inputs, it is required to apply several consecutive clock cycles without<br>capturing outputs or applying new inputs | .75 |  |  |

| Figure 6.12: | Verilog code of a finite state machine of a wrapper                                                                                                                                                                                                                                                                                                                                                                           | .76 |  |  |

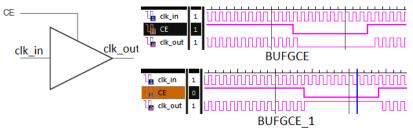

| Figure 6.13: | The controllable clock buffer allows controlling the application clock.<br>When it is enabled the application run. When it is disabled the application<br>freezes. The upper timing diagram shows a clock buffer which always<br>produces a low output when its enable signal is off. The lower timing<br>diagram shows a clock buffer which always produces a high output when<br>its enable signal is off.                  | .77 |  |  |

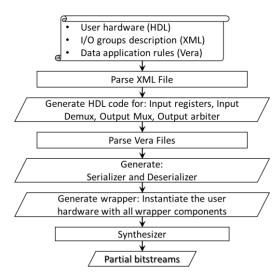

| Figure 6.14: | CCM creation flowchart.                                                                                                                                                                                                                                                                                                                                                                                                       | .78 |  |  |

| Figure 6.15: | Algorithm for generating the wrapper from the XML specification file<br>and the Vera description file                                                                                                                                                                                                                                                                                                                         | .79 |  |  |

| Figure 6.16: | Algorithm for parsing the XML specification file and generating Verilog code for the modifiable parts of the wrapper                                                                                                                                                                                                                                                                                                          | .80 |  |  |

| Figure 6.17: | The JSON schema file for describing hardware I/Os and their groups to the wrapper generator                                                                                                                                                                                                  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 6.18: | The XML schema file for describing hardware I/Os and their groups to the wrapper generator                                                                                                                                                                                                   |

| Figure 6.19: | The OpenVera code is translated to microinstructions then the Serialized is generated                                                                                                                                                                                                        |

| Figure 6.20: | The FDCT I/O specification in the XML file85                                                                                                                                                                                                                                                 |

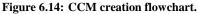

| Figure 6.21: | The serializer for the FDCT can be generated automatically from the Vera specification code Using a microcode-template. Each cycle of the microcode generates data for one input group and generates the group index and one bit represents whether to apply a clock or not for this data.   |

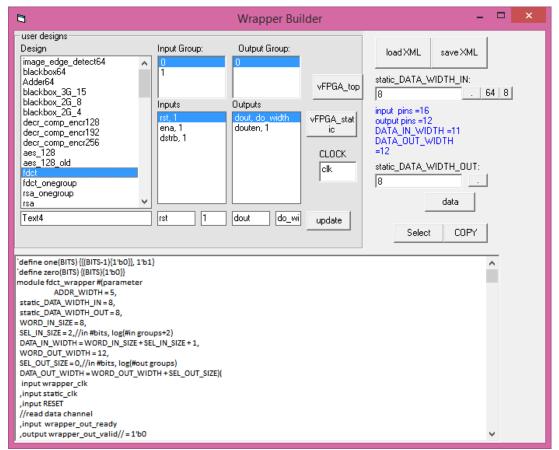

| Figure 6.22: | A snapshot of the wrapper builder software. The list on the left contains<br>several hardware cores. The wrapper is generated instantly for the<br>selected hardware core. The bottom large textbox contains the generated<br>wrapper Verilog code                                           |

| Figure 7.1:  | Generating the wrapper for the JPEG Encoder from the XML and Vera specifications                                                                                                                                                                                                             |

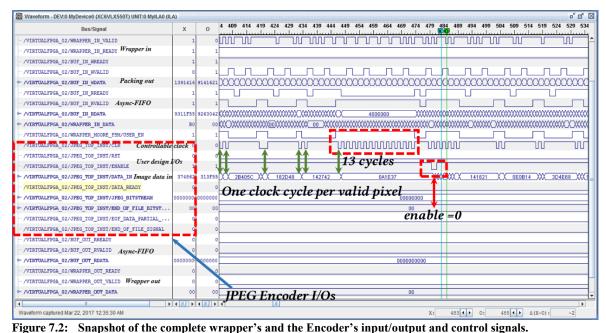

| Figure 7.2:  | Snapshot of the complete wrapper's and the Encoder's input/output and control signals95                                                                                                                                                                                                      |

| Figure 7.3:  | Packing the 8-bit wrapper inputs into the Encoder's 28-bits inputs in ~28/8 cycles per input. e.g. input sequence 7F FF D4 00 00 00 is packed into 7FFFFD 4000000 sequence                                                                                                                   |

| Figure 7.4:  | Unpacking the Encoder's 39-bits outputs to produce 8-bit wrapper's output per cycle                                                                                                                                                                                                          |

| Figure 7.5:  | Simulation methodology to simulate the whole platform. The simulator inputs are Ethernet packets. The simulator outputs are Ethernet packets97                                                                                                                                               |

| Figure 7.6:  | The simulation of the FDCT core as it is designed by the core designer.<br>The total computation time is measured to be 175,811.2 nanoseconds97                                                                                                                                              |

| Figure 7.7:  | The simulation of the FDCT core placed within a vFPGA in the implemented virtualization platform (using 10GE). The time from receiving the first Ethernet packet (RXDV changes) until the last Ethernet packet is transmitted out (TXEN changes) is measured to be 198,860.6 nanoseconds     |

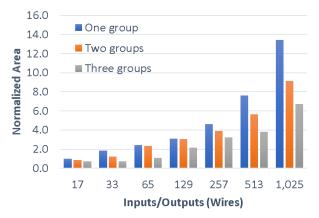

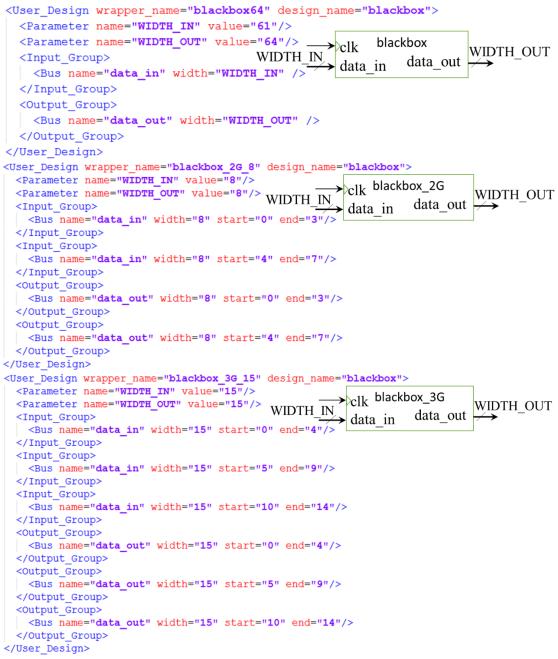

| Figure 7.8:  | Wrapper area versus the number of the application I/Os for 1, 2, 3 grouping                                                                                                                                                                                                                  |

| Figure 7.9:  | The XML specification of the input/output groups of a black box (one group, two groups, and three groups). The black box has no design inside. It is used to generate a wrapper for an assumed design with arbitrary inputs/outputs and an arbitrary number of groups. The black box is used |

|              | to evaluate the wrapper area for different number of inputs/outputs and different number of groups                                                                                                                                                                                            |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

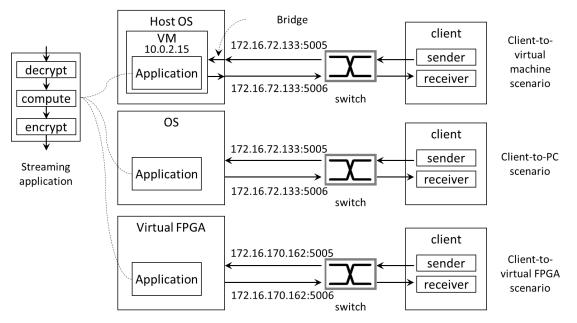

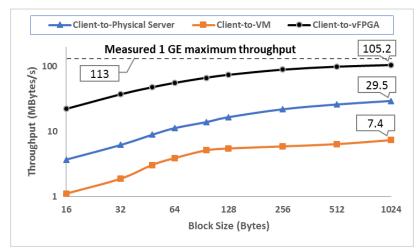

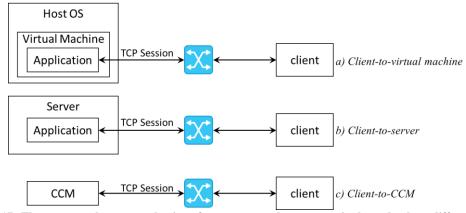

| Figure 7.10: | The three platforms used to evaluate the performance of a streaming application; (a) Running in a virtual machine, (b) directly on the physical server, and (c) on a vFPGA. A client SW sends encrypted data and receives encrypted computation results                                       |

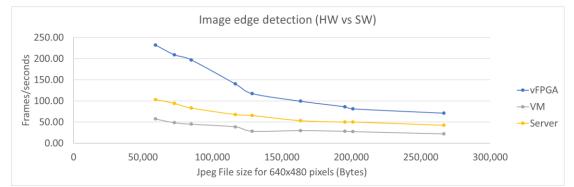

| Figure 7.11: | Streaming application throughput versus block size comparisons the proposed vFPGA platform and physical servers and virtual machines109                                                                                                                                                       |

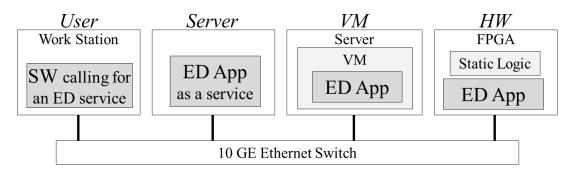

| Figure 7.12: | The experimental setup with several versions of the secure edge detection (ED) application                                                                                                                                                                                                    |

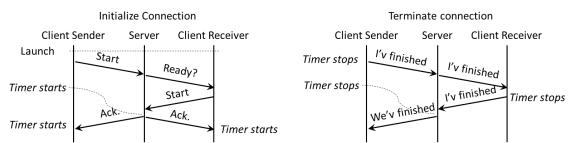

| Figure 7.13: | Synchronization process among the sender, receiver and the server. The server manages to start and to end the work in the three steps at the same time                                                                                                                                        |

| Figure 7.14: | The FPGA virtualization platform with the Edge detector application implemented as a CCM                                                                                                                                                                                                      |

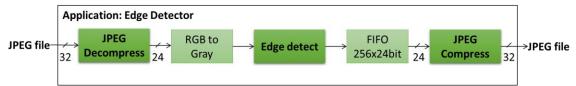

| Figure 7.15: | Image edge detection hardware uses four already-made cores; AES 128 [72], Image Compress [69], Canny Edge Detection [78], and JPEG encoder [70]112                                                                                                                                            |

| Figure 7.16: | The software version of the application "Secure image edge detection" written in Python using standard SW libraries                                                                                                                                                                           |

| Figure 7.17: | The user uses the same socket interface to request the same service hosted n three different machines; a) the service is hosted in a VM, b) the service is hosted in a server, c) the service is a CCM on virtual FPGA                                                                        |

| Figure 7.18: | Compute nodes performance comparison for a specific application. vFPGA outperforms a virtual machine and a bare-metal server                                                                                                                                                                  |

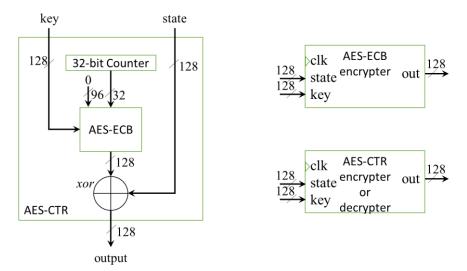

| Figure 7.19: | Using the AES-ECB core [72] to build AES-CTR that can be used as a decrypter and encrypter. By XORing the input text with the encrypted counter output we achieve a throughput of one data block per cycle. AES-CTR throughput is one block per cycle because the XORing takes one cycle only |

| Figure 7.20: | Different boot time components of a vFPGA-CCM118                                                                                                                                                                                                                                              |

| Figure 8.1:  | The XML specification of the input/output groups of the jpeg encoder core [70]126                                                                                                                                                                                                             |

| Figure 8.2:  | The XML specification of the input/output groups of the jpeg encoder core [72]                                                                                                                                                                                                                |

| Figure 8.3:  | The XML specification of the input/output groups of the rsa512 core [71]                                                                                                                                                                                                                      |

| Figure 8.4:  | The XML specification of the input/output groups of the DCT core [69].                                                                                                                                                                                                                        |

|              |                                                                                                                                                                                                                                                                                               |

| Figure 8.5:  | The XML specification of the input/output groups of the image edge detection we designed by combining several cores                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 133 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 8.6:  | The XML specification of the input/output groups of the decrypt-<br>compute-decrypt hardware designed using the AES-CTR which uses the<br>AES-ECB core [72].                                                                                                                                                                                                                                                                                                                                                                                                                                   | 133 |

| Figure 8.7:  | Generate platform test bench.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 134 |

| Figure 8.8:  | Make UDP header algorithm. The algorithm is inspired by the IP formal definition in RFC 791 [83] and the UDP formal definition in RFC 768 [84]                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 135 |

| Figure 8.9:  | Calculate IP checksum algorithm. The algorithm is inspired by the IP checksum calculation description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 136 |

| Figure 8.10: | Calculate UDP checksum algorithm. The algorithm is inspired by the UDP checksum calculation description in the UDP formal definition in RFC 768 [84].                                                                                                                                                                                                                                                                                                                                                                                                                                          | 136 |

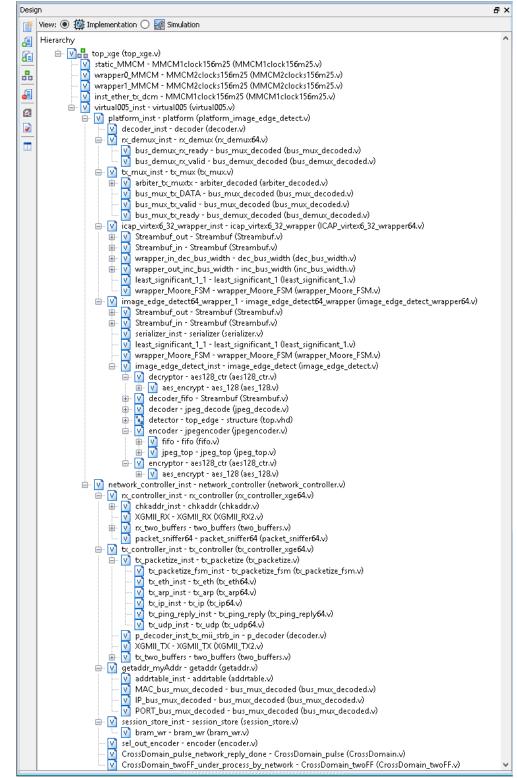

| Figure 8.11: | A snapshot shows the hierarchy and components of an implemented version of the virtualization platform. The hierarchy starts the root node "top_xge" which contains clocking resources appears in the first four nodes and the virtualization module "virt005" which contains the platform and the network controller. The platform contains data routers (mux and demux), the reconfiguration module (uses ICAP) and one vFPGA. The vFPGA contains the image_edge_detect application which uses four already-made cores; AES_128 [72], jpeg_decode [77], top_edge [78] and jpeg encoder [70]. | 138 |

## LIST OF ABBREVIATIONS

| AL   | : | Abstraction Layer                       |

|------|---|-----------------------------------------|

| ARP  | : | Address Resolution Protocol             |

| ASIC | : | Application Specific Integrated Circuit |

| AXI  | : | Advanced eXtensible Interface           |

| BRAM | : | Block RAM                               |

| ССМ  | : | Custom Computing Machines               |

| СМ   | : | Configuration Manager                   |

| CPU  | : | Central Processing Unit                 |

| DC   | : | Data Center                             |

| DHCP | : | Dynamic Host Configuration Protocol     |

| DPR  | : | Dynamic Partial Reconfiguration         |

| DSP  | : | Digital Signal Processor                |

| FF   | : | Flip-Flop                               |

| FPGA | : | Field-Programmable Gate Array           |

| GPU  | : | Graphic Processing Unit                 |

| GMII | : | Gigabit media-independent interface     |

| HLS  | : | High Level Synthesis                    |

| HW    | : | Hardware                                  |

|-------|---|-------------------------------------------|

| IOB   | : | Input Output Buffer                       |

| IP    | : | Internet Protocol                         |

| LUT   | : | Lookup Table                              |

| MII   | : | Media-independent interface               |

| PCIe  | : | Peripheral Component Interconnect Express |

| PR    | : | Partial Reconfiguration                   |

| SDN   | : | Software-defined networks                 |

| SW    | : | Software                                  |

| ТСР   | : | Transmission Control Protocol             |

| UDP   | : | User Datagram Protocol                    |

| vFPGA | : | Virtual FPGA                              |

| VM    | : | Virtual Machine                           |

| XGMII | : | 10 gigabit media-independent interface    |

### **DISSERTATION ABSTRACT**

- Full Name : Amran Abdulrahman Al-Aghbari.

- Thesis Title : Cloud-based FPGA custom computing machines.

- Major Field : Computer science and engineering.

- Date of Degree : December 2018

Field Programmable Gate Arrays (FPGAs) were first introduced as large capacity platforms of glue logic used for logic emulation and prototyping. Later, research efforts explored the use of FPGAs as computing devices. FPGAs provide excellent performance for several application domains, achieve lower power per operation, provide more deterministic latency, and can be connected to hosts or other FPGAs using different types of interfaces. On the negative side, FPGAs have a long design time in comparison with other computing machines such as CPUs and GPUs. Designing a hardware application, debugging it, and verifying its correctness requires hours and days. The resulting hardware application is both a vendor and a device-dependent. As such, developing an FPGA-based HW application is still restricted to hardware designers. For others to develop HW applications on FPGAs, the FPGA has to be properly virtualized, and its interfaces abstracted. Virtualization also enables integrating FPGAs within computing infrastructures such as data centers and clouds. In this dissertation, we introduce an FPGA virtualization platform that enables any application hardware to be ported on virtual FPGA and accessed as a standalone custom computing machine (CCM). We propose an FPGA cloud computing platform that introduces CCM as a service. A prototype of the virtualization platform has been implemented to evaluate its area, speed, and overhead. Comparison with other platforms shows that the proposed platform provides a general abstract interface to any design (not domain specific) and supports dynamic partial reconfiguration (so designs can be added to an FPGA that have other applications running) at comparable overhead to other notable platforms. Experimental results, using a streamed application in a cloud-like environment, showed that the proposed platform is a very viable computing option (in terms of throughput) for some applications compared to conventional server-based or virtual-machine based SW implementations.

# ملخَّصُ بحث درجةُ الدكتوراةِ في الفلسفةِ

- الاسم الكامل : عمر ان عبد الرحمن عبد الولي الأغبري

- عنوان الرسالة : آلات حوسبة متخصصة باستخدام الرقاقات القابلة للبرمجة (FPGAs) و دمجها في الحواية المحابية

- التخصص : علوم و هندسة الحاسب الآلى

- تاريخ الدرجة العلمية : ديسمبر 2018

عرفت المصفوفات القابلة للبرمجة في بداياتها بأنها منصات ذات كمية كبيرة من الدوائر الرقمية و استخدمت في محاكات الأجهزة الرقمية و عمل نماذج لها. الجهود البحثية الأخيرة بحثت في إستخدام الصفوفات القابلة للبرمجة كالمجهزة و إمكانية استخدامها لتنفيذ برمجيات. لقد أظهرت المصفوفات القابلة للبرمجة، أداءً عاليا في العديد من كأجهزة حوسبة و إمكانية استخدامها لتنفيذ برمجيات. لقد أظهرت المصفوفات القابلة للبرمجة، أداءً عاليا في العديد من المجالات، كما أظهرت أنها أقل استهلاكا للطاقة لكل عملية حسابية، و الزمن اللازم للحساب فيها أكثر قابلية للتحديد من عبرها، بالإضافة لقابلية ربطها بالأجهزة الأخرى عبر أنواع عديدة من المنافذ. من جهة أخرى، الوقت المستهلك من غيرها، بالإضافة لقابلية ربطها بالأجهزة الأخرى عبر أنواع عديدة من المنافذ. من جهة أخرى، الوقت المستهلك في تصميم البر امج للمصفوفات القابلة للبرمجة طويل مقارنة بأجهزة الحوسبة الأخرى كمعالجات الحواسبب أو و أيام. و هذا البرامج للمصفوفات القابلة للبرمجة والتا للبرمجة و التأكد من حملة الحرى، الوقت المستهلك و أيام. و هذا البر امج للمصفوفات القابلة للبرمجة والتالم من غيرها، بالأخرى كمعالجات الحواسبب أو و أيام. و هذا البر امج للمصفوفات القابلة للبرمجة والتارمجة و التأكد من صحة عملة ديستهلك ساعات العرابي و هذا البر نامج لا يعل إلا على نوعية المصفوفات القابلة للبرمجة التي تم تميمه عليها. و بالتالي ، تصميم و أيام. و هذا البر نامج لا يعل إلا على نوعية المصفوفات القابلة للبرمجة التي تم تمصميم عليها. و بالتالي ، تصميم معلي الموفات الباب أو من علية المرمجة إفتر المنية كما ينبغي تبسيط طرق الاتي بالذسبة لغير المختصين، و أنام. و هذا البر نامج لا يعل إلى حكرا على المختصين فيها فقط حتى الأن. بالذسبة لغير المختصين من الضروري تصميم مصفوفات البرامج على المصفوفات القابلة للبرمجة والتي أو ضعها من أجز في علية المن معاي معالي مرامج على المن روري تصميم مصفوفات البرامج على المصفوفات القابلة للبرمجة التي من أجهزة الحرى في الخرى في المختصين، و أنام روري تصميم مصفوفات القابلة للبرمجة إفتر منمية تحتوي عليه معن وري يابن معاي معالي و مالا مروري يسبم ماروري تصميم مصفوفات البرمجة واللرمجة والماني و مالم مروري معلي مالم مون وعلية المكنية لو ضعها ضمن أجهزة الحوسبة الألم مرة وي و التي مالم مرور و مام مر كزر الي أخرى من أ

نسميها خدمة جهاز حوسبة متخصص. قمنا بتنفيذ نموذج للمصفوفات القابلة للبرمجة الافتراضية بغرض تقييمها من حيث المساحة و السرعة و الكلفة، و قمنا بمقارنته مع المقترحات البحثية الشبيهة. المقارنة أظهرت أن المنصة التي نقترحها تعطي طرق اتصال أعم و بالتالي يمكنها قبول أية برامج و هي غير مقتصرة على مجال محدد من البرمجيات و كلفتها مقبولة مقارنة بالأعمال المشابهة. كما أن المنصة تدعم التركيب الجزئي في المصفوفات القابلة للبرمجة و هو يعني أن المصفوفة الواحدة يمكن تقسيمها إلى عدة منصات افتر اضية يمكن أن يتم تحميل البرامج على أي منها دون الحاجة لتوقيف جميع المنصات. في التجارب العملية، استخدمنا برامج تستخدم بيانات مستمرة في بيئة تشبه بيئة الحوسبة السحابية. أظهرت النتائج أن المنصلة المقترحة هي خيار ذو قيمة عالية جدا في مجال الحوسبة من ناحية الانتاجية لبعض التطبيقات مقارنة بالخوادم و الآلات الافتر اضلية المستخدمة حميا الموسبة من ناحية الانتاجية لبعض المنصات. في التجارب العملية، استخدمنا برامج تستخدم بيانات مستمرة في بيئة تشبه بيئة الحوسبة السحابية. أظهرت النتائج أن المنصلة المقترحة هي خيار ذو قيمة عالية جدا في مجال الحوسبة من ناحية الانتاجية لبعض التطبيقات مقارنة بالخوادم و الآلات الافتر اضلية المستخدمة حمليا كمنصات التوايز في الانتاجية البرمجيات في التجارية المقترحة بي خيار ذو قيمة عالية جدا في مجال الحوسبة من ناحية الحوسبة السحابية و مراكز البيانات.

## **CHAPTER 1**

### Introduction

#### **1.1 Motivation**

Field Programmable Gate Arrays (FPGAs) were first introduced as large capacity platforms of glue logic used for logic emulation and prototyping. Later, research efforts explored the use of FPGAs as computing devices. FPGAs reports excellent performance for AI, image processing, data compression, and other applications. By using FPGA accelerator attached to CPUs, different applications in pattern matching can become 300+ times faster, 200+ times faster for compression, 100+ times faster in machine learning and more [1]. Intel announced three powerful FPGA-based accelerator libraries [2]; 1) Intel's Convolutional Neural Networks (CNN) engine for FPGAs. 2) Real-time data analytics algorithms. 3) Data compression algorithms with dynamic compression ratios. Different Azure network relies on FPGA-powered software-defined networking (SDN) [3]. The bandwidth between two VMs inside Azure, with a 40-gigabit network adapter on each VM,

is only around 4Gbps per second; with FPGA-accelerated networking, that goes up to 25Gbps, with five to ten times less latency [3].

Excellent performance for several applications is not the only motivation for using FPGAs in computation. FPGAs are the least power consumers per operation among existing processing units such as CPUs and GPUs [4, 5]. Real-time applications prefer FPGA because their latency is deterministic with accuracy reaches to nanoseconds. FPGA can be programmed to deal with any type of interfaces and can be offered as a standalone computing device.

Unfortunately, FPGA programmability is the worst among other computing devices such as CPUs and GPUs [5]. Compiling an application code written in hardware description languages (HDL), the standard method to write designs for FPGAs, to FPGA configuration bitstream takes minutes and maybe hours (a typical FPGA design flow is explained in chapter 3). Hardware debugging and verification usually require several design changes, synthesis (compilation), and simulation that cost hours and maybe days. Due to this long design and compilation time, hardware designers tend to produce their designs as hardware cores which are simulated, verified, tested and then introduced as black boxes. Those hardware cores could be used directly for computation or as a building block within other hardware cores.

Although using FPGAs for computation succeeded for several application domains, their usage is still limited to hardware designers. Working with FPGAs requires a hardware-background which prevents many users from using FPGAs for computation purposes. A lot of work is required before having FPGAs available on the cloud for the mass. First,

FPGAs must be virtualized to be a cloud resource. Virtual FPGAs reveals the user from implementation details. There are a lot of physical details that need to be hidden from the FPGA user. FPGAs vary in their architecture, capacity, vendors, clocking resources and frequency. There are common tasks that are needed for all applications such as FPGA programming, clocking management, securing data and interfacing FPGA with the ecosystem. FPGA virtualization hides physical details and automates the frequently needed tasks. Second, the FPGA interface must be abstracted to enable FPGA to interact with the ecosystem smoothly. Each hardware core has its own interface and interfacing protocol. Using the hardware core requires following the core specifications provided by its designer. FPGA interface needs to be abstracted such that it provides FPGA that can easily hold any hardware core and let it work smoothly. Third, standard software libraries should be able to work easily with the data structures used in the ecosystem.

There is an increasing trend for using FPGAs in cloud and data centers since they provide better utilization with low power compared with the current CPU-based servers which consume excessive power with low utilization. Microsoft uses FPGAs to accelerate the Bing search [6]. It uses FPGA-based SDN to accelerate its networking operations [2]. Amazon introduced FPGA infrastructure as a service [7] two years ago. The increasing trend for using FPGAs reveals the need to virtualize FPGAs and introduce an easier method to interact with them. FPGA virtualization is the first step to introduce them as cloud computing resources. Two common approaches have emerged for attaching FPGAs to data centers (DCs); as accelerators attached to compute nodes via a local bus such as the Peripheral Component Interconnect Express (PCIe), or as stand-alone independent computing resources connected to the DC's interconnect fabric (i.e. Ethernet LAN). Since cloud computing resources are network-attached nodes, FPGAs should be networkattached devices rather than PCIe-attached ones. FPGAs should be disaggregated from CPUs, dealt with as standalone computing machines and provided as standalone cloud computing resources.

To summarize, the main motivation behind this work is to facilitate the use of custom application hardware in typical computing infrastructures such as data centers and clouds. This requires the following:

- 1) A method for deploying HW applications on any network-attached FPGA without the need to re-design or re-synthesize the application for different FPGAs,

- A method for completely abstracting hardware interfaces to enable accessing them as standalone computing machines (similar to SW application servers). Abstraction layers should be clearly identified and auto-generation tools for these layers should be provided,

- The overheads (cost/area, performance, and power) resulting from these abstraction layers must be evaluated to determine the feasibility of the whole approach,

- 4) Finally, even with virtualization and abstraction, current FPGAs are not general computing platforms. Hence suitable applications and execution models for the developed techniques must be identified.

#### **1.2** Thesis statement and contributions

The notion of building a custom computing machine (CCM) appeared to indicate creating special hardware for a specific computing task on FPGA. There are a lot of alreadydesigned hardware cores that efficiently do computations on FPGA such as crypto cores, image and video processors, arithmetic cores and machine learning cores. Some of these cores are open-source cores provided in websites such as "github.com" and "opencores.org" while other cores require licenses from the provider. Each core could be introduced as a standalone CCM accessible over the network by users with a non-hardware background. Whatever the design flow used to build hardware cores, there should be a flexible platform capable of hosting them, abstract their interfaces and deploy their services to the mass. This platform should provide flexibility by hiding hardware complexities and restricting the input method to well-known data formats used in the ecosystem such as text, images, and video streams. It should provide low power consumption since it uses FPGAs only without the help of an external CPU-based controller. The hardware core should also maintain its high performance when it is hosted on the platform. The platform should virtualize FPGAs, abstract their interface and enable integrating them on data centers and introducing them as cloud services. The process of accessing and using CCMs should be automated. The resulting CCM should interact with the user using a software library that can be integrated with the high-level programming language (HLL) used by the user.

The goal of this dissertation is to develop a new methodology for using FPGA for computation in cloud and data centers. Here, we outline the contributions of this dissertation as follows: