# HARDWARE-BASED SOLUTIONS FOR SECURING USERS' DATA IN PUBLIC CLOUDS

BY

#### MOHAMMED AL-ASALI

A Dissertation Presented to the DEANSHIP OF GRADUATE STUDIES

# KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

# **DOCTOR OF PHILOSOPHY**

In

COMPUTER SCIENCE AND ENGINEERING

**MAY 2017**

#### KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

#### DHAHRAN-31261, SAUDI ARABIA

#### **DEANSHIP OF GRADUATE STUDIES**

This thesis, written by **Mohammed Al-Asali** under the direction of his thesis advisor and approved by his thesis committee, has been presented and accepted by the Dean of Graduate Studies, in partial fulfillment of the requirements for the degree of **DOCTOR OF PHILOSOPHY IN COMPUTER SCIENCE AND ENGINEERING.**

/ Dr. Adel F. Ahmed

Department Chairman

Prof. Salam A. Zummo

Dean of Graduate Studies

GRADUA

14/9/17

Date

Dr. Muhammad E. S. Elrabaa (Advisor)

Dr. Marwan H. Abu-Amara (Member)

Ladin Lait

Prof. Sadiq M. Sait (Member)

Dr. Aiman H. El-Maleh (Member)

Dr. Tarek Helmy El-Basuny (Member)

larac Hels

© Mohammed Al-Asali

2017

To

my parents

#### ACKNOWLEDGMENTS

I would like to thank King Fahd University of Petroleum and Minerals for offering me the opportunity to pursue my graduate and undergraduate studies and for supporting this research.

I would like to express my deep appreciation and heartfelt gratitude to my advisor Dr. Muhammad Elrabaa for his invaluable guidance and infinite patience. He has helped me improve my research and technical writing skills. I have learned a lot of valuable lessons from him and I hope to continue working with him in future.

I would like to thank my committee members Dr. Marwan Abu-Amara, Prof. Sadiq Sait, Dr. Aiman El-Maleh, and Dr. Tarek Helmy EL-Basuny for their valuable comments and suggestions. I especially thank Dr. Marwan Abu-Amara for his valuable time and for his reviews, support and guidance in the field of data security, and Prof. Sadiq Sait for his comments and advices; I learnt a lot while working with him in the CCITR center.

I am thankful to my colleagues and friends: Amran Al-Aghbari, Feras Chikh Oughali, Asim Al-Mekhlafy, Zaid alyafey, Abdullah Al-Sermy, Mohammed Yaqot and Abdullah Alqubalee for their support and valuable information. I also thank Ken Eguro from Microsoft research for his suggestions and comments and Jonathan Dawson for his time in troubleshooting the Chips 2.0 compiler and the Ethernet controller.

# TABLE OF CONTENTS

| ACI  | KNOWLEDGMENTS                                              | V    |

|------|------------------------------------------------------------|------|

| TA   | BLE OF CONTENTS                                            | VI   |

| LIS  | T OF TABLES                                                | X    |

| LIS  | T OF FIGURES                                               | XI   |

| LIS  | T OF ABBREVIATIONS                                         | .XV  |

| AB   | STRACTX                                                    | VIII |

| سالة | ملخص الر                                                   | .XX  |

| 1    | CHAPTER INTRODUCTION                                       | 1    |

| 1.1  | Motivation                                                 | 1    |

| 1.2  | Problem Definition and Dissertation Contributions          | 2    |

| 1.3  | Dissertation Outline                                       | 4    |

| 2    | CHAPTER BACKGROUND                                         | 6    |

| 2.1  | Overview of Cloud Architectures and Management             | 6    |

| 2.2  | Overview of Attack Models and Insider Attacks in the Cloud | 10   |

| 2   | 2.2.1 | Cryptographic Attacks                                | 10         |

|-----|-------|------------------------------------------------------|------------|

| 2   | 2.2.2 | Network Attacks                                      | 12         |

| 2   | 2.2.3 | Physical Attacks                                     | 14         |

| 2   | 2.2.4 | Insider Attacks in the Cloud                         | 16         |

| 2   | 2.2.5 | Cryptographic Algorithms for Cloud Computing         | 17         |

| 2.3 | Trust | ed Computing                                         | 19         |

| 2   | 2.3.1 | Trusted Platform Module                              | 20         |

| 2   | 2.3.2 | Intel Trusted Execution Technology                   | 22         |

| 2   | 2.3.3 | Intel Software Guard Extensions (SGX)                | 23         |

| 2.4 | Physi | cally Unclonable Functions                           | 27         |

|     |       |                                                      |            |

| 2.5 | Proxy | y Re-encryption                                      | 30         |

| 3   | CHA   | APTER LITERATURE REVIEW                              | 33         |

| 3.1 | Prote | ecting Users' Data from Other Users                  | 33         |

| 3.2 | Prote | ecting Users' Data from Cloud Providers              | 36         |

| 3.3 | Trust | ed Computing in the Cloud                            | 40         |

| 3   | 3.3.1 | Intel Software Guard Extensions                      | 43         |

| 3.4 | Secui | re Processors                                        | 44         |

| 3.5 | Sumr  | mary and Discussion                                  | 46         |

| 4   | CHA   | APTER SECURING CLIENT DATA IN THE CLOUD USING FPGAS5 | 50         |

| 41  | latus | duction                                              | <b>5</b> 1 |

| 4.2 | The   | Proposed Scheme for Securing Client Data in the Cloud     | 52   |

|-----|-------|-----------------------------------------------------------|------|

|     | 4.2.1 | Preliminary                                               | 53   |

|     | 4.2.2 | FPGA Static Logic                                         | 54   |

|     | 4.2.3 | The Overall Framework                                     | 55   |

|     | 4.2.4 | The Security Protocol                                     | 56   |

|     | 4.2.5 | The Masking Circuitry                                     | 60   |

|     | 4.2.6 | Security Analysis                                         | 62   |

| 4.3 | Expe  | rimental Results                                          | 70   |

|     | 4.3.1 | Background on OpenStack                                   | 70   |

|     | 4.3.2 | Testbed Implementation                                    | 73   |

| 4.4 | Clier | nt's Circuit Intellectual Properties on the Cloud         | 92   |

| 4.5 | Cond  | clusions                                                  | 94   |

| 5   | CHA   | APTER SECURE DATA PROCESSING FOR CLOUD-INTEGR             | ATED |

| IN  | TERN  | ET OF THINGS USING FPGAS                                  | 95   |

| 5.1 | Intro | duction                                                   | 96   |

| 5.2 | Clou  | d-Integrated IoT Security Models                          | 98   |

| 5.3 | The   | Proposed Scheme                                           | 101  |

|     | 5.3.1 | Description of the Proposed Symmetric Proxy Re-encryption | 104  |

|     | 5.3.2 | The Proposed Security Protocol                            | 107  |

|     | 5.3.3 | Security Analysis                                         | 113  |

| 5.4 | Resu  | ılts and Discussion                                       | 116  |

|     |       | FPGA Implementation                                       |      |

|     | フ・サ・エ | UA                                                        |      |

| 5.4.2  | PRE Implementation                                    | 123       |

|--------|-------------------------------------------------------|-----------|

| 5.4.3  | Performance Evaluation                                | 124       |

| 5.5 Co | onclusions                                            | 128       |

| 6 CI   | HAPTER CONCLUSION AND FUTURE WORK                     | 129       |

| REFER  | RENCES                                                | 131       |

| APPEN  | NDICES                                                | 154       |

| APPEN  | NDIX A: FPGA IMPLEMENTATION AND SIMULATION            | 154       |

| a. Cli | ient Data Protection Scheme Components                | 154       |

| b. Io  | T Scheme Implementation Related Components:           | 165       |

| APPEN  | NDIX B: PROVERIF CODE FOR THE CLIENT SENSITIVE DATA P | ROTECTION |

| PROT   | OCOL                                                  | 170       |

| APPEN  | NDIX C: PROVERIF CODE FOR THE IOT SENSITIVE DATA P    | ROTECTION |

| PROT   | OCOL                                                  | 174       |

| APPEN  | NDIX D: PYTHON SCRIPTS                                | 176       |

| VITAE  |                                                       | 180       |

# LIST OF TABLES

| Table 1: Summery of SW approaches targeting data protection in the cloud            |

|-------------------------------------------------------------------------------------|

| Table 2: Summery of existing secure processors                                      |

| Table 3: Summery of existing approaches that can be utilized for data protection in |

| the cloud                                                                           |

| Table 4: Attack types and our countermeasures                                       |

| Table 5: Static Logic resource consumption                                          |

| Table 6: Boot time (in seconds) for different virtual machine sizes on the          |

| implemented OpenStack cloud                                                         |

| Table 7: The image processor resource utilization                                   |

| Table 8: Performance comparison with Intel SGX                                      |

| Table 9: Summery of countermeasure against most popular attacks                     |

| Table 10: Resource utilization of the Static Logic                                  |

| Table 11: keys and hash values Examples                                             |

| Table 12: FPGA resource usage by the PRE Logic                                      |

# LIST OF FIGURES

| Figure 1: Cloud computing architecture [191]                                      | . 7 |

|-----------------------------------------------------------------------------------|-----|

| Figure 2: Business model of cloud computing                                       | 8   |

| Figure 3: Percentage of use of various encryption algorithms in the cloud         | 18  |

| Figure 4: Trusted platform proves to a remote data owner that it is communicating |     |

| with the right container [40]2                                                    | 23  |

| Figure 5: Creating an enclave [41]                                                | 24  |

| Figure 6: Copying enclave pages to the EPC [41]                                   | 25  |

| Figure 7: Enclave instructions [41]                                               | 26  |

| Figure 8: Code/data are encrypted outside the CPU package [41]                    | 27  |

| Figure 9: PUFs challenge response                                                 | 28  |

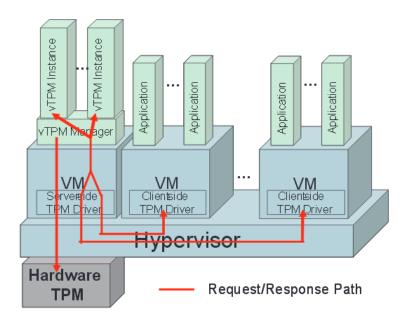

| Figure 10: Virtual TPM Architecture of [115].                                     | 12  |

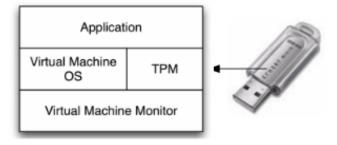

| Figure 11: The abstracted architecture of the trusted extension device (TED)      | 12  |

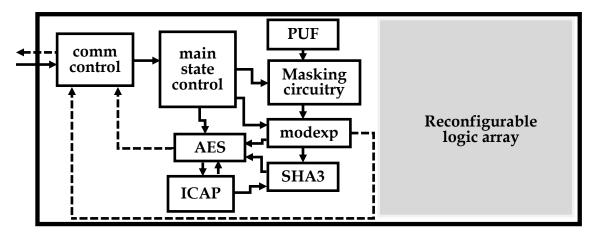

| Figure 12: The proposed FPGA structure and the components of the static logic.    |     |

| Dotted lines represent outputs5                                                   | 55  |

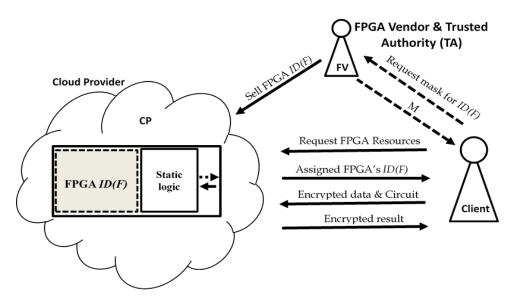

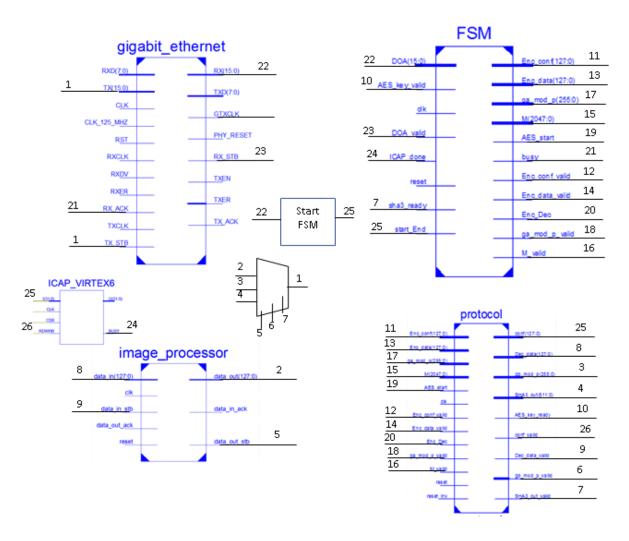

| Figure 13: The proposed framework of the scheme.                                  | 56  |

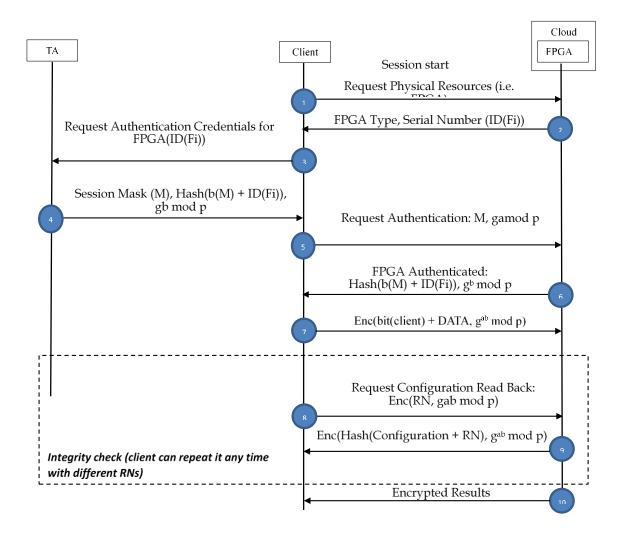

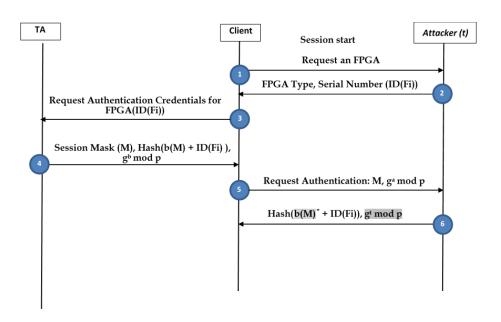

| Figure 14: The protocol sequence diagram.                                         | 59  |

| Figure 15: A variant of the protocol. Double hashing is computed by the FPGA and  |     |

| the client to avoid sending g <sup>b</sup> mod p by the TA                        | 50  |

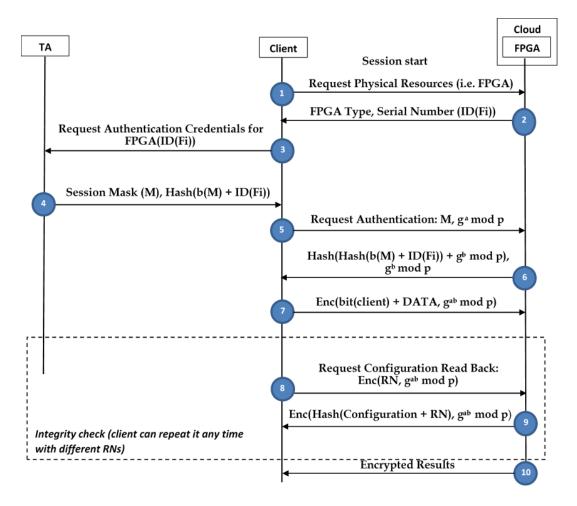

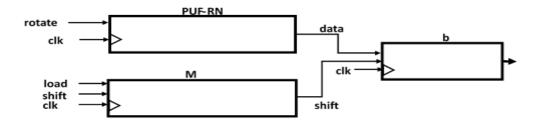

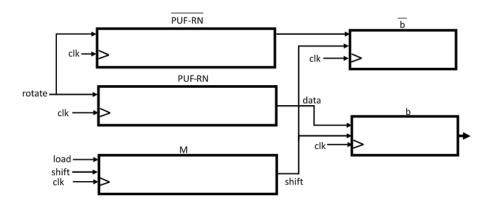

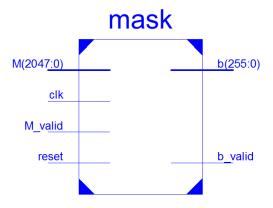

| Figure 16: The masking circuitry                                                  | 51  |

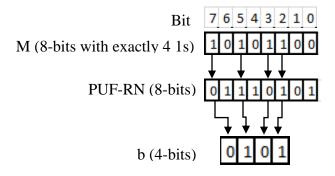

| Figure 17: An example of producing an L-bits b from n-bits PUF-RN and M; n in     |     |

| this example equals 8 and L equals 4                                              | 51  |

| Figure 18: FPGA impersonation prevention.                                         | 53  |

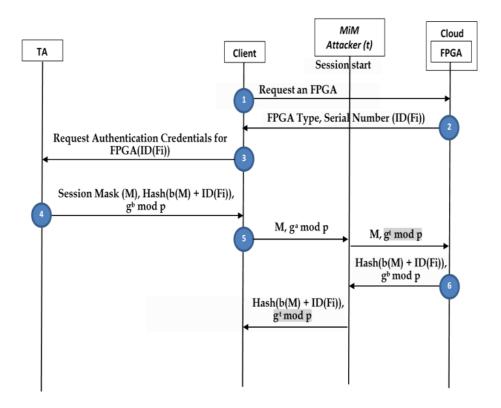

| Figure 19: Man-in-the-middle attack prevention.                                   | 54  |

| Figure 20: A masking circuitry resistant to physical attacks                                                                                                                                                                                                                                     | . 65 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

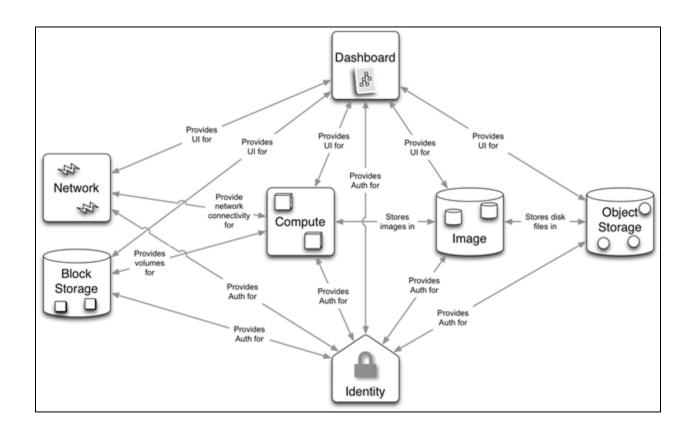

| Figure 21: OpenStack Architecture shows the seven main components of OpenStack                                                                                                                                                                                                                   |      |

| and communication between them [28]                                                                                                                                                                                                                                                              | . 72 |

| Figure 22: Xilinx Virtex 6 XC6VLX550T board                                                                                                                                                                                                                                                      | . 75 |

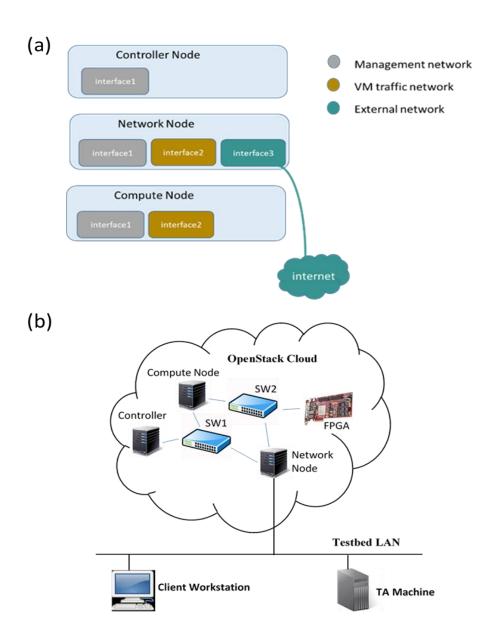

| Figure 23: The implemented OpenStack cloud. (a) OpenStack Cloud implementation logical architecture, (b) OpenStack Cloud implementation physical                                                                                                                                                 | 77   |

| implementation                                                                                                                                                                                                                                                                                   |      |

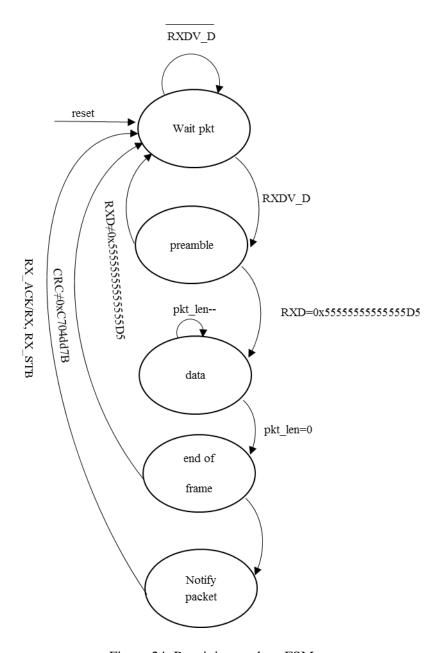

| Figure 24: Receiving packets FSM                                                                                                                                                                                                                                                                 | . 79 |

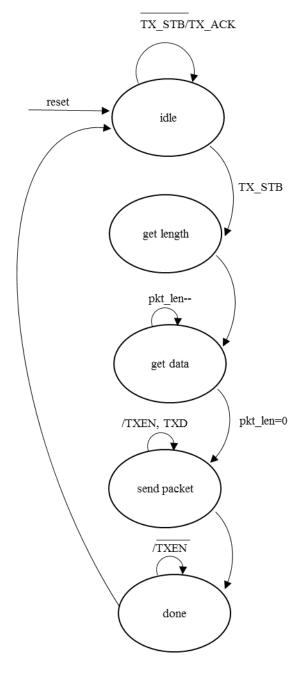

| Figure 25: Sending packets FSM                                                                                                                                                                                                                                                                   | . 80 |

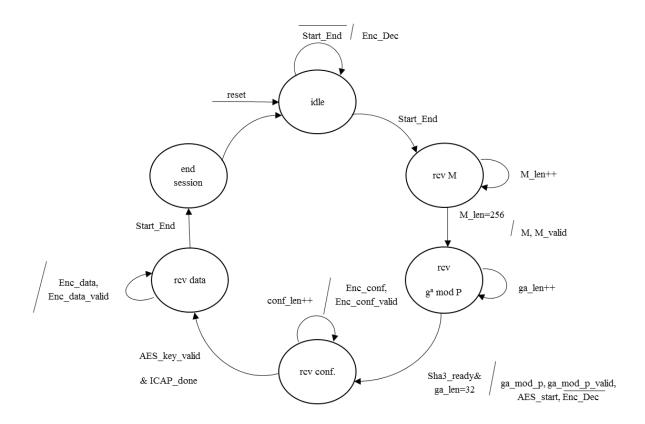

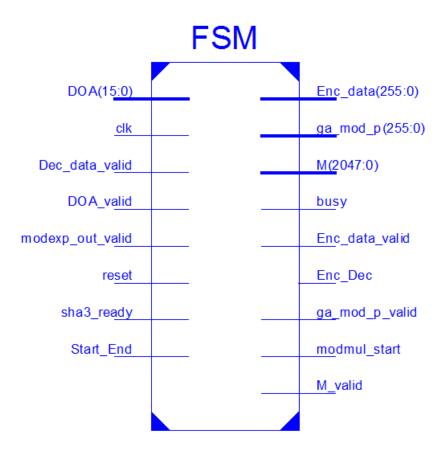

| Figure 26: Main FSM                                                                                                                                                                                                                                                                              | . 81 |

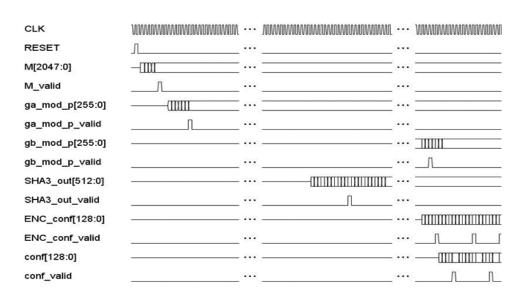

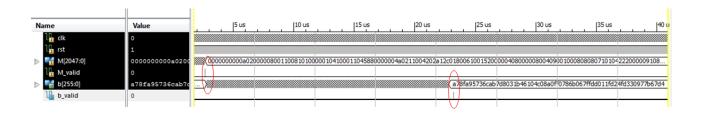

| Figure 27: The expected behavior of the Static Logic.                                                                                                                                                                                                                                            | . 85 |

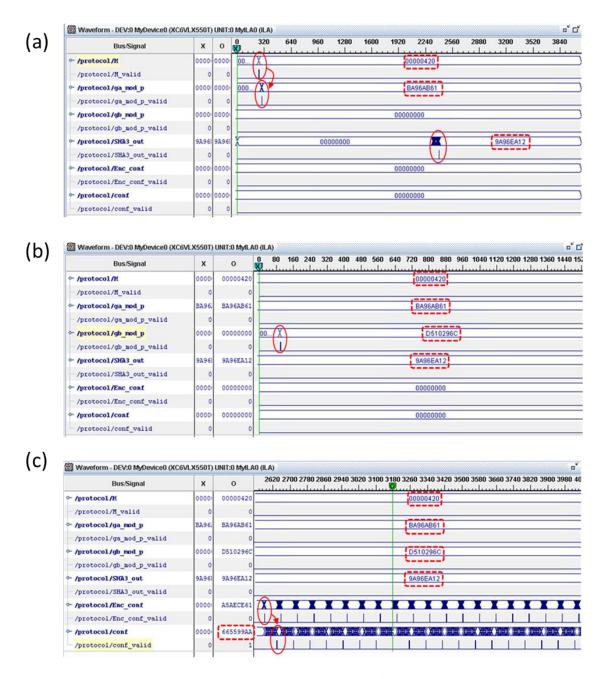

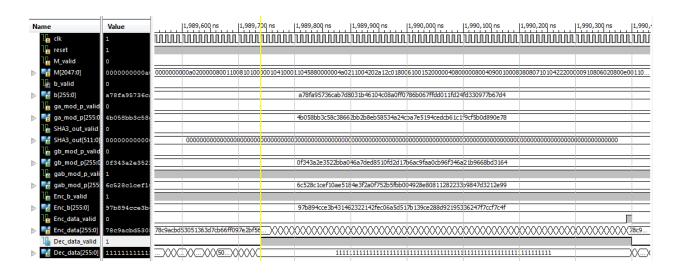

| Figure 28: Chipscope screenshots showing the various signals of the implemented Static Logic. (a) Receiving M, ga mod p and producing the hash value, (b) gb mod p generation, (c) Receiving the encrypted partial configuration. The output cursor points to the beginning of the configuration |      |

| (665599AA)                                                                                                                                                                                                                                                                                       | . 86 |

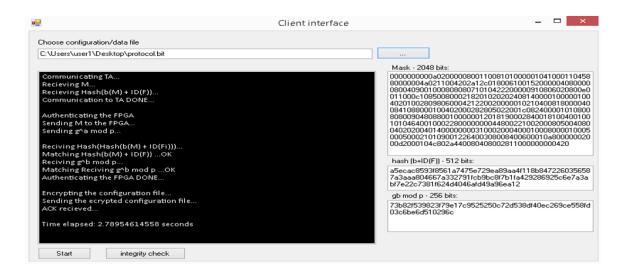

| Figure 29: The user C# interface showing the message exchanged during session establishment                                                                                                                                                                                                      | . 88 |

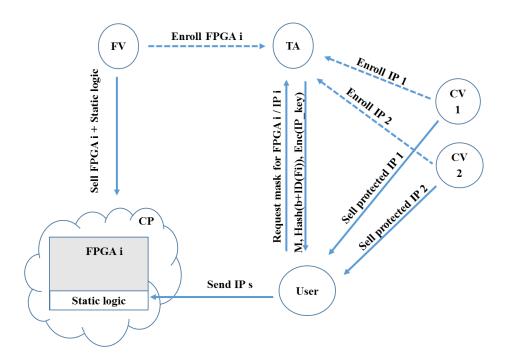

| Figure 30: The framework for protecting IPs in the cloud                                                                                                                                                                                                                                         | . 93 |

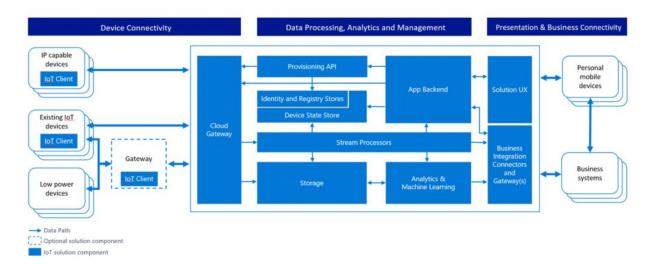

| Figure 31: Microsoft's Internet of Things security architecture [172]                                                                                                                                                                                                                            | 100  |

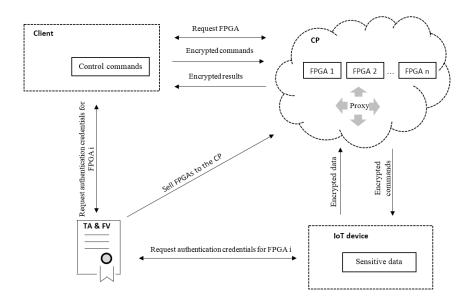

| Figure 32: The framework of the proposed scheme.                                                                                                                                                                                                                                                 | 104  |

| Figure 33: The proposed symmetric proxy re-encryption                                                                                                                                                                                                                                            | 107  |

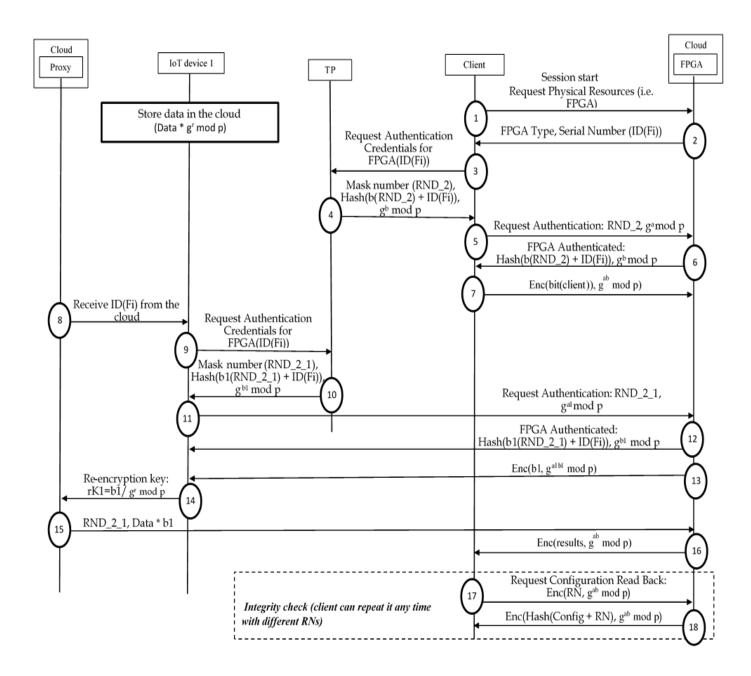

| Figure 34: The sequence diagram of the protocol.                                                                                                                                                                                                                                                 | 111  |

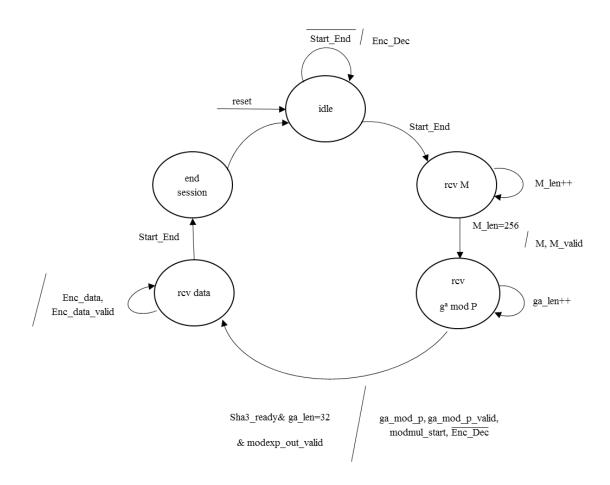

| Figure 35: Main FSM of the IoT scheme.                                                                                                                                                                                                                                                           | 117  |

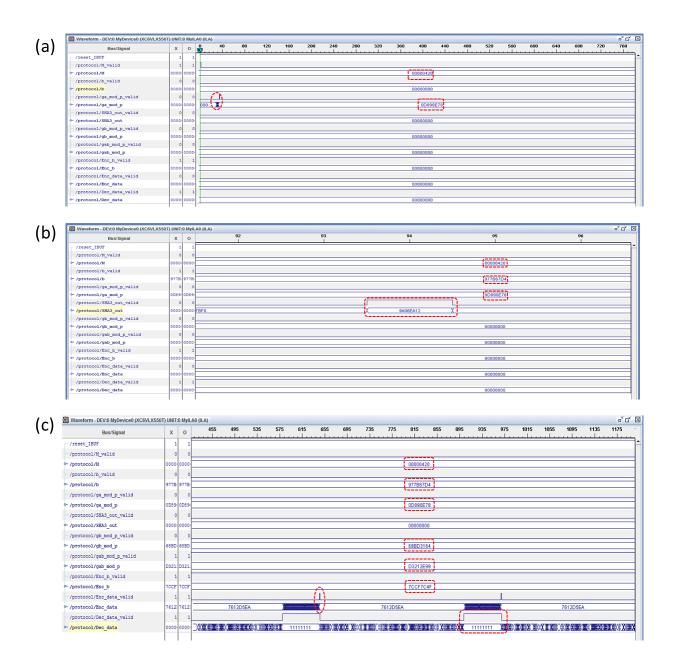

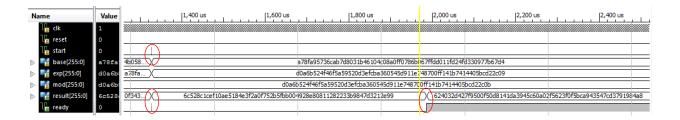

| Figure 36: Chipscope screenshots showing the operations of the implemented Static Logic on the FPGA. (a) Receiving M. ga mod p. (b) Producing b and the                                                                                                                                          |      |

| hash values, (c) Producing gb mod p, gab mod p, encrypted b and                                                                                                                            |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| receiving the encrypted data and decrypting it.                                                                                                                                            | 122 |

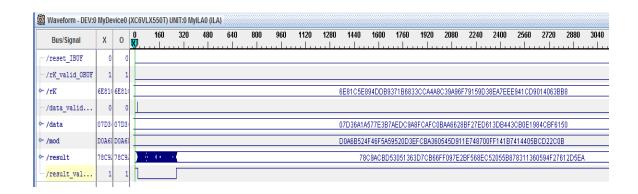

| Figure 37: Chipscope image showing the operations of the PRE                                                                                                                               | 124 |

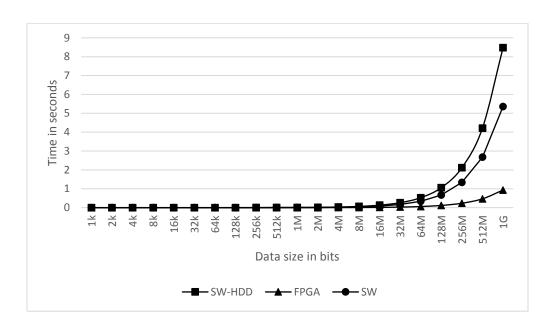

| Figure 38: Time comparison of the PRE FPGA implementation and the SW PRE. In the SW implementation, the data is read from the memory and SW-HDD means that the data is read from the disk. |     |

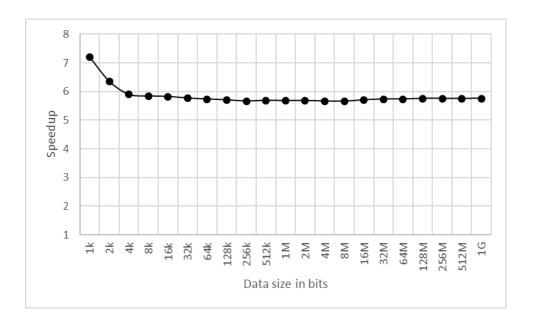

| Figure 39: The speedup obtained by our PRE FPGA implementation over PRE SW implementation. The data is read from the memory.                                                               |     |

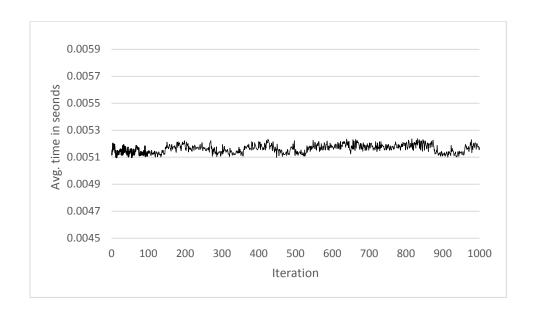

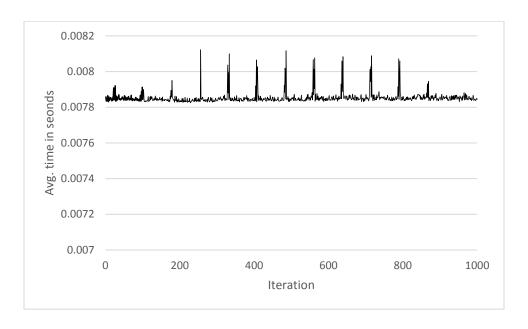

| Figure 40: The time of the python PRE over 1000 runs. The data is read from the memory.                                                                                                    |     |

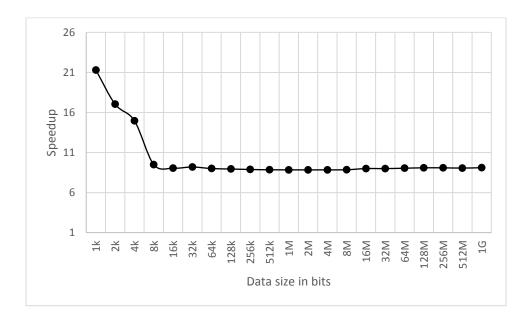

| Figure 41: The speedup obtained by our PRE FPGA implementation over PRE SW implementation. The data is read from the disk.                                                                 |     |

| Figure 42: The time of the python PRE over 1000 runs. The data is read from the disk                                                                                                       |     |

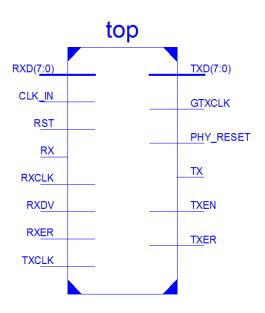

| Figure A 1: Top module inputs/outputs                                                                                                                                                      | 154 |

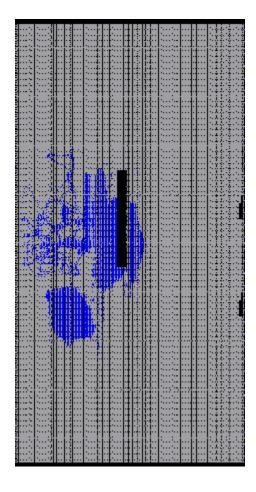

| Figure A 2: Implementation of the design placed in Xilinx Virtex 6 device                                                                                                                  | 155 |

| Figure A 3: Simulation of the top module of the design                                                                                                                                     | 155 |

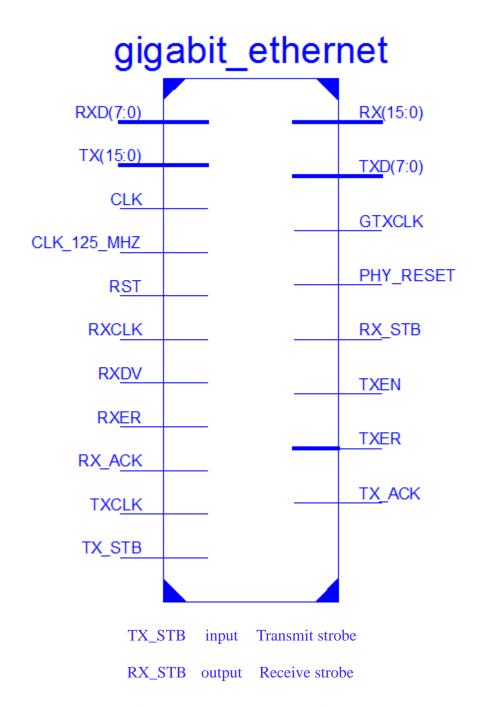

| Figure A 4: Ethernet controller block                                                                                                                                                      | 156 |

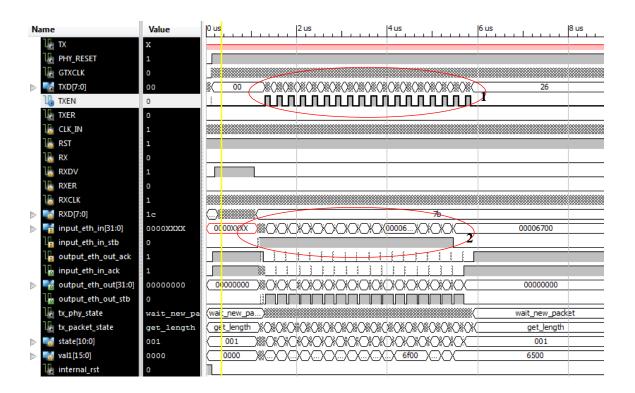

| Figure A 5: Ethernet controller simulation (1) transmitting a packet (2) receiving a packet.                                                                                               |     |

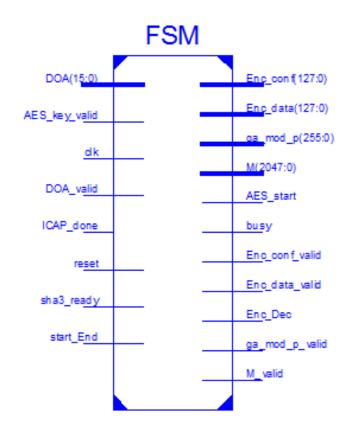

| Figure A 6: Main FSM module                                                                                                                                                                | 158 |

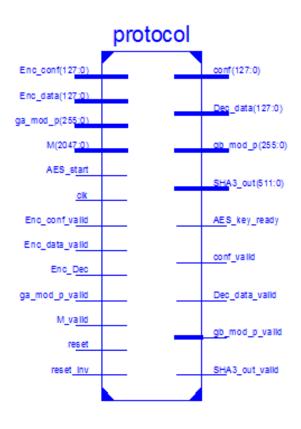

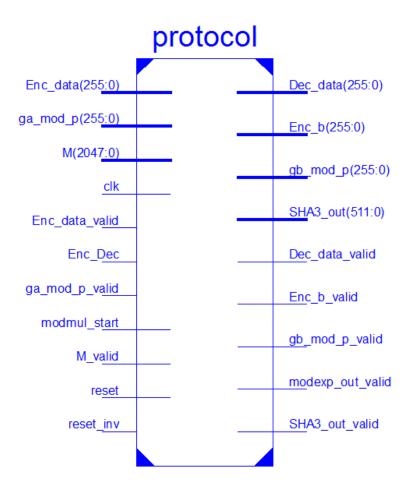

| Figure A 7: Protocol block and inputs/outputs                                                                                                                                              | 159 |

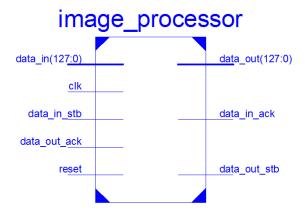

| Figure A 8: Image processor module                                                                                                                                                         | 159 |

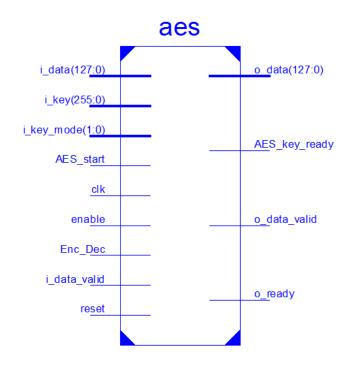

| Figure A 9: AES module                                                                                                                                                                     | 160 |

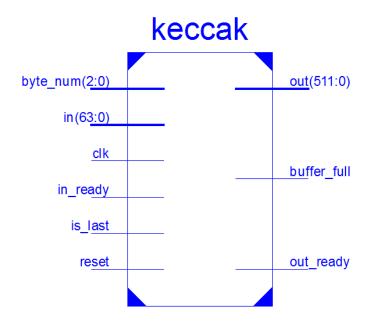

| Figure A 10: SHA3 module                                                                                                                                                                   | 161 |

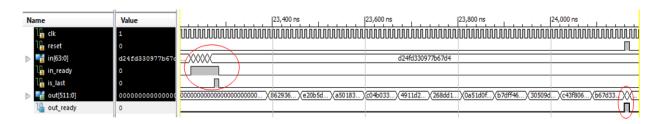

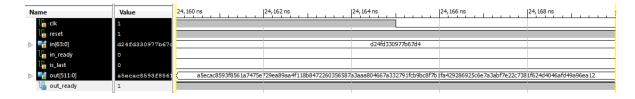

| Figure A 11: The operations of SHA3                                                                                                                                                        | 161 |

| Figure A 12: The output of SHA3 when out_ready goes high                                     | 161 |

|----------------------------------------------------------------------------------------------|-----|

| Figure A 13: The result of SHA3                                                              | 162 |

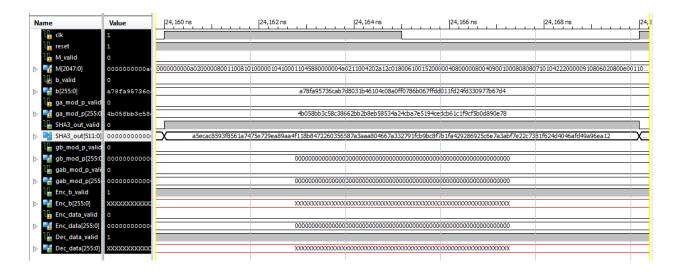

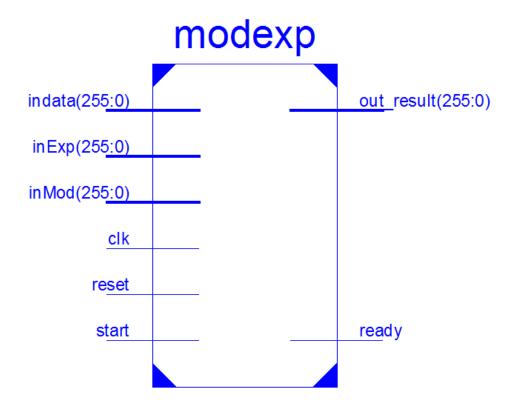

| Figure A 14: Modular exponentiation module                                                   | 162 |

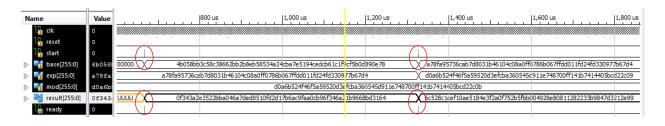

| Figure A 15: The operations of modexp, producing 3 <sup>b</sup> mod p (b is exp and p is mod |     |

| in the figure)                                                                               | 163 |

| Figure A 16: The operations of modexp, producing 3 <sup>ab</sup> mod p                       | 163 |

| Figure A 17: Masking circuitry module                                                        | 163 |

| Figure A 18: The operations of the masking circuitry                                         | 163 |

| Figure A 19: Simplified view of the top components                                           | 164 |

| Figure A 20: Main FSM module                                                                 | 165 |

| Figure A 21: Protocol module                                                                 | 166 |

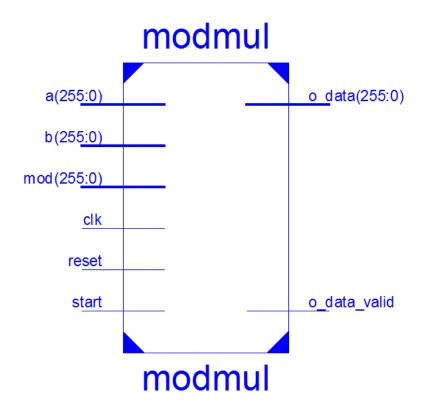

| Figure A 22: Modular multiplication module                                                   | 167 |

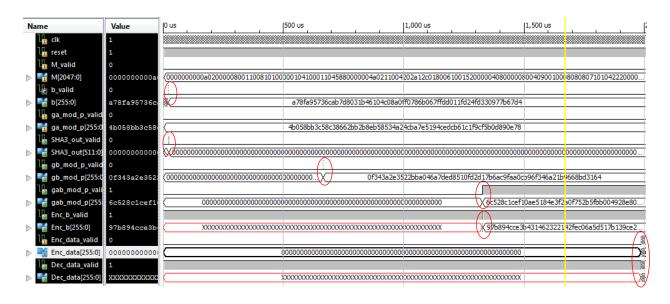

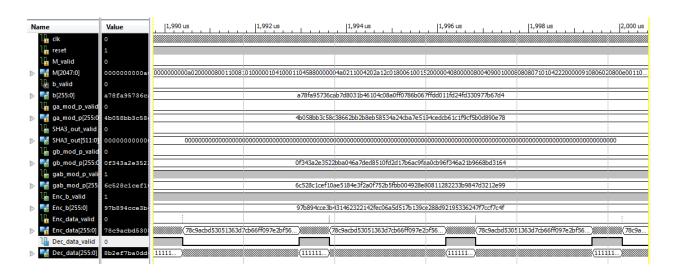

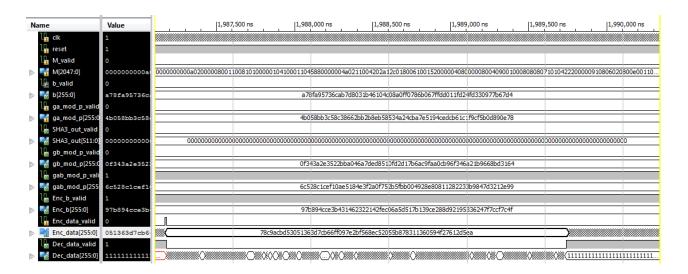

| Figure A 23: Encrypting and decrypting data; all other values are also shown such as         |     |

| M, b, etc                                                                                    | 167 |

| Figure A 24: The value of the encrypted data zoomed                                          | 168 |

| Figure A 25: The value of decrypted data zoomed                                              | 168 |

| Figure A 26: The operations of modexp, producing the multiplicative modular                  |     |

| inverse of b                                                                                 | 169 |

| Figure A 27: The operations of the modular multiplication                                    | 169 |

# LIST OF ABBREVIATIONS

**AES**: Advanced Encryption Standard

**AIK**: Attestation Identity Keys

**ASIC**: Application-Specific Integrated Circuit

**BRAM:** Block RAM

**CA** : Certificate Authority

**CLB**: Configurable Logic Block

**CoT** : Chain of Trust

**CP**: Cloud Provider

**DCM**: Digital Clock Manager

**DH** : Diffie–Hellman–Merkle Key Exchange

**DMA**: Direct Memory Access

**DSP**: Digital Signal Processing

**EK** : Endorsement Key

**EPC**: Enclave page cache

**EPCM**: Enclave page cache metadata

**FHE**: Fully Homomorphic Encryption

**FIPS**: The Federal Information Processing Standard

**FPGA**: Field Programmable Gate Arrays

**FV**: FPGA Vendor

**HDL**: Hardware Description Language

**HMAC:** Hashed Message Authentication Code

**IaaS**: Infrastructure as a Service

IC: Integrated Circuit

**ICAP**: Internal Configuration Access Port

**ICMP**: Internet Control Message Protocol

**IO** : Input/Output

**IoT** : Internet of Things

**IP** : Intellectual Property

**ITRS**: International Technology Roadmap for Semiconductors

**KPA**: Known-Plaintext Attacks

**KVM**: Kernel-based Virtual Machine

**DRTM:** Dynamic Root of Trust Measurement

**LUTs**: Lookup Tables

MAC : Message Authentication Code

MI : Malicious Insider

**MiM**: Man-in-the-Middle

**MODEXP:** Modular Exponentiation Block

**NVM**: Non-Volatile Memory

**OEM**: Original Equipment Manufacturer

**OTP**: One-Time-Programmable

**PaaS**: Platform as a Service

**PCR**: Platform Configuration Registers

**PFS**: Perfect Forward Secrecy

**PRE** : Proxy Re-Encryption

**PRM**: Processor Reserved Memory

**PUFs**: Physically Unclonable Functions

**ROT**: Root of Trust

**SaaS**: Software as a Service

**SGX**: Software Guard Extensions

**SHA** : Secure Hash Algorithm

**ACM**: Authenticated Code Module

**SMM**: System Management Mode

**SPRE**: Symmetric Proxy Re-Encryption

**SRK**: Storage Root Key

**SRTM**: Static Root of Trust for Measurement

**SSL** : Secure Socket Layer

TA: Trusted Authority

TC: Trusted Computing

**TCCP:** Trusted Cloud Computing Platform

**TCG**: Trusted Computing Group

**TED**: Trusted Extension Device

**TPM**: Trusted Platform Module

**TXT**: Trusted Execution Technology

**User**: a person who uses the on-cloud FPGA. It is interchangeable with client,

and client application.

**Verilog** : a hardware description language

**VHSIC**: VHSIC: Very High Speed Integrated Circuit

# **ABSTRACT**

Full Name : Mohammed Abdulqaher Ahmed Al-Asali

Thesis Title : Hardware-Based Solutions for Securing Users' Data in Public Clouds

Major Field : Computer Science and Engineering

Date of Degree: May 2017

Traditional software-based protection methods are insecure against cloud operators/service providers related attacks. This is due to the fact that cloud service providers physically own the hardware that hosts users' data and computation. Therefore, cloud computing is not achieving maximum growth since sensitive data are not going to be processed in the cloud. A hardware solution is the most valid method that would possibly tackle the problem and expand the use of cloud computing paradigm. In the literature, protecting users' data in the cloud has been an active research area. Significant progress has been made in securing clients' data in the cloud in the last few years. However, existing research either is mostly concerned with traditional attacks that are not targeting the new emerging threat (i.e. securing data from cloud providers and other users in the cloud) or lacks the practicality in the multi-tenant environment or suffering from security weaknesses and large performance overhead. In this dissertation, we propose FPGA-based solutions for securing users' data from cloud providers and other various kinds of attacks. The proposed solutions are suitable for the multi-tenant nature of the cloud and are practical in terms of cost and performance. The proposed solutions in this

dissertation can target two primary areas: (1) securing sensitive data that are owned by a client who performs the computation on his data in the cloud, (2) securing sensitive data that are aggregated from multiple sources and processed in the cloud such as internet of things (IoT) data that is collected from IoT devices. We propose a secure way to aggregate and process such data in the cloud and give its software and FPGA implementation details. The results show that the proposed solutions integrate well with other cloud resources and can boot 15 times faster than booting a medium-size conventional virtual machine (VM) on the same cloud and their performance is comparable to a software processing plaintext data. For secure IoT data processing in the cloud, the results also show that our proposed solution is efficient in terms of resources and performance.

## ملخص الرسالة

الاسم الكامل: محمد عبدالقاهر احمد العسلى

عنوان الرسالة: حلول هار دوير لحماية بيانات المستخدم في الحوسبة السحابية العامة

التخصص: علوم و هندسة الحاسب الآلي

تاريخ الدرجة العلمية: مايو 2017

طرق الحماية التقليدية القائمة على البرمجيات غير آمنة ضد مشغلي السحابة والهجمات ذات الصلة. ويرجع ذلك إلى حقيقة أن مقدمي الخدمات السحابية يمتلكون الأجهزة التي تستضيف بيانات المستخدمين والتي تقوم باداء العمليات عليها. ولذلك، فإن الحوسبة السحابية لا تحقق أقصى قدر من النمو حيث ان البيانات الحساسة لن يتم وضعها في السحابة الالكترونية. استخدام الهار دوير هو الأسلوب الأكثر فعالية والذي من المحتمل أن يعالج المشكلة ويوسع استخدام الحوسبة السحابية. ان حماية بيانات المستخدمين في السحابة مجالا بحثيا نشطا وقد أحرز تقدم كبير في تأمين بيانات العملاء في السحابة في السنوات القليلة الماضية. ومع ذلك، فإن البحوث الحالية تتعلق في الغالب بالهجمات التقليدية التي لا تستهدف التهديد الجديد الناشئ (أي تأمين البيانات من مشغلي الخدمات السحابية وغيرهم من المستخدمين في السحابة) أو تفتقر إلى التطبيق العملي في بيئة السحابة المتعددة أو تعاني من نقاط ضعف أمنية او اداء ضعيف يجعلها غير عملية. في هذه الأطروحة، نقترح الحلول القائمة على FPGA لحماية بيانات المستخدمين من مشغلي السحابة وغيرها من أنواع مختلفة من الهجمات. الحلول المقترحة هي مناسبة لطبيعة العمليات في السحابة وهي عملية من حيث التكلفة والأداء. يمكن للحلول المقترحة في هذه الرسالة أن تستهدف مجالين رئيسيين هما: (1) تأمين البيانات الحساسة التي يملكها العميل الذي يقوم بإجراء العمليات على بياناته في السحابة، (2) تأمين البيانات الحساسة التي يتم تجميعها من مصادر متعددة ومعالجتها في السحابة مثل بيانات إنترنت الأشياء التي يتم جمعها من أجهزة مختلفة. واقترحنا طريقة أمنة لتجميع ومعالجة هذه البيانات في السحابة وفصلنا برامجها و تفاصيل تنفيذ الطريقة في FPGA وأظهرت النتائج أن الحلول المقترحة تتكامل بشكل جيد مع موارد السحابة الأخرى ويمكن أن تبدأ أسرع ب 15 مرة مقارنة بالبرمجيات الافتراضية التقليدية متوسطة الحجم على نفس السحابة وأداءها يمكن مقارنته مع معالجة البيانات الغير مشفرة. ولتحسين معالجة بيانات إنترنت الاشياء في السحابة، أظهرت النتائج أيضا أن حلنا المقترخ فعال من حيث استهلاك الموارد والاداء..

## **CHAPTER**

# **INTRODUCTION**

#### 1.1 Motivation

Cloud computing is an emerging paradigm that has many benefits for users and enterprises. Reduction of capital costs, which is one of the essential benefits of cloud computing, makes cloud computing the ultimate choice for enterprises. However, cloud security is a major concern that makes cloud computing not appropriate for applications with sensitive data such as financial data processing, medical data and sensitive internet of things (IoT) data. Existing solutions either focus on protecting users' data against external or peer attacks only or lack a more robust attack model. There is an implied assumption that the cloud operator is a trusted entity. This leads many organizations with sensitive data not to process such data in the cloud.

Current cloud infrastructures are not fully secured since the cloud provider has access to users' data on the cloud servers. According to ESG Insider Threats Survey [1], insider attacks, which is carried by a staff in the cloud company, was ranked at third most dangerous attacks of the cloud. Also, 66% of all organizations are very vulnerable to insider attacks methods [1]. Furthermore, 53% of respondents of US State of Cybercrime Survey confessed that damages caused by the insider attacks affect their business more than outsider attacks [2]. For example, Ristenpart et al. outlines how a malicious insider

can extract RSA and AES keys in Amazon's cloud by exploiting shared caches [3]. Another case occurred at Twitter when many companies documents were revealed by Twitter administrator's account that was hacked by a malicious insider [4]. Therefore, there is a need for an effective solution that could build the trust between cloud service providers and the clients so that enterprises take advantage of the cloud to reduce their capital cost and economies of scale.

#### 1.2 Problem Definition and Dissertation Contributions

The dissertation addresses the problem of protecting sensitive data processing in the cloud. The challenge of the problem is that the sensitive data need to be processed in a hardware resource owned by the cloud such that no one, even the hardware resource owner (i.e. the cloud provider), can disclose it while processing. The client outsources the sensitive data to be processed by hardware resources owned by the cloud, such as field-programmable gate arrays (FPGAs), and under the cloud premises, uses software provided by the cloud to authenticate the hardware resource, securely sends the FPGA application that is owned (partially or totally) by the client or another party to the cloud and securely outsource the sensitive data. Securing sensitive data processing in the cloud is even more challenging when the data is collected from multiple sources (i.e. IoT devices) that are deployed in locations under the premises of some party and are owned by the client or another party.

In this dissertation, FPGAs are utilized to secure sensitive data processing in the cloud. FPGAs can be integrated with other cloud HW resources to form flexible, scalable, independent and secure compute resources within the cloud infrastructure. Therefore, clients can safely perform the computation of their sensitive data in the cloud in a secure manner while utilizing the benefits of the cloud and the fast and secure computation of the FPGAs. Sensitive data can be farmed out from the untrusted cloud servers to FPGAs, which are configured by the client's application, for secure processing. Compared to conventional software-based systems, the attack surface is substantially smaller and better defined. This is because FPGA configuration does not require the involvement of operating systems, drivers or compilers, making them suitable to build security solution under more robust attack models and stronger security guarantees. Further, FPGAs can build more sophisticated solutions for modern machine-to-machine communication, IoT data processing and big data applications [5]. As utilizing FPGAs for data protection in the cloud is either limited or unsecured in the literature, there is a substantial need for an efficient and secure FPGA schemes to protect sensitive data in the cloud. Other CPU based attempts to solve this problem are not fully secure, not suitable for on-cloud IoT data protection and suffer from large overhead that make them impractical for medium and big data secure processing.

Hence, the dissertation has the following main contributions to address the problem of securely processing sensitive data in the cloud:

An efficient and practical FPGA-based scheme for securing client sensitive data processing in the cloud from various kinds of attacks (including malicious cloud providers) which has a very little area overhead and can be efficiently integrated with other cloud resources.

- A scheme for protecting third party's intellectual properties (IPs) in the cloud. The scheme facilitates the use of IPs from third parties in the client applications who is not necessarily a hardware expert.

- A security scheme for securing IoT sensitive data processing in the cloud and a

symmetric proxy re-encryption scheme for IoT data on-cloud transformation. The

scheme is suitable for publish/subscribe systems. It was evaluated and a complete

FPGA prototype for the scheme and the proxy re-encryption is presented in this

dissertation.

#### **1.3 Dissertation Outline**

The rest of this dissertation is organized as follows:

Chapter two presents a background in topics related to the contributions of this dissertation including cloud computing architectures, attack models and insider attacks in the cloud, an overview on trust in modern platforms, physically unclonable functions and proxy re-encryption. Chapter three reviews cloud computing security directions; including protecting users' data from other tenants and protecting users' data from the cloud provider. Chapter three also provides a literature review on the current research and products of trusted computing and secure processors. Chapter four presents an overview of the proposed security scheme for securing client data in the cloud. It also covers the FPGA implementation details and performance evaluation of our scheme. Chapter five covers the proposed scheme for IoT data protection in the cloud along with a symmetric proxy re-encryption to provide secure data transformation in the cloud environment. It

also describes the existing IoT business models and presents the experimental results of our proposed cloud-integrated IoT scheme. Chapter five also discusses the performance results of the software and hardware implementations of our symmetric proxy reencryption. Finally, the dissertation is concluded in chapter six.

# **CHAPTER**

## **BACKGROUND**

In this chapter, we give an overview of architectures and management aspects in recent cloud platforms. We will then discuss attack models and demonstrate how a malicious insider could utilize these architectures to carry out attacks to users' virtual machines and data. Further, we will provide an overview of topics that are related to this dissertation such as trusted computing, physically unclonable functions and proxy re-encryption.

## 2.1 Overview of Cloud Architectures and Management

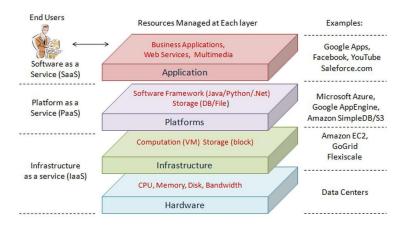

The architecture of a cloud computing can roughly be categorized into four layers: the application layer, the platform layer, the virtualization layer and the hardware layer as shown in Figure 1.

The application layer: this layer is at the top of the hierarchy and consists of cloud applications. Cloud applications have the interesting characteristics of availability, lower operating cost compared to conventional applications, and automatic-scaling feature, which maintains applications' availability and allows an application to scale its capacity up and down to satisfy its needs.

The platform layer: operating systems and software framework lie in this layer. The goal of this layer is to make the deployment of the applications into the virtual machines

simpler. For example, Microsoft Azure works at the platform layer to provide support for storage, and database for applications in the application layer.

The virtualization layer: Also known as the infrastructure layer, assigns computing resources and storage to the target virtual machine by dividing the hardware resources using virtualization technologies (called hypervisors) such as Xen [6] and KVM [7]. The virtualization layer is an important layer in the cloud computing architecture because it involves many recent topics related to the overall design of the cloud, such as dynamic resource allocation. Indeed, this layer is essential in terms of security of the cloud. As it is just above the hardware layer, any security solution would be brought down to the hardware layer.

The hardware layer: the hardware layer is responsible for managing the hardware resources of the cloud, such as physical servers, power, cooling systems, routers, and switches. This layer is implemented as what is called data centers in practice. The data center consists of thousands of servers organized in racks. These racks are interconnected through switches and routers.

Figure 1: Cloud computing architecture [191]

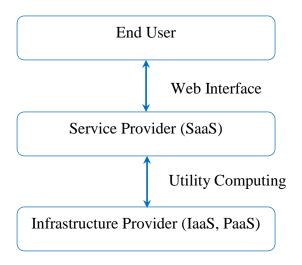

Cloud computing architecture is modular and every architectural layer is loosely coupled with the layers above or below. This modularity allows layers to change separately similar to the design of the OSI model for network protocols. Conceptually, each layer can be seen as a client of the layer below and each layer can be implemented as a service to the above layer. Though, clouds offer services, in practice, they are gathered into three categories: infrastructure as a service (IaaS), platform as a service (PaaS), and software as a service (SaaS). IaaS denotes the provisioning of resources infrastructure. PaaS is for providing operating systems and software development frameworks. SaaS provides applications over the Internet. Users interact with the cloud using the web interface, which shows the SaaS. Then, the requests from the users are processed and deployed by PaaS and IaaS [8]. The business model of cloud computing is shown in Figure 2.

Figure 2: Business model of cloud computing

Mostly, the job of cloud providers is to manage the hardware resources, i.e. compute, network and storage resources that form the infrastructure of the cloud. Management of these resources can be classified into seven areas [9]:

- Global scheduling of virtualized resources: refers to the system-wide monitoring of virtual resources and the underline hardware resources consistent with cloud providers goals.

- Resource utilization estimation: This is necessary for both the cloud provider and the client because it increases the utilization of the physical and virtualized resources.

- Resource pricing and profit maximization: This is due to the nature of pricing

used in the cloud. As the resource consumption is decreased, the cost is also

decreased and vice versa. Hence, resource pricing needs to be managed in a

proper way.

- Local scheduling of cloud resources: This type of scheduling is similar to

operating system scheduler. It deals with one server, hosting multiple virtual

machines, and schedules requests to the physical resources of the server such as

CPU and memory.

- Application scaling and provisioning: To increase the performance of the service for large applications.

- Workload management: This is due to the fact the cloud user might be a business

enterprise and hence the workload request from the enterprise users have to meet

certain requirements from cloud user.

- Cloud management systems: For feedback of resources to the cloud user.

#### 2.2 Overview of Attack Models and Insider Attacks in the Cloud

This section discusses attack models, which are classified into cryptographic attacks, network attacks and physical attacks, and cloud insider attacks as well as cloud cryptographic algorithms.

#### 2.2.1 Cryptographic Attacks

Known-plaintext attack (KPA) is a type of attack which assumes that the attacker has the ciphertext and at least a limited number of samples of the corresponding plaintext. An example of such attack is the use of the encrypted bitstream and the unencrypted bitstream to extract the key embedded in the Xilinx FPGAs [10].

In Chosen-plaintext attack (CPA), the attacker specifies an arbitrary input plaintext and forces the encryption engine to produce the resulted ciphertext. Using the plaintext and the corresponding ciphertext, the attacker can infer information about the encryption algorithm and the key used for encryption. As an example, consider a file storage system that uses the same key to encrypt/decrypt users' files. The attacker can encrypt a file and obtain the corresponding encrypted file. Using these files, the attacker can extract the key used for encryption and use it to decrypt other users' files.

There are two types of chosen-plaintext attack, adaptive chosen-plaintext attack and batch chosen-plaintext attack. In the adaptive chosen-plaintext attack, the attacker can encrypt more plaintexts and obtain the ciphertexts of these plaintexts. The attacker has the opportunity to analyze the previous pairs before choosing a new plaintext as an input to

the encryption engine. In batch chosen-plaintext attack, the attacker encrypts all of the plaintext before obtaining any ciphertext.

To differentiate between KPA and CPA, if the attacker is able to obtain a pair of plaintext and ciphertext, but not any specific pairs, then the attack is KPA and if the attacker is required to give input plaintext and obtain the corresponding ciphertext, then the attack is CPA. Note that KPA is a special kind of CPA.

Ciphertext-only attack (COA) is a type of attacks in which it is assumed that the attacker can obtain the ciphertext only and the plaintext is not accessible by the attacker. COA can happen most likely in real life cryptanalysis. However, it is the weakest attack because the attacker lacks information and only the ciphertext is available for him. Therefore, COA is typically the hardest to design and at the same time the easiest to implement. Exhaustive key search or brute force attack is an example of COA, in which all keys are tried by the attacker until the correct key is found. The success of COA depends on the length of the key and does not depend only on the cipher strength or the type of the cipher being used.

Chosen-ciphertext attack (CCA) is the opposite of CPA and the attacker chooses a ciphertext and obtains the corresponding plaintexts. This enables the attacker to investigate different portions of the plaintext state space and may enable him to find vulnerabilities. Types of CCA include lunchtime attack and adaptive chosen-ciphertext attack. The attacker in lunchtime attack have access to a limited ciphertexts and plaintexts pairs. The attacker in adaptive chosen-ciphertext attack can pick a sequence of ciphertexts to be decrypted and obtains the ciphertexts. For further steps, he has the chance to learn from the previous results and choose more effective next ciphertexts.

The open key attack model assumes that the attacker has some knowledge about the key used for encryption/decryption. Related-key attack is an attack of such model and the attacker uses a key that is related mathematically to the target key to encrypt the plaintext and access the ciphertext. Known-key distinguishing attack is another type of open key model and the attacker chooses a key and study the cipher and distinguishes between a random data and a ciphertext.

#### 2.2.2 Network Attacks

Network attacks include wiretapping, port scan, idle scan, man-in-the-middle, impersonation, replay, ARP poisoning, ping flood, ping of death and Smurf attacks.

Wiretapping is a clear example of network attacks and is effective when the data sent is unencrypted. In port scan attack, the attacker sends packets to the victim machine while varying the port in every packet in attempt to know which ports are open and to identify the operating system and the services in the victim machine. Idle scan attack is a kind of port scan attack on TCP ports and the attacker sends packets to TCP ports using impersonated machines (i.e. machines with their identity stolen) to identify and learn the services on the victim machine.

ARP (address resolution protocol) is used to identify the MAC address of the target machine. The sender machine broadcasts a message over the network containing the IP address of the target machine. The target machine sends a reply containing its MAC address. ARP poisoning attack occurs when the attacker replaces the MAC address in the reply message by his own MAC address; causing the sender machine to send the traffic

through the attacker machine. This attack is possible in local area networks that utilize ARP and can be used to launch other attacks such as denial of service attacks [11].

Ping flood is a type of denial of service attack in which an attacker sends ping packets to the victim machine as fast as possible without waiting for replies. The attack is more effective when the bandwidth of the attacker is more than the bandwidth of the victim. Ping of death happens when the attacker sends a ping packet that is larger than the bytes allowed by the IP protocol. The packet gets fragmented, sent and reassembled in the victim machine. When reassembled, buffer overflow occurs which causes system crash and allows injection of malicious code [12].

Internet Control Message Protocol (ICMP) is part of the internet protocol suite and is used to send control messages such as error and ping messages. The attacker in Smurf attack spoofs the IP address of the victim machine and broadcasts large ICMP messages to the network using this IP address. If number of machines in the network is large, the responses from these machines will flood the victim machine; causing denial of service [13].

#### 2.2.3 Physical Attacks

Physical attacks are divided into invasive, non-invasive and semi-invasive attacks [14]. Invasive attacks are hardware attacks that require manipulation of the physical properties of the chip. Non-invasive attacks are similar to invasive attacks but do not damage the chip package. Semi-invasive attacks are relatively new type of attacks that require depackaging the chip, similar to invasive attacks, but do not create contacts with internal chip lines.

Invasive attacks require expensive equipment, knowledge and time. A well-known attack of this type is miroprobing; where a needle is attached onto the internal wires of the chip to extract the chip secrets. Non-invasive attacks require moderate level of equipment and knowledge to implement. Non-invasive attacks include side-channel, brute force, fault injection and data remanence attacks [15].

Side-channel attack is any attack that use data about the encryption or decryption process to break the system such as using the noise created by encryption engines or measuring the time of various computations. Side channel attack includes, generally, cache, timing, power analysis and electromagnetic attacks. Cache attack is based on monitoring cache accesses made by the user in a shared environment such as cloud servers. Timing attack is based on measuring the time it takes to do the operation such as measuring how many cycles a memory access take to identify whether the access is read or write. Power analysis attack makes use of power consumption that is varied by the hardware during computation. Power analysis attacks is classified into simple power analysis (SPA) and differential power analysis (DPA). SPA obtains the information directly from the power consumption of the device (current versus time), while DPA obtains the information from

power variations by observing differences between traces of different operations and statistical analysis is applied to obtain the secrets from noisy measurements that are difficult to analyze using SPA. Electromagnetic attack is based on electromagnetic radiation, which can provide information about plaintexts and may directly disclose the plaintext and other information. Fault injection can be used to exploit the erroneous result or unexpected behavior of the chip to extract its secrets. Data remanence is the sensitive data that is read by the attacker but is supposed to be erased [15].

Semi-invasive attacks use ultraviolet (UV) light, X-rays and other light sources to disturb chip operations and extract sensitive information. Attacks of this type include UV, optical fault injection, and optical side-channel Attack [16].

There are a number of attacks that are targeting FPGAs such as Reverse Engineering, Tampering, Cloning, Counterfeiting, and Crippling attacks. Reverse Engineering can cause bypassing security measures of the configuration. An adversary can study the configuration blocks and replace security components by his own malicious components in order to disclose configuration secrets and sensitive data. Tampering is a special type of reverse engineering, where the adversary modifies the configuration to gain access to its secret keys or interrupt its functionality or disclose its data. Hardware Trojans are a clear example of tampering [17]. Cloning attack occurs when an exact copy of the FPGA configuration is created by an adversary. Counterfeiting attack is an extension to the cloning attack and it occurs when all FPGAs of the same family and size are identical. Thus, a configuration made for one device can be used with another. This can be easily done in the cloud environment [18]. The details of the design do not need to be known by the attacker and the configuration is just regarded as a black-box reducing the effort of

compromising the FPGA to insert a snooping circuitry to disclose FPGA secrets and therefore disclose users' data. Crippling attacks are similar to denial of service attacks on networked servers. The attacker re-configures the FPGA with an invalid configuration to bring the FPGA system offline [19].

#### 2.2.4 Insider Attacks in the Cloud

How a malicious insider (MI), who could be an employee in the cloud, could carry attacks to users data of the cloud was reported by many survey publications, such as [20][21]. An MI could utilize the system to carry out various kinds of attacks depending on his position in the cloud. An administrator who can manage client's virtual machines (VMs), for instance, can do anything to the VM he is managing. Similarly, an employee working in cloud hypervisors might inject a code to monitor all the activities of client's VMs on the underlying hardware [20]. Memory Dump Scanning, Templates Poisoning and Snapshot Cracking are examples of exploiting client's information in the cloud [21]. Dumping the memory to get sensitive information is called Memory Dump Scanning attack; the MI can easily dump the memory to a flash or external storage. Although the retrieved data would be large and sensitive data is concealed in hundreds of megabytes of data, the MI usually use techniques such as social engineering, which count on human communication and involves tricking them into breaking security measures, to extract the critical data.

Cloud providers usually provide templates for the virtual machines images to be created from. The default templates and virtual machines that are deployed from an infected template could be downloaded and analyzed by an employee; passively revealing VM owners' sensitive data. This attack is relevant to many platforms and is also applicable to OpenStack which is the top open source cloud computing technology in 2014 [22].

Cloud providers manage the users and passwords of the VMs in a normal manner, assuming trust of their staff. Not all VMs disks are encrypted due to many difficulties facing disk encryption such as sharing resources with other tenants [23]. If an MI is a VM administrator, he can easily make an attack on that VM by simply reading all the required information from the unencrypted information.

# 2.2.5 Cryptographic Algorithms for Cloud Computing

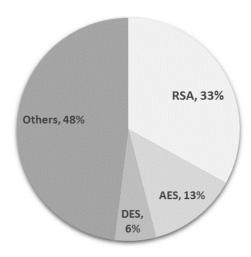

This section reviews cryptographic algorithms used or preferred in the cloud. According to Soofi et al. [24], most approaches are based on RSA encryption. 60% out of the 30% RSA encryption techniques results are validated by experiments. Figure 3 below depicts the use of encryption algorithms in the cloud. Patwal and Mittal [25] also reported that RSA, DES and AES are widely implemented in the cloud.

Figure 3: Percentage of use of various encryption algorithms in the cloud

An algorithm called Diffie–Hellman–Merkle key exchange (DH) was invented by Ralph Merkle for sharing a key between two parties over unsecured channels [26], [27]. The secret key can then be used as a session key to encrypt/decrypt the data the two parties want to send/receive. The algorithm works as follows:

Let the two parties be A and B.

A and B agree on a prime number p and base g (which is normally a small number such as 2).

A chooses an integer a and sends B  $g^a$  mod p.

B chooses an integer b and sends  $A g^b \mod p$ .

A computes  $K = (g^b \mod p)^a \mod p$

$B \ computes \ K = (g^a \ mod \ p)^b \ mod \ p$

A and B now share the secret K.

All values except a and b are non-secret and can be sent between the two parties. For example, if A and B agrees on p to be 23 and g to be 5, then A chooses a = 6 and sends B the value 8 and B chooses b = 15 and sends A the value 19. K then will be 19<sup>6</sup> mod 23 = 8<sup>15</sup> mod 23 = 2 which is the secret they now share. Ephemeral Diffie-Hellman can be used such that every time A and B share a secret, different shared key is created enabling what is called perfect forward secrecy, which means that even if the private keys are compromised, past communications are still secure.

Leading cloud computing platforms use the DH such as OpenStack [28], which uses this algorithm for key sharing between its components. The DH is one of the best protocols of sharing keys between parties and in this dissertation, we make use of its basic principle for key sharing between FPGAs and other parties because of its lightweight computation which is suitable for cloud computing and IoT.

# 2.3 Trusted Computing

The Trusted Computing Group had developed the Trusted Computing (TC) technology. TC is an attempt to ensure that computers will behave as expected and this behavior would be enforced by hardware and software. The enforcement is achieved by including a special chip integrated with computers' hardware, which includes unique, inaccessible by other components of the system, encryption keys. The concept of trusted computing leads to the fact that the hardware of the system is theoretically secure from all kinds of attacks, including its owner [29].

Trusted computing is implemented in practice as a hardware component attached to other hardware components of computer assets, in addition to software drivers. Trusted computing witnessed a remarkable success in personal computers. Unfortunately, it is in its early stages in cloud computing because the intention of trusted computing was not targeting virtualization [30]. The most common and most widely used hardware component is the trusted platform module (TPM). Hence, we will consider, in the following subsections, the TPM in our discussion and will discuss the implications of using the TPM in the cloud paradigm.

#### 2.3.1 Trusted Platform Module

The Trusted Platform Module (TPM) is a special chip issued by the Trusted Computing Group (TCG) to secure hardware by embedding cryptographic keys into devices. The TPM was developed to provide device identification, authentication, measurement, encryption, and device integrity. Software can use the TPM to authenticate hardware devices and the TPM is capable of monitoring and reporting configuration state by using the main bus of the computer from the point of computer power-up.

A TPM has at least 16 Platform Configuration Registers (PCR registers), which are initialized to a known value when the machine is rebooted. The values of these registers cannot be arbitrarily set. The values of the PCR registers can be retrieved from the TPM by issuing the TPM Quote operation.

The TPM is mainly used to create a foundation of trust of the software installed in the host where the device is present. A process called Static Root of Trust for Measurement

(SRTM) performs a chain of measurements, starting when the host platform is reset, of the components and configuration data involved in the system boot while the Dynamic Root of Trust Measurement (DRTM) is the process of taking the measurements while the system is running. Each component measures the next component before passing the control to it, forming what is called a Chain of Trust (CoT). The CoT, at least, involves the BIOS, the boot loader and the operating system kernel. The resulting measurements must be always the same unless the boot components are modified. The combination of the TPM Quote operation and the SRTM process, allows the remote attestation of the host [32]. An external attester can request a TPM Quote of the PCRs, and compare the obtained values with a baseline of the PCR values of the system generated when it was in a trusted state.

There are three keys produced by the TPM; Endorsement Key (EK), Storage Root Key (SRK) and Attestation Identity Keys (AIK). The Endorsement Key is created by the TPM manufacturer and is never released outside of the TPM. EK is used to ensure that the data was encrypted by the TPM (the data can be trusted). A private EK which is used to encrypt the data can be proven to be from the TPM by using it to decrypt a value that has been encrypted with the public EK. When the TPM is initialized by the user, in the process of taking the TPM ownership, the SRK is generated. It is used to protect TPM keys created by applications, so that these keys cannot be used without the TPM (all the keys the user requests are produced by the SRK). Finally, the AIK are used as an alias of the EK for signing information produced by the TPM, e.g. the PCR register values issued after the TPM Quote operation. The problem with the TPM, in general, is the unsecured

bus between it and other computer components and most of the attacks are actually carried out from this unsecure bus [33].

### 2.3.2 Intel Trusted Execution Technology

Intel's Trusted Execution Technology [34] is a technology developed to provide attestation of a platform and the operating system running in that platform and to ensure that the OS starts in a trusted environment. TXT relies on the TPM and another chip to provide the measurements of the platform components and the software. TXT aim is to provide an isolated environment for VMs from untrusted software by providing the VM control over the platform while it is active. A warm system reset is performed by the authenticated code module (SINIT ACM) before starting the VM. The TPM measures the hardware and updates the SRTM registers and when the VM is initialized, it updates the DRTM registers. Therefore, the VM can start from a valid state and can execute in a trusted environment. Similar to the TPMs, TXT is vulnerable to physical DRAM attacks since DRAM encryption is not implemented. The System Management Mode (SMM) is the most privileged execution mode in which all executions are suspended and only a special software stored inside a firmware (stored in a ROM and is theoretically inaccessible by the operating system or applications) is executed. Several attacks were reported to the SMM such as [35]-[39], which leads to granting an attacker access to all computer software including accessing the TXT memory.

### 2.3.3 Intel Software Guard Extensions (SGX)

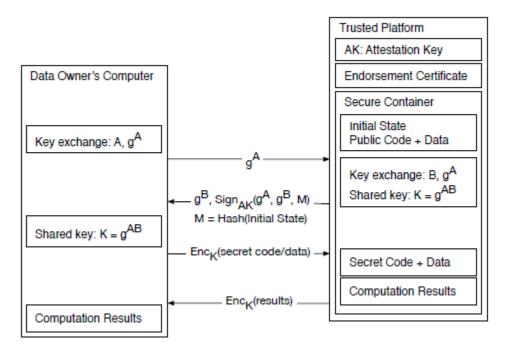

Intel SGX follows the approach in Figure 4 below. Data owner has the measurement of the initial state as he computes its hash locally by creating the exact container (or enclave) in his local machine. The attestation key (the private part of it) is used to sign the hash M, g<sup>A</sup> and g<sup>B</sup> and it is decrypted by the data owner by the AK public key, which is publicly available and is certified using the Endorsement Certificate (only the public key can verify information signed with the private key). The hash is done for the initial state only and any other code or data that will be received later will not be measured. After successfully attesting the container and sharing K using Diffie-Hellman key exchange, the data owner sends the code and the data encrypted to the enclave using K.

Figure 4: Trusted platform proves to a remote data owner that it is communicating with the right container [40]

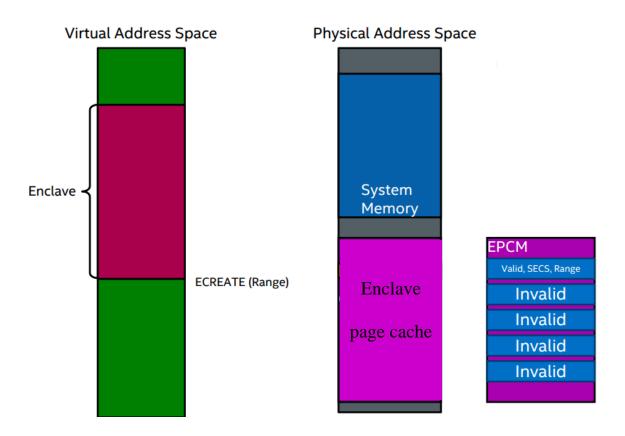

The Data owner creates an enclave in his local machine using ECREATE instruction, Figure 5. ECREATE instruction will result in reserving part of the virtual address space for the enclave, creating an isolated part in the Processor Reserved Memory (PRM) called enclave page cache (EPC) and its Metadata (EPCM). EPCM is used to store information about the enclave and its pages and to ensure that each EPC page belongs to exactly one enclave.

Figure 5: Creating an enclave [41]

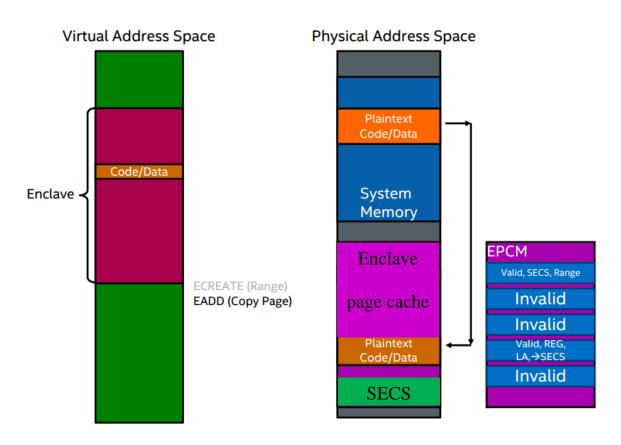

Data owner then executes EADD instruction, Figure 6, to copy the required pages to the enclave area one by one. MRECNLAVE is a measurement register to store the measurement of the hash. EEXTEND instruction updates the enclave's measurement

(MRECNLAVE) used in the software attestation process. The SGX Enclave Control Structure (SECS) is inside the EPC and stores enclave metadata and is used by the CPU for the enclave identity.

Figure 6: Copying enclave pages to the EPC [41]

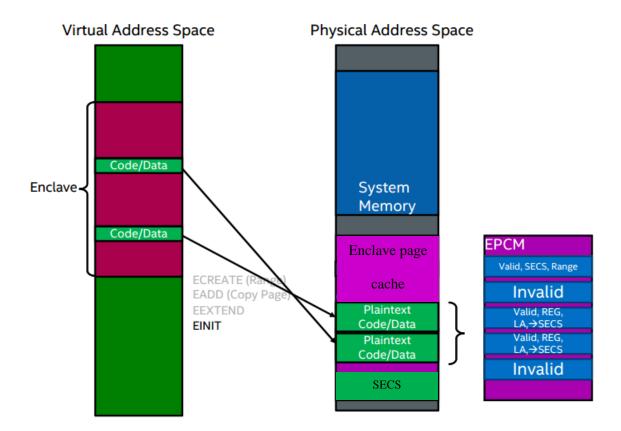

Other instructions are shown in Figure 7. The EINIT instruction marks the enclave's SECS as initialized. Setting INIT to true means that EADD cannot be invoked on that enclave anymore and MRENCLAVE will hold the final measurement. The EENTER instruction is used to execute enclave code. The EEXIT instruction is used when the enclave code finishes performing its task to return the execution control to the process which invoked the enclave.

Figure 7: Enclave instructions [41]

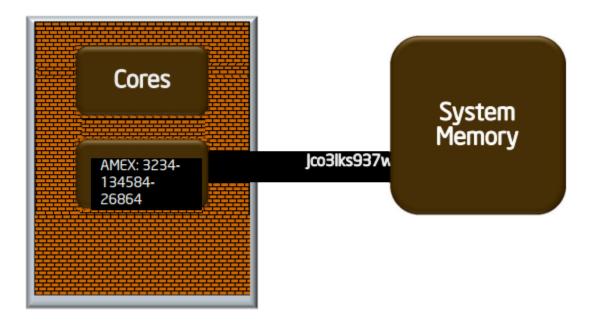

The code and data are unencrypted inside the CPU package and if the code/data leaves the CPU package, they are encrypted using a symmetric key randomly generated on power up (Figure 8).

Figure 8: Code/data are encrypted outside the CPU package [41]

To run the enclave in a remote host, the same procedures described above are done in the remote host. Hence, the same value of MRENCLAVE will be produce by the remote host. Data owner can remotely attest MRENCLAVE value and compare it with his own value. As a result of the remote attestation process (as in Figure 4), a symmetric key can be shared and this key can be used to send encrypted data to/from the enclave.

# 2.4 Physically Unclonable Functions

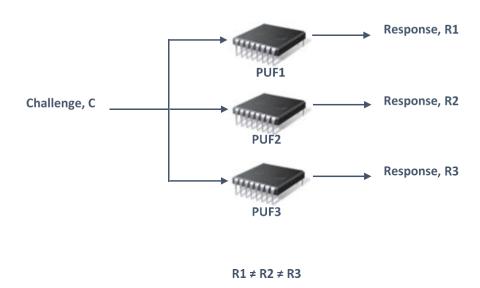

Physically unclonable functions (PUFs) topic is one of the hottest topics in the field of chip authentication and reconfigurable computing. PUFs are functions that make use of the manufacturing process variations to uniquely identify devices. These variations cannot be controlled and therefore making PUFs behavior and response unpredictable. Figure 9 shows how a PUF can be used for device authentication. An ideal PUF, when a

challenge is applied, should have a response that is unique (a device response should not match a response from another device), steady (when the same challenge is applied the device should give the same response), random (is based on uncontrolled variations and cannot be predicted) and tamper resistance (when the PUF is propped, it gives a different response).

Figure 9: PUFs challenge response

PUFs can be classified into two categories; PUFs using explicitly-introduced randomness and PUFs using intrinsic randomness. Optical PUF and Coating PUF are two different types of PUFs using explicitly-introduced randomness. Optical PUF was one of the first attempts in producing unique identifiers for integrated circuits (ICs) and is formed when a transparent material is doped and when a laser beam is induced to the material at certain angle, a unique and random pattern is formed. This pattern is very difficult to duplicate and therefore this type of PUFs is unclonable. Optical PUF is rather laborious because it

requires laser setup and a complex mechanical system to position the laser beam [42]. On the other side, Coating PUF is built when a network of wires is created on the top layer of an IC. The space between the wires is filled with a material and doped with dielectric particles randomly. Therefore, the capacitance between these wires would be random; creating a unique identifier for the device [43].

PUFs using intrinsic randomness do not require modifications to the manufacturing process and therefore are highly attractive. PUFs of this type can be divided into a delay-based PUFs and memory-based PUFs. Delay-based PUFs include Arbiter PUF [44], Ring oscillator PUF [45] and Glitch PUF [46] and memory-based PUFs include Butterfly PUF [47] and SRAM PUF [48]. Arbiter PUF is based on two parallel racing paths with an arbiter at the end of the two paths. A signal is applied simultaneously to the two paths and the resulting analog delay difference is processed by the arbiter to get the required digital value. Ring oscillator PUF utilize the delay characteristics of multiple ring oscillators and a comparison of them is made to produce the digital value. SRAM PUF and Butterfly PUF are called memory-based PUFs. SRAM PUF [49] makes use of the initial values of the SRAM cells as these initial values are different from chip to chip due to the variations in the manufacturing processes, in which the state of the bit at power up determines its initial value. Butterfly PUF is an emulation of SRAM PUF in FPGAs.

PUFs in FPGAs include Arbiter PUF [44], Ring oscillator PUF [45]; enhanced by many other publications such as [50]–[53], Anderson PUF proposed by J.H. Anderson [54], Butterfly PUF [47], and SRAM PUF. Anderson PUF is considered as Glitch PUF and is based on the delay of lookup tables (LUTs) in shift register mode and carry chain multiplexers in the FPGA slices to extract the physical variations of FPGA devices.

SRAM PUF was made possible using recent Xilinx [55] and Altera devices [56]. In this dissertation, we assume the use of the SRAM PUF for generating random numbers as other PUFs are currently suffering from low stability, uniqueness, and entropy compared to SRAM PUF [57].

Although many types of the PUFs can be implemented using most of nowadays FPGAs, we believe that most of these PUFs are still facing many drawbacks when used in FPGAs and we though recommend the use of SRAM PUFs as it is considered more appropriate for FPGAs and are already available in recent FPGA devices [56].

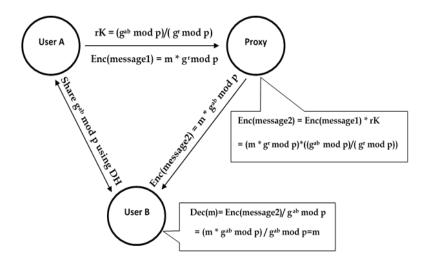

# 2.5 Proxy Re-encryption

Proxy re-encryption (PRE) is a method for transforming a ciphertext c1 encrypted using a key (K1) to another ciphertext c2, which can be decrypted using a key (K2), without decrypting/disclosing the plaintext during the transformation. The benefit from such transformation is that the time for transformation is less compared to decrypt-then-encrypt and the transformation does not expose the plaintext, which means that the entity that does the transformation (i.e. the proxy) is not necessarily trusted. PRE was first introduced by Mambo and Okamoto [58] and later Blaze, Bleumer, and Strauss [59] proposed the BBS scheme in which a semi-trusted proxy converts a ciphertext encrypted by user's A public key to another ciphertext to be decrypted by user's B private key. Semi-trusted in this context means that the proxy will correctly execute the code required for the conversion and does not mean that users A and B trust it partially. The conversion is possible when user A provides a re-encryption key to be used for the conversion. The

BBS was improved by Ateniese et al. [60] and many other public key based PREs were proposed such as [61] [62] [63] [64]. These public key based PRE methods are used when the delegator (user A) is for some reason unwilling to receive the data and want to give delegation to another party (user B) to decrypt the data without revealing his private key to user b or the semi-trusted proxy. For example, a manager wishes to give delegation for his employee to check his email messages without giving him his private key. The manager gives a re-encryption key to the email server so that the messages are converted by the email server and his employee can decrypt the data without fully trusting the email server or giving the employee the manger private key. Symmetric key based PRE scheme was proposed by Syalim et al. [65]. The scheme uses the all-ornothing transform [66] which means that the ciphertext cannot be decrypting if any part of it is missing. However, the scheme requires the generation of 8 keys to do the conversion and these keys had to be shared between the two communicating parties and the proxy; making the conversion complicated. The preferred properties of the PRE are:

- 1- Unidirectional: a PRE scheme is unidirectional if the proxy is able to transfer delegator ciphertext to the delegatee ciphertext but not the opposite.

- 2- Non-transitive: The proxy cannot give the delegation alone to a third user C from the re-encryption keys of users A and B. for example, user A gives re-encryption key (rK1) to delegate the rights to user B and user B gives re-encryption key (rK2) to delegate the rights to user C. Then the proxy cannot give the delegation rights of user A to user C by using rK1 and rK2.

- 3- Collusion-resistant: if the proxy and another user collude, they cannot obtain the private key of the other party.

- 4- Non-interactive: when the private key of the delegatee is not required to create the re-encryption key, then the PRE is non-interactive.

- 5- Multi-use/Single-use: if only the original ciphertext can be re-encrypted, then the PRE is single-use and the opposite is correct for multi-use.

- 6- Key-privacy: if the identity of the delegator and the delegatee cannot be identified by the proxy from the re-encryption keys and the ciphertext, then the PRE is key-private.

- 7- Transparent: a PRE is transparent if the delegatee is unable to note the existence of the proxy between him and the delegator.

- 8- Key-optimal: the PRE is key-optimal if it is required to store small amount of data (the private keys only).

- 9- Temporary: if the delegator can delete the decryption rights after some time, then the PRE has the temporary property.

## **CHAPTER**

### LITERATURE REVIEW

In this chapter, we will discuss recent contributions related to securing users' data in the cloud. This includes surveying the techniques published in securing users' data from both other cloud clients and the cloud providers. We will also investigate recent advances in trusted computing as it is a fundamental topic in outsourced data secure processing. Finally, we explore secure processors and their implementation methods.

# 3.1 Protecting Users' Data from Other Users

Protecting users' data from other cloud users requires securing user's virtual machines form other virtual machines in the same cloud server. There are two lines of research heavily investigated in the literature; securing hypervisors from being compromised and virtual machine isolation.

Ferrie [67] described an attack scenario for identifying which hypervisor is being used to deploy the virtual machines. Leading hypervisors (QEMU, VirtualPC, Bochs, Parallels, Hydra and VMWare) were compromised using his scenario. The attack is based on specific unusual instructions that leads to raising exception that are not handled by the hypervisors. The work also provided a solution for each hypervisor by handling the unusual instructions. Similar attacks were also reported by Joanna [68] and Tobias [69].

Louis and Jordan discussed some of the vulnerabilities related to granting access to users' metadata in hypervisors [70]. Among these attacks, redirecting data flows using firewall Ports, utilizing user application interface, hooking calls to library and hooking system calls were illustrated in detail.

Breaking the isolation between virtual machines is also carried out on the weak parts of the hypervisor. This attack causes Denial of Service, System halt, and memory overflow. Attacks similar to this one were reported in many contributions in the literature such as [71]–[73].

Fog computing and decoy methods were used intensively to protect users' data in the cloud. Fog computing relies on making distributed cloud resources such that the cloud parts (storage and servers) can be geographically closer to the user. Fog computing was mentioned to be more secure because it places the data geographically close to the end user and therefore certain policies can be applied to restrict access to cloud resources to users in the same geographic area [74]–[77]. Decoy files/documents are trap files that are used to trap illegitimate user. The search behavior of an illegitimate user is random to some extent when entering the system and when the trap file is hit, it will fire an alarm. If the alarm is a false positive, the legitimate user will be challenged with a question and his legitimacy will be checked.

Several attempts were carried out to tackle the attacks to users' data from other users using Fog computing and Decoy method and these techniques are not helpful for tackling attacks from the providers of the cloud since the architecture of the cloud itself is being ignored as well as dumping the memory of cloud servers. Most previous studies are theoretical and are not directly related to commercial clouds. A common factor between