## CUDA OPTIMIZATION OF A CLASS OF ITERATIVE LINEAR ALGEBRA SOLVER

BY

LUTFI AZIZ FIRDAUS

A Thesis Presented to the DEANSHIP OF GRADUATE STUDIES

KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

## **MASTER OF SCIENCE**

In

**COMPUTER ENGINEERING**

MAY 2017

#### KING FAHD UNIVERSITY OF PETROLEUM & MINERALS DHAHRAN 31261, SAUDI ARABIA

#### DEANSHIP OF GRADUATE STUDIES

This thesis, written by LUTFI AZIZ FIRDAUS under the direction of his thesis adviser and approved by his thesis committee, has been presented to and accepted by the Dean of Graduate Studies, in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE IN COMPUTER ENGINEERING.

#### Thesis Committee

Pouhamed Mayor Al

Dr. Mayez Al-Mouhamed (Adviser)

Dr. Muhammad Elrabaa (Member) Dr. Muhamed Mudawar (Member) Dr. Ahmad Almulhem Department Chairman Dr. Salam A. Zummo DEP Dean of Graduate Studies OFGRADUN 116/17 Date

©Lutfi Aziz Firdaus 2017

To my beloved father, may Allah grant him Jannat al-Firdaus

## ACKNOWLEDGEMENTS

All the praises is due to Allah alone, who has granted me the ability to finish my Master study in Computer Engineering Department, College of Computer Science and Engineering, King Fahd University of Petroleum and Minerals (KFUPM). After that, I would like to thank my advisor, Dr. Mayez Abdullah Al-Mouhamed, for his patience, guidance, support, and encouragement that help me to finish this thesis. There are so much knowledge and the skills I have obtained under his supervision. Also, to Dr. Muhammad Elrabaa and Dr. Muhamed Mudawar as my thesis committee members, I would like to give my gratitude for helping me to complete my thesis.

Special thanks to my beloved father, Ikin Sodikin -may Allah bless him-, the one who support me fully to study and to complete this Master even though at the last moment he could not see me finishing it. Also to my mother, Siti Nurjanah Jamilah, for her presence, kindness, pray, and everything that I could not ever repay.

Many thanks and apologize I would like to say to my love of my life, Endang Muthiarini, and my son Fudhail Abdullah Firdaus for everything we have been through together because of this.

Last but not least, for Pa Usep and all Indonesian community member that I could

not mention name by name, thank you very much for our togetherness. You are just like my second family here.

May Allah reward you all with goodness.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                                             | v    |

|------------------------------------------------------------------------------|------|

| LIST OF TABLES                                                               | xi   |

| LIST OF FIGURES                                                              | xiii |

| ABSTRACT (ENGLISH)                                                           | xvii |

| ABSTRACT (ARABIC)                                                            | xix  |

| CHAPTER 1 INTRODUCTION                                                       | 1    |

| 1.1 Iterative Methods                                                        | 4    |

| 1.2 Problem Statement                                                        | 5    |

| 1.3 Contributions to this Topic                                              | 6    |

| CHAPTER 2 BACKGROUND                                                         | 7    |

| 2.1 GPU and CUDA                                                             | 7    |

| 2.1.1 GPU Architecture                                                       | 7    |

| 2.1.2 CUDA Programming                                                       | 11   |

| 2.1.3 Numerical Library                                                      | 13   |

| 2.2 Multi-GPU Programming                                                    | 15   |

| 2.3 Biconjugate Gradient Stabilized Method (BiCGStab) $\ldots \ldots \ldots$ | 19   |

| CHAPTER 3 SPARSE MATRIX STORAGE FORMATS                                      | 21   |

| 3.1 General Sparse Storage Format and Its SpMV                               | 21   |

|      | 3.1.1  | Coordinate Format (COO)                               | 23 |

|------|--------|-------------------------------------------------------|----|

|      | 3.1.2  | Compressed Storage Row Format (CSR)                   | 24 |

|      | 3.1.3  | Block Compressed Storage Row Format (BSR)             | 26 |

|      | 3.1.4  | ELLPACK Format (ELL)                                  | 26 |

|      | 3.1.5  | Hybrid Format (HYB)                                   | 28 |

|      | 3.1.6  | Diagonal Format (DIA)                                 | 30 |

| 3.2  | Previo | ous Work Studies                                      | 32 |

| CHAP | TER 4  | 4 LITERATURE REVIEW                                   | 39 |

| 4.1  | CUDA   | A Application                                         | 41 |

|      | 4.1.1  | Ocean Modelling                                       | 41 |

|      | 4.1.2  | Artificial Intelligence                               | 41 |

|      | 4.1.3  | Oil and Gas                                           | 42 |

|      | 4.1.4  | Math Compiler                                         | 44 |

|      | 4.1.5  | RSA Decryption                                        | 45 |

| 4.2  | CUDA   | A Multi-GPU                                           | 46 |

| 4.3  | CUDA   | A BiCGStab                                            | 52 |

| CHAP | TER    | 5 METHODOLOGY                                         | 55 |

| 5.1  | Gener  | al Hepta BDIA (BDIA-GH)                               | 55 |

| 5.2  | Sparse | e Matrix-Vector Multiplication for BDIA-GH            | 64 |

| 5.3  | BiCG   | Stab with General Hepta                               | 69 |

| 5.4  | Multi- | -GPU BiCGStab BDIA-GH                                 | 70 |

| 5.5  | Analy  | sis of Deadlock in Inter-Block Synchronization        | 73 |

|      | 5.5.1  | Evaluating Number of Active Blocks on Kernel in       |    |

|      |        | Kepler K20Xm and Deadlock Condition with Experimental |    |

|      |        | Validation                                            | 75 |

|      | 5.5.2  | General Conclusion                                    | 82 |

| CHAP | TER (  | 6 RESULTS AND DISCUSSION                              | 85 |

| 6.1  | Sparse | e Matrix-Vector Multiplication                        | 86 |

| 6.2  | BiCGStab on Single GPU         | 88  |

|------|--------------------------------|-----|

| 6.3  | CUDA Memory Transfer           | 91  |

| 6.4  | BiCGStab on Multi GPU          | 95  |

| 6.5  | Overhead in Computing BiCGStab | 103 |

| CHAI | PTER 7 CONCLUSION              | 118 |

| RE   | FERENCES                       | 119 |

| VI   | ΓΑΕ                            | 130 |

# LIST OF TABLES

| 2.1  | Device Specification for Tesla K80                                 | 10 |

|------|--------------------------------------------------------------------|----|

| 5.1  | Matrix Market File configuration                                   | 65 |

| 5.2  | BiCGStab Algorithm with Its Function Call kernels                  | 71 |

| 5.3  | Validation Experiment for Analyzing Deadlock on inter-block GPU    |    |

|      | synchronization using Jacobi Algorithm                             | 84 |

| 6.1  | SpMV Execution Time of Various Storage Formats (Single GPU)        | 88 |

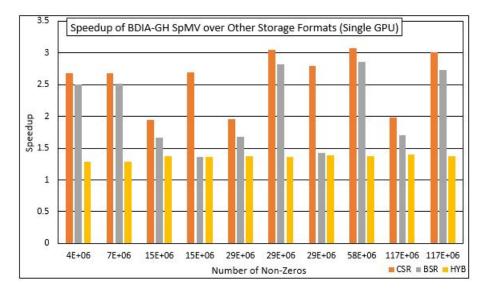

| 6.2  | SpMV Speedup of BDIA-GH over Other Storage Formats (Single         |    |

|      | GPU)                                                               | 89 |

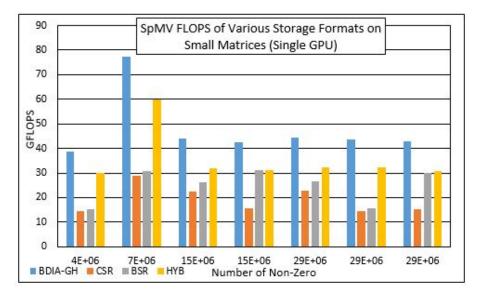

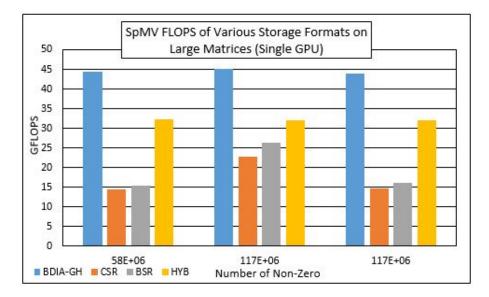

| 6.3  | SpMV FLOPS of Various Storage Formats (Single GPU) $\ . \ . \ .$   | 89 |

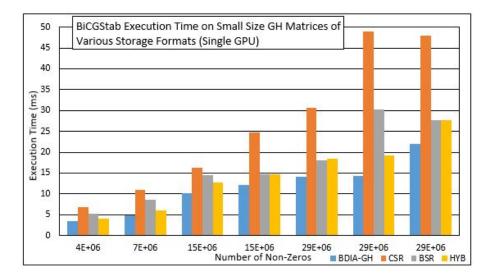

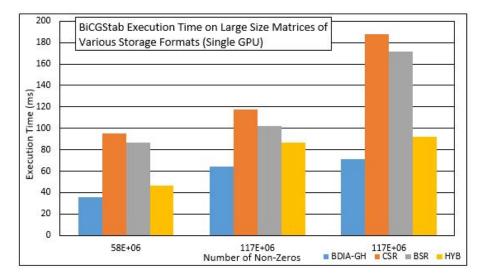

| 6.4  | BiCGStab Execution Time on GH Matrices of Various Storage          |    |

|      | Formats (Single GPU)                                               | 92 |

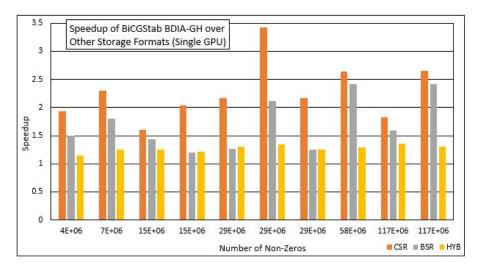

| 6.5  | Speedup BiCGStab BDIA-GH over Other Formats (Single GPU) .         | 92 |

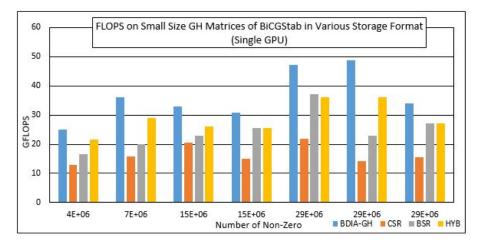

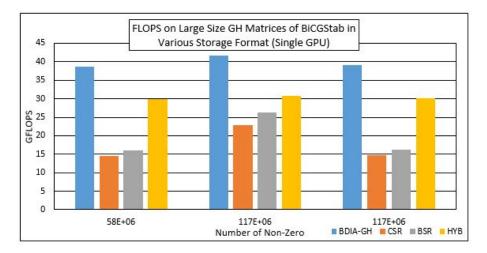

| 6.6  | BiCGStab GFLOPS on GH Matrices of Various Storage Formats          |    |

|      | (Single GPU)                                                       | 94 |

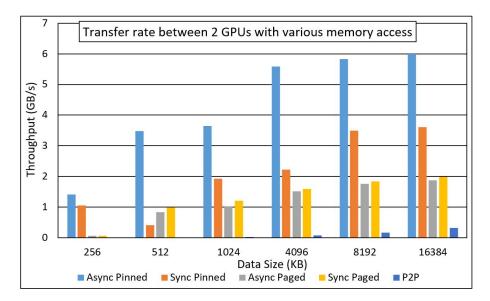

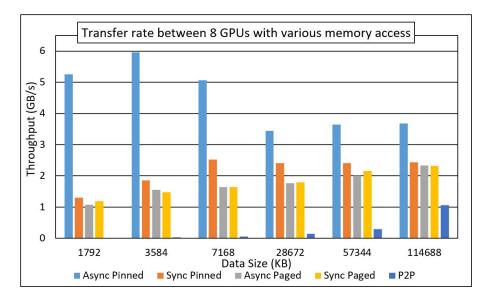

| 6.7  | Transfer rate between 2 GPUs with various memory access            | 94 |

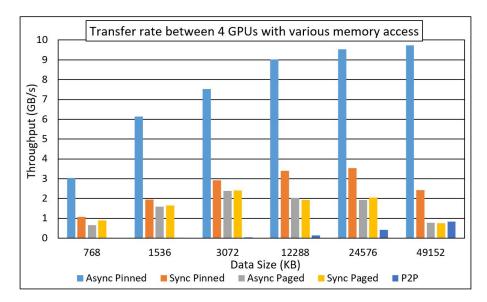

| 6.8  | Transfer rate between 4 GPUs with various memory access            | 94 |

| 6.9  | Transfer rate between 8 GPUs with various memory access            | 95 |

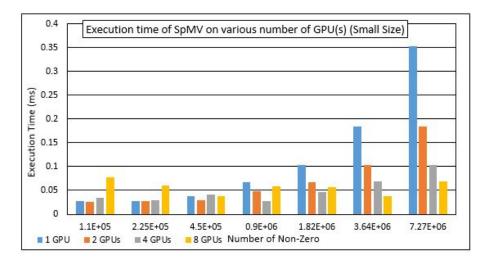

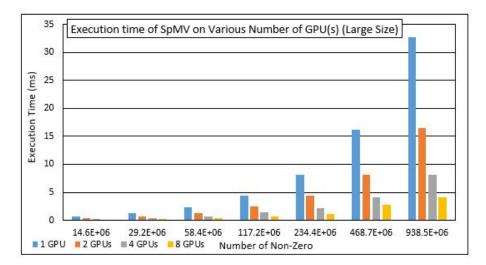

| 6.10 | Execution time of SpMV with Various Number of GPU(s) $\ . \ . \ .$ | 97 |

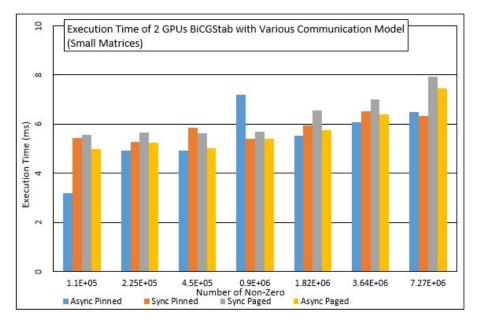

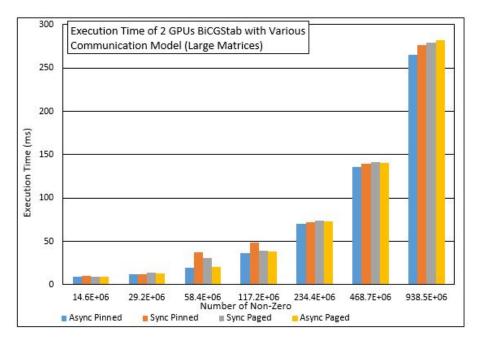

| 6.11 | Execution Time of 2 GPUs BiCGStab with Various Communication       |    |

|      | Model                                                              | 97 |

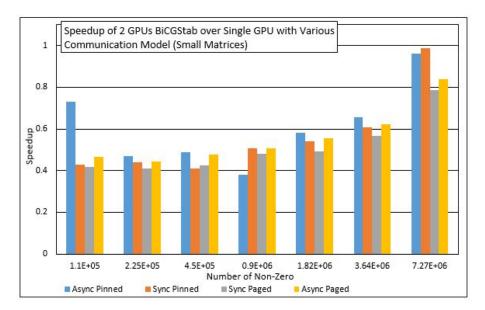

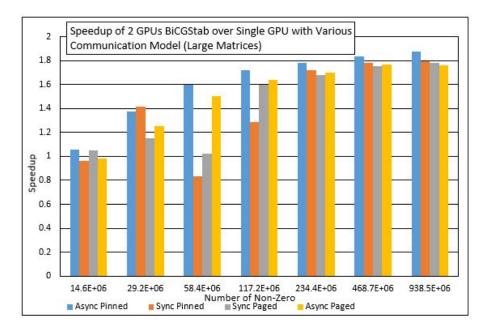

| 6.12 | Speedup of 2 GPUs BiCGStab with Various Communication Model        |    |

|      | over Single GPU                                                    | 99 |

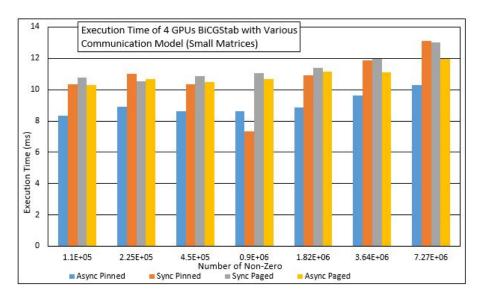

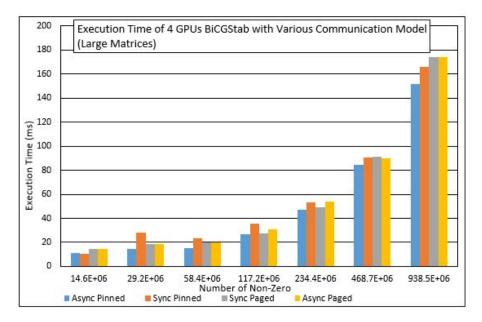

| 6.13 | Execution Time of 4 GPUs BiCGStab with Various Communication    |     |

|------|-----------------------------------------------------------------|-----|

|      | Model                                                           | 99  |

| 6.14 | Speedup of 4 GPUs BiCGStab with Various Communication Model     |     |

|      | over Single GPU                                                 | 101 |

| 6.15 | Execution Time of 8 GPUs BiCGStab with Various Communication    |     |

|      | Model                                                           | 101 |

| 6.16 | Speedup of 8 GPUs BiCGStab with Various Communication Model     |     |

|      | over Single GPU                                                 | 102 |

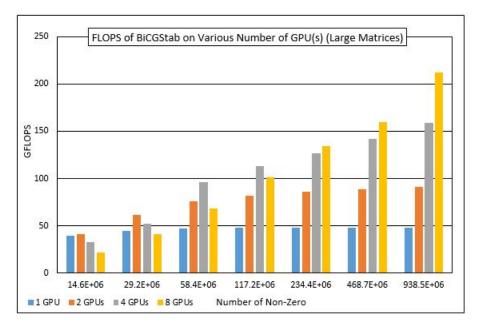

| 6.17 | GFLOPS of BiCGStab on Various Number of $\operatorname{GPU}(s)$ | 102 |

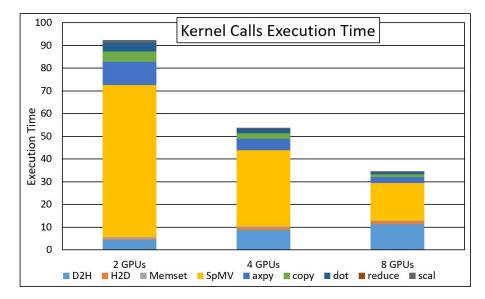

| 6.18 | Number of Kernel Calls on BiCGStab                              | 106 |

| 6.19 | Number of Arithmetic Operation in BiCGStab                      | 106 |

| 6.20 | Kernel Calls Execution Time of BiCGStab on various number of    |     |

|      | GPUs                                                            | 106 |

| 6.21 | Kernel Calls Execution Time Percentage of BiCGStab              | 107 |

# LIST OF FIGURES

| 2.1  | Growth of GPU computing [9]                                                                                                                    | 8         |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 2.2  | SMX on Kepler Architecture [10]                                                                                                                | 9         |

| 2.3  | Warp Scheduler [10]                                                                                                                            | 10        |

| 2.4  | Hyper-Q on Tesla Kepler K80 [10]                                                                                                               | 11        |

| 2.5  | RDMA GPUDirect [10]                                                                                                                            | 12        |

| 2.6  | Description of CUDA Architecture [11]                                                                                                          | 13        |

| 2.7  | CUDA Threads and Memory Hierarchy [10]                                                                                                         | 14        |

| 2.8  | CPU-GPU communication schemes (a) inside CPU memory (b)                                                                                        |           |

|      | between CPUs memory (c) between GPUs memory in same host                                                                                       |           |

|      | (d) between GPUs memory in different host (e) CPU memory to                                                                                    |           |

|      | GPU memory and vice versa in same system (f) CPU memory to                                                                                     |           |

|      | GPU memory and vice versa in the different system [13] $\ldots$ .                                                                              | 17        |

| 2.9  | Paged host memory scheme (left), Pinned host memory scheme                                                                                     |           |

|      | $(right) \ldots \ldots$ | 18        |

| 2.10 | PEX 8747 48-Lane, 5-Port PCI Express                                                                                                           | 18        |

| 3.1  | Examples of Sparse Matrices [2]                                                                                                                | 22        |

| 3.2  | COO representation of A with arrays row, col, and data [17]                                                                                    | <br>23    |

| 3.3  | COO SpMV kernel memory access pattern with the arrays row col,                                                                                 |           |

|      | and data [17]                                                                                                                                  | 24        |

| 3.4  | CSR representation of A with arrays ptr, indices, and data [17].                                                                               | - 1<br>25 |

| 3.5  | CSR sparse matrix format using serial CPU SpMV kernel [17]                                                                                     | 25<br>25  |

| 0.0  | Usit sparse matrix format using serial Or O spint v kerner $[17]$ .                                                                            | $_{20}$   |

| 3.6  | $\operatorname{CSR}\operatorname{SpMV}$ kernel memory access pattern using arrays indices and |    |

|------|-----------------------------------------------------------------------------------------------|----|

|      | data [17]                                                                                     | 25 |

| 3.7  | ELL representation of A with arrays data and indices $[17]$                                   | 27 |

| 3.8  | Example of the matrix that is suitable with ELL form<br>at $[17]$                             | 27 |

| 3.9  | Example of the matrix that is not suitable for ELL form<br>at $\left[17\right]$ .             | 28 |

| 3.10 | ELL sparse matrix format SpMV kernel [17]                                                     | 29 |

| 3.11 | Memory access pattern of ELL SpMV and its data linearization [17]                             | 29 |

| 3.12 | Five diagonals sparse matrix [17]                                                             | 30 |

| 3.13 | DIA representation of A in arrays data and offsets $[17]$                                     | 31 |

| 3.14 | Sparse matrix type that not suited well with DIA form<br>at $[17]$                            | 32 |

| 3.15 | DIA SpMV memory access pattern and data array linearization [17]                              | 32 |

| 3.16 | DIA sparse matrix format SpMV kernel [17]                                                     | 33 |

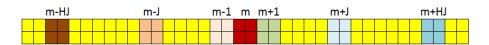

| 5.1  | Example of General Hepta (GH) row                                                             | 56 |

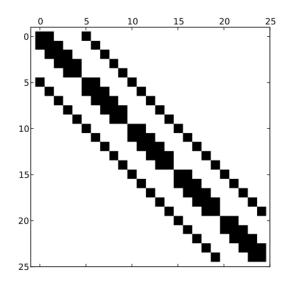

| 5.2  | Example of GH matrix with parameter J=2, H=4, I=2, Nc=2 $$ .                                  | 57 |

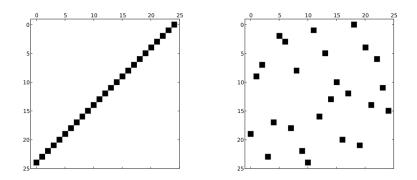

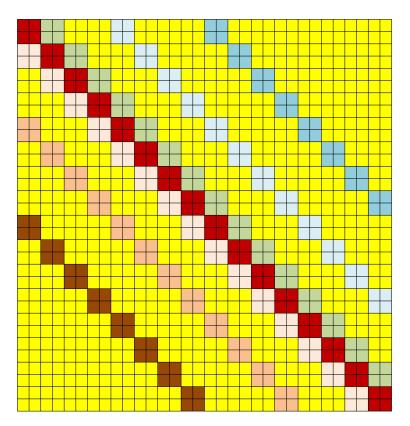

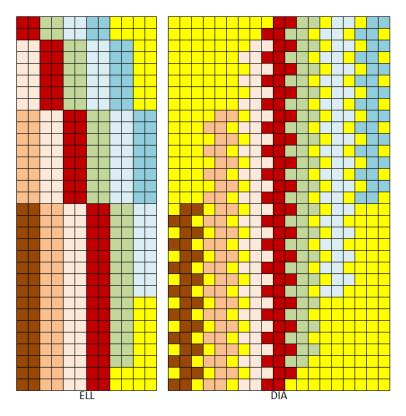

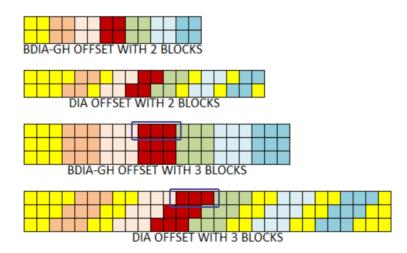

| 5.3  | Comparison between ELL and DIA storage format for GH $\ . \ . \ .$                            | 58 |

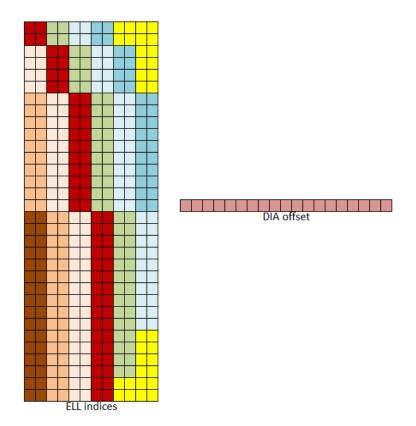

| 5.4  | Comparison between ELL indices and DIA offset $\ .\ .\ .\ .$ .                                | 59 |

| 5.5  | Proposed BDIA-GH storage format that contains two array: data                                 |    |

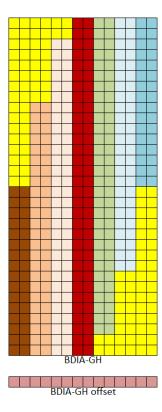

|      | and offset                                                                                    | 60 |

| 5.6  | Comparison between BDIA-GH and DIA in one row of block                                        | 61 |

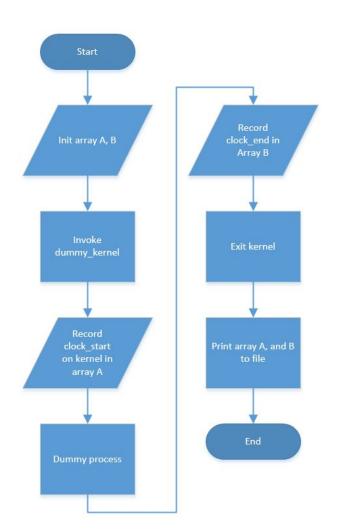

| 5.7  | Flowchart of block dispatching order                                                          | 74 |

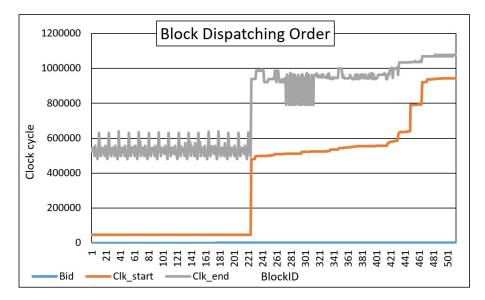

| 5.8  | Block dispatching order result                                                                | 75 |

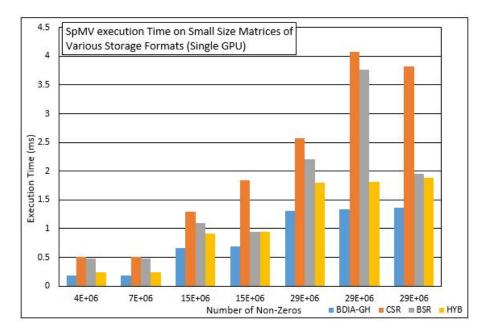

| 6.1  | SpMV execution Time on Small Size Matrices of Various Storage                                 |    |

|      | Formats (Single GPU)                                                                          | 90 |

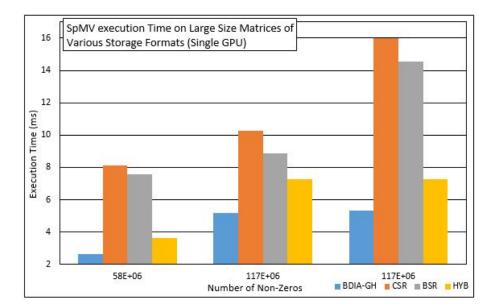

| 6.2  | SpMV execution Time on Large Size Matrices of Various Storage                                 |    |

|      | Formats (Single GPU)                                                                          | 91 |

| 6.3  | Speedup of BDIA-GH SpMV over Other Storage Formats (Single                                    |    |

|      | GPU)                                                                                          | 93 |

| 6.4  | SpMV FLOPS of Various Storage Formats on Small Matrices                                       |    |

|      | (Single GPU)                                                                                  | 95 |

| 6.5  | SpMV FLOPS of Various Storage Formats on Large Matrices                                         |     |

|------|-------------------------------------------------------------------------------------------------|-----|

|      | (Single GPU)                                                                                    | 96  |

| 6.6  | BiCGStab Execution Time on Small Size GH Matrices of Various                                    |     |

|      | Storage Formats (Single GPU)                                                                    | 98  |

| 6.7  | BiCGStab Execution Time on Large Size GH Matrices of Various                                    |     |

|      | Storage Formats (Single GPU)                                                                    | 100 |

| 6.8  | Speedup of BiCGStab BDIA-GH over Other Storage Formats                                          |     |

|      | (Single GPU)                                                                                    | 103 |

| 6.9  | FLOPS on Small Size GH Matrices of BiCGStab in Various Storage                                  |     |

|      | Format (Single GPU)                                                                             | 104 |

| 6.10 | FLOPS on Large Size GH Matrices of BiCGStab in Various Storage                                  |     |

|      | Format (Single GPU)                                                                             | 104 |

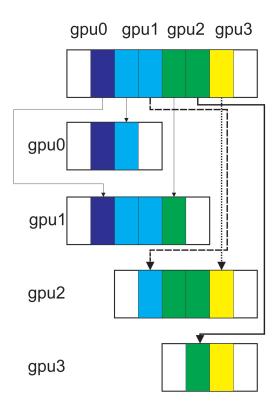

| 6.11 | Memory transfer routes on 4 GPUs implementation                                                 | 105 |

| 6.12 | Peer-to-Peer GPUDirect 4 GPUs implementation. (a) right                                         |     |

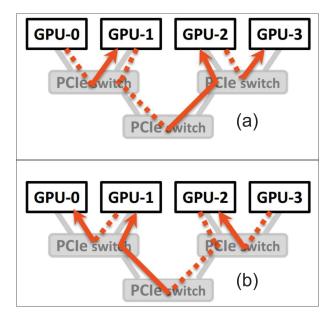

|      | communication, (b) left communication                                                           | 107 |

| 6.13 | Transfer rate between 2 GPUs with various memory access $\ldots$ .                              | 108 |

| 6.14 | Transfer rate between 4 GPUs with various memory access $\ . \ . \ .$                           | 108 |

| 6.15 | Transfer rate between 2 GPUs with various memory access $\ldots$ .                              | 109 |

| 6.16 | Execution time of SpMV on various number of $\operatorname{GPU}(\operatorname{s})$ (Small Size) | 109 |

| 6.17 | Execution time of SpMV on various number of $\operatorname{GPU}(\operatorname{s})$ (Large Size) | 110 |

| 6.18 | Execution Time of 2 GPUs BiCGStab with Various Communication                                    |     |

|      | Model (Small Size)                                                                              | 110 |

| 6.19 | Execution Time of 2 GPUs BiCGStab with Various Communication                                    |     |

|      | Model (Large Size)                                                                              | 111 |

| 6.20 | Speedup of 2 GPUs BiCGStab over Single GPU with Various                                         |     |

|      | Communication Model (Small Size)                                                                | 111 |

| 6.21 | Speedup of 2 GPUs BiCGStab over Single GPU with Various                                         |     |

|      | Communication Model (Large Size)                                                                | 112 |

| 6.22 | Execution Time of 4 GPUs BiCGStab with Various Communication                                    |     |

|      | Model (Small Size)                                                                              | 112 |

| 6.23 | Execution Time of 4 GPUs BiCGStab with Various Communication                            |     |

|------|-----------------------------------------------------------------------------------------|-----|

|      | Model (Large Size)                                                                      | 113 |

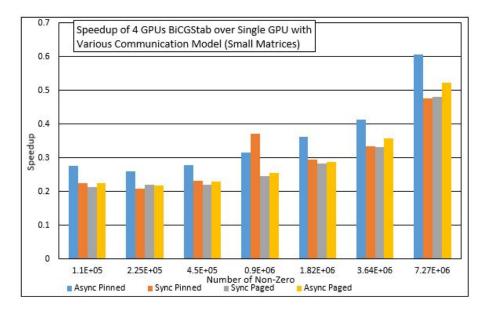

| 6.24 | Speedup of 4 GPUs BiCGStab over Single GPU with Various                                 |     |

|      | Communication Model (Small Size)                                                        | 113 |

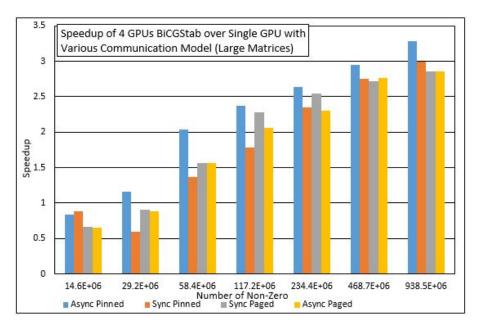

| 6.25 | Speedup of 4 GPUs BiCGStab over Single GPU with Various                                 |     |

|      | Communication Model (Large Size)                                                        | 114 |

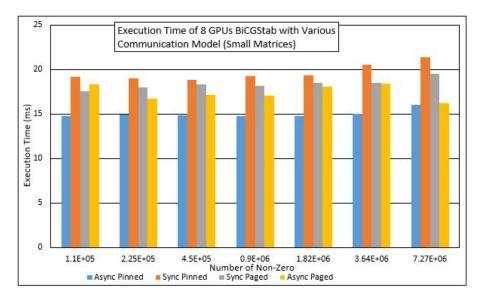

| 6.26 | $\label{eq:communication} Execution Time of 8 GPUs BiCGStab with Various Communication$ |     |

|      | Model (Small Size)                                                                      | 114 |

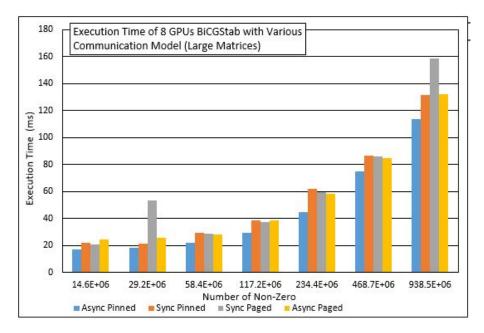

| 6.27 | Execution Time of 8 GPUs BiCGStab with Various Communication                            |     |

|      | Model (Large Size)                                                                      | 115 |

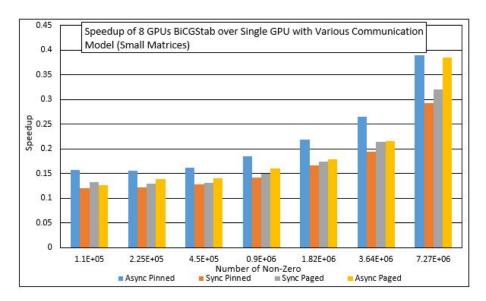

| 6.28 | Speedup of 8 GPUs BiCGStab over Single GPU with Various                                 |     |

|      | Communication Model (Small Size)                                                        | 115 |

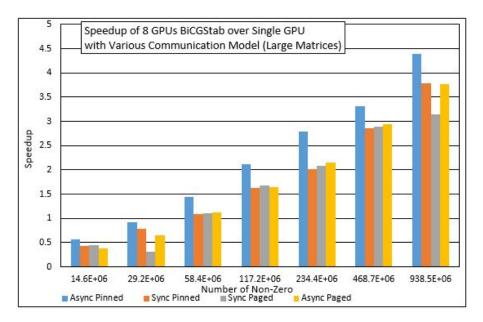

| 6.29 | Speedup of 8 GPUs BiCGStab over Single GPU with Various                                 |     |

|      | Communication Model (Large Size)                                                        | 116 |

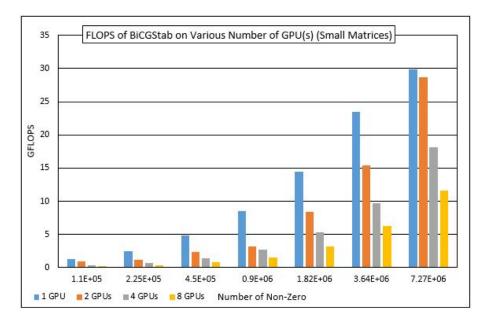

| 6.30 | FLOPS of BiCGStab on Various Number of GPU(s) (Small Size)                              | 116 |

| 6.31 | FLOPS of BiCGStab on Various Number of GPU(s) (Large Size)                              | 117 |

| 6.32 | Kernel Calls Execution Time of BiCGStab on various number of                            |     |

|      | GPUs                                                                                    | 117 |

## THESIS ABSTRACT

NAME: Lutfi Aziz Firdaus

TITLE OF STUDY: CUDA OPTIMIZATION OF A CLASS OF ITERATIVE LINEAR ALGEBRA SOLVERS

MAJOR FIELD: COMPUTER ENGINEERING

DATE OF DEGREE: May 2017

Modern scientific computing focuses on developing applications using GPU (Graphics Processing Unit) because of the rapid growth in computing power and drop in the price of massively parallel accelerators. The growth in emerging architectures is also supported with powerful programming languages like the Compute Unified Device Architecture (CUDA) released by NVIDIA. The abundant parallel arithmetic hardware in GPUs largely exceeds that available with multi-core CPU (Central Processing Unit). Science simulations heavily depend on Iterative linear algebra solvers (ILAS). ILAS is one of the algorithms that could exploit this GPU massive parallelism provided by GPGPU (General Purpose Graphics Processing Unit) to accelerate science simulation. BiCGStab (Biconjugate Gradient Stabilized) is a relatively general solver for solving sparse systems of

linear equations. BiCGstab is selected on this thesis to solve on implementing the reservoir simulation. The characteristic matrices that come from reservoir simulation allow defining the pattern and properties of the above matrix. TheGeneral Hepta (GH) sparse matrix is found to be the matrix pattern for reservoir simulation. GH must be handled effectively and efficiently especially for Sparse Matrix-Vector Multiplication (SpMV) that takes most of the computation time in the simulation. To optimize the storage, a new sparse matrix storage format called Block Diagonal General Hepta (BDIA-GH) is proposed in this work to accelerate the corresponding SpMV. Evaluation shows that the speedup of using BDIA-GH in the SpMV on single GPU is up to 3.0 compared to other storages like CSR (Compressed Storage Row) format, 2.8 compared to BSR (Block Compressed Storage Row) format, and 1.4 compared to HYB format. The optimization of SpMV, leads to the improvement on BiCGStab on a single GPU by 2.64 speedup over CSR, 2.4 over BSR, and 1.35 over HYB. With multi-GPU, the SpMV almost scaled perfectly. Speedup of 2 is gained by 2 GPUs over single GPU, 3.97 for 4 GPUs, and 7.97 for 8 GPUs. Multi-GPU BiCGStab also proposed as a novel approach to improve the computing performance. Speedup with 1.88 factor gained by using 2 GPUs over single GPU, and 3.28 by using 4 GPUs, and 4.38 by using 8 GPUs. This work contributes to development of scalable SpMV and BiCGstab for reservoir simulation on many-core.

#### ملخص الرسالة

الاسم الكامل: لطفى عزيز فردوس عنوان الرسالة: كودا أوبتيميز اتيون أوف كلاس أوف إيتير اتيف لينير ألجيبر اسولفرس التخصص: هندسة الحاسوب تاريخ الدرجة العلمية: شعبان ١٤٣٨ هـ

تركز الحوسبة العلمية الحديثة على تطوير التطبيقات باستخدام وحدة معالجة الرسومات (GPU) بسبب التطور السريع في قوة الحوسبة وانخفاض سعر المسرعات المتوازية بشكل كبير. التطور في عمارة الحاسب الناشئة مدعوم أيضا من لغات برمجة متطورة مثل معمارية حوسبة الاجهزة الموحدة (كودا) (CUDA) الصادرة عن نيفيديا. الاجزاء المسؤولة عن العمليات الحسابية المتوازية المتوفرة في وحدات معالجة الرسومات تتجاوز إلى حد كبير تلك المتوفرة في وحدة المعالجة المركزية متعددة النواة. تعتمد عمليات المحاكاة العلمية بشكل كبير على الطريقة التكرارية في حل معادلات الجبر الخطي (ILAS). (ILAS) هي واحدة من الخوارزميات التي يمكن أن تستغل هذا التوازي الضخم المقدم من وحدة معالجة الرسومات التي تقدمها وحدة معالجة الرسومات للاغراض العامة لتسريع المحاكاة العلمية. طريقة المرافق الثنائي المتدرج الثابت BiCGStab هوحل عام نسبيا لحل المعادلات الخطية للانظمة الخفيفة. اختيارنا طريقة المرافق الثنائي المتدرج الثابت BiCGStab في هذه الأطروحة لحل ينفذ على محاكاة الخزانات المائية الكامنة. خصائص المصفوفات المرتبطة بمحاكاة الخزانات المائية الكامنة تسمح بتحديد نمط وخصائص المصفوفة أعلاه. المصفوفة العامة السباعية الشبه صفرية تمثل نمط مصفوفة المحاكاة للخزانات المائية الكامنة. المصفوفة السباعية يجب التعامل معها بشكل فعال وكفء وخاصة بالنسبة لعمليات الضرب بين المصفوفة والمتجه الشبه صفري (SpMV) والتي تأخذ معظم الوقت الحسابي في المحاكاة. لتحسين واستغلال التخزين، اقترحنا في هذا العمل صيغة جديدة لتخزين المصفوفة الشبه صفرية يسمى المصفوفة السباعية القطرية القاطاعات (BDIA-GH) لتسريع عمليات الضرب بين المصفوفة والمتجه الشبه صفري(SpMV) . التقييم اوضح أن سرعة استخدام المصفوفة السباعية القطرية القاطاعات BDIA-GH لحل عمليات الضرب بين المصفوفة والمتجه الشبه صفري على وحدة المعالجة الرسومية الواحدة يصل إلى ثلاثة اضعاف مقارنة مع غيرها من طرق التخزين مثل ضغط التخزين المعتمد على الصف CSR ، CSR اضعاف مقارنة بضغط التخزين المعتمد على قطاعات الصف BSR ، و 1.4 مقارنة ب صيغة الخليط HYB . تحسين عمليات الضرب بين المصفوفة والمتجه الشبه صفري (SpMV) ، يؤدي إلى تحسين طريقة المرافق الثنائي المتدرج الثابت BiCGStab على وحدة معالجة رسومية واحدة ب 2.64 ضعف على ضغط التخزين المعتمد على الصف CSR، 2.4 اضعاف مقارنة بضغط التخزين المعتمد على قطاعات الصف BSR ، و 1.35 مقارنة ب صيغة الخليط HYB . مع تعدد وحدات المعالجة الرسومية، عمليات الضرب بين المصفوفة والمتجه الشبه صفري (SpMV) وتتناسب بشكل مناسب جدا. التسريع يصل الى 2 باستخدام وحدتى معالجة رسومية مقارنة بوحدة معالجة رسومية واحدة، و 3.97 ل 4 وحدات معالجة الرسومات، و 7.97 ل 8 وحدات معالجة الرسومات. طريقة المرافق الثنائي المتدرج الثابت BiCGStab على وحدات معالجة رسومية متعددة اقترحت ايضا كنهج جديد لتحسين أداء الحوسبة. ليصل الى 1.88 ضعف باستخدام وحدتي معالجة رسومات مقارنة بوحدة معالجة رسومية، و 3.28 باستخدام 4 وحدات معالجة الرسومات، و 4.38 باستخدام 8 وحدات معالجة رسومات. ويسهم هذا العمل في تطوير وتحسين عمليات الضرب بين المصفوفة والمتجه الشبه صفري (SpMV) و طريقة المرافق الثنائي المتدرج الثابت BiCGStab لمحاكاة الخزانات المائية الكامنة على المعالجات متعددة النواة.

## CHAPTER 1

## INTRODUCTION

Modern scientific and engineering applications are increasing in size and complexity due to the need for higher resolution in large scale modeling and simulations. These applications dominant a wide range of daily engineering and scientific applications. Large scale scientific simulations generally need high-performance computing to accelerate the simulation time and/or increasing the simulation accuracy. Solving large system of linear equations requires a lot of computation time using both direct solvers and iterative approaches. Most science simulations spend a significant fraction of time in the solver algorithm [1].

Usually, two solver approaches are most commonly used, which are the direct and the iterative linear algebra methods. The direct methods are more reliable and more accurate but require much more storage than the other methods, which make them difficult to scale. Excessive transfer and storage of data in a massive parallel computing system may easily become the bottleneck in addition to the high computational complexity. The iterative methods are more scalable, so large sparse systems have abundant data parallelism, which favor the iterative methods over the direct methods especially when a high accuracy is not needed. The Krylov subspace solvers [1] represents the iterative methods to solve large sparse linear systems. Specifically, the Bi-conjugate Gradient Stabilized (BiCGstab) algorithm is one example of techniques that belongs to the above sub-space of solvers. The most computational effort in science simulation is the solving of large sparse linear systems. These approaches require linear algebra operations such as matrix-vector multiplication, norm, dot product, vector scaling, and summation of vectors [2].

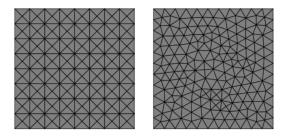

Modeling of various modern scientific and engineering applications requires repetitive solving of a large sparse system of linear equations. Hence the use of efficient sparse matrix data structure is the pre-requisite for the efficient implementation of these application on wide SIMD (Single Instruction Multiple Data) such as GPUs and other many core. Several bottlenecks which may limit the performance of the GPUs which are the low efficiency due to the sparse structure of above matrices and the increased overhead due to the irregular accesses to the memory which may cause a limitation on the memory bandwidth [3].

Offloading all computation of matrix and vectors to the GPU is considered a straightforward method to utilize the GPU accelerator to implement a Krylov subspace solver using the functions available in the numerical libraries. Although, this approach provides good improvement in the performance comparing to CPU-based implementation, sometimes the high capability of these accelerators is not efficiently exploited due to the limitations caused by the operations of the linear algebra functions available in the numerical libraries [4], [5].

The GPU acceleration provides tremendous computational power provided that it is properly programmed to take advantage of all its abundant parallelism [6]. The Compute Unified Device Architecture (CUDA) programming language is developed by NVIDIA. CUDA is designed as a general purpose programming model [2] which has enough control of the hardware to control the explicit memory system, distribute the work over the available parallel compute units, and provide some tools for run-time profiling.

The sparse matrix-vector multiply (SpMV) is considered one of the most important computational and time-consuming kernel for a wide range of engineering and scientific applications ranging from structural mechanics to quantum physics including fluid dynamics. Thus, to achieve scalable performance for these applications, it is important to optimize the SpMV by developing customized sparse matrix storage format and efficiently utilizing the underlying GPU architecture to optimize its operations.

To decrease the overhead and avoid the bottlenecks mentioned above, many studies have proposed some storage formats for sparse matrices to take advantage of their data layouts in optimizing the memory access pattern and to reduce the matrix storage space in GPU memory. Each of these formats has different storage requirements and computational properties.

### **1.1** Iterative Methods

Solving systems of linear equations in scientific computing is one of the most common encountered problems [7]. Given a known matrix A and a known vector b, the problem is to find a solution x satisfying:

$$Ax = b \tag{1.1}$$

Gaussian Elimination (GE) is the most straightforward approach to solve the above system of linear equations. Although GE provides more accurate solution compared to other methods, it has one important drawback which is the excessive storage which is a major problem to scalability. This problem can be alleviated by iterative methods.

Iterative methods are not very accurate compared to direct methods but have abundant parallelism and can be engineered to produce a refined solution. The solution of this method could approach the exact solution within the margin of error determined by the user. By using initial guess as the value of x, the xmay converge to an exact solution using more iterations. On every iteration, the solution will be updated and the margin of error will be reduced if some conditions are satisfied such the use of proper preconditioning.

### 1.2 Problem Statement

The high-performance computing technology nowadays is escalating rapidly. Devices and architectures are improving along with so many research conducted to maximize computer architecture performance. But programming with optimal code on high performance computing is not easy. Certain problems usually need to be solved by considering the detailed knowledge of the hardware. There is no general solution for implementing all of the possible programming optimizations to account for the hardware complexity. That is also the case for iterative linear algebra solver with sparse matrix vector multiplication. Several storage formats have been proposed to accommodate many kinds of sparse matrices, but still none of them provide the solution in best practices. Implementation on BiCGStab as the chosen iterative linear algebra solver also needs to be optimized. That is why several questions arise to address these problems. Here are some critical questions that our work has attempted to answer:

- What is the best storage scheme for sparse matrix on reservoir simulation?

- How to implement matrix vector multiplication that suits well with the storage scheme proposed for reservoir simulation?

- How to optimize the implementation of the BiCGStab to utilize the available hardware using CUDA?

### **1.3** Contributions to this Topic

In this thesis we developed a customized storage format that is suitable to solve reservoir simulation problems. The storage is called BDIA-GH (Block DIA General-Hepta) Format. Sparse matrix-vector multiplication SpMV uses the above storage format as one of its problem optimizations. We first present a methodology for optimizing SpMV and BiCGStab algorithm using CUDA programming for one GPU. Next, we extend our work to a cluster of GPUs and present a methodology for Multi-GPU implementation of SpMV and BiCGStab using a shared virtual memory at the server level. We evaluate performance using execution time, speedup, and Flops performance and assess the scalability of the proposed implementations. Also to the best of our knowledge, our work is the first implementation BiCGStab on multi-GPU with several optimizations.

### CHAPTER 2

## BACKGROUND

## 2.1 GPU and CUDA

#### 2.1.1 GPU Architecture

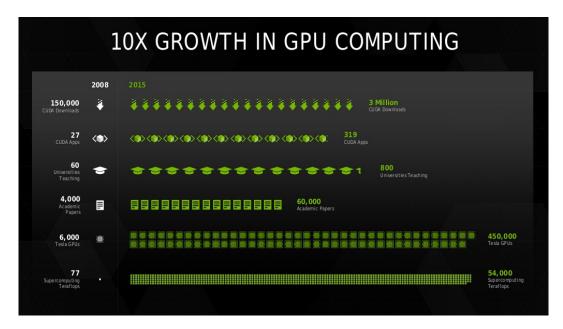

The new architecture of GPU with Tesla leads to very highly efficient general-purpose parallel computing application [8]. Because this GPU architecture could be programmed directly in C with CUDA, the number of research on this general-purpose GPU (GPGPU) computing escalates very quickly (figure 2.1).

This programmability of GPU in C with CUDA is available in many kinds of computing devices like servers, workstations, desktops, and laptop. For example, as shown in Table 2.1, Tesla K80 that has CUDA computing capability of 3.7 has 13 Streaming Multiprocessors (MP) that called as SMX with 192 single-precision CUDA Cores on each SMX (figure 2.2).

Each Tesla K80 GPU has a total 2496 single-precision CUDA Cores. Each

Figure 2.1: Growth of GPU computing [9]

SMX has 2048 maximum number of threads. It means maximum number of active thread at a time is:

$$N_{max\_active\_threads} = N_{SMX} \times N_{active\_thread/SM} = 13 \times 2048 = 26624$$

(2.1)

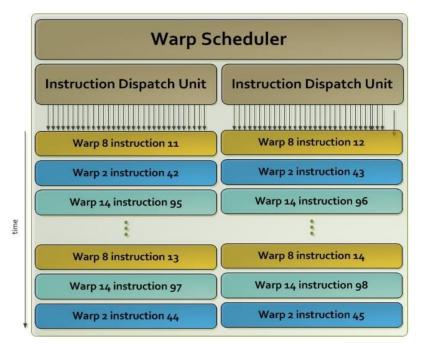

Every 32 threads are grouped as one warp. In every SMX, there are 4 warp schedulers with 2 instruction dispatch unit for each scheduler to schedule the work on warps (figure 2.3).

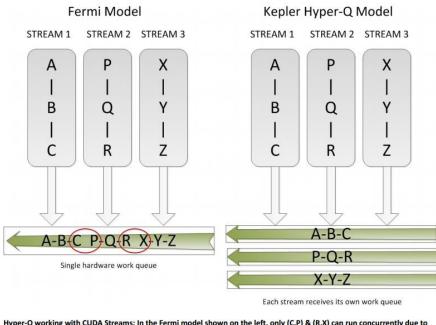

For each GPU, the global memory is 11441 MBytes and shared memory per block is 49152 bytes. There are also 64 double-precision units, 32 special function units (SFU), and 32 load/store unit (LD/ST). On Kepler architecture, the CUDA cores could run tasks simultaneously with Hyper-Q feature (figure 2.4). Instead of using only one single hardware work queue for all the streams, the Kepler architecture supports each stream to work in parallel using separate work queues.

|      |       |       |                | _     | -                                   |        |                |        | tructa | on Ca          |         |       |         |        | -              |       |         |       | -  |

|------|-------|-------|----------------|-------|-------------------------------------|--------|----------------|--------|--------|----------------|---------|-------|---------|--------|----------------|-------|---------|-------|----|

|      | -     |       | eduler         | te b  | Warp Scheduler<br>Dispatch Dispatch |        |                |        |        | Warp Scheduler |         |       |         |        | Warp Scheduler |       |         |       |    |

| Di   | spate |       | Dispai         | icn   | D                                   | spate  |                | Dispat | icn    | DI             | spate   | n     | Dispai  | icn    | U              | spate | in      | Dispa | cn |

|      |       |       |                | Regi  | ster                                | File ( | 65,536         | x 32-  | bit G  | K110           | )   (1: | 31,07 | 2 x32-l | oit Gl | (210)          |       |         |       |    |

| ÷    | +     | +     | +              | +     | +                                   | +      | +              | +      | +      | +              | +       | +     | +       | +      | Page 1         | +     | +       | +     | +  |

| Core | Core  | Core  | <b>DP Unit</b> | Core  | Core                                | Core   | DP Unit        | LD/ST  | SFU    | Core           | Core    | Core  | DP Unit | Core   | Core           | Core  | DP Unit | LD/ST | SF |

| Core | Core  | Core  | DP Unit        | Core  | Core                                | Core   | DP Unit        | LD/ST  | SFU    | Core           | Core    | Core  | DP Unit | Core   | Core           | Core  | OP Unit | LD/ST | SF |

| Core | Core  | Core  | DP Unit        | Core  | Core                                | Core   | DP Unit        | LD/ST  | SFU    | Core           | Core    | Core  | DP Unit | Соге   | Core           | Core  | DP:Unit | LD/ST | SF |

| Core | Core  | Core  | DP Unit        | Core  | Core                                | Core   | <b>BP Unit</b> | LD/ST  | SFU    | Core           | Core    | Core  | DP Unit | Core   | Core           | Core  | DP Unit | LD/ST | SF |

| Core | Core  | Core  | DP Unit        | Core  | Core                                | Core   | DP Unit        | LD/ST  | SFU    | Core           | Core    | Core  | DP Unit | Core   | Core           | Core  | DP Unit | LD/ST | SF |

| Core | Core  | Core  | DP Unit        | Core  | Core                                | Core   | DP Unit        | LD/ST  | SFU    | Core           | Core    | Core  | DP Unit | Core   | Core           | Core  | DP Unit | LD/ST | SF |

| Core | Core  | Core  | DP Unit        | Core  | Core                                | Core   | DP Unit        | LD/ST  | SFU    | Core           | Core    | Core  | DP Unit | Core   | Core           | Core  | DP Unit | LD/ST | SF |

| Core | Core  | Core  | DP Unit        | Core  | Core                                | Core   | DP:Unit        | LD/ST  | SFU    | Core           | Core    | Core  | DP Unit | Core   | Core           | Core  | DP Unit | LD/ST | SF |

| Core | Core  | Core  | DP Unit        | Core  | Core                                | Core   | DP Unit        | LD/ST  | SFU    | Core           | Core    | Core  | DP Unit | Core   | Core           | Core  | DP Unit | LD/ST | SF |

| Core | Core  | Core  | DP Unit        | Core  | Core                                | Core   | DP Unit        | LD/ST  | SFU    | Core           | Core    | Core  | DP Unit | Core   | Core           | Core  | DP Unit | LD/ST | SF |

| Core | Core  | Core  | DP Unit        | Core  | Core                                | Core   | DP Unit        | LD/ST  | SFU    | Core           | Core    | Core  | DP Unit | Core   | Core           | Core  | DP Unit | LD/ST | SF |

| Core | Core  | Core  | DP Unit        | Core  | Core                                | Core   | DP Unit        | LD/ST  | SFU    | Core           | Core    | Core  | DP Unit | Core   | Core           | Core  | DP Unit | LD/ST | SF |

| Core | Core  | Core  | DP Unit        | Core  | Core                                | Core   | DP Unit        | LD/ST  | SFU    | Core           | Core    | Core  | DP Unit | Core   | Core           | Core  | DP Unit | LD/ST | SF |

| Core | Core  | Core  | DP Unit        | Core  | Core                                | Core   | DP Unit        | LD/ST  | SFU    | Core           | Core    | Core  | DP Unit | Core   | Core           | Core  | DP Unit | LD/ST | SF |

| Core | Core  | Core  | DP Unit        | Core  | Core                                | Core   | DP Unit        | LD/ST  | SFU    | Core           | Core    | Core  | DP Unit | Core   | Core           | Core  | OP Unit | LD/ST | SF |

| Core | Core  | Core  | DP Unit        | Core  | Core                                | Core   | DP Unit        | LD/ST  | SFU    |                |         | Core  | DP Unit | Core   | Core           | Core  | DP Unit | LD/ST | SF |

|      | (     | 64 KI | B Shar         | ed Me | emor                                | y / L1 | l Cache        |        |        | ct Ne<br>(128  |         | Share | ed Mem  | iory / | L1 C           | ache  | GK21    | 0)    |    |

|      |       |       |                |       |                                     |        | 48 K           | B Rea  | ad-O   | niy D          | ata C   | ache  | )       |        |                |       |         |       |    |

|      | Tex   |       | Tex            |       |                                     | Tex    |                | Tex    | (      |                | Tex Tex |       | (       | Tex    |                | Tex   |         |       |    |

|      | Tex   |       | Tex            |       |                                     | Tex    |                | Tex    | ¢      |                | Tex     |       | Tex     | ¢      |                | Tex   |         | Tex   |    |

SMX: 192 single-precision CUDA cores, 64 double-precision units, 32 special function units (SFU), and 32 load/store units (LD/ST).

Figure 2.2: SMX on Kepler Architecture [10]

| Device Specification for Tesla K80             |                            |  |  |  |  |  |  |

|------------------------------------------------|----------------------------|--|--|--|--|--|--|

| CUDA Driver Version / Runtime Version          | 8.0 / 8.0                  |  |  |  |  |  |  |

| CUDA Capability Major/Minor version number:    | 3.7                        |  |  |  |  |  |  |

| Total amount of global memory:                 | 11441 MBytes               |  |  |  |  |  |  |

| (13) Multiprocessors, (192) CUDA Cores/MP:     | 2496 CUDA Cores            |  |  |  |  |  |  |

| GPU Max Clock rate:                            | 824 MHz (0.82 GHz)         |  |  |  |  |  |  |

| Memory Clock rate:                             | 2505 Mhz                   |  |  |  |  |  |  |

| Memory Bus Width:                              | 384-bit                    |  |  |  |  |  |  |

| L2 Cache Size:                                 | 1572864 bytes              |  |  |  |  |  |  |

| Total amount of constant memory:               | 65536 bytes                |  |  |  |  |  |  |

| Total amount of shared memory per block:       | 49152 bytes                |  |  |  |  |  |  |

| Total number of registers available per block: | 65536                      |  |  |  |  |  |  |

| Warp size:                                     | 32                         |  |  |  |  |  |  |

| Maximum number of threads per multiprocessor:  | 2048                       |  |  |  |  |  |  |

| Maximum number of threads per block:           | 1024                       |  |  |  |  |  |  |

| Max dimension size of a thread block (x,y,z):  | (1024, 1024, 64)           |  |  |  |  |  |  |

| Max dimension size of a grid size (x,y,z):     | (2147483647, 65535, 65535) |  |  |  |  |  |  |

| Support host page-locked memory mapping:       | Yes                        |  |  |  |  |  |  |

| Device has ECC support:                        | Enabled                    |  |  |  |  |  |  |

| Device supports Unified Addressing (UVA):      | Yes                        |  |  |  |  |  |  |

Table 2.1: Device Specification for Tesla K80

Each Kepler SMX contains 4 Warp Schedulers, each with dual Instruction Dispatch Units. A single Warp Scheduler Unit is shown above.

Figure 2.3: Warp Scheduler [10]

Hyper-Q working with CUDA Streams: In the Fermi model shown on the left, only (C,P) & (R,X) can run concurrently due to intra-stream dependencies caused by the single hardware work queue. The Kepler Hyper-Q model allows all streams to run concurrently using separate work queues.

Figure 2.4: Hyper-Q on Tesla Kepler K80 [10]

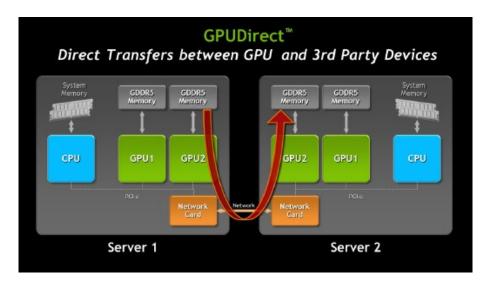

Other features that are supported by this architecture of Kepler is GPUDirect (figure 2.5) that enable multi-GPU system to communicate each other without the need of host to be involved. The communication goes through the NIC (Network Interface Card) using RDMA (Remote Direct Memory Access) feature.

#### 2.1.2 CUDA Programming

CUDA (Compute Unified Device Architecture) is a parallel computing platform and programming model for many programming languages including C/C++that enable the programmer to do programming in software and hardware side by using NVIDIA GPU.

A CUDA application could call a parallel program to be executed in NVIDIA

Figure 2.5: RDMA GPUDirect [10]

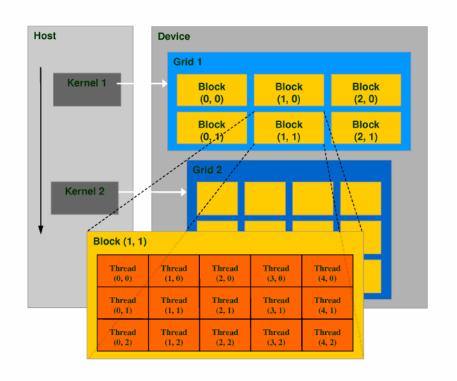

GPU CUDA enabled device that called as kernel. This kernel invoking many threads in parallel to work on the CUDA core inside GPU. A kernel is a set of thread block organized as a 1D, 2D, or 3D grid as shown in figure 2.6.

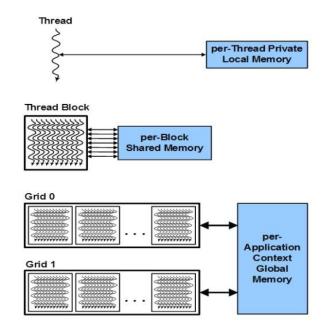

In every thread block, each thread executes the same program from the kernel and run all created threads in parallel using the SIMD (Single Instruction Multiple Data) model. Figure 2.7 shows that every thread has own private local memory, and the thread block has Shared Memory that could be accessed by every thread in the thread block. The global memory is accessed by all thread blocks in the grid. The mapping of CUDA application into the hardware is as follows: a GPU could execute one or more kernel grids. The SMX and CUDA cores in the GPU works on their assigned thread blocks.

Figure 2.6: Description of CUDA Architecture [11]

#### 2.1.3 Numerical Library

As parallel programming in CUDA is complex, researcher use numerical libraries for the basic algebra operators and many other math function to alleviate the problem of developing optimized code for all involved operations. This greatly improves the use of the NVIDIA CUDA for programming scientific computing applications. Therefore, there are many numerical libraries available to be used for linear algebra like BLAS and Sparse, FFT, seismic imaging, etc. Our focus in this thesis is on NVIDIA CUBLAS and CUSPARSE numerical libraries.

Figure 2.7: CUDA Threads and Memory Hierarchy [10]

#### 2.1.3.1 CUBLAS

CUBLAS (CUDA Basic Linear Algebra Subroutines) is a library of BLAS (Basic Linear Algebra Subroutines) that contains many operators for solving linear algebra problems using CUDA. The operation is divided into 3 level functions. Level-1 is scalar-vector operation, level-2 is matrix-vector operation, Level-3 is matrix-matrix operation. Dense matrix is assumed in this library. The examples operation of Level-1 operations are copying vector to other vector (e.g. cublasScopy), calculating dot product of two vectors (e.g. cublasSdot), axpy operation that multiply vector x by the scalar a and adds it to the vector y (e.g. cublasSaxpy). The examples for level-2 CUBLAS operations are symmetric banded matrix-vector multiplication (cublasSsbmv), symmetric packed matrix-vector multiplication (cublasSspmv), and many more. As for level-3, the example of operations are matrix-matrix multiplication (cublasSgemm),

symmetric matrix-matrix multiplication (cublasSsymm), hermitian matrix-matrix multiplication (CublassChemm), and others.

#### 2.1.3.2 CUSPARSE

CUDA Sparse Matrix library (CUSPARSE) is a library of BLAS (Basic Linear Algebra Solver) that contains many operators for solving sparse linear algebra problem using CUDA but specialized for working on sparse matrices. This library supports some general purpose sparse storage formats like ELL/HYB, CSR, Blocked CSR (BSR), and COO. These assume general sparse distribution of non-zeros (NZs) without specific regularity. Just like CUBLAS, CUSPARSE also has three level operation. Level-1 is sparse vector and dense vector operations, level-2 is sparse matrix and dense vector operations, and level-3 is sparse matrix and dense vector operation (tall matrix). There are also routines for sparse matrix by sparse matrix addition and multiplication. Also in this library, the storage formats conversion is available between COO to other formats and vice versa.

### 2.2 Multi-GPU Programming

Multi-GPU programming is becoming a new trend in recent years that attracts many researchers to carry out research on parallel application scalability over a set of cooperating GPUs [12] that communicate using share host memory or using some dedicated links. There are many advantages on implementing applications on Multi-GPU systems. Firstly, Multi-GPU could accelerate the computation of scientific applications. Secondly, Multi-GPU implementation could handle larger problem size because more memory is available. Furthermore, it could save power by using Multi-GPU on the same node so it could amortize the server cost among more GPUs.

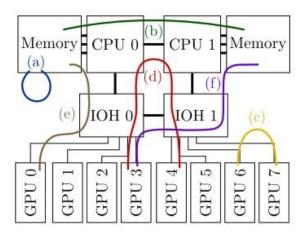

Performance of Multi-GPU systems depends on how communication could be done within GPUs and CPU(s). Figure 2.8 shows the memory transfer path in Multi-GPU communication [13]. This octo-GPU system illustrating 6 kinds of memory transfer paths. The type of data transfers are:

- 1. from the host memory to other host memory,

- 2. from host memory to own host memory,

- 3. from device memory to other device memories in the same host,

- 4. from device memory to other device memory in different host,

- 5. from device to host and host to device, and

- 6. from device to other hosts, and from other hosts to own device.

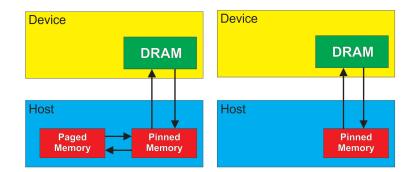

Besides the transfer paths, the communication model also determined by how the data will be allocated in the host memory. Figure 2.9 shows the difference between paged and pinned memory scheme in host. By default, the data in the host will be stored in paged memory. But in Tesla "Kepler" K80, as shown in table 2.1, it support host page-locked memory mapping. It means the data in the host could be stored in pinned memory so the transfer path from host to device or vice versa

Figure 2.8: CPU-GPU communication schemes (a) inside CPU memory (b) between CPUs memory (c) between GPUs memory in same host (d) between GPUs memory in different host (e) CPU memory to GPU memory and vice versa in same system (f) CPU memory to GPU memory and vice versa in the different system [13]

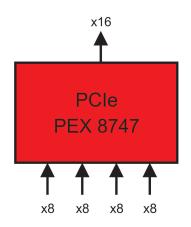

could go directly from pinned memory to DRAM instead of from paged memory to pinned memory and then stored into DRAM. But there is limitation of using pinned memory, because by default this memory is reserved as the temporary memory and if it reserved for certain data, then available physical memory to be used by other applications will be reduced. The other component that effected the performance of communication is PCI-e bridge. PEX 8747 (figure2.10) is PCI Express that has 48 lanes with 5 ports. Maximum latency of this PCI-e is 100ns. The configuration of this PCI-e is by using 4 port from the devices, and 1 port to the host. Each port from the device has 8 lanes, while the port to the host is 16 lanes. This number of ports could make some limitation to the number of connection from devices to host.

Figure 2.9: Paged host memory scheme (left), Pinned host memory scheme (right)

Figure 2.10: PEX 8747 48-Lane, 5-Port PCI Express

## 2.3 Biconjugate Gradient Stabilized Method (BiCGStab)

On solving a system of linear equations, there are two kinds of iterative methods. First is stationary iterative methods and the second is Krylov subspace methods that has more general implementation of matrices. Stationary iterative methods examples are Successive over-relaxation method, Gauss-Seidel method, and Jacobi method. While Krylov methods examples are generalized minimal residual method (GMRES), conjugate gradient (CG), and biconjugate gradient method (BiCG) that has variant called biconjugate gradient stabilized method (BiCGStab) that could be used for non-symmetric linear system and could be used when there is no transposed matrix available. This method also gives faster and smoother convergence than original BiCG [14].

From algorithm 1, we could see that there are several reductions and global writes that must be done cooperatively by all blocks and all kernels especially for Multi-GPU BiCGStab implementation. At the step 7, 11, and 14 the reductions are occurring. It means all the GPUs should communicate to gather the dot products. Before SpMV (at step 10 and 13), a global synchronization also has to be called to make sure the operation on SpMV using previous arrays is correct because of the communication between GPUs and CPU to transfer parts of the array from previous operation on devices to host and then host to devices. For all of the SpMV operations are using our own code BDIA-GH and also CUSPARSE

### Algorithm 1 BiCGStab algorithm

1:  $\mathbf{x_0}$  is an initial guess 2:  $\mathbf{r_0} \leftarrow \mathbf{b} - \mathbf{A}\mathbf{x_0}$ 3: Choose an arbitrary vector  $\hat{\mathbf{r}_0}$  such that  $(\hat{\mathbf{r}_0}, \mathbf{r_0}) \neq 0$ , e.g.,  $\hat{\mathbf{r}_0} = \mathbf{r_0}$ 4:  $\rho_0 = \alpha_0 = \omega_0 = 1$ 5:  $v_0 = p_0 = 0$ 6: for i = 0 to  $i_{max}$  do 7:  $\boldsymbol{\rho}_i \leftarrow (\hat{\mathbf{r_0}}, \mathbf{r_{i-1}})$  $oldsymbol{eta} \leftarrow (oldsymbol{

ho}_i / oldsymbol{

ho}_{i-1}) (oldsymbol{lpha} / oldsymbol{\omega}_{i-1})$ 8:  $\mathbf{p_i} \leftarrow \mathbf{r_{i-1}} + \boldsymbol{\beta}(\mathbf{p_{i-1}} - \boldsymbol{\omega}_{i-1}\mathbf{v_{i-1}})$ 9:  $\mathbf{v_i} \leftarrow \mathbf{Ap_i}$ 10: $oldsymbol{lpha} \leftarrow oldsymbol{

ho}_i/(\mathbf{r_0},\mathbf{v_i})$ 11:12: $\mathbf{s} \gets \mathbf{r}_{i-1} - \alpha \mathbf{v}_i$  $\mathbf{t} \leftarrow \mathbf{As}$ 13: $\boldsymbol{\omega}_i \leftarrow (\mathbf{t}, \mathbf{s})/(\mathbf{t}, \mathbf{t})$ 14: $\mathbf{x_i} \leftarrow \mathbf{x_{i-1}} + \alpha \mathbf{p_i} + \boldsymbol{\omega_i s}$ 15:16:If  $\mathbf{x}_{\mathbf{i}}$  accurate enough, then quit 17: $\mathbf{r_i} \leftarrow \mathbf{s} - \boldsymbol{\omega_i} \mathbf{t}$ 18: **end for**

library, while other operations like vector dot products (step 7, 11, 14), axpy operation (step 9, 12, 15, 17), and scal (step 9) are using CUBLAS library.

### CHAPTER 3

# SPARSE MATRIX STORAGE FORMATS

# 3.1 General Sparse Storage Format and Its SpMV

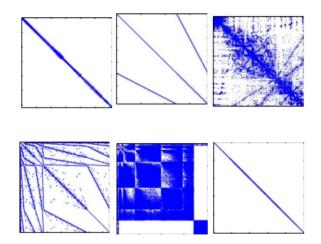

Matrix operation often used in scientific computations are mainly needed for implementing iterative linear algebra solver. From the real applications, it is found that matrix to be used in scientific computing is in form of sparse matrices (figure 3.1) [15]. By definition, sparse matrix defined as "The matrix may be sparse, either with the nonzero elements concentrated on a narrow band centered on the diagonal or alternatively they may be distributed in a less systematic manner. We shall refer to a matrix as dense if the percentage of zero elements or its distribution is such as to make it uneconomic to take advantage of their presence." [16].

Figure 3.1: Examples of Sparse Matrices [2]

The distribution of zeros and non-zeros in matrices my considerably vary for each case. But generally, [15] these matrices can be grouped into two categories. The first category includes the problems which have no 2D/3D geometry. The second category is for the problems with 2D/3D geometry. In each category there are sub-categories that grouped by the type of computation. For example, circuit simulation problem, directed graph, linear programming problem that lies into the problems with no 2D/3D geometry, where materials problem, thermal problems, computational fluid dynamics problem are lies into the problems with 2D/3D geometry.

Because of the variation in the type of sparse matrix, Bell et. al. [17] proposed a general storage format that could help computing and manipulating the sparse matrix to achieve better performance.

$$\mathbf{A} = \begin{bmatrix} 1 & 7 & 0 & 0 \\ 0 & 2 & 8 & 0 \\ 5 & 0 & 3 & 9 \\ 0 & 6 & 0 & 4 \end{bmatrix}$$

$$\mathbf{row} = \begin{bmatrix} 0 & 0 & 1 & 1 & 2 & 2 & 2 & 3 & 3 \\ \mathbf{col} = \begin{bmatrix} 0 & 1 & 1 & 2 & 0 & 2 & 3 & 1 & 3 \\ \mathbf{data} = \begin{bmatrix} 1 & 7 & 2 & 8 & 5 & 3 & 9 & 6 & 4 \end{bmatrix}$$

Figure 3.2: COO representation of A with arrays row, col, and data [17]

### 3.1.1 Coordinate Format (COO)

The simplest storage format is the Coordinate (COO) of the non-zero elements. This storage format basically will have stable performance on every kind of sparse matrices, because the required storage capacity is linear with the number of non-zero in the matrix regardless its structure. This scheme stores row and column indices explicitly. Therefore, this storage formats have three arrays: an array to store the data, an array to store the row indices and an array to store the column indices (figure 3.2). Because the storage format is straight forward, the SpMV application in this format is also straight forward. The parallelization is done by dividing the data among the threads. Because the indices are all stored explicitly, any access to the data requires accessing the row and column indexing. The drawback of this scheme is the access to the memory is not coalesced manner which makes it inefficient in using the parallel memory bandwidth (figure 3.3).

| row                        | [0      | 0              | 1 | 1 | 2 | 2 | 2 | 3 | 3]     |

|----------------------------|---------|----------------|---|---|---|---|---|---|--------|

| col                        | [0      | 1              | 1 | 2 | 0 | 2 | 3 | 1 | 3]     |

| data                       | [1      | $\overline{7}$ | 2 | 8 | 5 | 3 | 9 | 6 | 4      |

|                            | 2       |                |   |   |   |   |   |   | 2      |

|                            |         |                |   |   |   |   |   |   |        |

| Iteration 0                | [0      | 1              | 2 | 3 |   |   |   |   | ]      |

| Iteration 0<br>Iteration 1 | [0<br>[ | 1              | 2 | 3 | 0 | 1 | 2 | 3 | ]<br>] |

Figure 3.3: COO SpMV kernel memory access pattern with the arrays row col, and data [17]

### 3.1.2 Compressed Storage Row Format (CSR)

Basically, Compressed Storage Row format (CSR) is like the extension of COO format. All the values in matrix data are stored in row-major order and the column indices for the corresponding value of data is stored explicitly. But the difference with the COO format is instead of storing all the row numbering explicitly, CSR stores the row implicitly using a pointer ptr to determine the address of the first and last row elements (figure 3.4). The SpMV operation requires loading the values of the data after accessing the row and the column indices on each row (figure 3.5). Therefore, parallelizing the SpMV is based on assigning a separate thread to each row. The problem of this implementation are the data and the column indices which are stored contiguously but their access is not in coalesced manner (figure 3.6). There are some proposed approach to overcome this problem, but not discussed in detail.

$$\mathbf{A} = \begin{bmatrix} 1 & 7 & 0 & 0 \\ 0 & 2 & 8 & 0 \\ 5 & 0 & 3 & 9 \\ 0 & 6 & 0 & 4 \end{bmatrix}$$

$$\mathtt{ptr} = \begin{bmatrix} 0 & 2 & 4 & 7 & 9 \end{bmatrix}$$

$$\mathtt{indices} = \begin{bmatrix} 0 & 1 & 1 & 2 & 0 & 2 & 3 & 1 & 3 \end{bmatrix}$$

$$\mathtt{data} = \begin{bmatrix} 1 & 7 & 2 & 8 & 5 & 3 & 9 & 6 & 4 \end{bmatrix}$$

Figure 3.4: CSR representation of A with arrays ptr, indices, and data [17]

Figure 3.5: CSR sparse matrix format using serial CPU SpMV kernel [17]

| indices<br>data            | -  | 1 7 |   |   |   |   |   |   | -  |

|----------------------------|----|-----|---|---|---|---|---|---|----|

| Iteration 0                | [0 |     | 1 | _ | 2 |   |   | 3 | ]  |

| Iteration 1<br>Iteration 2 | [  | 0   |   | 1 |   | 2 | 2 |   | 3] |

Figure 3.6: CSR SpMV kernel memory access pattern using arrays indices and data [17]

### **3.1.3** Block Compressed Storage Row Format (BSR)

Block Compressed Sparse Row (BSR) is another version of compressed storage row (CSR). This scheme takes advantages of sparse matrices that have non-zeros in a group of neighbours, which can be considered as a data block. In scientific computation, the blocked structure represents interaction between cells that have more than one state variable. The general idea of this storage scheme is the same with CSR but in blocked version. Instead of storing each value of the data in row major order, they combine the row by the size of the block and put the block values into the data array with row major order of the block in block rows and also row major order within the block. Inside the block, there at least one number of non-zero. Therefore, it is not suitable if the non-zero elements in the sparse matrix is highly scattered because the block data will store too many zero elements. Other variations of this scheme stores the column indices of the blocks, pointers to each block in the matrix to determine the first end of the last block in a row of the matrix.

### **3.1.4** ELLPACK Format (ELL)

ELLPACK storage format is more specific compared to previous mentioned storage format because this scheme is suitable when the maximum number of non-zeros in the row of the matrix (K) is close to the average number of non-zero in other rows. Otherwise, like in figure 3.9 the data and indexing arrays will store too many non-zeros. Figure 3.8 shows some suitable matrices for this scheme.

$$A = \begin{bmatrix} 1 & 7 & 0 & 0 \\ 0 & 2 & 8 & 0 \\ 5 & 0 & 3 & 9 \\ 0 & 6 & 0 & 4 \end{bmatrix}$$

$$data = \begin{bmatrix} 1 & 7 & * \\ 2 & 8 & * \\ 5 & 3 & 9 \\ 6 & 4 & * \end{bmatrix} \qquad \qquad indices = \begin{bmatrix} 0 & 1 & * \\ 1 & 2 & * \\ 0 & 2 & 3 \\ 1 & 3 & * \end{bmatrix}$$

Figure 3.7: ELL representation of A with arrays data and indices [17]

Figure 3.8: Example of the matrix that is suitable with ELL format [17]

This format is constructed by grouping the non-zero elements in every row of the matrix (assuming  $M \times N$  matrix) to the left side of the matrix and the zeros will be on the right. The row  $(K^{th})$  that has the maximum number of non-zero will be the limit and the zeros on the right side of  $K^{th}$  row that will be trimmed so the new data matrix will be  $M \times K$ . Besides the data, other array called indices are used in this format for indexing the column. ELL scheme stores the row implicitly and stores the column indices explicitly in an array like COO (figure 3.7).

Figure 3.10 shows how SpMV with this ELL format has been done. Generally, kernel of ELL is similar to DIA format, ELL can be helpful to parallelize the computation by assigning one thread per row. But because the column indices is stored explicitly, while DIA store the column implicitly, generally DIA will

Figure 3.9: Example of the matrix that is not suitable for ELL format [17]

perform better on matrices that have some diagonal trend. Also the memory access of the x vector is not always referring to contiguous addresses (3.11).

### 3.1.5 Hybrid Format (HYB)

Hybrid format is combining the format of ELL and format of COO. As mentioned in section 3.1.4, ELL is not suitable if the maximum number non-zero in a row is very different compared to the average non-zero number in a row. To overcome this problem, hybrid scheme is storing the non-zero to the left and the zeros to the right like ELL storage scheme and then truncating the number of non-zero in the row that has maximum number of non-zero. The new maximum number of non-zero in the row decreases and approaches the average number of non-zero in a row for other rows. This truncated non-zero elements in the matrix will be stored as COO storage format.

```

__global__ void

spmv_ell_kernel(const int num_rows,

const int num_cols,

const int num_cols_per_row,

const int * indices,

const float * data,

const float * x,

float * y)

{

int row = blockDim.x * blockIdx.x + threadIdx.x;

if(row < num_rows){</pre>

float dot = 0;

for(int n = 0; n < num_cols_per_row; n++){</pre>

int col = indices[num_rows * n + row];

float val = data[num_rows * n + row];

if(val != 0)

dot += val * x[col];

}

y[row] += dot;

}

}

```

Figure 3.10: ELL sparse matrix format SpMV kernel [17]

| data        | [1 | 2 | 5 | 6 | 7 | 8 | 3 | 4 | * | * | 9        | *] |

|-------------|----|---|---|---|---|---|---|---|---|---|----------|----|

| indices     | [0 | 1 | 0 | 1 | 1 | 2 | 2 | 3 | * | * | <b>3</b> | *] |

|             | L  |   |   |   |   |   |   |   |   |   |          | 1  |

| Iteration 0 | [0 | 1 | 2 | 3 |   |   |   |   |   |   |          | ]  |

| Iteration 1 | [  |   |   |   | 0 | 1 | 2 | 3 |   |   |          | ]  |

| Iteration 2 | [  |   |   |   |   |   |   |   | 0 | 1 | 2        | 3] |

Figure 3.11: Memory access pattern of ELL SpMV and its data linearization [17]

Figure 3.12: Five diagonals sparse matrix [17]

### 3.1.6 Diagonal Format (DIA)

Diagonal format is not suitable for general sparse matrix type and it is even more specific format than ELL. But when the non-zero elements are highly concentrated and restricted in the diagonal of the sparse matrix, this storage scheme could give the best performance because this format is very efficient in term of data storage and computation.

Figure 3.12 shows a band diagonal sparse matrix that is suitable with this format and figure 3.14 is not suitable. There are two arrays that represents this storage scheme. We need to store the data values of the non-zero elements and the offsets to determine the row and column position of the non-zero element. The main diagonal in the matrix represented by 0 in the offset, where the upper diagonal will be represented by positive value (i > 0) and lower diagonal will be represented with negative value (i < 0) compared to diagonal. The value is determined by how far the distance from the main diagonal. To understand more about the

$$A = \begin{bmatrix} 1 & 7 & 0 & 0 \\ 0 & 2 & 8 & 0 \\ 5 & 0 & 3 & 9 \\ 0 & 6 & 0 & 4 \end{bmatrix}$$

$$data = \begin{bmatrix} * & 1 & 7 \\ * & 2 & 8 \\ 5 & 3 & 9 \\ 6 & 4 & * \end{bmatrix} \qquad \qquad \text{offsets} = \begin{bmatrix} -2 & 0 & 1 \end{bmatrix}$$

Figure 3.13: DIA representation of A in arrays data and offsets [17]

storage scheme of this format, Figure 3.13 illustrate the implementation of this scheme. From the Figure 3.13, we see that the matrix A has non-zeros in three diagonal places. In the main diagonal, upper diagonal with one distance, and lower diagonal with two distances. So the data will have three columns to represent each diagonal, and there will be an offset array that represent the diagonal position of each data column. In term of storage scheme, if the matrix has a diagonal type the storage requirement for this format will be the least compared to other formats.

This storage format has some advantages. This format stores the data, x, and y, in contiguous way so that the memory access will be efficient. Furthermore, unlike the COO formats, the row and the column of this format stored implicitly so that it will reduce the memory occupation and also reduce memory access when SpMV is being computed.

Figure 3.16 shows how SpMV in DIA storage format is being computed. Parallelizing the SpMV in DIA storage format can be done by assigning a thread to every result. The thread will compute the dot product along the non zero on

Figure 3.14: Sparse matrix type that not suited well with DIA format [17]

| data                       | [* | * | 5 | 6 | 1 | 2 | 3 | 4 | 7 | 8 | 9        | *]     |

|----------------------------|----|---|---|---|---|---|---|---|---|---|----------|--------|

| Iteration 0<br>Iteration 1 | [  |   | 2 | 3 | 0 | 1 | 2 | 3 |   |   |          | ]<br>] |

| Iteration 2                | [  |   |   |   |   |   |   |   | 0 | 1 | <b>2</b> | ]      |

Figure 3.15: DIA SpMV memory access pattern and data array linearization [17]

the same row and compute the column index the non-zero value is placed using the offset. The result y of each row is the accumulation of the value of non-zero in the data times the value of x vector in the certain column. The best practice on storing the data is by using column major so the access of thread to the data will be coalesced. And also, each thread access to every diagonal will leads to the contiguous access to the vector x because in the same diagonal the column is contiguous (figure 3.15).

### 3.2 Previous Work Studies

Bell and Garland paper [18] first presented a comprehensive analysis of performance for the SpMV on General Purpose GPUs (GPGPUs) using different

```

__global__ void

spmv_dia_kernel(const int num_rows,

const int num_cols,

const int num_diags,

* offsets,

const int

const float * data,

const float * x.

float * y)

ł

int row = blockDim.x * blockIdx.x + threadIdx.x;

if(row < num_rows){</pre>

float dot = 0;

for(int n = 0; n < num_diags; n++){</pre>

int

col = row + offsets[n];

float val = data[num_rows * n + row];

if(col >= 0 && col < num_cols)</pre>

dot += val * x[col];

}

y[row] += dot;

}

}

```

Figure 3.16: DIA sparse matrix format SpMV kernel [17]

storage formats. It has been shown that the main bottleneck of the COO and CSR is memory bandwidth due to the explicit storage of the row and column indices. So the computation to communication ratio is low due to frequent access to the GPU global memory. Unlike COO and CSR, DIA and ELL formats store both row and columns indices implicitly. This paper also concluded that DIA is most appropriate for the structured matrices especially when non-zero values are located into a small number of matrix diagonals. They have showed that for unstructured matrices, the CSR or HYB schemes produce the best performance. However, the DIA storage format produces the best performance for the structured matrices.

Using the libraries or basic routines is an excellent approach to support programming on the GPU to compute many scientific simulation operations and practical applications accelerated via GPU. In this direction, a large number of routines related to matrix computation are provided by NVIDIA such as CUSPARSE [19] and Cusp [20]. CUSPARSE firstly introduced in 2010 [21] by NVIDIA. This library supports Level-1, Level-2, Level-3 operations and also Sparse Matrix Format conversion. Sparse matrix storage format that supported by this library is COO, CSR, CSC, ELL, HYB, BSR, and BSRX. In CUSPARSE, level-1 operation means vector-vector operation, level-2 is sparse matrix-vector operation, and level-3 is sparse matrix-matrix operation.

Paper [22] proposed a static method to predict the optimal storage format depending on the input matrix and time needed to communicate and transfer data between CPU and GPU. They claim that the overhead time needed for the prediction is very small compared to overall time of SpMV execution time. All analyzed matrices are square for simplicity. The capability of bus between CPU and GPU and data size of an input matrix are used to measure the communication cost. The communication time is defined as the ratio of total data size for the chosen format to the effective bandwidth of bus used between CPU and GPU. In that paper, the proposed algorithm tested on number of matrices presented in Sparse Matrix Collection of Florida University.

In addition to communication time used as a factor in a prediction model, pre-processing associated with the format conversion is also used to choose the optimal sparse format and this factor is used when the format is not decided based on the previous factor. Pre-processing overhead comes from three parameters which are number of used data Structures, number of iterations, and the non-zero elements or number of rows in the representation. This paper concluded that, CSR format is recommended for non-square matrices and dense matrices. If the number of columns is more than number of rows, then it is better to use CSR, otherwise ELL is recommended. The matrix is categorized into highly sparse or densely sparse types for square sparse matrices, based on number of the rows and the average number of non-zero elements in a row. In each category, the matrix is further analyzed with respect to the non-zero element distribution based on maximum number non-zero elements per row and average number of non-zero elements in the rows.

Further, paper [22] proposed a Bit Level Single Index (BLSI) representation to reduce the memory foot print and pre-processing overhead. This procedure is used if the prediction model mentioned above selects the HYB or ELL as an optimal storage format and that because these two formats have high pre-processing overhead. In this case the input matrix is converted into BLSI representation. A BLSI format is not used to represent the matrix but used for indices to reduce the pre-processing overhead. As a summery, this paper don't consider the structure of non-zero elements in the matrix. It carry out a test on a set of specific matrices and suggest the optimal storage format to be used.

The Authors in paper [23] proposed a method to increase the SpMV kernel performance by studying some quantities values of the input matrix such as number of non-zero elements deviation in each row, number of non-zero elements average in each row, etc. They improve the performance by balancing the load for every thread, reducing irregular memory access of the vector, coalescing memory access, reducing the overhead of loading matrix element, and concerning about the data structure. From the observation, they conclude that CSR and ELL format have low computational load. The memory access of both formats is also coalesced. From that observation, they decided to combine both CSR and ELL formats and proposed some changes in HYB by storing some rows in CSR and the remaining rows in ELL.

To address the issue of load balancing when using this combination, multiple warps are assigned to a row that depends on the number of non-zero in that row. In their proposed method, the threshold value is found empirically because the CSR format is used for rows that have more nonzero elements than the threshold and for the remaining rows the ELL format is used. Also, the thresholds on the minimum and maximum number of nonzero elements are evaluated for warps assigned to the CSR and ELL formats, respectively. Multiple warps are assigned to a row stored in both formats. Their storage format improves the performance by a factor of 25% on average compared with the best results of HYB that was previously proposed by Bell and Garland.

The experiments performed on a set of highly unstructured sparse matrices and also on standard dataset contains 14 sparse matrices from the work of Williams et. al. [24] and these matrices have varying degree of sparsity. Some matrices have a structure of a dense matrix, some highly unstructured sub-matrices, and others with few non-zero elements per row. They compared their results with the best performance of CSR and HYP formats presented in the work of [25].