## **DESIGN OF A PROGRAMMABLE WIDEBAND MICROWAVE FEED NETWORK**

BY

Sameir Elsayed Elsayed Deif

A Thesis Presented to the DEANSHIP OF GRADUATE STUDIES

KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

# **ASTER OF SCIENCE**

In

**Electrical Engineering**

May 2013

## KING FAHD UNIVERSITY OF PETROLEUM & MINERALS DHAHRAN 31261, SAUDI ARABIA

#### DEANSHIP OF GRADUATE STUDIES

This thesis, written by **SAMEIR ELSAYED DEIF** under the direction of his thesis adviser and approved by his thesis committee, has been presented to and accepted by the Dean of Graduate Studies, in partial fulfillment of the requirements for the degree of **MASTER OF SCIENCE IN ELECTRICAL ENGINEERING DEPARTMENT**.

Thesis Committee Dr. M. S. Sharawi (Adviser) Dr. S. S. Igbal (Member) Dr. O. Hammi (Member) Dr. Ali Ahmad Al-Shaikhi Department Chairman Dr. Salam A. Zummo Dean of Graduate Studies 17 09] 5 Date

© Sameir Deif 2013 To my parents, Dawlat and Sameir, To my beloved wife, Nesma, To my beautiful daughter, Renad.

# ACKNOWLEDGMENTS

In the name of God and prayer and peace be upon the Messenger of Allah -Muhammad, peace be upon him - and his family and companions and blessings.

First of all, I would like to thank my parents, especially my mother, for their support and prayers. Without their prayers, I would not have been able to be successful in my life. Special thanks to my beloved wife, without her patience and support, this work can not be done.

I would also like to thank Dr. Mohammad S. Sharawi for everything. He allowed me to improve my all skills, reading, writing, presentation, and even for dealing with others. It was a great chance to work under his supervision because he was completely involved in my work and we never lost track throughout my thesis work. In addition to his technical support, I would like to specifically thank him for his financial support to be comfort in my social life.

In addition to my supervisor, I would also like to thank my thesis committee members, Dr. Oualid Hammi and Dr. Sheikh Sharif Iqbal to rigorously review and improve my thesis work.

I want to thanks my colleagues in KFUPM specially Dr. M. Ali, M. Adel, Abdullah Ibrahim for their support and advices.

# TABLE OF CONTENTS

| LIS  | T OF   | TABLES                           | vii  |

|------|--------|----------------------------------|------|

| LIS  | T OF I | FIGURES                          | viii |

| AB   | STRA   | CT (ENGLISH)                     | xii  |

| ABS  | TRAC   | T (ARABIC)                       | xiv  |

| CHAP | TER 1  | INTRODUCTION                     | 1    |

| 1.1  | Thesis | Objectives                       | 2    |

| 1.2  | Thesis | Organization                     | 3    |

| CHAP | TER 2  | 2 BACKGROUND                     | 4    |

| 2.1  | RF Ci  | rcuits: Design and Parameters    | 4    |

|      | 2.1.1  | Microstrip Transmission Lines    | 4    |

|      | 2.1.2  | Layout Design Fundamentals       | 8    |

|      | 2.1.3  | S-Parameters                     | 11   |

|      | 2.1.4  | Noise                            | 12   |

|      | 2.1.5  | Linearity Metrics of RF Circuits | 16   |

|      | 2.1.6  | Stability of Active Circuits     | 20   |

| 2.2  | Beamf  | formers                          | 21   |

|      | 2.2.1  | Power Divider BFN                | 22   |

|      |        | 2.2.1.1 T-junction Power Divider | 23   |

|      |        | 2.2.1.2 Wilkinson Power Divider  | 25   |

|                                                              |                                                                                                      | 2.2.1.3                                                                                                                                            | Switched-Line Phase Shifters                                | 27                                                                                                                     |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

|                                                              |                                                                                                      | 2.2.1.4                                                                                                                                            | The 90° Hyprid Coupler $\ldots \ldots \ldots \ldots \ldots$ | 28                                                                                                                     |

|                                                              | 2.2.2                                                                                                | Power D                                                                                                                                            | Dividers BFN examples                                       | 29                                                                                                                     |

|                                                              | 2.2.3                                                                                                | Network                                                                                                                                            | BFN                                                         | 33                                                                                                                     |

|                                                              |                                                                                                      | 2.2.3.1                                                                                                                                            | Maxon-Blass matrix                                          | 33                                                                                                                     |

|                                                              |                                                                                                      | 2.2.3.2                                                                                                                                            | Butler matrix                                               | 35                                                                                                                     |

|                                                              |                                                                                                      | 2.2.3.3                                                                                                                                            | Nolen Matrix                                                | 36                                                                                                                     |

|                                                              | 2.2.4                                                                                                | Lens BF                                                                                                                                            | N                                                           | 37                                                                                                                     |

|                                                              |                                                                                                      | 2.2.4.1                                                                                                                                            | Rotman Lens                                                 | 37                                                                                                                     |

| CHAP                                                         | TER                                                                                                  | 3 LIT                                                                                                                                              | ERATURE REVIEW AND RESEARCH                                 |                                                                                                                        |

| ME                                                           | THOE                                                                                                 | OLOGY                                                                                                                                              | <i>C</i>                                                    | 40                                                                                                                     |

| 3.1                                                          | Litera                                                                                               | ture Revi                                                                                                                                          | ew                                                          | 40                                                                                                                     |

| 3.2                                                          | Resear                                                                                               | ch Metho                                                                                                                                           | odology                                                     | 47                                                                                                                     |

|                                                              |                                                                                                      | 4                                                                                                                                                  |                                                             |                                                                                                                        |

|                                                              |                                                                                                      |                                                                                                                                                    | GRAMMABLE FEED NETWORK ARCHI-                               |                                                                                                                        |

| TE                                                           | CTUR                                                                                                 | E AND                                                                                                                                              | DESIGN                                                      | 50                                                                                                                     |

| 4.1                                                          | D:                                                                                                   | Architor                                                                                                                                           | eture                                                       | 50                                                                                                                     |

|                                                              | Design                                                                                               | ATCHILE                                                                                                                                            |                                                             | 00                                                                                                                     |

| 4.2                                                          | 0                                                                                                    |                                                                                                                                                    | pecifications                                               | 50<br>52                                                                                                               |

| 4.2<br>4.3                                                   | Comp                                                                                                 | onents' S                                                                                                                                          |                                                             |                                                                                                                        |

|                                                              | Compo<br>Schem                                                                                       | onents' Sj<br>atic Desi                                                                                                                            | pecifications                                               | 52                                                                                                                     |

| 4.3                                                          | Compo<br>Schem<br>PCB I                                                                              | onents' Sj<br>atic Desi<br>Board De                                                                                                                | pecifications                                               | 52<br>56                                                                                                               |

| 4.3<br>4.4                                                   | Composition<br>Schem<br>PCB I<br>Microo                                                              | onents' S<br>atic Desig<br>Board Des<br>controller                                                                                                 | pecifications                                               | 52<br>56<br>59                                                                                                         |

| <ul><li>4.3</li><li>4.4</li><li>4.5</li></ul>                | Composition<br>Schem<br>PCB I<br>Microo<br>Conclu                                                    | onents' Sj<br>atic Desig<br>Board Des<br>controller<br>1sion                                                                                       | pecifications                                               | 52<br>56<br>59<br>62                                                                                                   |

| <ul><li>4.3</li><li>4.4</li><li>4.5</li><li>4.6</li></ul>    | Compo<br>Schem<br>PCB I<br>Microo<br>Conclu                                                          | onents' Sj<br>atic Desi<br>Board Des<br>controller<br>usion<br><b>6 RESU</b>                                                                       | pecifications                                               | 52<br>56<br>59<br>62<br>66                                                                                             |

| 4.3<br>4.4<br>4.5<br>4.6<br>CHAP                             | Compo<br>Schem<br>PCB I<br>Microo<br>Conclu<br><b>TER 5</b><br>Simula                                | onents' S<br>atic Desi<br>Board Des<br>controller<br>usion<br><b>5 RESU</b><br>ation Mod                                                           | pecifications                                               | <ul> <li>52</li> <li>56</li> <li>59</li> <li>62</li> <li>66</li> <li>68</li> </ul>                                     |

| 4.3<br>4.4<br>4.5<br>4.6<br><b>CHAP</b><br>5.1               | Compo<br>Schem<br>PCB I<br>Microo<br>Conclu<br><b>TER 5</b><br>Simula<br>Plottin                     | onents' S<br>atic Desi<br>Board Des<br>controller<br>usion<br><b>5 RESU</b><br>ation Mod                                                           | pecifications                                               | <ul> <li>52</li> <li>56</li> <li>59</li> <li>62</li> <li>66</li> <li>68</li> <li>68</li> </ul>                         |

| 4.3<br>4.4<br>4.5<br>4.6<br><b>CHAP</b><br>5.1<br>5.2        | Compo<br>Schem<br>PCB I<br>Microo<br>Conclu<br><b>TER 5</b><br>Simula<br>Plottin<br>Simula           | onents' S<br>atic Desi<br>Board Des<br>controller<br>usion<br><b>5 RESU</b><br>ation Moo<br>ng Script<br>ation Res                                 | pecifications                                               | <ul> <li>52</li> <li>56</li> <li>59</li> <li>62</li> <li>66</li> <li>68</li> <li>68</li> <li>71</li> </ul>             |

| 4.3<br>4.4<br>4.5<br>4.6<br><b>CHAP</b><br>5.1<br>5.2<br>5.3 | Compo<br>Schem<br>PCB I<br>Microo<br>Conclu<br><b>TER 5</b><br>Simula<br>Plottin<br>Simula<br>4-path | onents' Sy<br>atic Designon<br>Board Designon<br>controller<br>usion<br><b>5 RESU</b><br>ation Moore<br>ing Script<br>ation Result<br>ation Result | pecifications                                               | <ul> <li>52</li> <li>56</li> <li>59</li> <li>62</li> <li>66</li> <li>68</li> <li>68</li> <li>71</li> <li>73</li> </ul> |

| 5.7  | Conclusion                       | 85  |

|------|----------------------------------|-----|

| CHAP | TER 6 A COMPACT SIZE 12-PORT COM | 1-  |

| BIN  | NER/SPLITTER (C/S)               | 86  |

| 6.1  | Introduction                     | 86  |

| 6.2  | Wilkinson C/S                    | 88  |

| 6.3  | Proposed 12-port C/S             | 89  |

|      | 6.3.1 Schematic and Board Design | 89  |

|      | 6.3.2 V1 Model Results           | 93  |

|      | 6.3.3 V2 Model Results           | 101 |

| 6.4  | Conclusion                       | 106 |

| CHAP | TER 7 CONCLUSION AND FUTURE WORK | 107 |

| 7.1  | Future Work                      | 108 |

| RE   | FERENCES                         | 109 |

| VIT  | <b>TAE</b>                       | 117 |

# LIST OF TABLES

| 3.1 | Comparison of proposed RF feed network                               | 46 |

|-----|----------------------------------------------------------------------|----|

| 4.1 | Truth table for switch HMC336                                        | 53 |

| 4.2 | Truth table for phase shifters HMC647 and HMC649                     | 54 |

| 4.3 | Truth table for amplifier HMC625.                                    | 55 |

| 4.4 | Dip switch 1 (and dip switch 1') control the phase of HMC647 (2.5 $$ |    |

|     | to 3.1 GHz) and the first switch HMC336. $\ldots$                    | 61 |

| 4.5 | Dip Switch 2 (and Dip Switch 2'): The gain of HMC625 (DC to          |    |

|     | GHz)                                                                 | 62 |

| 4.6 | Dip switch 3 (and dip switch $3'$ ) control the phase of HMC649 (3   |    |

|     | to 6 GHz) and the second switch HMC336                               | 62 |

| 6.1 | Typical performance data of C/S components                           | 96 |

# LIST OF FIGURES

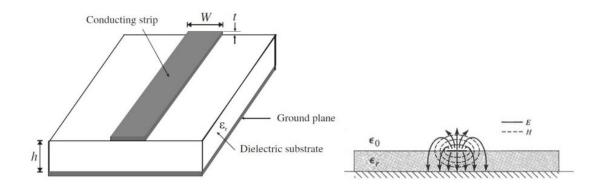

| 2.1  | Structure and dimension of microstrip transmission line                  | 5  |

|------|--------------------------------------------------------------------------|----|

| 2.2  | Microstrip design example by TXLINE software                             | 7  |

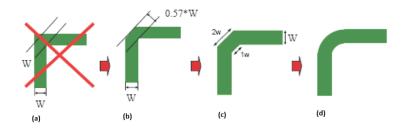

| 2.3  | Different design of right angle bends, worst to best from left to right. | 9  |

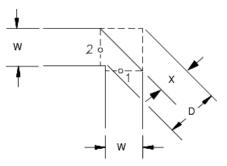

| 2.4  | The structures and the design parameters of the mitered BEND             | 10 |

| 2.5  | Printed mitered bend.                                                    | 10 |

| 2.6  | S-parameters for two-port network.                                       | 12 |

| 2.7  | Noise figure for a cascaded system                                       | 15 |

| 2.8  | Third-order intercept point.                                             | 17 |

| 2.9  | 1 dB Compression Point                                                   | 18 |

| 2.10 | Error vector magnitude.                                                  | 19 |

| 2.11 | Power splitting/combining in dividers/splitters                          | 23 |

| 2.12 | T-junction power divider.                                                | 24 |

| 2.13 | An equal-split three-port resistive power divider                        | 25 |

| 2.14 | The Wilkinson power divider.                                             | 26 |

| 2.15 | Switched-line phase shifter                                              | 27 |

| 2.16 | 90° Hybrid Coupler                                                       | 28 |

| 2.17 | Simple beamformer using quadrature coupler                               | 30 |

| 2.18 | Wilkinson-type in-phase power divider                                    | 31 |

| 2.19 | Seven-way divider/combiner                                               | 32 |

| 2.20 | Electrical configuration of the second seven-way divider/combiner.       | 32 |

| 2.21 | The structure of the corporate fed reconfigurable antenna array          | 33 |

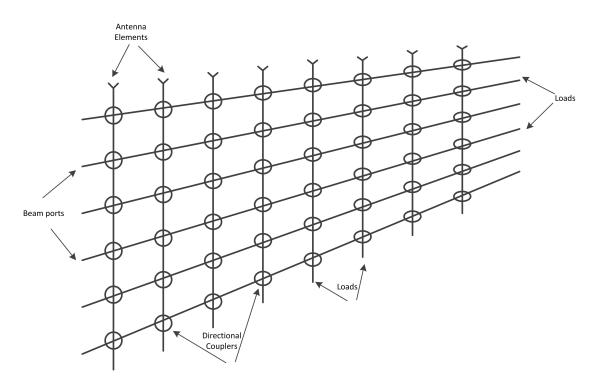

| 2.22 | Schematic of a Blass matrix BFN for 6 beams with eight antenna           |    |

|      | ports.                                                                   | 34 |

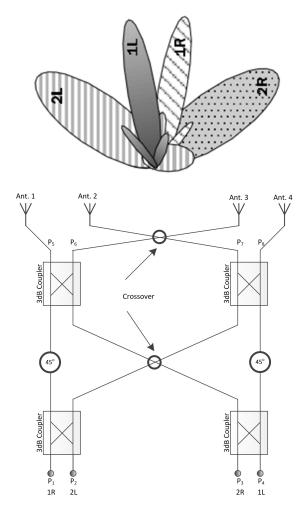

| 2.23 | Schematic for four-port Butler matrix.                             | 36 |

|------|--------------------------------------------------------------------|----|

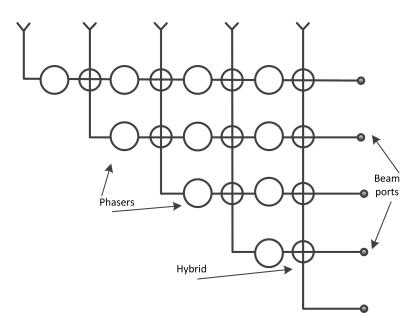

| 2.24 | Schematic for Nolen matrix BFN                                     | 37 |

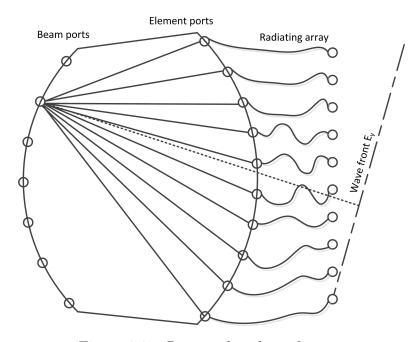

| 2.25 | Rotman lens beamformer.                                            | 38 |

| 3.1  | Block diagram of the interaction between the various phases of the |    |

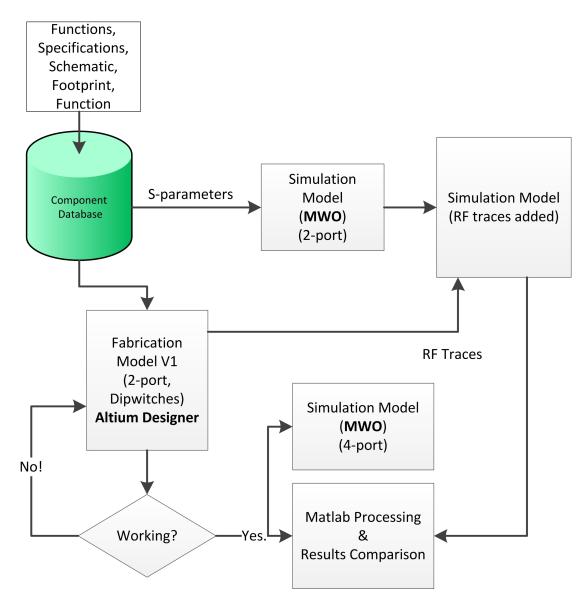

|      | project. Shaded blocks are the contributions of this work          | 48 |

| 3.2  | Block diagram of the interaction between the various phases of the |    |

|      | project                                                            | 49 |

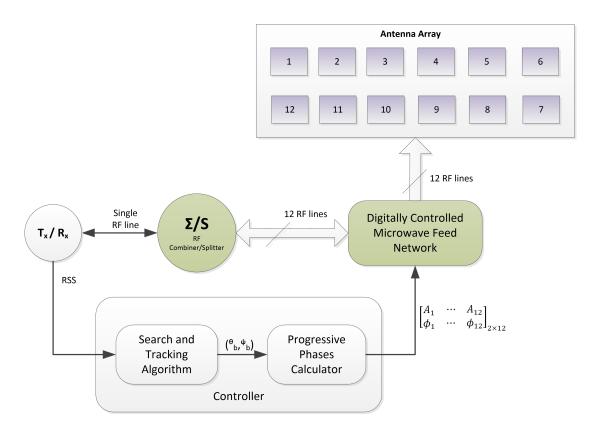

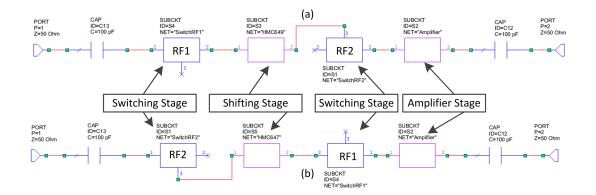

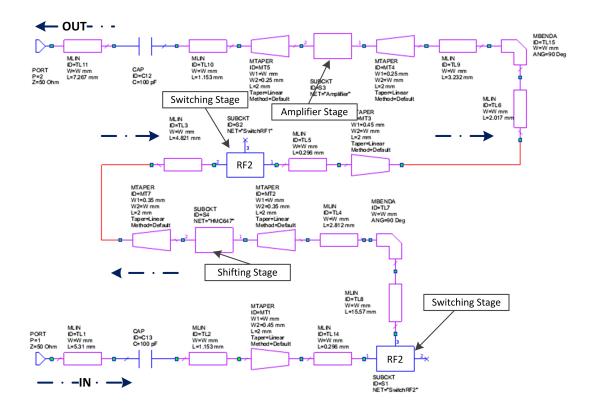

| 4.1  | Proposed architecture of the wideband programmable Feed network.   | 52 |

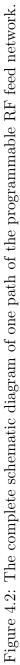

| 4.2  | The complete schematic diagram of one path of the programmable     |    |

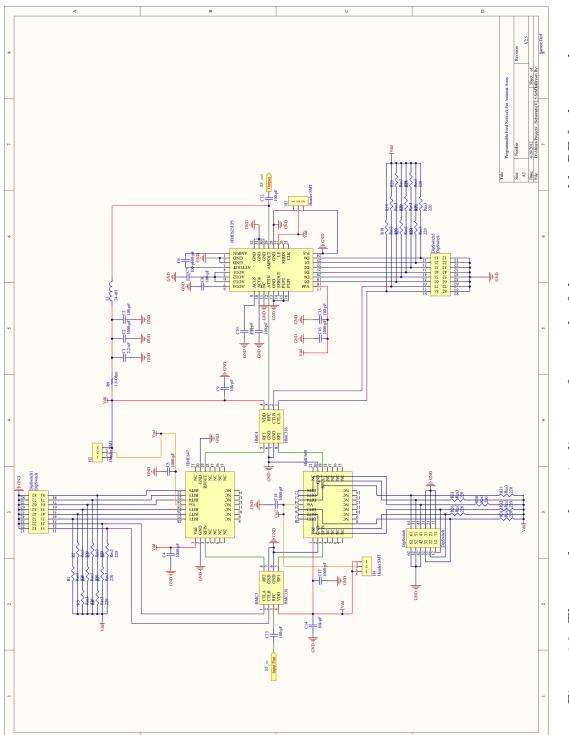

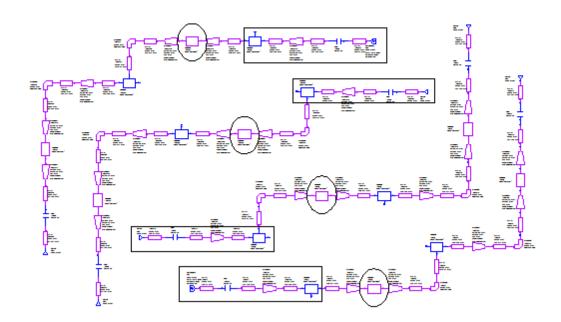

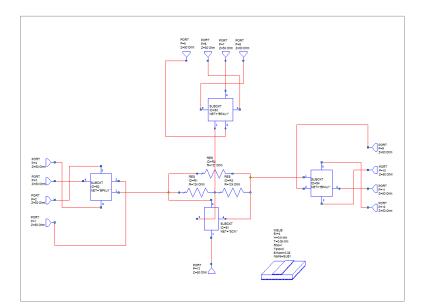

|      | RF feed network                                                    | 58 |

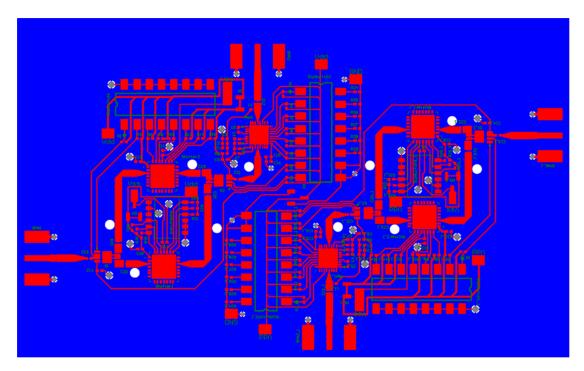

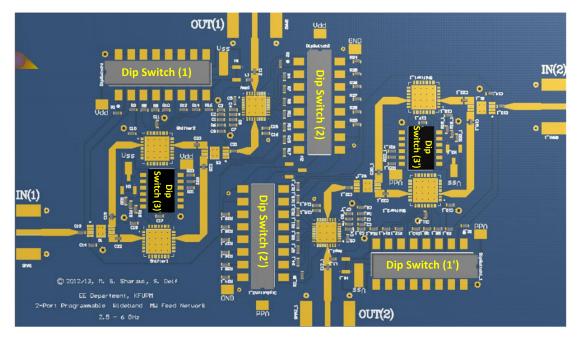

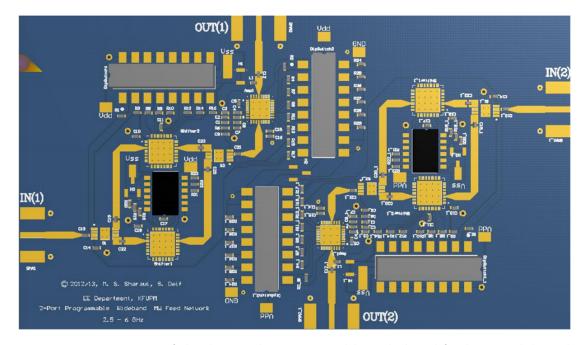

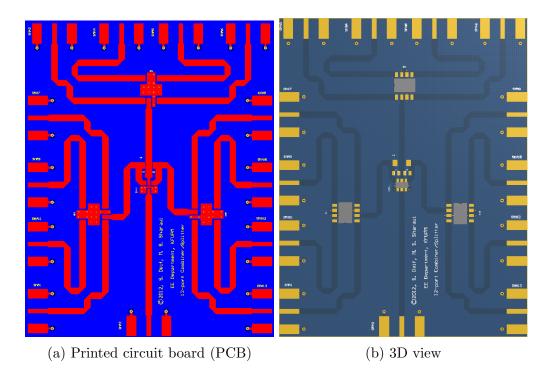

| 4.3  | The PCB board for 2-port model network                             | 60 |

| 4.4  | The numbering of the dip switches on the board                     | 61 |

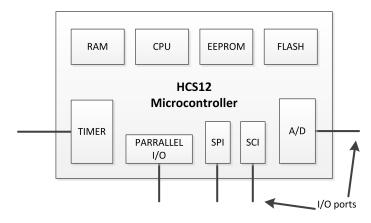

| 4.5  | The block diagram of a typical HC12 microcontroller                | 63 |

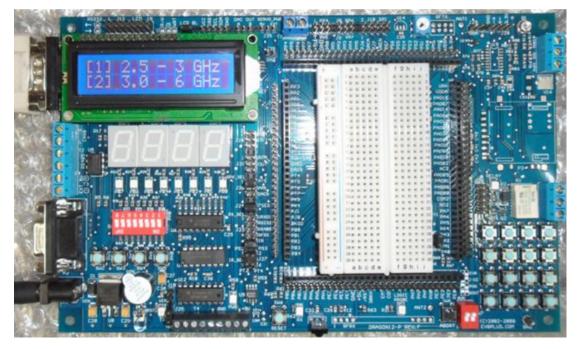

| 4.6  | Drgon-12 Board that carry the Microcontroller Unit                 | 64 |

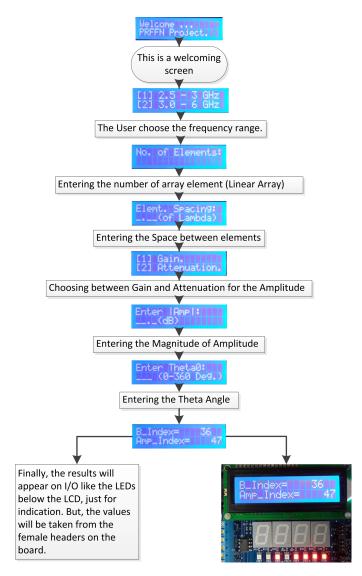

| 4.7  | Flow chart of the Microcontroller program                          | 66 |

| 5.1  | Two circuit schematics of the network without RF lines (a) branch  |    |

|      | one (b) branch two                                                 | 69 |

| 5.2  | The circuit schematic included RF traces for one branch            | 70 |

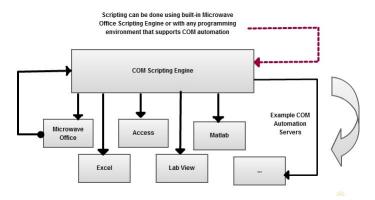

| 5.3  | COM Automation client used to connect to other COM servers         | 71 |

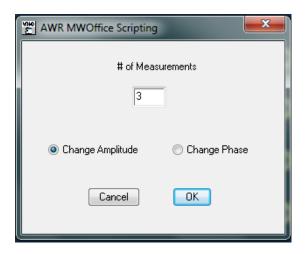

| 5.4  | The proposed scripting for the AWR environment                     | 72 |

| 5.5  | Change Amplitude Screen.                                           | 73 |

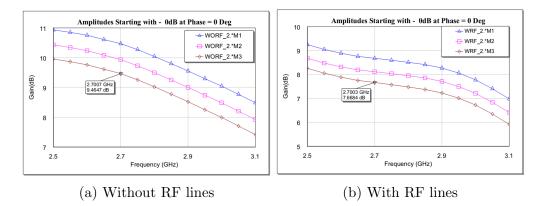

| 5.6  | Simulated insertion loss of the first path                         | 74 |

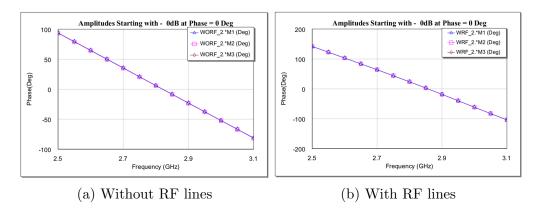

| 5.7  | Simulated phase response of first path (2.5-3 GHz). $\ldots$ .     | 74 |

| 5.8  | Simulated insertion loss of second path (3-6 GHz)                  | 75 |

| 5.9  | Simulated phase response of second path                            | 75 |

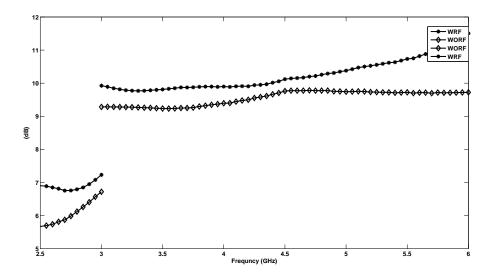

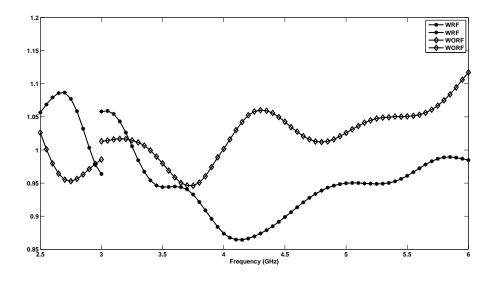

| 5.10 | Noise figure of the feed network WRF and WORF. $\ldots$            | 76 |

| 5.11 | Stability factor.                                                  | 77 |

| 5.12 | Stability Measure (B)                                              | 77 |

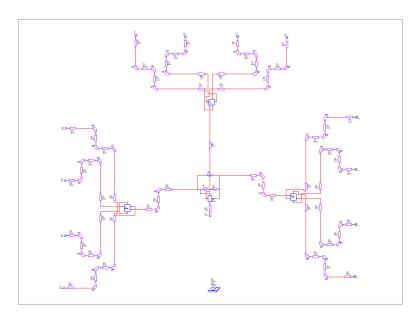

| 5.13 | Circuit schematic for the 4-path model                                 | 78 |

|------|------------------------------------------------------------------------|----|

| 5.14 | 3D view of the designed programmable wide-band feed network            |    |

|      | board in Altium.                                                       | 79 |

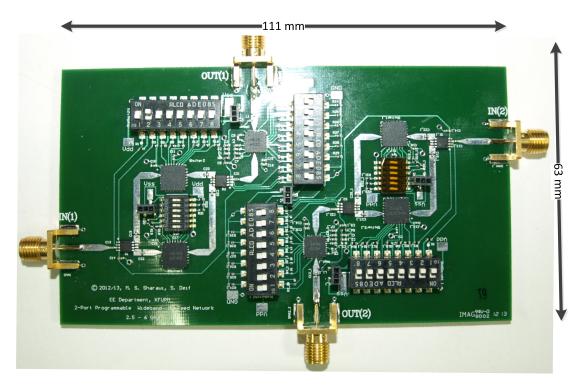

| 5.15 | Fabricated (in USA) board of the proposed 2-port network               | 80 |

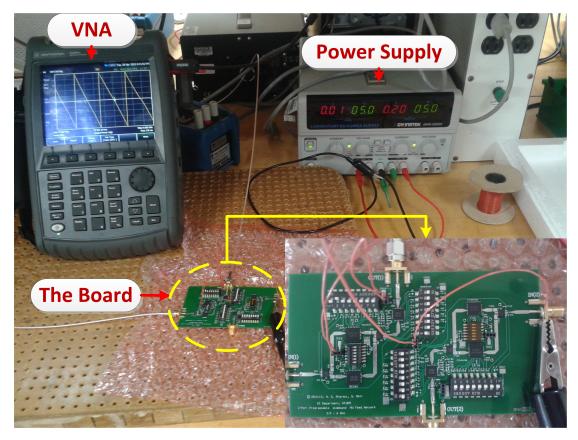

| 5.16 | The measurement setup                                                  | 81 |

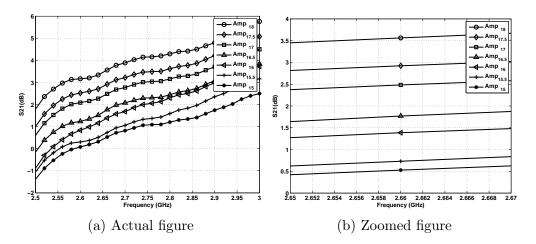

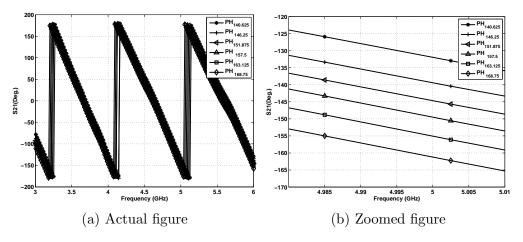

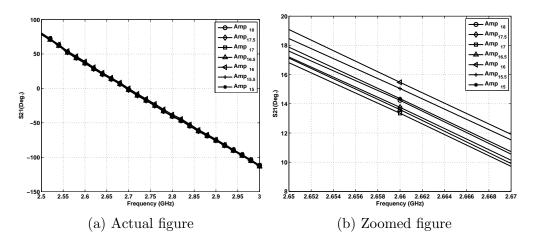

| 5.17 | Measured results for amplitude change (2.5-3 GHz.)                     | 82 |

| 5.18 | Measured results for amplitude steps (3-6 GHz.)                        | 82 |

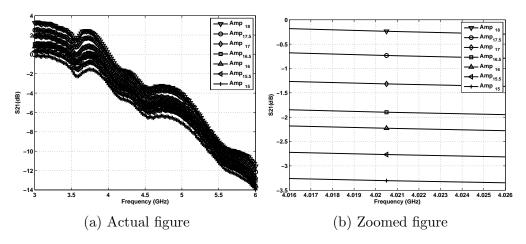

| 5.19 | Measured results for phase steps (2.5-3 GHz.) $\ldots$                 | 83 |

| 5.20 | Measured results for phase steps (3-6 GHz.) $\ldots$                   | 83 |

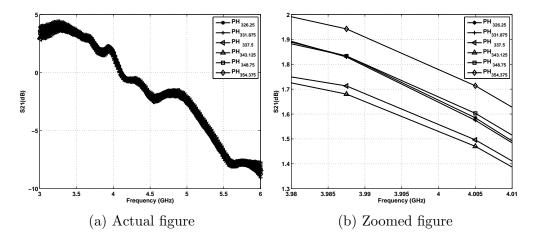

| 5.21 | Measured results for phase at amplitude change (2.5-3 GHz) . $\ .$ .   | 84 |

| 5.22 | Measured results for amplitude variations due to phase changes $(3-6)$ |    |

|      | GHz)                                                                   | 84 |

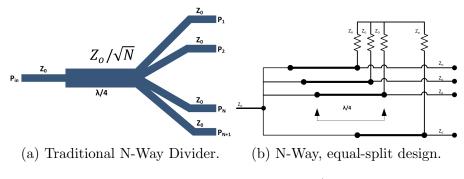

| 6.1  | N-way power C/S.                                                       | 88 |

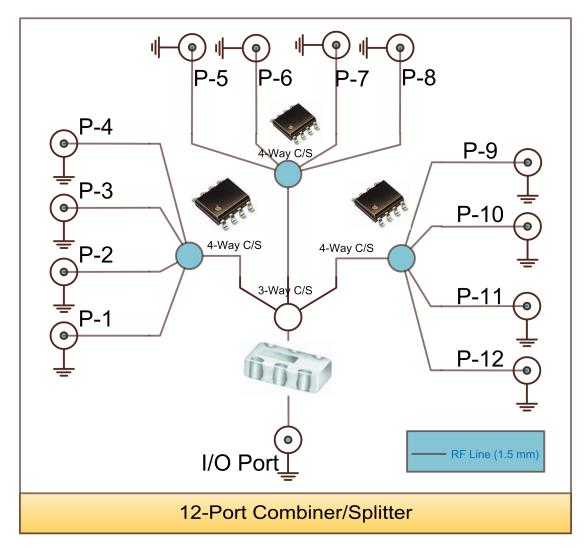

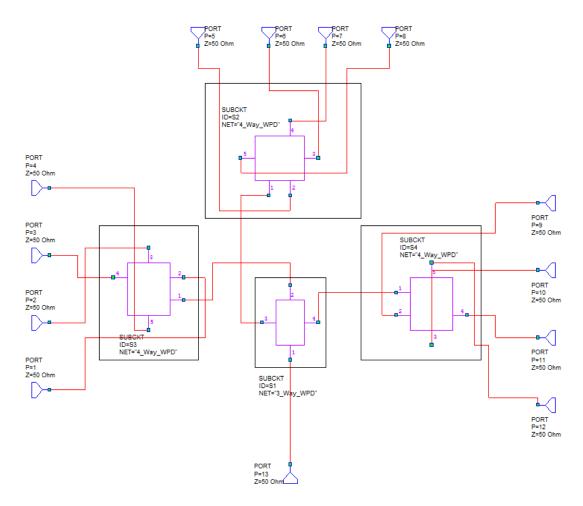

| 6.2  | Design architecture for the proposed 12-port C/S                       | 90 |

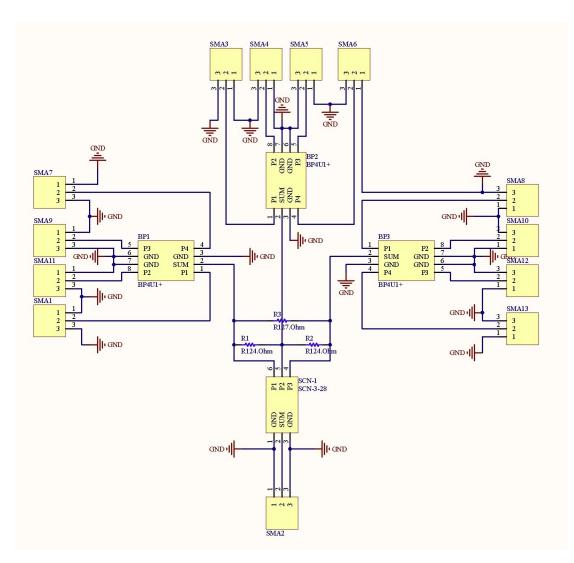

| 6.3  | Circuit schematic for the proposed 12-port C/S                         | 91 |

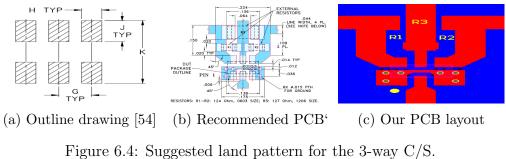

| 6.4  | Suggested land pattern for the 3-way C/S                               | 91 |

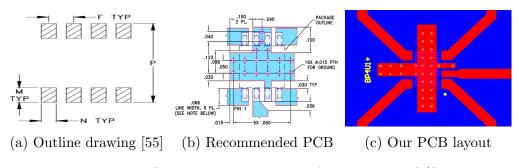

| 6.5  | Suggested land pattern for the 4-way C/S                               | 92 |

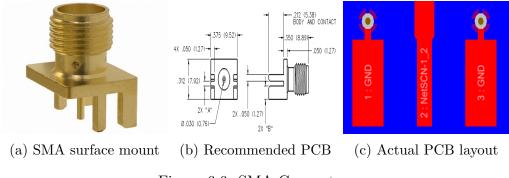

| 6.6  | SMA Connector.                                                         | 92 |

| 6.7  | The PCB board of the proposed circuit and the 3D view                  | 93 |

| 6.8  | Simulation model of the 12-port C/S without RF lines for V1. $$ .      | 94 |

| 6.9  | Simulation model of the 12-port C/S included RF lines for V1           | 94 |

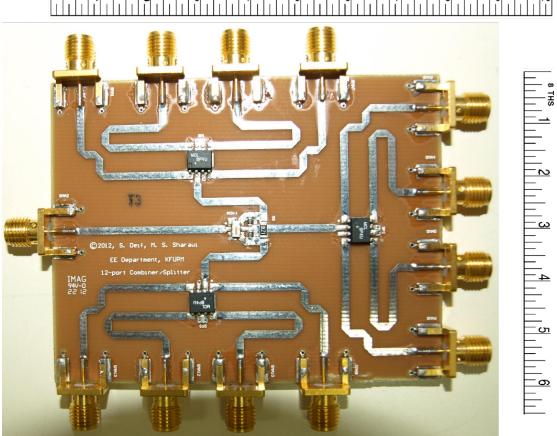

| 6.10 | Fabricated board for the first version V1                              | 95 |

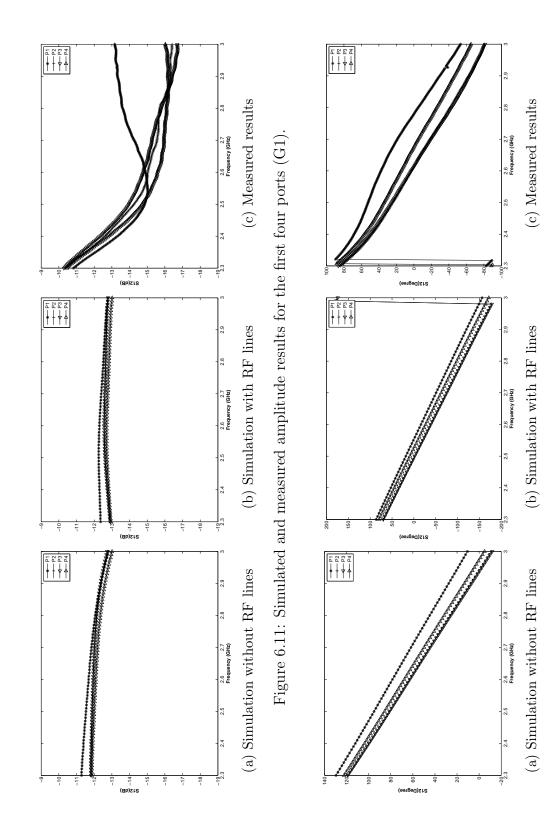

| 6.11 | Simulated and measured amplitude results for the first four ports      |    |

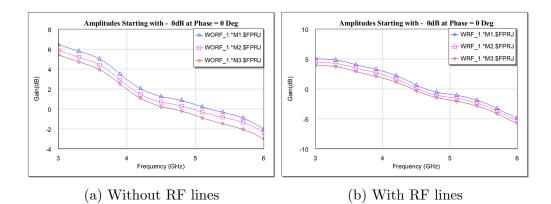

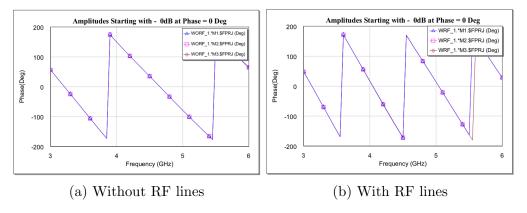

|      | (G1)                                                                   | 98 |

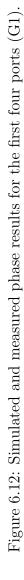

| 6.12 | Simulated and measured phase results for the first four ports (G1).    | 98 |

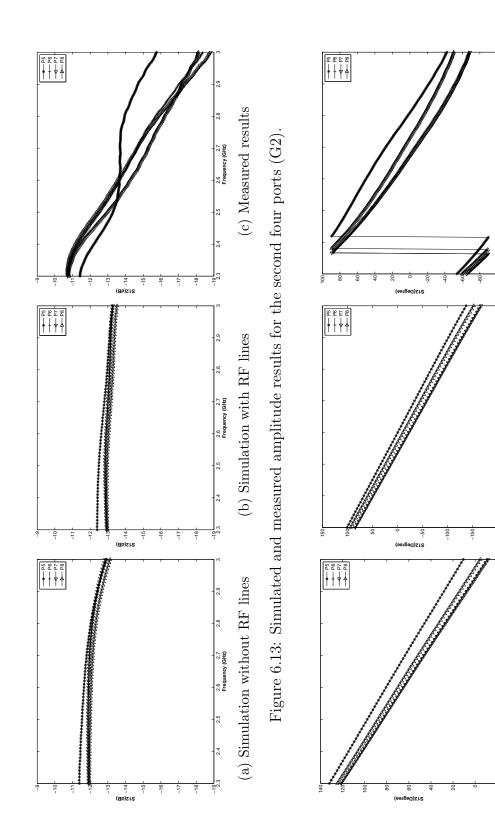

| 6.13 | Simulated and measured amplitude results for the second four ports     |    |

|      | (G2)                                                                   | 99 |

| 6.14 | Simulated and measured phase results for the second four ports (G2).   | 99 |

|      |                                                                        |    |

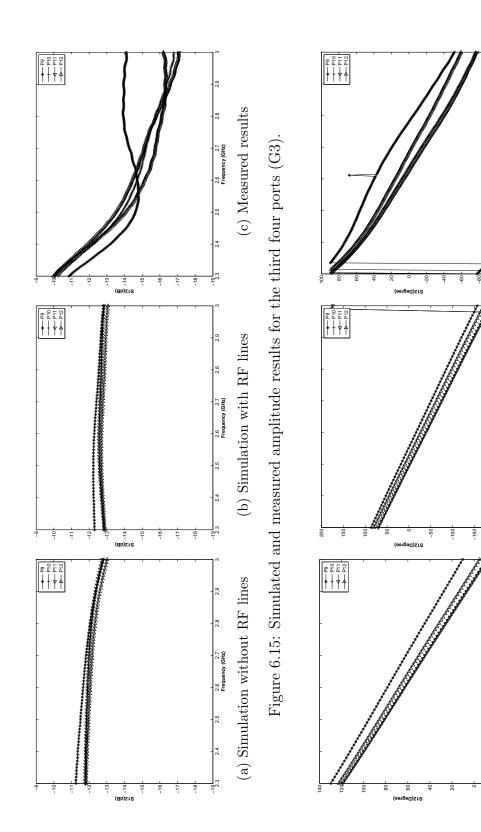

| 0.15 | Simulated and measured amplitude results for the third four ports   |     |

|------|---------------------------------------------------------------------|-----|

|      | (G3)                                                                | 100 |

| 6.16 | Simulated and measured phase results for the third four ports (G3). | 100 |

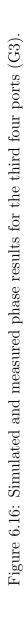

| 6.17 | Compensated model of the 12-port C/S, V2                            | 102 |

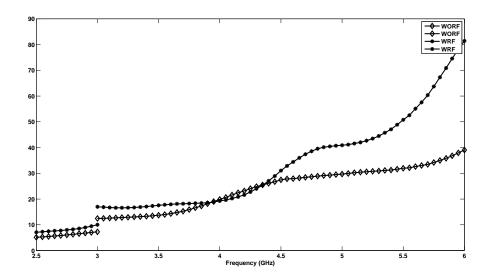

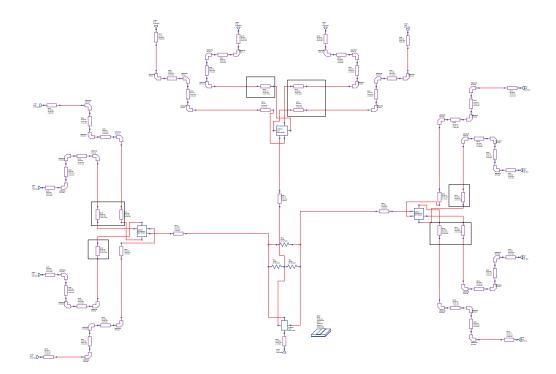

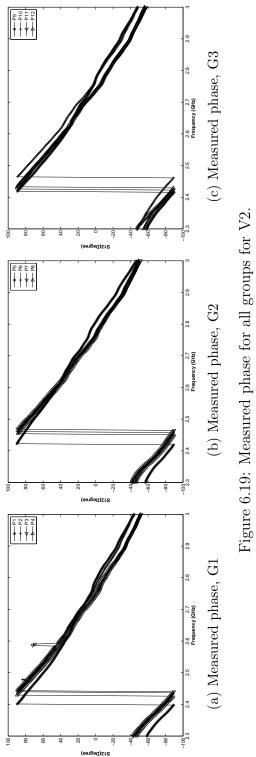

| 6.18 | Measured phase for all groups for V1                                | 103 |

| 6.19 | Measured phase for all groups for V2                                | 103 |

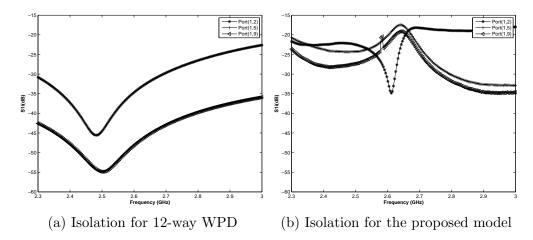

| 6.20 | Measured results for V1 and V2                                      | 104 |

| 6.21 | Circuit schematic of the 12-way WPD                                 | 105 |

| 6.22 | Isolation comparison for the WPD vs the proposed model              | 106 |

#### C 15 C: 1. nod ( aplitude regulta fo . **∠**1. third fo ir porte 1. 1

# THESIS ABSTRACT

| NAME:           | Sameir Elsayed Deif                              |

|-----------------|--------------------------------------------------|

| TITLE OF STUDY: | Design of A Programmable Wideband Microwave Feed |

|                 | Network                                          |

| MAJOR FIELD:    | Electrical Engineering Department                |

| DATE OF DEGREE: | May 2013                                         |

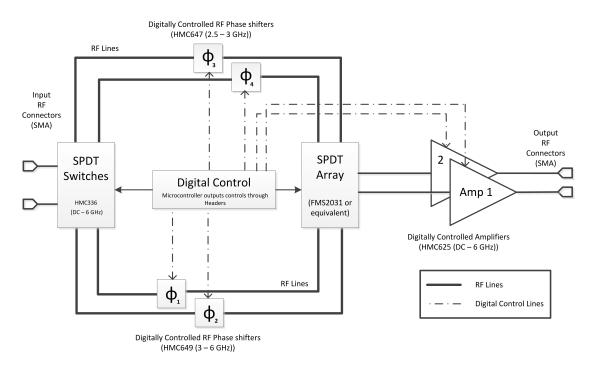

The design and fabrication of a wide-band programmable microwave feed network is proposed. The design architecture is composed of four main stages, switching, phase shifting, amplification/attenuation and control. The proposed feed network is designed to cover a wide band from 2.5 to 6 GHz over two separate branches, one covers from 2.5 to 3 GHz and the other covers from 3 to 6 GHz. Digitally controlled phase shifters are used to control the phase. A digital control unit is used to provide the required control signals for all the feed network stages. Digitally controlled wide-band variable gain amplifiers are used to set the appropriate amplitude to the signal in both paths.

The feed network is simulated and fabricated on an FR-4 substrate with thickness of 0.8mm. Good matching between simulation and measurement results is achieved. The measured amplitude resolution was 0.5 dB with an error of less than  $\pm 0.22/-0.12$  dB. The measured phase resolution was approximately 5.625° with an error of less than  $\pm 1^{\circ}$ . This value of phase resolution can achieve a scanning beam resolution of 1.8° for a linear antenna array. Also, the sidelobe levels can be controlled by amplitude tapering functionality of the proposed network. The proposed network is a generic two-path design that can be used as a standalone network to feed any kind of array system. The size of the two-path feed network was  $110 \times 63 \times 0.8 \text{mm}^3$ .

Since the feed network needs a kind of combiner circuit to combine all the outputs from the network to the input of a transceiver, a compact size 12-port microwave combiner with phase compensation is designed and fabricated. The combiner covers the band from 2.3 to 3 GHz. Its size was  $78.5 \times 61 \times 0.8 \text{mm}^3$ .

في هذا العمل تم تصميم وصنع شبكة تغذية ميكروويف واسعة النطاق ومبرمجة ذاتيا. تتكون بنية التصميم من أربع مراحل أساسية، التبديل، إزاحة الطور، توهين ومرحلة التحكم. صُممت هذه الشبكة لكي تغطي نطاق ترددي من ٢٠٥ إلى ٦ جيجاهيرتز. مغيري الطور يتم التحكم بهم رقميا للتحكم في الطور. وحدة تحكم رقمية تستخدم للتحكم في جميع مراحل شبكة التغذية. لإعطاء الإتساع المطلوب يتم استخدام مكبرات متغيرة التكبير رقميا.

لأن الشبكة تحتاج نوع من المجمع لتجميع كل النواتج إلى مدخل جهاز الإرسال والإستقبال، تم تصميم وتصنيع مجمع صغير الحجم ذو ١٢ منفذ. هذا المجمع صُم لنطاق ترددي من ٢٠٣ إلى ٣ جيجاهيرتز وشغل حجم 0.8 × 61 × 78.5 م <sup>3</sup> .

## CHAPTER 1

# INTRODUCTION

Programmable and tunable microwave circuits are attractive to microwave researchers because they offer flexibility and are needed in reconfigurable systems. These circuits can be digitally programmed and can be used for various functions based on specific needs. The design of dynamic reconfigurable microwave circuits operating at high frequencies seems to be a challenging task. However, these kind of circuits can be realized due to the advancement in Digital Signal Processing (DSP), microcontrollers and Field-Programmable Gate Array (FPGA) technology [1].

Radio Frequency (RF)/microwave feed networks can be constructed from a number of different high frequency circuit technologies for precise control of antenna patterns over a wide bandwidth. These networks can be used in military electronic systems, typically to control the signal amplitude and phase of multiple antennas or radiating elements in applications such as jammers, phased-array radar systems, and Unmanned Aerial Vehicles (UAV). They can be quite simple or complex, depending on the number of processing signal beams, and can be used for both transmission and reception.

Early designs were typically fixed-beam architectures. Recent configurations include complex adaptive beam forming networks. These networks can be formed with either active or passive configurations, printed circuit board or fabricated with Microwave Monolithic Integrated Circuits (MMIC) technology. Phased array antennas are complex systems with a combination of multidisciplinary designs encompassing array synthesis and analysis, design of RF feed networks, design of phase shifters biasing network, electronic switching control and programming the control algorithm with either a microcontroller or a Field Programmable Gate Array (FPGA).

For lower power consumption, short set-up time, easy to program and easy to change the design functionality, lower cost, and small size, we propose a design of a programmable RF feed network controlled by a microcontroller unit. The feed network will be a wideband one that covers wireless communications standards that lie between 2.5-6.0 GHz.

## 1.1 Thesis Objectives

The thesis objectives are as follows:

1. To come up with a wideband microwave feed network architecture that is digitally programmable in both phase and amplitude. Two-path (simulation and fabrication) and four-path versions (simulation) will be investigated.

- 2. To model and analyze the performance of the programmable wideband feed network and optimize its on-board performance.

- 3. To fabricate and test the performance of a 2-path programmable wideband feed network in the laboratory environment.

- 4. To come up with a complete program for controlling the phases and amplitudes of the feed network on a microcontroller board/chip.

## 1.2 Thesis Organization

The organization of this work is as follows, RF circuits fundamentals and design parameters are discussed in Chapter 2. Chapter 3 includes a detailed literature review in the area of feed networks and beamformers. The architecture and the design of the proposed feed network, PCB design, the fabricated model and the microcontroller unit are described in Chapter 4. Chapter 5 discusses the measured results for the proposed model. The 12-port combiner/splitter and its design process are discussed in Chapter 6 and finally Chapter 7 states the conclusions and future work.

## CHAPTER 2

# BACKGROUND

## 2.1 RF Circuits: Design and Parameters

In this section we will describe some basic RF design concepts and parameters that are used to characterize passive and active RF circuits. Then, the basic ideas of multi-beam networks and beamformers will be discussed in details.

### 2.1.1 Microstrip Transmission Lines

The planar transmission lines has the advantages of ease of fabrication and ease of integration with other microwave circuit devices. The stripline, microstrip line and slotline are examples of planar transmission lines. The most popular type of these lines is the microstrip line [2]. The structure of the microstrip line is a flat strip conductor of with (W) suspended above a ground plane by a thin dielectric material substrate of thickness (h) and relative permeability  $(\varepsilon_r)$ .

Figure 2.1: Structure and dimension of microstrip transmission line.

As shown in Figure 2.1 [2], microstrip has some (usually most) of its field lines in the dielectric region, concentrated between the strip conductor and the ground plane, and some fraction in the air region above the substrate. So, the microstrip line cannot support a pure TEM wave. The exact field of the microstrip line is very complex and constitute of a hybrid TM-TE waves. When the longitudinal components of the field for the dominant mode of a microstrip line is much smaller than the transverse components ( $h \ll \lambda$ ), the quasi-TEM approximation is applicable to facilitate design. So, by using this assumption, the phase velocity, propagation constant, and characteristic impedance can be obtained from static or quasi-static solutions. The guided wavelength of a microstrip line is given by:

$$\lambda_g = \frac{\lambda_o}{\sqrt{\varepsilon_{re}}} \text{ or } \lambda_g = \frac{300}{f(GHz)\sqrt{\varepsilon_{re}}}mm$$

(2.1)

where  $\varepsilon_{re}$  is the effective dielectric constant or the microstrip line (the equivalent dielectric constant to the air and the substrate together). Thus this value should

satisfy the following relation in (2.2) and can be calculated from (2.3).

$$1 < \varepsilon_{re} < \varepsilon_r \tag{2.2}$$

$$\varepsilon_{re} = \begin{cases} \frac{\varepsilon_r + 1}{2} + \frac{\varepsilon_r - 1}{2} \left(1 + \frac{12h}{W}\right)^{-0.5} + 0.04 \left(1 - \frac{W}{h}\right)^2; \text{ for } \frac{W}{h} \le 1\\ \frac{\varepsilon_r + 1}{2} + \frac{\varepsilon_r - 1}{2} \left(1 + \frac{12h}{W}\right)^{-0.5}; \text{ for } \frac{W}{h} > 1 \end{cases}$$

$$(2.3)$$

where, W and h represent the width and height of the transmission line, respectively. The characteristic impedance  $(Z_O)$ , given these line dimensions, can be calculated in (2.4).

$$Z_{o} = \begin{cases} \frac{\eta}{2\pi\sqrt{\varepsilon re}} \ln(\frac{8h}{W} + \frac{0.25W}{h}); \text{ for } \frac{W}{h} \le 1\\ \frac{\eta}{\sqrt{\varepsilon re}} \frac{W}{h} + 1.393 + 0.677 \ln(\frac{W}{h} + 1.4444)^{-1}; \text{ for } \frac{W}{h} > 1 \end{cases}$$

(2.4)

The propagation constant  $(\beta)$  of such a line is given by,

$$\beta = \frac{2\pi}{\lambda_g} \tag{2.5}$$

while it's phase velocity  $(\nu_p)$  is found from,

$$\nu_p = \frac{\omega}{\beta} = \frac{c}{\sqrt{\varepsilon_{re}}} \tag{2.6}$$

A microstrip electric length is  $(\theta)$  and it is defined as,

$$\theta = \beta l \tag{2.7}$$

There are many calculators available on the internet like AppCAD form Agilent, emtalk [3], and TXLINE [4] which is embedded in the Microwave Office (MWO) software that can be used to get the proper microstrip patameters based on its geometry and substrate type. Figure 2.2 shows an example for the synthesis of a microstrip line using the TXLINE software. A 50  $\Omega$  microstrip on an RT/Duroid 5880 substrate of  $\epsilon_r = 4$  and loss tangent  $\tan(\delta)$  of 0.03 should be 0.5mm wide on a substrate thickness of 10 mils (0.254 mm).

| licrostrip Stripline C    | PW   CPW Grour | nd   Round Coaxia | I   Slotline   C | oupled MSLine Cou     | pled Stripline  |             |      |

|---------------------------|----------------|-------------------|------------------|-----------------------|-----------------|-------------|------|

| Material Parameters       |                |                   |                  |                       |                 |             | _    |

| Dielectric RT/Duroi       | d 5880         | Conductor         | Copper           |                       | ]               | -₩ <u>+</u> |      |

| Dielectric Constant       | 4              | Conductivity      | 5.88E+07         | S/m 💌                 | ] [ ]           | ε, †<br>Τ   |      |

| Loss Tangent              | 0.03           |                   |                  | AWR                   | ]   <del></del> | °r .        | 777. |

| Electrical Characteristic | cs             |                   | 7 6              | Physical Characterist | ic              |             |      |

| Impedance                 | 50             | Ohms 💌            |                  | Physical Length (L)   | 17.0717         | mm          |      |

| Frequency                 | 2.5            | GHz 💌             | -                | Width (W)             | 0.519306        | mm          |      |

| Electrical Length         | 90             | deg 💌             | ->1              | Height (H)            | 10              | mil         |      |

| Phase Constant            | 5271.89        | deg/m 💌           |                  | Thickness (T)         | 0.003           | mm          |      |

| Effective Diel. Const.    | 3.08383        |                   |                  |                       |                 |             |      |

| Loss                      | 13.4104        | dB/m ▼            |                  |                       |                 |             |      |

Figure 2.2: Microstrip design example by TXLINE software.

There are several RF design concepts that should be taken into consideration during the design process. For a two-layer board (our design), the power stage, RF signal lines and RF components should be all on one layer (Top Layer) and the other layer (Bottom Layer) must be the ground (GND) plane. In the coming few sections, more details will be given on these concepts and parameters.

#### 2.1.2 Layout Design Fundamentals

RF layout is usually based on microstrip lines as the wave moves faster compared to a stripline structure. In addition, the traces and connections need to be done in a way to avoid impedance discontinuities such as 90° bends and vias. The separation between adjacent lines is also important to avoid crosstalk. Each of these issues will be discussed with some details in the points and definitions to come.

- **Crosstalk** The crosstalk is defined as the mutual influence of two nearby routed parallel traces or lines such as telephone lines, data lines, or system components. One of these two traces that carry the signal is called the aggressor and the other one is called the victim that is influenced by the aggressor. This occurs because of the inductive and capacitive coupling between these two traces. This effect can only appear in microstrip lines and can be canceled completely in stripline structures. So, we must keep the traces apart from each other at least 2 times the trace width to avoid or at least minimize crosstalk. Also crosstalk can occur between layers and to minimize this effect we need to route the line 90° to each other on different layers.

- Vias The use of vias is important in any RF design. They are used to provide stability and trace connections on various layers. Vias increase the trace length, generate additional inductance and capacitance, and reflections can occur due to impedance change.

Also when connecting the ground pins of RF Integrated Circuits (ICs), using Vias, it should be connected to the ground plane by the shortest way. In a stripline board, a sufficient number of via holes should be used to reduce the unwanted effects of the ground.

**RF T-Line bends** The design of the RF bend is very important and effective. The worst way for designing a bend is to use the right angle one because it has a huge amount of radiation. This is because right angle bend change the impedance at the corner due to the capacitance generated. It is not recommended to use the right-angle bends since it is the most lossy configuration for the RF bends. This is shown in Figure 2.3.

Figure 2.3: Different design of right angle bends, worst to best from left to right.

In our design, we used Optimally Mitered bends (MBEND3 in MWO). The Mitered bend geometry as designed in MWO is shown in Figure 2.4 [5].

Figure 2.4: The structures and the design parameters of the mitered BEND.

An optimum miter based on the dimensions shown in Figure 2.4 can be found from [5]:

$$\frac{X}{D} = 0.52 + .65 \times e^{-1.35 \times (W/H)}$$

(2.8)

where, H is the substrate thickness. Mitered bend has the range of use according to (2.9).

$$0.5 \le \frac{W}{H} \le 2.75$$

,  $2.5 \le \varepsilon_r \le 25$  and  $f \le \frac{15}{H(mm)}(GHz)$  (2.9)

here f is the simulation frequency. Finally, the printed mitered bend that is used in our design is shown in Figure 2.5.

Figure 2.5: Printed mitered bend.

#### 2.1.3 S-Parameters

A two-port network can be represented by different parameters such as an impedance matrix (Z), admittance matrix (Y), hybrid matrix (H), ABCD matrix, and S-parameters (S). At microwave frequencies Z, Y, H, and ABCD parameters are very difficult if not impossible to measure. The reason is that short and open circuit conditions to AC signals are difficult to implement over a broadband at microwave frequencies. Also, an active two-port might oscillate under short or open-circuit conditions. Therefore, a more appropriate representation of the two-port network at microwave frequencies is needed.

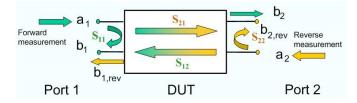

The S-parameters are seen to represent reflection or transmission coefficients. The S-parameters are measured at the specific locations shown as Port 1 and Port 2 in Figure 2.6 and are defined as follows [6];

$$S_{11} = \left(\frac{b_1}{a_1}\right)_{a_2=0} \tag{2.10}$$

$S_{11}$ : Input reflection coefficient with output properly terminated.

$$S_{21} = \left(\frac{b_2}{a_1}\right)_{a_2=0} \tag{2.11}$$

$S_{21}$ : Forward transmission coefficient with output properly terminated.

$$S_{22} = \left(\frac{b_2}{a_2}\right)_{a_1=0} \tag{2.12}$$

$S_{22}$ : Output reflection coefficient with input properly terminated.

$$S_{12} = \left(\frac{b_1}{a_2}\right)_{a_1=0}$$

(2.13)

$S_{12}$ : Reverse transmission coefficient with input properly terminated.

Figure 2.6: S-parameters for two-port network.

The advantage of using the S-parameters is that they are measured using matched conditions. Using matched resistive terminations to measure the S-parameters of an amplifier has the advantage that the amplifier does not oscillate. Also, the S-parameters can be cascaded easily to predict the system performance. Most of the simulation tools also can generate the S-parameters easily in different format. Finally, all the other parameters such as Y, Z, etc can be computed by knowing the S-parameters.

#### 2.1.4 Noise

Noise is usually generated by the random motions of charges or charge carriers in devices and materials. Several mechanisms that generate noise in active circuits are thermal noise, shot noise, flicker noise, plasma noise, and quantum noise. Because of the fact that, the thermal noise is the most important type of noise and it is the dominant one, we are going to discuss it in details in the next section.

**Thermal Noise** [7]: Any matter above 0K contains thermal energy that moves atoms and electrons around in a random way, leading to random currents, which are considered noise or thermal noise. The thermal noise spectral density in a resistor is given by

$$N_{resistor} = 4kTR \tag{2.14}$$

where T is the Kelvin temperature of the resistor, k is Boltzman constant  $(1.38 \times 10^{-23} J/K)$ , and R is the value of the resistor. Thermal noise is white noise, meaning it has a constant power spectral density with respect to frequency (i.e. wideband).

The output power spectral density when maximum power transfer occurs  $(P_o)$  is given by

$$P_o = \frac{{v_n}^2}{4R} = kT \tag{2.15}$$

where  $v_n$  is the rms value of the noise voltage and is given as a function of the bandwidth  $\Delta f$  by

$$v_n = 4kTF\Delta f \tag{2.16}$$

It is clear from (2.15) that the available power is independent of the resistor. The total output power is given as a function of the bandwidth B(Hz) by

$$P_{out} = kTB \tag{2.17}$$

For any receiver required to receive a given signal bandwidth, the minimum detectable signal can now be determined. As was seen in (2.17), the noise

floor depends on the bandwidth B. The signal-to-noise ratio (SNR) can be determined by

$$SNR = \frac{S}{NoiseFloor} \tag{2.18}$$

where S is the signal power. By considering there is no noise added to the circuit from other electronics, the Noise floor is given from (2.17) by

$$NoiseFloor = kTB = -174dBm/Hz + 10\log_{10}B(dBm)$$

(2.19)

The noise floor of a receiver determines its **sensitivity** to low-level signals and its capability of detecting and demodulating those signals.

Noise added by the electronics will be directly added to the noise from the input [8]. Noise from electronics is described by the *NoiseFactor* (F), which is a measure of how much the signal-to-noise ratio is degraded through the system and is given by [9]

$$F = \frac{S_i/N_{i(Source)}}{S_o/N_{o(Total)}}$$

(2.20)

where  $N_{o(total)}$  is the total noise at the output which is given by

$$N_{o_{(total)}} = N_{o_{(source)}} + N_{o_{(added)}}$$

$$(2.21)$$

and  $N_{o(source)}$  is the noise at the output originating from the source, and  $N_{o_{(added)}}$  is the noise at the output added by the electronic circuitry. The

Noise Figure (NF) is related to Noise Factor (F) by

$$NF = 10\log_{10}F\tag{2.22}$$

The NF is a measure of the degradation in the Signal-to-Noise ratio between the input and the output of the component, and thus,

$$F = \frac{S_i/N_i}{S_o/N_o} \ge 1 \tag{2.23}$$

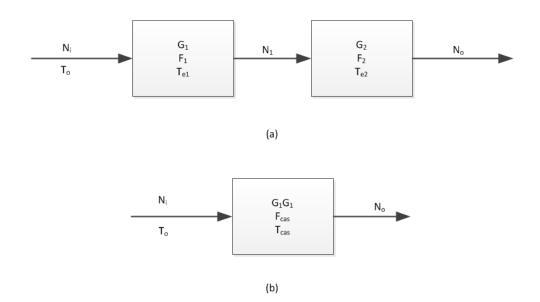

For the cascaded system shown in Figure 2.7, the cascaded NF can be calculated by the relation:

$$F_{cas} = F_1 + \frac{1}{G_1}(F_2 - 1) \tag{2.24}$$

Figure 2.7: Noise figure for a cascaded system.

where  $F_1$  and  $F_2$  are the noise figures of the first and second stages, respectively.  $G_1$  and  $G_2$  are the gains of the first and second stages, respectively.

#### 2.1.5 Linearity Metrics of RF Circuits

In real devices, and unlike ideal systems, the transfer function or the relationship between the input and output is not linear. The most common source of the non-linearity in RF circuits is the amplifier.

In this section, we will show the definitions of some amplifier metrics such as the 1-dB compression point and the third-order intercept point. Also, stability and sensitivity definitions will be discussed.

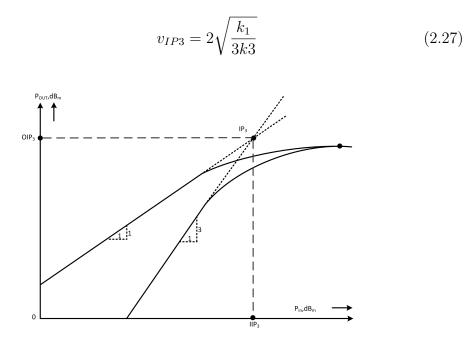

Third Order Intercept Point [10] The most common way to test the linearity of a circuit is to apply two signals at the input (two-tone test), having equal amplitude and offset by some frequency. Figure 2.8 shows the third-order intercept point of a real amplifier as a function of the input power. The output of the non-linear system can be written as a power series of the form

$$v_{out} = k_0 + k_1 v_{in} + k_2 v_{in}^2 + k_3 v_{in}^3 + \dots$$

(2.25)

, where  $v_{in}$  and  $v_{out}$  are the input and output waves of the system, and k's are the series coefficients. For the tone-tone test, the input  $v_{in}$  will be in the form

$$v_{in} = v_1 \cos \omega_1 t + v_2 \cos \omega_2 t \tag{2.26}$$

From the plot, the third-order intercept point (IP3) is determined. The thirdorder intercept point is a theoretical point where the amplitudes of the intermodulation tones at  $2\omega_1 - \omega_2$  and  $2\omega_2 - \omega_1$  are equal to the amplitudes of the fundamental tones at  $\omega_1$  and  $\omega_2$ . The output voltage at the third-order intercept point  $(v_{IP3})$  can be calculated by

Figure 2.8: Third-order intercept point.

The third-order intercept point (IP3 ) can be defined either with respect to the input (IIP3 ) or the output (OIP3 ) power of the circuit as shown in Figure 2.8 [11].

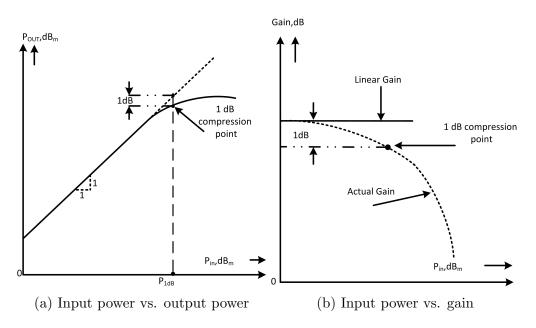

**1-dB Compression Point** [10]: The 1-dB compression point is simply the power level, specified at either the input or the output, where the output power is 1-dB less than it would have been in an ideally linear device. The

1-dB compression point is shown in Figure 2.9. Figure (2.9a) shows the input power versus output power. From this figure, we can get the 1-dB point with respect of the input or the output. Figure (2.9b) shows the gain versus input power [9].

Figure 2.9: 1 dB Compression Point.

The 1-dB compression voltage is given by

$$v_{1dB} = 0.22 \sqrt{\frac{k_1}{|k3|}} \tag{2.28}$$

where  $k_1$  and  $k_3$  are found from (2.25).

Typically, for solid state power amplifier, the third-order output intercept point is 10 dB higher than the output power at the 1-dB compression point.

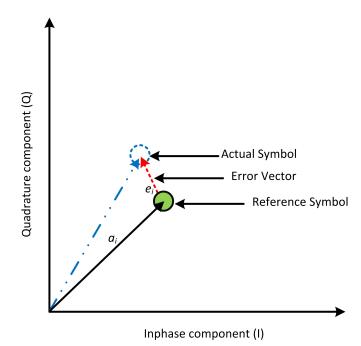

Error Vector Magnitude Error Vector Magnitude (EVM) is a very important

parameter to measure how accurately a transmitter has reproduced the vectors that correspond to the data being transmitted. EVM is the magnitude of the error vector, and is different from the magnitude error between the actual and reference constellation points. Figure 2.10 shows the error vector magnitude .

The instantaneous value of the EVM is defined as the ratio of the magnitude of the reference vector to the magnitude of the error vector

$$EVM_i = \frac{|e_i|}{|a_i|} \tag{2.29}$$

where  $e_i$  is the  $i^{th}$  error vector and  $a_i$  is the  $i^{th}$  reference vector.

Figure 2.10: Error vector magnitude.

#### 2.1.6 Stability of Active Circuits

The stability of an amplifier, or its resistance to oscillate, is a very important consideration in a design and can be determined from the S Parameters, the matching networks, and the terminations. In an amplifier, the oscillation is possible if either the input or output port impedances have a negative real part, or in other words, when  $|\Gamma_{in}| > 1$  or  $|\Gamma_{out}| > 1$ , where  $|\Gamma_{in}|$  and  $|\Gamma_{out}|$  are the input and output reflection coefficients, respectively. We have two types of stability:

- 1. Unconditional stability: The network is unconditionally stable if  $|\Gamma_{in}| < 1$ and  $|\Gamma_{out}| < 1$  for all passive source and load impedances.

- 2. Potentially unstable: This happen if  $|\Gamma_{in}| < 1$  and  $|\Gamma_{out}| < 1$  for a certain range of passive source and load impedances and not all ranges/values.

A convenient way of expressing the necessary and sufficient conditions for unconditional stability is

$$K > 1 \text{ and } |\Delta| < 1, \tag{2.30}$$

where

$$K = \frac{1 - |S_{11}|^2 - |S_{22}|^2 + |\Delta|^2}{2|S_{12}S_{21}|}$$

(2.31)

$$\Delta = S_{11}S_{22} - S_{12}S_{21}, \tag{2.32}$$

where K is called the stability factor.

Another form for the stability condition is:

$$K > 1 \text{ and } |B| > 0,$$

(2.33)

where B is the stability measure and can calculated using:

$$B = 1 + |S_{11}|^2 - |S_{22}|^2 - |\Delta|^2$$

(2.34)

These factors and their variants can be used to predict amplifier stability from S-parameter measurements.

## 2.2 Beamformers

Beamformers are complex networks used to precisely control the phase and amplitude of RF energy passing through them. When an array of N elements is connected to a beamformer with M beam ports, multiple simultaneous beams will be produced. Beamformers are typically used in RF transmitting and receiving systems. Beamforming can also be used to control a single beam out of an array and change its radiation maximum by changing the relative amplitude and phases of the excitations.

Beamformers are employed between the antenna arrays and the receiver, in a receiving mode, to effectively focus the radiation beam of the receiving system to a certain direction (the target). On the other hand, in the transmitting mode, radar systems for example, the beamformers are connected between the RF signal source and the antenna array system to shape the antenna beam towards a certain target or direction.

In general, beamformers are either networks or quasioptical lenses. Networks or lenses can be called beamforming networks (BFN). Power dividers , the Butler matrix , the Blass matrix, and the Nolen matrix are an examples of BFN networks.While, the Rotman lens, the Bootlace lens, and the Dome lens are an examples of BFN lenses [12]. In a lens BFN, the beamwidths and crossover levels are dependent on frequency, while beam angles are fixed. This is because the lenses are true-time delay devices. Hence, they produce the same beam angles independent of frequency. In a network BFN, changing the frequency will change the beamwidths and beam angles, while beam crossover levels are independent of frequency.

In this section, we are going to describe in details the theory behind these different types of BFN. For the network BFN, the Butle matrix is the most popular one, while for lenses, the Rotman lenses had many practical applications.

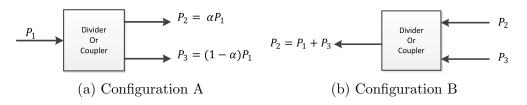

#### 2.2.1 Power Divider BFN

The simplest BFN uses power dividers to split the transmitted power between N input elements of antenna array. A constant phase shifter is employed in each division to achieve the progressive phase shift. Power dividers and directional couplers are passive microwave circuits used for splitting or combining power. Dividers and couplers are used in feed networks for antenna arrays, balanced mixers, power transmitters and test instruments.

Figure 2.11 shows the working concept of the combiners/splitters, where  $0 < \alpha < 1$ . A coupler may be a three or four port component. T-junction and other power dividers are three-port networks, while directional couplers and hybrids are four-port networks.

Equal power division (3-dB type) and unequal power division ratios are also possible with power dividers. Directional couplers are used to get arbitrary power division, while hybrids { 90° hybrid (Quadrature) or 180° hybrid (magic-T)} usually have equal power division [2].

Figure 2.11: Power splitting/combining in dividers/splitters.

Before going into the details of the power divider beamformers, we are going to describe the functionality of the basic elements of the power dividers.

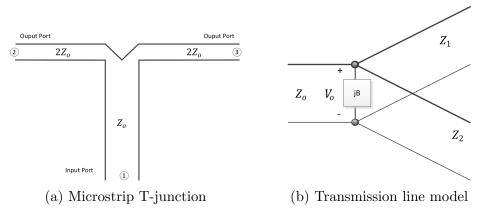

#### 2.2.1.1 T-junction Power Divider

The simplest three-port power divider is the T-junction which can be used as a divider or combiner. The microstrip T-junction design and its transmission line model are shown in Figure 2.12. This type of divider is considered lossless, but it cannot be matched simultaneously at all ports. The T-junction can be modeled by a transmission line model as shown in Figure 2.12(b). By assuming a lossless

junction, we must have the condition in equation (2.35) to match the input line with the two output lines [2].

$$\frac{1}{Z_1} + \frac{1}{Z_2} = \frac{1}{Z_o} \tag{2.35}$$

where  $Z_o$  is the characteristic impedance of the input line, and  $Z_1$ ,  $Z_2$  are the characteristic impedances of the output ports. So, we can choose  $Z_1$  and  $Z_2$  to provide ratios of power division. For a 3-dB (equal division) power divider, if the input line characteristic impedance  $Z_o$  is 50 $\Omega$ , a 100 $\Omega$  output line will be chosen.

Figure 2.12: T-junction power divider.

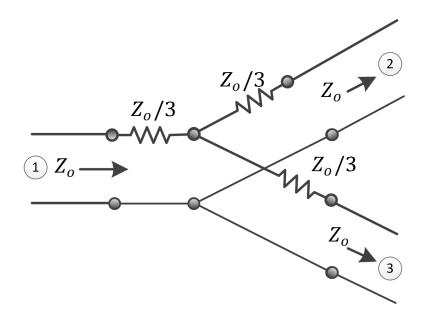

If we need all ports to be matched, lossy components such as lumped resistors are used. In such case, the output ports are not isolated anymore. This divider is called the resistive divider which uses lumped resistors. Equal and unequal splitting are possible with resistive dividers. Equal-split three-port resistive power divider is shown in Figure 2.13. All ports have the same characteristic impedance  $Z_o$ , accordingly all ports are matched together and matched with the load lines.

Figure 2.13: An equal-split three-port resistive power divider.

The S-parameters of the input-output ports,  $S_{21}$ ,  $S_{31}$  and  $S_{23}$  are equal 0.5 and hence the network is reciprocal and the scattering matrix is symmetric, and can be written as

$$[s] = \frac{1}{2} \begin{bmatrix} 0 & 1 & 1 \\ 1 & 0 & 1 \\ 1 & 1 & 0 \end{bmatrix}$$

(2.36)

Low isolation between the output ports, and the resistive losses are the major two disadvantages of the resistive power divider. As a result, the Wilkinson [13] power divider is considered to overcome these two problems.

#### 2.2.1.2 Wilkinson Power Divider

The Wilkinson power divider (WPD) is generally an N-way hybrid splitter with arbitrary power division. Since the isolation between the output ports in a T- junction and the resistive divider is still not achieved, the Wilkinson power divider has the property that the reflected power is dissipated, hence good isolation between output ports is achieved. In the ideal case, the scattering matrix of a Wilkinson divider given by [14],

$$[s] = \frac{-j}{\sqrt{2}} \begin{bmatrix} 0 & 1 & 1 \\ 1 & 0 & 0 \\ 1 & 0 & 0 \end{bmatrix}$$

(2.37)

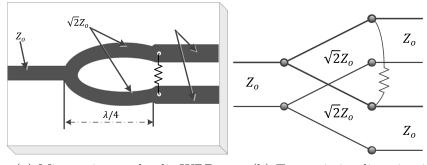

A two-way microstrip Wilkinson power divider is shown in Figure 2.14. In this design, the input at port (1) is evenly divided in amplitude and phase at output ports (2) and (3). A high isolation between output ports can obtained by using  $\lambda/4$  impedance transformers having a charcteristics impedance of  $\sqrt{2}Z_o$  and a lumped isolation resistor of  $2Z_o$  with all three ports matched. The equivelent transmission line circuit is shown in Figure 2.14(b).

(a) Microstrip equal-split WPD. (b) Transmission line circuit.

Figure 2.14: The Wilkinson power divider.

#### 2.2.1.3 Switched-Line Phase Shifters

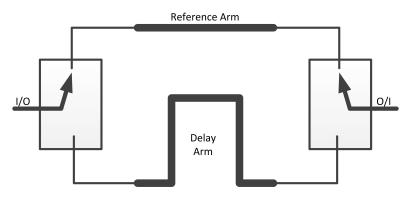

A simple phase shifter can be implemented by switching between a two different transmission line lengths. This type of phase shifter called switched-line phase shifter. Figure 2.15 shows the fundamental unit (1 bit) of the switched-line phase shifter. It has two arms, a reference arm and a delay one. Switched-line phase shifter has the advantages of wideband, low loss, simple structure, and high performance in phase accuracy and isolation.

Figure 2.15: Switched-line phase shifter.

The switched-line phase shifter os dependent on the lengths of microstrip line used. In N-bit phase shifter, the incoming input signal is routed/switched through one of N-way alternate paths to the output, so as to introduce specific phase shifts with minimum loss [15].

The switching elements in the switched-line phase shifter can be relays (or mechanical switch), Field Effect Transistors (FET), PIN diodes, or microelectromechanical switches (MEMS) [16]. Depending on the frequency band of interest, the switching technology can be chosen. The PIN diodes can be used up to 18 GHz and it is preferred compared to FET technology but it is difficult for integration and fabrication.

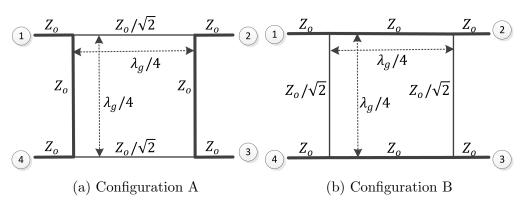

#### 2.2.1.4 The 90° Hyprid Coupler

The conventional 90° hyprid coupler is essentially a four-port device comprising four arms. Each of its arms has a length of one quarter-wavelength at the operating desired design frequency [17]. Schematic diagrams are shown in Figure 2.16 for two configurations of the hybrid coupler. The effect of the two configurations is the same, but Figure 2.16(b) is more suitable since it has two continuous  $Z_o\Omega$ tracks joined by two parallel arms of impedances  $Z_o/\sqrt{2}$ .

Figure 2.16: 90° Hybrid Coupler

If the signal is fed at port (1) (in this case, port (4) is loaded with  $Z_o$ ), the output ports (2) and (3) will be have two equal output signals, but with a 90° difference in phase. The same process will happen if the feed was from port (3) { and port (1) is loaded by  $Z_o$  }. No power is coupled to port (4) (the isolated port). Thus, the [S] matrix will have the following form [2]

$$[s] = \frac{-1}{\sqrt{2}} \begin{bmatrix} 0 & j & 1 & 0 \\ j & 0 & 0 & 1 \\ 1 & 0 & 0 & j \\ 0 & 1 & j & 0 \end{bmatrix}$$

(2.38)

#### 2.2.2 Power Dividers BFN examples

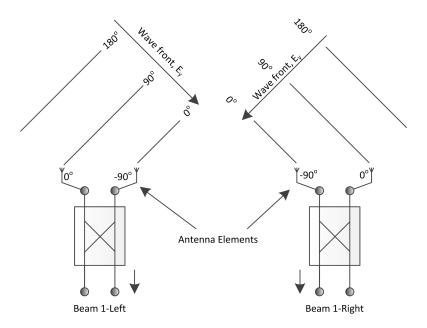

The design of a beamforming network using power dividers, hybrids, and directional couplers were done in [18–21]. A simple beamformer comprising a simple antenna array connected to a quadrature coupler is shown in Figure 2.17. As mentioned in section 2.2.1.4, the quadrature coupler in a receiver system will combine the signals separated by  $90^{\circ}$  in one output and cancel it in the other output. If the wavefront is arriving form the left, it will arrive at the left antenna prior to the right one. Hence, the signal will route to the left arm of the coupler. On the other hand, a reversed situation will happen when the wavefront will arrive from the right.

Figure 2.17: Simple beamformer using quadrature coupler.

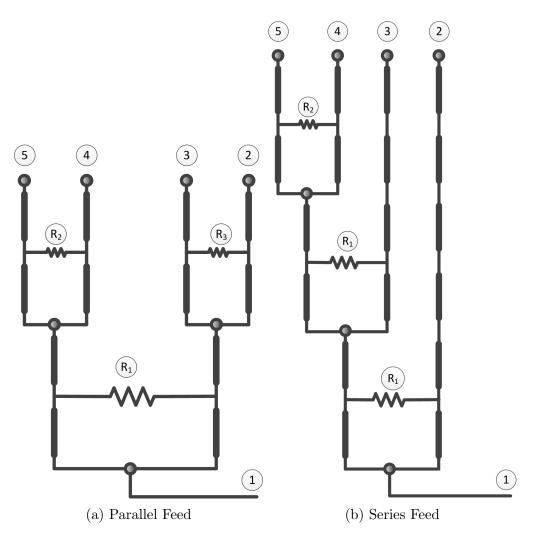

In [19], a Wilkinson-type and coupled-line power dividers were used to feed a planar antenna array system. These networks allow parallel or series feed. The outputs of the feed networks were all in-phase with non-uniform power distribution. This will control the sidelobe suppression level. In order to equalize the phase shift at the output ports, a wilkinson-type in-phase power divider is presented in 2.18. In Figure 2.18(a), a parallel feed network is shown, in which signal power is divided at each level of the pyramid structure of the network at every port, while in Figure 2.18(b), a series feed network is shown, in which the signal power is divided only at the left hand side ports of the individual dividers.

Figure 2.18: Wilkinson-type in-phase power divider.

Another work that used the hybrid power dividers as a feed network was [18]. In this work, a design of two different feed networks for phased array applications were presented. The directional couplers were applied in a series feed network while the Wilkinson dividers were applied in a parallel feed.

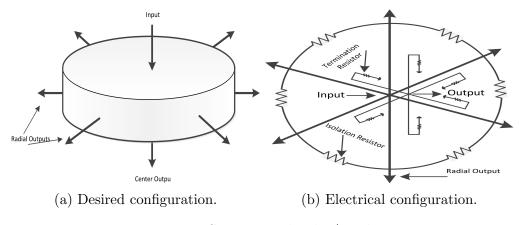

A novel beamforming network using a seven-way power divider/combiner was used in [20]. New two configurations of a seven power divider/combiner were presented as the key of the proposed feed networks. The schematic and electrical configuration of the first divider is shown in Figure 2.19.

Figure 2.19: Seven-way divider/combiner.

In this design, half of the input power must be delivered to the center output, while the remaining power is divided equally among the six radial ports. The second configuration of the divider depends on a two-way Wilkinson power divider as shown in Figure 2.20. The first design has the advantages of physical simplicity, circular symmetry, and low loss, while the second design has high isolation (Wilkinson) and easier construction.

Figure 2.20: Electrical configuration of the second seven-way divider/combiner.

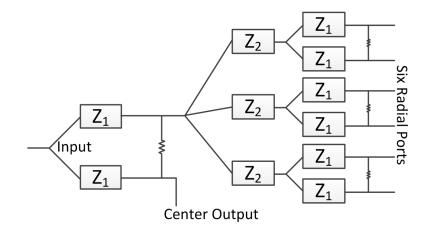

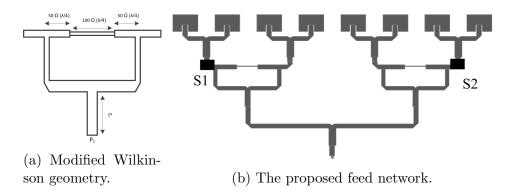

A new way of controlling the beam shape by altering the number of array elements was presented in [21]. As shown in Figure 2.21(a), a modified Wilkinson power divider was used to construct the reconfigurable antenna array in Figure 2.21(b). S1 and S2 are PIN (Intrinsic PN) diode RF switches that are used to alter between 4-elements and 8-elements antenna array structure. For an 8-element, the radiation pattern has a concave patten, while for the 4-element antenna mode, a convex pattern will be generated.

Figure 2.21: The structure of the corporate fed reconfigurable antenna array.

#### 2.2.3 Network BFN

#### 2.2.3.1 Maxon-Blass matrix

The Maxon-Blass matrix uses a set of array element transmission lines which intersect a set of beam ports lines, with a directional coupler at each intersection [22]. It is particularly useful when a small number of M narrow beams is required from a ralatively large number of array ports N. The line lenghts between the couplers in the series feeds to the array ports must achieve spatial orthogonality of the beams at the design frequency. Out of frequency range, the beam directions will change. A schematic of a Blass matrix BFN for six beams with eight antenna elements is shown in Figure 2.22 [17].

Figure 2.22: Schematic of a Blass matrix BFN for 6 beams with eight antenna ports.

Along the radial directions, the transmission line section have equal length, while along the circumferential directions, the line sections have different lengths. This difference in length will generate a constant progressive phase at each array port, generating a scanned beam. If the Blass matrix is used with TEM transmission lines (ex. coaxial cables), the beam location will not change with frequency and the Blass matrix will be a true time-delay beamformer in this case. While, for non-TEM transmission lines (ex. waveguide), the beam location will change with frequency. Also, amplitude tapering can be achieved by suitably selecting coupling factors of the directional couplers [23].

#### 2.2.3.2 Butler matrix

The Butler matrix is a typical example of an analog beamformer. It consist of a network of couplers, fixed phase shifter (added line length), and crossovers with N input ports, connected to the antenna elements, and an equal number of beam outputs. A schematic design for a four-port Butler matrix is shown in Figure 2.23. Because of the fact that the Butler matrix is the microwave realization of the fast Fourier transform (FFT), it has the minimum number of couplers. Since the Butler matrix has crossovers, it uses a multi-layer structure. Modern Butler matrices can be implemented on printed circuit boards. Some limitations of the Butler matrix are:

- 1. Narrow band.

- 2. Very complicated design for a large number of beam ports [17].

- 3. The sidelobes are realtively high (No amplitude tapering).

- 4. There is a loss of the order 3-5 dB.

- 5. Designed for  $2^n$  array elements.

Figure 2.23: Schematic for four-port Butler matrix.

### 2.2.3.3 Nolen Matrix

A generalization of Blass and Butler matrices yields a Nolen matrix [24]. It consists mainly of hybrid couplers and phase shifters as shown in Figure 2.24.

Figure 2.24: Schematic for Nolen matrix BFN.

In Nolen matrix, the number of beam ports can differ from the number of antenna elements as in Blass matrix. Nolen matrix is an implementation of the general discrete Fourier transform (DFT) algorithm, which can be applied to any number of elements. Therefore, it can be reduced to simpler forms, as the FFT algorithm and its application of the Butler matrix [25]. Due to the difficulties of the Nolen BFN and its network adjustments, it is seldom used [12].

#### 2.2.4 Lens BFN

#### 2.2.4.1 Rotman Lens

Figure 2.25 shows the schematic of a two-dimensional Rotman lens. The original lens uses parallel plate waveguide for the feed portion (beam ports), and coaxial cables for the transmission lines connecting the element ports to the radiating array elements. The beam ports are situated along a beam port surface and the array ports are located on an array port surface. The two surfaces are circular arcs. The beam port surfaces usually have a large curvature than the array port surface [12].

Figure 2.25: Rotman lens beamformer.

The Rotman lens are, in principle, wideband systems since their design is based upon geometrical optics and corresponds to a time-delay beamformer. Assuming the transmit mode operation of the lens, the beam ports are considered radiators and the array ports as receiving elements that are connected to the array elements though transmission lines. The lengths of these transmission lines are equal. Because of this, and to keep the antenna array on a line, some of the lines are more squeezed than others.

To explain the principle of operation of the lens, assume the lens is working in

the transmit mode. If one of the beam ports (radiator) is exited, the signal will arrive at each receiving element with a phase difference proportional to the patch length between the radiator and the receiving element [23]. Now, if the array port surface is designed such that the path length varies linearly with the locations of the receiving elements on the array port surface, then the array elements will have a linear phase distribution resulting in a scanned beam. Thus each beam port has a beam with a unique scan angle. Unfortunately, it is impossible theoretically to obtain a linear phase for all beams. Also, the amplitude asymmetry for the beams raises the sidelobe levels [12]. Another disadvantage is the relatively low number of achievable beams and difficulty of achieving low sidelobes and low losses [26].

## CHAPTER 3

## LITERATURE REVIEW AND RESEARCH METHODOLOGY

## 3.1 Literature Review

In this section, we will go over the related work of standalone feed networks and their performance as they appeared in the literature. Many types of feed networks such as fixed beam, multi-beam (most of them done by Butler matrix feed network) and switchable feed networks were proposed. The main goal of the research in this area is to improve the resolution of the scanning beam as well as cover a wide frequency range. Most of the designs covered narrow-band frequency range and were under 3 GHz. Thus, there is a need to widen the frequency ranges as well as make the beam scanning process programmable for better flexibility.

As discussed in chapter 2, the feed network or beamformer can be done with networks such as power dividers/combiners and Butler matrix [27–31], or lenses such as the Rotman lens [32–35]. In this literature review, we are going to focus on the most two popular BFNs which are the Butler matrix and the Rotman lens. In [27], a multi-beam matrix network created by four 90° hybrid couplers which realizes the required excitation for four beams spaced by 90° in the azimuth plane for antenna arrays is presented. The concept of the matrix developed for this application is much simpler than conventional methods and uses only four directional couplers feeding the four antenna elements, without additional fixed phase shifters and without line crossings as known from the Butler Matrix. The matrix covers the band from 2.4 to 3.4GHz with isolation better than 25dB and the reflection coefficient better than -15dB. For a four-square array of monopoles, the desired four beams are at  $\pm 45^{\circ}$  and  $\pm 135^{\circ}$  in the azimuth plane and the 3dB beam widths were about  $80^{\circ}$ . The cross-over levels of neighboring beams are about 3dBbelow the main beam peak and deep nulls appear under  $\pm 90^{\circ}$  form the direction of the main beam.

The design of a 2.5 GHz monolithic  $4 \times 4$  Butler matrix was introduced in [28]. This was the first complementary metal oxide semiconductor (CMOS) Butler matrix MMIC. Unlike the conventional Butler matrix, the 3dB quadrature coupler is replaced by a CMOS coupler that is called phased compensated transformer. The CMOS quadrature coupler is realized with the bifilar broadside-coupled transformer. Comparing this CMOS quadrature coupler (insertion loss is 4.21dB at 2.5GHz) with and ideal 3dB quadrature coupler, the additional 1.2dB loss is caused by the parasitic resistance of metal lines and the substrate. The isolation and return loss of the coupler are better than 20*dB*. The transformer-based quadrature coupler is terminated at port 2 and port 3 by purely reactive (lossless) loads to build the reflection-type phase shifter. The multilayer crossover achieves isolation better than 50*dB*. The area of the designed CMOS Butler matrix is  $1.36 \times 1.47mm^2$  and was fabricated using  $0.18\mu m$  CMOS process. Beam directions at  $-45^{\circ}$ ,  $-15^{\circ}$ ,  $15^{\circ}$ , and  $45^{\circ}$  are generated when connecting the matrix to a  $1 \times 4$  linear antenna array. The measured amplitude imbalanced is less than 1.5dB and the phase imbalance is less than  $4^{\circ}$  from  $2.4\mathbf{to}2.6GHz$ .

A feed network for a  $2 \times 2$  antenna array to construct a sectoral conical beam was presented in [29]. The feed network was constructed using four 90° hybrids, one crossover, and four 90° delay lines which are connected to the one coupled port of one of the 90° hybrids. Depending on the input port used, the radiation patterns are created at 45°, 135°, 225°, and 315° azimuth angles. This design can be used to communicate with satellites in geostationary orbits for Satellite Digital Multimedia Broadcasting (S-DMB). The design was fabricated on a Microstrip substrate with dielectric constant of 6.5 and thickness of 0.635mm. The design operated at 2.6GHz and the distance between the antenna elements was 60mm along the x and y directions.

In [36], a single-feed switchable feed network that combines two ports of a microstrip antenna with a quarter-wavelength feed lines was presented. This network assumes that the operating frequency ratio to be less than 1.4 : 1 for the two microstrips patch antennas. The network consists basically of two quarter-wavelength branch lines with different characteristic impedance  $(l_1 \text{ and } l_2)$  and two microstrip patch antennas. Since the resonance frequency of the two antennas are very close  $(\frac{f_1}{f_2} \leq 1.4)$ , then the two branch lines are almost equal in length. Thus if it is applied  $f = f_1$  to the input port, one patch would be at resonance and the other one would be at off-resonant, and vice versa. So, by applying  $f_1$  or  $f_2$ , this network will act as a switch. Such that the feed network can be applied to a radiation pattern or polarization reconfigurable antenna system where diversity is needed. The overall dimension of the network (including the two patch antennas) was  $200mm \times 100mm$  that was designed on a Teflon substrate ( $\varepsilon_r = 3.48, t = 1.5mm$ ) and fed by a 50 $\Omega$  coaxial connector. This network is working at two resonant frequencies, 1.94GHz and 2.13GHz.