# A SPECIAL PURPOSE PROCESSOR FOR IC TESTING AND SPEED CHARACTERIZATION

BY AMRAN AL-AGHBARI

9

e de de de de

Celek 1

A Thesis Presented to the DEANSHIP OF GRADUATE STUDIES

KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

# **MASTER OF SCIENCE**

In

**COMPUTER ENGINEERING**

December, 2012

#### KING FAHD UNIVERSITY OF PETROLEUM & MINERALS DHAHRAN- 31261, SAUDI ARABIA **DEANSHIP OF GRADUATE STUDIES**

This thesis, written by AMRAN ABDULRAHMAN ABDULWALI AL-AGHBARI under the direction his thesis advisor and approved by his thesis committee, has been presented and accepted by the Dean of Graduate Studies, in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE IN COMPUTER ENGINEERING.

Dr. Basem AL-Madani Department Chairman

Dr. Salam A. Zummo Dean of Graduate Studies

Dr. Mohammed E. S. Elrabaa. (Advisor)

Dr. Aiman Helmi El-Maleh (Member)

Dr. Abdulhafidh Bouhroua (Member)

17/3/13

Date:

# © AMRAN ABDULRAHMAN ABDULWALI AL-AGHBARI 2012

## Dedication

To my beloved parents, brothers and sisters all of them who I live for and think of. To my wonderful wife who are behind my happiness and success. To my teachers and doctors who taught me with good emotions and feeling that they care of me. To my friends who support me and are being happy when they feel me on a right way. To all who respect the truth and the goodness and follow the truth once they know it.

## ACKNOWLEDGMENTS

All thanks and praise are due to my God, Allah (azzawajal) who created me, blessed me with health, as well as provided me with patience and ambition to achieve this research.

I acknowledge deeply my thesis advisor Dr. Mohammed Elrabaa who guided me in this research and I actually learned from him many things in this specific field and in computer engineering in general.

I acknowledge my university King Fahd University for Petroleum and Minerals (KFUPM). I acknowledge the Computer Engineering Department (COE). I acknowledge the faculties who taught me, helped me and were very very cooperative and interactive. I acknowledge all of them for pushing me to be at my current scientific level.

I acknowledge King Abdulaziz City for Science and Technology (KACST) for their supporting for the project related to the thesis and for providing us with all needed devices.

I acknowledge Saudi Arabia Kingdom for providing me an MS scholarship and for the facilitations on different fields and providing us with an excellent learning environment.

## **TABLE OF CONTENTS**

| DEDICATION                                  | III  |

|---------------------------------------------|------|

| ACKNOWLEDGMENTS                             | IV   |

| TABLE OF CONTENTS                           | V    |

| LIST OF TABLES                              | XI   |

| LIST OF FIGURES                             | XII  |

| LIST OF ABBREVIATIONS                       | XVII |

| ABSTRACT                                    | XIX  |

| ملخص الرسالة                                | XX   |

| CHAPTER 1 INTRODUCTION                      | 1    |

| 1.1 Circuit IPs                             | 2    |

| 1.2 IC Testing                              |      |

| Design for Testability (DFT)                |      |

| Testing Principle                           |      |

| Characterization Process                    | 4    |

| 1.3 Thesis Organization                     | 5    |

| CHAPTER 2 LITERATURE REVIEW                 | 6    |

| 2.1 Digital circuit prototyping             | 6    |

| Virtual Prototyping                         | 6    |

| Physical Prototyping                        | 7    |

| BIST-based test processors                  | 7    |

| Software-based testing                      |      |

| Low-cost FPGA-Based testers                 |      |

| 2.2 Multi-cycle processors                  |      |

| CHAPTER 3 OVERVIEW OF THE PROPOSED TEST AN  | D    |

| CHARACTERIZATION PLATFORM                   | 14   |

| 3.1 The TACP Support circuitry (TSC)        |      |

| TSC Fixed interface                         |      |

| 3.1.1 The Configurable Clock Generator      |      |

| 3.1.2 The Frequency Measuring Circuit (FMC) |      |

| 3.1.3    | The Clock Selection and Application Circuit (CSaAC) | 20 |

|----------|-----------------------------------------------------|----|

| 3.1.4    | The Port Selection Block                            | 22 |

| 3.1.5    | The Test Application/Result Ports (TAP/TRP)         | 23 |

| 3.2 Use  | r Interface Software                                |    |

| Interfa  | ace Protocol                                        |    |

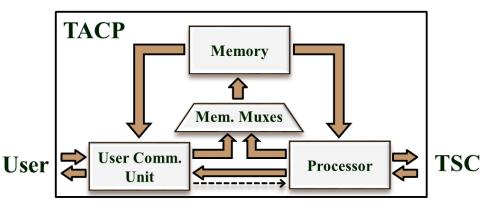

| 3.3 Test | t and Characterizing Processor (TACP)               |    |

|          | ssor                                                |    |

| Memo     | ries                                                | 29 |

| User (   | Communication Unit                                  |    |

| СНАРТЕ   | R 4 DESIGN OF THE TEST AND CHARACTERIZATION         |    |

| PROCES   | SOR                                                 |    |

| 4.1 Inst | ruction Design and Microinstructions                |    |

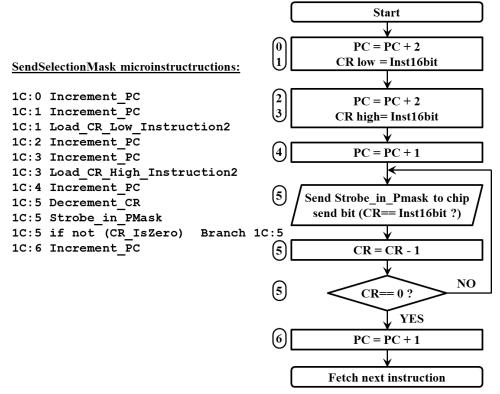

| 4.1.1    | SendSelectionMask instruction design                |    |

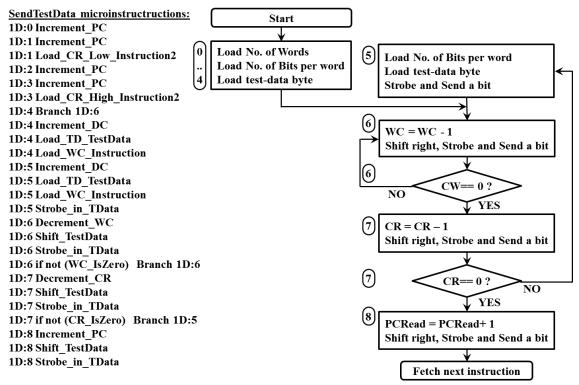

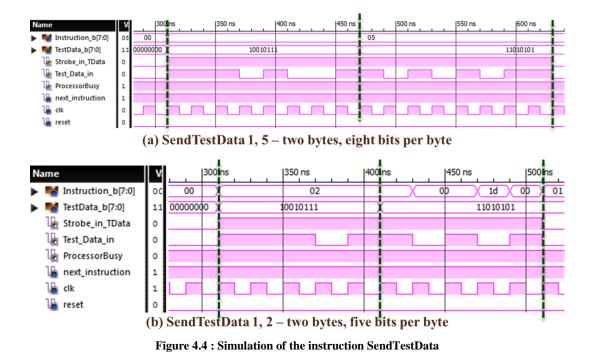

| 4.1.2    | SendTestData instruction design                     |    |

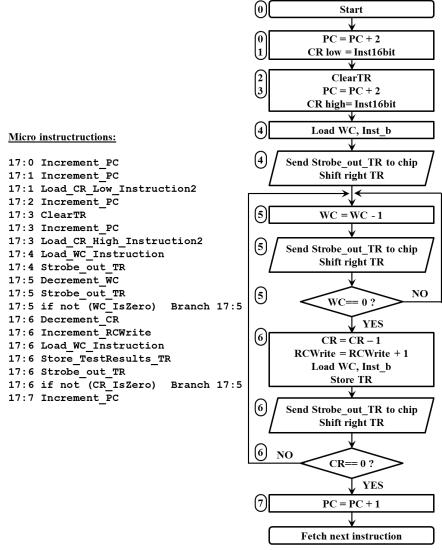

| 4.1.3    | ReadResult instruction design                       |    |

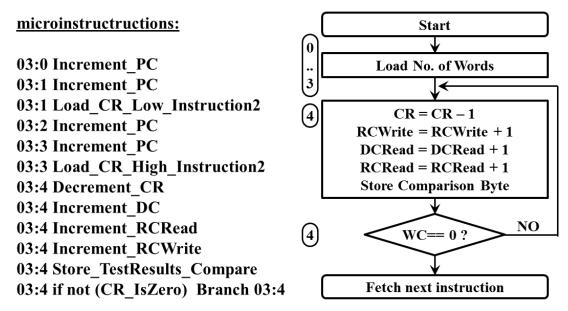

| 4.1.4    | Compare instruction design                          |    |

| 4.2 TA   | CP Top Level Design                                 |    |

| 4.3 Use  | r Communication Unit                                |    |

| 4.3.1    | UART module                                         | 40 |

| 4.3.2    | Communication flags                                 |    |

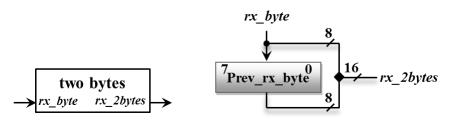

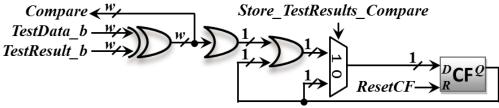

| 4.3.3    | Previous received byte register                     | 44 |

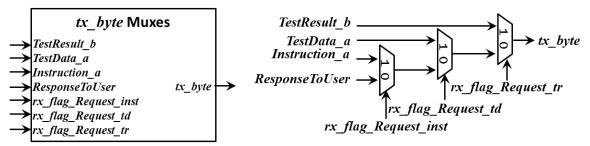

| 4.3.4    | Transmitted byte multiplexers                       | 44 |

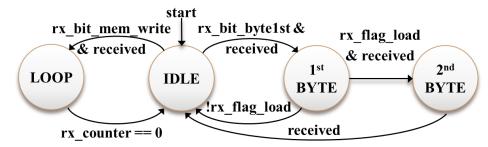

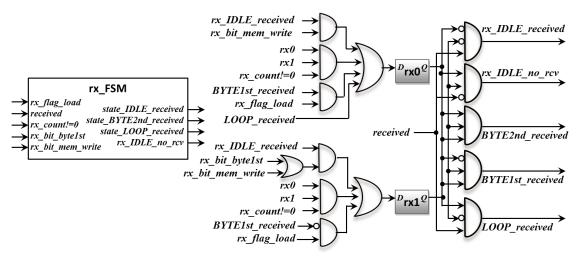

| 4.3.5    | Receiving state machine (rx_FSM)                    | 45 |

| 4.3.6    | Transmitting state machine (tx_FSM)                 | 47 |

| 4.3.7    | Break point register                                | 49 |

| 4.3.8    | Receiving counter                                   | 49 |

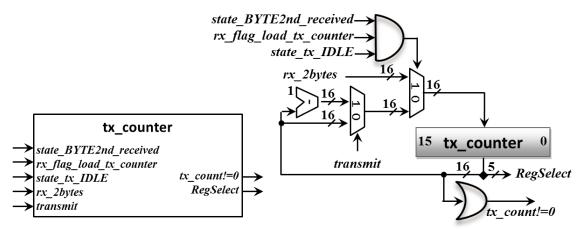

| 4.3.9    | Transmitting counter                                | 50 |

| 4.3.10   | Communication Error Flag                            | 51 |

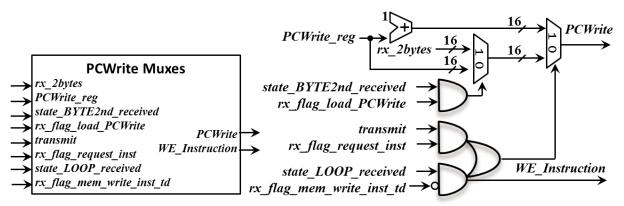

| 4.3.11   | PCWrite circuitry                                   | 51 |

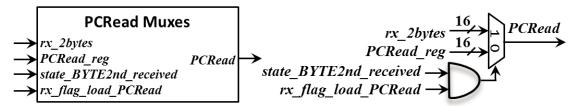

| 4.3.12   | PCRead circuitry                                    |    |

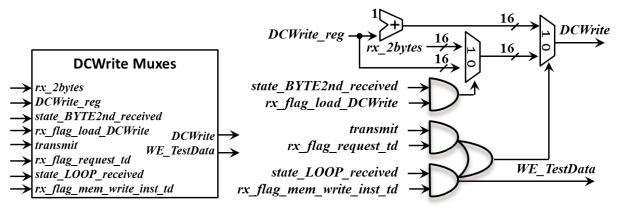

| 4.3.13   | DCWrite circuitry                                   | 53 |

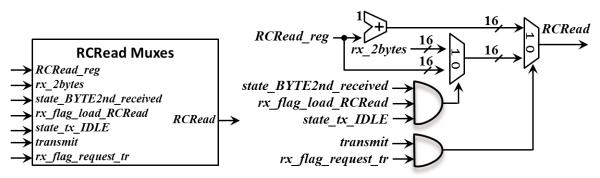

| 4.3.14   | RCRead circuitry                                    | 54 |

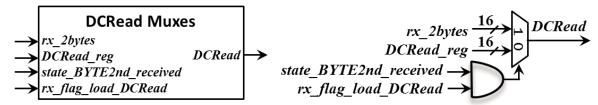

| 4.3.15   | DCRead circuitry                        | 54 |

|----------|-----------------------------------------|----|

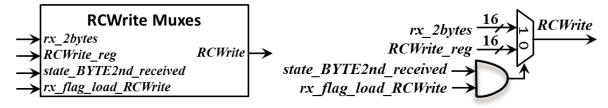

| 4.3.16   | RCWrite circuitry                       | 55 |

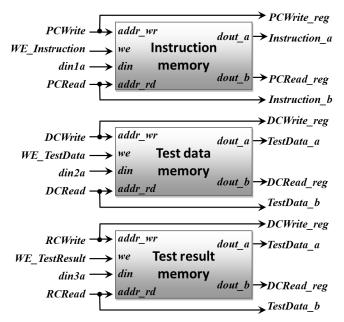

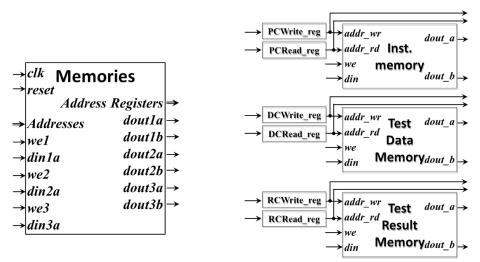

| 4.4 Men  | nories                                  | 55 |

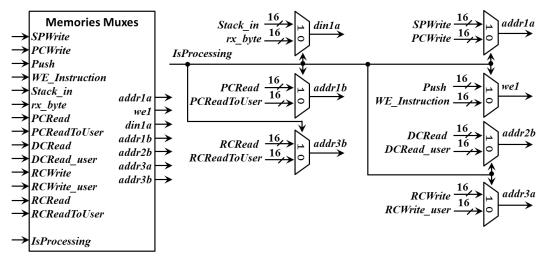

| 4.5 Men  | 10ry Multiplexer                        | 56 |

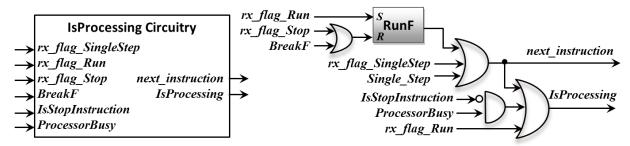

| IsProce  | essing Circuitry                        | 57 |

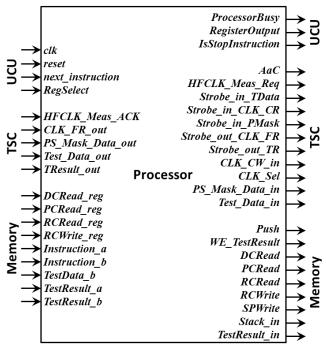

| 4.6 TAC  | CP Processor                            |    |

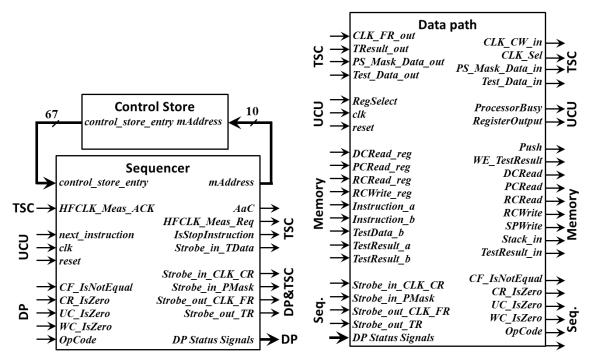

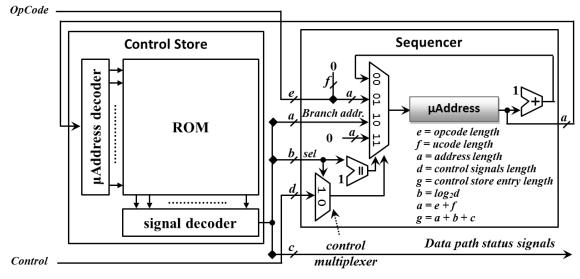

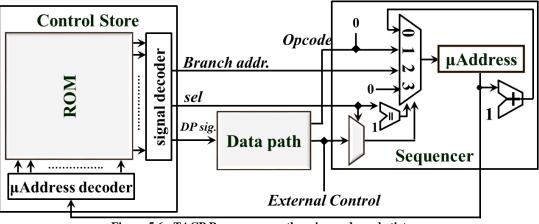

| 4.6.1    | The sequencer                           | 60 |

| 4.6.2    | The control store                       | 61 |

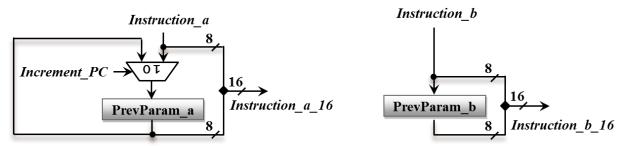

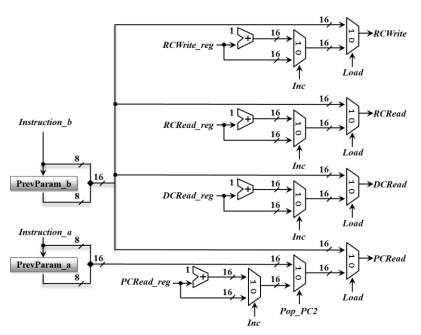

| 4.6.3    | Two previous parameter registers        | 64 |

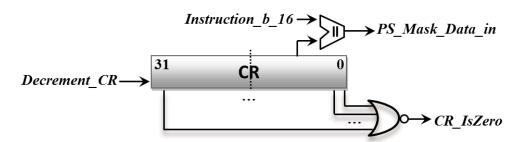

| 4.6.4    | Port selection mask circuitry           | 65 |

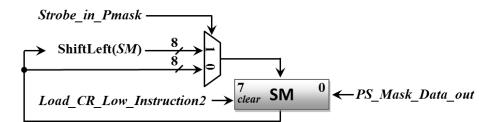

| 4.6.5    | Selection mask shift register SM        | 66 |

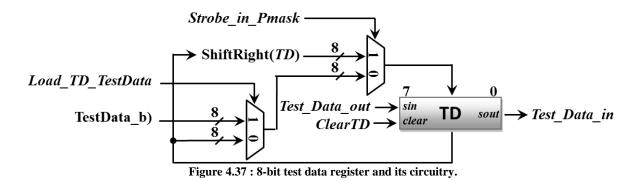

| 4.6.6    | Test data shift register TD             | 67 |

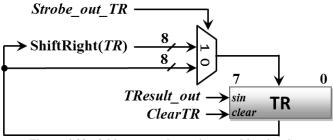

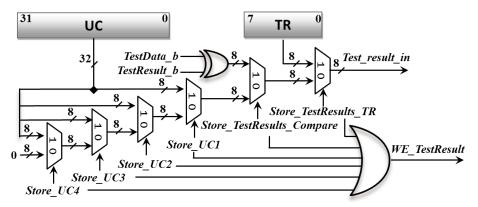

| 4.6.7    | Test result shift register TR           | 67 |

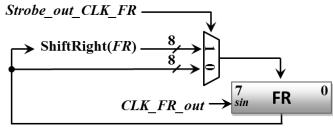

| 4.6.8    | Frequency register FR                   | 68 |

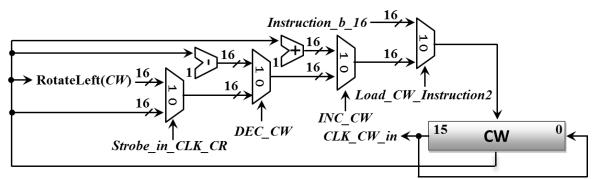

| 4.6.9    | Frequency control word register CW      | 68 |

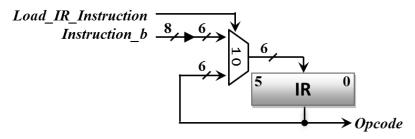

| 4.6.10   | Instruction Register IR                 | 69 |

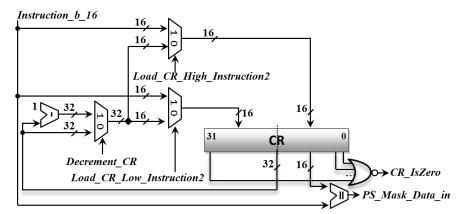

| 4.6.11   | General counter CR                      | 70 |

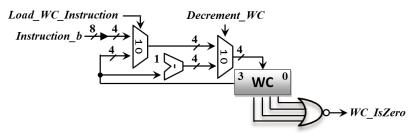

| 4.6.12   | Word counter WC                         | 70 |

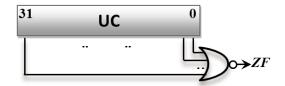

| 4.6.13   | User counter register UC                | 71 |

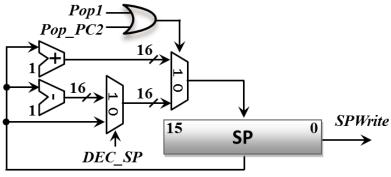

| 4.6.14   | Stack pointer SP                        | 72 |

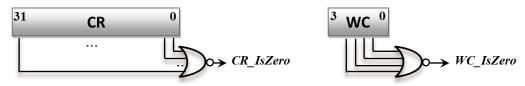

| 4.6.15   | Flags                                   | 73 |

| 4.6.16   | Memory addressing circuitry             | 74 |

| 4.6.17   | Test result memory writing circuitry    | 75 |

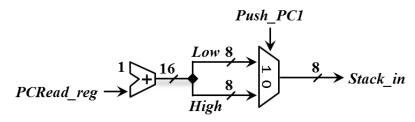

| 4.6.18   | Push circuitry                          | 76 |

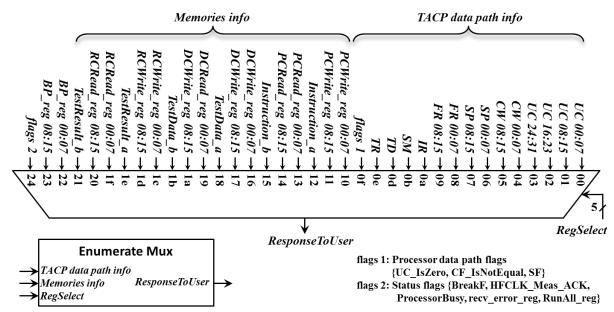

| 4.6.19   | Enumerate multiplexer                   | 76 |

| СНАРТЕ   | R 5 TEST AND CHARACTERIZATION PROCESSOR |    |

| IMPLEM   | ENTATION                                | 78 |

| 5.1 User | Interface Implementation                |    |

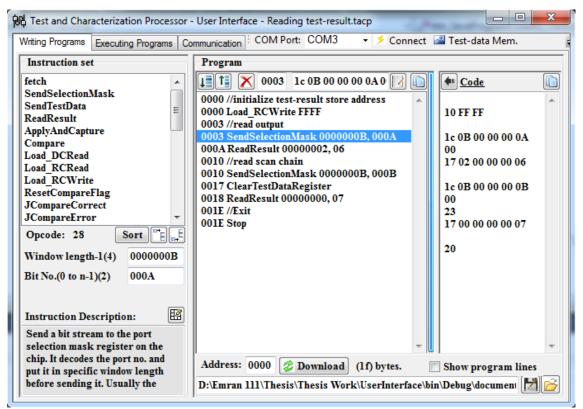

| Writin   | g Programs                              | 79 |

| Execut   | ing Programs                            |    |

|          | ry Interface                            |    |

| 5.2 The  | Instruction Builder Software            |    |

| 5.3 TS             | C Prototyping                                                            |     |

|--------------------|--------------------------------------------------------------------------|-----|

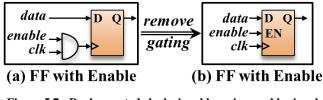

| 5.3.1              | Clock gating                                                             | 86  |

| 5.3.2              | Clock multiplexing                                                       | 87  |

| 5.3.3              | Emulating the Configurable Clock Generator (CCG)                         |     |

| 5.4 IPs            | Under Test (IUTs)                                                        |     |

| 1 <sup>st</sup> IU | T: 4-bit Combinitional Adder                                             | 92  |

| 2 <sup>nd</sup> IU | JT: 8-bit pipelined Adder                                                | 93  |

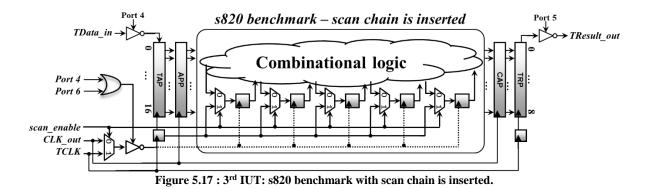

| 3 <sup>rd</sup> IU | T: s820 benchmark with scan chain is inserted                            | 93  |

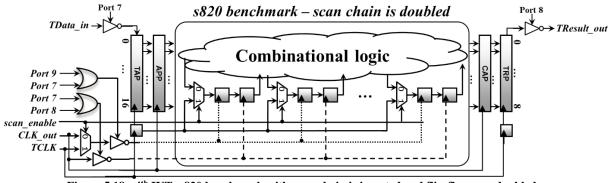

| 4 <sup>th</sup> IU | T: s820 benchmark with scan chain is inserted and flip-flops are doubled | 94  |

| CHAPT              | ER 6 TEST RESULTS                                                        | 96  |

| 6.1 Ma             | ximum Frequency Test                                                     |     |

| 6.2 Tes            | ting the 1 <sup>st</sup> IUT: the 4bit Combinational Adder               |     |

| 6.3 Tes            | ting the 2 <sup>nd</sup> IUT: the 8-bit Pipelined Adder                  | 101 |

| 6.4 Co             | mplete Testing and Characterizing Program                                | 103 |

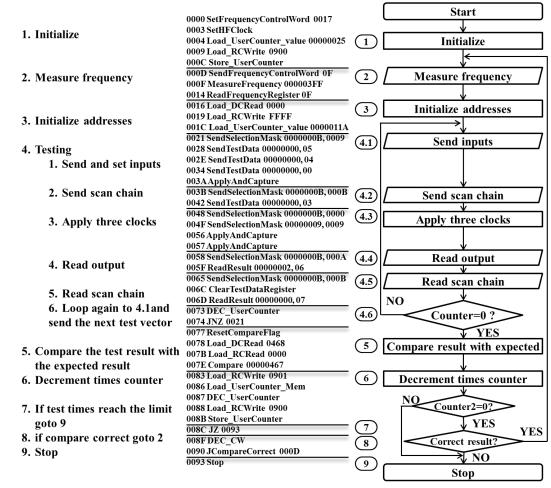

|                    | ng and characterizing the 3 <sup>rd</sup> IUT                            |     |

| Testi              | ng and characterizing the 4 <sup>rd</sup> IUT                            | 108 |

| 6.5 Tes            | ting of the Loop Back from the chip                                      | 111 |

| CONCL              | USION AND FUTURE WORK                                                    | 114 |

| CHAPT              | ER 7 APPENDIX                                                            | 115 |

| A. Ins             | truction-Set List with their microinstructions                           | 115 |

| A.1.               | fetch                                                                    |     |

| A.2.               | SendSelectionMask                                                        |     |

| A.3.               | SendTestData                                                             | 116 |

| A.4.               | ReadResult                                                               | 117 |

| A.5.               | ApplyAndCapture                                                          |     |

| A.6.               | Compare                                                                  | 118 |

| A.7.               | Load_DCRead                                                              | 119 |

| A.8.               | Load_RCRead                                                              | 119 |

| A.9.               | Load_RCWrite                                                             | 119 |

| A.10               | ResetCompareFlag                                                         | 119 |

| A.11.              | JCompareCorrect                                                          |     |

| A.12.   | JCompareError            |     |

|---------|--------------------------|-----|

| A.13.   | SetFrequencyControlWord  |     |

| A.14.   | SendFrequencyControlWord |     |

| A.15.   | MeasureFrequency         |     |

| A.16.   | ReadFrequencyRegister    |     |

| A.17.   | INC_CW                   |     |

| A.18.   | DEC_CW                   |     |

| A.19.   | SetHFClock               |     |

| A.20.   | ResetHFClock             |     |

| A.21.   | Load_UserCounter_value   |     |

| A.22.   | Load_UserCounter_Mem     |     |

| A.23.   | Store_UserCounter        |     |

| A.24.   | INC_UserCounter          |     |

| A.25.   | DEC_UserCounter          |     |

| A.26.   | JNZ                      |     |

| A.27.   | JZ                       |     |

| A.28.   | Jump                     |     |

| A.29.   | Call                     |     |

| A.30.   | Return                   |     |

| A.31.   | NOP                      |     |

| A.32.   | Stop                     |     |

| A.33.   | ClearTestDataRegister    |     |

| B. Inst | ruction Builder Tutorial | 127 |

| 1.      | Starting empty project   |     |

| 2.      | Add signals              |     |

| 3.      | Add instructions         |     |

| 4.      | Add microinstructions    |     |

| 5.      | Write data path code     |     |

| 6.      | Generate microcode       |     |

| 7.      | Export instructions      |     |

| 8.      | Generate test benches    |     |

| C. User | · Interface Tutorials    |     |

| VITA                                    |  |

|-----------------------------------------|--|

| REFERENCES                              |  |

| Importing test vectors to memory window |  |

| Test-result memory window               |  |

| Test-data memory window                 |  |

| Memory windows                          |  |

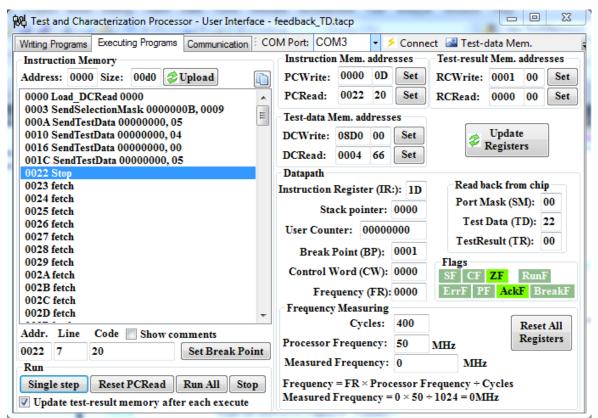

| Executing Programs tab                  |  |

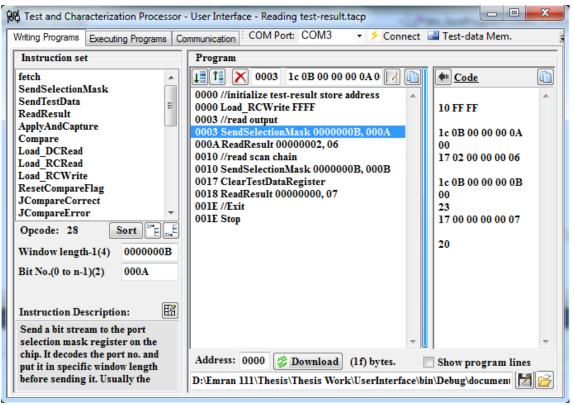

| Writing Programs tab                    |  |

## LIST OF TABLES

| Table 3.1: Communication protocol - the available user commands with their codes                      | . 27 |

|-------------------------------------------------------------------------------------------------------|------|

| Table 4.1: Instructions and their opcodes                                                             | . 32 |

| Table 4.2: Communication protocol – UART communication speed.                                         | . 40 |

| Table 4.3: Communication protocol - the available user commands with their codes                      | . 45 |

| Table 4.4: Sequencer to data path signals (micro-instructions signals)                                | . 62 |

| Table 4.5: Selecting port examples                                                                    | . 65 |

| Table 5.1: The generated clock frequencies and their control words using the DCMs in prototyped chip. |      |

## **LIST OF FIGURES**

| Figure 1.1 : Principle of testing with ATEs: apply test patterns, capture response<br>compare them with expected ones |    |

|-----------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.2 : Characterization process: test the IP under different frequencies to find o maximum.                     |    |

| Figure 2.1 : Basic BIST Architecture Block Diagram                                                                    | 8  |

| Figure 2.2 : A 4-bit linear feedback shift register (LFSR) which is used as a test p generator (TPG).                 | -  |

| Figure 3.1 : The Proposed Platform: PC, Test Processor on FPGA board, and S Circuitry On Chip.                        |    |

| Figure 3.2 : Block diagram of the TACP Support Circuitry (TSC) to be placed prototype chip.                           |    |

| Figure 3.3 : The fixed interface between TACP and TSC.                                                                | 17 |

| Figure 3.4 : The configurable clock generator                                                                         | 19 |

| Figure 3.5 : The frequency measuring Circuit (FCM).                                                                   | 20 |

| Figure 3.6 : The state diagram of the control unit of the frequency measuring circuit (                               |    |

| Figure 3.7 : The Clock Frequency Control Register                                                                     |    |

| Figure 3.8 : The Clock Selection and Application Circuit                                                              |    |

| Figure 3.9 : Logic Simulation Results for the CSaAC [1]                                                               |    |

| Figure 3.10 : The Port Selection Circuitry                                                                            |    |

| Figure 3.11 : Test application port (TAP) and test results port (TRP).                                                | 24 |

| Figure 3.12 : Scan test application/result ports                                                                      | 25 |

| Figure 3.13 : Packet type list. Each packet starts with flags defining a commar determines packet size.               |    |

| Figure 3.14 : TACP main components.                                                                                   | 28 |

| Figure 3.15 : The three memories. Each memory has four inputs and four outputs                                        | 30 |

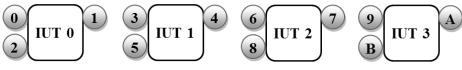

| Figure 4.1 : Four IUTs, each has three ports, each port has a serial number                                           | 33 |

| Figure 4.2 : SendSelectionMask microinstructions and flow chart.                                                      | 34 |

| Figure 4.3 : SendTestData microinstructions and flow chart.                                                           | 35 |

| Figure 4.4 : Simulation of the instruction SendTestData                                                               | 36 |

| Figure 4.5 : ReadResult microinstructions and flow chart.                                                             | 37 |

| Figure 4.6 : Compare microinstructions and flow chart                                                                                                                       | 38     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Figure 4.7 : TACP design top view and its subcomponents                                                                                                                     | 39     |

| Figure 4.8 : Communication protocol connected to UART module                                                                                                                | 40     |

| Figure 4.9 : The UART module input/output diagram                                                                                                                           | 41     |

| Figure 4.10 : Decoding the received type-byte to eighteen flags                                                                                                             | 42     |

| Figure 4.11 : Combining previous received byte with the current received byte to for 16-bit word.                                                                           |        |

| Figure 4.12 : tx_byte multiplexers                                                                                                                                          | 44     |

| Figure 4.13 : Receiving state machine FSM diagram                                                                                                                           | 46     |

| Figure 4.14 : Receiving state machine circuitry.                                                                                                                            | 47     |

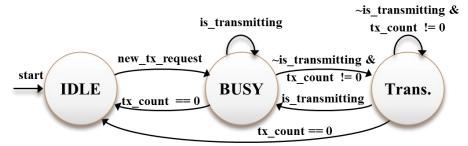

| Figure 4.15 : transmitting state machine sends test result and register values to the us                                                                                    | ser.48 |

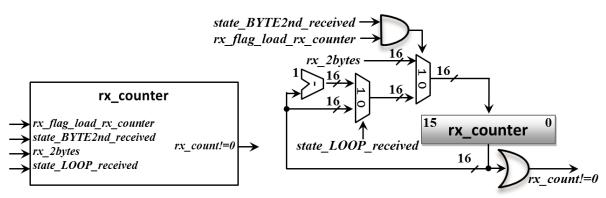

| Figure 4.16 : transmitting state machine circuitry and the transmit signal                                                                                                  | 48     |

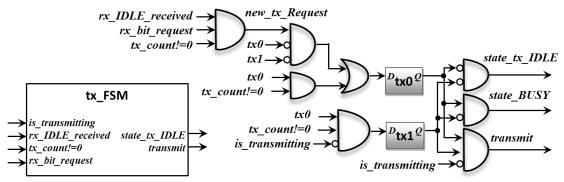

| Figure 4.17 : Break point register circuitry and BreakF flag                                                                                                                | 49     |

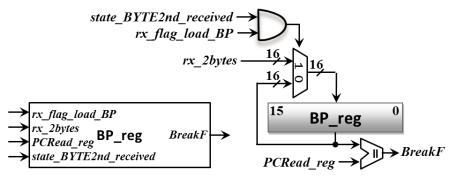

| Figure 4.18 : The receiving counter and its circuitry                                                                                                                       | 50     |

| Figure 4.19 : The transmitting counter and its circuitry.                                                                                                                   | 50     |

| Figure 4.20 : Error flag circuitry                                                                                                                                          | 51     |

| Figure 4.21: PCWrite circuitry in the communication protoocol.                                                                                                              | 52     |

| Figure 4.22 : PCRead circuitry in the communication protoocol.                                                                                                              | 53     |

| Figure 4.23 : DCWrite circuitry in the communication protoocol                                                                                                              | 53     |

| Figure 4.24 : RCRead circuitry in the communication protoocol                                                                                                               | 54     |

| Figure 4.25 : DCRead circuitry in the communication protoocol.                                                                                                              | 55     |

| Figure 4.26 : RCWrite circuitry in the communication protocol                                                                                                               | 55     |

| Figure 4.27 : Memories and address registers. Each memory has four inputs and outputs. Each memory has two address registers; one write/read register and one read register | d only |

| Figure 4.28 : Memory multiplexer circuitry manage memory access between the data and the protocol                                                                           | -      |

| Figure 4.29 : Memory multiplexer circuitry manage memory access from the TACE path and the communication protocol to the memories                                           |        |

| Figure 4.30 : Processor top diagram.                                                                                                                                        | 58     |

| Figure 4.31 : Processor components: sequencer, control store, and data path                                                                                                 | 58     |

| Figure 4.32 : The sequencer and the control store.                                                                                                                          | 61     |

| Figure 4.33 : Control store entry consists of selection, status signal, and branch address                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.34 : Combining previous and current byte to form a 16-bit word for each port on instruction memory                                                                                                                                    |

| Figure 4.35 : CR down-counter with the 16 bit port selection mask generation circuitry and the CR_IsZero flag                                                                                                                                  |

| Figure 4.36 : 8-bit selection mask register shifts in the returned-back port selection from the chip                                                                                                                                           |

| Figure 4.37 : 8-bit test data register and its circuitry                                                                                                                                                                                       |

| Figure 4.38 : 8-bit test results register and its circuitry                                                                                                                                                                                    |

| Figure 4.39 : Frequency register circuitry                                                                                                                                                                                                     |

| Figure 4.40 : 16-bit control word register and its circuitry                                                                                                                                                                                   |

| Figure 4.41 : Six bit instruction register                                                                                                                                                                                                     |

| Figure 4.42 : The 32 bit general counter CR and its circuitry                                                                                                                                                                                  |

| Figure 4.43 : 4-bit Word Counter WC and its circuitry71                                                                                                                                                                                        |

| Figure 4.44 : User-counter circuitry                                                                                                                                                                                                           |

| Figure 4.45 : Stack pointer circuitry                                                                                                                                                                                                          |

| Figure 4.46 : Zero flag circuitry for the user counter register                                                                                                                                                                                |

| Figure 4.47 : Zero flag circuitry for the user counter register                                                                                                                                                                                |

| Figure 4.48 : Zero flags circuitry of the general counters                                                                                                                                                                                     |

| Figure 4.49 : Clock selection Flag circuitry74                                                                                                                                                                                                 |

| Figure 4.50 : Compare error flag circuitry74                                                                                                                                                                                                   |

| Figure 4.51 : Addressing circuitry in the TACP data path                                                                                                                                                                                       |

| Figure 4.52 : Test-result memory data-in port and write enable circuitry75                                                                                                                                                                     |

| Figure 4.53 : Push circuitry generates Stack_in bus which is connected to the data-in port in the instruction memory                                                                                                                           |

| Figure 4.54 : 5-bit multiplexer selects one byte at a time to be send as a response to the user interface                                                                                                                                      |

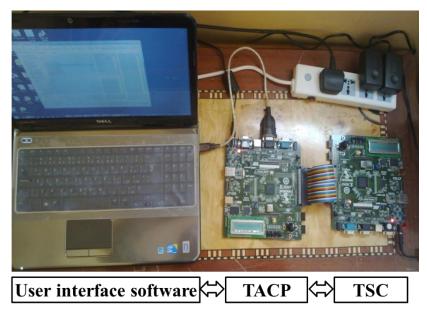

| Figure 5.1: The Implemented test & characterization platform; the host PC running the user interface tool, an FPGA board for the TACP connected to the PC, and another FPGA board containing the TSC and 4 CUTs and connected to the TACP FPGA |

| Figure 5.2 : User interface to write and download programs to the TACP FPGA                                                                                                                                                                    |

| Figure 5.3 : User interface thet executes the program and tracks register contentss on the TACP FPGA                                                                                                                                           |

| Figure 5.4 : User interface to display memory contenets                                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

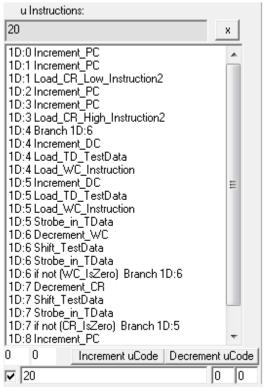

| Figure 5.5 : Eight signal types in microcode                                                                                                                                                                                                                        |

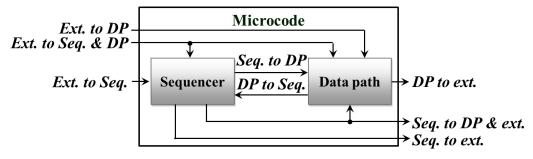

| Figure 5.6 : TACP Processor uses the microcode archeticture                                                                                                                                                                                                         |

| Figure 5.7 : Replace gated clock signal by using enable signal. gated_clock = CLK && Enable                                                                                                                                                                         |

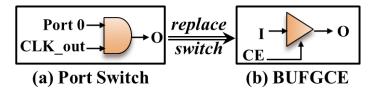

| Figure 5.8 : Replace gated clock signal by using FPGA clock tri-state buffer. gated_clock = Port <sub>0</sub> && CLK_out                                                                                                                                            |

| Figure 5.9 : BUFGCE simulation – dedicated clock signals tri-state with no pulse lose. 87                                                                                                                                                                           |

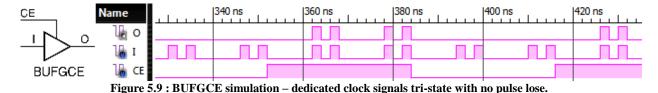

| Figure 5.10 : The BUFGMUX clock multiplexer simulation                                                                                                                                                                                                              |

| Figure 5.11 : The ASIC version of clock selection and application circuit (CSaAC). The circuitry has a clock multiplexer and a clock gating                                                                                                                         |

| Figure 5.12 : The FPGA implementation of clock selection and application circuit CSaAC with the implementation of four CUTs clock gating. All gated clocks are replaced by FPGA clock buffers BUFGMUX and BUFGCE. The critical path has four level of clock gating. |

| Figure 5.13 : Emulating the DCO using eight DCMs. The DCO is combined with the four phase divider. The frequency is chosen by the 6-bit control word register                                                                                                       |

| Figure 5.14 : Illustration of assigning the ten port selection bits to the four IUTs                                                                                                                                                                                |

| Figure 5.15 : 1 <sup>st</sup> IUT: 4-bit combinitional adder                                                                                                                                                                                                        |

| Figure 5.16 : 2 <sup>nd</sup> IUT: 8-bit piplined adder                                                                                                                                                                                                             |

| Figure 5.17 : 3 <sup>rd</sup> IUT: s820 benchmark with scan chain is inserted                                                                                                                                                                                       |

| Figure 5.18 : 4 <sup>th</sup> IUT: s820 benchmark with scan chain is inserted and flip-flops are doubled                                                                                                                                                            |

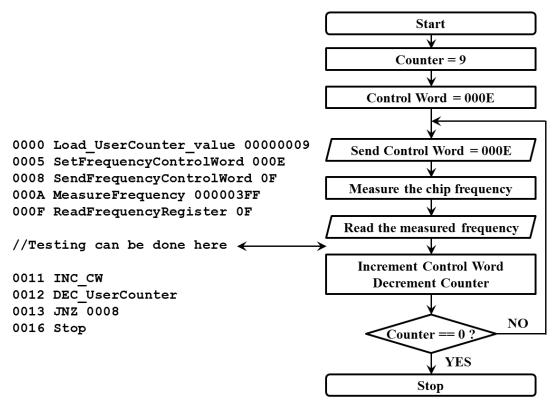

| Figure 6.1 : Code and flow chart of the test program that changes frequency within a loop                                                                                                                                                                           |

| Figure 6.2 : Execution snapshot of the test program that changes frequency within a loop.                                                                                                                                                                           |

| Figure 6.3 : Program execution window snapshot. The program tested a compinational 4-<br>bit adder                                                                                                                                                                  |

| Figure 6.4 : Memory windows snapshot after executing the test program of the compinational 4-bit adder. The three windows show the test data, the test result and the comparision                                                                                   |

| Figure 6.5 : Program execution window snapshot. The program tested a compinational 4-<br>bit adder                                                                                                                                                                  |

| Figure 6.6 : Program execution window snapshot. The program tested a compinational 4-<br>bit adder                                                                                                                                                                  |

Figure 6.7 : A complete test program and its flow chart for the S820S benchmark IUT.

Figure 6.8 : IUT3 testing: Snapshots for the user interface with four instances of the memory viewer after executing the IUT 3 test program. At this point, not all test results matches the expected. The comparison window shows some non-zero values where a difference exists. This indicates that the chip cannot handle the current frequency. ..... 107

| Figure 7.3 : | : Add & edit | instruction and | define its | parameters | sizes and | d names | 128 |

|--------------|--------------|-----------------|------------|------------|-----------|---------|-----|

- Figure 7.11 : Comparing results sorted by the third column to rise up vector caused error.

- 139

| Figure        | 7.12 : Import | test-vector dialog wind | dow and test-vectors file snapshot |  |

|---------------|---------------|-------------------------|------------------------------------|--|

| $\mathcal{O}$ | 1             | $\mathcal{O}$           | 1                                  |  |

## LIST OF ABBREVIATIONS

| ASIC        | : Application Specific Integrated Circuit.          |

|-------------|-----------------------------------------------------|

| ASIP        | : Application Specific Instruction-set Processor.   |

| ATE         | : Automatic Test Equipment                          |

| ATPG        | : Automatic Test Pattern Generator                  |

| BIST        | : Built-In Self-Test                                |

| BRAM        | : Block RAM                                         |

| CAD         | : Computer Aided Design                             |

| CCG         | : Configurable Clock Generator.                     |

| CPI         | : Cycle Per Instruction or Clocks Per Instructions. |

| CPU         | : Central Processing Unit                           |

| CSaAC       | : Clock Selection and Application Circuitry.        |

| DP          | : Data Path.                                        |

| DCM         | : Digital Clock Manager                             |

| DUT         | : Device Under Test                                 |

| EDA         | : Electronic Design Automation                      |

| FPGA        | : Field Programmable Gate Array                     |

| FMC         | : Frequency Measurement Circuitry.                  |

| FSM         | : Finite State Machine                              |

| GUI         | : Graphical User Interface                          |

| HW          | : Hardware                                          |

| IC          | : Integrated Circuit                                |

| I/O         | : Input/Output                                      |

| IP          | : Intellectual Property                             |

| IUT         | : IP Under Test                                     |

| LUT         | : Look Up Table                                     |

| µ-Address   | : Micro-Address                                     |

| µ-Operation | : Micro-Operation                                   |

| opcode      | : Operation Code                                    |

|             |                                                     |

- RAM : Random Access Memory

- ROM : Read-Only Memory

- SoC : System on Chip

- SW : Software

- TACP : Test And Characterization Processor

- TSC : Test Support Circuitry

- UCU : User Communication Unit.

- USB : Universal Serial Bus

### ABSTRACT

Full Name: AMRAN ABDULRAHMAN ABDULWALI AL-AGHBARIThesis Title: A Special Purpose Processor for IC Testing and Speed CharacterizationMajor Field: Computer Engineering

Date of Degree : December, 2012

Conventionally, IC testing and speed characterization is carried out using very expensive Automatic Test Equipments (ATEs). Built-in-self-test (BIST) techniques can also be used as a low-cost solution for at-speed testing. However, BIST may require some modification of the circuit under test (CUT) to coup with the pseudo random nature of the test vectors (what is known as test points insertion). Also, speed characterization can't be directly carried out by BIST. Other low-cost testing and speed characterization methods are needed especially for developers of circuit IPs in small companies and universities. In this thesis, a special purpose test and characterization processor (TACP) for IC testing and speed characterization has been developed, implemented and tested. The processor utilizes specially developed test support circuitry (TSC) which is fabricated on the chip containing the IPs under test. The TSC, in coordination with the off-chip stand-alone TACP processor, receives test data serially, re-format them, apply them to IPs under test, reformat the test results and send it serially to the test processor. The TSC also include a configurable clock generator which is controlled by the TACP. By controlling the testing frequency and test patterns application, the IPs can be characterized to find their maximum frequency of operation. A proof-of-concept implementation was realized using two FPGA boards; one for the processor and the other to emulate the chip that contains IPs and on-chip circuitry. Also, a complete user interface tool has been developed allowing the user to write, load and administer his/her test program, download test data and receive the test results through a standard PC.

### ملخص الرسالة

الاسم الكامل : عمران عبد الرحمن عبد الولي الأغبري عنوان الرسالة : تصميم معالج خاص باختبار الدوائر المتكاملة و توصيف سرعتها التخصص : هندسة حاسوب

تاريخ الدرجة العلمية : ديسمبر 2012م

يتم اختبار و توصيف سرعة الدوائر الإلكترونية الرقمية IC بطرق تقليدية تعتمد على استخدام أجهزة اختبار أوتوماتيكية مكلفة جداً (ATEs) Automatic Test Equipments. يمكن أيضا استخدام دوائر الفحص التلقائي (BIST) كحلول قليلة التكلفة لتقوم باختبارات السرعة العالية. لكن استخدامها يتطلب تعديلات في الدائرة المراد اختبارها لتتلائم مع طريقة التوليد العشوائي لسلاسل الاختبار (و تعرف أيضا بإضافة نقاط أختبار). كما أنها غير مصممة لاستخدامها مباشرة من أجل توصيف السرعة. هناك حاجة لطرق أخرى أقل كلفة لاختبار و توصيف سرعة الدوائر، خاصة لمبتكري الدوائر الرقمية المبتكرة Circuit IPs في الشركات الصغيرة و الجامعات. في هذه الرسالة، تم تصميم و تطبيق و اختبار معالج خاص باختبار و توصيف الدوائر الإلكترونية A Special Purpose Test and Characterization Processor (TACP). المعالج يستخدم دائرة إلكترونية أخرى مساندة صممت خصيصا لتسهيل عمله، بحيث يتم دمجها و تصنيعها في رقاقة إلكترونية مع الدوائر الرقمية المطلوب إختبارها و توصيف سرعتها. الدائرة المساندة – بالتنسيق مع المعالج المستقل (الغير مصنوع معها في نفس الرقاقة الإلكترونية)- تستلم بيانات الإختبار و تعيد ترتيبها ثم تطبقها على الدائرة المطلوب إختبارهاز و بعد ذلك تقوم بترتيب النتائج ثم ترسلها للمعالج بالطريقة التسلسلية Serially. الدائرة المساندة فيها أيضا ترددات قابل للضبط (Configurable Clock Generator (CCG يتحكم به المعالج. فعندما يقوم المعالح بتطبيق بيانات الإختبار مع التحكم بالتردد يمكن توصيف الدائرة و إيجاد أعلى سرعة يمكن أن تعمل عليه. تم إثبات هذا المفهوم بتطبيقه عمليا باستخدام الدوائر الرقمية القابلة للبرمجة Field Programmable Gate Array (FPGA)، حيث تم تصميم المعالج على واحدة منها و تم عمل محاكاة للدائرة المساندة مع بعض الدوائر للإختبار في واحدة أخرى. كما تم تصميم برنامج حاسوبي متكامل يسمح للمستخدم بكتابة برنامج إختبار و إدخال بيانات الإختبار و قراءة النتائج عبر الحاسوب.

## **CHAPTER 1**

## **INTRODUCTION**

Developers of circuit intellectual properties (IPs) in universities and small companies need to silicon-prove their IPs. Unfortunately, automatic test equipments (ATEs) that can handle Giga-Hertz testing are very expensive making them beyond the reach of many universities and IP developers in small companies. ATEs are best suited for testing thousands of chips of the same design, however, they are not practical for developers who prototype and verify only several number of different circuit IPs.

In this thesis, a special purpose processor that can test and characterize prototypes of circuit IPs has been developed. These IPs are fabricated along with a special test support circuitry (TSC) on the same chip. The processor is a part of the low-cost testing and characterizing platform introduced in [1]. The processor is designed and implemented on an FPGA board. To verify the processor's operation, the rest of the platform has also been implemented. The support circuitry with some IPs are emulated on another FPGA board. A graphical user interface tool was implemented to write programs and control executing them on the processor. Many successful programs were successfully run.

#### 1.1 Circuit IPs

Circuit intellectual property is a reusable unit of logic, cell, or chip layout design. It is also called IP for simplicity. It is used as building blocks within larger designs. IPs are licensed either as soft IPs which are a synthesizable hardware-description language modules or as hard IPs which are layout macros [2].

IP-based design promise large productivity gains. Many IPs are used and integrated with other circuitries to work together as a single system. IP-based design has a very short time-to-market development cycle because it reuses existing IPs to build larger designs. IPs have rapidly become the cornerstone of the SoC industry [3, 4, 5]. In SoC, pre-designed and pre-verified hardware and software blocks can be combined on chips for many different applications.

Many researchers in universities and small companies are developing new IPs but they face a huge problem when they try to market them. Unfortunately, IPs cannot be marketed unless siliconproven with specific performance numbers (Maximum frequency of operation, maximum throughput, maximum latency, average power, etc.). Moreover, fabricating an IP prototype is relatively cheap, testing and characterizing it on the other hand could be very costly. Developing a cost-effective solution would enable circuit designers to prototype, test and characterize their IPs at the operational speeds.

#### **1.2 IC Testing**

Testing is a manufacturing step that ensures that each of the fabricated physical devices (integrated circuits or ICs), has no manufacturing defect(s). Testing also characterizes the fabricated ICs by determining their maximum operating frequency (called speed or frequency binning).

Verification, on the other hand, is a predictable testing that comes before fabrication in all phases of the IC design flow used to prove the correctness of the design. Functional simulation and timing simulation are examples of verification methods.

#### **Design for Testability (DFT)**

To facilitate the test process, modification on the synthesized design is suggested to get a testable design. Design for testability (DFT) methods were developed and became a standard phase after the synthesis phase in the IC design flow. In this phase, all storage elements inside the IC are replaced with scan cells which are connected and forms multiple shift registers (i.e. scan chains). Thus, the IC can be set directly into a specific state by shifting in stimulus to all storage elements. Additional test points may be inserted to improve the observeability and controllability of the design in case a pseudo random pattern generator is used to generate the test vectors (as the case with BIST).

#### **Testing Principle**

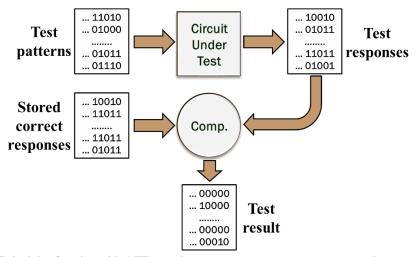

Figure 1.1 illustrates the basic principle of digital testing with ATEs. Test patterns are applied to the IC, and then test responses are captured and compared with stored expected responses. The circuit is considered good if the responses match. The quality of the tested circuit will depend upon the thoroughness of the test vectors that are usually generated using Automatic Test Pattern Generation (ATPG) techniques. The test vector itself usually has two parts; the first is applied to the IC inputs, and the other part is shifted into the scan chain of the IC under test to change its storage elements values and therefore force the IC to a specific state.

Figure 1.1 : Principle of testing with ATEs: apply test patterns, capture responses and compare them with expected ones..

#### **Characterization Process**

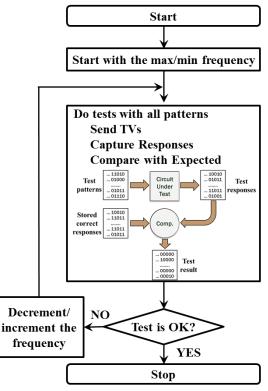

Characterization is to determine the exact limits of device operating values: What is the maximum frequency the design can operate on with no errors? How much power does it consume? In this thesis, the main concern is speed characterization. To do that, the IC clock frequency is set initially at minimum value, and then at-speed testing of the IC is administered by applying stimuli and comparing the test results with expected ones. If the test result is OK, the frequency is increased and the test is done again and again. The test continues until reaching the maximum frequency or getting a difference between the test result and the expected results. Figure 1.2 illustrates this process.

In at-speed testing, part of the stimulus is shifted into the scan chain while the rest is used as primary inputs. Thus, the stimulus length is equal to the scan chain length plus the number of primary inputs while the result vector length is equal to the scan chain length plus the number of primary outputs. Testing is done by applying two clock cycles at a specific frequency. The first clock pulse results in new stimulus which is applied with the next clock pulse. This way a transition delay fault can be discovered which indicates that the frequency has to be decremented.

Figure 1.2 : Characterization process: test the IP under different frequencies to find out the maximum.

#### **1.3 Thesis Organization**

The next chapter contains a literature survey on test and characterization methods and multicycle processors. The platform overview is explained in chapter three. Chapter four contains the complete design of the TACP and its components in details. The implementation of the platform is presented in chapter four with a discussion about the ASIC emulation problems. Experimental results are presented and discussed in chapter six followed by conclusions and references. Several appendices that summarize the TACP instruction set and provide user tutorials on the different software tools developed are provided at the end.

## **CHAPTER 2**

## LITERATURE REVIEW

This chapter includes literature survey about IC test processors and other testing and characterizing methods. The survey shows the contribution of the testing platform on the IC testing and characterizing field. The last section in the chapter introduces the multi-cycle processor architecture that are needed to build the testing processor.

#### 2.1 Digital circuit prototyping

Developers of circuit IPs need to prove the functional correctness of their IPs and to characterize their performance (speed and power). There are two main methods for verifying new circuit IPs functionality and performance; simulation-based verification with very detailed process and device models in what is called virtual prototyping, and through physical prototyping by either using FPGA implementation or via fabrication with a silicon foundry.

#### **Virtual Prototyping**

One way to prove the correctness of an IP is virtual prototyping. Virtual prototyping tools attempt to capture the effects of all physical parameters (process and otherwise) through modeling. Virtual prototypes are used to faithfully represent the "product-to-be", so as to be able to simulate

its features, performances, functionality and usage before the real product is actually built [6]. Virtual prototyping is just simulation-based verification software that is more accurate than traditional simulations. The existing virtual prototype software costs high and is not practical for testing circuit IPs. Furthermore, it is still a simulation that cannot be compared with a silicon-proven chip.

#### **Physical Prototyping**

Chip fabrication is the most trusted and accepted method of verification, since it reveals the actual performance of the circuit being prototyped. Fabricated chips would achieve the highest performance but they would require very expensive automatic testing equipments (ATEs) to test and characterize their performance at their operational speeds (called at-speed testing).

Automatic test equipments (ATEs) are standalone devices that can be used to test digital designs. They have many advantages such as digital and analog test capability, high-current pin protections and high-speed test execution. They also has disadvantages such as they are very expensive and require an accurate setup. Agilent, Advantest and Teradyne are example of companies that provide these machines. The ATEs mainly detects failures due to manufacturing defects, aging, environment effects and others [7] and helps manufacturers to maintain their manufacturing tools. They are not practical for prototyping IPs of universities researchers and small companies because of their high cost.

#### **BIST-based test processors**

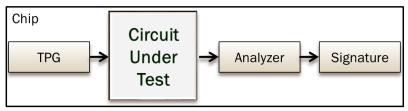

Built-in self-test (BIST) is the primary test methodology which reduces dependency on external Automatic Test Equipment (ATE). It is a circuitry that is designed and integrated on the chip with

the circuit under test (CUT). It has many components as shown in the simple block diagram in Figure 2.1. The test pattern generator (TPG) generates test patterns to be applied to the circuit under test (CUT). The analyzer retrieves the responses, updates responses signature and compares the signature with a good CUT signature to detect fault.

Figure 2.1 : Basic BIST Architecture Block Diagram.

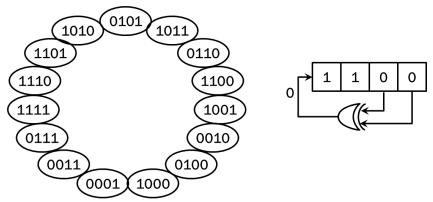

Test pattern generators (TPG) is the main component that affect the test process. It could be deterministic or pseudorandom (i.e. requires a seed to start the pattern random generation). In the deterministic way a ROM could be used to store good test vectors that covers most faults. These good vector usually are generated using automatic test pattern generator (ATPG). However, this is too expensive in the chip area. Another way is to use a counter on the circuit input to generate all permutations. This is not practical if inputs number is large [8]. For pseudorandom TPGs, Linear feedback shift register (LFSR) is a well-known example of TPGs that needs a small hardware. Figure 2.2 show a 4-bit LFSR and the sequences that it can generate. It randomly generates all 4bit permutations (except the sequence that has all zeros). Another successful TPG idea is to use LFSR with a small ROM that stores some test patterns that are not covered by LFSR. This called the mixed-mode testing in which the pseudo-random testing is followed by a deterministic testing approach. General-LFSR is presented and well explained in [9] to be used instead of LFSR. GLFSR is the general form of LFSR, MISR. It can generate higher randomness test vectors so the fault can be discovered with fewer patterns. Using GLFSR for a mixed-mode testing approach is presented in [10] to investigate its performance. It starts by pseudo-random test while a controller counts the generated test vectors. When the counter reaches a predefined number, it starts the deterministic test.

Figure 2.2 : A 4-bit linear feedback shift register (LFSR) which is used as a test pattern generator (TPG).

A BIST-Based test processor is presented in [11] that contains linear feedback shift register (LFSR), signature analyzer and RAMs. The LFSR is programmable and can set user seed for every test set. The processor uses LFSR to generate random numbers and apply them to the circuit under test (CUT). Then, it compress the responses to generate the signature and store them in its RAM to be sent later to computer to compare them with a signature of a good CUT. Other RAMs is used to store the seeds, test length and the polynomial.

It is not practical to test the circuit using all 2n combinations. Many researches are done on selecting the best seeds that can cover most faults. Test length affects the testing time. High fault coverage cannot be achieved within an acceptable test length. Reseeding is a technique which has been proposed to solve this problem. A heuristic approach is presented in [12] that come of a small leads to very small number of seeds, short test sequences and almost complete fault coverage. Based on that approach, [13] proposes and simulate an external test processor architecture.

In general, BIST test quality depends on signature analysis that can detect more than 99% of faults. This coverage percentage decreases with the increasing of the complexity of the design.

BIST-based test processors achieve fault coverage for memory cores better than complex design such as microprocessors and IP cores. BIST also adds an overhead area for each CUT since it is included in the chip that contains the CUT. Some researchers proposed efficient utilization of area by using one BIST to test multiple components in SoC [14]. They used a microcode-based controller to control one BIST to test multiple RAM cores for SoC system.

In summary, BIST is a good random test method that require a reasonable area. It can reach to 100% fault coverage for some designs and more than 90% in average but also requires modification of the CUT in order to achieve the high fault coverage.

#### Software-based testing

Software-based self-testing strategy is a proposed for complex designs that cannot be tested perfectly using BIST techniques such as system-on-chip (SoC). System-on-chip consists of many heterogeneous embedded modules such as RAMs, processors, IPs, etc. There is a need for special test processor designed on the chip to test all its components for these reasons; some of these components could be black boxes and not designed for testability. In addition, the controllability and observability become more limited with the increase of the complexity of the design. Also, most of SoC components are not connected to the ASIC pins and cannot be tested by external testers.

Trying to utilize BIST-based testing for SoC, researchers in [15] suggest using BIST-based testing strategy for testing processor IPs by generating random instructions. This way, they achieve a good fault coverage with a minimum area and without the need for scan chain insertion into the processor under test.

Researchers in [16] remark the fact that most SoC has at least one processor core. They suggest utilizing existing processors and use a subset of their instruction set for testing purposes. They also suggest mutual self-test of processors that can do hardware- and software-based test strategy in which the following possibilities are considered; one processor is made active and tests the other passive processor at the logic block level via scan-chains(hardware-based testing). Then both processors are made active one of them test the other using valid op-code, valid data and functional inputs (software-based testing). Also the processor can provide active March test for a memory block. In addition, one of the test processors can work as a watchdog that monitor the chip correctness at normal operation.

In most cases, the test processor in SoC generates the test vectors. Some researchers suggest connecting the SoC to large external RAM that holds the test program, data and expected responses [17]. This way the RAM could be considered as an external ATE but the test process is controlled by the chip.

The test processor in [18] is a 16-bit RISC processor and supported by a scan controller that is connected to all components scan chains in the chip. It can support bus tests, functional tests, scan testing and act as a watchdog in normal operation.

#### Low-cost FPGA-Based testers

FPGA is also used in many testing platforms to present a standalone low-cost tester. An FPGA holds the tester, software to control the tester and the chip under test which is usually put on a daughter board that is connected to the FPGA board. This platform is good for functional testing. It can also do at-speed testing but at low speeds (not more than few hundred MHz) [19, 20, 21, 22, 23]. FPGAs are also used as a verification method to prototype ASIC designs [21].

An FPGA-based functional tester to test SoC is presented in [22]. An automatic software tool in a host PC prepares a compressed test set and a decompression logic. Then, the compressed test set is downloaded into SRAM on the FPGA-board and the decompression logic is downloaded into the FPGA. The FPGA reads, decompresses the test set from the RAM, sends them to the DUT and captures the responses.

SRAM testing platform is presented in [20]. It is consist of FPGA board (i.e. Xilinx Virtex 4) connected to slave board accommodates SRAM under test. The FPGA executes a special March-C testing algorithm using a Microblaze<sup>TM</sup> micro-processor that could detect specific SRAM faults.

FPGA-based test platform is presented in [19]. It is consist of FPGA board (Xilinx Spartan 3) connected to slave board that accommodates the DUT. The platform uses three SRAMs to store timing data, test patterns and responses. There are a PC software to read timing data and test files and send them to SRAMs. A state machine on the FPGA manages all operations.

In the work presented in [23], a new multiplier architecture is designed, implemented, fabricated and then used as a DUT for the presented FPGA-based testing platform.

An on-chip and at-speed tester for memories is presented in [24]. The presented patent platform can do at-speed testing and characterizing of multiple memories. It consists of two parts; the centralized flow controller and the localized signal generator. The centralized flow controller consists of memory, processor and a user interface. The localized signal generator is to be included with the memory under test in an integrated circuit. It has also a clock generator, characterization circuit and a phase lock loop (PLL). The memory stores some memory test algorithms and the test program that use these algorithms. The testing starts by receiving an execute signal indicating the memory type and the storing test operations. That platform is excellent since it can do testing and characterizing. However, it is dedicated for memories only and cannot be generalized because it depends on specific stored testing algorithms.

#### 2.2 Multi-cycle processors

Processor architecture can be single-cycle in which each instruction is executed in one cycle (i.e. Clock Per Instruction (CPI) = 1) or multi-cycle in which the instruction is executed in multiple cycles (i.e. CPI > 1). Multi-cycle architecture is suitable for our work because it can deal with variable data size. Instructions of variable data size are needed to send test data, receive test results and compare results.

Microcode is a simple well-known processor architecture that allows multi-cycle instructions. It has the ability to add and remove instructions with relatively less effort. It consists of three parts; data path, sequencer and control store. The sequencer is the control unit that fetches low-level microinstructions from a control store and derives the appropriate control signals as well as micro-program sequencing information from each microinstruction. The data path is controlled by these control signals. Control store is a ROM and stores microinstructions of all instructions. Each entry reflects all the signal values at specific clock. In the data path all operations and data manipulations are performed. It may contain registers, shifters, ALUs, or any combinational and sequential circuits. Data path is controlled by control signals coming from the selected entry of the control store. A good view of microcode history is presented in [25]. It discusses the evolution of microcode from its introduction to its decline and to its likely resurgence in custom computing machines and reconfigurable computing.

### **CHAPTER 3**

# OVERVIEW OF THE PROPOSED TEST AND CHARACTERIZATION PLATFORM

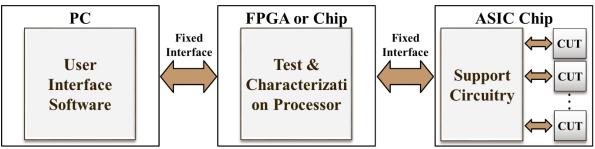

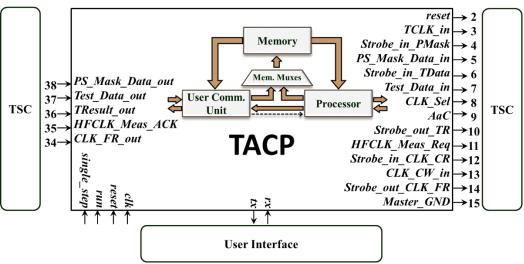

This chapter gives an overview of the targeted test and characterization platform [1] and describes its components in details. Figure 3.1 shows the general architecture of the test and characterization platform. Unlike many previous techniques which either use a test circuit that is entirely on-chip with the device under test or entirely off the DUT's chip, the new method uses a hybrid approach. Also, unlike the approach in [20] where voltage and clock controllers are integrated on the DUT's chip while the test controller could be off-chip, this method provides a general way for applying stimuli and capturing results with fixed interfaces (i.e. the same test controller can be used to test and characterize any circuit). Also, unlike the approach in [20] no BIST circuitry is required. The test controller (TACP) can be implemented on an ASIC or a Field-Programmable Gate Array (FPGA). The TACP could be interfaced to a PC for receiving test instructions and data and sending the test results. The TACP's on-chip support circuitry provides the fixed interface (Figure 3.3) to the TACP and the controlled clock source for the IUTs. All interfaces use serial data communications to save I/O pins [1].

Figure 3.1 : The Proposed Platform: PC, Test Processor on FPGA board, and Support Circuitry On Chip.

#### **3.1** The TACP Support circuitry (TSC)

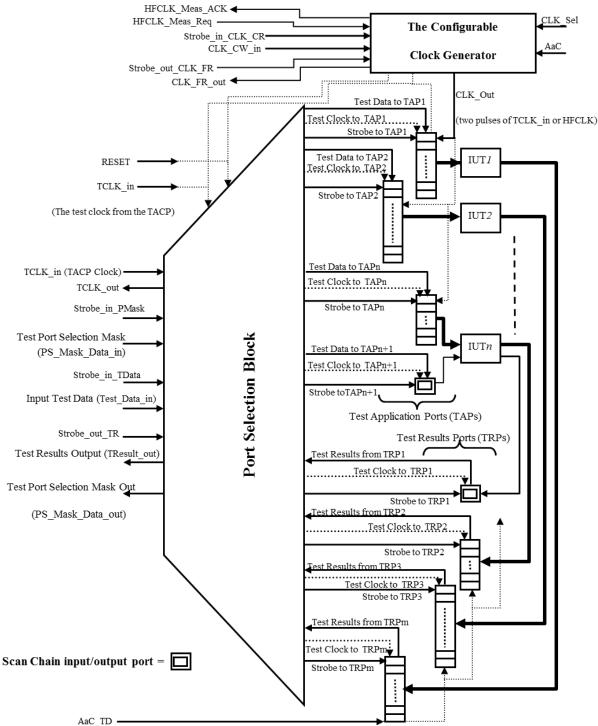

The TACP support circuitry (TSC), shown in Figure 3.2, performs the following functions:

- **Port Selection**: The proposed method supports testing and characterization of unlimited number of IPs on the prototype chip. Each IP could also have several input/output ports for different purposes (functional I/Os and scan I/Os). The TSC provides a mean to select a specific port to apply/receive test data to/from.

- Serial-to-Parallel and Parallel-to-Serial data conversion (SERDES): To have fixed logic interfaces between the TACP and the prototype chip all data communications are serial. As such, the TSC converts the received serial test data to parallel data to be applied to the IUT. It also converts back the captured test results from parallel form to serial form.

- **Controlled Clock Source:** All data transfer between the TACP and the prototype chip and functional characterization is carried out using the TACP relatively low frequency clock to ease the design of the interface. For speed characterization, a high speed digitally controlled oscillator is provided as part of the TSC. The user can increase/decrease this oscillator frequency and use it for at speed testing of his/her IP(s).

Figure 3.2 shows a block diagram of the TSC. The main components are the configurable clock generator, the port selection block, test application ports (TAPs), and test result ports (TRPs).

(Apply & Capture Test Data

Figure 3.2 : Block diagram of the TACP Support Circuitry (TSC) to be placed on the prototype chip.

## **TSC Fixed interface**

Figure 3.3 shows the interface between the TACP and the prototype chip. This interface is fixed and will not change with any chip being tested or characterized. Whatever the number of IPs to be tested and whatever the number of inputs each IP has, the interface is fixed and does not change. The interface has twenty pins as depicted in Figure 3.3. Data is moved serially. The transition of the test data happens while the strobe signal is high which works as a shift signal for the serial data.

- **TCLK\_in**: The processor clock operates the TSC to synchronize it with the processor.

- **TCLK\_out**: The same processor clock loops back for de-skewing purpose.

- Strobe\_in\_PMask: Strobe signal for scanning in the port selection bits.

- **PS\_Mask\_Data\_in**: Port selection input stream.

- **PS\_Mask\_Data\_out**: Port selection output stream used for loop back testing purposes.

- Strobe\_in\_TData: Strobe signal for scanning in test data.

- **Test\_Data\_in**: Test data input stream.

- Test\_Data\_out: Test data output stream used for loop back testing purposes.

- **CLK\_Sel**: Selects the clock source for testing; either the TACP TCLK or the on-chip HFCLK.

- **AaC\_TD**: Apply-and-capture signal that prompt the TSC to apply two cycles of the selected clock to the selected IUT and capture the result.

- Strobe\_out\_TR: Strobe to read out test result.

- **TResult\_out**: Test result output stream.

- **HFCLK\_Meas\_Req**: A request to measure the selected frequency on the chip.

- **HFCLK\_Meas\_ACK**: An acknowledgement indicates finishing the frequency measurement process.

- **Strobe\_in\_CLK\_CR**: Strobe to input the control word of the on-chip clock generator.

- CLK\_CW\_in: Control word input stream.

- Strobe\_out\_CLK\_FR: Strobe to read out the measured frequency register.

- CLK\_FR\_out: Measured frequency register output stream.

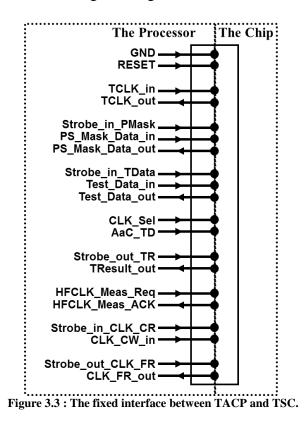

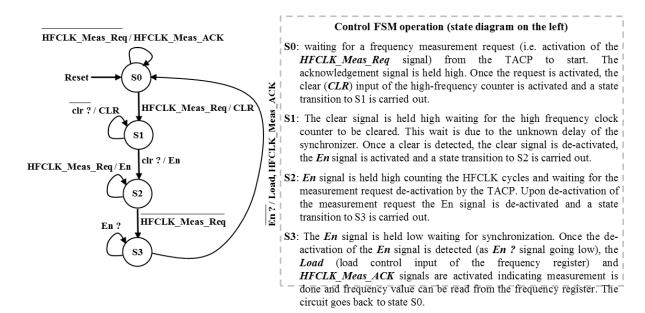

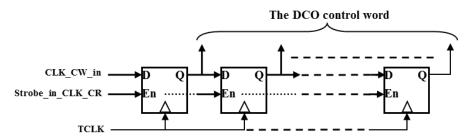

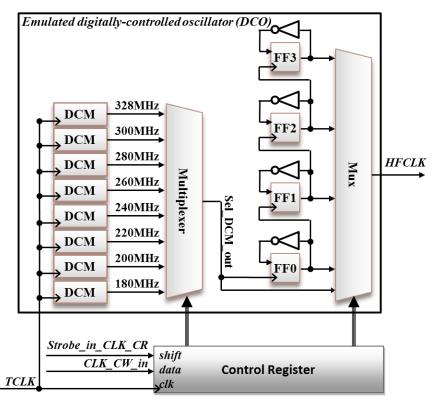

#### **3.1.1** The Configurable Clock Generator

As mentioned before, the regular test clock is coming from the TACP which is off-chip. This clock is kept at a moderate frequency (50~100 MHz). Hence no special high-frequency transceivers or signal traces are required. This eases the design of the interface and keeps its cost to a minimum. At the same time this clock is adequate for scanning in/out the test data/results and performing functional characterization of the IUTs. Frequency characterization, however, requires a clock source that can be configured to produce a high-frequency clock. This configurable source is placed on the prototype chip and dubbed the Configurable Clock Generator. This generator, as illustrated in Figure 3.4, is made up of a frequency measuring circuit (FMC), Figure 3.5 and Figure 3.6, a clock frequency control register, Figure 3.7, and a clock selection and application circuit, Figure 3.8.

Figure 3.4 : The configurable clock generator.

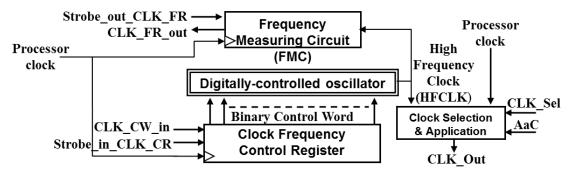

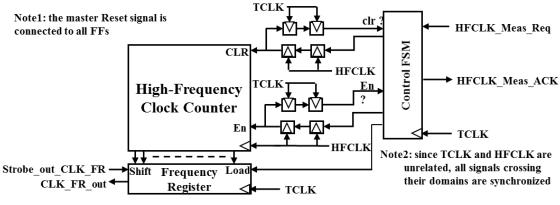

# 3.1.2 The Frequency Measuring Circuit (FMC)

The FMC, simply counts the number of high-frequency clock cycles within a certain period and puts the result in a shift register that would be shifted out by the TACP using the Strobe\_out\_CLK\_FR strobe signal and through the CLK\_FR\_out pin. The measurement period is specified by the TACP as the difference between activating the measurement request (HFCLK\_Meas\_Req) and deactivating the request. When the FMC is done it activates the acknowledgement signal (HFCLK\_Meas\_ACK) which remains high till a new measurement request is received. The detailed design of the FCM including its controller's state diagram and its operation is shown in Figure 3.5 and Figure 3.6. The user can control the accuracy of the measurement by having a longer measurement period. To get the frequency the following formula is used:

$$Measured Frequency = \frac{FR \times TACP \text{ processor frequency}}{Request \text{ period length (Cycles)}}$$

Figure 3.5 : The frequency measuring Circuit (FCM).

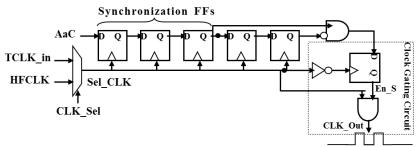

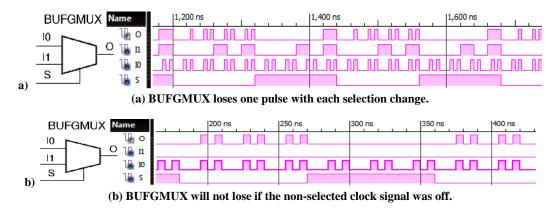

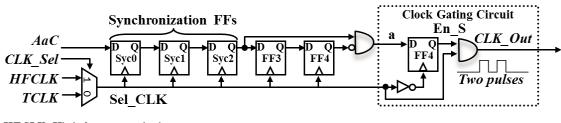

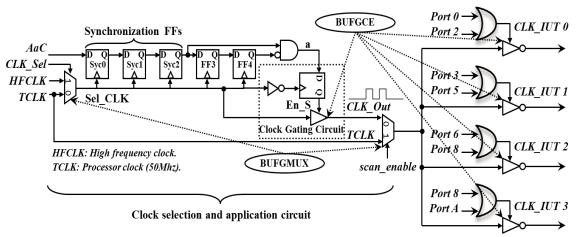

#### **3.1.3** The Clock Selection and Application Circuit (CSaAC)

The clock selection and application circuit (CSaAC), Figure 3.7, is responsible for selecting the required test clock (based on the CLK Sel input signal from the TACP) and applying exactly two pulses of that clock to the selected TAP/TRP ports (in response to a strobe on the AaC input). The TACP triggers the CSaAC by setting the AaC signal to high for at least two cycles of the selected clock (Sel CLK). The CSaAC will produce exactly two pluses of the selected clock for each AaC pulse, but in order for this circuit to fire again, the AaC signal must be reset for at least two cycles of the selected clock. The clock gating circuit ensures that the two pulses applied are complete with no glitches by enabling the output clock when the selected clock is low. The only constraint for this circuit is that the sum of the clock inverter delay, the FF's clock to Q delay and the clockgating AND gate delay is less than the width of the negative pulse of the selected clock. Also, due to the required synchronization of the AaC input with the selected clock (3 FF synchronizer is used), the output clock pulses will have a latency of 3 cycles of the selected clock. The TACP takes care of all these issues by applying the AaC signal for two TCLK\_in cycles (TCLK\_in frequency is always  $\leq$  than the selected clock frequency) and then resetting it for two more cycles before setting it again (in case of successive apply and capture commands).

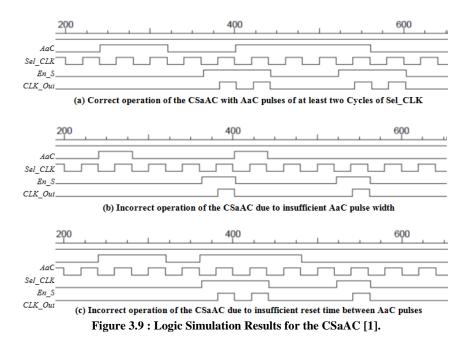

Figure 3.9 shows logic simulation results of the CSaAC with unit gate delays. Figure 3.9 (a) shows how the circuit functions correctly when the AaC pulse is at least two cycles of Sel\_CLK and the so is the reset time in between AaC pulses. When the AaC pulse is less than two cycles or the reset time in between pulses is less than two cycles, the circuit fails, as shown in Figure 3.9 (b) and Figure 3.9 (c), respectively.

Figure 3.6 : The state diagram of the control unit of the frequency measuring circuit (FMC).

Figure 3.7 : The Clock Frequency Control Register.

Figure 3.8 : The Clock Selection and Application Circuit.

# 3.1.4 The Port Selection Block

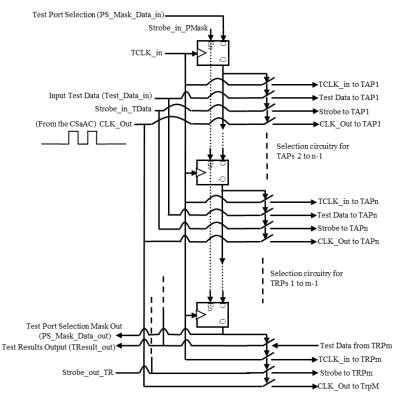

This block is responsible for selecting a specific test application/test result port to deliver the strobes, test clock and input test data to or receive test results from. The user can select a single input/output port or two ports (one input and one output). To make this block general yet with a fixed interface to the TACP, it is made up by cascading a basic cell as shown in Figure 3.10. The selection mask is loaded serially through the PS\_Mask\_Data\_in input using the Strobe\_in\_PMask strobe signal. The TACP supports variable length selection mask (up to 216 bits). The port selection mask is also read out through PS\_Mask\_Data\_out for testing the selection chain.

Figure 3.10 : The Port Selection Circuitry.

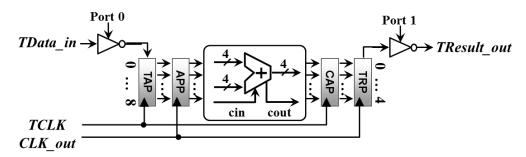

#### **3.1.5** The Test Application/Result Ports (TAP/TRP)

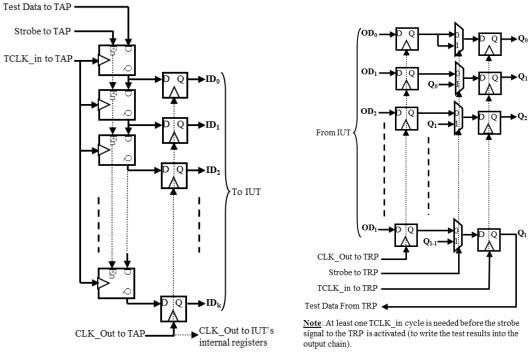

There are two types of test application/result ports as was illustrated in Figure 3.2. The first type, shown in Figure 3.11 (a) and Figure 3.11 (b), are used for applying and capturing primary inputs/outputs of an IUT. These are similar to boundary scan ports and are made of shift registers for scanning in/out the test data/results and parallel-load registers for applying/capturing the test data/results. As Figure 3.11 shows, each TAP (or TRP) is made of a cascaded number of identical cells equal to the port's data width. The shift registers use the TCLK\_in and the application/capture registers use the selected apply and capture clock (CLK\_Out). The CLK\_Out clock is also used for the IUT's internal registers. For the TRP, the TACP needs to apply at least one TCLK\_in cycle (to load the test results into the shift register) before activating the Strobe\_out\_TR signal to read out the results.

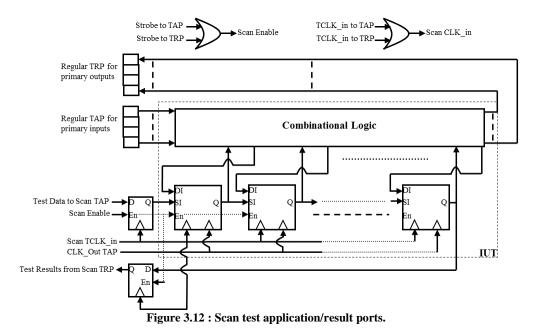

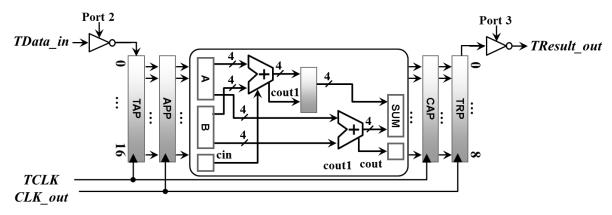

IP designers may also need to use full-scan designs in addition to/or instead of boundary-scan. This requires making all or part of the internal Flip Flops scanable (forming one long scan chain). Such scan chains could be used for debugging/diagnostics of an IUT internal circuitry or to fully test a sequential circuit which is difficult to do using only primary inputs/outputs. Special TAP/TRP scan ports were developed for scan chain inputs/outputs of IUTs, as shown in Figure 3.12. These ports have to be used (i.e. selected) in pairs where data is shifted through the chain when either the Strobe\_in\_TR or the Strobe\_out\_TR signals is activated. The TCLK\_in, Scan\_En and CLK\_Out signals are made available for the internal scan FFs of the IUT. Regular TAP/TRP ports are used for non-scan primary inputs and outputs of the IUT. The TACP instructions support shifting test data in, shifting test results out, or simultaneous shifting in and out of test data and results, respectively.

(a) k-bits wide test application port (TAP).

(b) l-bits wide test results port (TRP).

Figure 3.11 : Test application port (TAP) and test results port (TRP).

#### 3.2 User Interface Software

This software enables the user to fully control the testing process. It provides the user with complete interfaces for writing and editing programs, downloading program and test data to memories, uploading programs, test data and test results from memories, reading register contents, sending control signals to reset registers, reset program execution, set a break point, edit the value of an address registers, start or stop running the current program.

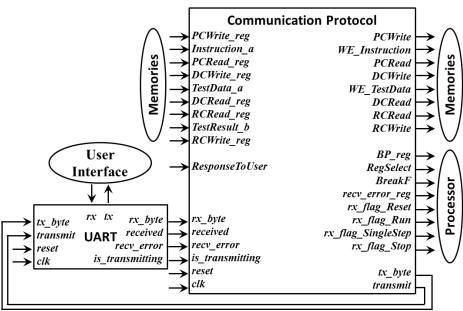

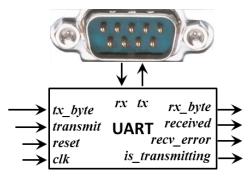

Any communication media can be used; Ethernet, USB or serial port (i.e. UART port). The user interface and the test processor can are communicating through a serial cable. A communication protocol is proposed to be implemented in both sides. The protocol take care of downloading and uploading from memories. It also forwards control signals from the user to the processor. It gives a high level of abstraction to facilitate the processor design and the user interface design.

# **Interface Protocol**

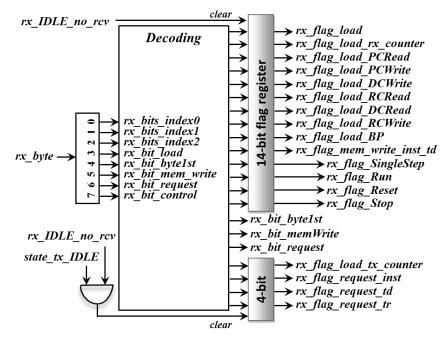

The user interface has to implement the user interface protocol which will be also implemented on TACP (a hardware version). The protocol defines 19 commands as listed and described in Table 3.1. They are categorized into four groups; loading registers commands, downloading to memories commands, uploading form memories requests and control commands. The communication unit is the packet. The user sends variable-size packets each packet starts with type byte that defines the packet type and length. A graphical representation of the implemented protocol structure is depicted in Figure 3.13.

Figure 3.13 : Packet type list. Each packet starts with flags defining a command and determines packet size.

| Class    | No. | Command                                                                                                          | Description                                                                                                           |  |  |  |  |  |

|----------|-----|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|