# A GENERALIZED MODULAR REDUNDANCY SCHEME FOR ENHANCING FAULT TOLERANCE OF COMBINATIONAL CIRCUITS

BY

## FERAS M. CHIKH OUGHALI

A Thesis Presented to the DEANSHIP OF GRADUATE STUDIES

## KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

1963

In Partial Fulfillment of the Requirements for the Degree of

# **MASTER OF SCIENCE**

In

COMPUTER ENGINEERING

October 2012

# KING FAHD UNIVERSITY OF PETROLEUM & MINERALS DHAHRAN 31261, SAUDI ARABIA DEANSHIP OF GRADUATE STUDIES

This thesis, written by

#### Feras M. Chikh Oughali

under the direction of his thesis advisor and approved by his thesis committee, has been presented to and accepted by the Dean of Graduate Studies, in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE IN COMPUTER ENGINEERING

Thesis Committee Dr. Aiman H. El – Maleh (Advisor)

Dr. Abdelhafid Bouhraoua (Member)

Dr. Sadiq M. Sait (Member)

Dr.Basem AL – Madani Department Chairman

Dr. Salam A. Zummo Dean of Graduate Studies

0/12/12 Date

Dedicated to

My Parents & dearest Sisters

## Acknowledgements

All sincere praises and thanks are due to Allah (SWT), for His limitless blessings on us. May Allah bestow his peace and blessings be upon his Prophet Mohammad (P.B.U.H) and his family. Acknowledgements are due to King Fahd University of Petroleum & Minerals for providing the computing resources for this research.

I would like to express my profound gratitude and appreciation to my thesis advisor Dr. Aiman H. El-Maleh for his support and endless patience in improving this work. His continuous guidance, advice and encouragement can never be forgotten. I would also like to express my appreciation to my thesis committee members, Dr. Sadiq M. Sait and Dr. Abdelhafid Bouhraoua for their feedback and constructive comments. Also, I would like to express my deepest thanks to faculty and staff members of Computer Engineering Department for their cooperation. I would like to address special thanks to my friends and fellow graduate students for their help. I am very grateful to all of you. Especially, my best friends Abdalrahman Arafeh, Mouheddin Alhaffar, Abdulrahman Idlbi, Abdulnaser Alsharaa and Mohammad Tamim.

I also thank my beloved parents and my cherished sisters for their everlasting love, support, and constant encouragement throughout my academic career. I undoubtedly could not have done this without you. Finally, thanks to everybody who contributed to this achievement in a direct or an indirect way.

# Contents

|                    | Ack               | nowledgements iv                    | 7 |

|--------------------|-------------------|-------------------------------------|---|

| List of Tables     |                   | of Tables ix                        | 2 |

| List of Figures    |                   | of Figures xi                       | i |

| Abstract (English) |                   | tract (English) xv                  | 7 |

|                    | Abstract (Arabic) |                                     | i |

| 1                  | Intr              | oduction 1                          | L |

|                    | 1.1               | Motivation                          | 2 |

|                    | 1.2               | Problem Statement                   | } |

|                    | 1.3               | Thesis Contributions 3              | } |

|                    | 1.4               | Thesis Organization                 | ł |

| <b>2</b>           | Lit€              | rature Review 5                     | 5 |

|                    | 2.1               | Errors, Faults, and Types of Faults | j |

|   | 2.2                                                                                                    | Fault Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6                                                                                  |

|---|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

|   | 2.3                                                                                                    | Fault Avoidance and Fault Tolerance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7                                                                                  |

|   | 2.4                                                                                                    | Soft Errors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9                                                                                  |

|   | 2.5                                                                                                    | Soft Error Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11                                                                                 |

|   | 2.6                                                                                                    | Soft Error Mitigation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13                                                                                 |

|   |                                                                                                        | 2.6.1 Hardened Storage Cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13                                                                                 |

|   |                                                                                                        | 2.6.2 Modular Redundancy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 14                                                                                 |

|   |                                                                                                        | 2.6.3 Error Detection using Checkers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 16                                                                                 |

|   |                                                                                                        | 2.6.4 Circuit-Level Time Redundancy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 16                                                                                 |

|   | 2.7                                                                                                    | Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17                                                                                 |

|   |                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                    |

| 3 | Ger                                                                                                    | neralized Modular Redundancy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31                                                                                 |

| 3 | <b>Ger</b><br>3.1                                                                                      | neralized Modular Redundancy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                    |

| 3 |                                                                                                        | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 31                                                                                 |

| 3 | 3.1                                                                                                    | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31                                                                                 |

| 3 | 3.1<br>3.2                                                                                             | Introduction       Types of States         Types of States       Protection of Dominant States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 31<br>32                                                                           |

| 3 | <ul><li>3.1</li><li>3.2</li><li>3.3</li><li>3.4</li></ul>                                              | Introduction       Types of States         Types of States       Protection of Dominant States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 31<br>32<br>33<br>36                                                               |

| 3 | <ul><li>3.1</li><li>3.2</li><li>3.3</li><li>3.4</li></ul>                                              | Introduction       Types of States         Types of States       Protection of Dominant States         Protecting Single Output       Protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ul> <li>31</li> <li>32</li> <li>33</li> <li>36</li> <li>40</li> </ul>             |

| 3 | <ol> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> </ol>               | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <ul> <li>31</li> <li>32</li> <li>33</li> <li>36</li> <li>40</li> <li>44</li> </ul> |

|   | <ol> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>Usin</li> </ol> | Introduction       Types of States         Types of States       Protection of Dominant States         Protecting Single Output       Protecting Single Output         Protecting Multiple Outputs       Protecting Multiple Outputs         Why Generalized Modular Redundancy?       Protecting Combinational                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <ul> <li>31</li> <li>32</li> <li>33</li> <li>36</li> <li>40</li> <li>44</li> </ul> |

|   | <ol> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>Usin</li> </ol> | Introduction       Types of States         Types of States       Protection of Dominant States         Protecting Single Output       Protecting Single Output         Protecting Multiple Outputs       Protecting Multiple Outputs         Why Generalized Modular Redundancy?       Protecting Combinational Combinat | <ul> <li>31</li> <li>32</li> <li>33</li> <li>36</li> <li>40</li> <li>44</li> </ul> |

|   | 4.2 | Module Replication against Customized Redundant Modules   | 47 |

|---|-----|-----------------------------------------------------------|----|

|   | 4.3 | Complexity of Correction Logic                            | 52 |

|   |     | 4.3.1 Masking of Correction Logic                         | 56 |

|   | 4.4 | Single Output Versus Pair Protection                      | 59 |

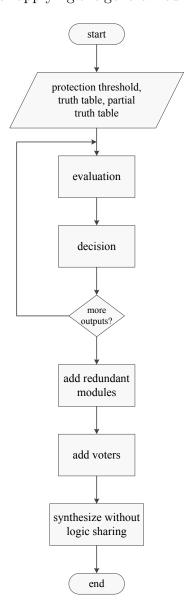

|   | 4.5 | Methodology of Applying GMR                               | 61 |

|   | 4.6 | Illustrative Example                                      | 66 |

| 5 | Exp | perimental Setup & Framework                              | 70 |

|   | 5.1 | Benchmarks                                                | 70 |

|   | 5.2 | Fault Model and Injection Mechanism                       | 70 |

|   | 5.3 | Measuring Reliability of Circuits                         | 72 |

|   | 5.4 | Tools                                                     | 74 |

|   | 5.5 | Work Flow                                                 | 75 |

| 6 | Exp | perimental Results & Discussion                           | 77 |

|   | 6.1 | Analyzing Benchmarks                                      | 77 |

|   | 6.2 | Evaluating Reliability at Different Protection Thresholds | 82 |

|   | 6.3 | Effectiveness of Single Output Protection                 | 88 |

|   | 6.4 | Effectiveness of Pair Protection                          | 89 |

|   | 6.5 | Effectiveness of GMR Protection                           | 91 |

|   | 6.6 | Reliability of Other Benchmarks at $thr$ Equals to $0.9$  | 92 |

|   | 6.7 | Protecting Voters                                         | 95 |

| 7 | Conclusion & Future Work |             | 99    |

|---|--------------------------|-------------|-------|

|   | 7.1                      | Conclusion  | . 99  |

|   | 7.2                      | Future Work | . 100 |

|   | BIE                      | BLIOGRAPHY  | 101   |

|   | Vita                     | ae          | 109   |

# List of Tables

| 3.1 | Truth table of a full adder                                                                         | 41 |

|-----|-----------------------------------------------------------------------------------------------------|----|

| 3.2 | Summary of protection methods and their area overhead                                               | 45 |

| 4.1 | Size of correction logic after multilevel minimization for all possible                             |    |

|     | scenarios of pair protection.                                                                       | 55 |

| 5.1 | Benchmarks circuits.                                                                                | 71 |

| 6.1 | Analyzing benchmarks at different protection thresholds (1)                                         | 79 |

| 6.2 | Analyzing benchmarks at different protection thresholds (2). $\ldots$                               | 80 |

| 6.3 | Analyzing benchmarks at different protection thresholds (3)                                         | 81 |

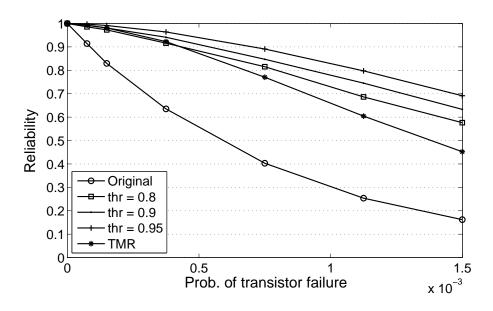

| 6.4 | Reliability of "apex4" benchmark at different protection thresholds                                 | 84 |

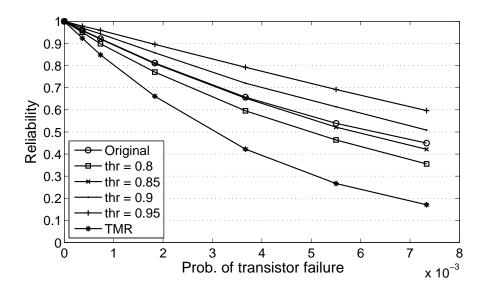

| 6.5 | Reliability of "ex5p" benchmark at different protection thresholds                                  | 86 |

| 6.6 | Total module savings & reduction percentages compared to TMR at                                     |    |

|     | thr equals to 0.9. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 87 |

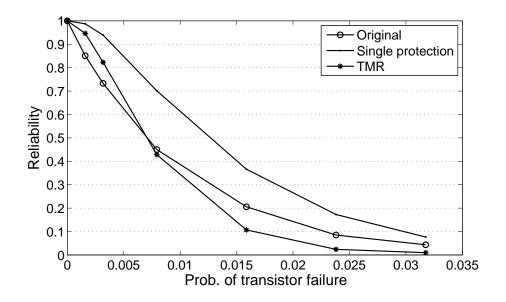

| 6.7 | Reliability of 6-bit equality comparator with single output protection.                             | 89 |

| 6.8  | Reliability of 4-bit general comparator with pair protection           | 90 |

|------|------------------------------------------------------------------------|----|

| 6.9  | Reliability of 24-bit leading zero detector                            | 92 |

| 6.10 | Reliability and area overhead of benchmarks for the GMR scheme         |    |

|      | with 0.9 protection                                                    | 93 |

| 6.11 | Reliability and area overhead of benchmarks for the TMR scheme         | 94 |

| 6.12 | Reliability of 4-bit general comparator with/without voter protection. | 97 |

| 6.13 | Reliability of "ex5p" benchmark with/without voter protection          | 98 |

# List of Figures

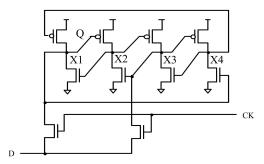

| 2.1  | Example of hardened storage cells: DICE [1]                            | 13 |

|------|------------------------------------------------------------------------|----|

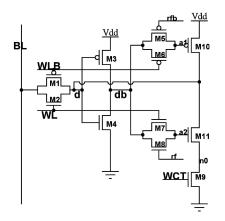

| 2.2  | 11-transistor nanoscale CMOS memory cell [2]                           | 14 |

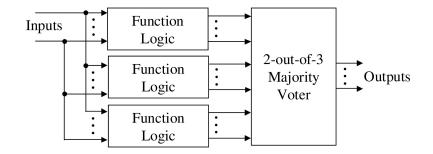

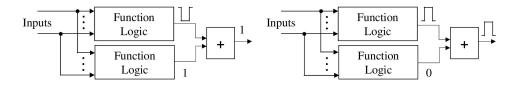

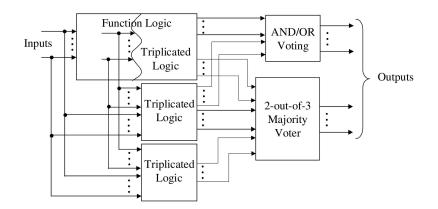

| 2.3  | Block diagram for TMR-based error masking [3]                          | 15 |

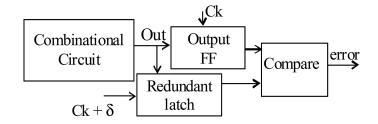

| 2.4  | A detection technique using a redundant latch and a delayed clock      | 17 |

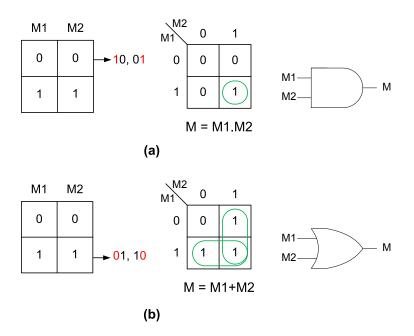

| 2.5  | Example of dominant value reduction for error masking [3]              | 19 |

| 2.6  | Partial error masking scheme [3]                                       | 19 |

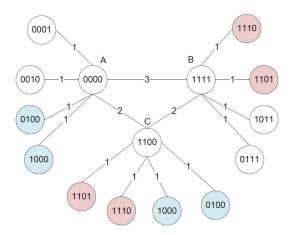

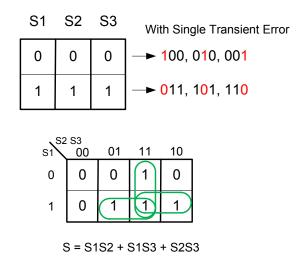

| 2.7  | Incorrect encoding for 3 states with redundancy [4]                    | 23 |

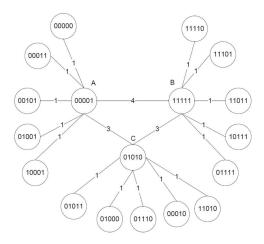

| 2.8  | Correct encoding for 3 states with redundancy [4]                      | 24 |

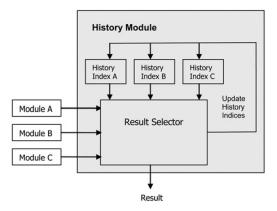

| 2.9  | HICC module [5]                                                        | 26 |

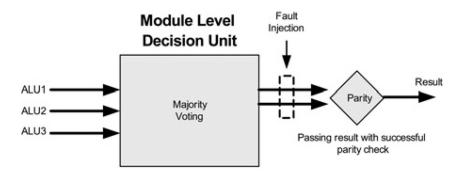

| 2.10 | Enhanced majority voting with parity checking at the module level [5]. | 27 |

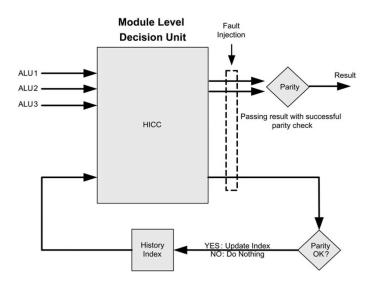

| 2.11 | Enhanced HICC unit with parity checking at the module level [5]        | 27 |

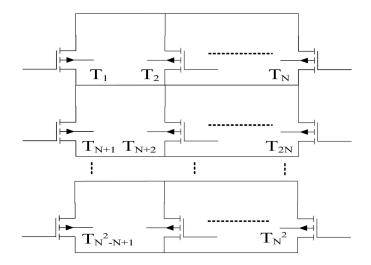

| 2.12 | Defect-tolerant $N^2$ -transistor structure [6]                        | 28 |

|      |                                                                        |    |

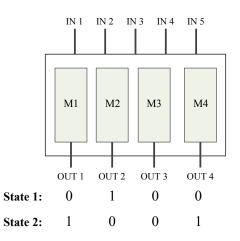

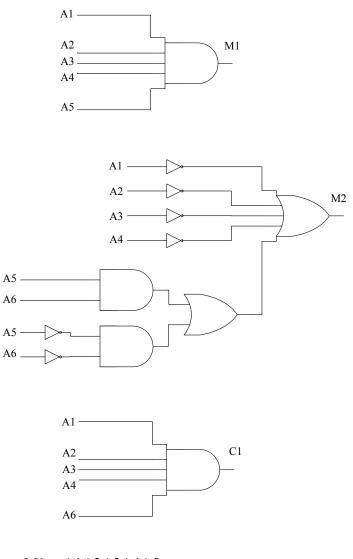

| 3.1  | States in combinational logic circuits                                 | 32 |

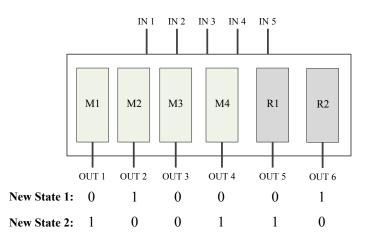

| 3.2  | New States after introducing redundant modules                         | 34 |

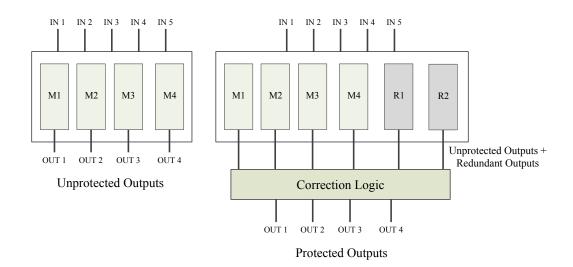

| 3.3  | Protected outputs after introducing redundant modules and correc-         |    |

|------|---------------------------------------------------------------------------|----|

|      | tion logic                                                                | 35 |

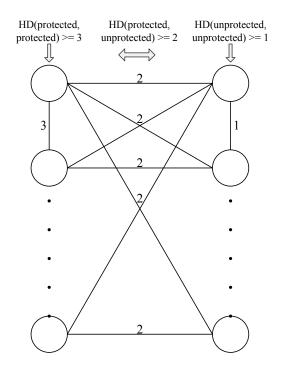

| 3.4  | Desired Hamming distance between different types of states                | 36 |

| 3.5  | Protecting one state in single output circuits.                           | 38 |

| 3.6  | Protecting all states in single output circuits                           | 39 |

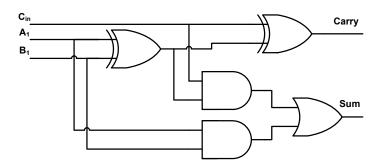

| 3.7  | Logic diagram of a full adder.                                            | 40 |

| 3.8  | Full adder's states after replication (protecting two states)             | 41 |

| 3.9  | Full adder's protected outputs after replication (protecting two states). | 42 |

| 3.10 | Full adder's protected outputs after replication (protecting all states). | 43 |

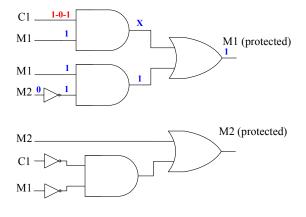

| 4.1  | Protecting states "00", "01", and "10" by: a) Module replication. b)      |    |

|      | Customized redundant modules                                              | 49 |

| 4.2  | Description of example circuit                                            | 50 |

| 4.3  | Description of example circuit after adding a customized redundant        |    |

|      | module                                                                    | 50 |

| 4.4  | Example circuit after adding a customized redundant module                | 51 |

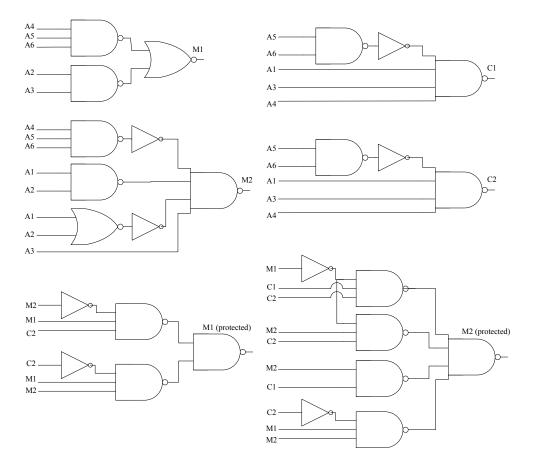

| 4.5  | Correction logic for modules $M1$ and $M2$ in example circuit             | 52 |

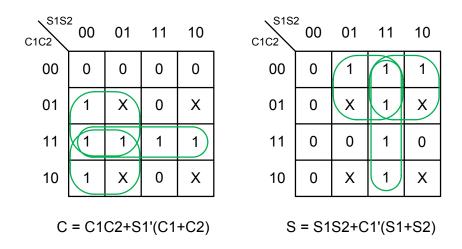

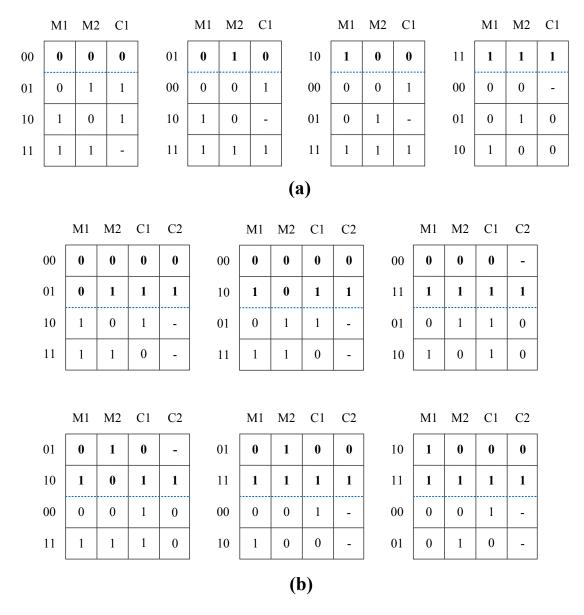

| 4.6  | Majority voter and correction logic for pair protection (with two-level   |    |

|      | minimization)                                                             | 54 |

| 4.7  | a) One customized redundant module to protect one state. b) Two           |    |

|      | customized redundant modules to protect two states                        | 57 |

| 4.8  | Three customized redundant modules to protect three states                   | 58 |

|------|------------------------------------------------------------------------------|----|

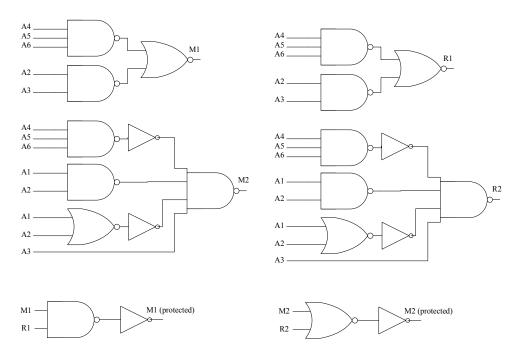

| 4.9  | Original and replicated modules for single protection of the example         |    |

|      | circuit along with correction logic                                          | 61 |

| 4.10 | Original and customized modules for pair protection of the example           |    |

|      | circuit along with correction logic                                          | 62 |

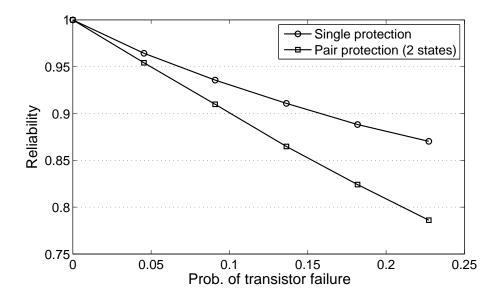

| 4.11 | Reliability of single protection against pair protection (protecting $2$     |    |

|      | states)                                                                      | 63 |

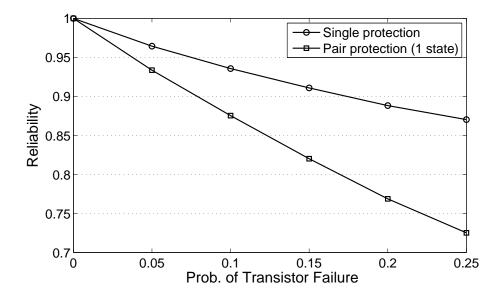

| 4.12 | Reliability of single protection against pair protection (protecting $1$     |    |

|      | state).                                                                      | 63 |

| 4.13 | Methodology of applying GMR for enhancing combinational circuits             |    |

|      | reliability.                                                                 | 65 |

| 4.14 | Actual file describing the truth table of the leading zero detector circuit. | 69 |

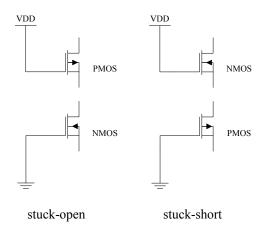

| 5.1  | Stuck-open and stuck-short fault models.                                     | 72 |

| 5.2  | Work flow for applying the generalized modular redundancy scheme.            |    |

|      |                                                                              |    |

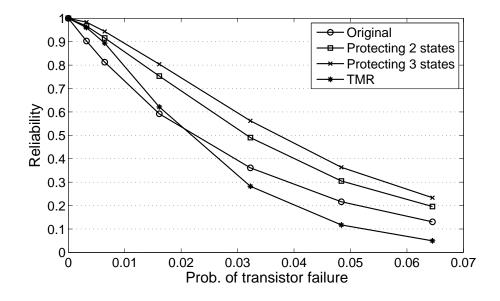

| 6.1  | Reliability of "apex4" benchmark at different protection thresholds          | 84 |

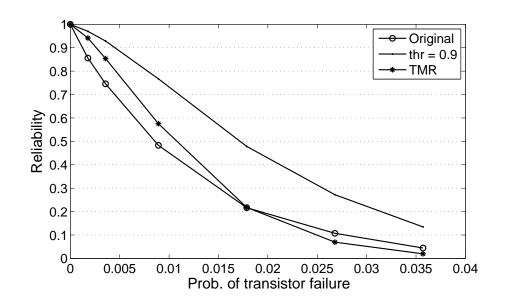

| 6.2  | Reliability of "ex5p" benchmark at different protection thresholds           | 86 |

| 6.3  | Reliability of 6-bit equality comparator with single output protection.      | 88 |

| 6.4  | Reliability of 4-bit general comparator with pair protection                 | 90 |

| 6.5  | Reliability of 24-bit leading zero detector                                  | 91 |

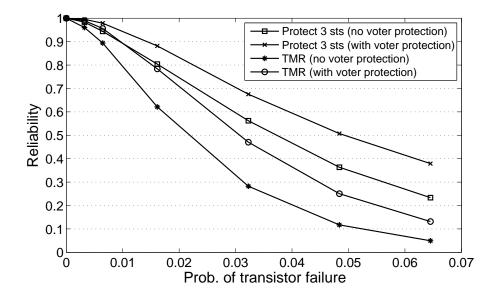

| 6.6  | Reliability of 4-bit general comparator with/without voter protection.       | 96 |

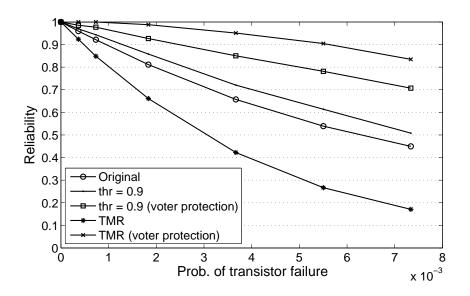

6.7 Reliability of "ex5p" benchmark with/without voter protection. . . . 98

#### THESIS ABSTRACT

| Name:           | Feras M. Chikh Oughali                                |

|-----------------|-------------------------------------------------------|

| Title:          | A Generalized Modular Redundancy Scheme for Enhancing |

|                 | Fault Tolerance of Combinational Circuits             |

| Major Field:    | Computer Engineering                                  |

| Date of Degree: | October 2012                                          |

Nano-scale devices are continuously shrinking, operating at lower voltages and higher frequencies. This makes them more susceptible to environmental perturbations and distinguished by their high dynamic fault rates. Redundancy techniques are widely used to increase the reliability of combinational logic circuits. In this work, soft error reliability is improved by using such techniques, and based on probability of occurrence for states at the outputs of circuits. A generalized modular redundancy scheme to enhance the reliability of combinational circuits is proposed. Additionally, several aspects regarding the application of this scheme are explored. This comprises types of redundant modules, complexity of correction logic and single versus multiple outputs protection. Also, a methodology for applying the generalized modular redundancy scheme is developed. Reliability analysis for various benchmarks from the LGSynth91 suite shows that the proposed methodology can achieve reliability figures higher than that of triple modular redundancy. In general, significant overhead savings are accomplished in addition to that superior reliability.

**Keywords:** Reliability, Soft errors, Combinational logic circuits, Modular redundancy, Low area overhead, Logic design.

#### MASTER OF SCIENCE DEGREE

King Fahd University of Petroleum & Minerals, Dhahran, Saudi Arabia.

October 2012

#### ملخص الرسالة

الاسم: فراس محمد معتز شيخ أوغلي

**العنوان:** مخطط عام لاستخدام الوحدات المتكررة من أجل زيادة وثوقية الدارات التركيبية التخصص: هندسة الحاسب الآلي

تاريخ الدرجة العلمية: تشرين الأول 2012

لا تزال الأجهزة النانوية آخذة بالنقلص مع مرور الوقت، إضافة إلى تطلبها إلى جهد تشغيل أقل وترددات عمل أعلى. هذا ما جعلها أكثر عرضة للمؤثرات الخارجية وأصبح من سماتها ارتفاع معدلات الخطأ الديناميكية. لحل هذه المشكلة سنلجأ لتقنيات النكرار، فهي تستخدم على نطاق واسع في زيادة وثوقية الدارات التركيبية. وقد قمنا في بحثنا هذا بتحسين الوثوقية ضد الأخطاء اللينة (أو الديناميكية) بالاعتماد على تقنيات التكرار وعلى احتمالات الحالة بحثنا هذا مخارج هذه المثكلة سنلجأ لتقنيات التكرار، فهي تستخدم على نطاق واسع في زيادة وثوقية الدارات التركيبية. وقد قمنا في بحثنا هذا بتحسين الوثوقية ضد الأخطاء اللينة (أو الديناميكية) بالاعتماد على تقنيات التكرار وعلى احتمالات الحالة على مخارج هذه الدارات. يقترح البحث مخططاً عاماً لاستخدام الوحدات المتكررة من أجل زيادة وثوقية الدارات التركيبية، وسيبحث إضافة إلى ذلك في عدة جوانب متعلقة بتطبيق هذا المخطط. ويشتمل ذلك على ثلاثة أمور: أنواع الوحدات المتكررة من أجل زيادة مخرج العن ثلاثة أمور: أنواع الوحدات المتكررة، تعقيد منطق التصحيح، والمقارنة بين حماية مخرج واحد لقاء حماية مخارج متعددة. النواع الوحدات المتكررة، تعقيد منطق التصحيح، والمقارنة بين حماية مخرج واحد لقاء حماية مخارج متعددة. الذي تم يعلون الوثوقية أنواع الوحدات المتكررة، تعقيد منطق التصحيح، والمقارنة بين حماية مخرج واحد لقاء حماية مخارج متعددة. ورفقية أنواع الوحدات المتكررة، تعقيد منطق التصحيح، والمقارنة بين حماية مخرج واحد لقاء حماية مخارج متعددة. ويشقوم علاوة على ذلك بتطوير منهجية لتطبيق المخطط العام لاستخدام الوحدات المتكررة. ويظهر تحليل الوثوقية أنواع الوحدات المتكررة، متعقيد منطق التصحيح، والمقارنة بين حماية مخرج واحد لقاء حماية مخارج متعددة. ورفي يوقية أنواع الوحدات المتكررة، منعوير منهجية لموسرعة المولالية العام لاستخدام الوحدات المتكررة ويظهر تحليل الوثوقية الذي تم إجرائه لدارات مرجعية عدة من مجموعة الحقائية إلى محايم مالوحدات المتكررة. ويظهر تحليل الوثوقية ألعلى من تلك التي يحققها تكرار الوحدات الثلاثي. وعلى العموم، فقد حققنا وفرات كبيرة في الوحدات ورؤوقية ألما مردوية بالوضافة إلى تحقيق الوثوقية العالية.

# Chapter 1

# Introduction

In future nano-scale technology, studies indicate that high-density chips, up to an order of  $10^{12}$  devices/cm<sup>2</sup> [7], will be increasingly accompanied by manufacturing defects and susceptible to dynamic faults during chip operation [8][9]. The reduced noise margin of nano-scale devices increases the effect of external fault sources such as electromagnetic interferences, thermal perturbations, and cosmic radiations. Moreover, operating at low voltages and high frequencies makes these devices more fragile and sensitive to environmental influences. Essentially, fault tolerant designs are required for reliable systems that will operate correctly in spite of transient dynamic faults. All fault tolerance approaches rely on some sort of redundancy; otherwise, there will be no way to tell that a device has changed its state.

### 1.1 Motivation

In nanometric technologies, circuits are increasingly sensitive to various kinds of perturbations. Soft errors, a concern in the past for space applications, become a reliability issue at ground level. Alpha particles and atmospheric neutrons induce single-event upsets affecting memory cells, latches, and flip-flops, and single-event transients initiated in the combinational logic and captured by the associated latches and flip-flops. To overcome this challenge, a designer must utilize a variety of soft error mitigation schemes adapted to various circuit structures, design architectures, and design constraints [10].

The soft error rate (SER) produced by these effects may exceed the failure in time (FIT) specifications in various application domains. In such applications, soft-error mitigation schemes should be employed for both memories and logic. Duplication and comparison such as triple modular redundancy (TMR) and majority voting, or more generally, N-modular redundancy (NMR) proposed by Von Neumann [11] are the most commonly used solutions for reducing SER induced by SEUs and SETs in logic parts. Many researches have investigated increasing the reliability of circuits using redundancy schemes. Their main concern is to increase reliability while minimizing the inevitable overhead of area, power, or time. In this work, we are targeting the reliability issue in the logic based on probabilities of signals and output states. We will make use of this information to build up a reliable version from the original circuit, while maintaining the minimum possible area overhead based on a generalized modular redundancy scheme.

## 1.2 Problem Statement

Given a combinational logic circuit, our aim is to increase the reliability of this circuit against soft errors using a generalized modular redundancy scheme, while maintaining minimum area overhead.

### **1.3** Thesis Contributions

The contributions of this work can be summarized as follows:

- Develop a generalized modular redundancy scheme to enhance the reliability of combinational logic circuits against soft errors based on probabilities of states at their outputs.

- Investigate different aspects concerning the application of the generalized modular redundancy scheme. This includes types of redundant modules, complexity of voters and single versus multiple outputs protection.

- Develop a methodology for applying the generalized modular redundancy scheme to increase the reliability of combinational logic circuits with variety of sizes.

#### 1.4 Thesis Organization

The thesis is organized as follows. Chapter 2 starts with a background about different types of faults and their models. Different soft error mitigation methods are also discussed. This includes hardened storage cells, modular redundancy and circuit-level time redundancy.

Chapter 3 introduces the generalized modular redundancy (GMR) concept. In Chapter 4, we start by discussing various aspects concerning the application of the generalized modular redundancy scheme. Based on that, the developed methodology of applying GMR to enhance the reliability of combinational circuits is then presented.

In Chapter 5, we present the work flow which has been followed to improve fault tolerance of combinational circuits. Fault model and reliability evaluation methodology along with simulation environment are also discussed in this chapter. Chapter 6 provides some analyses and evaluations of different aspects about the proposed methodology. Reliability results of various benchmarks are also reported. Finally, Chapter 7 concludes this work and suggests future work.

# Chapter 2

## Literature Review

#### 2.1 Errors, Faults, and Types of Faults

As stated in [12], we term an internal state of a system an erroneous state when there exist circumstances in which further processing, by the normal algorithms of the system, will lead to a failure. The term "error" is used to designate that part of the state which is "incorrect." An error is thus an item of information; and the terms error, error detection, and error recovery are used as equivalents for erroneous state, erroneous state detection, and erroneous state recovery.

A fault is the mechanical or algorithmic cause of an error, while a potential fault is a mechanical or algorithmic construction within a system such that (under some circumstances within the specification of the use of the system) the construction will cause the system to assume an erroneous state. Faults due to hardware component failures, are often classified by duration, extent, and value. Duration refers to whether the fault is permanent or transient; extent applies to whether the effect of the fault is localized or distributed; and value indicates whether the fault creates fixed or varying erroneous logical values.

#### 2.2 Fault Models

In engineering, models are used to bridge the gap between the physical reality and mathematical abstraction. They allow the development of analytical tools. Therefore, they are essential in the design process. Modeling of faults is highly related to the modeling of the circuit. Generally, the level refers to the degree of abstraction. Thus, the behavioral level has fewer implementation details, and fault models at this level may have no obvious correlation to manufacturing defects. The registertransfer level (RTL) or logic level consists of a netlist of gates. Stuck-at faults at this level are the most popular fault models in digital testing. Other faults at this level are bridging faults and delay faults. Transistor and other lower levels, which referred to as component levels, include stuck-open and stuck-short types of faults. Considering a MOS transistor as an ideal switch, a defect is modeled as the switch being permanently in either the open or the shorted state. This fault model assumes only one transistor to be stuck-open or stuck-short. Stuck-short is also referred to as stuck-on or stuck-closed. These models were proposed by Case [13].

Stuck-at faults are modeled by assigning a fixed (0 or 1) value to a signal line in the circuit. A signal line can be an input or an output of a logic gate or a flip-flop. The most popular forms are the single stuck-at faults, i.e., a line can have two faults: stuck-at-1 and stuck-at-0. There are three assumptions assumed for single stuck-at faults: (1) only one line is faulty, (2) the faulty line is permanently set to either 0 or 1, and (3) the fault can be at an input or output of a gate. In general, several stuck-at faults can be simultaneously present in a circuit. A circuit with n lines can have  $(3^n - 1)$  possible stuck line combinations. This is because each line can be in one of the three states: stuck-at-1, stuck-at-0, or fault-free. All combinations except one, having all lines in fault-free states, are counted as faults. It is clearly evident that even a moderate value of n will give an enormously large number of multiple stuck-at faults. For this reason, it is a common practice to model only single stuck-at faults, where an n-line circuit can have at most 2n single stuck-at faults [14]. In addition, a large percentage of multiple stuck-at faults are detected by single stuck-at fault tests.

#### 2.3 Fault Avoidance and Fault Tolerance

The traditional approach to achieving reliable computing systems has been based largely on fault avoidance (termed fault intolerance by Avizienis [15]) which includes: utilization of the most reliable components, elimination of expected forms of interference and carrying out of comprehensive testing to eliminate hardware and software design faults. Many recent methods have been proposed to perform fault avoidance through reconfiguration. These methods are classified into two groups: (1) Hardware-oriented methods, where a faulty basic element (BE) is automatically swapped with a spare using additional wires, switches, and controllers, along the replacement policy. (2) Reconfiguration-oriented, where reconfigurability is exploited for fault avoidance with partial mapping modification [16].

An alternative approach to fault avoidance is that of fault tolerance. This approach involves the use of protective redundancy. A system can be designed to be fault tolerant by incorporating additional components and special algorithms, which attempt to ensure that occurrences of erroneous states do not result in later system failures. The degree of fault tolerance depends on the success with which erroneous states, which corresponds to faults, are identified and detected, and the success with which such states are repaired or replaced [12].

The objective of fault tolerance is either to mask, or to recover from, faults once they have been detected [17]. Many researches on reliable systems are concerned with the detection of faults using error detecting and correcting codes or fault detecting and self repairing circuits. The tolerance itself is achieved using redundancy techniques.

## 2.4 Soft Errors

When high-energy neutrons (present in terrestrial cosmic radiation) or alpha particles (originating from impurities in the packaging materials) strike a sensitive region in a semiconductor, they generate a dense local track of electron-hole pairs. These electron-hole pairs are then collected at a p-n junction, and create a single event transient (SET). This unexpected current pulse of a short duration, under some conditions, may be misinterpreted by the circuit as a valid signal, and result in an incorrect state or output, thus producing a soft error [3]. As this type of faults does not reflect a permanent failure, hence soft or transient terms are used.

Historically, soft errors have been of great concern in memory cells, that are much more susceptible to particle strikes than combinational logic, where SET are frequently masked before reaching an output or a storage element [18] [19]. However, technological trends such as faster clock rates, smaller device sizes, lower supply voltages, and shallower logic depths are drastically reducing SET masking, and remarkably increasing the occurrence of soft errors in combinational logic [20]. The single event transient may propagate through the combinational logic, and errors may or may not reach a storage element or an output depending on the following factors [21]:

Logical masking: The hazard may not propagate because there is not any sensitized path from the node where the strike happened to any output of the combinational logic circuit.

- **Temporal masking:** As the hazard propagates towards a sequential element, it will form a sort of noise on the data input of that sequential element. This noise may reach the sequential element outside its latching window. Hence, the error will not be latched and there will be no soft error.

- **Electrical masking:** Since all CMOS circuits have limited bandwidths, hazards with bandwidths greater than the cut-off frequency will be attenuated. The amplitude of the hazard pulse will be reduced, and eventually the hazard pulse may disappear. However, since most logic gates are nonlinear circuits with a substantial voltage gain, low-frequency pulses with sufficient initial amplitude will be amplified [22].

As stated earlier, with the increase in clock rates, and the reduction in both feature sizes and supply voltages the effect of those masking is becoming more limited.

The most deceitful form of single event transient errors is silent data corruption (SDC), where a fault causes the system to produce erroneous outputs. To avoid silent data corruption, designers often employ basic error detection mechanisms, such as parity. With the ability to detect a fault but not correct it, we can avoid generating incorrect outputs, but cannot recover when an error happens. That is to say, error detection mechanism does not reduce the overall error rate, but does provide fail-stop behavior and thereby avoids any data corruption. Such errors are

categorized as detected unrecoverable errors (DUE) in [23].

There are two techniques that can be used to reduce soft errors impact: (1) error detection and retry and (2) error masking. Error detection and retry involves using on-line error detection circuitry [24] [25] [26] which monitors the outputs of a circuit for the occurrence of an error. If an error is observed, the system recovers through rollback and retry, therefore preventing a fault from happening. Error masking employs circuitry that masks errors using schemes such as: quadded logic [27], interwoven logic [28], and triple modular redundancy (TMR) [26]. For real-time systems, it may not be possible to do error detection and retry, therefore error masking is the only available choice. Sometimes, the cost of implementing error detection and retry may be comparable to that of implementing error masking schemes [3].

#### 2.5 Soft Error Rate

Currently, the industry specifies soft error rates in terms of silent data corruption (SDC) and detected unrecoverable errors (DUE) numbers. Both SDC and DUE rates are typically expressed in FIT (Failure(s) in Time). One FIT expresses one error in a billion (10<sup>9</sup>) hours. FIT rates are additive, so we can compute the SDC or DUE FIT rate of a chip or a system by summing the SDC or DUE FIT rates of all its components. The sum of SDC and DUE FIT is usually referred to as the soft error rate (SER) of a chip [23]. The additive property of FIT makes it convenient for

calculations. However, mean time to failure (MTTF) is another important indicator. MTTF is inversely related to FIT. A FIT rate of 1000 is equivalent to MTTF of 114 years  $(10^9/(1000 \times 24 \times 365))$ . Vendors usually set soft error rate budgets for their chips or systems based on target market requirements. For example, IBM targets 114 SDC FIT (1000 yr MTTF), for its Power4 systems [29].

Soft error rate (SER) estimation can be performed at different levels of design hierarchies, through modeling soft errors across the device, logic, and architectural levels. Device level abstracts the soft error impact as a transient pulse waveform. Soft errors are modeled by using nuclear and device physics tools, with an aim of creating a transient current waveform library that captures different process and operating conditions that impact the soft error rate. SPICE simulation is usually used to obtain the estimation at this level of abstraction. At the logic level, estimation of SER is based on attempting to capture electrical, logic, and latch window masking models. This can be used next to compute SET occurrence rate, the error propagation probability (EPP), and the error latching probability. Architectural level solutions may be more effective than circuit or logic level solutions, because the definition of what constitutes an error typically lies in the architecture. For example, in microprocessor architecture, a strike on a branch prediction unit does not result in an error in the microprocessor.

Figure 2.1: Example of hardened storage cells: DICE [1].

## 2.6 Soft Error Mitigation

Radiation affects logic due to single event transient in combinational logic and single event upset in sequential cells. Solutions for these effects comprise hardened sequential cells, self-checking design, modular redundancy, and circuit-level time redundancy.

#### 2.6.1 Hardened Storage Cells

Hardened storage cells like SRAM cells, latches, and flip-flops preserve their state even if the state of one of their nodes is altered by a transient soft error. Several hardened storage cells have been proposed in the literature. Figure 2.1 shows the DICE cell [1] which is robust against any single event disturbing a single node of the cell.

Another hardening approach is proposed in [30]. In [2] this solution was adapted to implement a new memory cell. This proposed hardening design makes use of 11 CMOS transistors. The proposed hardened memory cell overcomes the problems

Figure 2.2: 11-transistor nanoscale CMOS memory cell [2].

associated with the previous designs by utilizing novel access and refreshing mechanisms. The cell was shown to provide similar protection against SEUs as DICE while requiring 20% less area and a 55% reduction of speed-power product. Details of several hardened cells can be found in [31].

#### 2.6.2 Modular Redundancy