# Multithreaded Processor Core Optimized for Parallel Thread Execution

BY Ayman Ali Mohammad Hroub

A Thesis Presented to the DEANSHIP OF GRADUATE STUDIES

KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

# MASTER OF SCIENCE

In

# **COMPUTER ENGINEERING**

May 2011

\*\*\*\*\*\*\*\*\*\*

# KING FAHD UNIVERSITY OF PETROLEUM & MINERALS DHAHRAN 31261, SAUDI ARABIA

# DEANSHIP OF GRADUATE STUDIES

This thesis, written by Ayman Ali Mohammad Hroub under the supervision of his thesis advisor and approved by his thesis committee, has been presented to and accepted by the Dean of Graduate Studies, in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE in COMPUTER ENGINEERING

Thesis Committee Dr. Muhamed Mudawar (Chairman) Dr. Aiman El-Maleh (Member) Dr. Abdelhafid Bouhraoua (Member) Dr. Basem AL-Madani Department Chairman Dr. Salam Zummo Dean of Graduate Studies Date

**Dedicated** to

# the memory of my mother

and

# the memory of my brother Abdul-Lateef

#### ACKNOWLEDGMENT

In the name of God the Merciful

All praises and glory be to Allah (SWT) who gave me everything and I pray that He continues giving me the guidance, the grace and the health during the rest of my life.

I would like to thank the great university; King Fahd University of Petroleum and Minerals for supporting this research and for giving me the opportunity to pursue my graduate studies.

I wish to express my appreciation to my advisor, **Dr. Muhamed Mudawar** for his guidance, support, help, cooperation and constructive feedback. Dr. Mudawar dedicated a lot of his valuable time for me and he always provides me with brilliant ideas. I am also very grateful to my thesis committee members: **Dr. Abdelhafid Bouhraoua and Dr. Aiman El-Maleh** for their help, cooperation, support, guidance and constructive feedback.

I would like to thank my family for their support and encouragement. I am so grateful to my father, my brothers and my sisters.

# **Table of Contents**

| LIST OF TABLES                                              |

|-------------------------------------------------------------|

| LIST OF FIGURES ix                                          |

| THESIS ABSTRACT xi                                          |

| THESIS ABSTRACT (ARABIC) xiii                               |

| CHAPTER 1 INTRODUCTION 1                                    |

| 1.1 Overview 1                                              |

| 1.2 Multithreaded Processors 2                              |

| 1.2.1 The Motivation Behind Having Multithreaded Processors |

| 1.3 PAR ISA 4                                               |

| 1.3.1 Par Instruction                                       |

| 1.3.2 Stop Bit6                                             |

| 1.3.3 Control Instructions                                  |

| 1.4 Thesis Motivation11                                     |

| 1.5 Thesis Organization11                                   |

| CHAPTER 2 LITERATURE REVIEW 12                              |

| 2.1 Multithreaded Processors 12                             |

| 2.2 Vector Processors                                       |

| 2.3 Processors Frontend                                     |

| 4  | 2.4  | Block-Structured ISA         | 22 |

|----|------|------------------------------|----|

| 2  | 2.5  | Simulation                   | 24 |

| 2  | 2.6  | Discussion                   | 26 |

| CH | IAPT | ER 3 PAR CORE HARDWARE MODEL | 29 |

|    | 3.1  | Overview                     | 29 |

|    | 3.2  | Assumptions                  | 31 |

|    | 3.3  | The Multithreading Approach  | 32 |

|    | 3.4  | Why is PAR Core Optimized?   | 33 |

|    | 3.5  | Frontend Structure           | 34 |

|    | 3.6  | How Does the Frontend Work?  | 39 |

|    | 3.7  | Backend Structure            | 44 |

|    | 3.7  | .1 Register File             | 46 |

|    | 3.7  | .2 Predicate Registers       | 47 |

|    | 3.7  | .3 Reorder Buffer (ROB)      | 48 |

|    | 3.7  | .4 Functional Units          | 49 |

|    | 3.7  | .5 Instruction Waiting Queue | 50 |

|    | 3.7  | .6 Decode and Dispatch Logic | 51 |

|    | 3.7  | .7 Issue Logic               | 52 |

|    | 3.7  | .8 Forwarding Network        | 52 |

|    | 3.7  | .9 Write Back Logic          | 55 |

| 3.8  | Hazards                                                     | 56 |

|------|-------------------------------------------------------------|----|

| CHAP | TER 4 PARSIM SIMULATOR                                      | 58 |

| 4.1  | Overview                                                    | 58 |

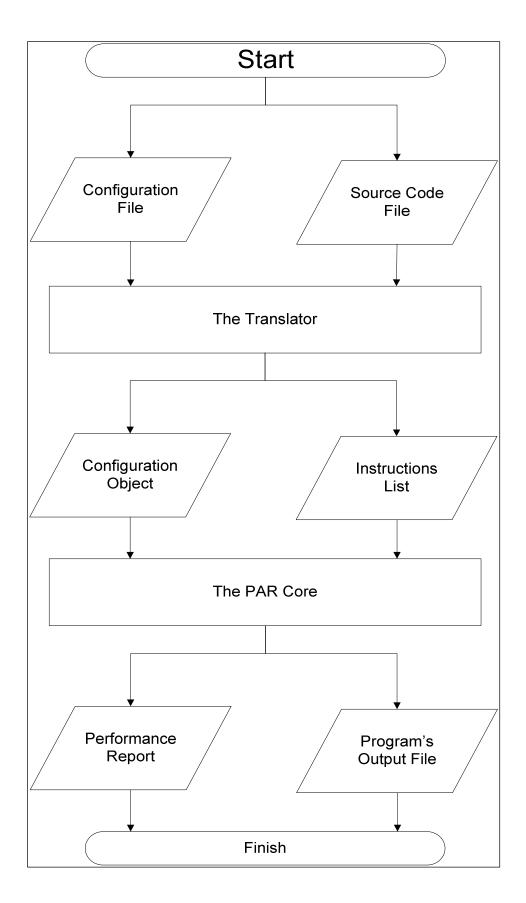

| 4.2  | ParSim Structure                                            | 59 |

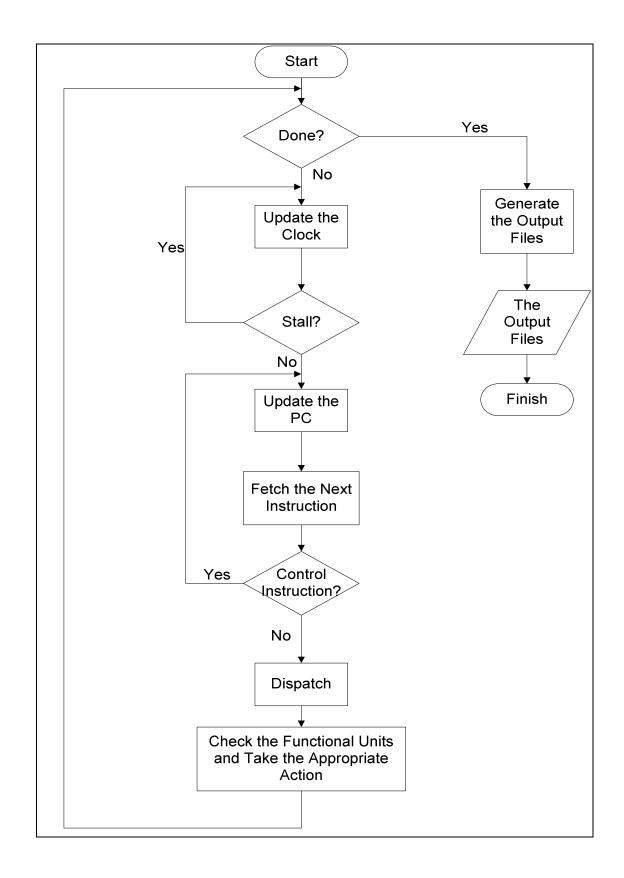

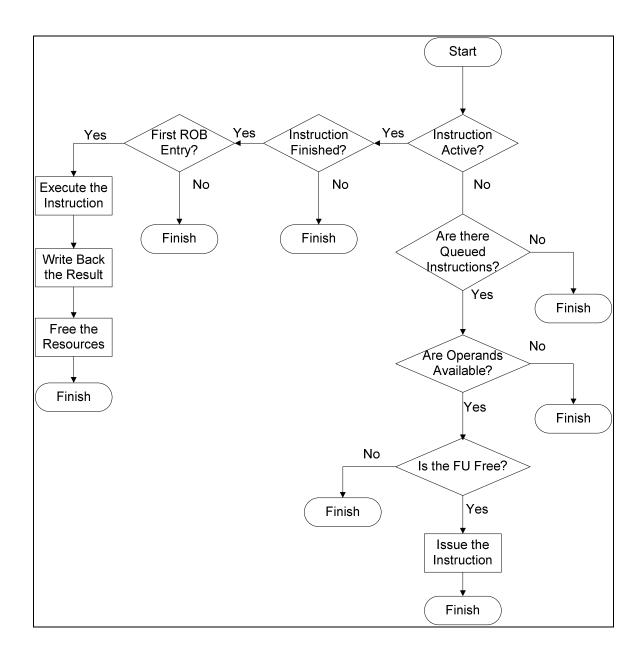

| 4.3  | Simulation Methodology                                      | 59 |

| 4.4  | Performance Metrics                                         | 66 |

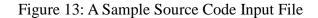

| 4.5  | The Source Code File                                        | 66 |

| 4.6  | The Configuration File                                      | 69 |

| 4.7  | The Performance Statistics Report File                      | 70 |

| 4.8  | Conclusion                                                  | 71 |

| CHAP | TER 5 BENCHMARKS                                            | 73 |

| 5.1  | Overview                                                    | 73 |

| 5.2  | Dense Matrix-Matrix Multiplication (DMMM)                   | 74 |

| 5.3  | Jacobi Iterative Method (JIM)                               | 74 |

| 5.4  | Gauss-Seidel (GS): Red-Black Gauss-Seidel on a 2D Grid [32] | 75 |

| 5.5  | RGB to YIQ Conversion (RGB-YIQ) [33]                        | 76 |

| 5.6  | RGB to CMYK Conversion (RGB-CMYK) [33]                      | 77 |

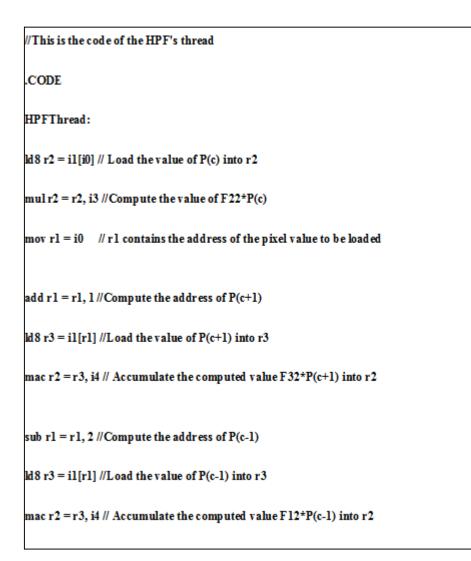

| 5.7  | High Pass Grey-Scale Filter (HPF) [33]                      | 77 |

| 5.8  | Scaled Vector Addition (SVA)                                | 79 |

| CHAP | FER 6   EXPERIMENTAL RESULTS AND DISCUSSION                 | 80 |

| 6.1      | Overview                                 | 30 |

|----------|------------------------------------------|----|

| 6.2      | Analyzing Single Lane Performance        | 31 |

| 6.3      | Analyzing Multiple Lanes Performance     | 35 |

| CHAPT    | ER 7 CONCLUSION AND FUTURE WORK 8        | 38 |

| Appendi  | x A PAR ISA9                             | 90 |

| Appendi  | x B Benchmarks C++ Source Code 11        | 0  |

| Appendi  | ax C Benchmarks PAR Assembly Source Code | 21 |

| Appendi  | x D Experimental Results                 | 13 |

| D.1      | Results for Single Lane                  | 13 |

| D.2      | Results for Multiple Lanes               | 16 |

| Bibliogr | aphy15                                   | 50 |

| Vitae    |                                          | 55 |

# LIST OF TABLES

| Table 1: The Values of the Fixed Parameters               |  |

|-----------------------------------------------------------|--|

| Table 2: DMMM Performance Results for Single Lane         |  |

| Table 3: JIM Performance Results for Single Lane          |  |

| Table 4: GS Performance Results for Single Lane           |  |

| Table 5: RGB-YIQ Performance Results for Single Lane      |  |

| Table 6: RGB-CMYK Performance Results for Single Lane     |  |

| Table 7: HPF Performance Results for Single Lane          |  |

| Table 8: SVA Performance Results for Single Lane          |  |

| Table 9: DMMM Performance Results for Multiple Lanes      |  |

| Table 10: JIM Performance Results for Multiple Lanes      |  |

| Table 11: GS Performance Results for Multiple Lanes       |  |

| Table 12: RGB-YIQ Performance Results for Multiple Lanes  |  |

| Table 13: RGB-CMYK Performance Results for Multiple Lanes |  |

| Table 14: HPF Performance Results for Multiple Lanes      |  |

| Table 15: SVA Performance Results for Multiple Lanes      |  |

# LIST OF FIGURES

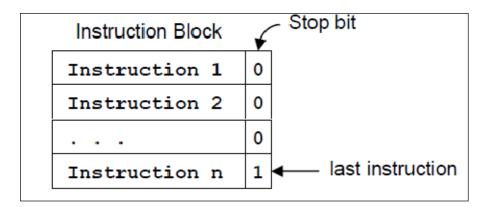

| Figure 1: An Instruction Block is Terminating with a Stop Bit                    | . 5 |

|----------------------------------------------------------------------------------|-----|

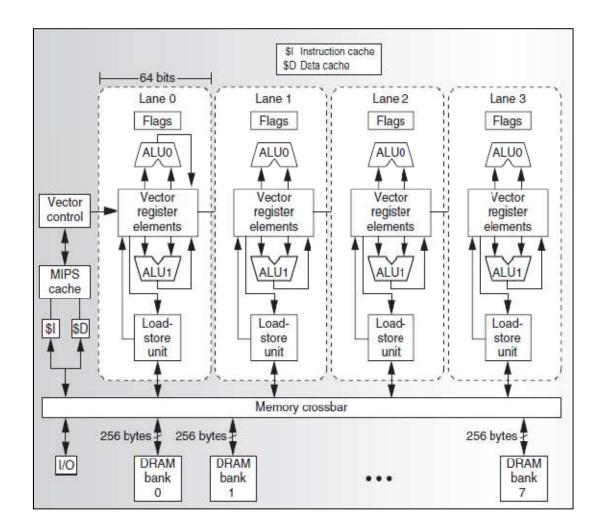

| Figure 2: VIRAM Prototype Processor [17]                                         | 18  |

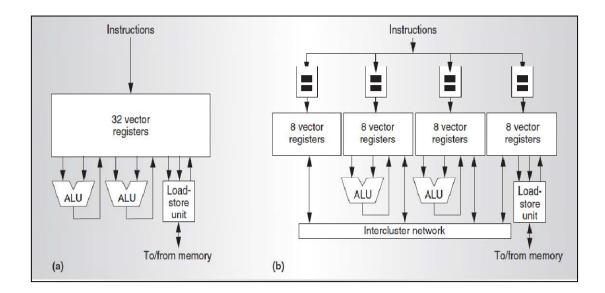

| Figure 3: Vector Lane Organization: Centralized (a) Clustered (b) [17]           | 19  |

| Figure 4: The 32-Bit Basic Block Descriptor Format in BLISS [3]                  | 23  |

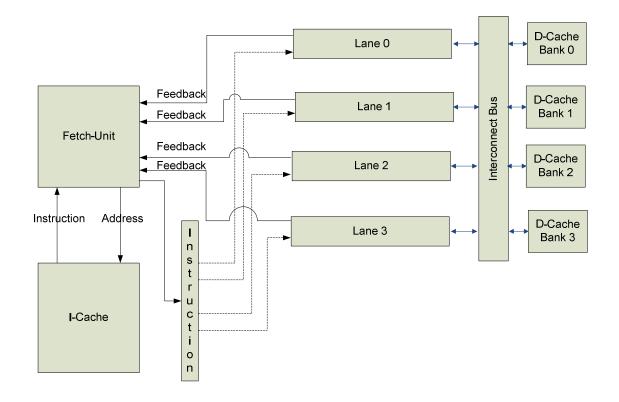

| Figure 5: High Level Block Diagram of PAR Core                                   | 30  |

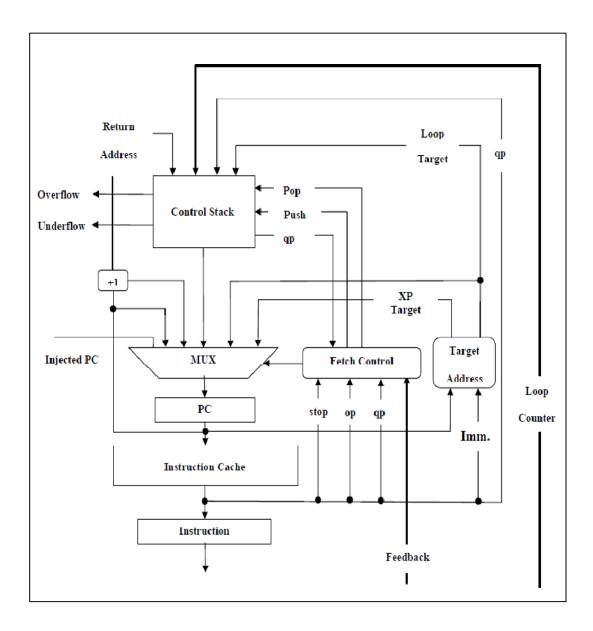

| Figure 6: Block Diagram of PAR Core's Frontend                                   | 36  |

| Figure 7: Block Diagram of PAR Core's Backend                                    | 45  |

| Figure 8: PAR Core's Register File                                               | 46  |

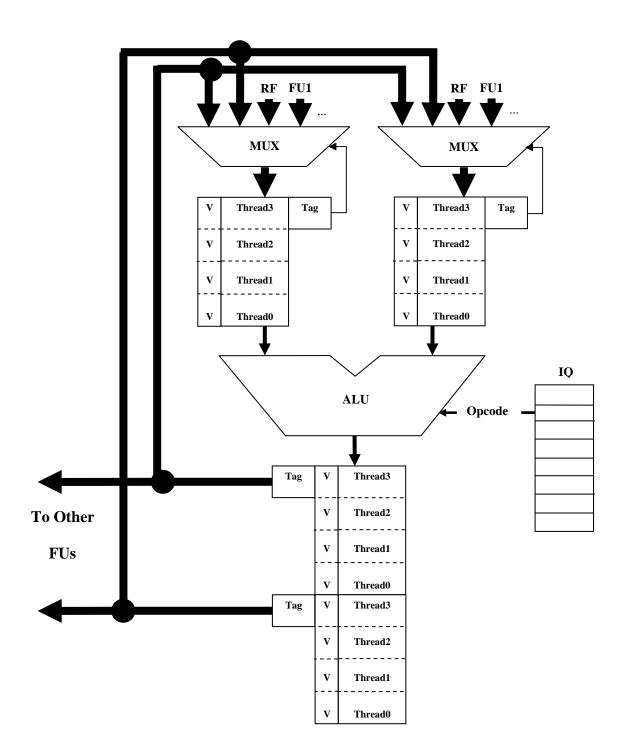

| Figure 9: Forwarding Network for ALU                                             | 54  |

| Figure 10: High Level Flowchart of ParSim                                        | 60  |

| Figure 11: ParSim's Simulation Process                                           | 62  |

| Figure 12: Functional Unit Monitoring Flowchart                                  | 65  |

| Figure 13: A Sample Source Code Input File                                       | 68  |

| Figure 14: A Snapshot of the Configuration File for ParSim                       | 70  |

| Figure 15: A Snapshot from the Performance Statistics Report Generated by ParSim | 71  |

| Figure 16: High Pass Grey-Scale Filter Coefficients [33]                         | 78  |

| Figure 17: High Pass Grey-Scale Filter Equations [33]                            | 78  |

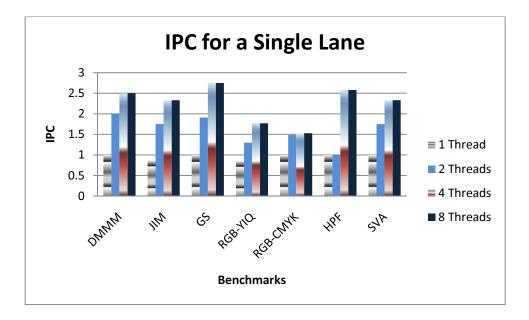

| Figure 18: IPC for a Single Lane                                                 | 82  |

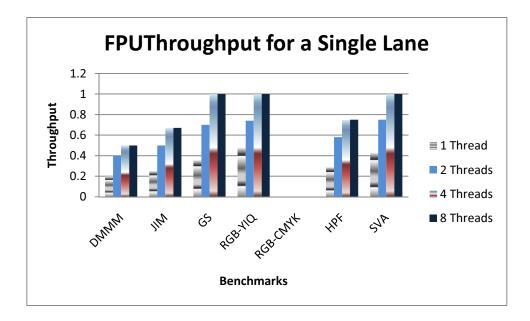

| Figure 19: FPU Throughput for a Single Lane                                      | 83  |

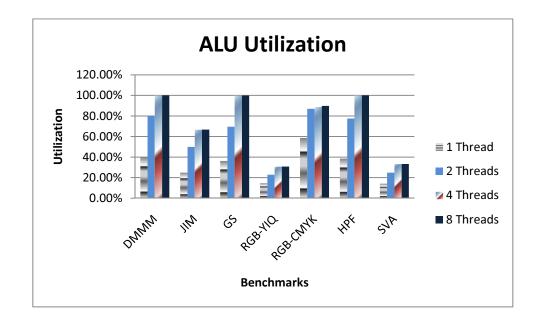

| Figure 20: ALU Utilization                                                       | 84  |

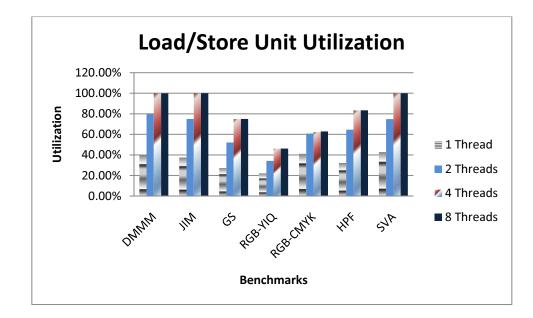

| Figure 21: Load/Store Unit Utilization                                           | 85  |

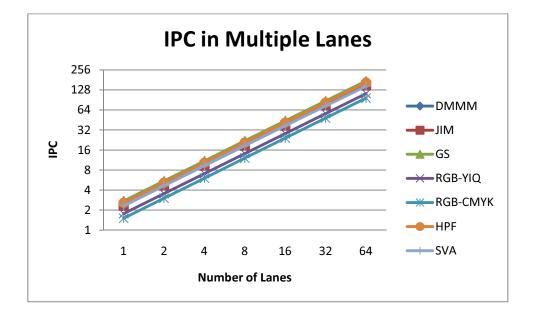

| Figure 22: IPC in Multiple Lanes                           |     |

|------------------------------------------------------------|-----|

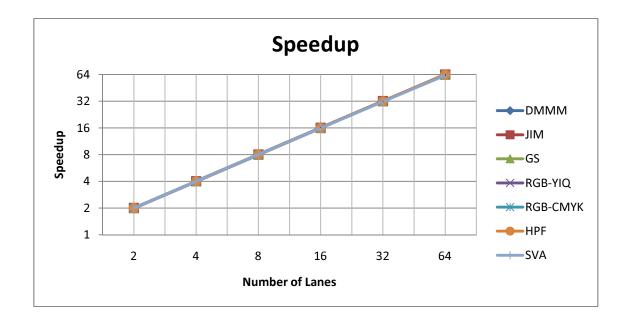

| Figure 23: Speedup across Multiple Lanes                   | 87  |

| Figure 24: Instruction Formats                             |     |

| Figure 25: ALU Instruction Formats                         |     |

| Figure 26: Format of the SET and SLI instructions          |     |

| Figure 27: Integer Multiply and Divide Instruction Formats | 102 |

| Figure 28: R-type and I-type Compare Instruction Formats   | 108 |

| Figure 29: DMMM C++ Source Code                            | 110 |

| Figure 30: JIM C++ Source Code                             | 111 |

| Figure 31: GS C++ Source Code                              | 113 |

| Figure 32: RGB-YIQ C++ Source Code                         | 115 |

| Figure 33: RGB-CMYK C++ Source Code                        | 117 |

| Figure 34: HPF C++ Source Code                             | 119 |

| Figure 35: SVA C++ Source Code                             | 120 |

| Figure 36: DMMM Source Code                                | 122 |

| Figure 37: JIM Source Code                                 | 124 |

| Figure 38: GS Source Code                                  | 127 |

| Figure 39: RGB-YIQ Source Code                             | 130 |

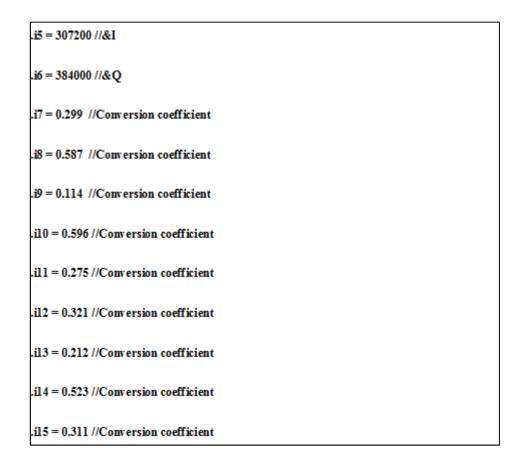

| Figure 40: RGB-CMYK Source Code                            |     |

| Figure 41: HPF Source Code                                 | 137 |

| Figure 42: SVA Source Code                                 |     |

#### **THESIS ABSTRACT**

#### Name: Ayman Ali Mohammad Hroub

Title: Multithreaded Processor Core Optimized for Parallel Thread Execution Major Field: Computer Engineering

### Date of Degree: May 2011

The accelerating improvements in VLSI technology allow adding more and more transistors on a single chip. This has been exploited by computer architects to develop more complex and more efficient processors like superscalar which exploits the instruction level parallelism (ILP) in the applications to handle multiple instructions simultaneously. Some applications like graphics processing and scientific computing are throughput applications and they have a lot of data level parallelism. The complex features such as aggressive branch prediction, multiple instructions issue and out of order execution that exist in many processors like superscalar are not needed for these computing areas. Special purpose processors should be designed for these applications. These processors should be single instruction multiple threads (SIMT) processors such that when an instruction is issued, it is executed for multiple independent threads sequentially.

In this research, I am proposing a processor core called PAR core which is based on the PAR instruction set architecture (PAR ISA) proposed by Dr. Mudawar. PAR core is an SIMT core that receives the workload from the master process in a format called PAR packet which orders the PAR core to execute the same sequence of instructions for a given number of threads specified by the PAR packet.

The simulation results showed that the PAR core has high throughput and high utilization of the hardware resources. The maximum hardware utilization is 100% and the maximum IPC gained is 2.75 instructions/ cycle for a 4-way multithreaded PAR core. Besides that, the simulation results showed that this architecture is completely scalable which means replicating the processing lanes will replicate the throughput. PAR core has been scaled up to 64 processing lanes and the speedup is linear and the maximum IPC is 174.26 instructions/ cycle.

# **THESIS ABSTRACT (ARABIC)**

ملخّص الرسالة

الاسم: أيمن علي محمد حروب

عنوان الرسالة: نواة معالج متعددة النياسب أمثلية للتنفيذ المتوازى للنياسب

التخصص: هندسة الحاسب الآلى

تاريخ التخرّج: أيّار ٢٠١١

لقد استغل معماريو الحاسب الآلي التطوّر المتسارع في تقنية الدوائر المتكاملة عالية الكثافة (VLSI) و المتمثل في زيادة عدد الترانزستورات على الرقاقة الإلكترونية الواحدة في تطوير معالجات أكثر تعقيدا ً و أكثر فعالية مثل معالج (Superscalar) الذي يعتمد على وجود تعليمات متوازية (ILP) في البرامج لكي يتسنّى له معالجة أكثر من تعليمة في آن واحد. بعض التطبيقات كمعالجة الرسوم و الحسابات العلمية هي تطبيقات كثيرة الإنتاجيّة حيث تحتوي على كمية هائلة من التوازي. إنّ المزايا المعقدة كالتنبأ بالتفرّع و إصدار أكثر من أمر معاً و التنفيذ غير المرتّب و الموجودة في العديد من المعالجات مثل (Superscalar) غيرضرورية لهذه التطبيقات. لذا فإن هذه التطبيقات تحتاج إلى معالجات خاصة تصمّم خصصيصا لها. هذه المعالجات الخاصة يجب أن تكون معالجات من نوع تعليمة واحدة و عدة نياسب (SIMT) و الذي يقتضي إصدار تعليمة واحدة و تنفيذها لعدة نياسب بالتعاقب.

إنني أقترح في هذا البحث نواة معالج تسمّى (PAR) و المبنية على مجموعة التعليمات (PAR ISA) التي اقترحها الدكتور مدوّر. تعتبر نواة المعالج (PAR) من نوع (SIMT) و تقوم باستلام العبء من الإجرائية الرئيسية على شكل رزمة تسمّى (PAR Packet) حيث تقوم النّواة (PAR) بتنفيذ البرنامج المرتبط بهذه الرزمة لعدد معيّن من النياسب يتم تحديده في الرزمة (PAR Packet). لقد أظهرت نتائج المحاكاة أن النواة (PAR) نواة عالية الإنتاجية و عالية الاستفادة من مصادر العتاد المادي الموجودة. لقد كانت نسبة الاستفادة من العتاديات المادية ١٠٠% في أحسن الأحوال و كان الحد الأقصى لعدد التعليمات التي يتم تنفيذها في الدورة الزمنية الواحدة ٢,٧٥ تعليمة/الدورة عندما كانت النواة تحتوي على أربعة نياسب. بالإضافة إلى ذلك، أظهرت نتائج المحاكاة أن هذا النوع من العمارة تتضاعف إنتاجيته بتضاعف مصادر العتاد المادي حيث تم زيادة حجم النواة إلى ٢٤ قناة معالجة فكان التسريع خطياً و كان عدد التعليمات التي يتم تنفيذها

# CHAPTER 1 INTRODUCTION

#### **1.1 Overview**

The accelerating improvements in VLSI technology which allow adding more and more transistors on a single chip have been exploited by the computer architects to develop more efficient processors. Adding more transistors means adding more functional units and thus increasing the processor's throughput if these units are utilized properly. The processor throughput is defined as the number of instructions executed per the unit of time. Increasing the processor throughput requires that the processor itself has multiple functional units as well as the architecture should take maximizing the utilization of these resources into consideration.

Moreover, there is an accelerating application demand on more powerful processors because the computer applications like simulation, scientific computing, multimedia processing etc. become more and more complex. The uniprocessor computer cannot fulfill the requirements of these applications because the execution time will be too long. Increasing the efficiency of a uniprocessor will make it more complex and it will be hit with the heat problem. The solution for that is having parallel computers.

The parallel computer is defined as "a collection of processing elements that cooperate and communicate to solve large problems fast" [1]. Parallel computing implies

replicating the processing unit to handle multiple processes concurrently. These parallel processing units may be arranged to communicate together via shared memory or message passing. So there are multiple architectures of parallel computers such that the workload is partitioned into smaller pieces that are assigned to different processing units.

In addition to the ability of parallelizing the execution of an application on multiple processing units, there is an ability to run multiple threads on a single processing pipeline using some multithreading technique. In this thesis, I am proposing an SIMT multithreaded processor core called PAR core to handle multiple independent threads concurrently.

# **1.2 Multithreaded Processors**

There are two approaches for multithreading architecture [2]. (1) The single chip multiprocessor approach which integrates two or more independent processors on a single chip. (2) The multithreaded processor which is able to pursue two or more threads of control in parallel within a single processor pipeline.

The multithreaded processor can be defined as a processor that is able to handle multiple instructions of multiple threads concurrently by multiplexing the functional units in the execution pipeline among these threads. The multithreaded processor pipeline can be single issue or multiple issue. Ungerer et al. [2] indicated that there are three principle multithreading techniques. (1) Interleaved multithreading technique in which one instruction from another thread is fetched and fed to the execution pipeline each clock cycle so this technique is a fine grained cycle-by-cycle multithreading technique. (2) Blocked multithreading technique, it is coarser grained than the first one such that in this technique a thread continues execution until a blocking event occurs like remote memory request, then another ready thread is activated. This technique of multithreading requires implementing some efficient context-switch mechanism. (3) Simultaneous multithreading in which the wide superscalar instruction issue is combined with multithreading such that instructions are simultaneously issued from multiple threads to the execution pipeline.

#### **1.2.1 The Motivation Behind Having Multithreaded Processors**

There were some reasons that pushed the architects to propose this kind of architecture. One of the strongest reasons is to tolerate the memory latency. When a process makes a remote memory request which takes a long time, then this process will be blocked until this request is satisfied. Blocking the process means killing the throughput and the hardware resources utilization. Multithreading solves this problem by switching to another thread and therefore the processor stays busy and productive.

Another reason for having multithreaded processors is the data dependence among the instructions of a single thread. While a long latency instruction is being executed, the subsequent instructions that depend on its result cannot be issued and then some functional units will stay idle which reduces the hardware utilization and the processor's throughput. Multithreading techniques can solve this problem by executing instructions from other threads on these functional units which increases the hardware utilization and the processor's throughput.

It is clear that the motivation behind having multithreaded processors is increasing the functional units' utilization and thus increasing the processor's throughput through filling the unused slots caused by data dependence and remote memory requests with useful work from other threads.

## **1.3 PAR ISA**

The PAR ISA is a block-structured ISA proposed by Dr. Mudawar. The program in this ISA consists of blocks of instructions. The instruction block is defined as a sequence of instructions starting at the target address of a control instruction and ending with an instruction whose stop bit is set. There is no need to store additional information to determine the instruction block end because the stop bit which is a part of the instruction binary format does that. Figure 1 shows an instruction block terminating with a stop bit.

Figure 1: An Instruction Block is Terminating with a Stop Bit

PAR ISA contains all kinds of standard instructions like integer and floating point (FP) arithmetic, logic, memory, compare and control instructions. Appendix A shows the syntax and the format of these instructions. In addition to that, PAR ISA contains the par instruction to run independent threads in parallel. All instructions have a fixed length of 32 bits. These 32 bits are divided into several fields according to the instruction format. Every instruction has a stop bit and a qualifying predicate register (qp). This means that all instructions are predicated such that the instruction will be dropped from the execution pipeline and doesn't change the system status when its qualifying predicate register value is zero. In the subsequent subsections, some of the PAR ISA features such as the par instruction, the stop bit, the control instructions and the control stack will be described.

#### **1.3.1 Par Instruction**

Par instruction is used to spawn a group of independent threads called worker threads that can work in parallel. This instruction appears only within a master thread which runs on a master core. This instruction has the following syntax:

## (qp) par i , target

When this instruction is encountered and its qp is true, then a set of PAR packets is generated. The PAR packet contains the number of threads to be executed, the values of the inherited registers from the master thread and the starting address of the thread program which is specified by the label *target*. The number **i** refers to the inherited registers from 0 to **i**. After the PAR packets are generated, the thread scheduler distributes them on the PAR cores according to the scheduling policy.

## **1.3.2** Stop Bit

As mentioned above, the stop bit is a part of the instruction format to mark the end of an instruction block. This feature is visible to the programmer. The programmer can indicate that a certain instruction is the last instruction in the instruction block by typing the optional hash symbol (#) at the end of the instruction line. When the assembler detects the hash symbol, it knows that this instruction is the last instruction in the block and therefore it sets the stop bit of that instruction and when no hash symbol is detected this means that this instruction is not the last instruction in the block and therefore the stop bit of this instruction is cleared.

The stop bit is beneficial for the following reasons:

- 1. It simplifies the hardware and the software because it eliminates the need to store additional information to track the instruction blocks and no complex action is needed from the compiler to detect the ends of the blocks and to perform further code optimization due the descriptors as in [3].

- 2. It removes the need of having a return instruction to return to the caller after the function execution finishes, so it saves one instruction per function call.

- 3. It offers simpler and more accurate mechanism in pre-fetching instructions from the I-cache to the execution pipeline because the fetch unit can detect the instruction block end.

- 4. The stop bit with the control stack that will be described later helps the fetch unit to detect the thread termination. The thread terminates when the last instruction is reached and the control stack is empty.

- 5. It helps in designing an instruction pre-fetcher to pre-fetch instructions from the main memory to the on chip I-cache since it tells the pre-fetcher where the end of the instruction block is.

### **1.3.3 Control Instructions**

PAR ISA contains five control instructions that control the program's execution flow. These instructions are useful in building an effective and more accurate fetch unit that can feed the execution engine with instructions in a high rate. These instructions include expand, indirect expand, counter-controlled loop, pure conditional loop and break instructions.

#### 1. The Expand Instruction

It is used to expand instruction blocks and it is equivalent to the function call instruction but without having a corresponding return instruction because the stop bit has eliminated this need. The expand instruction syntax is as follows:

#### (qp) xp Label

As any other instruction in PAR ISA, the expand instruction is predicated. If qp is true, then the execution flow should be transferred to the target address specified by the label and when qp is false then the expand instruction is skipped. In addition to its role in the program flow control, the expand instruction can be exploited in implementing instruction pre-fetchers to transfer the instruction blocks from the main memory to the I-Cache ahead of time. This can be done by checking the opcode of the instruction while the instruction block is being fetched and when a control instruction is detected like expand, indirect expand or loop instruction then the next required block will be known ahead of time and it can be pre-fetched. The expand instruction and the other control instructions also guide the fetch unit to update the program counter.

#### 2. The Indirect Expand Instruction

This instruction is used when the target address is known at runtime. The value of the target address is specified indirectly in a general purpose register. The syntax of this instruction is:

#### (qp) xp r

It can be used to address shared libraries that are dynamically linked at runtime, to expand methods indirectly in object-oriented programming languages etc.

#### 3. The Counter-Controlled Loop Instruction

This instruction is used to implement the counter-controlled loops. It has the following syntax:

#### (qp) loop r, L

In this instruction, the loop block at the target address specified by the label is executed at most n times. The number n is specified in a general purpose register **r**. As long as the value of qp is true, the loop instruction block is expanded.

If the loop instruction is not the last instruction of the instruction block, its effect will be loop and continue i.e. after the loop instruction finishes, the execution flow resumes at the next instruction after the loop instruction. However if the loop instruction is the last instruction of the instruction block, then its effect will be loop and return i.e. after the loop finishes, the execution flow resumes at the return address.

#### 4. The Pure Conditional Loop Instruction

It is equivalent to the *while* loop in C++. It has the following syntax:

#### (qp) loop L

When this instruction is encountered, the instruction block at the target address specified by the label is expanded as long as the qp is true.

## 5. The Break Instruction

The effect of this instruction is to terminate the current instruction block prematurely by resuming execution at the return address that is popped off the control stack. The general syntax of this instruction is:

#### (qp) brk n

If n is not specified, the effect of this instruction will be skipping the rest of instructions in the current instruction block and resumes execution from the return address when this instruction is encountered in a non-loop instruction block. However, if it is encountered in a loop instruction block, the effect will be skipping the rest of instructions in the current loop iteration and resuming execution from the next iteration and this is equivalent to the *continue* statement in C++.

If n equals 1 and the break instruction is encountered within a non-loop instruction block, the effect will be skipping the rest of instructions in the current instruction block and its parent block. If it is encountered in a loop instruction block, the effect will be skipping the remaining instructions in the current iteration and the remaining iterations and this is equivalent to the *break* statement in C++.

## **1.4** Thesis Motivation

The existence of data parallel applications that have completely independent fine grained threads motivate to have a multithreaded architecture that issues one instruction and executes it for multiple threads. This kind of architecture increases the processor's throughput.

Besides that, the features of the PAR ISA like the PAR instruction, the PAR packet and the ability to have a simple processor frontend have motivated me to propose the PAR core.

# **1.5** Thesis Organization

This Thesis has been organized in seven chapters. Chapter 2 contains a literature review about the related work to this research. In the literature review, some existing vector processors, multithreaded architectures and fetch mechanisms have been discussed. In chapter 3, the microarchitecture of the PAR core has been described. Chapter 4 describes ParSim simulator which is a cycle accurate multithreaded simulator that has been developed to assess the performance of the PAR core. In chapter 5, the data parallel benchmarks that have been used to measure the PAR core's performance have been discussed. In chapter 6, the experimental results have been displayed and analyzed. Finally chapter 7 describes the conclusion drawn from this research work and it contains the future work activities that extend this research.

# CHAPTER 2 LITERATURE REVIEW

# 2.1 Multithreaded Processors

A multithreaded processor is a processor that can handle more than one instruction from different threads simultaneously. The first multithreaded processors appeared in 1970s and 1980s to solve the problem of remote memory access. From those days until now, many multithreading architectures have been proposed either for general or special purpose computing.

In 1998, El-Kharashi et al. predicted that the multithreaded processors will be the upcoming generation for multimedia chips because the multimedia applications suffer from long latencies as a result of networks contention, frequent memory references and limited communication bandwidth. Having multithreaded processors will tolerate these latencies by switching to another thread whenever some thread faces a long latency operation. El-Kharashi et al. mentioned the motivations of having multithreaded processors such as: hiding latencies, having dynamic task scheduling, it is a further step towards concurrency, to improve multichip behavior, to alleviate the operating system overhead. They also mentioned that the multithreaded processor can be fine-grained and coarse-grained and each class has its pros and cons and it has its own hardware and software requirements. They listed the general hardware requirements for a multithreaded processor and these requirements include: handling multiple contexts, efficient register manipulation, hardware thread scheduler, state replication, additional control circuitry,

handling pipelining, sharing resources, advanced memory management, scalable memory protection, efficient communication and built-in synchronization.

Many ideas have been proposed to increase the performance of multithreaded processors by proposing new multithreaded architectures to make better utilization of the resources, to decrease the hardware complexity or to target a given class of applications like multimedia or scientific computing. In 1999, Zahran and Franklin [4] proposed a speculative multithreaded architecture with dynamic thread resizing at runtime. In this architecture, the threads are extracted from a sequential program by the compiler or by hardware and they are speculatively executed in parallel. In the first step, tasks are generated statically at compile time and later they are resized dynamically at runtime according to the program behavior. Their main contributions are: Hierarchical technique for building threads. A non-sequential scheme to assign threads to the processing elements (PEs) since the sequential scheme has some limitations. A selection scheme to squash threads in case of misprediction. They showed that the dynamic thread resizing approach has 11.6% greater performance than the conventional speculative multithreaded processors.

In 2002, Ungerer et al. surveyed and classified the various multithreading techniques in research and in commercial microprocessors [2]. As I mentioned in chapter 1, they classified the multithreading techniques into Interleaved multithreading technique, blocked multithreading technique and simultaneous multithreading.

Also Ungerer et al. talked about two types of multithreading architectures. (1) Implicit multithreading in which several threads are extracted from a single sequential program with or without the help of the compiler and these threads are executed concurrently. A thread in this architecture refers to any contiguous region of the static or dynamic instruction sequence. In 2003, Park et al. [5] proposed an implicitly-multithreaded processor (IMT) which executes compiler speculative threads from a sequential program on a wide issue SMT pipeline. They showed that IMT outperforms on aggressive superscalar and the two prior proposals TME [6] and DMT [7]. (2) Explicit multithreading in which the processor interleaves the execution of instructions of different threads of control in the same pipeline.

In 2001, IBM introduced Power4-based systems in which two processor cores have been integrated on a single chip. In 2004, they introduced the Power5 processor [8] as a next generation after Power4. Power5 is a dual-core multithreaded processor; its processor core supports both enhanced SMT and single-threaded (ST) operation modes. Power5 provides higher performance in the ST mode than Power4 at equivalent frequencies. Power5 has some enhancements over Power4 processor like dynamic resource balancing, software-controlled thread prioritization and dynamic power management. The multithreading approach in Power5 is two-way SMT on each of the chip's two processor cores.

In 2005, Sun Microsystems developed the Niagara processor [9] which is a multithreaded processor designed to provide high performance for commercial server applications. The Niagara processor is an entirely new implementation of the SPARC V9. This processor supports 32 threads of execution such that these threads are organized in groups of four so the processor has eight thread groups. The threads in each thread group share one processing pipeline and there is a fair thread selection policy such that the least

recently used thread is selected. This kind of architecture helps in hiding the latency of the memory access such that when one thread is stalled because it made a memory request, then another thread is selected. The context switch in Niagara processor has a penalty of zero cycles.

Lindholm et al. [10] described the Tesla architecture that was introduced in 2006 in the GeForce 8800 GPU. Tesla architecture is based on a scalable processor array. GeForce 8800 GPU consists of 128 streaming-processor (SP) cores organized as 16 streaming multiprocessors (SMs). The 16 multithreaded processors are also organized in eight independent processing units called texture/processor clusters (TPCs). Tesla architecture is scalable and it achieves high throughput for the throughput applications which have extensive data parallelism, intensive floating- point arithmetic, modest task parallelism and modest inter-thread synchronization.

The SIMT architecture has been introduced in SM which creates, manages and executes threads in groups of 32 parallel threads called wraps. The threads in the same wrap are of the same type and they start from the same address but during the execution they are free to branch independently.

Tesla SM manages a pool of 24 wraps which have a total number of 768 threads. At each time an instruction is issued, the SIMT multithreaded instruction unit selects a ready wrap and broadcasts the SIMT instruction to the active parallel threads of that wrap. Moreover, Tesla introduced the cooperative thread array (CTA) which is an array of threads that execute the same thread program and can cooperate to compute a result. In 2008, Latorre et al. [11] studied the synergies and trade-offs between the clustering in SMT processors. They proposed a novel resource assignment scheme for the clustered approaches and this scheme improved the performance by 17.6% compared with the Icount and it improved the fairness by 24%.

In 2010, Li et al. [12] adopted the hardware context switch driven by external events in multithreaded processors that are used in IP-Packet processing. The proposed processor has only one hardware context that can support multiple program counters which belong to different threads and there are tags to distinguish among the instructions of different threads in the pipeline. They showed that their proposal improved the overall performance by almost 3.8 times greater than the baseline structure while the area has increased by only 7%.

# 2.2 Vector Processors

Single instruction multiple data (SIMD) is the key aspect of vector processors [13], [14], [15]. In this type of processors, the operands are vectors so there is a need to have vector register file; the same instruction has to be executed on multiple elements of the vector simultaneously.

Kozyrakis et al. [16] proposed a novel micro-architecture called CODE (Clustered Organization for Decoupled Execution) to overcome the following limitations of the conventional vector processors, namely:

- 1. Complexity of multi-ported centralized vector register file VRF: since it stores a large number of vector elements. It supports high bandwidth communication of operands among the vector functional units so it should have large number of ports. To overcome this problem, they proposed the clustered vector register file CLVRS such that each cluster has a partition of the vector register file storing the operands of the local vector functional unit. The number of ports of the CLVRF is independent of the number of clusters and it is five; 2 ports of operands read and one for result write, 2 ports are used for intercluster communication one for input and the other for output.

- 2. The difficulty of implementing precise exceptions for vector instructions.

- 3. The high cost of on-chip vector memory systems.

They claimed that CODE is scalable up to eight functional units and it can hide the latency of off-chip memory access. In the cluster organization they proposed, each cluster consists of a single vector functional unit and a small number of vector registers.

In [17], Kozyrakis et al. talked about scalable vector processors for embedded systems. To demonstrate that vector architectures meet the requirements of embedded media processing, they evaluated the Vector IRAM (VIRAM) architecture using benchmarks from the Embedded Multiprocessor Benchmark Consortium (EEMBC). VIRAM architecture is a complete load-store architecture defined as a coprocessor extension to the MIPS architecture. Vector load and store instructions support the three common access patterns: unit stride, strided, and indexed (scatter/gather). The elements in the VIRAM vector can be 64, 32 or 16 bits wide. VIRAM uses flag registers to support the predicated execution of instructions. Also it implements speculative vectorization of loops with data-dependent exit points. Figure 2 shows VIRAM prototype processor.

Figure 2: VIRAM Prototype Processor [17]

From figure 2, we notice that the processor consists of four lanes. Lanes make the processor scalable in performance, power dissipation and complexity. The drawback of

this architecture is the complexity of VRF partition within each lane, since the number of ports increases as the number of functional units increases. They used clustering to reduce the VRF complexity and improve the performance. Each cluster contains a data path for a single vector functional unit and a few vector registers as shown in figure 3 but they still need an inter-cluster network to communicate among the clusters.

Figure 3: Vector Lane Organization: Centralized (a) Clustered (b) [17]

Krashinsky et al. [18] introduced the thread-vector VT architecture to unify the vector and multithreaded compute models, so the VT architecture is a hybrid of these two models. The VT abstraction provides the programmer with a control processor and a vector of virtual processors VPs. The control processor can broadcast the instructions to the VPs using the vector-fetch or the VP can use thread-fetching to direct its control flow. In this architecture, there are two interacting instruction set architectures: one for the control processor and the other is for the VP.

Each VP has a set of registers and ALUs. VP instructions are grouped in atomic instruction blocks (AIBs). The block must be requested explicitly by the VP or the control processor because there is no automatic program counter or implicit instructions fetch mechanism. They focused on an instantiation of the VT architecture called SCALE. It was designed for high performance and low power consumption for embedded systems.

## 2.3 **Processors Frontend**

Each processor consists of two parts: the frontend and the backend or the execution engine. The frontend job is to feed the backend of instructions to be executed. The appearance of superscalar processors that exploits ILP has placed more pressure on the frontend to provide instructions in a higher rate so as to exploit the hardware resources in the backend. For this reason, many complex frontend architectures have been proposed. These frontends implement pre-fetching mechanisms for higher instruction fetch rates and also they implement branch-prediction mechanisms. Many instruction pre-fetching techniques like [19], [20], [21], [22] have been proposed to increase the instruction fetch rate.

Also some people proposed instruction streaming as a way of providing the execution engine with instructions in a smooth way and some people exploited the block-structured ISA for this purpose. For example, in 2002, Ramirez et al. [23] proposed novel fetch architecture called next stream architecture. This architecture is based on the execution of long streams of sequential instructions exploiting the code layout

optimizations. In this architecture, they focused on simplifying the frontend design while getting a performance that is close to the state-of-art.

The instruction stream is defined as a sequence of instructions from the target of a taken branch to the next taken branch which can contain multiple basic blocks. The instruction stream is identified by the starting instruction address and the stream length. In this architecture, the instruction stream is the unit of fetching and it directly maps to the structures of the high-level programming constructs. These things make the design complexity under control.

For wide issue processors, the next stream predictor performance was 10% higher than the EV8 fetch architecture and 4% higher than the FTB fetch architecture. It was 1.5% slower than the trace cache architecture but with less design complexity.

In 2007, Santana et al. [24] proposed to enlarge these instruction streams to get significant performance in a new mechanism called multiple-stream predictor that combines single frequently executed streams into long virtual streams regardless the type of these single streams. This predictor provides predictions that contain on average 20 instructions. It doesn't need hardware overriding mechanism to hide the branch prediction table access latency.

In 2004, HE et al. [25] proposed an IPC-Based Fetch Policy (IPCBFP) for SMT processors; IPC refers to the number of instructions executed per clock cycle. This policy fetches instructions for any running thread depending on the instantaneous value of the IPC and the number of instructions in the instruction queue for that thread. So this policy should be able to count the number of instructions for each thread in the instruction queue

and to approximate the current value of the IPC for each thread. This policy selects the two threads with the least instructions in the instruction queue and feeds as many as needed number of instructions to every selected thread up to eight in total.

## 2.4 Block-Structured ISA

In the block-structured ISA, the program consists of basic blocks. This kind of architectures appeared in 1990s to increase the instructions fetch rate in the wide issue processors to utilize the ILP and the hardware resources. Hao et al. [26] defined an instance of a block-structured ISA for a wide issue dynamically scheduled processors. They constructed a compiler to generate a block-structured code. They used an optimization technique called block enlargement in which multiple basic blocks are combined together in one larger basic block and they forced the atomic execution of the block to reduce the hardware complexity.

Hao et al. showed that for SPECint95 benchmarks that the block-structured ISA processor executing enlarged atomic blocks outperforms a conventional ISA processor by 12% with less hardware complexity.

In 2006, Zmily et al. [3] proposed a block-aware instruction set architecture called BLISS to address the basic challenges of frontend for wide issue high frequency superscalar processors. BLISS defines basic block descriptors in addition and separately from the actual instructions of each program, so the code segment of each program consists of two sections; the basic block descriptors and the actual instructions of the program. The basic block BB is defined as a sequence of instructions starting at the target or fall-through of a control flow instruction and ending with the next control flow instruction or the next potential branch target.

The descriptor consists of several fields to store sufficient information about the basic block of instructions. Figure 4 shows a 32-bit BB descriptor:

| 4    | 8      | 4      | 13                  | 3     |

|------|--------|--------|---------------------|-------|

| Туре | Offset | Length | Instruction Pointer | Hints |

Figure 4: The 32-Bit Basic Block Descriptor Format in BLISS [3]

The descriptor appearing in figure 4 contains the following fields:

**Type:** The basic block type i.e. type of the terminating branch.

Offset: Displacement of program counter (PC)-relative branches and jumps.

Length: Number of instructions in the BB

Instruction Pointer: The address of the first instruction in the BB

**Hints:** Hints generated by the compiler to help the processor takes some decisions like control-flow predictions and instruction fetch at runtime in a more efficient way. Hints aim at balancing the load overhead between the hardware and the software to simplify the hardware and reduce the power consumption.

The execution of the BB is atomic to simplify the hardware and the software. The naive generated is larger than the assembly code because of adding descriptors. But this code can be highly optimized in multiple ways like removing the jump instructions because they provide no information with the existing of the descriptors. Also the repeated instruction sequences can be removed.

Based on this architecture, Zmily et al. proposed a simple decoupled frontend for the superscalar processor by replacing the branch target buffer with a BB-cache that caches the block descriptors in programs. They demonstrated that BLISS has achieved 20% performance improvement and 14% total energy savings over conventional superscalar design. It also achieved 13% performance improvement and 7% total energy savings over aggressive frontend that dynamically builds fetch blocks in hardware.

# 2.5 Simulation

Simulation is very important for computer architects because it is more flexible and it has low cost. It helps the architect to explore the design space and to find the optimal design. Although the simulators are very helpful, the architects may suffer because in some cases the simulators are very slow and they have poor accuracy. In 2006, Yi et al. [27] surveyed the existing methodologies and techniques for cycle-accurate simulation. They stated that the accuracy is affected by four factors. (1) Simulator's accuracy. (2) The soundness of the simulation methodology. (3) The representativeness of the benchmarks. (4) The simulation technique that is used. Yi et al. classified the simulators that they surveyed into five classes. (1) Singleprocessor performance simulators such as SimpleScalar simulator. (2) Full system simulators like Simics simulator. (3) Single-processor power consumption simulator like Wattch simulator. (4) Multiprocessor performance simulators like Rice Simulator ILP Multiprocessors (RSIM). (5) Modular simulators like Liberty Simulation Environment (LSE).

Yi et al. defined the simulation process as the sequence of steps that the architect must perform to run and analyze the simulation. They divided the simulation process into six steps. (1) Simulator validation and accuracy. In this step, the simulator must be validated before the results can be trusted. (2) Processor enhancement, implementation and verification. (3) Selecting processor and memory parameter values. (4) Selecting benchmarks and input sets. (5) Simulation; in which the benchmarks are run on the configured simulator. (6) Performance analysis. In this final step, the obtained results are analyzed to see the effect of the enhancement.

For some benchmarks, the input data sets are very large and therefore the simulation time is very long. To address this problem, there are several techniques like reducing, truncating and sampling the input sets.

In 2008, Cho et al. [28] proposed a simulation framework called Two-Phase Trace-driven Simulation (TPTS). The motivation was increasing the simulation speed through splitting the detailed timing simulation into two phases. (1) Trace generation phase. (2) Trace simulation phase. In the trace generation phase, they use a filtering

25

technique in order to avoid the need for simulating uninteresting architectural events in the repeated simulation phase.

In 2010, Ubal et al. [29] proposed a simulation framework called Multi2Sim to evaluate multi-core multithreaded processors. They claimed that this simulation framework was intended to cover the limitations of the existing simulators and it models the major components of the incoming systems.

Since developing a cycle-accurate simulator is a complex and timing-consuming task, there are techniques like Architecture Description Languages (ADLs) that are used to provide an abstraction layer for describing the computer architecture and generating simulators for these architectures automatically. In [30], they presented an XML-based ADL that receives the functional description of the architecture in XML format and generates the corresponding multithreaded simulator.

# 2.6 Discussion

In this chapter, I have explored the related work to my research. One of the related architectures to the PAR core is vector architecture. In vector processors, once an instruction is issued, it is executed on a vector of data in parallel; so many functional units are needed, whereas in PAR core the single instruction is executed for multiple threads sequentially on the same functional unit. Also it is possible to replicate the processing lane in PAR core and have higher throughput.

Vector processors need to define vector instructions and vector register file. However, PAR core uses scalar instructions to execute instructions for multiple threads. In addition to that, the frontend of PAR core is more dynamic and more flexible such that the threads can expand and terminate loops independently. Moreover, the vector processor is a standalone processor while PAR core is a part of a larger system which contains master cores to run the master processes. So the PAR core is integrated within a multicore system and it executes the parallel threads assigned from the master core.

In the recent multithreaded processors, NVIDIA TESLA architecture is the closest one to PAR core. The main similarity between them is that both of them are SIMT processors. Moreover, the idea of having multiple multithreaded lanes such that each lane manages a group of threads is similar to thread grouping proposed in Niagara processor. One of the main differences between the two architectures is that the single processing pipeline in Niagara processor supports multiple threads with different instruction streams, whereas the PAR core's lane executes the same sequence of instructions for a number of times equals the number of thread group per lane.

Regarding the frontend complexity, PAR core's frontend is simpler than the previous proposals; it doesn't contain branch prediction and instruction pre-fetchers. There are two reasons that make PAR core's frontend simple. (1) The features of the PAR ISA like the stop bit and the control stack. (2) The nature of the SIMT architecture which doesn't place a pressure on the fetch unit, because once an instruction is issued it does a lot of work so there is no need for a high fetch rate.

Regarding the block-structured ISA, they have been proposed to increase the instructions fetch rate. PAR ISA allows having a high instruction fetch rate but with simpler fetch unit because the need for branch prediction can be eliminated. Also PAR ISA doesn't need to store information about the instruction blocks as in BLISS ISA [3] because of the existence of the stop bit which marks the end of the instruction blocks.

Regarding simulators, ParSim is a cycle-accurate execution-driven simulator. The goal of ParSim was to show the throughput and the scalability of the proposed architecture. My experiments showed that the number of threads specified in a PAR packet doesn't affect the performance results like IPC and speedup if the number of threads exceeds a certain limit. This limit was not large and then if the benchmark has a huge number of threads, then these threads can be truncated and the simulation time will be in minutes or even in seconds.

# CHAPTER 3 PAR CORE HARDWARE MODEL

## 3.1 Overview

PAR core is a multi-lane multithreaded processor core i.e. it consists of multiple lanes such that each lane is multithreaded. This core is intended to receive a PAR packet generated by a master process running on a separate core called the master core and executes the threads specified by this packet simultaneously. The PAR packet's threads are completely independent, so the communication overhead among them is zero and thus the ideal speedup is expected. This kind of threads can be found in data-parallel applications in which the elements of an array or a matrix are processed independently; these applications can be found in multimedia processing and scientific computing areas.

PAR core can be described as a single instruction multiple threads (SIMT) processor since once an instruction is issued, it is executed for multiple threads. This kind of architecture reduces the pressure on the frontend and reduces the hardware cost because it eliminates the need for having a wide issue frontend, branch prediction policies and instructions' pre-fetching.

Figure 5 shows a high level block diagram of the PAR core. From this figure, it is clear that there is only one fetch unit for all lanes because all threads will execute the same instruction. Since the thread program is going to be executed multiple times, may be thousands or millions, the level one instruction cache should be large enough to store all instructions of the thread program. Usually the number of instructions per PAR packet's

thread program is not large, so an instruction cache with reasonable size will be able to store all of these instructions and therefore the instruction cache miss will be zero after brining all of these instructions from the main memory or the lower level cache memory to the first level instruction cache.

Figure 5: High Level Block Diagram of PAR Core

Besides that, PAR core has many characteristics such as it is a single issue, inorder issue and an in-order commitment processor. Despite the fact that different instructions may complete out of order because they have different latencies, their results are written back in order to guarantee the correctness of the program's results. Most of these characteristics make the PAR core simpler in terms of hardware complexity.

## **3.2 Assumptions**

- 1. The level one instruction cache is assumed to be large enough to contain the whole thread program. This assumption is reasonable because the thread program is most probably small enough to fit in an instruction cache with an acceptable size. This assumption results in a zero cache miss rate except the cold start misses. It is necessary to realize this assumption because the thread program will be executed many times, so caching the whole thread program results in higher performance.

- 2. In PAR core, the data cache has been replaced by a memory module called the local memory. Currently, this local memory is treated as a black box and it will be added to the PAR core later. It has been assumed that the local memory miss rate is zero. This assumption can be realized up to certain point thanks to the global load and global store instructions that will be implemented later. Global load and global store instructions are intended to allow data exchange between local memories and the global memory in bulks and they will be implemented in a way to allow communication-computation overlapping.

- 3. For PAR packet's threads that contain counter-controlled loops, it has been assumed that all threads have the same loop counter. This assumption simplifies the hardware because only single counter has to be maintained per counter-controlled loop. This assumption will not prevent threads from having the freedom to exit loops independently.

# 3.3 The Multithreading Approach

PAR core implements two multithreading techniques. (1) The simultaneous multithreading approach in which different independent threads run simultaneously on multiple lanes; but this is different from the traditional SMT technique because in this technique only one instruction is fetched and executed for multiple threads. (2) The interleaving approach which has been implemented within the single lane. Inside each lane, the threads interleave with each other since the instruction is executed multiple times sequentially such that each time it is executed for another thread. This interleaving technique is different from the traditional cycle-by-cycle interleaving technique because in this technique the instruction is fetched, issued only once and it is executed for multiple threads.

Since all instructions including the control instructions are predicated, then it is natural that some threads within the same lane are going to expand and some of them are not, some of threads are going to break a loop and some of them are not etc. So it is important to give each lane this kind of flexibility. To implement that, each lane has a mask register. The width of this register equals the number of simultaneous threads supported by the lane. Each bit in the mask register corresponds to one thread. The mask register plays the role of the top controller of the lane. The thread is active if its corresponding bit in the mask register is true and it is inactive otherwise. For an instruction to write back its result and to affect the state of the system, its corresponding bits in the mask register and the qualifying predicate register must be true.

## 3.4 Why is PAR Core Optimized?

PAR core has many features that make it optimized in terms of performance and hardware complexity. These features are the following:

- There is no context switch overhead. PAR core repeats the execution of the same instruction multiple times, so it doesn't need to switch among different threads of different instruction address spaces.

- Since PAR core is an SIMT, then the functional units' utilization should be high because the issued instruction does a lot of work because it is executed for multiple threads.

- 3. Control instructions' overhead is reduced. The control instructions are predicated and the qualifying predicate register's value may not be ready at the fetching time, so the fetch unit has to stall until the value of the qualifying predicate register becomes ready. Since the instruction is fetched once for multiple threads, then the overhead associated with the control instructions and the fetch unit in general is reduced.

- 4. There is only one and a light weight fetch unit for the PAR core. The fetch unit is light because it has no branch prediction, no wide issue and no instruction prefetching policies.

- 5. The instructions are issued in-order. So the logic needed to maintain out of order execution has been eliminated.

- 6. Since the floating point unit (FPU) is pipelined, running the same FP instruction sequentially for multiple independent threads guarantees that the FPU is highly utilized and the FP instructions' latency is hidden.

- 7. If the load instruction is going to load for multiple threads from the same address, then this load instruction is executed only once and its result is replicated.

- 8. There is no instruction cache miss except the cold start misses, because the level one instruction cache must be large enough to store all instruction blocks of the thread program.

# 3.5 Frontend Structure

The frontend is responsible for providing the execution engine with instructions in a reasonable rate. The reasonable rate is the rate that makes the computing resources in the backend busy. Figure 6 shows a block diagram of the PAR core's frontend. PAR core's frontend is decoupled from the backend. The backend receives instructions from the frontend and provides it with information like the loop counter, the qualifying predicates registers' values, mask register and the stall signal. The feedback port shown in figure 6 abstracts all information sent from the backend to the frontend except the loop counter. In this section, the structure of the frontend will be described. From figure 6, it is noticed that the frontend consists of the following components:

- **1. Instruction cache**: it caches the instructions of the thread program. The instruction cache must be large enough to store all of these instructions because they are going to be executed many times.

- 2. Control Stack: it is used to schedule the execution of the program. It can be split into two independent stacks: the counter control stack which saves the loops' counters and the remaining number of threads to be executed and the command control stack which stores the commands that are used to guide the fetch unit in how the PC should be updated. These commands include:

Figure 6: Block Diagram of PAR Core's Frontend

• The PAR Command: this command entry is pushed on the command control stack upon the reception of the PAR packet. In this entry, the starting address of the thread program is saved. Besides that, a counter entry is pushed on the counter control stack to indicate the number of threads to be executed. Each time the PAR command becomes the top entry of the command control stack, this means that the

end of the thread program has been reached and therefore the top entry of the counter control stack is checked. If the counter value is greater than the number of simultaneous threads supported by PAR core, then it is decremented by the number of simultaneous threads supported by PAR core, say 16 threads if the PAR core has four lanes and each lane is 4-way multithread, and the PC is set to the starting address of the thread program. If the number of simultaneous threads supported by PAR core and the PC is set to the starting address of the thread program. If the number of simultaneous threads supported by PAR core, then the counter is set to zero and the PC is set to the starting address of the thread program. When the PAR command becomes the top command on the command control stack and the corresponding counter is zero, then this indicates that the PAR packet's execution has finished and both stacks are freed.

- The Return Command: this command is used to save the return address and the mask registers. If an expand or a loop instruction is encountered and the stop bit of this instruction is cleared, then the return address and the mask registers are saved within the return command which is pushed on the command control stack.

- The Loop Command: this command is used to schedule the loop instruction execution. If a conditional counter-controlled loop is encountered, then the starting address of the loop block and the qualifying predicate register number are stored within the loop command which is pushed on the command control stack. Regarding the loop counter, it is saved on the counter control stack. If a pure conditional loop instruction is encountered, then it is treated in the same manner as the counter-controlled loop except that in this case there is no counter entry.

There are two fields common among the control commands. (1) The command type field which tells if the command is a PAR, counter-controlled loop, pure conditional loop or a return command. (2) The address field. In PAR command, the address field is the starting address of the thread program. In loop command, it is the starting address of the loop block. Finally, it is the return address in the return command.

Besides that, the return command contains an additional field which stores the mask registers of PAR core's lanes. Also the loop command has a field to store the qp register number of the loop instruction. The control command entry size should equal to the size of the longest command which is the return command.

- **3.** Fetch Control: this component is the heart of the fetch unit, it controls the PC update and it detects the program termination. The PC can be updated in different methods according to the type of the fetched instruction, the stop bit value and the top entry of the command control stack. The following are the different cases of updating the PC:

- The PC is injected from outside within the PAR packet. This PC value is the starting address of the thread program. This is done only once per PAR packet.

- The PC is not updated and this happens when there is a stall.

- The PC is simply incremented and this happens when the fetched instruction is a non-control instruction and its stop bit is cleared.

- The PC is set to the starting address of the thread program and this occurs when the end of the thread program is reached and the number of the remaining threads is non-zero.

- The PC is set to the return address popped off the command control stack. This happens when the execution of an instruction block terminates and the top entry on the command control stack is a return command entry.

- The PC is set to the starting address of the loop block for the first qualified loop iteration and each time the loop block finishes and there is still at least one loop iteration remaining.

#### **3.6 How Does the Frontend Work?**

The frontend contains the fetch unit that fetches instructions from the first level instruction cache and feeds them to the execution engine to be executed, but not all types of instructions are executed by the execution engine. Only the non-control instructions are fed to the execution pipeline and the control instructions are executed in the fetch unit. Before the fetched instruction is sent to the execution engine, it is checked by the fetch control to determine its type and to decide how to update the PC. The fetch control reads the opcode, the stop bit and the qualifying predicate register number of the fetched instruction on the flight while the fetched instruction is being transferred from the instruction cache to the instruction register. Checking the instruction's opcode determines the instruction's type and guided by the stop bit, the qualifying predicate register and the control stack the fetch control decides whether to send the instruction to the execution pipeline or not and decides how to update the PC.

In this section, I will describe the two scenarios of the fetch control behavior. These two scenarios are:

- 1. If the fetched instruction is a non-control instruction, then it is broadcasted to all lanes and the PC is updated according to the value of the instruction's stop bit and the type of the topmost command on the command control stack. If the stop bit is cleared then the PC is simply incremented. If the stop bit is set, then the command and counter control stacks are checked and the PC is updated accordingly. The following are the possible cases in updating the PC when the fetched instruction is a non-control instruction and its stop bit is set:

- a. If the topmost command of the command control stack is a return command, then the PC is set to the return address.

- b. If the topmost command of the command control stack is a counter-controlled loop command, then the qualifying predicate register and the topmost counter on the counter control stack are checked. If the counter is non-zero and the qualifying predicate register value ANDed with the current mask registers is true for at least one thread, then the loop counter is decremented and the PC is set to the loop target address. Nevertheless, if the counter is zero or the qualifying predicate register value ANDed with the current mask registers is false for all threads, then the counter and the loop command entries are popped off the stacks and the PC is updated according to the new topmost command.

- c. If the topmost command on the command control stack is a pure conditional loop command, then the qualifying predicate register is checked. If the qualifying predicate register value ANDed with the current mask registers is true for at least one thread, then the PC is set to the loop target address. Nevertheless, if the qualifying predicate register value ANDed with the current mask registers is false for all threads, then the loop is terminated and the loop command entry is popped off the stack and the PC is updated according to the new topmost command.

- d. If the topmost command on the command control stack is a par command, then the topmost counter on the counter control stack is checked. If the counter is non-zero, then it is decremented by the number of simultaneous threads supported by PAR core and the PC is set to the starting address of the thread program. However, if the counter is zero, then this indicates the termination of the program and the PAR core is freed.

- 2. If the fetched instruction is a control instruction, then it is processed in two stages: the first stage includes fetching it from the instruction cache and checking the opcode, the stop bit and qualifying predicate register and this stage is common among all kinds of instructions. The second stage includes reading the qualifying predicate register associated with it. If the qualifying predicate register value ANDed with the current mask value is false for all threads, then the control instruction is skipped. However, if the qualifying predicate register value ANDed with the current mask value is true at least for one thread, then the control instruction will have an effect and it will change the execution flow of the program.

If the qualifying predicate register value is not ready because it is being produced by another instruction, then the fetch unit has to stall until the qualifying predicate register value becomes ready.

In the rest of this section, I will talk about how the control instructions are implemented in PAR core.

#### a. Direct Expand Instruction (xp)

For each lane, the new mask register's value is calculated by bitwise ANDing the current mask register with the qualifying predicate register of the xp instruction. If the new mask value is true for at least one thread, then the execution flow is transferred to the target address of xp. If the stop bit of this instruction is cleared, the return address and the old mask are saved on the command control stack. However, if the stop bit is set, then nothing is pushed on the command control stack.

The two stages of executing the xp instruction take place in two clock cycles. (1) The instruction is fetched and the PC is updated to the target address. (2) The qualifying predicate register is read and the first instruction of the target block is fetched. If the xp is qualified, then the flow of execution proceeds. If the xp instruction is disqualified, then the fetched instruction is ignored and the PC is updated to the return address popped off the control stack.

### b. Counter-Controlled Loop Instruction

For PAR core, it has been assumed that the value of the loop counter is unified for all threads and it is specified in an inherited register. For each lane, the new mask register's value is calculated by bitwise ANDing the current mask register's value with the qualifying predicate register of the loop instruction. This instruction is qualified if the mask register is true for at least one thread and it is skipped otherwise.

When the loop instruction is qualified, a loop command entry is pushed on the command control stack and a counter entry is pushed on the counter control stack. The command entry specifies that this command is a counter-controlled loop command; it contains the qualifying predicate register number associated with this loop instruction and the starting address of the loop block. The counter entry simply contains the number of the remaining loop iterations.

If the loop instruction's stop bit is cleared i.e. it is in the middle of an instruction block, then its effect is loop and continue. To implement that, a return command is pushed on the command stack before the loop command is pushed. This return command saves the return address and the current mask registers value.

At the end of each loop iteration, the mask register is updated to reflect any possible changes on the qualifying predicate register within the loop body. Besides that, the loop counter is decremented and the PC is set to the starting address of the loop block. The loop continues until the loop counter becomes zero or the mask register becomes false for all threads. When the loop terminates, the loop command and the counter entries are popped off the stacks and the execution resumes at the address specified by the next entry on the command control stack.

#### c. Pure Conditional Loop Instruction

This loop is a pure conditional loop i.e. it is not controlled by a counter. It continues as long as the qualifying predicate register ANDed with the current

mask register is true at least for one thread. This loop is implanted as the counter controlled loop except that it has no counter.

#### d. Break Instruction

The break instruction that has been implemented in PAR core is used to terminate the loop instruction prematurely if its qualifying predicate register is true for all threads. If not all bits of the qualifying predicate register are true, then some threads are going to break and some threads are not going to break. When all threads are going to break, then the loop entries are popped off the control stacks and the PC is updated according to the next command on the command control stack. If not all threads are going to break then the mask register is updated by ANDing it with the bitwise complement of the qualifying predicate register associated with the break instruction.

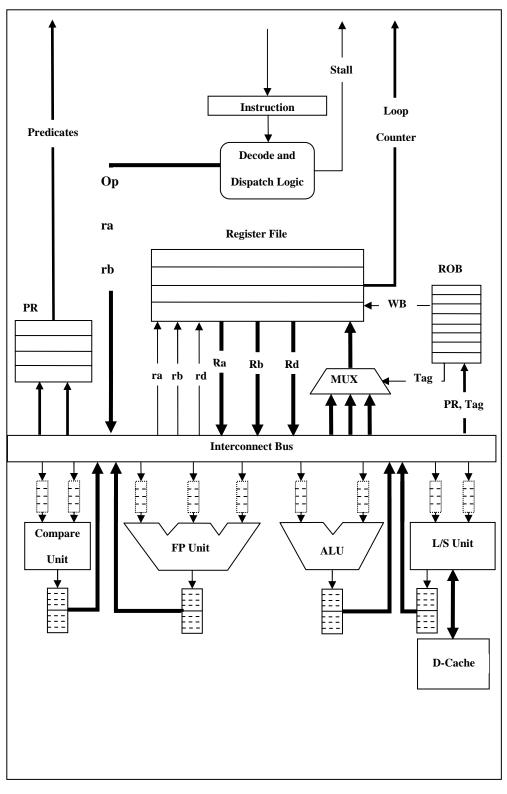

## 3.7 Backend Structure

PAR core pipeline consists of six stages: instruction fetch, decode, dispatch, issue, execute and write back. Once a non-control instruction is fetched, it is sent to the backend for execution. Each lane has the same computational resources which include decode and dispatch logic, issue logic, forwarding network, write back logic, functional units and their instructions' queues, functional units' input buffers, functional units' output buffers, general purpose registers, predicate registers and inherited registers. Figure 7 shows a

block diagram of the execution pipeline for a single PAR core's lane. In this section, the functionality of each component in the backend has been described.

Figure 7: Block Diagram of PAR Core's Backend

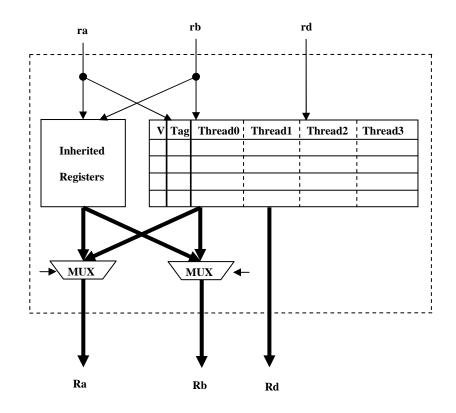

### 3.7.1 Register File

Each lane has a wide general purpose register file such that the width of the register is proportional to the number of simultaneous threads supported by a single lane. Each thread has a register of 64 bits from that wide register as shown in figure 8.

Figure 8: PAR Core's Register File

Besides the general purpose registers, there are inherited registers whose values are inherited from the master thread. The inherited registers are read only. They contain constant values which may represent base addresses, coefficients, loop counters, etc. The inherited register i0 contains the thread index and it is the only inherited register whose value is not constant. This register is updated automatically each time the end of the thread program is reached