# DESIGN AND MODELING OF HIGH SPEED MODULO MULTIPLIERS FOR CRYPTOSYSTEMS

$\mathbf{B}\mathbf{Y}$

Muhammad Yahya Imam Mahmoud

A THESIS PRESENTED TO THE

## **DEANSHIP OF GRADUATE STUDIES**

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE

### **MASTER OF SCIENCE**

IN

COMPUTER ENGINEERING

# KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

May 2004

## KING FAHD UNIVERSITY OF PETROLEUM & MINERALS DHAHRAN 31261, SAUDI ARABIA DEANSHIP OF GRADUATE STUDIES

This thesis, written by Muhammad Yahya Imam Mahmoud

under the direction of his thesis advisor and approved by his thesis committee, has been presented to and accepted by Dean of Graduate Studies, in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE IN COMPUTER ENGINEERING.

Thesis Committee

Dr. Alaaeldin Amin (Advisor)

Prof. Mostafa Abd-El-Barr (Member)

Dr. Muhammad F. Khan (Member)

Prof. Sadiq M. Sait (Department Chairman)

Dr. Mohammad Al-Ohali (Dean of Graduate Studies)

May 2004

## ACKNOWLEDGMENT

Praise be to ALLAH the Lord of the universe who has created mankind and made them into tribes and nations, that they may know each other. Peace be upon the Prophet Muhammad, his family, his companions, and all those who followed him until the day of judgment.

ALLAH said (9-105):

"And say: Work (righteousness): Surly will ALLAH observe your work, so will his messenger, and the believers."

I would like to express my sincere and deepest gratitude to my advisor Dr. Alaaeldin Amin for his constant help, personal attention, inspiring guidance, suggestions, and encouragement throughout the period of this research. I also would like to express my sincere appreciation to Dr. Mostafa Abd-El-Barr and Dr. Muhammad F. Khan who have given me invaluable help and support. I also wish to thank my colleagues at KFUPM for their encouragement and good will wishes.

# **TABLE OF CONTENTS**

| List of Tablesvi                                                                                                                                                                                           | ii                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| List of Figuresvi                                                                                                                                                                                          | iii                             |

| List of Algorithmsx                                                                                                                                                                                        |                                 |

| Thesis Abstractxi                                                                                                                                                                                          | i                               |

| Thesis Abstract (Arabic) ملخص الرسالة xi                                                                                                                                                                   | ii                              |

| CHAPTER 1 Introduction1                                                                                                                                                                                    |                                 |

| 1.1. Background                                                                                                                                                                                            |                                 |

| 1.1.1. Cryptographic Systems                                                                                                                                                                               |                                 |

| 1.1.2. Arithmetic Operations                                                                                                                                                                               |                                 |

| CHAPTER 2 Design and Modeling of Asynchronous Modulo Multiplier                                                                                                                                            | 2                               |

| 2.1. Description of the Asynchronous Algorithm                                                                                                                                                             | 2                               |

|                                                                                                                                                                                                            | 3                               |

| 2.1.1. Initialization Step                                                                                                                                                                                 |                                 |

| 2.1.1. Initialization Step                                                                                                                                                                                 | 5                               |

|                                                                                                                                                                                                            | 5<br>5                          |

| 2.1.2. The Recoding And Adding Step                                                                                                                                                                        | 5<br>5<br>7                     |

| 2.1.2. The Recoding And Adding Step                                                                                                                                                                        | 5<br>5<br>7<br>9                |

| 2.1.2. The Recoding And Adding Step       32         2.1.3. Scaling Step       37         2.1.4. Correction Step       39                                                                                  | 5<br>5<br>7<br>9                |

| 2.1.2. The Recoding And Adding Step       3:         2.1.3. Scaling Step       3:         2.1.4. Correction Step       3:         2.1.5. Illustrative Example       40                                     | 5<br>5<br>7<br>9<br>0           |

| 2.1.2. The Recoding And Adding Step       33         2.1.3. Scaling Step       37         2.1.4. Correction Step       36         2.1.5. Illustrative Example       40         2.2. Design issues       41 | 5<br>5<br>7<br>9<br>0<br>1<br>3 |

| 2.3.1. Hardware Complexity                                               | 55 |

|--------------------------------------------------------------------------|----|

| 2.3.2. Time Complexity                                                   | 55 |

| CHAPTER 3 Montgomery Multiplier (A Complete Solution)                    | 57 |

| 3.1. MONTGOMERY'S MODULAR MULTIPLICATION                                 | 59 |

| 3.1.1. Algorithm Parameters and Notations                                |    |

| 3.1.2. Algorithm Features                                                |    |

| 3.2. Description of the Algorithm                                        | 65 |

| 3.2.1. Approach                                                          |    |

| 3.2.2. Illustrative Example                                              |    |

| 3.3. Design Issues                                                       | 69 |

| 3.3.1. An Optimal Radix-4 Right-To-Left Recoding Algorithm               | 69 |

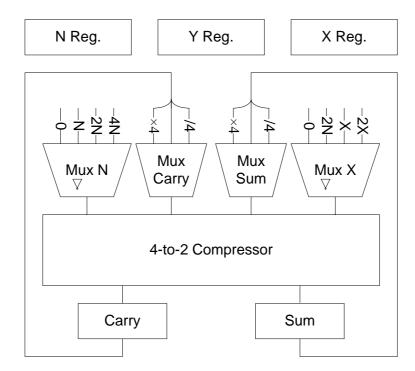

| 3.3.2. N-Multiple Selection For Shift Right Loop                         | 70 |

| 3.3.3. Data Path Design                                                  | 72 |

| 3.4. A Complete Hardware Implementation for Montgomery<br>Multiplication | 75 |

| 3.4.1. Modulus Selection for Shift Left Loop                             | 76 |

| 3.4.2. Illustrative Example                                              | 77 |

| 3.5. Algorithm Complexity                                                | 81 |

| 3.5.1. Hardware Complexity                                               |    |

| 3.5.2. Time Complexity                                                   |    |

| CHAPTER 4 Testing of the Four-to-Two Compressor Array                    | 83 |

| C-Testability for Iterative Logic Array                                  | 84 |

| 4.1.1. Preliminaries                                                     |    |

| 4.1.2. Circuit Hazards                                                   |    |

| 4.1.3. Test Invalidation                                                       | 86  |

|--------------------------------------------------------------------------------|-----|

| 4.1.4. Robustness                                                              | 86  |

| 4.1.5. Fault Models For ILA                                                    | 87  |

| 4.2. A BIST Methodology for ILA.                                               | 89  |

| 4.3. Testability of the 4-2 Compressor                                         | 90  |

| CHAPTER 5 Results and Conclusion                                               | 97  |

| Appendices                                                                     | 102 |

| APPENDIX A : Analysis on Vitit's Multiplication Algorithm                      | 102 |

| A.1. Assumptions                                                               | 102 |

| A.2. Algorithm's Proof                                                         | 102 |

| APPENDIX B : Binary Numbers Recoding Analysis                                  | 105 |

| APPENDIX C : Compressor's Worst-Cass Delay                                     | 108 |

| APPENDIX D : Applying Genetic Evolution Algorithm to Obtain a Good<br>Test Set | 109 |

| References                                                                     | 111 |

# LIST OF TABLES

| TABLE                                                             | Page |

|-------------------------------------------------------------------|------|

| TABLE 1.1: Two's Complement Signed Numbers Multiplication Example | 11   |

| TABLE 1.2: Booth Recoding.                                        | 13   |

| TABLE 1.3: Radix-4 Booth Recoding Algorithm.                      | 14   |

| TABLE 1.4: SRT Division Example                                   | 16   |

| TABLE 1.5: Multiplier Recoding Rule.                              |      |

| TABLE 2.1: Left-to-Right Recoding.                                |      |

| TABLE 2.2: Extreme Cases with the Proper Multiple on N.           |      |

| TABLE 3.1: Mapping Integers to 13-Residue Class                   | 61   |

| TABLE 3.2: Radix 4 Optimal Recoding Algorithm.                    | 69   |

| TABLE 3.3: Modulus Selection for Shift Right Loop.                | 71   |

| TABLE 3.4: Modulus Selection for Shift Left Loop.                 | 76   |

| TABLE 4.1: Genetic Algorithm's Output Test Set.                   | 94   |

| TABLE 4.2: Modified Test Set.                                     | 95   |

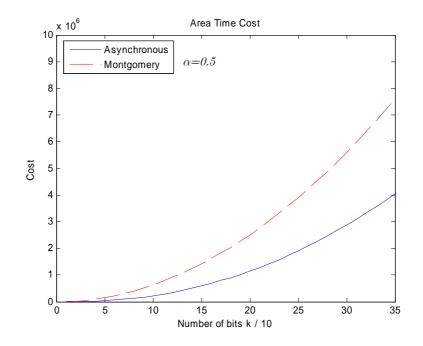

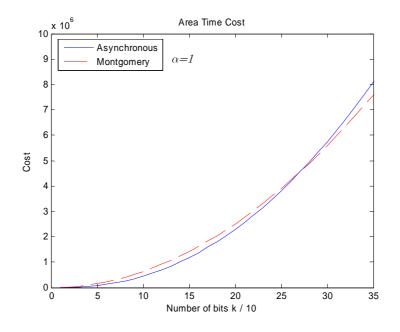

| TABLE 5.1: AT Cost Comparison for the Multiplier Designs.         | 99   |

# LIST OF FIGURES

| Figure                                                          | Page |

|-----------------------------------------------------------------|------|

| Figure 1.1: Symmetric Cryptosystem                              | 3    |

| Figure 1.2: Public-Key Encryption                               | 5    |

| Figure 1.3: Dot Notation for Two 4-word Numbers Multiplication. | 10   |

| Figure 1.4: Multiplier recoding example                         |      |

| Figure 1.5: Illustration of the compared bits.                  | 27   |

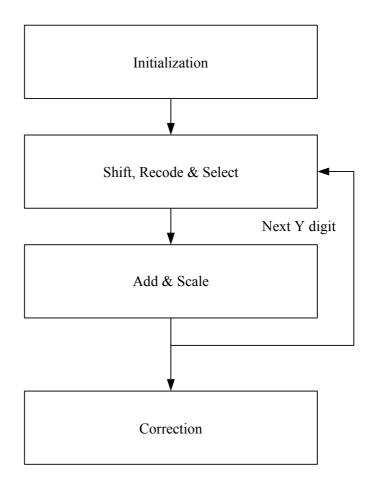

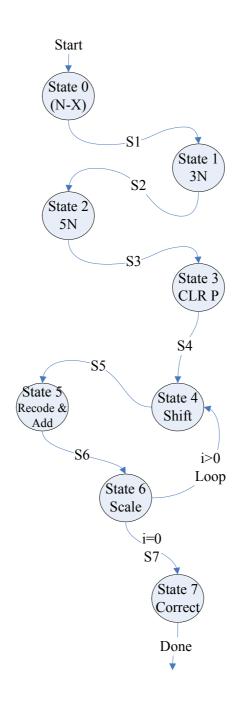

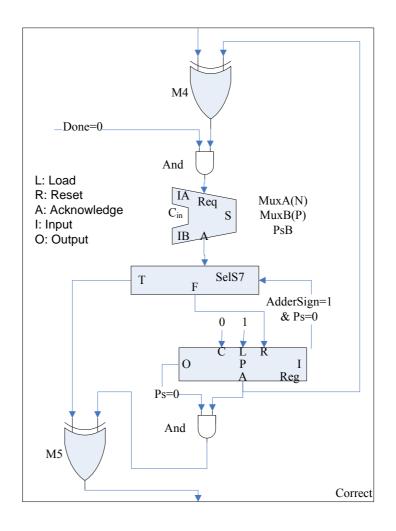

| Figure 2.1: Modular Multiplication Data Flowchart.              |      |

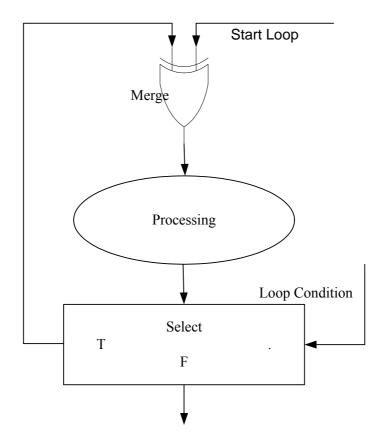

| Figure 2.2: Loop Implementation                                 | 41   |

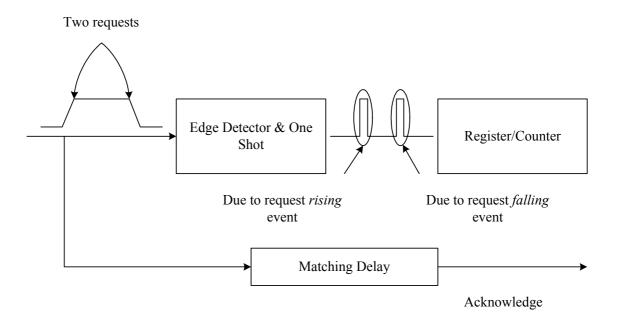

| Figure 2.3: Clock Pulse Generation for Registers/Counter.       |      |

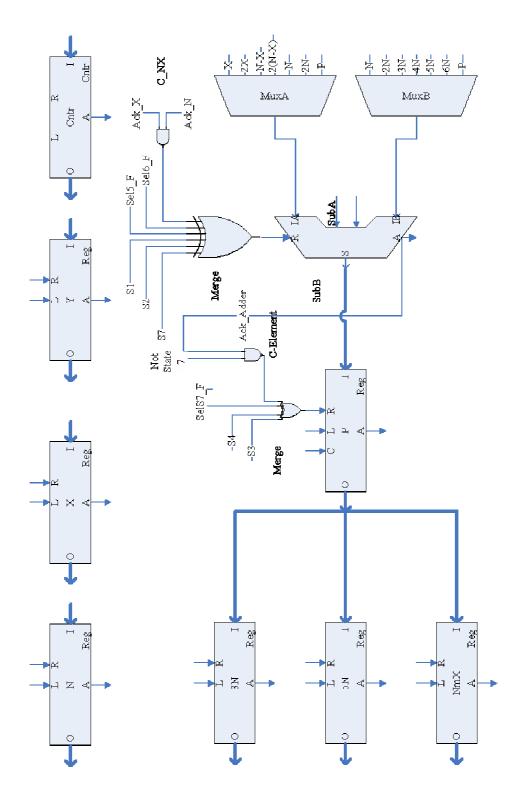

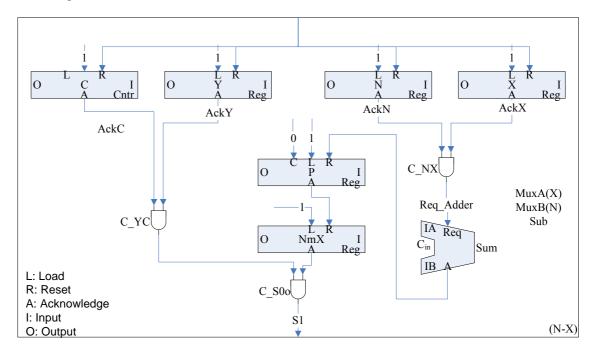

| Figure 2.4: Asynchronous Modulo Multiplier Hardware Data Flow   | 44   |

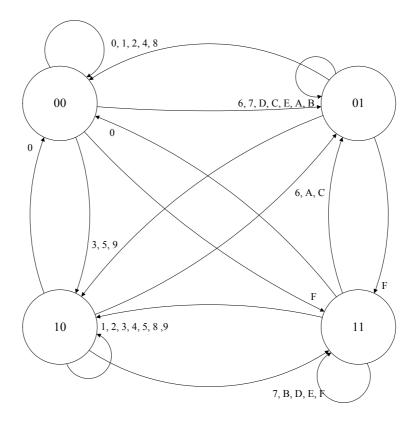

| Figure 2.5: Asynchronous Modulo Multiplier State Diagram        |      |

| Figure 2.6: State 0, Computing N-X.                             | 47   |

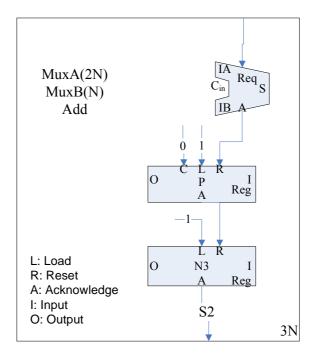

| Figure 2.7: State 1, Computing 3N                               |      |

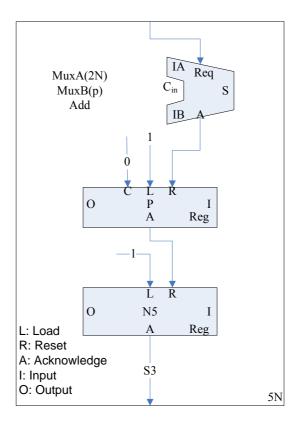

| Figure 2.8: State2, Computing 5N                                |      |

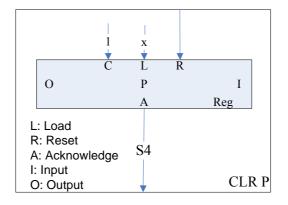

| Figure 2.9: State3, Clearing P                                  |      |

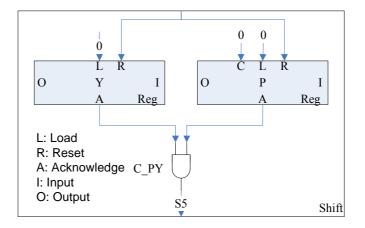

| Figure 2.10: State 4, Shifting P and Y                          | 51   |

| Figure 2.11: State 5, Computing Partial Products.               |      |

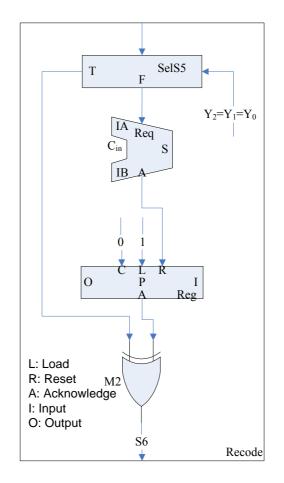

| Figure 2.12: State 6, Scaling & Loop Condition Checking         | 53   |

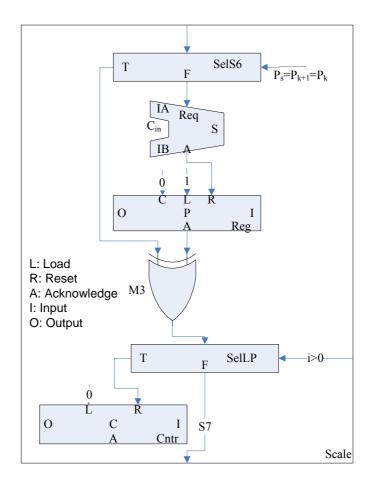

| Figure 2.13: State 7, Correction.                               | 54   |

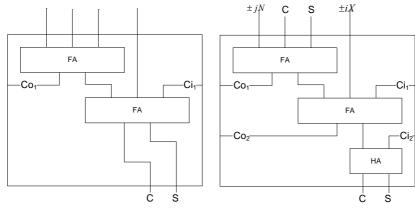

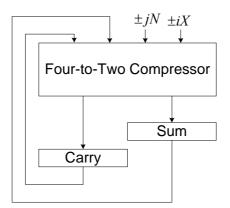

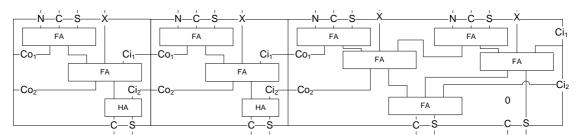

| Figure 3.1: Four-to-Two Compressor Structure.                   |      |

| Figure 3.2: Simultaneous Use of Modulus and Multiplicand        | 65   |

| Figure 3.3: Compressor Multiplier Data Path.                         | 72  |

|----------------------------------------------------------------------|-----|

| Figure 3.4: Four-to-Two Compressor                                   | 73  |

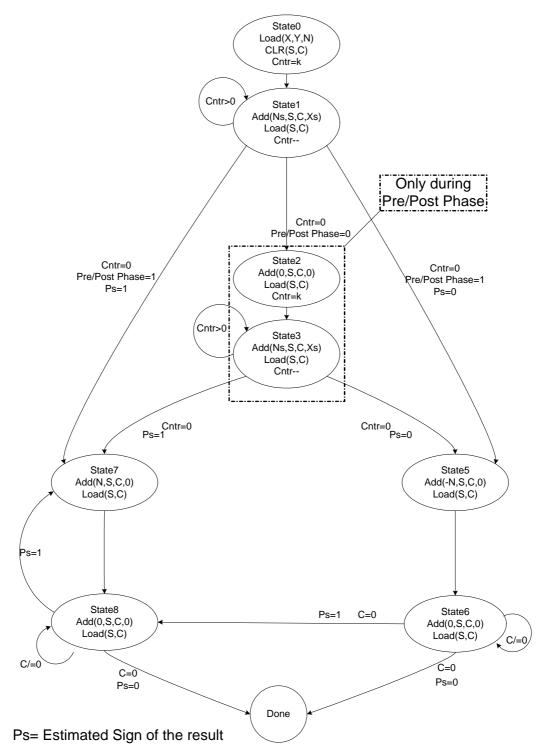

| Figure 3.5: Montgomery Modulo Multiplier State Diagram               | 80  |

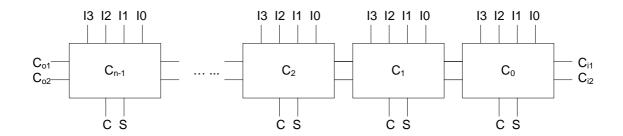

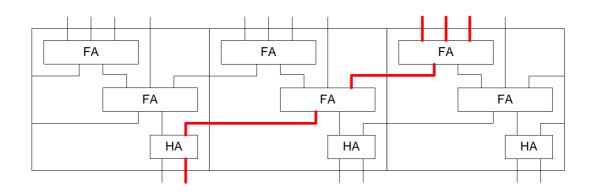

| Figure 4.1: One Dimensional 4-2 Adder ILA.                           | 90  |

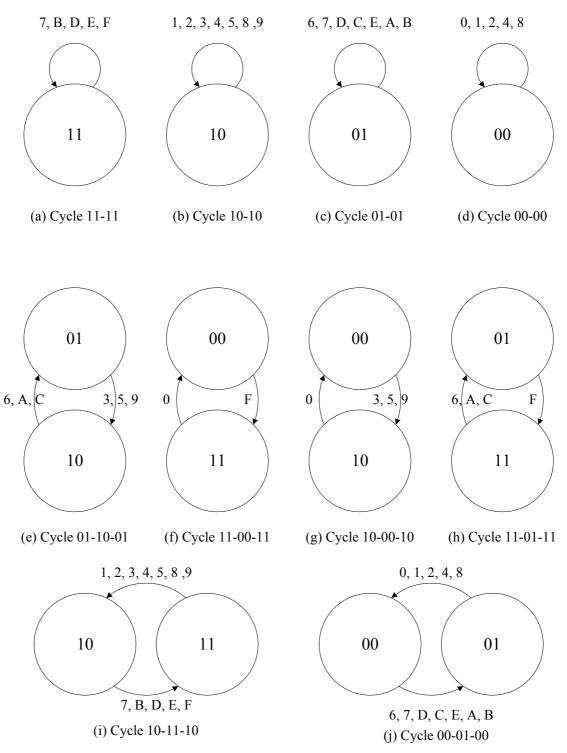

| Figure 4.2: 4-2 Adder's Carry-Out State Diagram.                     | 91  |

| Figure 4.3: Possible Partitioning of the State Diagram 4-2 Adder     | 92  |

| Figure 5.1: Area Delay Cost Comparison for $\alpha = \frac{1}{2}$ .  | 99  |

| Figure 5.2: Area Delay Cost Comparison for $\alpha = 1$              | 100 |

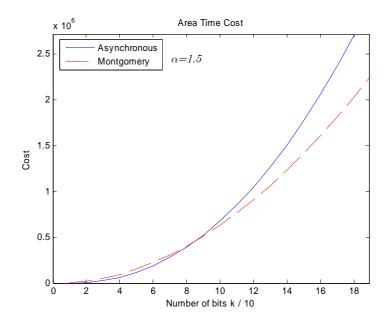

| Figure 5.3: Area Delay Cost Comparison for $\alpha = 1\frac{1}{2}$ . | 100 |

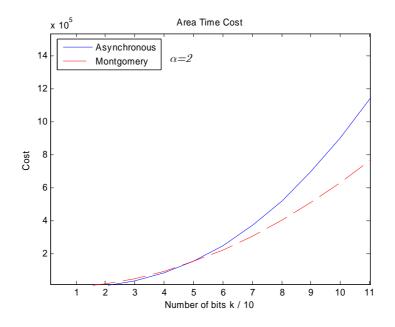

| Figure 5.4: Area Delay Cost Comparison for $\alpha = 2$ .            | 101 |

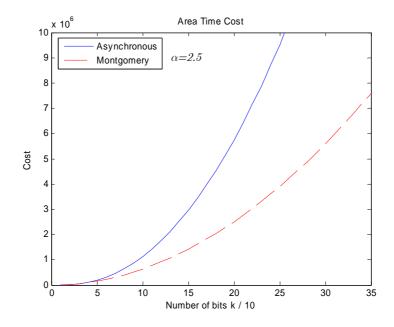

| Figure 5.5: Area Delay Cost Comparison for $\alpha = 2\frac{1}{2}$ . | 101 |

| Figure 5.6: Worst Case Rippling.                                     | 108 |

# LIST OF ALGORITHMS

# Algorithm

| Algorithm 1.1: Exponentiation                               | .20  |

|-------------------------------------------------------------|------|

| Algorithm 1.2: Modular Exponentiation.                      | .21  |

| Algorithm 1.3: Triangle Addition Modular Multiplication     | . 23 |

| Algorithm 1.4: Interleaving Modular Multiplication.         | 24   |

| Algorithm 1.5: Takagi's Radix-4Modular Multiplication.      | .27  |

| Algorithm 1.6: Montgomery Modular Multiplication Algorithm. | . 29 |

| Algorithm 2.1: Asynchronous Modulo Multiplication           | . 34 |

| Algorithm 3.1: Montgomry's Multiplication.                  | . 62 |

| Algorithm 3.2: Modified Montgomery Multiplication           | . 64 |

| Algorithm 3.3: Montgory Modular Multiplication              | . 68 |

| Algorithm 3.4: A Complete Montgory Modular Multiplication.  | . 79 |

### **THESIS ABSTRACT**

#### Name: Muhammad Yahya Imam Mahmoud

Title: Design and Modeling of High Speed Modulo Multipliers for Cryptosystems

Major Field: Computer Engineering

Date of Degree: May 2004

Advances in networking and data processing speeds have led to the need for high-speed *cryptosystems*. The speed of a *cryptosystem* is function of its complexity and the technology used to implement it. This work investigates the techniques of designing *fast modulo multipliers* since *modulo-multiplication* is a basic essential operation in *public-key cryptography*. Two types of *modulo multipliers* have been designed and modeled using VHDL and MatLab. While the first multiplier is based on *asynchronous* adder design, the other multiplier is based on *four-to-two compressor* design. In addition, a **B**uilt In Self Test (BIST) methodology has been developed for the *Compressor* based multiplier designs have been evaluated and compared based on their *area-delay* cost.

## **THESIS ABSTRACT (ARABIC)**

ملخص الرسالة

الاســــــم: محمد يحيى إمام محمود عنوان الرسالة: تصميم ومحاكاة ضاربة باقي القسمة عالية السرعة لأنظمة التشفير . التخصــــص: هندسة الحاسب الآلي

تاريخ التخرج: ربيع ثاني 1425 هـ

أوجد النطور المتزايد في عالم الشبكات ومعالجة البيانات الحاجة لتطوير أنظمة تشفير عالبة السرعة، بينما تعتمد سرعة أي نظام للتشفير على مدى صعوبة وتعقيد النظام المستخدم وعلى التقنية المستخدمة في تصنيعه. ترتكز تقنيات التشفير المعتمدة على المفتاح المعلن على عملية الضرب وباقي القسمة. تستكشف هذه الأطروحة بعض الأساليب المتبعة في تصميم ضاربة باقي القسمة عالية السرعة وتتضمن تصميم ومحاكاة نوعين منها باستخدام اللغة الوصفية لبرمجة مكونات الحاسب الآلي (VHDL) ولغة (MatLab). بينما يعتمد تصميم الضاربة الأولى على المجمّع غير المتزامن، يعتمد التصميم الآخر على المجمع الموفر للانتشار. تضمنت هذه الأطروحة نظام فحص ذاتي للضاربة الأخيرة كما تم تقييم التصميمين بناءً على تكلفة الزمن في المساحة.

## **CHAPTER 1**

### INTRODUCTION

In the information age, the age of public electronic connectivity, as computer systems and their internetworking grow in complexity, the dependence on secure data storage and exchange has become critical. Data security and integrity is threatened by the increased activity of hackers, electronic fraud, and eavesdropping. This has led to a need for protecting and authenticating access to data and their resources. There has been no age where data security and integrity have received as much attention as this age. Military applications, financial transactions, and multimedia communications, are examples that require authentication and data protection algorithms [53].

Public-key cryptosystems, which are based on one way mathematical functions, are becoming very popular because they do not need complex key distribution mechanisms. Based on modulo operations, the RSA [43] and Elgamal [48] encryption algorithms are examples of public-key crypto-algorithms. The speed of a crypto-algorithm and its hardware cost are important performance measures particularly for mobile systems. They are direct function of the algorithm complexity, and the technology used to implement it. Thus, efficient implementation of modular multipliers is essential for the design of efficient high-speed crypto-processors [53].

In this work, two types of modular multiplication algorithms are evaluated and the corresponding hardware is designed and modeled. The first is a self-timed asynchronous

modular multiplier, while the other is a synchronous multiplier that is based on a new fast architecture utilizing a four-to-two compressor. We have used area-delay cost as basis for comparison between the two designs. Furthermore, we have devised a BIST structure for the synchronous design based on a realistic sequential fault model for iterative logic arrays.

The rest of this thesis is organized as follows. In CHAPTER 1, a brief review of essential arithmetic operations is provided, some modular multiplication algorithms are outlined and a brief overview of clocked and event-driven systems is given. CHAPTER 2 describes the design of the proposed asynchronous modulo multiplier. CHAPTER 3 presents a complete design solution for Montgomery modular multiplication. It starts with a review of the algorithm's notation then a hardware implementation of the algorithm is illustrated. In CHAPTER 4, a brief background of hardware testing is given then a Built-In-Self-Test methodology for the compressor modulo multiplier is presented. Finally, the thesis results and conclusion are given in CHAPTER 5.

### **1.1. BACKGROUND**

## 1.1.1. Cryptographic Systems

### 1.1.1.1. Symmetric Cryptosystems (Secret Key)

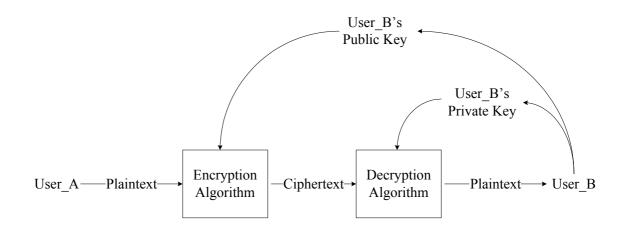

Conventional cryptosystems, also referred to as symmetric or single-key cryptosystems, are based on the use of a common single key and a common algorithm. For the same plaintext message, the algorithm produces different ciphertexts for different keys, see Figure 1.1.

Figure 1.1: Symmetric Cryptosystem.

In conventional cryptosystems, the algorithm should not depend on the input message and should not to be kept secret. Only the key needs to be kept secret and it should be computationally impractical to decrypt the ciphertext knowing only the encryption/decryption algorithm together with samples of plaintext and their corresponding ciphertext [53].

Since, in this method, both the sender and the receiver have the same key, which must be kept secret, There should be a secure key distribution mechanism. Good key distribution mechanisms are not trivial and are not without disadvantages [53].

#### 1.1.1.2. Public-key Cryptosystems

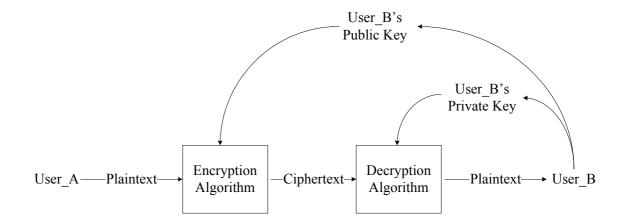

Unlike symmetric cryptosystems, public-key cryptosystems do not use the same key to encrypt and decrypt messages. Instead, each of the two parties has two different but related keys, a public key (KU) and a private key (KR) and they consider a message as consisting of a number of blocks where every message block M has a binary value that is less than some value N (known to both ends). Encryption and decryption algorithms used for public-key cryptosystems are mainly based on modulo operations.

For USER\_A to send an encrypted message to USER\_B, he must use USER\_B's public-key. This message cannot be decrypted without USER\_B's private key that is known only to USER\_B. Figure 1.2 shows an illustration of the public-key cryptography principle.

Figure 1.2: Public-Key Encryption.

For any public-key algorithm, the following equations must hold whenever User\_A needs to send an encrypted message to User\_B:

$Ciphered = E_{KU_B} (Message)$  $Message = D_{KR_B} (Ciphered)$  $= D_{KR_B} [E_{KU_B} (Message)]$  $= E_{KU B} [D_{KR B} (Message)]$

Where *E* and *D* are the encryption and decryption algorithms respectively.

It should be computationally infeasible to infer the decryption key or the original message given only the algorithm, the encryption key and samples of ciphertexts [29] [53].

Encryption algorithms can be implemented using software or hardware. Whereas software implementations are less expensive, easier to modify, and slow, hardware implementations are more expensive, difficult to modify but are quite faster.

Hardware implementations are evaluated based on their running time (speed), VLSI area, and power dissipation. A practical complexity measure for fast mobile cryptosystems is the area-delay product (AT) [49].

1.1.1.2.1. **RSA Algorithm.** One of the most commonly used public-key cryptosystems is the RSA algorithm. The RSA algorithm was devised by Rivest, Shamir, and Adleman [43]. If M is the message to be encrypted and C is the ciphered message, the RSA algorithm is based on the following three requirements:

- Finding integers e, d, and N such that  $M = M^{ed} \mod N$ .

- It should be easy to compute M<sup>e</sup> and C<sup>d</sup>.

- It should be almost impossible to find *d* knowing only *e* and *N*.

Usually N is a large difficult to factor integer and the message block M is such that  $0 \le M \le N$ . The ciphertext C is computed as follows:

$$C = M^e \mod N$$

The plaintext message can be retrieved back using the decryption key d as follows:

$$M = C^d \mod N = (M^e)^d \mod N = M^{ed} \mod N$$

Both the sender and the receiver know N, and e, while only the receiver knows d and the keys are represented as:

$$KU = \{e, N\}, KR = \{d, N\}$$

To satisfy the algorithm requirements, the modulus *N* is defined as the product of two prime numbers *p*, *q* (*N*=*pq*). Therefore  $\Phi(pq) = (p-1)(q-1)$  where  $\Phi(x)$  is the number of positive integers which are smaller than *x* and are relatively prime to *x*. The decryption key *d* is computed as: [43] [53].

$$gcd(\Phi(N), d) = l$$

and  $l < d < \Phi(N)$ , and  $e \equiv d^{-l} \mod \Phi(N)$

1.1.1.2.2. <u>The Elgamal Algorithm.</u> In this algorithm [48], the system has two public keys; N and g, where N is a large prime and N-1 has at least one large prime factor, and g is a primitive element mod N. Each party has its own private key KR\_x ( $1 < KR_x < N-1$ ) and its public key KU x that can be computed from the private key as follows:

$$KU_x = g^{KR_x} \mod N$$

For USER\_A to send a message M ( $0 \le M < N$ ) to USER\_B, he should first choose some random number U ( $0 \le U \le N$ ), then a transaction key K is computed using USER B's Public key (KU b).

$$K = KU \ b^U \mod N$$

The ciphered message is then computed as a pair  $C = (c_1, c_2)$  where

$$c_1 = g^U \mod N \qquad \& \qquad c_2 = KM \mod N$$

Note that the size of the encrypted message is double the size of the original message.

USER\_B can decrypt the ciphered message C by first retrieving the transaction key K. This should be easy for USER\_B since

$$K \equiv KU\_b^U \equiv (g^{KR\_b})^U \equiv (g^U)^{KR\_b} \equiv c_1^{KR\_b} \mod N$$

Then the original message M will be easily retrieved by dividing  $c_2$  by K.

$$M = c_2 / K$$

For increased security the transaction key *K* should not be used for more than one message block. Otherwise, the knowledge of one block allows attackers to know all other blocks [15] [21] [29] [33] [48].

## 1.1.2. Arithmetic Operations

In this section, after reviewing several multiplication schemes, some division algorithms are also discussed. In addition, the exponentiation operation is described. Finally several modulo multiplication algorithms are outlined.

#### 1.1.2.1. Multiplication Algorithms

Three types of multiplication algorithms are reviewed in this section. First, the sequential multiplication for two's complement singed numbers is described. Then, Booth multiplication algorithm which is based on multiplier recoding is presented. The third algorithm is a high-radix version of Booth multiplication algorithm.

1.1.2.1.1. <u>Sequential Multiplication.</u> If X and A are two k-digit numbers, their product P will be 2k-digits long. Let the multiplier X and the multiplicand A be represented as:

$X = x_{k-1} x_{k-2} \dots x_1 x_0$

$A = a_{k-1} a_{k-2} \dots a_1 a_0$

Where  $x_i$  and  $a_i$  are digits in a number system of radix  $\beta$ .

For unsigned numbers, the product *P* requires *k* steps to obtain. In step *i*, the product  $Ax_i$  is shifted and cumulatively added to the partial product P.

$$X = \sum_{i=0}^{k-1} x_i \beta^i.$$

$$P = X \cdot A$$

$$= A * \sum_{i=0}^{k-1} x_i \beta^i.$$

$$= A x_0 \beta^0 + A x_1 \beta^1 + A x_2 \beta^2 + \dots + A x_{k-1} \beta^{k-1}$$

This multiplication is illustrated in Figure 1.3 using dot notation for two 4-digit numbers [4].

$$A$$

$$X$$

$$PP_{0} = Ax_{0}\beta^{0}.$$

$$PP_{1} = Ax_{1}\beta^{1}.$$

$$PP_{2} = Ax_{2}\beta^{2}.$$

$$PP_{3} = Ax_{3}\beta^{3}.$$

$$P = PP_{0} + PP_{1} + PP_{2} + PP_{3}$$

Figure 1.3: Dot Notation for Two 4-word Numbers Multiplication.

In the case of signed numbers,  $x_{k-1}$ ,  $a_{k-1}$  are the sign bits. The product *P* requires *k* steps to obtain. In step *i*, the product  $Ax_i$  is shifted and added to the partial product *P*. The multiplication algorithm can be expressed using the following recursion:

$$X = -x_{k-1} \cdot \beta^{k-1} + \sum_{i=0}^{k-2} x_i \cdot \beta^i$$

$P = X \cdot A$

$$P = -x_{k-1} \cdot \beta^{k-1} \cdot A + \sum_{i=0}^{k-2} x_i \beta^i \cdot A.$$

The following example (see TABLE 1.1) illustrates the multiplication algorithm for binary signed numbers in two's complement representation.

TABLE 1.1: Two's Complement Signed Numbers Multiplication Example.

| А                                                     |   | 00101        |      | 5   |

|-------------------------------------------------------|---|--------------|------|-----|

| Х                                                     |   | 11011        |      | -5  |

| P <sup>(0)</sup> =0                                   |   | 00000        |      |     |

| $X_0=1 \rightarrow add A$                             | + | 00101        |      |     |

|                                                       |   | 00101        |      |     |

| Shift $\rightarrow P^{(1)}=$                          |   | 00010        | 1    |     |

| $X_1=1 \rightarrow add A$                             | + | <u>00101</u> |      |     |

|                                                       |   | 00111        | 1    |     |

| Shift $\rightarrow P^{(2)}=$                          |   | 00011        | 11   |     |

| $X_2=0 \rightarrow \text{Shift} \rightarrow P^{(3)}=$ |   | 00001        | 111  |     |

| $X_3=1 \rightarrow add A$                             | + | 00101        |      |     |

|                                                       |   | 00110        | 111  |     |

| Shift $\rightarrow$ P <sup>(4)</sup> =                |   | 00011        | 0111 |     |

| $X_{sign}=1 \rightarrow add -A$                       | + | <u>11011</u> |      |     |

| P=                                                    |   | 11110        | 0111 | -25 |

To speed up the multiplication process we can do one of the following:

- Use faster adders using:

- o Faster Architecture.

- o Faster technology.

- Reduce the number of partial products

- Using high radix multipliers (scanning more than one multiplier bit at a time)

- o Using Multiplier Recoding techniques.

1.1.2.1.2. **Booth Multiplication.** In Booth multiplication, the number of partial products is reduced using multiplier recoding technique. The multiplication process consists of add and shift operations with addition requiring much more time than the shift operation. The objective is to recode the multiplier bits such that it has less number of ones and more zeros, which reduces the required number of add operations. This can be achieved by skipping chains of zeros and recoding chains of ones [4]. Booth multiplier recoding is illustrated in TABLE 1.2.

### **Example**

Both recoding of  $(1 \ 1 \ 0 \ 0 \ 1 \ 1 \ 1 \ 0)$  is  $(1 \ 0 \ \overline{1} \ 0 \ 1 \ 0 \ \overline{1} \ 0)$

| ĺ | Current Bit | Previous Bit     | Recoded Bit    |                             |

|---|-------------|------------------|----------------|-----------------------------|

|   | $X_i$       | X <sub>i-1</sub> | Y <sub>i</sub> | Note                        |

|   | 0           | 0                | 0              | No string of ones in sight  |

|   | 0           | 1                | 1              | End of string of ones       |

| ľ | 1           | 0                | Ī              | Beginning of string of ones |

|   | 1           | 1                | 0              | Middle of string of ones    |

**TABLE 1.2: Booth Recoding.**

1.1.2.1.3. High Radix Booth Multiplication. Booth algorithm has two disadvantages. The first one is that the number of shifts is not constant. Therefore, the algorithm can not be useful for synchronous systems. The second disadvantage is that the algorithm will give worst results for multipliers that have many isolated ones. For example, if we try to recode 001010101(0), which has four ones (add operations), we will get  $1 \overline{1} 1 \overline{1} 1 \overline{1} 1 \overline{1} 1 \overline{1}$ , which has eight ones. To overcome the latter problem, higher radix Booth recoding can be used.

TABLE 1.3 illustrates radix-four Booth recoding in which two bits are recoded at a time.

| Current                         | Previous         | Recoded          |                                                |

|---------------------------------|------------------|------------------|------------------------------------------------|

| Bits                            | Bit              | Bits             | Note                                           |

| X <sub>i+1</sub> X <sub>i</sub> | X <sub>i-1</sub> | $Y_{i\!+\!1}Y_i$ |                                                |

| 0 0                             | 0                | 0 0              | No string of ones in sight                     |

| 0 0                             | 1                | 01               | End of string of ones                          |

| 0 1                             | 0                | 01               | One between Zeros                              |

| 0 1                             | 1                | 10               | End of string of ones                          |

| 10                              | 0                | $\overline{1}$ 0 | Beginning of string of ones                    |

| 10                              | 1                | 0 1              | End of string of ones and starting of another. |

| 11                              | 0                | 0 1              | Beginning of string of ones                    |

| 11                              | 1                | 0 0              | Middle of string of ones                       |

TABLE 1.3: Radix-4 Booth Recoding Algorithm.

For more on binary numbers recoding see APPENDIX B.

Fast multiplication can also be achieved in a number of other ways, such as tree multiplication and array multiplication [4].

#### 1.1.2.2. Division Algorithms

Division is the most complex of the four basic arithmetic operations. Unlike the other three arithmetic operations, the result of division consists of two components; a quotient Q and a remainder R. Therefore, the result of dividing some dividend X by a divisor D consists of a quotient Q and a remainder R such that  $X=Q\cdot D+R$  where |R| < |D|.

1.1.2.2.1. <u>SRT Division.</u> In non-restoring binary division the divisor D is a normalized fraction. The quotient is computed digit by digit starting with the most significant digit. In is in a form of binary singed digits  $q_i$  i.e.,  $q_i \in \{-1, 0, 1\}$ . the remainder is computed using the following recurrence:

$$r_i = 2r_{i-1} - q_i D$$

Where:

$$\begin{split} r_0 &= X \\ q_i &= \begin{cases} 1 & & \text{if } 2\mathbf{r}_{\mathbf{i}\cdot\mathbf{1}} \; \geq \; 0 \\ \\ \bar{\mathbf{1}} & & \text{if } 2\mathbf{r}_{\mathbf{i}\cdot\mathbf{1}} \; < \; 0 \end{cases} \end{split}$$

The selection criteria can be modified to perform the comparison with D as:

$$q_{_{i}} = \begin{cases} 1 & \qquad \text{if } 2\mathbf{r}_{_{i-1}} \ \geq \ \mathbf{D} \\ 0 & \qquad \text{if } -\mathbf{D} \ \leq \ 2\mathbf{r}_{_{i-1}} \ < \ \mathbf{D} \\ \overline{1} & \qquad \text{if } 2\mathbf{r}_{_{i-1}} \ < \ -\mathbf{D} \end{cases}$$

However, this selection criterion requires full precision comparison of  $r_{i-1}$  and D. We can overcome this costly comparison by restricting D to be normalized fraction, and the comparison needed will be with  $\pm 1/2$  instead of  $\pm D$ . Therefore, all numbers will be presented as fractions and the new quotient selection mechanism is given by

$$q_{i} = \begin{cases} 1 & \text{if } 2\mathbf{r}_{\mathbf{i}\cdot\mathbf{1}} \geq 1/2 \\ 0 & \text{if } -1/2 \leq 2\mathbf{r}_{\mathbf{i}\cdot\mathbf{1}} < 1/2 \\ \overline{1} & \text{if } 2\mathbf{r}_{\mathbf{i}\cdot\mathbf{1}} < -1/2 \end{cases}$$

This is known as SRT algorithm after its three authors D. W. Sweeney, J. E. Robertson, and K. D. Tocher [37].

**Example:** The example in TABLE 1.4 illustrates SRT division.

| $r_0 = X$ $2r_0$ Add -D                              | + | 0.0101<br>0.1010<br>1.0100                                         | >1/2 => q <sub>1</sub> =1                                                            |

|------------------------------------------------------|---|--------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| $r_1$<br>$2r_1=r_2$<br>$2r_2=r_3$<br>$2r_3$<br>Add D | + | 1 .1 1 1 0<br>1 .1 1 0 0<br>1 .1 0 0 0<br>1 .0 0 0 0<br>0 .1 1 0 0 | $>-1/2 \Rightarrow q_2=0$<br>$>-1/2 \Rightarrow q_3=0$<br>$<-1/2 \Rightarrow q_4=-1$ |

| r <sub>4</sub><br>Add D<br>r <sub>4</sub>            | + | 1 .1 1 0 0<br>0 .1 1 0 0<br>0 .1 0 0 0                             | -ve remainder & +ve<br>X<br>correction<br>Final remainder                            |

**TABLE 1.4: SRT Division Example.**

1.1.2.2.2. <u>High Radix SRT Division.</u> One can reduce the number of shift/subtract operations by using higher radices. Therefore, instead of using the radix-2 SRT, we use higher radix  $\beta$ , where  $\beta = 2^m$ , the number of shift/subtract steps will reduce from n to  $\lceil n/m \rceil$ , and m quotient bits are produced per step. The remainder recurrence relation will be:

$$r_i = 2^m r_{i-1} - q_i D$$

Where  $q_i \in \{\overline{\beta - 1}, ..., \overline{2}, \overline{1}, 0, 1, 2, ..., \beta - 1\}$ .

This recurrence relation gives the maximum redundancy for radix- $\beta$ , which might be too costly. To find the lower bound, let us assume that  $q \in D_a = \{\overline{a}, ..., \overline{2}, \overline{1}, 0, 1, 2, ..., a\}$ meaning that it can be any of these 2a+1 digits. However, we need at least  $\beta$  digits to represent a number in radix- $\beta$  therefore the following must hold [4]:

$2a+l\geq\beta$

$\Rightarrow \beta > a \ge (\beta - 1)/2$

1.1.2.2.3. <u>Vitit's Division Algorithm.</u> This algorithm [51] is simpler than radix-4 SRT and is based on radix-2 SRT. It has simpler iteration hardware and the number of iterations - at worst - is equal to those of radix-4 SRT [4] and it does not require the use of a lookup table.

Recall that, the SRT algorithm is based on the following recurrence:

$$r_i = 2r_{i-1} - q_i D$$

Initially assume that both  $2r_{i-1}$  and D are positive. Therefore,  $q_i$  can be selected as follows:

$$q_{i} = \begin{cases} 0 & \text{if} \quad 2r_{i,1} < 1/2 \\ 1 & \text{if} \quad 2r_{i,1} \ \ge \ 1/2 \text{ and } q_{i+1} = \begin{cases} \overline{1} & \text{if} \ 2r_{i,1} < D \ (3\text{-bit comparison}) \\ 0 & \text{if} \ 2r_{i,1} = D \ (3\text{-bit comparison}) \\ 1 & \text{if} \ 2r_{i,1} > D \ (3\text{-bit comparison}) \end{cases}$$

The 3-bit comparison is done on the most significant fractional bits.

The algorithm can be easily modified for signed numbers as follows:

$q_{i} = \begin{cases} 0 & \text{ if } |2\mathbf{r}_{i\cdot\mathbf{l}}| < 1/2 & \text{ and } \mathbf{r}_{\mathbf{i}} = 2\mathbf{r}_{i\cdot\mathbf{l}} \\ \text{SS} & \text{ if } |2\mathbf{r}_{i\cdot\mathbf{l}}| \geq 1/2 & \text{ if this is last q digit else} \\ & q_{i}q_{i+1} = \begin{cases} 0 & \text{SS if } |2\mathbf{r}_{i\cdot\mathbf{l}}| < |\mathbf{D}| \text{ (3-bit comparison)} \\ \text{SS SS if } |2\mathbf{r}_{i\cdot\mathbf{l}}| = |\mathbf{D}| \text{ (3-bit comparison)} \\ \text{SS SS if } |2\mathbf{r}_{i\cdot\mathbf{l}}| > |\mathbf{D}| \text{ (3-bit comparison)} \\ \text{SS SS if } |2\mathbf{r}_{i\cdot\mathbf{l}}| > |\mathbf{D}| \text{ (3-bit comparison)} \end{cases} \text{ and } \mathbf{r}_{\mathbf{i}} = 2\mathbf{r}_{i\cdot\mathbf{l}} - SSD, \text{ and } \mathbf{r}_{i+1} = 2\mathbf{r}_{\mathbf{i}} - SSD \end{cases}$

Where:

SS is  $\operatorname{Sign}(r_{i-1})^*\operatorname{Sign}(D)$ .

We can use only 2-bit comparison instead of 3-bit comparison if  $2r_{i-1}$  and D are positive as follows:

$$q_i = \begin{cases} 0 \quad \text{if} \quad 2\mathbf{r}_{\mathbf{i}\cdot\mathbf{1}} < 1/2 & \text{and} \ \mathbf{r}_{\mathbf{i}} = 2\mathbf{r}_{\mathbf{i}\cdot\mathbf{1}} \\ 1 \quad \text{if} \quad 2\mathbf{r}_{\mathbf{i}\cdot\mathbf{1}} \ \ge \ 1/2 & \text{if} \ \text{this is last q digit else} \\ \\ q_i q_{i+1} = \begin{cases} 10 \ \text{if} \ 2\mathbf{r}_{\mathbf{i}\cdot\mathbf{1}} \ \le \ \mathbf{D} \ (2\text{-bit comparison}) & \text{and} \ \mathbf{r}_{\mathbf{i}+1} = 4\mathbf{r}_{\mathbf{i}\cdot\mathbf{1}} - 2D \\ 11 \ \text{if} \ 2\mathbf{r}_{\mathbf{i}\cdot\mathbf{1}} \ > \mathbf{D} \ (2\text{-bit comparison}) & \text{and} \ \mathbf{r}_{\mathbf{i}+1} = 4\mathbf{r}_{\mathbf{i}\cdot\mathbf{1}} - 3D \end{cases}$$

Up to four dividend bits may be retired instead of 3 per iteration as follows:

$$q_i = \begin{cases} 0 & \text{if} \quad 2\mathbf{r}_{i\cdot 1} < 1/2 & \text{and} \ \mathbf{r}_i = 2\mathbf{r}_{i\cdot 1} \\ 1 & \text{if} \quad 2\mathbf{r}_{i\cdot 1} \ \ge \ 1/2 & \text{if} \ \text{this is last q digit else} \\ & q_i q_{i+1} q_{i+2} = \begin{cases} 011 \ \text{if} \ 2\mathbf{r}_{i\cdot 1} \ \le \ \mathbf{D} \ (2\text{-bit comparison}) & \text{and} \ \mathbf{r}_{i+2} = 8\mathbf{r}_{i\cdot 1} - 3D \\ 100 \ \text{if} \ 2\mathbf{r}_{i\cdot 1} \ > \mathbf{D} \ (2\text{-bit comparison}) & \text{and} \ \mathbf{r}_{i+2} = 8\mathbf{r}_{i\cdot 1} - 4D \end{cases}$$

It is obvious that we need to compute 3D and -3D in order to run this algorithm improvement[51].

The proof of this algorithm is given in APPENDIX A.

### 1.1.2.3. Exponentiation

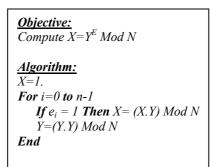

Exponentiation is performed as a number of squaring and multiplication operations depending on the length of the exponent. The algorithm is shown in Algorithm 1.1.

Algorithm 1.1: Exponentiation.

Where:

*n*: number of bits in the exponent *E*.

$$E = e_{n-1} e_{n-2} \dots e_2 e_1 e_0.$$

$e_i$ : the *i*'th bit of E.

The algorithm can be easily modified for modular exponentiation by replacing the multiplication step in Algorithm 1.2 with a modular multiplication [16].

Algorithm 1.2: Modular Exponentiation.

#### 1.1.2.4. Modular Multiplication

1.1.2.4.1. <u>**Triangle Addition Algorithm.**</u> Modular multiplication algorithms -for nword numbers- are mostly classified into the following two categories:

- Division-after-multiplication: Here, an n-word by n-word multiplication is performed first, then a 2n-word by n-word division is carried out. This method requires 2n-word memory space to store intermediate results, but it does not need many subtraction steps.

- Division-during-multiplication: In this category, division residue subtraction steps are interleaved with the multiplication addition steps and only (n+1)-word memory space is needed. On the other hand, it requires n-word subtractions and (n+1)-word by n-word division per residue calculation step.

The modular multiplication with triangle addition algorithm is a new algorithm that does not belong to any of the above categories [34]. It combines the advantages of the other two approaches by having the same memory space requirement as division-duringmultiplication, and the same number of steps needed by the division-after-multiplication category. It is a completely new algorithm in which the upper half triangle of the all partial products is added up and its residue is calculated. Then the sum of the lower half triangle of all partial products is added to the pre-calculated residue. Finally, the final residue of the total result is calculated.

#### **Assumptions and Notations**

For  $(A \times B \mod N)$

- A, B and N are n-word numbers satisfying  $0 \le A$ , B < N.

- $n \leq \beta$ . Where  $\beta$  is the radix.

- $\delta = \sum_{i=0}^{n-1} \delta_i . \beta^i$  Where  $\delta$  can be A, B or N.

#### **The Algorithm**

The algorithm (shown in Algorithm 1.3) is based on the following formula [34]:

$$A \times B \mod N = \sum_{i,j} A_i . B_j . \beta^{i+j} \mod N$$

$$= \left( \left( \sum_{i+j \ge n-1} A_i . B_j . \beta^{i+j} \right) \mod N + \sum_{i+j < n-1} A_i . B_j . \beta^{i+j} \right) \mod N$$

Algorithm 1.3: Triangle Addition Modular Multiplication.

$$P \Leftarrow \sum_{i+j \ge n-1} A_i . B_j . \beta^{i+j-n+1}$$

$$P \Leftarrow (P . \beta^{n-1}) \mod N$$

$$P \Leftarrow P + \sum_{i+j < n-1} A_i . B_j . \beta^{i+j}$$

$$P \Leftarrow P \mod N$$

1.1.2.4.2. <u>Holger and Peter's Interleaving Algorithm.</u> In [16], modular multiplication is done by interleaving the multiplication with the division. In Algorithm 1.4, P plays the role of partial remainder in SRT division and partial product in

multiplication where the algorithm adds partial product, subtract divisor multiple, and shift left the result P.

| -                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------|

| $\frac{Objective:}{Compute P = (A.B)mod N}$                                                                          |

| Algorithm:<br>P=0                                                                                                    |

| For i=n-1 downto 0                                                                                                   |

| q = estimate(P/N)<br>$P=2^{k} P + a_{i} B - 2^{k} qN$                                                                |

| End                                                                                                                  |

| P correction                                                                                                         |

| <i>Where:</i><br><i>n: number of radix 2<sup>k</sup> words.</i><br>a <sub>i</sub> : the i'th digit of the multiplier |

**Algorithm 1.4: Interleaving Modular Multiplication.**

The P correction step is required because an estimated value of q is used. The estimate of q should be good enough to keep P from diverging during the calculations.

In order to save time, carry save redundant representation of P is used – in which the value of P is represented in two registers usually called SUM and CARRY.

To estimate q, a *parallel exhaustive search* is used, in which the following expression is performed in parallel for all values of q:

$$P - q 2^k N$$

Only few bits of *P* and  $-q 2^k N$  are used in this estimation, twelve bits for radix 32 as an example. According to [16], this method generally is very expensive in terms of hardware, but may be acceptable for operands longer than 500 bits.

1.1.2.4.3. <u>Takagi's Radix-4 Algorithm.</u> Takagi [35] has presented a fast Radix-4, division-during-multiplication, modular multiplication algorithm. In this algorithm, operands and partial products are represented in redundant formats and the intermediate results are stored in more redundant format to reduce the number of additions/subtractions required. There is only one time-consuming, carry propagation step at the end of the algorithm. The algorithm calculates P=A.B (mod N), and uses the following recurrence:

$$P_j := 4.P_{j+1} + \hat{b_j}.A - 4c_j.N$$

Where:

- *N*: n-bit binary number,  $2^{n-1} \le N < 2^n$ .

- A: (n+1)-digit redundant binary number, -N < A < N.

- B: (n+1)- digit redundant binary number, -N < B < N.

- P: (n+1)- digit redundant binary number, -N < P < N.

- $\hat{b}_j$ : The *i'th* digit of the recoded *B* (multiplier). It depends only on five digits of *B* ( $b_{2j+1}$  down to  $b_{2j-3}$ ).

- $c_j$ : used for residual calculation,  $c_j \in \{\overline{2}, \overline{1}, 0, 1, 2\}$ .

The recoded multiplier  $\widehat{B}$  is a  $(\lfloor \frac{n}{2} \rfloor + 1)$  – digit radix-4 signed digit number that can be obtained using TABLE 1.5 where  $u_j$ ,  $t_j$  are intermediate temporary values. A recoding example is shown in Figure 1.4.

|            |                  |                                    |                  | $\widehat{b_j}$                 |       |   |   |

|------------|------------------|------------------------------------|------------------|---------------------------------|-------|---|---|

|            |                  |                                    |                  | t <sub>j</sub> u <sub>j-1</sub> | 1     | 0 | 1 |

|            | u <sub>j</sub> , | t <sub>j</sub>                     |                  | $\overline{2}$                  | ×     | 2 | 1 |

| $b_{2j+1}$ | 1                | 0                                  | 1                | ī                               | 2     | 1 | 0 |

| Ī          | 1,1              | $10, \overline{2}/\overline{1}, 2$ | $0,\overline{1}$ | 0                               | 1     | 0 | 1 |

| 0          | 0, 1             | 0,0                                | 0,1              | 1                               | 0     | 1 | 2 |

| 1          | 0,1              | <sup>1</sup> 1, <u>2</u> /0,2      | 1,1              | 2                               | 1     | 2 | × |

|            | Stag             | e 1                                |                  | Sta                             | ige 2 |   |   |

| $0 \overline{1}$ | 0 1 | 1 0            | B 0 | 0 1 |     | В             |

|------------------|-----|----------------|-----|-----|-----|---------------|

| 0                | 1   | 0              | 0   | 0   | (0) | u             |

| $\overline{1}$   | 1   | $\overline{2}$ | 0   | 1   |     | t             |

| 1                | 2   | $\overline{2}$ | 0   | 1   |     | $\widehat{B}$ |

Figure 1.4: Multiplier recoding example.

<sup>&</sup>lt;sup>1</sup> b2j-1 is nonnegative/otherwise

Choice of  $c_j$  based on the following:

$$c_j := \begin{cases} \overline{2} & \text{if} & \operatorname{top}(R_j) < -\operatorname{top}(6.N) \\ \overline{1} & \text{if} & -\operatorname{top}(6.N) \le \operatorname{top}(R_j) < -\operatorname{top}(2.N) \\ 0 & \text{if} & -\operatorname{top}(2.N) \le \operatorname{top}(R_j) < \operatorname{top}(2.N) \\ 1 & \text{if} & \operatorname{top}(2.N) \le \operatorname{top}(R_j) < \operatorname{top}(6.N) \\ 2 & \text{if} & \operatorname{top}(R_j) \ge \operatorname{top}(6.N) \end{cases}$$

Top means the most significant 4 digits of N, top 5 digits of (2.N), the top 6 digits of (6.N), or 8 digits of R [32] [35] [36]. In other words, left pad N, 2N, and 6N with zeros to make them (n+4)-digits numbers. Then the comparison is carried out on the most significant eight bits of them as illustrated in Figure 1.5. The algorithm steps are shown in Algorithm 1.5.

| n+4   | n+3   | n+2     | n+1     | Ν        | <b>n-1</b> | <b>n-2</b> | n-3      | 2        | 1        |                |

|-------|-------|---------|---------|----------|------------|------------|----------|----------|----------|----------------|

|       |       |         |         | $\times$ | $\times$   | imes       | $\times$ | Х        | $\times$ | Ν              |

|       |       |         | $\succ$ | $\times$ | $\times$   | imes       | imes     | Х        | imes     | 2N             |

|       |       | $\succ$ | $\succ$ | imes     | imes       | imes       | imes     | imes     | imes     | 6N             |

| $\ge$ | $\ge$ | $\succ$ | $\ge$   | $\ge$    | $\times$   | $\ge$      | $\times$ | $\times$ | $\times$ | R <sub>i</sub> |

Figure 1.5: Illustration of the compared bits.

Algorithm 1.5: Takagi's Radix-4Modular Multiplication.

Step 1:

$$P_{\lfloor n/2 \rfloor + 1} := 0$$

Step 2: for  $j = \lfloor n/2 \rfloor$  down to -1

$R_j = 4.P_{j+1} + \hat{b}_j.A$

$P_j = R_j - 4.c_j.N$

Step 3:  $P = P_{-1}/4$

Where:

$R_j$  is (n+4)-digit RBN (Residue Binary Number) and  $R_j := 4 P_{j+1} + \hat{b}_j A$

1.1.2.4.4. **Montgomery's Algorithm.** Montgomery [39] came up with an elegant way to calculate the modular multiplication. The idea is to transfer the problem to another domain which will be referred to as the Montgomery domain. The modulo multiplication in the Montgomery domain is made easier and faster.

It is required to compute  $A \cdot B \mod N$ , where A, B, and N are n-bit numbers with 0 < A, B < N, and N being an odd number. First the operands A and B are mapped into the Montgomery domain where A is mapped into  $\overline{A} = AR \mod N$  and B is mapped into  $\overline{B} = BR \mod N$  where  $R = 2^n$ . The two mapped numbers  $\overline{A}$  and  $\overline{B}$  are presented to the Montgomery product procedure  $Mon \_\Pr o(\overline{A}, \overline{B})$ . The algorithm requires the calculation of  $R^{-1}$  and N where  $R \cdot R^{-1} \mod N = 1$  and  $R \cdot R^{-1} - N \cdot N = 1$ . The calculation of N and the transformation to and form the Montgomery domain are time consuming steps. However, this cost is tolerable for modulo exponentiation  $(X^E \mod N)$  where modulo multiplication is performed repeatedly. Hence, transformation to Montgomery domain is performed once at the beginning, and then the result of the modulo exponentiation operation is transformed back form the Montgomery domain at the end [6].

Modifications to Montgomery algorithm were made by V.Bunimov et al [49], where the original operands are fed directly to the algorithm as  $Mon_Pro(A,B) = \overline{P}$  while the second pass will be for  $Mon_Pro(\overline{P}, \Re) = P$  where  $\Re = R^2 \mod N$ . The steps are shown in Algorithm 1.6.

| Objective:           Compute Mon_Pro(A,B)                                           |

|-------------------------------------------------------------------------------------|

| $\frac{Algorithm:}{T=0}$ For i=0 to n-1<br>$T=T+ai \times B + t0 \times N$<br>T=T/2 |

| If $T \ge N$ then $T = T - N$<br>Where:                                             |

| $a_i$ is the i'th bit of A and $t_0$ is the LSB of T.                               |

Algorithm 1.6: Montgomery Modular Multiplication Algorithm.

Keeping in mind that adding multiple of the modulus (*N*) does not affect the final result and since *N* is an odd number, the result of the first line of the *for* loop is always even. Therefore, the division in the second line of the *for* loop will have no remainder. By going through the first pass, the algorithm would have performed division by  $R = 2^n$ , i.e.,  $T = (A \times B/R) \mod N$ . This is why we need to run the algorithm for a second time with *T* and  $R^2$  as operands. The output of the second pass will be

$$P = (R^2 \times T/R) \mod N = [R (A \times B/R)] \mod N = (A \times B) \mod N.$$

The only time consuming step in this version is the computation of  $\Re = R^2 \mod N$ [6] [39] [49]. A more detailed description on versions of Montgomery algorithm is given in page 57.

#### 1.1.2.5. Synchronous and Asynchronous Circuits

1.1.2.5.1. <u>Clocked synchronous circuits.</u> Synchronous circuits generally use a common global clock. It is quite simple to design circuits using synchronous logic, because it is commonly understood and used. Moreover, clocked-logic parts are widely available in the market and there is no timing hazards associated with it.

Synchronous systems performance follows the worst-case behavior and suffers from clock skew problems that limit the clock speed. Replacing any system module will require complex and costly timing analysis. While asynchronous circuit module are activated and consume power only upon request, synchronous circuit module, however, dissipate power even if not active since they are regularly clocked (charged and discharged) [8] [23] [48].

1.1.2.5.2. **Event-driven asynchronous circuits.** These circuits use a request-Acknowledge handshaking protocol rather than a global clock signal. For such systems, various modulus act in an independent manner based on local events and the system overall speed performance follows the average-case behavior. Overall system speed is improved by replacing any module with a faster one without any need for timing analysis since they do not use a global clock. Using CMOS technology for implementation, power dissipation of asynchronous systems is less since only active modules will consume power. On the other hand, it is more difficult to design asynchronous modules since they are subject to timing hazards and signal races. Asynchronous circuit modules generally require more silicon area than their synchronous components [8] [23] [48].

For controllers, event-driven transition signaling is based on signal transitions (events). All signal transitions have the same meaning and there is no distinguishing between rising or falling transactions, which might double the speed over clocked logic. The following components are typically employed in event-driven based controllers:

- <u>C-Element</u>: C-Element performs ANDING of events where an event is generated at the output only if events are detected on all of the input ports. It is assumed that no simultaneous events may occur at the inputs of a C-Element [29] [30].

- Merge Element: Merge element performs ORING of events in which an event on the output is generated if an event occurs on any of its two input ports. It is assumed that no simultaneous events may occur at the inputs of a Merge-Element [29] [30].

#### CHAPTER 2

# DESIGN AND MODELING OF ASYNCHRONOUS MODULO MULTIPLIER

This work investigates the use of asynchronous techniques for the design of efficient modulo multipliers. With the large size operands commonly used in cryptosystems, using array or parallel multipliers would require prohibitively large areas. Instead, sequential multipliers are employed in this work. Since sequential multipliers use repeated add and shift operations, an asynchronous implementation can significantly improve the speed at a modest increase in area. For k-bit adders, the speed of an asynchronous adder is O (Log k) on the average [14] compared to the O (k) speed of carry-propagate adders. Asynchronous event logic based on transition signaling is used, where signal transitions are used as control events [21].

The multiplication process consists of a number of add and shift operations with addition requiring much more time than the shift operation. In addition to using an asynchronous adder with O (Log k) average speed [1], a number of other measures were adopted to further improve the overall speed of the system. For one, the developed algorithm uses radix-4 system, which retires two bits per iteration instead of one. For another, multiplier recoding as a signed-digit number [4] is used to allow skipping over chains of zeros as well as chains of ones which results in a considerable reduction in the number of required add operations, and hence a significant speed improvement.

#### **2.1. DESCRIPTION OF THE ASYNCHRONOUS ALGORITHM**

It is required to compute  $P = X \times Y \mod N$ , where the modulus N, the multiplicand X and the multiplier Y are k-bit numbers. Typically, N is a very large odd number, i.e., generally  $N_{k-1} = N_0 = 1$ . The developed algorithm uses radix-4 system, but may be extended to higher radixes as well. In addition, a Booth-like recoding of the multiplier (Y) into an equivalent signed digit representation is used. Such recoding increases the number of 0s and reduces the number of Is and -Is. This reduces the number of required add/subtract operations thus improving the overall speed. The overall procedure is given in Algorithm 2.1 and consists of four major steps:

- a. Initialization

- b. Recoding and adding

- c. Scaling

- d. Correction

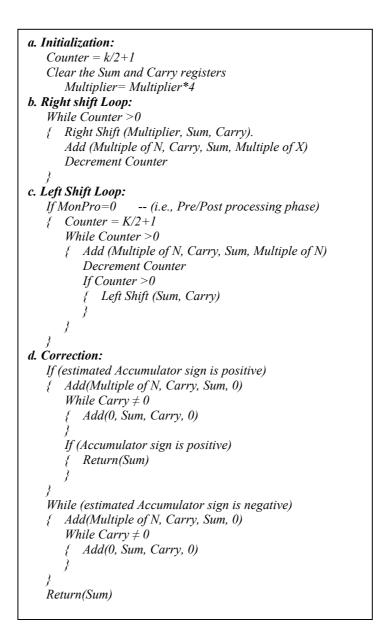

Algorithm 2.1: Asynchronous Modulo Multiplication.

| a. Initialization:                                                                                                                                                                                                                                                                           |                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|                                                                                                                                                                                                                                                                                              | e k is the number of bits in N. |

|                                                                                                                                                                                                                                                                                              |                                 |

| Left pad Y by two bits                                                                                                                                                                                                                                                                       |                                 |

| Compute (N-X), 3N at                                                                                                                                                                                                                                                                         | nd 5N. $i=k+1$                  |

|                                                                                                                                                                                                                                                                                              |                                 |

| b. Recoding and Adding                                                                                                                                                                                                                                                                       | :                               |

| WHILE $i > 0$                                                                                                                                                                                                                                                                                |                                 |

| $P \leftarrow 4P;$                                                                                                                                                                                                                                                                           |                                 |

|                                                                                                                                                                                                                                                                                              | V IC                            |

| $CASE P_{k+2} Y_i Y_{i-1}$                                                                                                                                                                                                                                                                   |                                 |

| { X000, X111                                                                                                                                                                                                                                                                                 | : skip<br>: P ← P-(N-X)         |

| 0001, 0010                                                                                                                                                                                                                                                                                   | $: P \leftarrow P - (N - X)$    |

| 0011                                                                                                                                                                                                                                                                                         | $P \leftarrow P - 2(N - X)$     |

| 0100                                                                                                                                                                                                                                                                                         | $: P \leftarrow P-2X$           |

| 0110, 0101                                                                                                                                                                                                                                                                                   | $: P \leftarrow P - X$          |

| 0110, 0101                                                                                                                                                                                                                                                                                   |                                 |

| 1110 1101                                                                                                                                                                                                                                                                                    | $: P \leftarrow P+(N-X)$        |

|                                                                                                                                                                                                                                                                                              |                                 |

| 1100                                                                                                                                                                                                                                                                                         | $: P \leftarrow P + 2(N-X)$     |

| 1011                                                                                                                                                                                                                                                                                         | $: P \leftarrow P+2X$           |

| 1001, 1010                                                                                                                                                                                                                                                                                   | $: P \leftarrow P + X$          |

| }                                                                                                                                                                                                                                                                                            |                                 |

|                                                                                                                                                                                                                                                                                              |                                 |

| c. Scaling:                                                                                                                                                                                                                                                                                  |                                 |

| $CASE P_{k+2} P_{k+1} P_k$                                                                                                                                                                                                                                                                   | $P_{k,l}N_{k,2}IS$              |

| $\{ 000XX, 111XX \}$                                                                                                                                                                                                                                                                         |                                 |

| 001XX                                                                                                                                                                                                                                                                                        | $P \leftarrow P-2N$             |

|                                                                                                                                                                                                                                                                                              |                                 |

| 010X1                                                                                                                                                                                                                                                                                        | $: P \leftarrow P-3N$           |

|                                                                                                                                                                                                                                                                                              | $: P \leftarrow P-4N$           |

| 01100                                                                                                                                                                                                                                                                                        | $: P \leftarrow P-5N$           |

| 01110                                                                                                                                                                                                                                                                                        | $: P \leftarrow P-6N$           |

|                                                                                                                                                                                                                                                                                              |                                 |

| 110XX                                                                                                                                                                                                                                                                                        | $: P \leftarrow P+2N$           |

| 101X1                                                                                                                                                                                                                                                                                        | $: P \leftarrow P+3N$           |

| -                                                                                                                                                                                                                                                                                            | $P \leftarrow P + 4N$           |

| 10120, 10021                                                                                                                                                                                                                                                                                 | $P \leftarrow P+5N$             |

|                                                                                                                                                                                                                                                                                              |                                 |

| 10000                                                                                                                                                                                                                                                                                        | $: P \leftarrow P+6N$           |

| }                                                                                                                                                                                                                                                                                            |                                 |

| <i>i=i-2</i>                                                                                                                                                                                                                                                                                 |                                 |

| }                                                                                                                                                                                                                                                                                            |                                 |

|                                                                                                                                                                                                                                                                                              |                                 |

| d. Correction:                                                                                                                                                                                                                                                                               |                                 |

| WHILE P>0                                                                                                                                                                                                                                                                                    |                                 |

| $\begin{cases} P \leftarrow P-N \end{cases}$                                                                                                                                                                                                                                                 |                                 |

| $\begin{array}{c} \begin{array}{c} \begin{array}{c} \end{array} \\ 1 \\ \end{array} \\ \end{array}$ |                                 |

|                                                                                                                                                                                                                                                                                              |                                 |

| $P \leftarrow P+N$                                                                                                                                                                                                                                                                           |                                 |

|                                                                                                                                                                                                                                                                                              |                                 |

#### 2.1.1. Initialization Step

In this step, the partial product register is cleared and the values required throughout the algorithm are computed. These values are (N-X) which is used in the recoding step, 3N and 5N that are used in the scaling step. Then the partial product accumulator -register P-is cleared again.

#### 2.1.2. The Recoding And Adding Step

The algorithm scans one multiplier digit (2bits) plus one look-ahead bit from left-to-rightevery iteration. Digit recoding is based on TABLE 2.1.

To compute  $P = X \times Y \mod N$ , the product register *P* is initially left padded with a total of four bits. Three bits to accommodate the sign and the left shift operation by one digit (2bits) and the fourth is needed because the multiple 6*N* is needed in the scaling step. For proper recoding, the multiplier is also left padded with two Zeros. After the initialization step, the proper multiple of *X* is added or subtracted from P based on the value of the recoded multiplier digit and the sign of *P*, i.e.,  $P_{k+4}$ . It should be noted that instead of subtracting/adding *X*, (*N*-*X*) may be equivalently added/subtracted. To reduce the chance of overflow, the performed operation, i.e., adding *X* or equivalently subtracting (*N*-*X*), is chosen to oppose the current sign of *P*. For example, according to TABLE 2.1, if  $y_i y_{i-1} y_{i-2}=001$  then X should be added to *P*. In this case, if *P* is negative, we add *X* to *P*, but if *P* is positive we subtract (*N*-*X*) from *P*. This requires pre-computation and storage of (*N*-*X*).

| Scanned Multiplier Digit        | Look Ahead Bit   | Action             |

|---------------------------------|------------------|--------------------|

| y <sub>i</sub> y <sub>i-1</sub> | y <sub>i-2</sub> |                    |

| 00                              | 0                | Shift 2-bits       |

| 00                              | 1                | +1 X; Shift 2-bits |

| 01                              | 0                | +1 X; Shift 2-bits |

| 01                              | 1                | +2 X; Shift 2-bits |

| 10                              | 0                | -2 X; Shift 2-bits |

| 10                              | 1                | -1 X; Shift 2-bits |