# Exploring Software Compartmentalisation with Hardware Capabilities

A thesis submitted to the University of Manchester for the degree of Master of Philosophy in the Faculty of Science and Engineering

2023

John Alistair Kressel Department of Computer Science

## Contents

| C                | onte  | nts                  |                                       | 2  |

|------------------|-------|----------------------|---------------------------------------|----|

| $\mathbf{L}^{:}$ | ist o | f figu               | res                                   | 5  |

| $\mathbf{L}^{:}$ | ist o | f tabl               | es                                    | 7  |

| L                | ist o | f pub                | lications                             | 8  |

| A                | bstr  | $\operatorname{act}$ |                                       | 9  |

| L                | ay al | ostrac               | et                                    | 10 |

| D                | ecla  | ration               | of originality                        | 11 |

| C                | opyr  | ight s               | statement                             | 12 |

| A                | .cknc | wledg                | gements                               | 13 |

| 1                | Inti  | roduc                | tion                                  | 14 |

|                  | 1.1   | Thesi                | s Structure                           | 16 |

| 2                | Bac   | kgrou                | and                                   | 17 |

|                  | 2.1   | Intro                | duction To Compartmentalisation       | 17 |

|                  |       |                      | What Is A Compartment?                | 17 |

|                  |       | 2.1.2                | The Need For Compartmentalisation     | 18 |

|                  |       | 2.1.3                | What Makes Good Compartmentalisation? | 20 |

|                  |       | 2.1.4                | Trust Models                          | 22 |

|                  | 2.2   | Mech                 | anisms                                | 24 |

|                  |       | 2.2.1                | Page Tables                           | 24 |

|                  |       | 2.2.2                | Software Fault Isolation (SFI)        | 27 |

|                  |       |                      | Safe Programming Languages            | 28 |

|                  |       | 2.2.4                | Software Capabilities                 | 28 |

|                  |       | 2.2.5                | Memory Encryption                     | 28 |

|                  |       | 2.2.6                | Trusted Execution Environments (TEE)  | 29 |

|                  |       | 2.2.7                | Memory Tagging                        | 30 |

|                  |       | 2.2.8                | Bounds Checking                       | 30 |

|                  |       | 2.2.9                | Hardware Capabilities                 | 31 |

|                  | 2.3   | Autor                | mation                                | 32 |

|                  |       | 2.3.1                | Manual Approaches                     | 32 |

|   |     | 2.3.2 Guided Manual                                   | 32              |

|---|-----|-------------------------------------------------------|-----------------|

|   |     | 2.3.3 Policy Based                                    | 32              |

|   |     | 2.3.4 Automatic                                       | 33              |

|   | 2.4 | Sharing Data                                          | 33              |

|   | 2.5 | Compartmentalisation In Practice                      | 33              |

|   |     | 2.5.1 Deployed Software                               | 33              |

|   |     | 2.5.2 What Is The Problem?                            | 34              |

|   | 2.6 | CHERI                                                 | 34              |

|   |     | 2.6.1 An Introduction To CHERI                        | 35              |

|   |     | 2.6.2 CHERI State Of The Art For Compartmentalisation | 38              |

|   | 2.7 | Unikernels                                            | 41              |

|   |     | 2.7.1 FlexOS                                          | 42              |

|   | 2.8 | Summary                                               | 43              |

| 0 | D., |                                                       | 4.4             |

| 3 | Des | Requirements                                          | <b>44</b> 44    |

|   | 5.1 | -                                                     | 44              |

|   |     | 3.1.1 Low Performance Cost                            | 44              |

|   |     | 3.1.2 Low Engineering Cost                            | $\frac{45}{45}$ |

|   | 2.0 | 3.1.3 Scalability                                     |                 |

|   | 3.2 | Design Overview                                       | 45              |

|   | 3.3 | Approaches To Data Sharing                            | 46<br>47        |

|   |     | 3.3.1 Manual Capability Propagation                   | 49              |

|   |     | 3.3.2 Overlapping Shared Data Region                  |                 |

|   |     | 3.3.3 Shared Data Capability                          | 51              |

|   |     | 3.3.4 Exception-Based Shared Data Access              | 52<br>52        |

|   |     | 3.3.5 Load/Store Macro-Based Shared Data Access       | 52<br>54        |

|   | 2.4 | 3.3.6 Shared Data With Multiple <i>DDCs</i>           | 54<br>54        |

|   | 5.4 | Summary                                               | 54              |

| 4 | Imp | plementation                                          | <b>56</b>       |

|   | 4.1 | Porting FlexOS To Morello In Hybrid Mode              | 56              |

|   |     | 4.1.1 Booting                                         | 56              |

|   |     | 4.1.2 Exceptions                                      | 57              |

|   |     | 4.1.3 Allocators                                      | 58              |

|   |     | 4.1.4 UART                                            | 58              |

|   | 4.2 | Isolation Mechanism Implementation                    | 59              |

|   |     | 4.2.1 CHERI Isolation Mechanism Overview              | 59              |

|   |     | 4.2.2 Compartment Structure                           | 60              |

|   |     | 4.2.3 Initialisation                                  | 61              |

|   |     | 4.2.4 Compartment ID                                  | 62              |

|   |     | 4.2.5 Switching                                       | 62              |

|   | 4.3 | Data Sharing Methods                                  | 64              |

|   |     | 4.3.1 Manual Capability Propagation                   | 64              |

|   |     | 4.3.2 Overlapping Shared Data Region               | 64         |

|---|-----|----------------------------------------------------|------------|

|   |     | 4.3.3 Exception-Based Shared Data Access           | 65         |

|   |     | 4.3.4 Macro-Based Shared Data Access               | 65         |

|   | 4.4 | Summary                                            | 66         |

| 5 | Eva | luation                                            | 67         |

|   | 5.1 | Evaluation Setup                                   | 67         |

|   |     | 5.1.1 Rationale For Compartmentalised Components   | 68         |

|   | 5.2 | Engineering Cost                                   | 69         |

|   |     | 5.2.1 SQLite                                       | 69         |

|   |     | 5.2.2 Libsodium                                    | 69         |

|   |     | 5.2.3 Summary                                      | 70         |

|   | 5.3 | Performance                                        | 70         |

|   |     | 5.3.1 SQLite                                       | 71         |

|   |     | 5.3.2 Libsodium                                    | 73         |

|   |     | 5.3.3 Microbenchmarks                              | 74         |

|   | 5.4 | Interface Security Properties                      | 75         |

|   |     | 5.4.1 Exposure of Addresses                        | 75         |

|   |     | 5.4.2 Exposure of Compartment-Confidential Data    | 75         |

|   |     | 5.4.3 Dereference of Corrupted Pointer             | 76         |

|   |     | 5.4.4 Usage of Corrupted Indexing Information      | 76         |

|   |     | 5.4.5 Usage of Corrupted Object                    | 76         |

|   |     | 5.4.6 Expectation of API Usage Ordering            | 76         |

|   |     | 5.4.7 Usage of Corrupted Synchronisation Primitive | 76         |

|   |     | 5.4.8 Shared-Memory Time-of-Check-to-Time-of-Use   | 77         |

|   |     | 5.4.9 Summary Of Security Properties               | 77         |

|   | 5.5 | Summary                                            | 77         |

| 6 | Coı | nclusion & Future Work                             | <b>7</b> 8 |

|   | 6.1 | Contributions                                      | 79         |

|   | 6.2 | Future Work                                        | 80         |

|   |     | 6.2.1 Compiler Propagated Capabilities             | 80         |

|   |     | 6.2.2 Pure Capability Compartments                 | 81         |

|   |     |                                                    |            |

Word count: 20588

82

References

# List of figures

| 2.1 | Example of sandboxing. Compartments 1 and 2 are sandboxed                                    | 22   |

|-----|----------------------------------------------------------------------------------------------|------|

| 2.2 | Example of safeboxing. Compartment 2 is safeboxed                                            | 23   |

| 2.3 | Example of mutual distrust                                                                   | 23   |

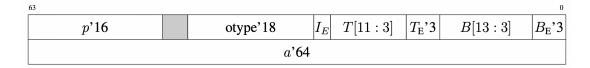

| 2.4 | The original encoding of a CHERI capability. This image is taken from                        |      |

|     | The CHERI capability model: Revisiting RISC in an age of risk [22].                          | 35   |

| 2.5 | The CHERI concentrate capability encoding. This image is taken from                          |      |

|     | $Capability\ Hardware\ Enhanced\ RISC\ Instructions:\ CHERI\ Instruction$                    |      |

|     | Set Architecture (Version 8) [179]. a: pointer address, $B \ \mathcal{E} \ T$ : base         |      |

|     | and top related to bounds, $I_E  \mathcal{E}  B_E  \mathcal{E}  T_E$ : exponent bits, otype: |      |

|     | object type, $p$ : permissions                                                               | 35   |

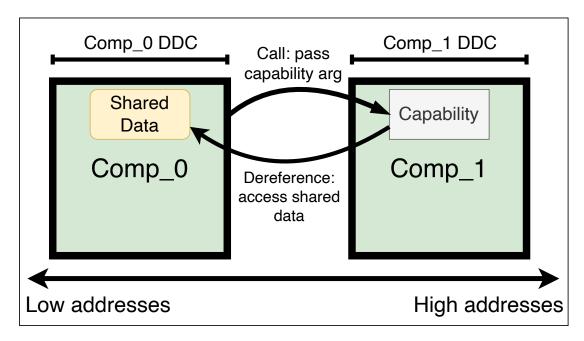

| 3.1 | Example of data accessed via a capability. Here, the shared data                             |      |

| 0.1 | is in compartment 0, which is unreachable from compartment 1. A                              |      |

|     | capability is passed as an argument when compartment 1 is called.                            |      |

|     | The data is then accessed by dereferencing the capability                                    | 47   |

| 3.2 | Path of execution, demonstrating the difficulty faced when manu-                             |      |

|     | ally annotating pointers to capabilities. Compartment 1: SQLite,                             |      |

|     | Compartment 2: vfscore + ramfs, Default Compartment: everyth                                 | ning |

|     | else                                                                                         | 49   |

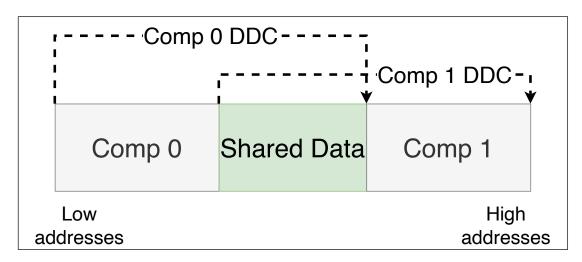

| 3.3 | Compartment bounds when a shared memory region is used. The                                  |      |

|     | compartment bounds overlap to encompass shared data. The grey                                |      |

|     | boxes represent compartment private data                                                     | 50   |

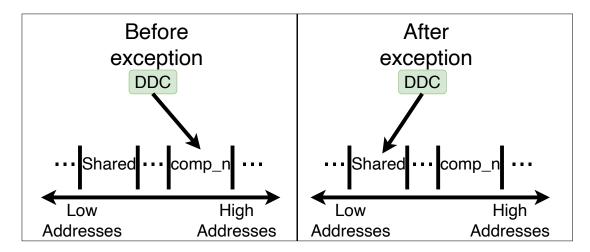

| 3.4 | Exception based shared data access approach. <i>DDC</i> before and after                     |      |

|     | a capability bounds fault when attempting to access shared data                              | 53   |

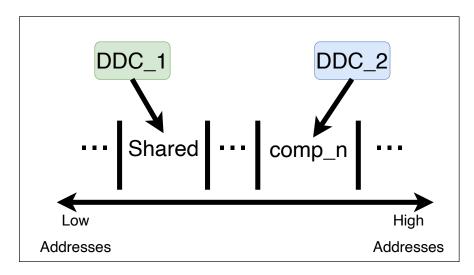

| 3.5 | Multiple $DDCs$ which are initialised to cover different memory regions,                     |      |

|     | thus avoiding the need to switch                                                             | 54   |

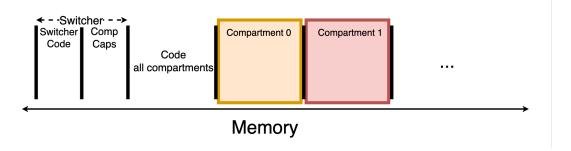

| 4.1 | Memory layout of FlexOS on Morello                                                           | 59   |

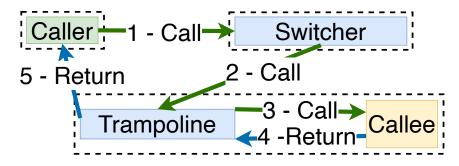

| 4.2 | Control flow of a compartment switch (call and return paths). Dashed                         |      |

|     | boxes represent compartments. The trampoline is available in the                             |      |

|     | compartment of the callee compartment                                                        | 59   |

|     | - ·                                                                                          |      |

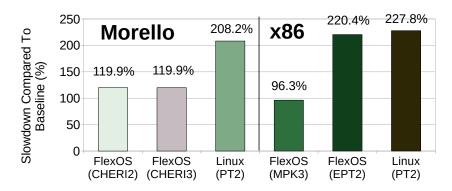

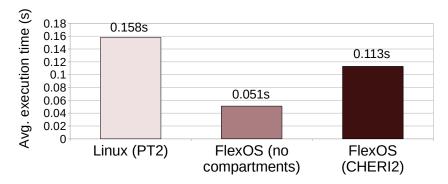

| 5.1 | Overhead relative to uncompartmentalised FlexOS on respective sys-   |    |

|-----|----------------------------------------------------------------------|----|

|     | tem (Morello and x86), of SQLite configurations. Uncompartmen-       |    |

|     | talised FlexOS is used as a baseline because this represents a stan- |    |

|     | dard unikernel lacking isolation between the application and kernel. |    |

|     | CHERI3 included with uktime in compartment 3 (manual capability      |    |

|     | propagation for comparison with MPK3). Also shown are the over-      |    |

|     | heads of MPK3, EPT2 and Linux taken from [15]                        | 72 |

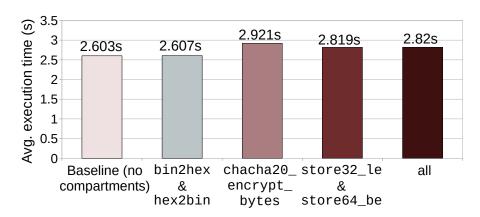

| 5.2 | Execution time in seconds of different configurations of SQLite run- |    |

|     | ning on Morello                                                      | 72 |

| 5.3 | Execution time in seconds of libsodium configurations running on     |    |

|     | Morello                                                              | 73 |

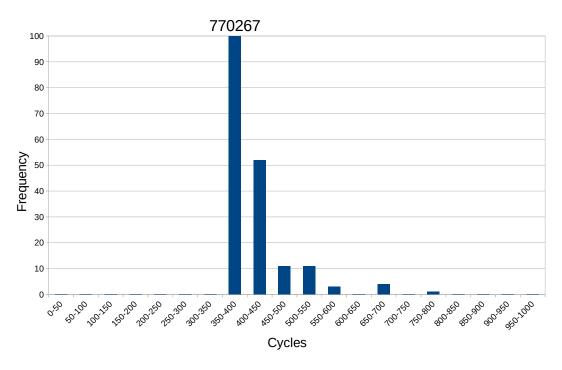

| 5.4 | Number of cycles per compartment switch (SQLite CHERI3)              | 74 |

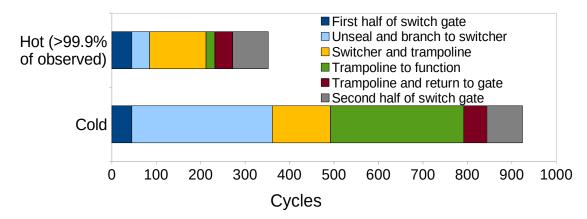

| 5.5 | Hot and cold compartment switch latencies, broken down into com-     |    |

|     | ponent parts                                                         | 75 |

## List of tables

| 2.1 | Permissions available in Morello                                          | 37 |

|-----|---------------------------------------------------------------------------|----|

| 2.2 | Comparison of compartmentalisation using CHERI. $SAS = $ Single Ad-       |    |

|     | dress Space Compartmetalisation, $EOH =$ Evaluated On Hardware            | 42 |

| 4.1 | Bits controlling capability store faulting                                | 57 |

| 4.2 | Bits controlling capability load faulting                                 | 58 |

| 5.1 | Porting effort required to compartmentalise                               | 69 |

| 5.2 | ${\bf SQLite~2~compartments~(vfscore+ramfs~isolated)~compartment~switch}$ |    |

|     | metrics                                                                   | 70 |

| 5.3 | Performance counters by for each configuration compared to the un-        |    |

|     | compartmentalised baseline                                                | 71 |

| 5.4 | Libsodium configurations compartment switch metrics.                      | 71 |

## List of publications

The following publication is based on the work done as part of this MPhil.

J. A. Kressel, H. Lefeuvre, and P. Olivier, "Software Compartmentalization Trade-Offs with Hardware Capabilities," 12th Workshop on Programming Languages and Operating Systems (PLOS 2023).

### Abstract

Compartmentalisation is a form of defensive software design in which an application is broken down into isolated but communicating compartments. Retrofitting compartmentalisation into existing applications is often thought to be expensive from the engineering effort and performance overhead points of view. ARM Morello combines a modern ARM processor with an implementation of Capability Hardware Enhanced RISC Instructions (CHERI) aiming to provide efficient and secure compartmentalisation by using CHERI capabilities to isolate portions code and data. CHERI provides a hybrid mode, where capabilities can be used alongside standard pointers in software. This promises to reduce the engineering burden associated with implementing compartmentalisation in legacy software by eliminating the need to port entire code bases.

This thesis explores possible compartmentalisation schemes available to developers in a single address space environment with CHERI in hybrid mode, and then proposes two approaches representing different trade-offs in terms of engineering effort, security, scalability, and performance impact. These approaches are described, implemented and evaluated on a prototype unikernel running bare metal on the Morello chip, compartmentalising two popular applications, SQLite and Libsodium. Unikernels feature no memory isolation between the kernel and application, with both occupying the same address space for performance reasons, which raises security concerns. CHERI compartmentalisation in hybrid mode is, therefore, explored as a way to establish isolation between components within a unikernel, with a potentially low engineering effort while preserving the performance advantages of sharing a single address space.

The evaluation shows that CHERI, in hybrid mode can achieve compartmentalisation within a single address space unikernel environment, at a performance overhead which is comparable to that achieved with Intel MPK and outperforms that achieved with Intel EPT. Furthermore, it shows that the isolation achieved, outperforms the user-kernel separation provided by Linux. However, the evaluation demonstrates that the engineering cost of applying CHERI compartmentalisation in hybrid mode using fine-grained capabilities for inter-compartment communication is high, making this approach impractical outside of small-scale scenarios. To tackle this issue an alternate data sharing method is proposed, which trades off scalability and security to reduce the engineering effort.

## Lay abstract

Security is often an afterthought in the design of a software system. With the increasing ubiquity of computer systems in critical infrastructure, it is important to isolate components of a system from each other to reduce the damage which can be done in the event of a successful attack on any component. Compartmentalisation offers a way to do this, by splitting software into compartments which have only the minimum privileges needed to complete their task. Many technologies exist to do this, including CHERI, a hardware implemented technique which can be used to restrict the parts of a system accessible to compartments. Splitting software systems into compartments is often associated with a performance cost and a significant engineering challenge. This thesis presents the design, exploration and evaluation of various methods for implementing CHERI based compartmentalisation, which trade off performance, engineering effort and scalability for improved security. In contrast to much of the existing work using CHERI, which is evaluated using simulators or soft cores, the system is implemented and evaluated on Morello hardware, an extension to a standard 64-bit ARM processor implementing CHERI.

## Declaration of originality

I hereby confirm that no portion of the work referred to in the thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

## Copyright statement

- i The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the "Copyright") and s/he has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

- ii Copies of this thesis, either in full or in extracts and whether in hard or electronic copy, may be made *only* in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

- iii The ownership of certain Copyright, patents, designs, trademarks and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the thesis, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

- iv Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy (see http://documents.manchester.ac.uk/DocuInfo.aspx?DocID=24420), in any relevant Thesis restriction declarations deposited in the University Library, The University Library's regulations (see http://www.library.manchester.ac.uk/about/regulations/) and in The University's policy on Presentation of Theses.

## Acknowledgements

I wish to thank my supervisor Dr. Pierre Olivier for providing me with invaluable support, guidance and mentorship in my research. I also wish to thank Professor Mikel Luján and Hugo Lefeuvre for their advice and support this year. Next, I would like to thank Abhinav Krishnan for his patient listening to my endless ramblings. Additionally, I would like to thank Dr. Andrew Attwood for his advice and feedback. Finally, I would like to extend my gratitude to my family and friends for being patient and supportive, thank you!

## Chapter 1

### Introduction

Software compartmentalisation is one of the ways to enforce the principle of least privilege [1]. Compartmentalisation enforces isolation between components of a software system, granting compartments only the minimal privileges they need to function. If a component of a compartmentalised system is subverted, the damage the attacker can do is limited to the privileges granted to the compromised compartment [2], [3]. Contrary to many other protection techniques, compartmentalisation allows defending against yet unknown and future vulnerabilities in existing code bases [4]. Many approaches have been proposed in recent years, utilising different hardware and software isolation mechanisms to compartmentalise libraries [5]–[15] as well as code at other granularities, including functions [16]–[19] and device drivers [20].

Morello [21] is an extension to the ARMv8-A architecture implementing the Capability Hardware Enhanced RISC Instructions (CHERI), designed specifically to enable high-performance and scalable compartmentalisation [4], [22], [23]. This is achieved by enforcing compartment bounds on most memory loads and stores in hardware, and letting communicating compartments securely grant memory access to each other using so-called hardware capabilities, a mechanism similar to fat pointers [24]–[26] implemented in hardware to restrict accesses to shared memory at a fine (byte-level) granularity. Compartmentalisation can be achieved by using CHERI capabilities to isolate the code and data accesses of compartments. To eliminate the need to port entire code bases to use capabilities, CHERI provides a hybrid mode, where regular pointers can be selectively replaced with capabilities by the developer. Additionally, all pointer memory accesses are implicitly checked against a set of global architectural capabilities. The promise of hybrid mode is, therefore, low engineering effort to integrate capabilities and compartmentalisation into an existing code base.

When retrofitting compartmentalisation to existing code bases, a key challenge is keeping refactoring costs low [27]. This is crucial not only for reducing the cost of deployment, but also to reduce the number of errors made during the compartmentalisation, which can undermine its efficiency or security guarantees [28]. Work exploring compartmentalisation with CHERI is so far limited mostly to solutions implemented in pure capability mode [4], [6], [29]–[31], where all pointers

are replaced with capabilities. This presents a need for an exploration of compartmentalisation in hybrid mode, especially given the promises of low engineering effort needed to integrate it into an existing code base. These existing works are further limited to MIPS/RISC-V emulated or FPGA prototypes, making it hard to understand the real-world performance one would observe on a hardware processor. In that context, the recent availability of Morello raises the following research questions which will be addressed in this thesis:

- **RQ1** Which compartment models are possible using Morello, using what programming abstractions, at which refactoring costs, and how do they scale?

- **RQ2** How does Morello's compartmentalisation performance compare to other single address space compartmentalisation mechanisms, such as Intel Memory Protection Keys (MPK)?

- **RQ3** What security properties does CHERI/Morello-based compartmentalisation offer, versus mechanisms such as MPK?

For this purpose, an existing compartmentalisation-oriented unikernel (libOS), FlexOS [15] is ported to run bare metal on Morello hardware in hybrid mode. Unikernels are statically linked and code and data resides in a single address space, which is done to improve performance. However, the lack of any isolation between application and kernel components is a security concern. Introducing compartmentalisation to restore isolation between certain parts of the system is desirable [18], [32]. Doing this in a way which maintains the performance of unikernels and does not require significant engineering effort is a requirement. In addition, exploring compartmentalisation within a single address space unikernel will allow findings to be applied to other single address space settings such as processes.

To achieve this, FlexOS is extended by developing compartmentalisation programming abstractions relying on CHERI hardware capabilities, each representing a particular trade-off in terms of porting costs, security guarantees, and their ability to be applied to many compartments. These include manual sandboxing as advocated by CHERI's designers [4], with every shared buffer protected by fine-grained capabilities and additionally an approach relying on a single region of shared memory between pairs of communicating compartments. These abstractions are used to compartmentalise popular open source software, SQLite [33] and Libsodium [34], at different isolation granularities: libraries and functions. The porting costs and degree of security of these solutions are evaluated. Further, their performance when executing on the Morello chip is analysed, comparing these results to that of other single address space isolation mechanisms, Intel MPK and Intel EPT, which have previously been used to introduce compartmentalisation to FlexOS.

The performance evaluation shows that the performance achieved by CHERI compartmentalisation in hybrid mode when applied to FlexOS using the shared memory approach is comparable to that achieved with Intel MPK and outperforms Intel EPT. Additionally, FlexOS with CHERI hybrid mode compartmentalisation applied still outperforms the same application running under Linux with a similar model of isolation.

Regarding the engineering cost of integrating compartmentalisation, while it is possible to make trade-offs to reduce the engineering cost, the challenge of sharing data in a single address space system means that hybrid mode using fine-grained capabilities presents engineering issues which require design compromises to overcome.

#### 1.1 Thesis Structure

Chapter 2 of this thesis first takes an in-depth look at the motivation for compartmentalising software, as well as the concepts needed to implement it. Further, it investigates the various compartmentalisation technologies which have been applied in the literature to give context of where this work stands in the broader field and finally, describes in detail how CHERI works and how it has been applied to the problem of compartmentalisation.

Chapter 3 introduces the design of the proposed system from a high level, including how data can be shared between compartments and considers the performance and engineering costs, as well as the scalability of the proposed solutions.

Chapter 4 goes on to detail the steps taken to port FlexOS to the Morello platform and how the system is implemented, including the precise programming abstractions and annotations needed for the different compartment models.

Next, chapter 5 evaluates the implemented system with respect to the performance cost, the engineering effort needed to port software to use it and the security guarantees it provides. These are compared to other popular mechanisms: MPK and EPT.

Chapter 6 presents the conclusion of this thesis, followed by the contributions made by this thesis and a description of proposed future work.

## Chapter 2

## Background

The following chapter considers, first, the motivation for researching compartmentalisation and how it is an important technique, as well as defines the important terms and principles needed to understand compartmentalisation and the available compartment models. Next, different mechanisms which can be used to enable compartmentalisation are examined in detail, followed by an in-depth look at CHERI, which is needed to understand the work presented in the remainder of this thesis.

#### 2.1 Introduction To Compartmentalisation

Compartmentalisation stems from the principle of least privilege, first defined by Saltzer et al. [1] in 1975, as "...the least set of privileges necessary to complete the job". In practice this means that system failures or malicious activities are limited to only part of the system and so the damage caused is also limited.

The study of software compartmentalisation focuses on the techniques and mechanisms to enable previously monolithic software systems such as applications to be partitioned into a set of smaller, isolated compartments with limited privileges, controlled data sharing and isolated private data. With the ubiquity of computer systems in everything from critical safety systems and the Internet of Things, to the infrastructure underpinning modern society, it becomes ever more necessary to protect these systems from malicious activities.

#### 2.1.1 What Is A Compartment?

A compartment can be simply defined as a unit of isolation encompassing part of the code and data of a larger entity. Compartments are granted the minimum bounds and permissions which are needed to execute their intended task. In practice this means that a compartment may contain some code such as a function or a library as well as data which is intended to be kept private. Limited data sharing is then established between compartments to allow controlled access to external resources.

#### 2.1.2 The Need For Compartmentalisation

The following section examines the real need for compartmentalisation in modern computer systems, starting with high level examples of well-known and costly security vulnerabilities, followed by a closer look at the types of attacks which can be thwarted by compartmentalisation when it has been applied properly.

#### It Affects Us All

Well known examples of security vulnerabilities which caused widespread disruption include: Heartbleed [35] which affected over 50% of all websites and allowed attackers to read private data from HTTPS encrypted websites by supplying an invalid length with a heartbeat message. A similarly critical and remotely exploitable vulnerability was discovered in log4j [36], the popular Java logging library. Both vulnerabilities resulted in widespread disruption and millions of vulnerable systems.

Both of these examples demonstrate the need for compartmentalisation to mitigate such memory safety issues. Such vulnerabilities are ever present in large code bases [37] and indeed, the number of new vulnerabilities reported is increasing every year. While problems can be fixed with patches and updates, these can be time-consuming to apply, and not all systems will receive fixes in a timely manner [35]. These points are critical, since during this time, vulnerabilities can be exploited.

When a vulnerability is exploited in an uncompartmentalised system, the exploited code or module has more privileges than it needs to execute its task, meaning the rest of the system is also liable to compromise. This presents attackers with the potential to steal sensitive data or perform other malicious tasks, regardless of how seemingly unimportant the compromised code was. Consequently, a system is only as secure as the weakest component in that system. Large and complex software systems may use hundreds of libraries.

#### How Compartmentalisation Can Help

Many different attack scenarios exist. Compartmentalisation research has focused on many of them. In addition to currently known attacks, compartmentalisation can be used to defend against yet unknown attacks by limiting the exploitable surface of a vulnerability. Compartmentalisation does this by reducing the privileges granted to a software component.

Memory safety refers to bugs and attacks which target unsafe memory accesses, for example buffer overflows and underflows. Such issues are particularly prevalent in C code bases because C is not a memory safe language, relying instead on

manual memory management by the developer, which is prone to bugs. Google and Microsoft have separately identified that 70% of their bugs stem from memory safety issues [38], [39]. Compartmentalisation can mitigate the damage caused by such bugs by limiting the accessible memory given to compartments. Much work has focused on memory safety [22], [40], [41]. Indeed, capabilities implemented in both hardware and software [24], [25] such as CHERI [22] specifically target memory safety vulnerabilities. Additionally, a growing area of interest for researchers is the use of memory safe languages in domains which have typically used C for the past decades, such as the inclusion of components written in Rust in the Linux kernel [42].

Supply chain attacks are possible because large code bases often use many different libraries and software components from different and untrusted sources. This is done to ease development by using tried and tested software libraries, for example cryptographic libraries. Vulnerabilities or malicious code present in such components can cause damage. Code can be acquired from many sources [43] including package managers. Compartmentalisation can be applied to separate application components into distrusted compartments, limiting the scope of such attacks [44], [45].

Side channel attacks gather additional information such as frequency and timing information to exploit systems [46]. Compartmentalisation can be used to protect against some side channel attacks by reducing the oversharing and leakage of data and enforcing security boundaries. A growing body of work is focused on mitigating side channel attacks [47]–[49], including attacks such as Spectre [50]–[53].

Fault tolerance is important in safety critical systems where continued operation despite malfunctioning or exploited code is necessary. For example, a denial-of-service attack on safety critical services, caused by exploiting vulnerable software or buggy device drivers, can result in a crash which can be very damaging and difficult to recover from. Consider a real-time safety system at a nuclear facility, or software controlling the movements of an autonomous vehicle; a crash in such systems could lead to catastrophic consequences. Protection against attacks and faults causing crashes can be achieved using compartmentalisation, since code is unprivileged and limited in its scope for damage and disruption [30], [54].

Protecting secret data such as cryptographic secrets and other highly sensitive data can be achieved through compartmentalisation. By isolating secret data and code which manipulates it, the data cannot be stolen via attacks on other components, for example the heartbeat component of OpenSSL [55] which was exploited by Heartbleed. A large body of work has focused on protecting private information [16], [56]–[60].

#### 2.1.3 What Makes Good Compartmentalisation?

So far the need for compartmentalisation has been examined. Next, the criteria for a good implementation are detailed. These criteria are critical for producing compartmentalisation which can be adopted by real software and thus have a tangible impact.

#### Low Performance Overhead

Partitioning monolithic applications into smaller components running within their own isolated compartments can potentially add a significant performance overhead to an application. This stems from a number of factors. Firstly, compartments can often no longer communicate as before by de-referencing pointer arguments. Instead, communication is frequently done via shared memory regions, inter-process communication, or using other mechanisms which are costlier due to the additional data copying which is required. Many isolation mechanisms also rely on additional checks inserted via instrumentation or traps, to check and catch an illegal code or data accesses [10], [61], [62]. Switches between compartments are also often inserted in the form of call gates in place of traditional function calls, which themselves can add significant overhead, since gates can be used to perform tasks such as switching compartment stacks and address space switching [15].

Security can come at a cost. The challenge to design a compartmentalisation scheme is to balance the performance and security needs to an acceptable degree to ensure that any performance cost is minimised, while still offering improved security. Systems with high performance overhead will struggle to find adoption in real applications, since lower performance will mean a greater hardware and energy cost to deploy large applications. DARPA CPM defined an acceptable CPU overhead of <15% for OS level isolation and <5% for application level isolation, in their call for proposals [27].

#### Low Engineering Effort

Alongside performance considerations are implementation costs, or the engineering effort which is required to port or retrofit an application to take advantage of compartmentalisation technologies and primitives. Legacy applications are often not designed with compartmentalisation in mind [28], resulting in complex data dependencies which can be challenging to unpick and isolate from an entangled system. Consequently, any solutions which require too much effort from a developer, are unfeasible for a number of reasons. Firstly, code may be decades old and either poorly maintained, poorly documented or both. Additionally, with increased complexity comes an increased risk of human error, which leads to poor compartmentalisation practices. Trying to retrofit compartmentalisation into such

code bases is costly in terms of both time and effort and can be a significant barrier to adoption.

#### Flexible Compartmentalisation Granularity

Flexibility when implementing compartmentalisation is important to reduce both the performance overhead and engineering effort involved. By enabling fine-grained compartmentalisation, a developer can choose to isolate large, coarse components such as libraries, smaller units of code such as functions, or just a few critical data structures such as cryptographic keys, depending on their performance and engineering budget, as well as the threat model. Some isolation mechanisms such as page table based approaches only allow coarse compartmentalisation down to the granularity of a page, which can be impractical for small and light implementations due to hardware pressures and inefficient use of memory pages, if only small quantities of data are shared.

#### Scalability

Scalability is the ability to create a few or many compartments without the cost of adding more becoming a burden. This is important because a solution which does not scale well will force potentially unwanted compromises, for example the inability to partition an application into the required number of compartments could lead to weakened security.

#### **Small Trusted Computing Base**

The Trusted Computing Base (TCB) is the hardware and software of a system which is trusted to be error free and correct in order for security properties and assumptions to hold true. If a flaw or bug exists in the TCB, it can have wide-ranging and potentially devastating consequences. Since the TCB must be error free, it is desirable for this portion of the system to be as small and simple as possible, to enable easier verification and also reduce the possibility for errors.

#### Secure Compartment Interfaces

Lefeuvre et al. [28] defined compartment interface vulnerabilities (CIVs) and established that simply compartmentalising an application is in most cases not enough. Trust boundaries are introduced where previously there was mutual trust. This means that compartments can be made to misbehave or share private information simply because the exposed interfaces do not sanitise malicious data which is passed into them, for example through confused deputy attacks [63]. Therefore,

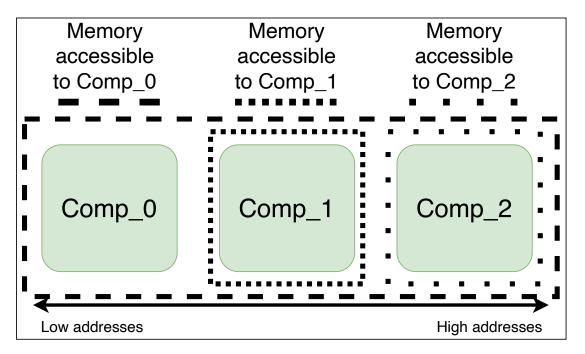

Figure 2.1. Example of sandboxing. Compartments 1 and 2 are sandboxed.

hand in hand with compartmentalisation must be a re-evaluation and hardening of the trust boundaries which this exposes.

#### 2.1.4 Trust Models

The different trust models which are available to someone wishing to compartmentalise a system are described in the following sections.

#### Sandboxing

Sandboxing can be thought of as a sandbox a child plays in. It is a place for them to explore and play, but they are also contained within to avoid them being able to cause damage to anything outside of the sandbox. In a computing sense, an untrusted code module is placed into a sandbox to prevent it from accessing the rest of the system. It is given only what it needs to function and is self-contained within it. In this trust model, the contents of the sandbox are untrusted and everything outside the sandbox is kept safe and implicitly trusted. Many popular applications and libraries such as Chromium [64] and OpenSSH [3] use sandboxing to contain potentially unsafe execution of components such as the decompression and decoders, which are frequently the source of exploits. Sandboxing is illustrated in Figure 2.1.

#### Safeboxing

In contrast to sandboxing, safeboxing trusts what is inside the box and protects it from what is outside. This means that access to data within a safebox must be

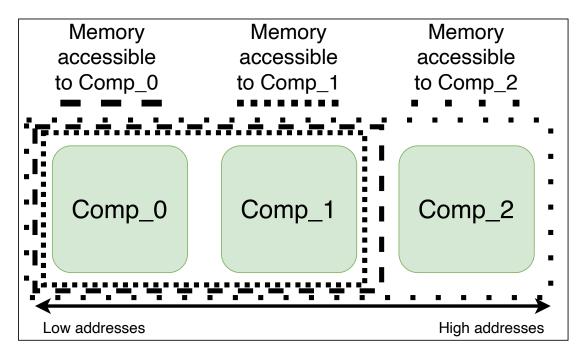

Figure 2.2. Example of safeboxing. Compartment 2 is safeboxed.

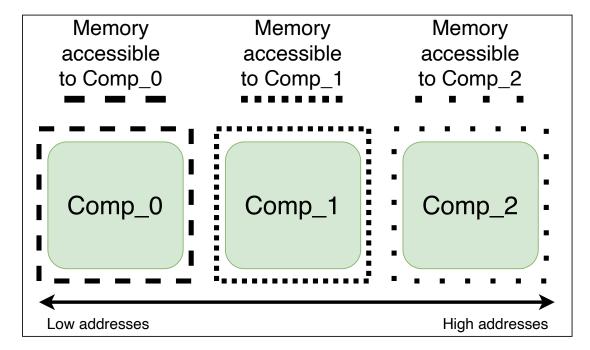

Figure 2.3. Example of mutual distrust.

carefully controlled and data entering from outside the safebox must be carefully sanitised. An example of a use case for safeboxing could be a cryptographic function which is trusted and is protected from compromise by preventing the rest of the system from accessing it. Safeboxing is illustrated in Figure 2.2.

#### **Mutual Distrust**

Mutual distrust is a middle ground between safeboxing and sandboxing. Here, entities distrust each other. Private compartment data must be kept isolated from all other compartments. This model has been used by works including FlexOS [15]. Mutual distrust can be used between an application and its libraries,

where each would like to protect itself from the other in case of compromise in another compartment. Mutual distrust is illustrated in Figure 2.3.

#### 2.2 Mechanisms

Various techniques have been implemented and explored to enforce isolation, these are examined in the following sections.

#### 2.2.1 Page Tables

Page tables are used by the hardware memory management unit to translate virtual to physical addresses. They are widely implemented in modern processors. This gives rise to many approaches to page table based isolation, including Arbiter [65], which provides isolation between application threads by using a different page table for each and LwCs [66] which provides page table based isolation within a process. Page table based isolation is often combined with privilege separation, such as that between user and kernel.

The following sections explore common page table based approaches to isolation.

#### **Processes**

Processes are used to provide isolation between different executing code, by giving each a distinct virtual address space, through the use of a process specific page table. Access to system resources is controlled and granted by the kernel via system calls. A process can be isolated not only from other processes, but also from critical kernel components. Switching compartment involves the kernel switching out the page table for that of another process.

Many compartmentalisation works take advantage of processes to implement isolation between different components of a system. Cali [13] and CompARTist [67] use processes to isolate an application from its libraries, with isolated libraries running in their own process. PtrSplit [12], Privman [68], Privtrans [57] and Salus [69] split an application into two differently privileged compartments. These compartments then run in separate processes. Wedge [59] provides OS primitives to allow developers to split monolithic applications into process-isolated compartments. ProgramCutter [70] uses dynamic analysis to automatically partition an application into separate processes at function granularity.

#### Access Control Bits

Access control bits are implemented as bits within a page table entry [71], [72] and enable access controls to be enforced for different regions of memory, including

the setting of read, write and execute permissions. This is an important feature, since it can prevent a malicious actor from modifying the executable portion of an application in memory, thereby circumventing protection mechanisms. Additionally, it can prevent writable portions of memory from being executed, which could otherwise allow an attacker to execute arbitrary instructions in memory.

#### Second Level Address Translation

Second Level Address Translation (SLAT), also referred to as nested page tables in the literature [73] is a type of hardware assisted virtualisation which makes guest to host address translation more efficient. This means that code can easily be virtualised. SLAT has been implemented by multiple hardware vendors including Intel [74], AMD [75] and ARM [71].

SLAT can be used to compartmentalise an application at the function level such as with SeCage [76] and Virtines [17] all the way to a more coarse grained library level compartmentalisation such as has been implemented by FlexOS [15] with two compartments.

#### Virtual Machines

Virtual Machines were first deployed by IBM with the VM370 time-sharing system [77] and then formally defined by Popok and Goldberg in 1973 [78]. They were introduced as a means to run multiple operating systems or other software which requires a bare-metal view of the machine [79], on the same hardware. Since then, they have grown in popularity, and are primarily used by Infrastructure as a Service (IaaS) providers to run multiple operating systems on server hardware, to serve the needs of numerous different clients. A hypervisor is used to coordinate the various virtualised systems.

Whilst useful to isolate operating systems running on the same hardware from each other, the idea can be extended to isolating applications from each other, by running applications on small operating systems like unikernels (LibOS) which are lightweight. Indeed, works such as FlexOS [15] take advantage of virtualisation to run an application in a unikernel on a host system. NGSCB [80], Proxos [81] and Minibox [82] focus on OS level virtualisation to improve security. Overshadow [83], SP3 [84], Inktag [85] and virtual ghost [86] focus on isolating applications from an untrusted operating system.

#### Mondrian Memory Protection (MMP)

Witchel et al. proposed Mondrian Memory Protection [87], [88] as a way to augment traditional page table based memory management with a special permissions

table for permissions which can be applied to memory regions down to word granularity. This is supported by a protection lookaside buffer (PLB) [89] and register sidecars, which contain the permissions associated with the address in the address registers, used to improve performance.

This allows for multiple compartments within a single address space. Compartment switches are performed by calling addresses or return addresses which are marked in the permissions table as being cross domain calls. This then triggers a compartment switch.

#### Memory Protection Keys (MPK)

Memory protection keys use bits in a page table entry to associate a numeric key with entries. They target isolation within a singe address space. Upon attempting to access memory via a load or store instruction, the current key is checked against the key associated with the page table entry corresponding to the attempted memory access. If the two do not match, a page fault is triggered. Therefore, a protection key corresponds to a compartment. MPK has been implemented by a number of architectures, including x86 [72], [75], RISC-V [11], [90], IBM Power [91] and ARM (ARM domains) [92]. These implementations allow for between 16 (x86 and ARM) - 1024 (RISC-V) compartments to be implemented. MPK on RISC-V is not currently widely available in hardware, and support for ARM domains was dropped in AArch64 meaning that limited work has used the mechanism [58]. This leaves x86 MPK as the only widely proliferated and available implementation of MPK.

x86 MPK compartment switches can be done from user space, via the unprivileged PKRU register, which means that compartment switches can be carried out with low overhead without needing expensive syscalls or other mechanisms to obtain the correct switching privileges. The downside to unprivileged user space access is that x86 MPK on its own, is not sufficient for secure isolation and must be paired with other techniques [11] such as control flow integrity or binary scanning to ensure that a malicious actor does not arbitrarily switch compartments.

MPK mechanisms have been utilised in a number of compartmentalisation works in recent years, including Donky [11], FlexOS [15], Hodor [9], CubicleOS [14], Shreds [58], libMPK [93], Enclosure [44] and by Sung *et al.* using RustyHermit [18].

#### Limitations of Page Tables

Page table based isolation mechanisms often suffer from two key limitations, making them potentially problematic for compartmentalisation.

Translation Lookaside Buffer (TLB) Performance The TLB is implemented in hardware to cache virtual address translations, reducing the cost of performing these translations. Process context switches will frequently cause the TLB to be invalidated and flushed. For example, when switching processes, the page table will be switched out. Although certain modern architectures are compartment aware, it is still likely that the number of TLB misses will increase due to compartment switching. Refilling the TLB with useful predictions is expensive, since it involves accessing main memory. MMP may also suffer from a similar performance penalty to the PLB. Since MPK is used in-process, this does not apply.

Granularity Since page table based approaches are based on the page table, it follows that the smallest unit of isolation is a page. However, pages are coarse. They are typically sized at 4KB, although many modern processors use larger pages. Most data structures will be smaller than the size of a page and so memory usage will be inefficient to facilitate isolation, or a significant amount of data may be overshared.

#### 2.2.2 Software Fault Isolation (SFI)

Software Fault Isolation, introduced by Wahbe et al. [94], is a runtime method for sandboxing memory accesses to occur only within defined bounds. This is done by instrumenting a binary with instructions which check the addresses being used, before they are used. Instrumentation can be inserted by the compiler at compile time, or retrofitted to a binary using binary rewriting. In order to avoid SFI instructions being skipped by an attacker, SFI is usually paired with some form of verification or control flow integrity [95], [96]. SFI normally applies to isolation within a single address space. A large body of research has looked at SFI, including ARMor [97], NaCl [61], [98], /CONFIDENTIAL [99], PittSFIeld [62], Rocksalt [100], XFI [101], LXFI [102], Datashield [103], Occulum [104] and RL-Box [10]. A downside of such a technique being implemented is the performance penalty imposed by adding additional instructions to the application.

In recent years, WebAssembly [105], [106] has emerged as a way to implement SFI with lower overhead. WebAssembly is a memory safe binary instruction format which can be used to run code in sandboxes with high performance. This is useful in applications, such as browsers, to restrict unsafe and untrusted code execution. Additionally, it has been explored in numerous works as a mechanism for compartmentalisation [10], [107]–[110]. RLBox has used Wasm to implement sandboxing in the production FireFox browser [10], [111].

#### 2.2.3 Safe Programming Languages

Popular memory safe programming languages such as Java [112] and Ruby [113] have existed for decades. Memory safe languages have traditionally relied on runtime checks and memory management, which impose a high performance penalty. This has typically made such memory safe languages unsuitable for low-level, performance sensitive systems software. KaffeOS [114], JX OS [115] and J-Kernel [116] implement OSes using Java, however, they are limited by performance and functionality. Singularity OS [117] uses Sing# to achieve memory safety. SPIN [118] uses language safety for security within the kernel only. MirageOS [119] uses OCaml [120] for memory safety.

With the arrival of Rust [121], a memory safe language which requires no expensive memory management, the performance calculus has changed. As a result, many systems which previously used unsafe languages such as C and C++ started exploring Rust [122]–[126]. Redleaf [54] demonstrates the use of Rust to isolate device drivers. Recently, Rust has been added to major OSes including Linux [42], Android [127] and Windows [128]. Most low level kernel software is old and written using C or C++, making the task of porting such software to use memory safe languages, such as Rust, difficult and time-consuming.

#### 2.2.4 Software Capabilities

Software capabilities represent tokens which grant the holder access to objects within the system and can be used to isolate different compartments, whilst still granting bounded and permissions-checked access to certain data. As opposed to hardware capabilities, discussed in Section 2.2.9, software capabilities exist entirely in software implementation, and rely upon software checks to enforce their bounds and permissions. This necessarily results in overhead when compared to implementations which perform the same checks in hardware. Works exploring the use of hardware capabilities to protect within an address space include Mungi [129], Opal [130] and LXFI [102].

Capsicum [131] extends UNIX APIs by providing primitives which allow processes to be placed in a sandbox mode. From there, they may only access system resources such as the file system using capabilities which have been granted to the process.

#### 2.2.5 Memory Encryption

A less studied but interesting technique is the use of cryptography to secure pointers or regions of memory to prevent unauthorised access and tampering. Cryptographic extensions to architectures are often utilised for this purpose, to enable more efficient transformation of data. This has been explored by PointerGuard [132], CCFI [133] and MemSentry [134]. Whilst usually implemented in software, memory encryption has also been explored in hardware, for example, Morpheus [135] and MorepheusII [136]. Trusted Execution Environments (TEEs) also make use of memory encryption. TEEs are described in Section 2.2.6.

#### 2.2.6 Trusted Execution Environments (TEE)

Trusted Execution Environments describe technologies which offer confidentially and integrity. In practice, this means that no external, unauthorised access to data is allowed. Additionally, to ensure integrity, unauthorised entities are unable to modify or replace code within the TEE. This creates a shielded execution environment for code and data, allowing applications to be run in scenarios where the host systems software including the OS and hypervisor is untrusted, for example when using cloud providers to run sensitive applications.

TEE was first defined in "Advanced Trusted Environment: OMTP TR1", published in 2009 [137]. Since then there have been numerous commercial implementations of the technology, including ARM TrustZone [71], Intel SGX [138], Keystone [139], MultiZone [140] and Sanctum [141] for RISC-V. These enable enclaves. The most widely used implementation is ARM TrustZone, which divides the system up into two worlds, secure and normal. This presents a limitation to fine-grained compartmentalisation, since it results in a maximum of two coarse protection domains. Work has been done to combine TEEs with hardware capabilities [142], which could be used to extend TrustZone to enable more fine-grained isolation. Intel SGX allows applications and OSes to create encrypted enclaves to secure components, applications, or even entire OSes.

The use of Intel SGX for compartmentalisation has been studied extensively. Haven [143] and Graphene-SGX [144] run applications within SGX to shield them from the rest of the system. SCONE [145] uses SGX to allow containers to execute securely. SGXBounds [146] provides memory safety for unmodified applications leveraging SGX. Glamdring [147] takes developer annotations for sensitive data, then automatically partitions an application into untrusted and enclave partitions, with the enclave partition then executed in an SGX enclave containing sensitive data and code. SecureKeeper [148] builds upon Apache Zookeeper, using multiple small enclaves to secure user data. Nested Enclaves [149] enable a second tier of isolation within an enclave, through the use of nested enclaves, which are shielded from the rest of the main enclave. CHANCEL [150] sandboxes threads within an enclave to allow an application to securely process requests from different users. Occulum [104] allows multitasking within an enclave, using Software Fault Isolation to isolate between processes.

More recently, another type of TEE has been researched: Confidential Virtual Machines [151]. These enhance the popular Virtual Machine abstraction with the confidentiality and attestability offered by TEEs. Enabled by technologies such as Intel TDX [152], AMD SEV [153], ARM CCA [154] and IBM PEF [155]. Confidential VMs can be used as a mechanism to secure sensitive workloads which are typically run in the cloud. Confidential VMs promise to be more compatible since they are enhanced versions of existing virtual machines and do not require applications to be rewritten, which is necessary to use TEEs. Whereas enclaves focus mainly on process level isolation, confidential VMs focus on entire system isolation. While such technologies offer greater security over traditional virtual machines, they are still vulnerable to attack [156].

#### 2.2.7 Memory Tagging

Memory tagging associates a tag with a portion of memory, with the tag encoded in unused upper bits of pointers. Upon attempted access to memory via a pointer, this tag is compared to that of the memory being accessed. A mismatch will cause the access to fail. This can be used to isolate regions of memory. Modern implementations of memory tagging features include ARM Memory Tagging Extension (MTE) [157], introduced with ARMv8.5, and ADI [158], introduced with the Oracle SPARC M7. The use of memory tagging is increasing with works including Loki [159], Multi-tag [160] and Taxi [161] investigating its use. Furthermore, LLVM provides plugins to accelerate memory tagging using available hardware features [162]. HAKC [163] uses ARM MTE as part of its approach to partitioning the Linux kernel.

#### 2.2.8 Bounds Checking

Bounds checking pointers in hardware is a technique used to constrain memory accesses to within certain bounds allowed for particular pointers. This is often used to prevent common memory safety issues including buffer over- and underflows by preventing such accesses at a potentially low performance cost. These bounds checks can be used to implement isolation between software components.

The most well known implementation is Intel Memory Protection Extensions (MPX). MPX bounds checks pointer accesses by providing instructions to do so. Implementation is optional and relies on a software toolchain to insert checks rather than being performed by default. A number of works have explored the use of MPX, including MemSentry [134]. MPX is no longer included in new CPUs due to numerous performance and security issues identified [164]. Many others have proposed custom hardware, ISA extensions or repurposing of other mechanisms, including AOS [165], Heapcheck [166], Watchdog [167], WatchdogLite [168], Hard-

#### 2.2.9 Hardware Capabilities

Capabilities can be thought of as a natural evolution of bounds checking mechanisms. They control access to memory not only through bounds, but also setting permissions on what can be performed by a capability which is held. First defined in 1966 by Dennis and Van Horn [171], as "locates by means of a pointer some computing object, and indicates the actions that the computation may perform with respect to that object", capabilities have been explored in systems over the years. Hardware capabilities are examined through the lens of memory protection in this thesis. However, they are in general a higher level concept which can be used to protect many different aspects of a system.

Capabilities were first seen on the Burroughs B5000 [171], [172] in 1961. It implemented a *Program Reference Table (PRT)* containing *descriptors* which located code and data segments in memory and *values* which are scalar data elements. Since these are contiguous regions of memory, the *descriptor* provided bounds. Descriptors also included a bit called a tag, to differentiate between *descriptors* and *values*. All memory references and branches went through the *PRT*.

The Plessey System 250 [173] implemented capabilities as 48-bit values, held in special capability registers, which grant the processor access to objects in the system. A capability consisted of three parts, a base address, a limit and access rights. This allowed bounding and the enforcement of permissions. A capability is always held, which points to a *Central Capability Block*, which defines the execution domain. Critically, the System 250 also had protected procedures, which had their own *Central Capability Block* and were accessed through enter capabilities and arguments were accessed via capabilities. Thus, a protected procedure executed in its own domain protected from the caller, before returning to the caller domain. The Cambridge CAP [174], [175] of the same era also implemented capabilities. Capabilities granted access to objects on the CAP system. Like the Plessey system, it also featured protected procedures.

The M-Machine [176] introduced a concept called *guarded pointers*. These 64-bit pointers, which were used to address a 54-bit virtual address space, encoded a tag to identify a pointer, permissions, and a length in the remaining upper bits. *Guarded pointers* could specify data access, code access, protected entry access or *keys*, which were unforgeable tokens, only accessible by a privileged entity.

The PICA system [177], [178] described an extension of a RISC architecture (MIPS). As well as implementing the well established capability hardware features, protection domain crossings were made simple by the provision of protected procedure calls, which grant access to defined entry points of a protection

domain. Alongside this, instructions to clear registers efficiently made domain switches cheap, with the authors noting only 12-15% performance overhead.

Low-fat pointers [24], building upon work done with fat pointers [25], [26] have been implemented more recently, encoding bounds and a tag to ensure the unforgeability of pointers. Bounds checks are implemented in hardware, with the authors noting a 0% performance penalty and a 3% memory overhead.

More recently, capabilities have been implemented as extensions to architectures including ARM and RISC-V, in the form of Capability Hardware Enhanced RISC Instructions (CHERI [179]) and x86 by CHEx86 [170] and

CODOMS [180]. The use of CHERI and its ARM implementation, Morello, is the focus of this thesis. For this reason, a more in-depth look at CHERI is available in Section 2.6.

#### 2.3 Automation

Automation of the compartmentalisation process is tightly linked with the amount of effort required from the developer. Below are described the main methods for implementing compartmentalisation.

#### 2.3.1 Manual Approaches

Manual approaches rely entirely on developer skill and knowledge to partition an application and implement compartmentalisation policies. While this approach can be the most accurate, it is also the most error-prone [16], with compartments granted too many or too few privileges. In the case of complex applications, some data may be missed, leading to incomplete compartmentalisation. An example of this is modifying an application to use CHERI capabilities in hybrid mode [4].

#### 2.3.2 Guided Manual

In a guided manual approach, the developer is still responsible for code annotations or transformations, however an analysis tool such as a compiler provides hints to a developer by identifying shared data and compartment boundaries, making the task easier [10], [16]. There is less risk of error compared to a fully manual approach.

#### 2.3.3 Policy Based

Whereas manual approaches require direct developer intervention to partition a program correctly, policy based compartmentalisation partitions the application based on a compartmentalisation policy which has been provided by the developer in the form of annotations. While this still requires the developer to reason about their requirements, the actual work of compartmentalising is done automatically [9], [13].

#### 2.3.4 Automatic

Fully automatic compartmentalisation is challenging to implement well. Inferring precise data dependencies can be difficult to do accurately [181], which means that such tools often need to err on the side of caution and often overshare to avoid breaking applications. However, automated approaches [57], [70] are regarded as the 'holy grail' since they allow compartmentalisation to be applied easily to applications and so increase adoption. Automation is an active field of research.

#### 2.4 Sharing Data

When a legacy application is compartmentalised, data which was previously accessible to the entire address space now becomes inaccessible to other compartments. This is by design but necessitates the use of mechanisms to restore limited data sharing between compartments. This is important to pass function arguments and return values amongst other data. Data sharing often involves some form of message passing between compartments. For example, for applications partitioned into separate processes, this could take the form of inter-process communication (IPC) [182].

In addition, some mechanisms provide specific communication methods. For example, CHERI capabilities [179] can be used in place of pointers to pass arguments between compartments.

#### 2.5 Compartmentalisation In Practice

Having described the theoretical principles and practical mechanisms of compartmentalisation, the following sections now move on to consider real implementations of compartmentalisation and answer the question: Why is compartmentalisation not mainstream?

#### 2.5.1 Deployed Software

Firefox uses RLBox to isolate itself from its libraries [10]. Libraries are placed into sandboxes. This has been used in deployed Firefox to sandbox performance sensitive web page decompression libraries, including libGraphite. RLBox is a

system which aids in the isolation of applications from their libraries by providing a simple API. It ensures that data-flows between compartments are sanitised by flagging such data-flows during compilation, creating a feedback loop for developers to fix these compile time errors. Isolation is implemented either through process based isolation, or SFI. In production Firefox, a WebAssembly based SFI sandbox is implemented. Analysis showed that by sandboxing libGraphite in production, an 85% performance penalty was applied that that code, which translated to a 50% slowdown for the renderer overall [10].

**OpenSSH** has implemented compartmentalisation techniques for over two decades. The first privilege separation was introduced in 2002, to separate the privileged server process from an unprivileged user authentication process [3]. The privileged server acts as a monitor of the unprivileged user process. OpenSSH also implements sandboxing of potentially unsafe code such as pre-authentication checks which could be exploited by an attacker. The sandboxes can use a variety of mechanisms including SELinux [183] and Capsicum [131] to achieve this.

By implementing privilege separation, two thirds of the source code executes without privileges, including third party libraries such as *zlib*. Due to the lack of data copying, privilege separation is found to not impose a performance penalty [3].

#### 2.5.2 What Is The Problem?

Despite having described many different approaches to compartmentalisation and many different trust models, compartmentalisation is still mostly a toy of academia and is not widely used in applications. There are a number of reasons for this. Firstly, many mechanisms impose a performance overhead, which is simply too high for many [8], [184]. Next, as well as a potential performance penalty, the cost of retrofitting applications which were not designed with compartmentalisation in mind, can be prohibitive without effective automation [13], [70]. Finally, certain mechanisms impose limitations [93], [185], such as a limited number of compartments available with MPK. Such limitations have stopped compartmentalisation from effectively being integrated into everyday software and can be summarised as: too slow, too hard and too limited.

#### 2.6 CHERI

Capability Hardware Enhanced RISC Instructions (CHERI) is a set of extensions for existing RISC architectures including MIPS, RISC-V [179] and later ARMv8 (the implementation is called Morello) [21]. CHERI adds hardware capabilities, described in Section 2.2.9, to existing architectures. Morello has since been implemented in hardware [186] based on an ARM Neoverse N1 SoC [187]. This section,

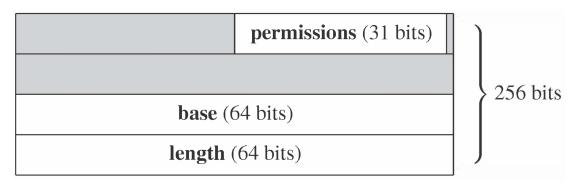

Figure 2.4. The original encoding of a CHERI capability. This image is taken from *The CHERI capability model: Revisiting RISC in an age of risk* [22].

Figure 2.5. The CHERI concentrate capability encoding. This image is taken from Capability Hardware Enhanced RISC Instructions: CHERI Instruction-Set Architecture (Version 8) [179]. a: pointer address,  $B \, \mathcal{E} \, T$ : base and top related to bounds,  $I_E \, \mathcal{E} \, B_E \, \mathcal{E} \, T_E$ : exponent bits, otype: object type, p: permissions.

first introduces CHERI concepts before moving on to a detailed study of the state-of-the-art compartmentalisation works using CHERI, in order to understand how the contribution described later in this thesis fits in to the existing body of work.

#### 2.6.1 An Introduction To CHERI

CHERI was first introduced by Woodruff et al. [22] in 2014. Originally implemented using MIPS [188], it has since been expanded to cover RISC-V and ARMv8 [189]. Since its first introduction, the ISA has also been refined. For example, capabilities were originally encoded using 256-bits on 64-bit architectures, displayed in Figure 2.4. With the introduction of the CHERI concentrate encoding [190] which is shown in Figure 2.5, capabilities can now be encoded in 128-bits for a 64-bit architecture, by utilising floating point encoding, however, not all memory bounds can be represented by this meaning that memory padding could be required.

#### Capabilities

At a high level, a capability can be thought of as a pointer with additional bounds and permissions information attached to it. The result is that an attempted memory access is automatically and atomically checked against these bounds and permissions in hardware to establish whether it is legal. This can be used to enable compartmentalisation in a single address space by restricting the bounds and permissions available to compartment capabilities to a limited portion of the address space.

CHERI capabilities are encoded using 128-bits on 64-bit systems and 64-bits on 32-bit systems. A capability encoding contains a 32- or 64-bit integer base value, which is equivalent to an integer pointer. This is augmented with bounds information in the form of a limit or a length. Bounds information specifies starting at the base what the allowable range of addresses is. Additionally, each capability stores an object type, permissions and a tag.

Since capabilities are double the size of regular pointers, special capability registers must be used to store them. This can either be implemented as a separate register file (CHERI-MIPS) or can be an extension of current general purpose registers providing an additional capability view. The latter is the implementation present on the Morello platform.

In addition to general purpose capability registers, several other registers are extended to enable capability support. These include the Capability Stack Pointer (CSP) which can be used to restrict the stack pointer via a capability, and the Program Counter Capability (PCC) which extends the program counter to bound instruction fetches, acting as a restriction on the code which can be executed. A Default Data Capability (DDC) register is also provided to restrict non-capability memory accesses.

#### Guarded Manipulation & Monotonicity

CHERI enforces monotonicity upon capabilities, which means that new capabilities may only be derived from existing capabilities via special guarded manipulations which prevent a capability from increasing its bounds, it may only narrow them, and prevents capabilities from obtaining additional permissions, it may only reduce permissions. These properties prevent capabilities being manipulated and undermining the protection they offer.

#### Capability Tag

Each capability has a tag associated with it. The tag indicates whether a capability is valid and can be dereferenced (tag set). If the tag is cleared, which can result from attempting to modify or use a capability illegally, then the capability cannot be dereferenced. Capability registers are 129-bits wide to accommodate the tag in bit 128. However, a capability stored in memory is stored separately from its tag to prevent forgery. The tag is architecturally invisible to the programmer. Any attempt to manipulate a capability in memory directly as opposed to using capability instructions will clear the tag associated with that location. When loaded into a register, the associated tag bit is automatically loaded alongside.

## Capability Permissions

Capability permissions indicate what a capability can be used to do. This also includes permissions on the *PCC* and *DDC* capabilities. The capability permissions implemented on Morello are listed in Table 2.1. Restricting capability permissions can be used to enforce lower privileges for compartments, for example, removing the ability to access system registers.

Table 2.1. Permissions available in Morello.

| Permission                                                                        | Purpose                                                                       |  |  |  |

|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--|--|--|

| Global                                                                            | Allow capability to be stored via capabilities that do not have StoreLocalCap |  |  |  |

|                                                                                   | permission set.                                                               |  |  |  |

| Executive                                                                         | Code is executed in executive mode, if this permission is not set, execution  |  |  |  |

|                                                                                   | takes place in restricted mode. These modes have different views of the same  |  |  |  |

|                                                                                   | global registers (register banking).                                          |  |  |  |

| Load                                                                              | Allows load via capability.                                                   |  |  |  |