## PARALLEL CACHE-EFFICIENT ALGORITHMS ON GPUS

## A DISSERTATION SUBMITTED TO THE GRADUATE DIVISION OF THE UNIVERSITY OF HAWAI'I AT MĀNOA IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

## DOCTOR OF PHILOSOPHY

IN

COMPUTER SCIENCE

AUGUST 2023

By

Kyle M. Berney

Dissertation Committee:

Nodari Sitchinava, Chairperson Henri Casanova Peter Sadowski Daniel Suthers June Zhang

Keywords: parallel algorithms, GPU, cache-efficent, bank conflicts, models of computation

Copyright © 2023 by Kyle M. Berney

## **ABSTRACT**

Graphics Processing Units (GPUs) have emerged as a highly attractive architecture for general-purpose computing due to their numerous programmable cores, low-latency memory units, and efficient thread context switching capabilities. However, theoretical research on parallel algorithms for GPUs is challenging due to the multitude of interdependent factors influencing overall runtime. Computational models are commonly employed to provide simplified abstractions of computing system architectures. However, developing a computational model that is both simple and accurate, encompassing all performance-affecting aspects of GPU algorithms, is a seemingly impossible task. Existing GPU models often incorporate numerous variables to account for specific performance factors, rendering them less accessible to researchers.

This dissertation obviates the lack of a widely accepted model of computation for GPUs by instead employing multiple classical parallel models to capture both parallel computational complexity and cache-efficiency. Namely, we leverage existing knowledge and algorithmic techniques from the Parallel Random Access Machine (PRAM), Parallel External Memory (PEM), and Distributed Memory Machine (DMM) models to aid in the design and analysis of GPU algorithms at various levels of detail. We validate and demonstrate our approach through case studies on specific problems (e.g., sorting, searching, and single source shortest paths), providing both theoretical analysis and corresponding empirical results. Our results highlights the applicability of the selected parallel models of computation to GPUs and illustrates how theoretical research can expose valuable insights into the performance of GPU algorithms in practice.

## TABLE OF CONTENTS

| Abstract |       |          |                                                                  |

|----------|-------|----------|------------------------------------------------------------------|

| Li       | st of | Tables   | ${f v}$                                                          |

| Li       | st of | Figure   | es                                                               |

| 1        | Intr  | oducti   | on                                                               |

|          | 1.1   | GPU (    | Overview                                                         |

|          | 1.2   | GPU I    | Models                                                           |

|          |       | 1.2.1    | Discrete Memory Machine (DMM) and Unified Memory Machine (UMM) 5 |

|          |       | 1.2.2    | Hierarchical Memory Machine (HMM)                                |

|          |       | 1.2.3    | Threaded Many-core Memory (TMM)                                  |

|          |       | 1.2.4    | Abstract GPU (AGPU)                                              |

|          |       | 1.2.5    | Abstract Transferring GPU (ATGPU)                                |

|          | 1.3   | Paralle  | el Models of Computation                                         |

|          |       | 1.3.1    | Parallel Random Access Machine (PRAM)                            |

|          |       | 1.3.2    | Parallel External Memory (PEM)                                   |

|          |       | 1.3.3    | Distributed Memory Machine (DMM)                                 |

|          | 1.4   | Organ    | ization                                                          |

| 2        | Para  | allel In | n-place Construction of Implicit Search Tree Layouts             |

|          | 2.1   | Prelim   | inaries                                                          |

|          |       | 2.1.1    | Memory Layouts of Static Search Trees                            |

|          |       | 2.1.2    | Previous Work on Permutations                                    |

|          |       | 2.1.3    | Parallel In-place Computations                                   |

|          | 2.2   | Contri   | butions                                                          |

|          | 2.3   | Involu   | tion Approach                                                    |

|          |       | 2.3.1    | BST Layout                                                       |

|          |       | 2.3.2    | B-tree Layout                                                    |

|          |       | 2.3.3    | van Emde Boas Layout                                             |

|          | 2.4   | Cycle-   | leader Approach                                                  |

|          |       | 2.4.1    | van Emde Boas Layout                                             |

|          |       | 2.4.2    | B-tree Layout                                                    |

|          |       | 2.4.3    | BST Layout                                                       |

|          | 2.5   | I/O O    | ptimizations                                                     |

|          |       | 2.5.1    | Involution-based Algorithms                                      |

|          |       | 2.5.2    | vEB Cycle-leader Algorithm                                       |

|          |       | 2.5.3    | B-tree Cycle-leader Algorithm                                    |

|          | 2.6   | Extens   | sions to non-perfect trees                                       |

|          | 2.7   | Experi   | imental Optimizations                                            |

|          |       | 2.7.1    | Query Optimization                                               |

|          |       | 2.7.2    | Hybrid BST Layout                                                |

|          |       | 2.7.3    | Modified van Emde Boas Layout                                    |

|          | 2.8   | Experi   | iments                                                           |

|          |       | 2.8.1    | Methodology                                                      |

|              |       | 2.8.2 Results                                            | 5 |

|--------------|-------|----------------------------------------------------------|---|

|              | 2.9   | Conclusion                                               | 7 |

| 3            | A P   | Parallel Priority Queue for Single-Source Shortest Paths | 9 |

|              | 3.1   | Preliminaries                                            | 9 |

|              |       | 3.1.1 Single-Source Shortest Paths                       | 9 |

|              |       | 3.1.2 Priority Queue                                     | 1 |

|              | 3.2   | Contributions                                            | 3 |

|              | 3.3   | Bucket Heap                                              | 4 |

|              |       | 3.3.1 Sequential Bucket Heap                             | 4 |

|              |       | 3.3.2 Parallel Bucket Heap                               | 5 |

|              | 3.4   | Analysis                                                 | 3 |

|              |       | 3.4.1 PRAM Analysis                                      | 8 |

|              |       | 3.4.2 I/O Analysis                                       | 9 |

|              | 3.5   | Experiments                                              | Э |

|              |       | 3.5.1 Implementation Details                             | O |

|              |       | 3.5.2 Methodology                                        | 1 |

|              |       | 3.5.3 Runtime Results                                    | 2 |

|              | 3.6   | Conclusion                                               | 3 |

| 4            | Woı   | rst-Case Inputs for Pairwise Merge Sort 68               | 5 |

|              | 4.1   | Preliminaries                                            | 6 |

|              |       | 4.1.1 GPU Pairwise Merge Sort                            | 6 |

|              |       | 4.1.2 Related Work                                       | 7 |

|              |       | 4.1.3 Our approach                                       | 7 |

|              | 4.2   | Worst-Case Bank Conflict Analysis                        | 9 |

|              | 4.3   | Experimental Results                                     | 4 |

|              |       | 4.3.1 Methodology                                        | 4 |

|              |       | 4.3.2 Results                                            | 5 |

|              | 4.4   | Conclusion                                               | 6 |

| <b>5</b>     | Ban   | ak Conflict Free Divide-and-Conquer Algorithms           | 0 |

|              | 5.1   | Preliminaries                                            | 1 |

|              | 5.2   | Load-Balanced Dual Subsequence Gather                    |   |

|              |       | 5.2.1 Coprime                                            |   |

|              |       | 5.2.2 Not Coprime                                        |   |

|              |       | 5.2.3 Thread Block                                       | 9 |

|              | 5.3   | Experiments                                              | 9 |

|              |       | 5.3.1 Results                                            | 2 |

|              | 5.4   | Conclusion                                               | 3 |

| 6            |       | ${f nclusion}$                                           | 5 |

| $\mathbf{A}$ | Nur   | mber Theory                                              | 6 |

| Bi           | bliog | ${ m graphy}$                                            | 9 |

## LIST OF TABLES

| 2.1 Asymptotic time and I/O complexity bounds of each of our in-place algorithms for |                                                                                      |    |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----|

|                                                                                      | permuting a sorted array into a particular search tree layout                        | 17 |

| 2.2                                                                                  | Number of queries needed for it to be beneficial (compared to an equal number of     |    |

|                                                                                      | binary search queries) to perform each of the search tree layout permutations on     |    |

|                                                                                      | each of our GPU platforms                                                            | 37 |

| 3.1                                                                                  | Comparison of priority queue operations in different sequential and parallel models. | 53 |

| 5.1                                                                                  | Descriptions of the main parameters for the load-balanced dual subsequence gather.   | 84 |

## LIST OF FIGURES

| 2.1          | BST layout for $N = 15$                                                                                  | 13  |

|--------------|----------------------------------------------------------------------------------------------------------|-----|

| 2.2          | Level-order B-tree layout for $N=26$ and $B=2$                                                           | 13  |

| 2.3          | van Emde Boas (vEB) layout for $N=15.$                                                                   | 14  |

| 2.4          | Illustration of the series of swaps needed to sequentially perform the equidistant                       |     |

|              | gather operation for $r = l$                                                                             | 21  |

| 2.5          | Illustration of the distinct cycles of the equidistant gather operation for $r = l$                      | 29  |

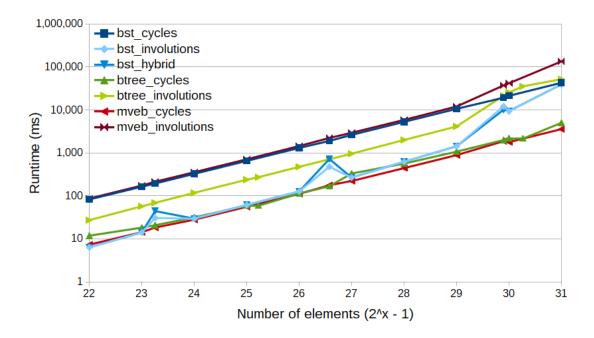

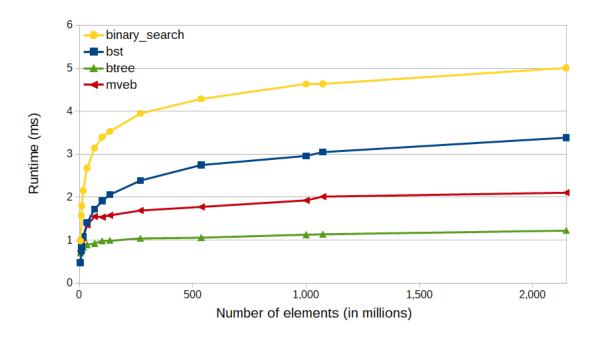

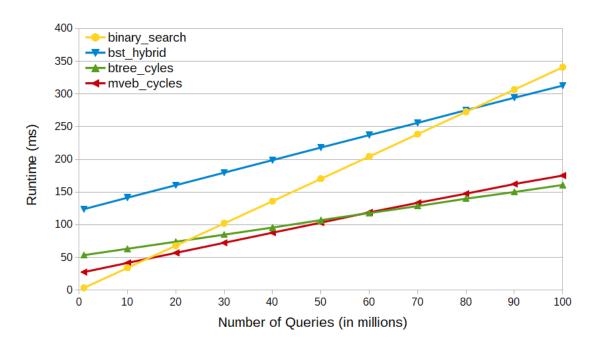

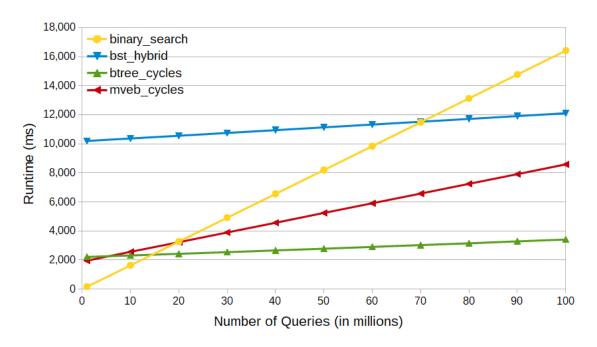

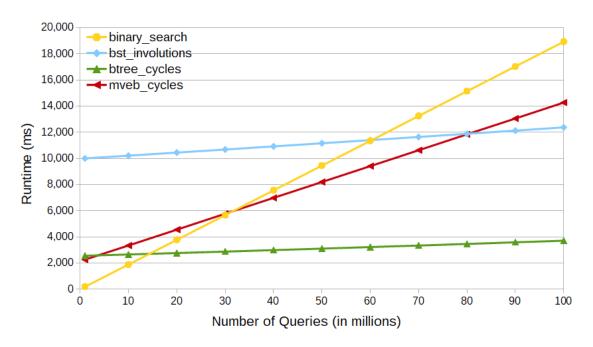

| 2.6          | Average time to permute a sorted array using each permutation algorithm on the                           |     |

|              | NVIDIA K40                                                                                               | 38  |

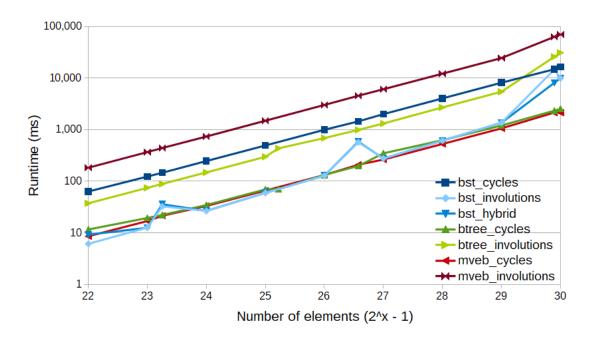

| 2.7          | Average time to permute a sorted array using each permutation algorithm on the                           |     |

|              | NVIDIA Quadro M4000                                                                                      | 39  |

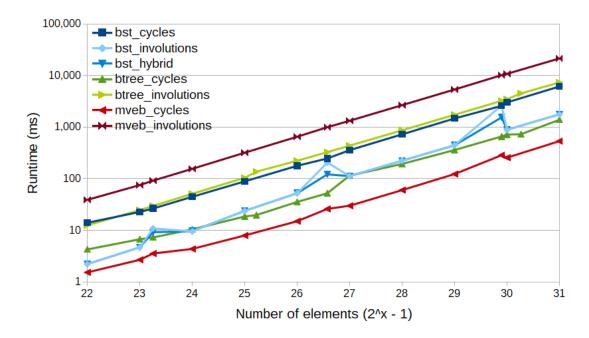

| 2.8          | Average time to permute a sorted array using each permutation algorithm on the                           |     |

|              | NVIDIA GeForce RTX 2080 Ti                                                                               | 39  |

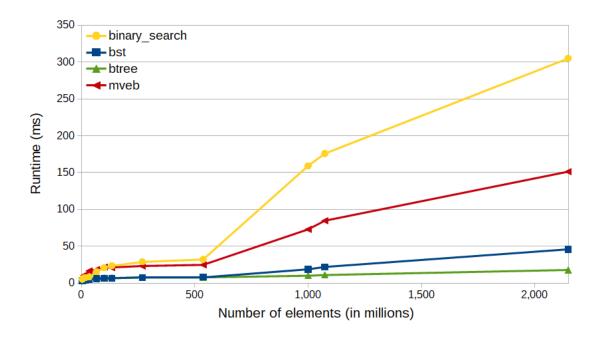

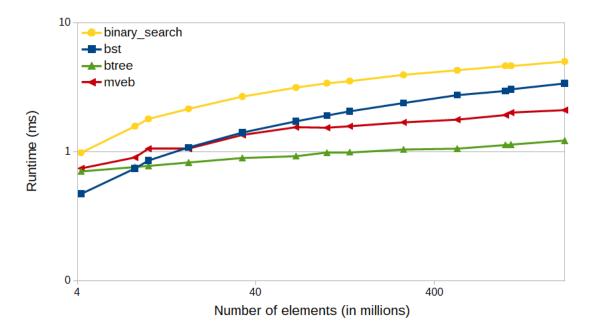

| 2.9          | Average time to perform 1 million queries on each search tree layout and binary                          |     |

|              | search on a sorted array on the NVIDIA K40                                                               | 40  |

| 2.10         | Average time to perform 1 million queries on each search tree layout and binary                          |     |

|              | search on a sorted array on the NVIDIA K40                                                               | 40  |

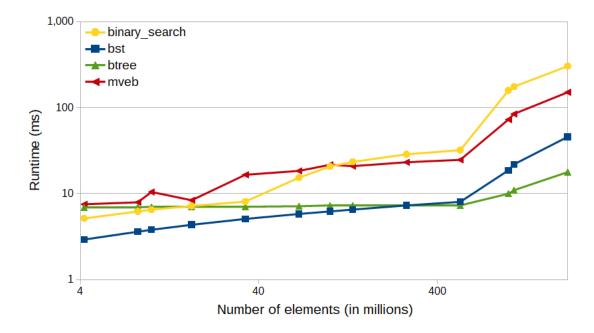

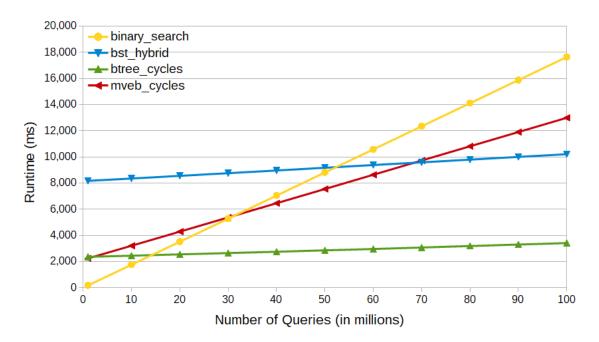

| 2.11         | Average time to perform 1 million queries on each search tree layout and binary                          |     |

|              | search on a sorted array on the NVIDIA Quadro M4000                                                      | 41  |

| 2.12         | Average time to perform 1 million queries on each search tree layout and binary                          |     |

|              | search on a sorted array on the NVIDIA Quadro M4000                                                      | 41  |

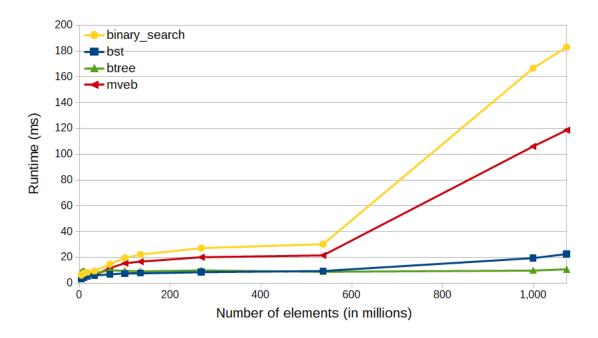

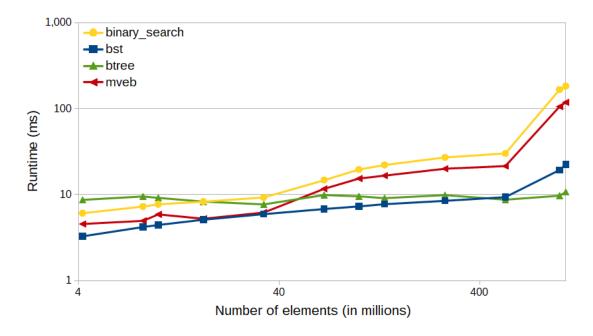

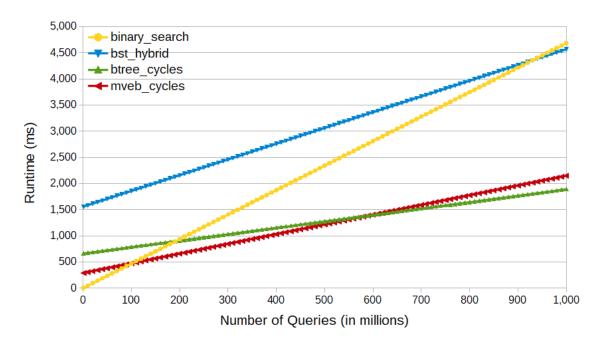

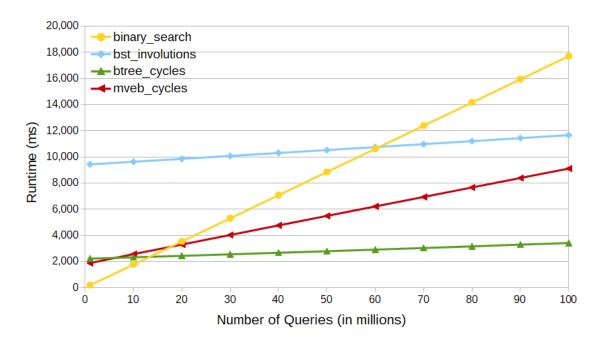

| 2.13         | Average time to perform 1 million queries on each search tree layout and binary                          |     |

|              | search on a sorted array on the NVIDIA GeForce RTX 2080 Ti                                               | 42  |

| 2.14         | Average time to perform 1 million queries on each search tree layout and binary                          |     |

|              | search on a sorted array on the NVIDIA GeForce RTX 2080 Ti                                               | 42  |

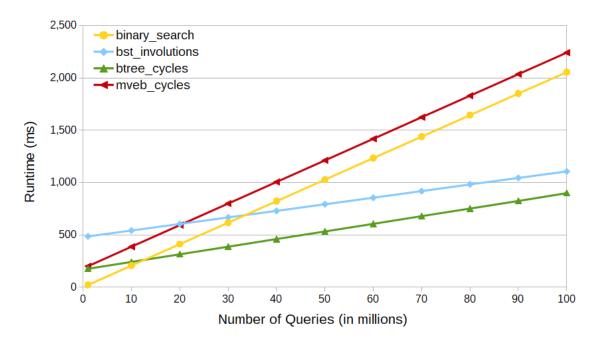

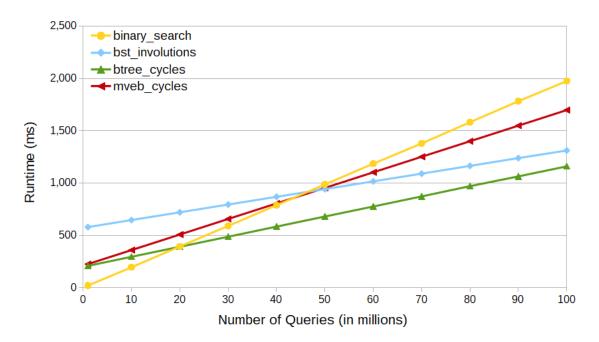

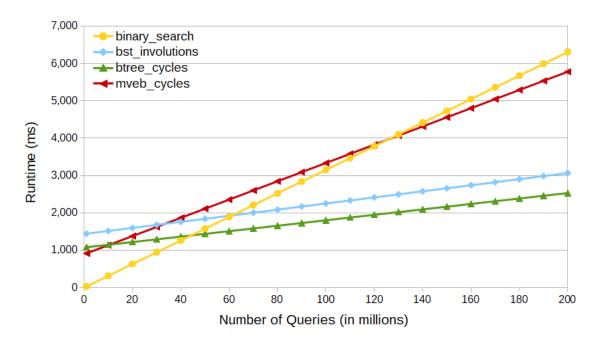

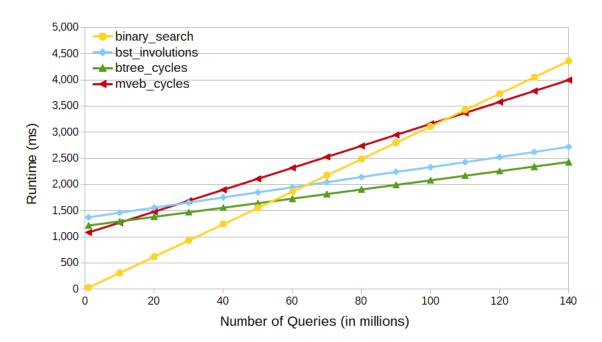

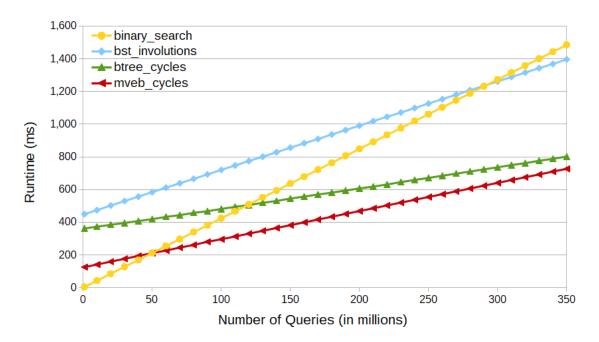

| 2.15         | Combined time to permute and query each layout on the NVIDIA K40 with $N=100$                            |     |

|              | million elements.                                                                                        | 43  |

| 2.16         | Combined time to permute and query each layout on the NVIDIA Quadro M4000                                |     |

|              | with $N = 100$ million elements                                                                          | 43  |

| 2.17         | Combined time to permute and query each layout on the NVIDIA RTX 2080 Ti with                            | 4.4 |

| 3.10         | N = 100 million elements                                                                                 | 44  |

| 2.18         | Combined time to permute and query each layout on the NVIDIA K40 with $N = \frac{229}{100}$              | 4.4 |

| 2.10         | 2 <sup>29</sup> – 1 elements                                                                             | 44  |

| 2.19         | Combined time to permute and query each layout on the NVIDIA Quadro M4000 with $N = 2^{29} - 1$ elements | 45  |

| 2 20         |                                                                                                          | 45  |

| 2.20         | Combined time to permute and query each layout on the NVIDIA RTX 2080 Ti with $N=2^{29}-1$ elements      | 45  |

| 0 01         | $N = 2^{N} - 1$ elements                                                                                 | 45  |

| 4.41         | billion elements                                                                                         | 46  |

| ) <u>)</u> ) | Combined time to permute and query each layout on the NVIDIA Quadro M4000                                | 40  |

| <u> </u>     | with $N=1$ billion elements                                                                              | 46  |

|              | WINT IT - I DIMON DICHIONO,                                                                              | -10 |

| 2.23 | Combined time to permute and query each layout on the NVIDIA RIX 2080 Ti with $N=1$ billion elements                | 47 |

|------|---------------------------------------------------------------------------------------------------------------------|----|

| 2.24 | Combined time to permute and query each layout on the NVIDIA K40 with $N=$                                          |    |

|      | $2^{30}-1$ elements                                                                                                 | 47 |

| 2.25 | Combined time to permute and query each layout on the NVIDIA Quadro M4000 with $N=2^{30}-1$ elements                | 48 |

| 2.26 | Combined time to permute and query each layout on the NVIDIA RTX 2080 Ti with $N=2^{30}-1$ elements                 | 48 |

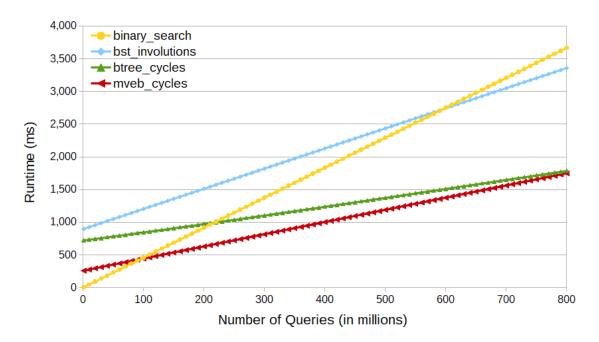

| 3.1  | Illustration of the sequential bucket heap structure of Brodal et al. [15]                                          | 54 |

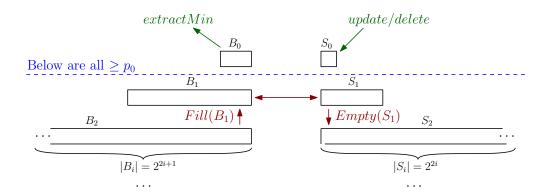

| 3.2  | Illustration of the dependencies when performing a series of operations                                             | 57 |

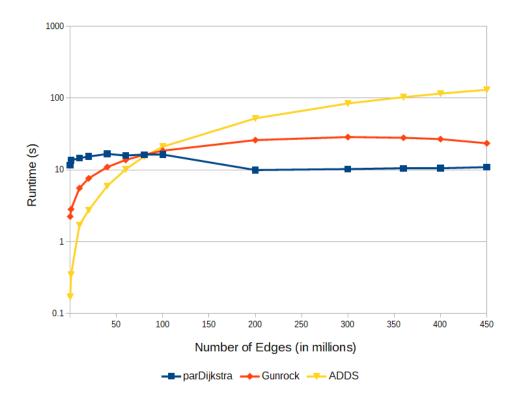

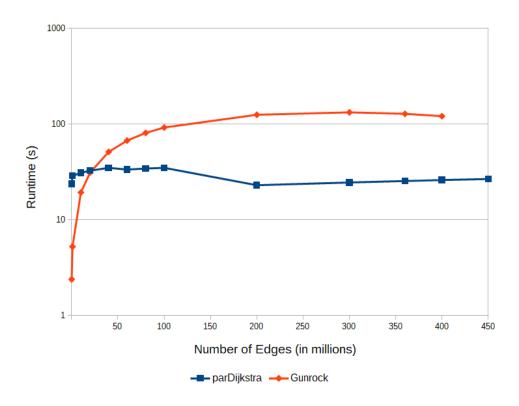

| 3.3  | Average runtime (in seconds) on the generated random DAGs on a RTX 2080 Ti                                          | 63 |

| 3.4  | Average runtime (in seconds) on the generated random DAGs on a Quadro M4000 $$ .                                    | 64 |

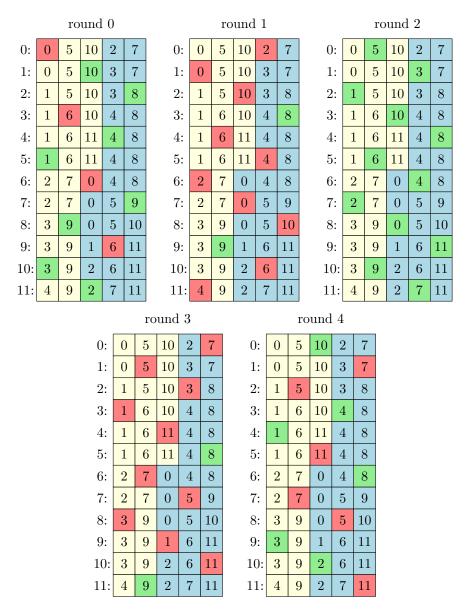

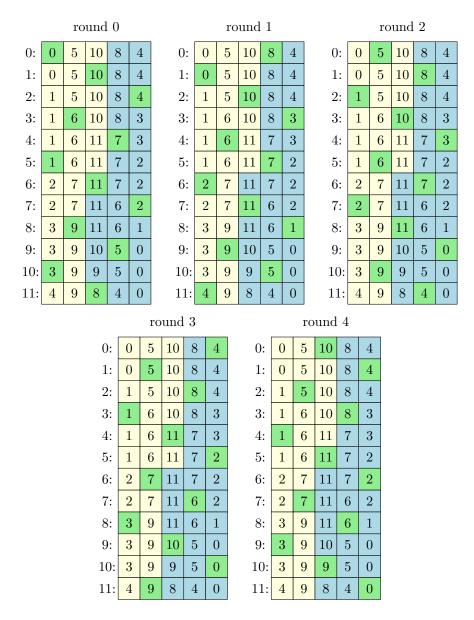

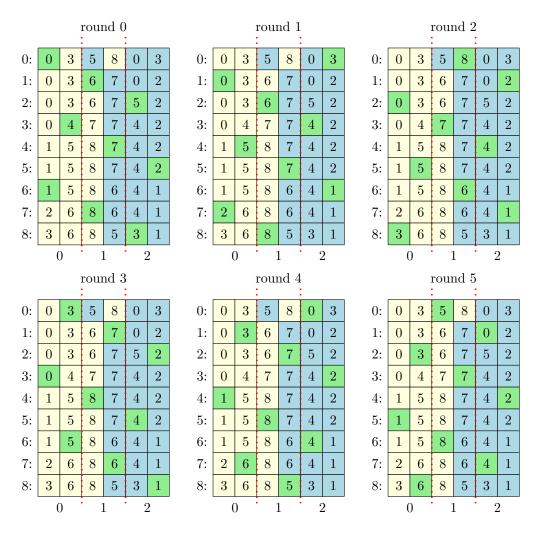

| 4.1  | Visualization of the constructed worst case inputs for a single warp for $w=12.$                                    | 74 |

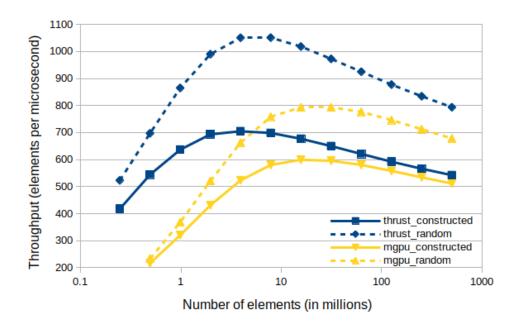

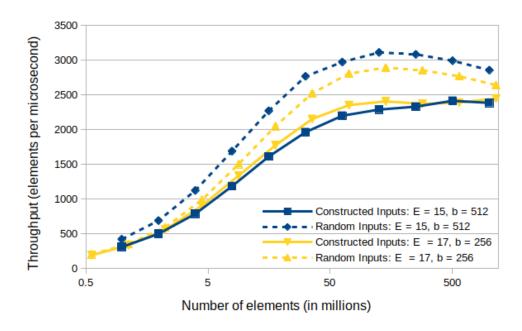

| 4.2  | Throughput results for both Thrust and Modern GPU on the Quadro M4000                                               | 76 |

| 4.3  | Throughput results for Thrust on the RTX 2080 Ti                                                                    | 77 |

| 4.4  | Throughput results for Modern GPU on the RTX 2080 Ti                                                                | 78 |

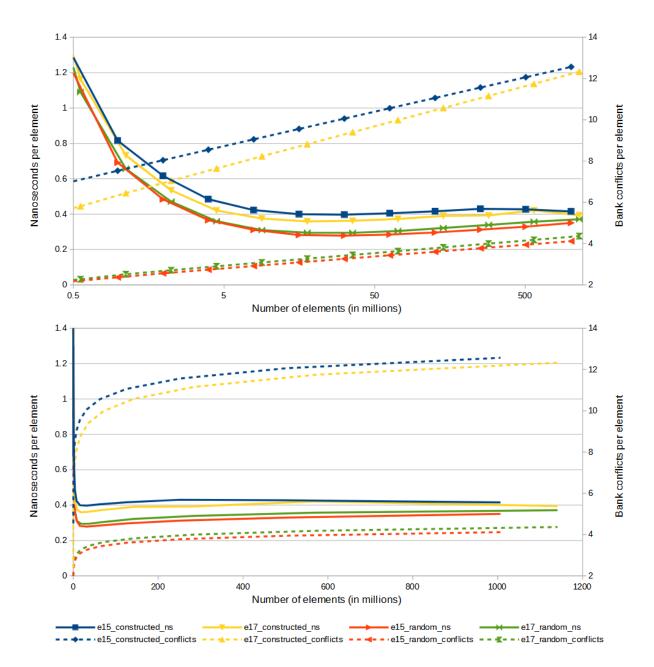

| 4.5  | Runtime (in nanoseconds) per element and bank conflicts per element for Thrust on the RTX 2080 Ti                   | 79 |

| 5.1  | Visualization of strided accesses in shared memory with $w=12$                                                      | 82 |

| 5.2  | Depiction of the read stalls caused by threads in a warp accessing up to 2 elements                                 |    |

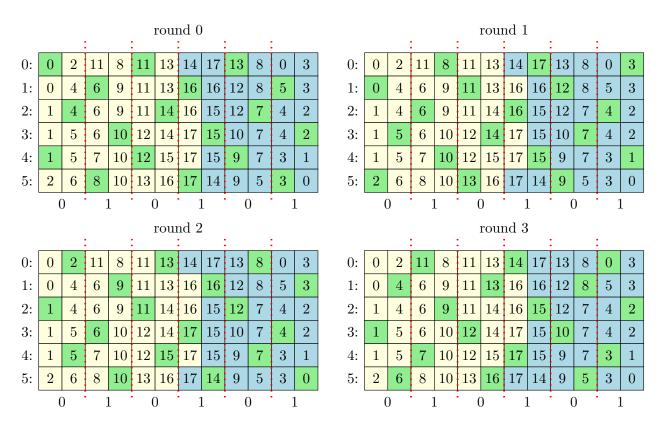

|      | per round for $w = 12$ , $E = 5$ , and $d = 1$ (i.e., coprime) on arbitrary input                                   | 85 |

| 5.3  | Shared memory accesses performed by a warp in the load-balanced dual subsequence                                    |    |

|      | gather for $w = 12$ , $E = 5$ , and $d = 1$ (i.e., coprime) on an arbitrary example input                           | 86 |

| 5.4  | Shared memory accesses performed by a warp in the load-balanced dual subsequence                                    |    |

|      | gather for $w = 9$ , $E = 6$ , and $d = 3$ (i.e., not coprime) on an arbitrary example input.                       | 88 |

| 5.5  | Shared memory accesses performed by a thread block in the load-balanced dual                                        |    |

|      | subsequence gather for $u = 18$ , $w = 6$ , $E = 4$ , and $d = 2$ (i.e., not coprime) on an arbitrary example input | 90 |

| 5.6  | arbitrary example input                                                                                             | 90 |

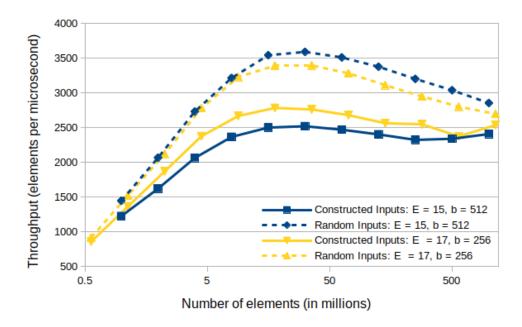

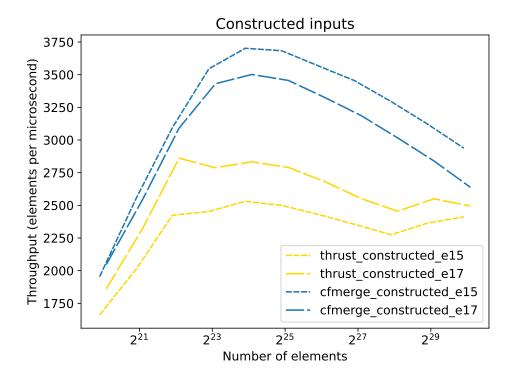

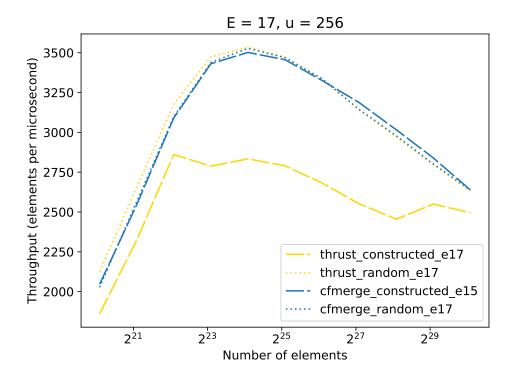

| 5.0  | RTX 2080 Ti using the constructed worst-case inputs                                                                 | 91 |

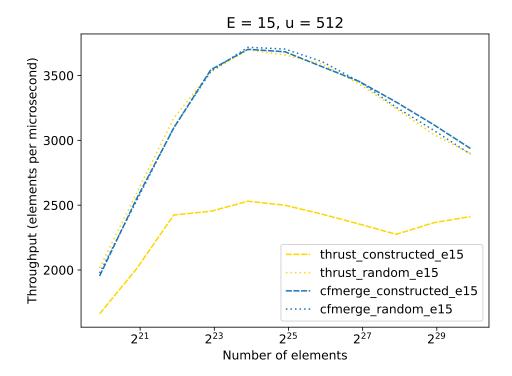

| 5.7  | Throughput results (elements per microsecond) for Thrust and CF-Merge on a NVIDIA                                   | JI |

| ~··  | RTX 2080 Ti using parameters $E = 15$ and $u = 512$                                                                 | 92 |

| 5.8  | Throughput results (elements per microsecond) for Thrust and CF-Merge on a NVIDIA                                   |    |

|      | RTX 2080 Ti using parameters $E = 17$ and $u = 256$                                                                 | 93 |

## CHAPTER 1 INTRODUCTION

Within the past decade, graphics processing units (GPUs) have become an increasingly popular and powerful numerical coprocessor. Modern day GPUs provide thousands of physical cores, lightweight context switching between virtual threads, and low-latency memory units. However, due to the complexity of the GPU architecture, leveraging the full computational power of GPUs is a challenging task. In general, a high performance GPU algorithm must be both highly parallel and cache-efficient. In addition, various interdependent factors must be considered such as: the hierarchical organization of threads, the allocation of hardware resources (e.g., the number of registers used per thread), and the maximum number of active threads scheduled onto the hardware (known as occupancy).

Across various scientific disciplines, models are used to facilitate the understanding of a particular system and/or phenomena. For traditional parallel central processing unit (CPU) systems, numerous parallel computational models have been developed that provide a simplified, but relatively accurate, abstract view of a modern multi-core CPU architecture. These models allow theoretical researchers to design and analyze provably efficient parallel algorithms that can then be implemented and optimized on CPU systems by experimental researchers. In contrast, while several computational models for GPUs have been developed, none have been widely used yet. One reason for this is the complexity of the GPU architecture, which makes it a difficult task to provide a simple and accurate abstract model of the GPU. This generally leads to GPU models that contain a plethora of variables to account for the various factors that can impact the overall runtime. Without a widely accepted model of computation for GPUs, there currently does not exist a standard approach on how to theoretically develop and analyze algorithms for GPUs.

Rather than utilizing a single GPU model that aims to provide a single overall runtime, in this dissertation, the approach is to use several parallel models to provide a set of complexity measures that captures both parallel computational complexity and parallel cache-efficiency. This approach has the additional advantage of leveraging past knowledge and algorithmic techniques that have already been developed in these parallel models. Furthermore, if an overall runtime measure is needed, the resulting set of complexity measures can generally be reused in more accurate and elaborate GPU models (either algorithmic or performance models). For example, I/O-complexity metrics are typically considered with other factors such as bandwidth and latency to the specific memory unit.

The remainder of this chapter is organized as follows: in Section 1.1 we provide an overview of the GPU; in Section 1.2 we review models of computation developed for GPUs; in Section 1.3 we review the parallel models of computation that we adpot for the GPU; and in Section 1.4 we present an overview of the problems considered in this dissertation.

## 1.1 GPU Overview

CUDA (Compute Unified Device Architecture) [85, 86] is a parallel software platform that allows NVIDIA GPUs to be programmed for general purpose computing (e.g., using high-level languages such as C++). As each new generation of NVIDIA GPUs feature architectural improvements over previous generations, a compute capability number is assigned to each GPU model that identifies specific architectural features that the particular GPU has. We say a compute capability number x.y, has a major number of x and a minor number of y. As a rule, significant architectural changes results in an increase in the major number; and smaller architectural changes results in an increase in the minor number. Thus, newer GPU models always have a compute capability number greater than or equal to older GPU models.

From a high-level perspective, a GPU program is composed of a sequence of special procedures that execute on a GPU, called kernels. Each kernel is executed in parallel by a set of virtual threads, called a grid. A grid is organized into equal sized groups of threads, called  $thread\ blocks$ ; and threads in a thread block are partitioned into groups of w threads, called  $thread\ blocks$ ; and threads in a thread block are partitioned into groups of threads, called  $thread\ blocks$ ; and  $threads\ blocks$ , where each  $thread\ blocks$  in a grid is launched onto the GPU, the thread blocks of the grid are distributed to available  $thread\ blocks$ , and warps within each thread block are distributed to  $thread\ blocks$ .

All SMs on a GPU are connected to a large and slow memory space, called *global memory*; a hardware managed L2 cache; and two read-only memory spaces, *constant memory* and *texture memory*. All cores on a SM are connected to a fast and small memory space, called *shared memory*; a hardware managed L1 cache; and two read-only hardware managed caches for accesses to constant and texture memory, called *constant cache* and *texture cache* respectively. Lastly, each SM processing block contains a very fast and small *register memory* space, a warp scheduler, a dispatch unit, and a hardware managed L0 instruction cache.

Global memory: If threads in a warp concurrently access contiguous global memory locations, then these accesses can be *coalesced* together into as few global memory transactions as possible (depending on the cache-line size and size of data elements accessed). In contrast, accessing global memory locations that are strided by w locations will maximize the number of global memory transactions. For example, for 4-byte data elements, performing coalesced global memory access results in O(1) number of global memory transactions compared to O(w) global memory transactions for uncoalesced global memory accesses.

Constant and Texture memory: Constant and texture memory are both read-only memory units that have corresponding caches within each SM, however, they differ in their optimal access

patterns. Texture memory is optimized for 2D spatial locality, i.e., if we lay out the memory space as a 2D array then to achieve peak bandwidth we want threads in a warp to concurrently access "nearby" elements. For constant memory, peak bandwidth is achieved when threads in a warp concurrently access the same memory location. If distinct memory locations are accessed, then the requests are serialized.

Shared memory: Shared memory is organized into w memory modules, also known as memory banks. Each 128-byte aligned contiguous memory segment is distributed across w=32 memory banks, so that each bank holds a 4-byte word. (For GPUs with compute capability strictly less than 5.0, memory banks can be configured to hold 8-byte words from a 256-byte aligned contiguous memory segment.) If all active threads in a warp concurrently access shared memory addresses that map to distinct memory banks, then each bank can serve the requests in parallel, known as bank conflict free access. However, if there exists a bank with k memory requests, then a k-way bank conflict occurs and the bank must serve the k memory requests in a serial manner. One exception is that threads are allowed to access the same shared memory location in the same memory bank without causing a bank conflict.

**Local memory:** In certain situations, the compiler may store data, whose scope is local to an individual thread, in *local memory* instead of register space. In particular, local memory will be used if there is insufficient space in registers or for arrays/data structures that the compiler determines may be accessed dynamically. It is important to note that the cost of accessing local memory is comparable to the cost of accessing global memory.

L1 and L2 cache: For GPU models with compute capability strictly less than 6.0, by default the L1 cache is used to cache accesses to local memory and the L2 cache is used to cache accesses to global memory. Using a compiler flag or inline PTX assembly code, the caching policy can be modified to additionally allow the caching of global memory accesses in L1 cache. (The compiler flag will change the caching policy for all accesses in the compiled program, while inline PTX assembly code allows for the caching policy to change on a per access basis.) However, changing the caching policy will also result in a change to the cache-line size to global memory. If only the L2 cache is used to cache accesses to global memory, then the cache-line size used is 32 bytes. On the other hand, if both the L2 and L1 cache are used to cache accesses to global memory, then the cache-line size used is increased to 128 bytes. For GPUs with compute capability 6.0 and higher, the default policy is to have global memory cached in both L1 and L2 cache; and a compiler flag or inline PTX assembly code can be used to change the policy to global memory cached in only L2 cache. Regardless of the cache setting used, the cache-line size to global memory is 32 bytes for these GPUs.

**Synchronization primitives:** A synchronization primitive syncthreads is provided to allow threads in the same thread block to synchronize with each other. For compute capability 7.0 and above, intra-warp synchronizations need to be additionally managed via a syncwarp primitive.

Warp scheduler: Each warp scheduler handles a static set of warps, where in each instruction time step, a warp scheduler can issue a single instruction for one of its active warps. Therefore, threads within a warp executing the same instruction are executed concurrently; this behavior is called Single-Instruction Multiple-Threads (SIMT). Prior to compute capability 7.0, if threads within a warp diverge in code (e.g., from a conditional statement), then each branch is executed serially. Hence, the execution of threads could be correctly viewed as Single-Instruction Multiple-Data (SIMD), i.e., lockstep execution of threads. Starting with compute capability 7.0, the warp scheduler maintains a program counter for each thread in a warp (rather than a single program counter for all threads in a warp). This allows for greater flexibility with branch divergence in code, as branches are no longer executed in a serial manner. Due to this, the behavior of threads is no longer restricted to lockstep execution.

Latency hiding: In order to keep the GPU hardware as busy as possible (i.e., minimize the amount of time that processors on the GPU are idle), GPUs are able to perform fast context switching between warps scheduled on the SM processing block. This effectively allows for the pipelining of memory accesses, either through having a sufficient number of warps available to be scheduled onto a SM processing block or by utilizing instruction-level parallelism (ILP), i.e., pipelining independent instructions by a single thread. The ratio of the number of active warps to the maximum number of possible active warps (hardware imposed), called *occupancy*, is a typical metric that is used to measure how well an algorithm allows the GPU hardware to hide latency via context switching. Achieving high occupancy is not as simple as launching a large number of threads, as each thread may require additional hardware resources (e.g., register or shared memory space) which are limited.

Warp-communication intrinsics: Starting with the introduction of the Kepler architecture (compute capability 3.0) in 2012, NVIDIA GPUs include warp-communication intrinsics that allow for data transfer and communication between threads in a warp.

- shuffle(variable, i) reads the value of variable from the i-th threads register space. Requires compute capability 3.0 and higher.

- vote(predicate) returns a bitstring of length w, where the i-th bit is set to 1 if the i-th thread in the warp evaluates the predicate to be true. Requires compute capability 3.0 and higher.

- vote\_all(predicate) returns true if all threads evaluates predicate to be true; otherwise returns false (i.e., reduction-and-broadcast).

- vote\_any(predicate) returns true if any thread evaluates predicate to be true; otherwise returns false (i.e., reduction-and-broadcast).

- match(variable) returns a bitstring of length w, where the i-th bit is set to 1 if the variable stored in the i-th threads register space is equal to the current threads value of variable; and 0 otherwise (i.e., broadcast-and-compare). Requires compute capability 7.0 and higher.

- reduce(variable, destination) performs a warp wide reduction operation (add, min, max, or, xor) on variable for each thread in the warp and stores the result in destination. Requires compute capability 8.0 and higher.

Additionally, certain bit-level primitives are provided:

- brev(x) reverses the bit order of x.

- clz(x) returns the number of consecutive high-order bits set to 0 in x.

- ffs(x) returns the index of the first least-significant bit set to 1 in x.

- popc(x) returns the number of bits set to 1 in x.

## 1.2 GPU Models

In this section, we provide a literature review of computational models designed directly for GPUs. Note that we present only computational models (i.e., algorithmic models), rather than performance models that rely on benchmark suites to calibrate variables (e.g., the number of clock cycles to perform an operation or memory access).

## 1.2.1 Discrete Memory Machine (DMM) and Unified Memory Machine (UMM)

The Discrete Memory Machine (DMM) and Unified Memory Machine (UMM) models focus on memory access to shared memory and global memory, respectively [82]. In both models, p threads are connected to w memory banks through a common memory management unit (MMU). Additionally, each thread has access to r local registers. Threads are partitioned into groups of w threads, called warps, and operate in lock-step. Warps are scheduled in a round robin manner, where each thread in the active warp is able to request a single memory access. Threads are restricted to a single active memory request, i.e., a thread cannot send another memory request until the previous request finishes. Data is stored across the w memory banks in a strided manner, i.e., data stored at memory address i is located in memory bank i (mod w). The latency of a memory access is denoted l (i.e., time for a memory request to complete). Note that w memory banks implies a bandwidth of w, since each memory bank can only processes a single memory request at a time.

The difference between the DMM and UMM models is the way that the MMU is connected to the w memory banks. In the DMM, each memory bank has its own dedicated address line connecting to the MMU; and in the UMM, all memory banks share the same address line. Therefore, in the DMM, memory cells in different memory banks can be accessed in a single time step (analogous to bank conflict free access in shared memory). While in the UMM, groups of w consecutive memory cells, called address groups, can be accessed in a single time step (analogous to coalesced access in global memory).

## 1.2.2 Hierarchical Memory Machine (HMM)

The Hierarchical Memory Machine (HMM) model aims to model a whole GPU by combining a single UMM with multiple DMMs (Section 1.2.1) [83]. The HMM consists of d DMMs, each with d/p threads, and a single UMM of p threads (same threads used in the d DMMs). Each of the d DMMs execute independently, hence, are analogous to a streaming multiprocessor on a GPU. The latency of each of the DMMs are considered to be constant and the latency of the UMM is defined as l. The remaining parameters are the same as in Section 1.2.1.

## 1.2.3 Threaded Many-core Memory (TMM)

The Threaded Many-core Memory (TMM) model reflects the architecture of machines that are characterized by a large number of threads which are able to hide latency to memory by taking advantage of fast context switching of threads [75]. The authors argue that the number of memory accesses does not matter, as long as a sufficient number of threads are available to hide latency. Thus, the TMM model aims to bound the number of threads needed in order to sufficiently hide latency.

The TMM model consists of a 2-level memory hierarchy: a slow global memory and a fast local memory of size Z shared by a group of Q threads, called *core groups*. All threads in a core group execute in lock-step. Data elements in slow global memory are transferred to fast local memory in chunks of C contiguous elements with latency L. P is the total number of processors and X is the hardware maximum number of threads that can be scheduled onto a single core (due to various resource constraints such as number of registers).

The performance metrics in this model are: work, denoted  $T_1$ ; span, denoted  $T_{\infty}$ ; total number of global memory chunk transfers (i.e., global memory transactions), denoted M; number of threads per core, denoted  $\tau$ ; and the amount of local memory used per thread, denoted S. Let  $T_E$  be the effective work (considers both computation and memory accesses),  $T_P$  be the runtime using P processors, and  $S_P$  be the speedup using P processors.

$$T_E = O\left(\max\left(T_1, rac{M \cdot L}{ au}

ight)

ight)$$

$$\begin{split} T_P &= O\left(\max\left(\frac{T_E}{P}, T_\infty\right)\right) = O\left(\max\left(\frac{T_1}{P}, T_\infty, \frac{M \cdot L}{\tau \cdot P}\right)\right) \\ S_P &= \frac{T_1}{T_P} = \Omega\left(\min\left(P, \frac{T_1}{T_\infty}, \frac{P \cdot T_1 \cdot \tau}{M \cdot L}\right)\right) \end{split}$$

## 1.2.4 Abstract GPU (AGPU)

The Abstract GPU (AGPU) model consists of a host (CPU), which allows for the execution of device programs (i.e., kernels), and a device (GPU) [72]. The device (GPU) is composed of p processors, each capable of running a single thread. Processors are partitioned into groups of size b, called a *multiprocessor*, hence, there are a total of k = p/b total multiprocessors. All processors in a multiprocessor executes in lock-step.

Each multiprocessor is connected to a large and slow global memory unit, which can be accessed by every multiprocessor and the host. The global memory unit is divided into blocks of b contiguous cells. Thus, when accessing a particular global memory location, all b elements of the particular block must be transferred. Additionally, each multiprocessor has its own small and fast *shared memory* unit of size M. Shared memory is divided into b banks, where all b processors can accesses a distinct bank in a single step. If multiple processors access the same bank, then the accesses are serialized, which is analogous to bank conflicts.

For an AGPU algorithm, the time complexity is the number of instructions executed per multiprocessor and the I/O complexity is the number of global memory accesses across all multiprocessors. Let m be the amount of shared memory used by a single multiprocessor. The efficiency of multithreading, called multiplicity, is defined as  $\mathcal{M} = M/m$ .

The AGPU model assumes that the number of threads and number of processors are equal. However, the authors provide a theorem to account for v virtual processors.

Theorem 1. Let v > p.

$$\begin{split} AGPU_{I/O}(p,b,M) &= AGPU_{I/O}(v,b,M) \\ AGPU(p,b,M) &\leq \left\lceil \frac{v}{p} \right\rceil AGPU(v,b,M) \end{split}$$

where  $AGPU_{I/O}(...)$  is the I/O complexity and AGPU(...) is the time complexity.

## 1.2.5 Abstract Transferring GPU (ATGPU)

The Abstract Transferring GPU (ATGPU) model extends the AGPU model (Section 1.2.4) by considering the the cost of data transfer between the host (CPU) and device (GPU) [19]. Thus, the ATGPU model uses the same parameters as in the AGPU model in addition to G, which is the size of global memory.

An algorithm in the ATGPU model is divided into rounds. A round starts with data transferred from the host to the device, then the kernel is executed on the device, and finally the round ends with data transferred from the device to the host (and additional synchronization overhead). Let R be the total number of rounds of a particular algorithm,  $t_i$  be the maximum number of executed operations across all multiprocessors in round i,  $q_i$  be the total number of global memory accesses across all multiprocessors in round i,  $I_i$  be the number of words transferred from the host to device in round i, and  $O_i$  be the number of words transferred from the device to host in round i.

Different cost functions are defined in order to factor in the cost needed to perform various hardware instructions. Let  $\gamma$  be the cost for a multiprocessor to execute an instruction (e.g., clock rate),  $\lambda$  be the cost to access a global memory block, and  $\sigma$  be the cost to synchronize (at the end of each round). The cost function for host and device data transfer involves additional parameters. Let  $\alpha$  be the initial overhead cost of data transfer transaction and  $\beta$  be the cost of sending a single word. Let  $\hat{I}_i$  be the number of data transfer transactions from the host to device in round i and  $\hat{O}_i$  be the cost of data transfer transactions from the device to host in round i. Let  $T_I(i) = \hat{I}_i \alpha + I_i \beta$  be the cost of data transfer from host to device in round i and  $T_O(i) = \hat{O}_i \alpha + O_i \beta$  be the cost of data transfer from host to device in round i.

Therefore, the cost of the whole algorithm is defined as:

$$\sum_{i=1}^{R} T_I(i) + \frac{t_i + \lambda q_i}{\gamma} + T_O(i) + \sigma$$

Similar to the AGPU model, the ATGPU model also has a theorem to account for different number of processors.

Theorem 2. Let k' < k

$$\sum_{i=1}^{R} T_I(i) + \frac{\left\lceil \frac{k}{k'\ell} \right\rceil t_i + \lambda q_i}{\gamma} + T_O(i) + \sigma$$

where  $\ell = \min(\lfloor \frac{M}{m} \rfloor, H)$  is the maximum number of concurrent blocks on a multiprocessor (H represents the hardware imposed limit).

## 1.3 Parallel Models of Computation

In this section, we provide a review of parallel models that we propose to use for developing and analyzing GPU algorithms. The Parallel Random Access Machine (PRAM) model (Section 1.3.1) models the overall parallelism and computational efficiency; the Parallel External Memory (PEM) model (Section 1.3.2) models the number of parallel coalesced accesses to global memory; and the Distributed Memory Machine (DMM) model (Section 1.3.3) models the number of parallel accesses to shared memory.

## 1.3.1 Parallel Random Access Machine (PRAM)

The Parallel Random Access Machine (PRAM) model [62] is a parallel extension of the well-known sequential RAM model. It consists of p processors connected to a shared memory space. Each processor is viewed as a sequential RAM machine and all processors execute in a synchronous manner (i.e., an implicit global synchronization is performed after every operation). All communication between processors are performed by reading from and writing into the shared memory space.

For an input of size n, there are two performance metrics in this model: (1) work, denoted W(n), which is the total number of operations performed by all processors; and (2) depth, denoted D(n), which is the maximum number of operations performed by any single processor if the algorithm is executed using infinite processors (also known as span or  $critical\ path\ length$ ). The runtime using p processors can then be computed as  $O\left(\frac{W(n)}{p} + D(n)\right)$ , which is known as Brent's Scheduling Principle [13].

The PRAM model has 3 standard variants, based on the allowed shared memory mechanisms: EREW (Exclusive Read Exclusive Write), CREW (Concurrent Read Exclusive Write), and CRCW (Concurrent Read Concurrent Write). In the EREW PRAM, both concurrent read and write access is not allowed; in the CREW PRAM, concurrent read access is allowed and concurrent write access is not allowed; and in the CRCW PRAM, both concurrent read and write access is allowed. Additional CRCW PRAM models have been defined based on various concurrent write access mechanisms (i.e., how to resolve write conflicts). For example, in the common-CRCW PRAM, concurrent writes are only allowed if all processors are writing the same value to the same memory location; and in the arbitrary-CRCW PRAM, only a single arbitrary processor succeeds in writing its value and the remaining processors fail (i.e., do not write its value to the memory location). As concurrent writes are undefined on GPUs, we utilize the CREW PRAM model to analyze the available parallelism and computational complexity of GPU algorithms.

Historical Note: The PRAM model was formalized as early as 1978 by Fortune and Wyllie [45]. They denote the model as P-RAM and it is defined to be an unbounded set of processors connected to an unbounded shared memory space. One major difference in the models is that in the P-RAM model, processors can execute a FORK instruction, which allows the processor to start an inactive processor. A P-RAM algorithm is then defined to start initially on a single processor and parallelism is invoked via calling FORK. Therefore, in the P-RAM model, it takes  $O(\log p)$  time to initialize p processors; while in the PRAM model, all p processors are active from the start of the algorithms.

## 1.3.2 Parallel External Memory (PEM)

The Parallel External Memory (PEM) model [4] is a parallel extension of the sequential External Memory model [2]. In the EM model, a processor contains fast internal memory of size M and

data initially resides in a large and slow external memory. To perform computation on data, that data must be transferred from external memory into the processors internal memory, using contiguous blocks of B data elements. The complexity metric of the EM model, I/O complexity, is the number of such blocks transferred during the algorithm. Similarly, in the PEM model, each of the P processors contains a private memory space of size M. However, external memory is now shared among all P processors. When performing computation on data, the data is still transferred between external memory and an individual processor's internal memory in blocks of size B. The performance metric in the PEM model is the parallel I/O complexity, which is the maximum number of blocks transferred by any one of the processors throughout the algorithm.

On a GPU, w contiguous global memory locations are able to be transferred to a group of w threads, called a warp. This behavior is equivalent to a single PEM processor accessing a block of w contiguous elements in global memory. In other words, by using B = w, each thread in a warp will accesses consecutive memory locations resulting in O(1) global memory transactions. Thus, by mapping each PEM processor to a warp and setting  $B = \Theta(w)$ , we can utilize the PEM model to analyze the number of parallel coalesced global memory accesses on a GPU.

## 1.3.3 Distributed Memory Machine (DMM)

The Distributed Memory Machine (DMM) model (originally called the Module Parallel Machine model) considers data to be stored across a set of memory modules, rather than in a single shared memory space [76]. The motivation for this model was to reflect the architecture of the Ultra-computer, which featured p processors connected to p memory modules [53]; and to study the granularity of parallel memories problem. This problem studies the simulation of shared memory models on distributed models (e.g., the simulation of PRAM algorithms on the DMM).

The DMM model consists of p synchronous processors and p memory modules with a complete interconnection network between processors and memory modules. In each step of a DMM algorithm, processors are able to send a memory request to any of the p memory modules. However, each memory module is only able to respond to a single memory request at a time. Thus, multiple memory requests to a single memory module results in these memory requests being queued in an arbitrary order and processed sequentially. The cost of each step is the maximum number of requests across all memory modules.

In the DMM model, when and where each processor sends its memory request to is called the access schedule. An access schedule is called simple if it does not make "complicated" decisions and does not redistribute memory requests among the processors before sending them to memory modules. Furthermore, an access schedule is called oblivious if processors communicate independently of input keys and non-oblivious otherwise.

The DMM model has been mostly overlooked by the GPU community and has been reinvented with minor variations to model accesses in shared memory. Dotsenko *et al.* [36] visualized shared

memory as a 2-dimensional matrix; and Nakano [83] formalized this approach with the Discrete Memory Machine model (see Section 1.2.1). Afshani and Sitchinava [1] simplified the Discrete Memory Machine model by removing the latency parameter and considering a single warp. This simplification of the Discrete Memory Machine model is equivalent to the DMM model (with p being equal to the number of threads in a warp). These minor variations of the DMM have been used to analyze various algorithms such as: scanning [36], sorting [1, 67], searching [66], transposition [20], and permuting [1, 68].

Automatic Conflict Resolution: Historically, the DMM model has been used to study the granularity of parallel memories problem [26, 27, 28, 34, 63, 76, 81, 103]: given p arbitrary access to memory, the problem is to find the access schedule that results in the least amount of memory requests to any single memory module on a p processor DMM. In other words, this problem considers the simulation of an arbitrary PRAM algorithm step on the DMM. The current best solution is a non-oblivious access schedule that results in  $O(\log \log \log p \log^* p)$  cost with high probability [27]. This approach relies on redundancy of data elements and universal hashing in order to reduce the expected number of requests to any single memory module.

## 1.4 Organization

In this dissertation, we use the PRAM model (Section 1.3.1), PEM model (Section 1.3.2), and DMM model (Section 1.3.3) to analyze and develop GPU algorithms. In Chapter 2, we study the problem of searching and use the PRAM and PEM models to analyze and develop parallel in-place permutations for constructing various implicit search tree layouts, which provide improved cacheefficiency when compared to binary search. We measure experimentally the cost of performing these permutations and a batch of queries, compared to binary search on a sorted array. Next in Chapter 3, we use the PRAM and PEM models and present a parallel priority queue, denoted PARBUCKETHEAP, and use it in a parallel variant of Dijkstra's algorithm for finding single source shortest paths (SSSP). We compare the performance of our SSSP implementation against the stateof-the-art GPU implementations for SSSP. In Chapter 4, we study the problem of pairwise merge on GPUs, which is the current fastest approach for comparison-based sorting on GPUs, and use the DMM model to prove that there exists inputs that cause the asymptotic worst-case number of bank conflicts in shared memory. Moreover, we show in practice that the bank conflicts incurred from our constructed worst-case inputs results in significant slowdown. Lastly, in Chapter 5, we present a bank conflict free algorithm for loading elements from shared memory into registers for balanced two-way divide-and-conquer algorithms. We experimentally show, via pairwise mergesort, that our bank conflict free approach eliminates the slowdown due to bank conflicts in practice.

# CHAPTER 2 PARALLEL IN-PLACE CONSTRUCTION OF IMPLICIT SEARCH TREE LAYOUTS

Searching is a fundamental computational problem that arises in many applications. When many queries are expected to be performed, data is often stored in a data structure that is conducive to efficient searching. One such example are pointer-based search trees, e.g., a binary search tree (BST) is a binary tree such that for every vertex v, the key stored at v is greater than all the keys stored in the subtree rooted at v's right child. Pointer-based data structures, however, use at least a constant factor more space than the data itself, which can be prohibitive in limited-memory environments. In contrast, if the data is stored in sorted order, efficient search can be performed using binary search without using any extra space. The advantage of search trees lies in their efficient updates (insertions and deletions of elements). However, in the case of static data (i.e., data which will not change in the future), storing data in sorted order and performing binary search seems to be the preferred approach [69].

In this chapter, we study efficient *parallel* transformations of a static sorted array into various *implicit* search tree layouts (defined in Section 2.1.1) and the minimum number of queries needed to justify the extra time to perform such transformations in practice. Moreover, since binary search on already sorted data does not require any additional space, we require that these transformations be performed *in-place*.

## 2.1 Preliminaries

#### 2.1.1 Memory Layouts of Static Search Trees

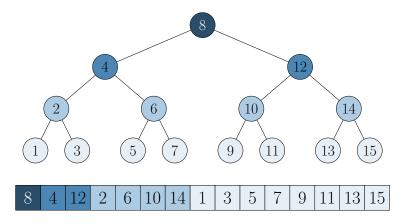

The BST layout is defined by the breadth-first left-to-right traversal of a complete binary search tree. Given the index i of a node v in the BST layout, the indices of the left and right children of v can be computed in O(1) time as 2i + 1 and 2i + 2 (using 0-indexing), respectively. Figure 2.1 depicts an example 15-node BST layout.

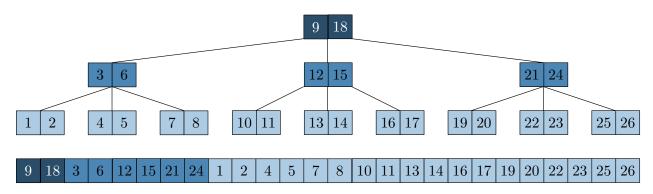

A complete B-tree [8] is a complete multi-way search tree, where each node (except possibly the last leaf node) contains exactly B elements and every internal node (except possibly the last one) has exactly B+1 children. The Level-order B-tree layout is defined by the breadth-first left-to-right traversal of a complete B-tree. Figure 2.2 depicts the B-tree layout for N=26 and B=2.

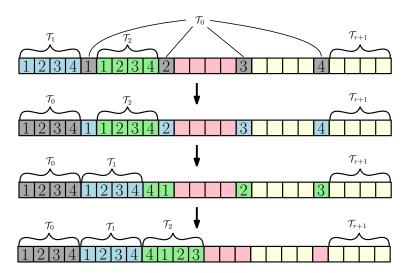

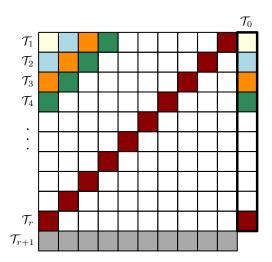

The van Emde Boas (vEB) layout [92] is defined recursively as follows. The vEB layout of a tree with a single vertex is the vertex itself. Given a complete binary search tree  $\mathcal{T}$  with N vertices and height  $h = \lfloor \log N \rfloor > 0$ , consider the top subtree  $\mathcal{T}_0$  of height  $\lfloor (h-1)/2 \rfloor$  containing  $r = 2^{\lfloor (h-1)/2 \rfloor} - 1$  vertices, and r+1 bottom subtrees  $\mathcal{T}_1, \mathcal{T}_2, \ldots, \mathcal{T}_{r+1}$ , each of height  $\lceil (h-1)/2 \rceil$  and

Figure 2.1: BST layout for N = 15.

Figure 2.2: Level-order B-tree layout for N=26 and B=2.

each rooted at the children of the (r+1)/2 leaves of  $\mathcal{T}_0$ . The vEB layout of  $\mathcal{T}$  is defined recursively as the vEB layout of  $\mathcal{T}_0$ , followed by the vEB layouts of each  $\mathcal{T}_1, \mathcal{T}_2, \ldots, \mathcal{T}_{r+1}$ . Figure 2.3 depicts an example vEB layout with 15 nodes.

The above definition of the vEB layout for  $N \neq 2^{h+1}-1$  complicates the permutation algorithms described in Sections 2.3.3 and 2.4.1 because the number of vertices in each bottom subtree may be different. Instead, in this work, we modify the definition of the vEB layout for  $N \neq 2^{h+1}-1$  as follows. Let  $r = 2^{\lfloor (h-1)/2 \rfloor} - 1$  and  $l = 2^{\lceil (h-1)/2 \rceil} - 1$ . The top subtree  $\mathcal{T}_0$  of the vEB layout will always contain r vertices and the remaining N-r elements will form  $x = \lceil (N-r)/l \rceil$  bottom subtrees,  $\mathcal{T}_1, \mathcal{T}_2, \ldots, \mathcal{T}_x$ . Each of the first  $y = \lfloor (N-r)/l \rfloor$  bottom subtrees,  $\mathcal{T}_1, \mathcal{T}_2, \ldots, \mathcal{T}_y$ , will consist of exactly l vertices. If N-r is not a multiple of l, i.e., x = y + 1, then the last bottom subtree,  $\mathcal{T}_x$ , will contain  $1 \leq l' < l$  vertices. As in the standard definition, the vEB layout consists of  $\mathcal{T}_0$ , immediately followed by  $\mathcal{T}_1, \mathcal{T}_2, \ldots, \mathcal{T}_x$ , with each subtree laid out recursively  $(\mathcal{T}_0, \mathcal{T}_1, \ldots, \mathcal{T}_y)$  uses the standard vEB layout and if x = y + 1, then  $\mathcal{T}_x$  uses this modified approach).

In our definition of the vEB layout, at each recursive level, there is at most one bottom subtree that contains a different number of vertices than all other bottom subtrees and if it exists, is always located at the end of the layout. This observation allows us to easily adapt the permutation algorithms described in Sections 2.3.3 and 2.4.1 and query optimizations described in Section 2.7.1 to work with arrays of sizes  $N \neq 2^{h+1} - 1$ , without affecting the asymptotic analysis.

Figure 2.3: van Emde Boas (vEB) layout for N = 15.

The I/O complexity of performing a search query on an array of size N in the BST layout is  $O(\log(N/B))$ , and  $\Theta(\log_B N)$  in the B-tree and vEB layouts [14, 92]. In theory, because the definition of the vEB layout does not make use of the parameter B, i.e., it is *cache-oblivious* [49], querying the vEB layout on architectures with multiple levels of cache will result in the asymptotically optimal number of accesses at every level of the memory hierarchy [92].

#### 2.1.2 Previous Work on Permutations

The transformation from sorted order to an implicit search tree layout is a special case of permuting an array of N elements. Let  $\pi:[N] \to [N]$  be an arbitrary permutation. For the purpose of this paper, we assume that  $\pi$  is given as a function that can be described concisely in O(1) space (e.g., not as a table that explicitly gives  $\pi(i)$  for each i). Let  $\tau_{\pi}$  be the time it takes to evaluate  $\pi(i)$ . For example, while  $\tau_{\pi} = O(1)$  for the BST and B-tree layouts, it is not obvious how to compute  $\pi(i)$  faster than  $O(\log \log N)$  time for the vEB layout.

Note that for the problem of permuting N elements using P processors,  $\Omega((N/P) \cdot \tau_{\pi})$  is the trivial lower bound in the PRAM model. If there is no in-place requirement, any permutation  $\pi$  can be implemented in  $O(\lceil N/P \rceil \cdot \tau_{\pi})$  time in parallel: each entry A[i] can be copied to  $B[\pi(i)]$  independently of each other. Thus, the BST and B-tree layouts can be constructed from sorted data in  $O(\lceil N/P \rceil)$  time and the vEB layout can be constructed in  $O(\lceil N/P \rceil \log \log N)$  time.

It is well known that every permutation can be decomposed into disjoint cycles. A cyclic permutation can be implemented sequentially in-place trivially by starting at a single vertex and following the cycle. However, for a general permutation this approach still needs additional space to mark the elements that have already been permuted, unless it can identify all disjoint cycles up

front.

When it comes to *in-place* permutations, Fich *et al.* [43] showed that every permutation  $\pi$  can be implemented sequentially in-place in  $O((N \log N) \cdot \tau_{\pi})$  time. For a special case when the data is permuted from a sorted order, they observed that they can check if an element has already been moved by computing the inverse permutation  $\pi^{-1}$  to determine if the element is not in its original sorted order. Thus, for this special case, the time can be reduced to  $O(N \cdot (\tau_{\pi} + \tau_{\pi^{-1}}))$ . However, it is not obvious how to parallelize their algorithm, nor is it trivial to compute  $\pi^{-1}$  for the vEB layout.

Yang et al. [111] observed that every permutation is the product of two involutions. A permutation  $\pi$  is an *involution* if it is its own inverse, i.e.,  $\pi(\pi(i)) = i$  for all i. Moreover, every involution is composed of disjoint cycles of length at most 2, i.e., can be implemented in parallel and in-place by swapping pairs of elements. Thus, if the two involutions of a permutation are known, this permutation can be implemented in parallel and in-place. This result is non-constructive, i.e., given an arbitrary permutation  $\pi$  it is not clear how to determine the two involutions that define  $\pi$ ; however, the authors show how to determine the involutions of a cyclic permutation.

One permutation of particular interest for this work is the perfect shuffle [33]: a permutation in which two lists of equal length are interleaved perfectly. A generalization is the k-way perfect shuffle, where k equal-length lists are interleaved perfectly [93]. These permutations have many applications (e.g., parallel processing [99], Fast Fourier Transforms (FFT) [30, 99], Kronecker products [30, 32], encryption [101], sorting [99], and merging [29, 41, 42]). Ellis et al. [39, 40] use a number-theoretic approach to compute representative elements of the disjoint cycles of the perfect shuffle and the k-way perfect shuffle, thus making a sequential in-place approach possible. Jain [61] relies on the fact that 2 is primitive root of  $3^k$  for any  $k \ge 1$ , which makes it possible to compute the representative elements of the disjoint cycles recursively for any N. Finally, Yang et al. [111] use the product of involutions approach and describe the involutions for the k-way perfect shuffle for two cases: (i)  $N = k^d$  and (ii) N = kd for some integer d > 1. For (i), the involutions involve reversing the base-k representation of element indices. For (ii), the involutions involve computing modular inverses of element indices and finding greatest common divisors. We use these results of Yang et al. [111] for designing our involution-based permutation algorithms.

## 2.1.3 Parallel In-place Computations

There is a bit of ambiguity in the literature when it comes to the definition of *in-place* algorithms. Strictly speaking, a (sequential) algorithm is said to be *in-place* if it uses at most  $\Theta(1)$  additional space (a processor needs at least one register to perform any useful work) [42]. However, for a recursive algorithm, at least  $\Omega(\log N)$  additional space is needed to implement the recursion stack of a balanced recursion. Therefore, it is reasonable for an in-place algorithm to use up to  $O(\log N)$  additional space, although often such algorithms are called *in-situ* [41, 71]. When it comes to

parallel algorithms, there is an additional complication. Each of the P processors needs to have  $\Omega(1)$  space to perform any meaningful work. Moreover, for asynchronous recursion,  $\Omega(\log N)$  space is needed per processor, i.e., a total of  $\Omega(P\log N)$  additional space. Therefore, if  $P = \frac{N}{\log N}$ , the total additional space becomes  $\Omega(N)$  and trivially non-in-place algorithms could be viewed as being in-place. To avoid this situation, we define *in-place parallel* computation as follows:

**Definition 3.** A parallel algorithm running on P processors each having an internal memory of size M is called in-place if it uses at most  $O(P(M + \log N))$  additional space and works correctly for any  $P \ge 1$  processors.

In the PRAM model, M = O(1) is the number of registers per processor so it reduces to  $O(P \log N)$ ; while in the PEM model, M is the size of each processor's internal memory. Note that the requirement for an algorithm to work correctly for any  $P \ge 1$  precludes the view of trivially non-in-place algorithms designed for large P as being in-place.

## 2.2 Contributions

We present parallel algorithms for the in-place permutation of a sorted array into the BST, B-tree, and vEB layouts, and analyze their time and I/O complexities. We propose two types of algorithms:

- 1. Building on the work of Yang et al. [111] and Fich et al. [43], we determine the pairs of involutions required to permute a sorted array into the BST layout. We also determine the  $\log_{B+1} N$  pairs of involutions required to permute a sorted array into the B-tree layout. The B-tree involutions can be used in order to permute a sorted array into the vEB layout.

- 2. Using a cycle-leader approach, we develop an efficient parallel in-place algorithm to permute a sorted array into the vEB layout. By recursively applying this approach, we are able to design algorithms for permuting a sorted array into the B-tree layout. The B-tree layout algorithm can be used to obtain the BST layout by setting B = 1.

The involution-based approach entails reversing a subset of the digits of numbers represented in an arbitrary base-k (for BST k=2, for B-tree k=B+1). If implemented in software, the worst-case complexity of this operation is linear with the number of digits in the base-k representation of the integer N being reversed, i.e.,  $O(\log_k N)$ . Some architectures provide it as a built-in hardware primitive (i.e., it takes O(1) time), in particular, NVIDIA GPUs implement this operation in hardware for k=2. We parameterize the time of this operation as  $T_{REV_k}(N)$ .

To the best of our knowledge, our algorithms are the first parallel in-place algorithms for permuting a sorted array into the considered search tree layouts. The time and I/O complexities of our algorithms are summarized in Table 2.1. Our cycle-leader algorithms exhibit better I/O complexity, while our involution-based algorithms are much simpler and trivial to parallelize. We

Table 2.1: Asymptotic time and I/O complexity bounds of each of our algorithms. N is the input size, P is the number of processors, M and B are the sizes of the internal memory and the transfer block, respectively, in the PEM model.  $K = \min(\frac{N}{P}, M)$  and  $T_{REV_k}(N)$  is the time complexity of reversing the digits of number N in the base-k representation.

| Algorithm           | Time complexity                                                      | I/O complexity                                                                            |

|---------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Involution BST      | $O\left(\frac{N}{P} \cdot T_{REV_2}(N)\right)$                       | $O\left(\frac{N}{P}\right)$                                                               |

| Involution B-tree   | $O\left(\left(\frac{N}{P} + \log_{B+1} N\right) \log N\right)$       | $O\left(\frac{N}{P} + B \log_{B+1} \frac{N}{K}\right)$                                    |

| Involution vEB      | $O\left(\frac{N}{P}\log N\right)$                                    | $O\left(\frac{N}{P}\log\log_K N\right)$                                                   |

| Cycle-leader BST    | $O\left(\left(\frac{N}{P} + \log N\right) \log N\right)$             | $O\left(\left(\frac{N}{PB} + \log \frac{N}{K}\right) \log \frac{N}{K}\right)$             |

| Cycle-leader B-tree | $O\left(\left(\frac{N}{P} + \log_{B+1} N\right) \log_{B+1} N\right)$ | $O\left(\left(\frac{N}{PB} + \log_{B+1} \frac{N}{K}\right) \log_{B+1} \frac{N}{K}\right)$ |

| Cycle-leader vEB    | $O\left(\frac{N}{P}\log\log N\right)$                                | $O\left(\frac{N}{PB}\log\log_K N\right)$                                                  |

evaluate these algorithms experimentally and find that, compared to a binary search on non-permuted input, the permutation overhead of our permutation algorithms is offset by the query time for as few as 0.013N on a NVIDIA GPU.

The remainder of this chapter is organized as follows. Section 2.3 presents our involution-based algorithms and Section 2.4 presents our cycle-leader algorithms, each section analyzing the time complexity of these algorithms. For ease of exposition, in Sections 2.3 and 2.4 we consider only *perfect* trees, i.e., complete trees in which every level is full. Section 2.5 analyzes the I/O complexity of our algorithms. Section 2.6 discusses extensions of our algorithms to non-perfect trees. Section 2.7 goes over experimental optimizations and Section 2.8 presents experimental results. Finally, Section 2.9 concludes with a summary.

## 2.3 Involution Approach

## 2.3.1 BST Layout

A perfect BST contains  $N = 2^d - 1$  vertices. Fich *et al.* [43] propose a sequential in-place algorithm to permute a sorted array into the BST layout. They note that the permutation satisfies the property that for a given index  $i = (x10^j)_2$  in binary representation, the index of that element in the BST layout is  $\pi(i) = (0^j 1x)_2$ . Let  $\text{REV}_k(b, i)$  be the operation that reverses the *b* least significant digits of the base-*k* representation of the integer *i*. The previously mentioned permutation can be computed as  $\pi(i) = \text{REV}_2(d - (j+1), (\text{REV}_2(d,i)))$ . Since  $\text{REV}_2$  is an involution [43], we can perform the permutation  $\pi$  in parallel in just two rounds of O(N) independent swaps.

The time to compute  $\pi(i)$  depends on the time to perform the REV<sub>2</sub> operation. Thus, this algorithm has depth  $D(N) = O(T_{\text{REV}_2}(N))$  and work  $W(N) = O(N \cdot T_{\text{REV}_2}(N))$ .

## 2.3.2 B-tree Layout

The B-tree layout algorithm relies on the k-way perfect shuffle involution approach developed by Yang et al. [111]. Let us first review their results.

Let  $J_r(i) = g \cdot (r \cdot (\frac{i}{g})^{-1} \pmod{\frac{N-1}{g}})$  where g is the greatest common divisor of i and N-1. Yang et al. [111] show that for  $N = k^d$  and N = kd the k-way perfect shuffle can be implemented as  $\Xi_1(i) = \text{REV}_k(d, \text{REV}_k(d-1, i))$  and  $\Xi_2(i) = J_k(J_1(i))$ , respectively, for any integer d > 1. We note that the k-way "un-shuffle", which we use, can be performed by simply reversing the order in which the involutions are performed.

A perfect B-tree has  $N = (B+1)^d - 1$  elements, for some d > 1. Since each leaf node contains B contiguous elements from the sorted array, every (B+1)-th element is stored in a non-leaf (i.e., internal) node. Let  $S_i$ , for  $i \in \{0, 1, 2, ..., B\}$ , denote the list of elements at locations i + j(B+1), for  $j \in \{0, 1, ..., \left\lfloor \frac{N}{(B+1)} \right\rfloor\}$ . In other words, each  $S_i$  is comprised of the elements starting at i, strided by B+1. By this definition,  $S_B$  contains all internal elements and  $S_l$ , for  $0 \le l \le B-1$ , contains the l-th element of each leaf node. We first perform the (B+1)-way perfect un-shuffle (via  $\Xi_1$  while using or simulating 1-indexing), which will gather each  $S_i$  into contiguous space and lay them out in sequence. We then apply the B-way perfect shuffle (via  $\Xi_2$  while using or simulating 0-indexing) on all  $S_l$  lists to interleave the leaf elements back into their corresponding leaf nodes, i.e., into their correct positions. All leaf elements are thus correctly permuted and we recurse on  $S_B$ .

Recall that  $REV_k$  can take up to  $O(\log_k N)$  time. Finding the modular inverse, however, requires using the extended Euclidean algorithm [111], which takes  $O(\log N)$  time. The latter dominates the running time, resulting in  $O(\log N)$  time for both operations. The work and depth complexities of our B-tree permutation algorithm are given in Proposition 4 and 5, respectively.

## Proposition 4.

$$W(N) = W\left(\frac{N}{B+1}\right) + O(N\log N)$$

$$= O(N\log N).$$

*Proof.* Guess:  $W(N) = c\left(\frac{B+1}{B}\right) N \log N - c\left(\frac{B+1}{B^2}\right) N \log (B+1)$ .

$$W\left(\frac{N}{B+1}\right) = c\left(\frac{B+1}{B}\right) \left(\frac{N}{B+1}\right) \log \frac{N}{B+1} - c\left(\frac{B+1}{B^2}\right) \left(\frac{N}{B+1}\right) \log (B+1)$$

$$= c\left(\frac{1}{B}\right) N \log N - c\left(\frac{1}{B}\right) N \log (B+1) - c\left(\frac{1}{B^2}\right) N \log (B+1)$$

$$= c\left(\frac{1}{B}\right) N \log N - c\left(\frac{1}{B} + \frac{1}{B^2}\right) N \log (B+1)$$

$$= c\left(\frac{1}{B}\right) N \log N - c\left(\frac{B}{B^2} + \frac{1}{B^2}\right) N \log (B+1)$$

$$\begin{split} &=c\left(\frac{1}{B}\right)N\log N-c\left(\frac{B+1}{B^2}\right)N\log \left(B+1\right)\,,\\ &W(N)=W\left(\frac{N}{B+1}\right)+cN\log N\\ &=c\left(\frac{1}{B}\right)N\log N-c\left(\frac{B+1}{B^2}\right)N\log \left(B+1\right)+cN\log N\\ &=c\left(\frac{1}{B}+1\right)N\log N-c\left(\frac{B+1}{B^2}\right)N\log \left(B+1\right)\\ &=c\left(\frac{1}{B}+\frac{B}{B}\right)N\log N-c\left(\frac{B+1}{B^2}\right)N\log \left(B+1\right)\\ &=c\left(\frac{B+1}{B}\right)N\log N-c\left(\frac{B+1}{B^2}\right)N\log \left(B+1\right)\,. \end{split}$$

Therefore,  $W(N) = O(N \log N)$ .

## Proposition 5.

$$D(N) = D\left(\frac{N}{B+1}\right) + O(\log N)$$

$$= O(\log_{B+1} N \cdot \log N).$$

*Proof.* Let  $h = \log_{B+1} N$ .

Guess:  $D(N) = c(h+1)\log N - \frac{c}{2}h^2\log(B+1) - \frac{c}{2}h\log(B+1)$ .

$$\begin{split} D(N) &= D\left(\frac{N}{B+1}\right) + c\log N \\ &= ch(\log N - \log{(B+1)}) - \frac{c}{2}(h-1)^2\log{(B+1)} - \frac{c}{2}(h-1)\log{(B+1)} + c\log N \\ &= c(h+1)\log N - ch\log{(B+1)} - \frac{c}{2}(h^2 - 2h + 1)\log{(B+1)} - \frac{c}{2}h\log{(B+1)} + \frac{c}{2}\log{(B+1)} \\ &= c(h+1)\log N - \frac{c}{2}h^2\log{(B+1)} - \frac{c}{2}h\log{(B+1)} \ . \end{split}$$

Therefore,  $D(N) = O(\log_{R+1} N \log N)$ .

## 2.3.3 van Emde Boas Layout

We are able to apply the B-tree layout algorithm for the vEB layout of height h, by using  $B = 2^{\lceil (h-1)/2 \rceil} - 1$  and recursing on each subtree of the vEB layout. The resulting work and depth complexities are:

## Proposition 6.

$$W(N) = \sqrt{N} \cdot W\left(\sqrt{N}\right) + O(N \log N)$$

$$= O(N \log N)$$

.

*Proof.* Guess:  $W(N) = 2cN \log N$

$$W(N) = \sqrt{N}(2c\sqrt{N}\log\sqrt{N}) + cN\log N$$

$$= cN\log N + cN\log N$$

$$= 2cN\log N.$$

Therefore,  $W(N) = O(N \log N)$ .

## Proposition 7.

$$D(N) = D\left(\sqrt{N}\right) + O(\log N)$$

$$= O(\log N).$$

*Proof.* Guess:  $D(N) = 2c \log N$

$$D(N) = 2c \log \sqrt{N} + c \log N$$

$$= c \log N + c \log N$$

$$= 2c \log N.$$

Therefore,  $D(N) = O(\log N)$ .

## 2.4 Cycle-leader Approach

## 2.4.1 van Emde Boas Layout

Recall from Section 2.1.1 that we define  $\mathcal{T}_i$  as the *i*-th subtree of size  $O(\sqrt{N})$ :  $\mathcal{T}_0$  is the "root" subtree consisting of  $r = 2^{\lfloor (h-1)/2 \rfloor} - 1$  vertices of the upper  $\lfloor \frac{h-1}{2} \rfloor$  levels, where  $h = \lfloor \log N \rfloor$ , while  $\mathcal{T}_1, \ldots, \mathcal{T}_{r+1}$  are "leaf" subtrees consisting of  $l = 2^{\lceil (h-1)/2 \rceil} - 1$  vertices each. Let  $A[a_i : b_i]$  be the interval within the input array where the elements of  $\mathcal{T}_i$  should be moved to. In particular,  $a_0 = 1$ ,  $b_0 = r$  and for all  $1 \leq j \leq r+1$ ,  $a_j = r+(j-1)l+1$  and  $b_j = r+jl$ . Our algorithm first moves each  $\mathcal{T}_i$  into  $A[a_i : b_i]$ , which we call the *equidistant gather* operation, then recursively permutes each  $A[a_i : b_i]$  into the vEB layout. (Our equidistant gather operation is general enough to work for any  $r \leq l$ .)

We use  $\mathcal{T}_i[a:b]$  to denote the subset of nodes of  $\mathcal{T}_i$  from the a-th smallest to the b-th smallest in the sorted order. E.g.,  $\mathcal{T}_i[1:k]$  represents the first k smallest elements of  $\mathcal{T}_i$ .

The following proposition bounds the range in the input array, where the elements of the leaf subtrees  $\mathcal{T}_j$ , for  $j \geq 1$ , are initially located:

**Proposition 8.** For all i = r - j + 2,  $1 \le j \le r + 1$ ,  $\mathcal{T}_j[i:l]$  are already in their destination interval  $A[a_j:b_j]$ . If i > l, then no elements of  $\mathcal{T}_j$  are in their destination interval.

*Proof.* Since the input is in sorted order, for all  $1 \leq i, j \leq l$ ,  $\mathcal{T}_j[i]$  is initially located at index  $i_{orig} = (j-1)(l+1) + i$ . Hence, we check if  $i_{orig} \geq a_j = r + (j-1)l + 1$ . Solving for i results in  $i \geq r - j + 2$ .

From the above proposition, we know that  $\mathcal{T}_1[r+1:l], \mathcal{T}_2[r:l], ..., \mathcal{T}_{r+1}[1:l]$  are already in their destination intervals and only  $\mathcal{T}_1[1:r], ..., \mathcal{T}_r[1]$  need to be moved.

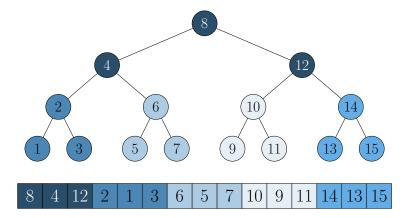

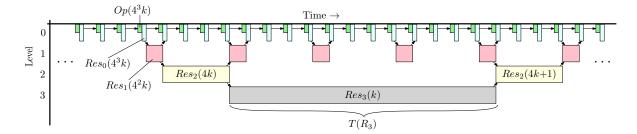

Figure 2.4: Illustration of the series of swaps needed to sequentially perform the equidistant gather operation for r = l.

We first consider a sequential strategy to perform the equidistant gather in-place: we perform r rounds of swapping, where after round i, all elements in the subtree  $\mathcal{T}_i$  are in  $A[a_i:b_i]$ . Figure 2.4 illustrates the first few rounds of swapping for r=l. We see that, initially, all elements of  $\mathcal{T}_0$  are distributed throughout the array. After the first round,  $\mathcal{T}_0$  is in  $A[a_0:b_0]$  and  $\mathcal{T}_1$  becomes distributed throughout the array. After repeating this process r times, each  $\mathcal{T}_i$  is in  $A[a_i:b_i]$ , however, the elements in each  $\mathcal{T}_i$  may not be in sorted order. Specifically, we need to perform a circular shift to the right by r+1-i places (or equivalently l-(r+1-i) to the left) on each  $\mathcal{T}_i$ .

We can parallelize this algorithm by unrolling the r sequential swap rounds and identifying the resulting disjoint cycles. We identify r disjoint cycles of the following form:

$$\mathcal{T}_0[1] \mapsto \mathcal{T}_1[1] ,$$