Six years ago the heavy ion group of INFN Florence 35 started the design of a four-channel digitizing board prototype to study the application of digital sampling 37 techniques to energy and time measurement and to particle identification [1–6]. The prototype allowed acquisition and 39 storing of signals, without on-board analysis capability: signal treatment was performed off-line on a dedicated 41 CPU, although the analysis algorithms were studied for an easy on-line implementation. In the following few years we 43 have studied in detail the application of digital sampling techniques to nuclear detector signals. We have found that 45 in several applications the same or better performance can be obtained from digital sampling as from standard analog 47 methods (e.g. in energy and time measurement or in particle identification [1-3,5]). Moreover, using sampling, 49 one can exploit the more detailed information achieved by recording complete signals and implement analysis meth-51

53

55

ods with no analog counterpart (e.g. fast Fourier trans-59 forms, curve fitting, comparison with tabulated data, etc.).

Along with these studies and developments, in the 61 framework of the NUCL-EX collaboration, we started a project for a fast digitizer with on-board processing 63 capabilities. The project has now reached the production stage. The new digitizers are modular in structure, each 65 channel being housed on a separate daughter-board plugged on a main mother-board. Up to eight sampling 67 channels can be plugged on a single mother-board. Each channel is equipped with a 12-bit, 125 MSamples/s ADC 69 and with a Digital Signal Processor (DSP) for on-board signal analysis. The DSP extracts the physically relevant 71 informations from the signal before transferring data to the acquisition system for storage, thus relaxing its bandwidth 73 and mass storage requirements. In fact, transferring complete signals to external (i.e. not on-board) CPUs or 75 to a mass storage device can be cumbersome for the acquisition system, especially when an apparatus with 77 many channels is involved. In our design, we maintained the possibility of transferring the full digitized sequence to 79 the acquisition system in each event (typically we choose to

83

Please cite this article as: G. Pasquali, et al., A DSP equipped digitizer for online analysis of nuclear detector signals, Nuclear Instruments and Methods in Physics Research A (2006), doi:10.1016/j.nima.2006.10.008

<sup>\*</sup>Corresponding author. Tel.: + 39 55 4572253; fax: + 39 55 4572676. E-mail address: pasquali@fi.infn.it (G. Pasquali).

<sup>0168-9002/\$ -</sup> see front matter © 2006 Elsevier B.V. All rights reserved. 57 doi:10.1016/j.nima.2006.10.008

<sup>81</sup>

**ARTICLE IN PRESS**

- 1 transfer a complete signal only every 256 events to monitor system performance).

- 3 We favoured a DSP-based design, with respect to a FPGA-based one like those proposed in Refs. [7,8], since

- 5 we were not interested in very high counting rates and we aimed at flexibility and short software developing times.

- 7 We also intended to develop a system as general-purpose as possible because of its expected application to various

- 9 detectors. The boards described in this paper are currently employed at the GARFIELD [9] apparatus at Laboratori

- 11 Nazionali di Legnaro (LNL) to treat about 200 CsI(Tl) scintillators and in the next future about 200 channels will

- 13 be added to treat Si detector and gas detector signals.

In Section 2 we briefly present the system in general. In

15 Section 3 a first version of a digitizing channel is described;

- Section 4 presents the 6U VME mother-board which can

- 17 host up to eight digitizing channels and can be read out either via VME or FAIR [10] bus; the general structure of a

- 19 DSP algorithm is illustrated in Section 5, while Section 6 presents, as a study case, results obtained from an online

- 21 analysis algorithm reproducing the behaviour of a standard semi-Gaussian shaper; an application to digital pulse shape

- 23 discrimination of light charged particles in CsI(Tl) scintillation detectors is the subject of Section 7.

- 25

## <sup>27</sup> 2. General description of the system

- <sup>29</sup> The system was designed to be easily re-configured and upgraded. We favoured a modular design in which each <sup>31</sup> channel is housed on a small  $(140 \times 25 \text{ mm}^2)$  piggy back

- board, plugged on a main "mother" board (cf. Section 4). <sup>33</sup> The mother-board acts as an interface between the

- channels local bus, whose signals are for the greatest part <sup>35</sup> those of the DSP direct memory access interface (IDMA)

- [11], and the acquisition readout bus, which in the presentboards can be either VME or FAIR bus. The biggest advantages of such a structure are:

- 39

- Channels with different specifications (e.g. input stage characteristics, sampling rate) can be plugged on the very same mother-board provided they adhere to the local bus specifications, making their upgrading an easy task.

- Adding support for new readout buses (e.g. PCI [12])

would imply re-designing (in part) the mother-board but not the channel daughter-board.

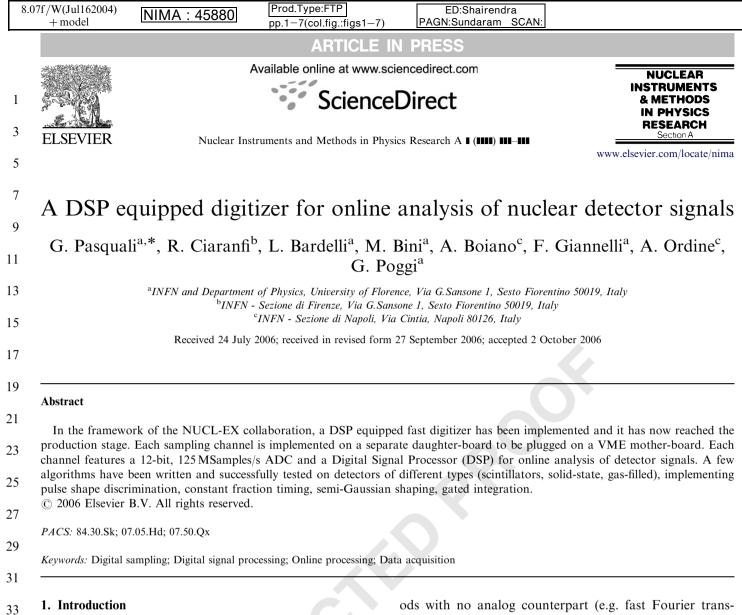

### 3. The digitizer channel

The present version of the digitizing channel is shown in Fig. 1. Each channel features an input LEMO connector for detector signals and an 8 pin connector for the input of trigger signals (cf. 3.3) and the output of logic signals generated by the DSP and by the on-board comparators.

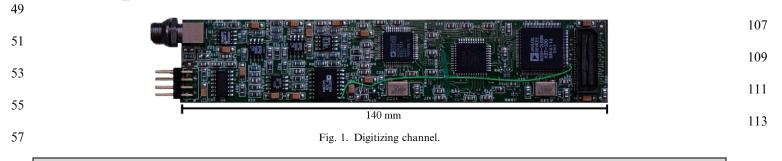

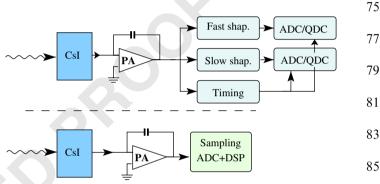

Fig. 2 shows a block diagram of a digitizing channel. Five sections can be identified: the analog input stage (programmable-gain amplifier and anti-aliasing filter), the digitizing section (ADC), the temporary storage section (FIFO memory), the processing section (DSP), the trigger section (programmable comparators and trigger logic).

### 3.1. Analog input stage and AD conversion

The analog input stage polarity (positive or negative) can be selected via a dedicated jumper on the channel board. 75 The ADC has a fixed input range of 2 V: the full range at channel input is, therefore, determined by the analog input gain. The input gain can be set by the on-board DSP to one out of 255 different values, corresponding to a full range going from 130 mV (maximum gain value) to 8 V (minimum gain value), allowing the system to adapt to various detector/preamplifier configurations with no circuit changes. 83

The input anti-aliasing filter is a 3-pole active low-pass filter, whose configuration and behaviour have already been discussed elsewhere (see Figs. 4 and 5 in Ref. [1]). In the present design filter attenuation at 62.5 MHz, i.e. the Nyquist frequency of the digitizer, is  $\approx 30$  dB.

The on-board DSP also controls an electronic switch (see Fig. 2) which selects one of two possible ADC input sources, the detector signal and the time reference (TR) signal common to all channels (see Section 4). The TR is provided for timing coincidence and time of flight measurements (see Refs. [2,6]).

The digitizing section exploits a 12-bit ADC operating at 95 125 MSamples/s and having an effective number of bits (ENOB) of about 10.7 [13]. In experimental tests 97 performed with the prototype described in Ref. [1] (a 12bit, 10.8 ENOB, 100 MSamples/s digitizer) we achieved 99 satisfactory resolutions both in timing measurements (100 ps FWHM with a Si detector [2]) and energy 101 measurements over a wide dynamic range (about 15 PSENOB [5,14]). The prototype digitizer also featured 103 good particle identification capabilities over a wide dynamic range (see Refs. [3,14]). Therefore, the presently 105

Please cite this article as: G. Pasquali, et al., A DSP equipped digitizer for online analysis of nuclear detector signals, Nuclear Instruments and Methods in Physics Research A (2006), doi:10.1016/j.nima.2006.10.008

2

59

61

63

65

67

69

71

73

85

# **ARTICLE IN PRESS**

G. Pasquali et al. / Nuclear Instruments and Methods in Physics Research A I (IIII) III-III

- 23 employed ADC is an effective choice for a general purpose system.

- 25 Typical characteristics of the digitizing channels, in this first version, are:

- 27

- 12-bit sampling at 125 MSamples/s.

- For low noise demanding applications, like those involving germanium detectors, 10.5 ENOB are obtained using a fixed-gain input stage. For channels with programmable input gain (like those employed at CADEVELED DETENDED)

- GARFIELD) 9.7 ENOB are typical.

- 0.25 LSB differential nonlinearity.

- 0.8 LSB integral nonlinearity.

- 37

33

- 39 3.2. Storing and processing

- 41 The ADC output values are continuously written to a First-In-First-Out (FIFO) memory which stores up to 8192

43 samples (≈ 64 us at 125 MSamples/s).

- In many applications (e.g. for amplitude measurements) a good estimate of the signal baseline is mandatory [14–16].

- In order to get this information, a suitable portion of the

baseline preceding the particle signal must be sampled and

collected. In our design, the first FIFO locations act as a

- 49 circular buffer. They are continuously re-written while the channel is waiting for a trigger (see Section 3.3). The length

- of the circular buffer can be changed by programming the on-board programmable logic device (PLD) which is used

mainly for channel's glue logic.

- When a trigger signal is received, the trigger logic (see 55 Fig. 2) enables the FIFO memory to be filled up so that the first samples of the stored signal will always correspond to

- 57 a time interval preceding the trigger (e.g.  $\approx 4\,\mu s$  for a 512

samples circular buffer) and can be used to calculate the current signal baseline. In Ref. [14] it has been shown that a baseline of a few  $\mu$ s length is usually adequate to spectroscopy-grade energy measurements.

The DSP can execute up to 80 million multiply-andaccumulate operations per second [11]. Its on-board RAM 85 memory is large enough (192kB) for signal storing and elaboration, thus no external memory chip is required. The 87 DSP reads sampled data from its I/O port, connected to the FIFO, and stores them in its internal data memory. The 89 acquisition system loads the DSP program in DSP internal memory and starts the program execution through the DSP 91 IDMA interface. The DSP controls the channel hardware (the DACs used for gain and threshold settings, etc.), 93 handles the validation logic of the event, performs signal analysis and prepares readout data in its internal memory. 95 The acquisition system can read/write data from/to the DSP internal memory asynchronously through the DSP 97 IDMA interface during program execution, for instance to read event data or to instruct the DSP to change gain, 99 thresholds. etc.

The acquisition system can check the status of the digitizing channel (idle, analyzing, waiting for readout) by accessing the mother-board local bus and polling a few logic signals controlled by the DSP.

### 3.3. Trigger

107

105

3

Signal storing in the FIFO and signal processing by the DSP are started by a trigger signal coming either from an 109 external device or from one of the two on-board comparators. There are two external trigger inputs, one 111 located on the 8 pin front connector and one located on the mother-board connector, the latter coming from the ECL 113 input of the mother-board. The comparators thresholds are

## ARTICLE IN PRESS

G. Pasquali et al. / Nuclear Instruments and Methods in Physics Research A I (IIII) III-III

- 1 controlled by the DSP by means of a dedicated programmable digital-to-analog converter. The analog input signal

- 3 is shaped by a CR-RC filter ( $\tau \approx 200 \, \text{ns}$ ) before being sent to the comparators, as shown in Fig. 2. Two comparator

- 5 ranges are available, both divided into 255 steps: one comparator can go up to the ADC full range ("high

- 7 threshold" in Fig. 2), the other can be adjusted between zero and 10% of the ADC full range ("low threshold").

- 9 This allows a fine tuning of the channel threshold in order to better treat low-amplitude signals. Comparators outputs

- 11 can also be picked out from the 8 pin front connector (for instance to build a second level trigger for the experiment) 13 as shown in Fig. 2.

- Another logic signal, common to all channels and 15 connected to all the DSPs, is fed to the mother-board via

- one of the user-defined pins on the VME P2 connector and 17 it is typically employed to validate the digitized events. The

- DSP program can test the level of this signal at any time 19 using a dedicated instruction (see Section 5).

#### 21 4. The main board

23 A 6U VME board (shown in Fig. 3) was the simplest choice as a first implementation of the mother-board, 25 though other readout buses (e.g. PCI) can be implemented without redesigning the digitizing channels, thanks to the 27 modular design of the system.

Actually, an alternative readout bus has already been 29 implemented on the same VME mother-board, the FAIR bus developed by LASS laboratory of INFN-Sezione di 31

Napoli [10]. The FAIR bus exploits the user-defined part of

the VME P2 connector. It can reach a bandwidth of 180 MB/s in optimal conditions. As usual with FAIR 59 modules, the mother-board features a 32-bit multi-event FIFO which is written with DSP data and buffers data for 61 read-out and event building [10]. The FAIR bus is currently employed in a few experimental apparatuses 63 (e.g. the GARFIELD [9] apparatus). The mother-board can be switched from VME to FAIR mode via a jumper 65 placed on the front panel (see Fig. 3).

The mother-board houses the interface from the readout 67 bus (VME or FAIR) to the "local" bus of the digitizing channels. It also features an 8 input ECL connector for the 69 trigger signals of the eight sampling channels (see Section 3.3). A common TR signal can be connected to a LEMO 71 input connector on the mother-board (see Fig. 3) and distributed to all the sampling channels as discussed in 73 Section 3.1. When the relevant part of the input signal has been sampled, the DSP can start sampling the TR by 75 controlling the electronic switch shown in Fig. 2. The sampled signal thus contains both the detector signal and 77 the TR signal. A numerical algorithm extracts the time difference between the two, with a sub-nanosecond 79 accuracy. Since the same TR signal is distributed to all the sampling channels, it is possible to perform timing 81 coincidences and time-of-flight measurements (the latter may require the TR signal to have a definite relationship to 83 the nuclear collision like, e.g. the RF signal of a pulsed beam). The basic idea of this method can be found in Ref. 85 [2], Section 5, while a more detailed discussion will be presented in Ref. [6]. 87

89

33 M ( 01 1202 3 N B W 1262 2 91 35 93 37 95 CHANNEL CONNECTORS 39 97 eterreterre inferierte anarterte 41 99 43 mentitite 101 45 103 47 105 minim 49 107 51 109 53 200 111 55 TR INPUT ECL Trig. INPUTS VME/FAIR SELECT. 113 Fig. 3. A 6U VME mother-board.

57

Please cite this article as: G. Pasquali, et al., A DSP equipped digitizer for online analysis of nuclear detector signals, Nuclear Instruments and Methods in Physics Research A (2006), doi:10.1016/j.nima.2006.10.008

# **ARTICLE IN PRESS**

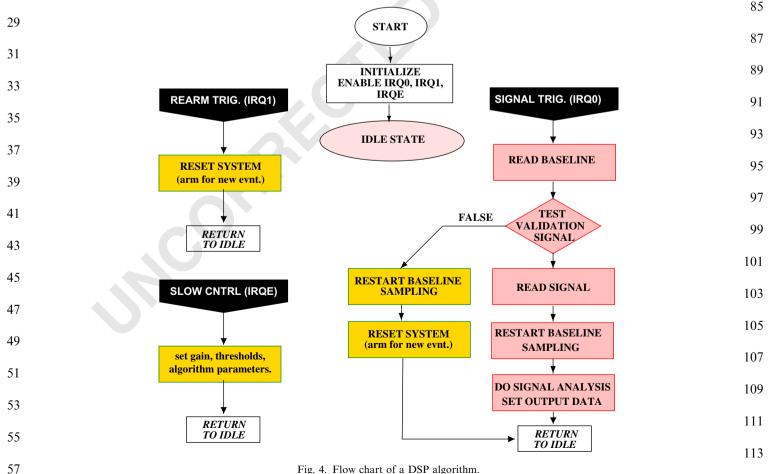

#### 1 5. Algorithm structure

3 The on-board DSP is used both to control the channel hardware and to perform signal analysis. The general structure of a DSP algorithm is shown in Fig. 4. The DSP 5 switches to an idle state after an initialization phase, 7 performed once and for all at bootstrap time, where the DSP sets up its internal registers, channel gain and 9 comparator thresholds, etc. Upon receiving a signal trigger (connected to the interrupt request signal IRO0) the DSP 11 jumps to an interrupt service routine which spends a few microseconds reading samples from the FIFO (usually 13 corresponding to the baseline), then checks a validation signal (e.g. the general trigger of the experiment). In case of 15 no validation, the DSP rearms the channel for a new trigger and returns to its idle state, otherwise it reads the 17 remaining samples from the FIFO and restarts the circular buffer. The signal analysis phase follows. Since signal 19 analysis lasts much longer than the buffer length expressed in us, the buffer has been filled completely before a new

21 trigger can be accepted. After the analysis step, the DSP prepares the output data in its internal memory for readout 23 and returns to its idle state. Readout takes place through the IDMA interface with no DSP intervention. After all 25 relevant data have been read, the acquisition system drives

the DSP IRQ1 interrupt signal (one of the local bus signals 27

on the mother-board) thus instructing the DSP to rearm the channel for a new trigger, as shown on the left side of 59 Fig. 4.

Hardware settings and algorithm parameters can be 61 accessed using a dedicated "slow control" interrupt routine associated to the IRQE interrupt signal (see Fig. 4). 63

### 6. Semi-Gaussian shaping: a study case

67 A few analysis routines have been written for the DSP, in ADSP21xx assembler language. At first, work has been 69 done to implement on DSP the calculations previously performed off-line including constant fraction timing 71 (either using linear or cubic interpolation), gated integration, amplitude estimation [1-4].

73 One peculiar task is to reproduce the behaviour of the standard analog semi-Gaussian shaper employed since a 75 few years at the GARFIELD apparatus for CsI(Tl) signals. The DSP algorithm had to closely reproduce the analog 77 shaper set to the shaping constant and pole zero values employed during measurements. This requirement was 79 called for in order to simplify and speed up the calibration of the data collected with digitizing electronics, expected to 81 substitute the analog shapers.

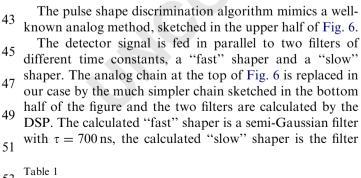

An Infinite Impulse Response (IIR) filter algorithm [17] 83 has thus been written and tested. A custom fit procedure

Fig. 4. Flow chart of a DSP algorithm.

Please cite this article as: G. Pasquali, et al., A DSP equipped digitizer for online analysis of nuclear detector signals, Nuclear Instruments and Methods in Physics Research A (2006), doi:10.1016/j.nima.2006.10.008

## ARTICLE IN PRESS

- 1 based on DE ("Differential Evolution": a populationbased, stochastic function minimizer [18]) has been used to

- 3 model filter response on that of GARFIELD analog shapers while keeping the calculation time as small as

- 5 possible by reducing the number of poles and zeros in filter's system function. The filter is implemented as a 7 constant-coefficients difference equation [17], whose coef-

- ficients are determined by the fit. The fit also takes into account the finite (16-bit) precision of filter coefficient

- representation in DSP memory. The calculation is carried 11 out using 32 bits words (the DSP ALU works on 16-bit

- operands) in order to get the desired filter stability and 13 precision. A satisfactory filter calculation time of about 50 us was obtained by performing a moving average on the

- 15 signal followed by a decimation by 16 before filtering. Averaging and decimation do not sensibly worsen the final

- resolution. The *2*-transform of the adopted filter has the 17 form

- 19

$$\mathscr{Z}(z) = \frac{b_0 + b_1 z^{-1}}{1 - a_1 z^{-1} - a_2 z^{-2} - a_3 z^{-3}}.$$

(1)

- To take decimation into account, coefficients had to be 23 calculated for a 128 ns sampling period. Their values are shown in Table 1.

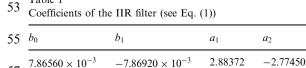

- 25 In order to compare the two filters (analog and digital IIR), the same "detector-like" pulser signal (a step with

- 27 variable rise-time followed by an exponential decay, as those produced by typical charge sensitive preamplifiers)

- 29 was fed to both the analog shaper and the digitizer. The output of the analog shaper was also sampled and stored.

- 31 In Fig. 5 we show the output of the analog shaper (sampled at 8 ns period and appearing as a continuous line in the

- 33 figure) and the output of the IIR filter (appearing as a stepped line, due to the decimation operated by the DSP,

- 35 effectively increasing the sampling period to 128 ns) for a few values of the input signal's rise time (ranging from

- 37 50 ns to 5  $\mu$ s). The IIR filter closely follows the analog one, also for different rise times of the input signal.

- 39

57

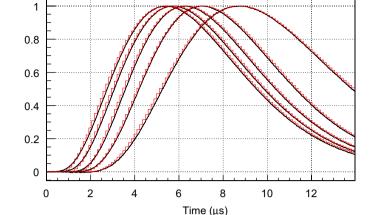

#### 7. Pulse shape discrimination in CsI(Tl) 41

Fig. 5. DSP and analog shaper outputs for different input signal rise times; each signal pair is normalized to unit maximum amplitude.

Fig. 6. A typical analog chain for pulse shape discrimination (top) compared to the set-up described in this paper (bottom).

described in Section 6, having a peaking time of about 6 µs. The amplitudes of the filtered signals  $(A_f \text{ and } A_s)$  are stored for the off-line analysis.

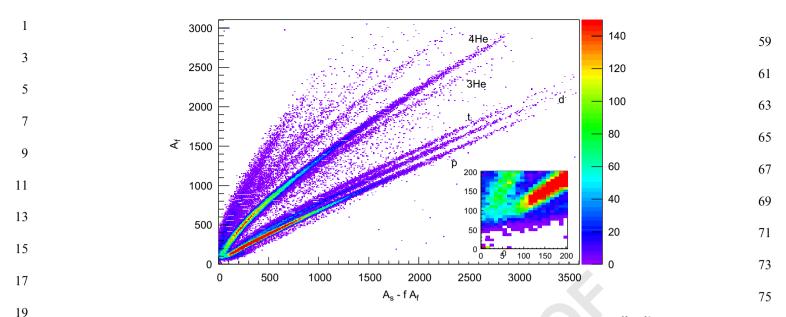

A "fast-slow" correlation—actually  $A_f$  vs.  $(A_s - f \cdot A_f)$ 93 where  $f \approx 4$ —is shown in Fig. 7. Hydrogen and helium isotopes are clearly resolved. The data were obtained from 95 one of GARFIELD's CsI(Tl) detectors in a physics run recently performed at LNL, exploiting the reaction 97 <sup>32</sup>S+<sup>56</sup>Fe at 16.5 AMeV (ALPI accelerator). About 200 digitizing channels have been used in the experiment and a 99 PSA quality similar to that of Fig. 5 is obtained for all the CsI(Tl) scintillators of GARFIELD. In Fig. 7, the curves 101 associated with different light particle isotopes can be followed down to the point where they merge (correspond-103 ing, e.g. to  $A_f \approx 200$  for hydrogen isotopes). The trigger threshold of the digitizer (see Section 3.3) sets a lower limit 105 on  $A_f$  values at  $A_f \approx 80$ , as evidenced in the inset. Therefore, for GARFIELD's CsI(Tl) detectors, the region 107 where light particle isotopes can be identified is not limited by the digitizer threshold. 109

## 8. Conclusions and future developments

A VME system aimed at digitizing and processing 113 detector signals has been designed and implemented. The

Please cite this article as: G. Pasquali, et al., A DSP equipped digitizer for online analysis of nuclear detector signals, Nuclear Instruments and Methods in Physics Research A (2006), doi:10.1016/j.nima.2006.10.008

$a_3$

0.890655

6

79

59

61

63

65

67

69

71

73

81

87

89

91

## **ARTICLE IN PRESS**

G. Pasquali et al. / Nuclear Instruments and Methods in Physics Research A I (IIII) III-III

Fig. 7. Pulse shape discrimination of light charged particles in CsI(Tl) performed by the on-board DSP; the reaction was  ${}^{32}S+{}^{56}Fe$  at 16.5 AMeV.

design is modular, consisting in a multi-channel motherboard on which up to eight digitizing daughter-boards can

be plugged. Data readout can be performed either via

VME bus or via the faster FAIR bus. Each daughter-board

is equipped with a 12-bit, 125 MSamples/s ADC and a DSP

for on-line processing of detector signals. About 200

channels and 30 mother-boards have already been built

and installed and they are presently in use at the

GARFIELD apparatus in LNL-Legnaro.

31 Work is currently under way to implement a new type of daughter-board where a FPGA will be used to implement

the on-board trigger, instead of the two comparators presently used. The FPGA will continuously receive the samples produced by the ADC, performing filtering and trigger logic on the digitized signal.

A prototype digitizing channel compatible with our mother-boards and including a much faster digitizer based on an analog pipeline [19] is also being developed in collaboration with IN2P3 in the framework of FAZIA [20],

41 a project for R&D of a next generation apparatus for nuclear physics experiments.

# 43 **References**

45 [1] L. Bardelli, et al., Nucl. Instr. and Meth. A 491 (2002) 244.

- [2] L. Bardelli, et al., Nucl. Instr. and Meth. A 521 (2004) 480.

- [2] L. Bardelli, et al., Nucl. Instr. and Meth. A 521 (2004) 480.

[3] L. Bardelli, et al., Proceedings of RNB6 conference 2003, Nucl. Phys. A 746 (2004) 272.

- [4] L. Bardelli, Ph.D. Thesis, University of Florence, 2005.

- [5] L. Bardelli, G. Poggi, Nucl. Instr. and Meth. A 560 (2006) 517.

- [6] L. Bardelli, et al., Nucl. Instr. and Meth. A, submitted for 83 publication.

- [7] Technical proposal for the "Advanced GAmma Tracking Array" (AGATA) project, available on (http://agata.pd.infn.it/). 85

- [8] M.A. Deleplanque, et al., Nucl. Instr. and Meth. A 430 (1999) 292.

- [9] F. Gramegna, et al., Nucl. Instr. and Meth. A 389 (1997) 474.

- [10] A. Ordine, et al., IEEE Trans. Nucl. Sci. NS-45 (3) (1998) 873.

- [11] Analog Devices, WEB site (www.analog.com), ADSP-218xN Series 89 datasheet.

- [12] F.A.Danevich, private communication.

- [13] Analog Devices, WEB site (www.analog.com), AD9433 Datasheet. 91

- [14] L. Bardelli, G. Poggi, Nucl. Instr. and Meth. A 560 (2006) 524.

- [15] V. Radeka, Rev. Sci. Instr. 38 (1967) 1397.

- [16] A. Pullia, G. Ripamonti, Nucl. Instr. and Meth. A 376 (1996) 82.

- [17] A.V. Oppenheim, R.W. Shafer, Digital Signal Processing, Prentice-Hall, Englewood Cliffs, NJ, 1975 ISBN 0-13-214107-8 01.

- [18] R. Storn, et al., Differential Evolution Algorithm, WEB page: (http:// www.icsi.berkeley.edu/~storn/code.html).

97

- [19] S. Drouet, J.C. Cuzon, P. Edelbruck, E. Wanlin, submitted for publication.

- [20]  $\langle http://fazia.in2p3.fr/\rangle$ .

- 101

77

81

87

93

- 103

- 105

- 107

- 109

- 111

113

55 57

47

49

51