**Universidade do Minho** Escola de Engenharia

Pedro Paulo Fontes Delgado

eal-Tim

an FPGA

Real-Time Implementation of 3D LiDAR Point Cloud Semantic Segmentation in an FPGA Pedro Paulo Fontes Delgado

×

Uminho | 2022

# **Real-Time Implementation of 3D LiDAR**

# **Point Cloud Semantic Segmentation in**

**Universidade do Minho** Escola de Engenharia

Pedro Paulo Fontes Delgado

Real-Time Implementation of 3D LiDAR Point Cloud Semantic Segmentation in an FPGA

Master Dissertation Master in Informatics Engineering

Dissertation supervised by Sanaz Asgarifar Victor Alves

October 2022

## DECLARATION

Name: Pedro Paulo Fontes Delgado

Dissertation Title: Real-Time Implementation of 3D LiDAR Point Cloud Semantic Segmentation in an FPGA

Supervisors: Sanaz Asgarifar, Victor Alves

Conclusion Year: 2022

Master Designation: Master in Informatics Engineering

Master Branch: Machine Learning and Data Science

I declare that I grant to the University of Minho and its agents a non-exclusive license to file and make available through its repository, in the conditions indicated below, my dissertation, as a whole or partially, in digital support.

I declare that I authorize the University of Minho to file more than one copy of the dissertation and, without altering its contents, to convert the dissertation to any format or support, for the purpose of preservation and access.

Furthermore, I retain all copyrights related to the dissertation and the right to use it in future works.

I authorize the partial reproduction of this dissertation for the purpose of investigation by means of a written declaration of the interested person or entity.

This is an academic work that can be used by third parties if internationally accepted rules and good practice with regard to copyright and related rights are respected.

Thus, the present work can be used under the terms of the license indicated below.

In case the user needs permission to be able to make use of the work in conditions not foreseen in the indicated licensing, he should contact the author through the RepositóriUM of the University of Minho.

**@ 0 8** E

## Atribuição-NãoComercial-SemDerivações CC BY-NC-ND

https://creativecommons.org/licenses/by-nc-nd/4.0/

University of Minho, \_\_\_\_/\_\_\_/

Signature: \_\_\_\_\_

This work is supported by European Structural and Investment Funds in the FEDER component, through the Operational Competitiveness and Internationalization Programme (COMPETE 2020) [Project n° 047264; Funding Reference: POCI-01-0247-FEDER-047264].

# List of publications

Delgado, P., Asgarifar, S., Alves, V. Real-Time Implementation of Squeezeseg-V3 Semantic Segmentation Using Vck190 FPGA Board. Submitted to WorldCist'23 - 11st World Conference on Information Systems and Technologies

## Acknowledgements

A lot of people have contributed to the successful writing of this thesis. To all of you, I am truly grateful to have shared this journey. Without you, this would have not been possible.

I would like to start by thanking both my supervisors, Sanaz Asgarifar and professor Victor Alves for giving me the freedom to take this exploratory work where I wanted it to go.

I give out all my appreciation to Alexandre Correia for encouraging me to explore a whole new area of study. I truly believe it had a tremendously positive impact on my development professionally and more importantly, personally.

To the FPGA team at Bosch, who received me with open arms and created the best working environment, thank you. Without your amazing knowledge, this work would simply have not been possible.

To my friends, who have supported me and allowed me to escape the loneliest and most stressful hours. Thank you for all the game nights, outings, and the most foolish debates.

To my parents who I profoundly admire and whom I see as amazing role models. Thank you for your open-minded education and amazing childhood. Without you, I would not be who I am.

To Mariana, my sister, and Artur, my nephew, with whom I can always count on for an amazingly good time. Thank you.

To João, my brother, who I also admire greatly. You inspire me to be my best self so you can hopefully have an additional role model.

To my dear partner, Sofia, for being there for me from the beginning of this journey, in the good and the hardest times. Thank you for the endless ideas, and meaningful debates and for always allowing me to trust myself. Your dedication and resilience inspire me. Your happiness drives me.

Pedro Delgado

## STATEMENT OF INTEGRITY

I hereby declare having conducted this academic work with integrity. I confirm that I have not used plagiarism or any form of undue use of information or falsification of results along the process leading to its elaboration.

I further declare that I have fully acknowledged the Code of Ethical Conduct of the University of Minho.

University of Minho, \_\_\_\_/\_\_\_/

| Signature: | <br> |

|------------|------|

|            |      |

## ABSTRACT

In the last few years, the automotive industry has relied heavily on deep learning applications for perception solutions. With data-heavy sensors, such as LiDAR, becoming a standard, the task of developing low-power and real-time applications has become increasingly more challenging. To obtain the maximum computational efficiency, no longer can one focus solely on the software aspect of such applications, while disregarding the underlying hardware.

In this thesis, a hardware-software co-design approach is used to implement an inference application leveraging the *SqueezeSegV3*, a LiDAR-based convolutional neural network, on the *Versal ACAP VCK190* FPGA. Automotive requirements carefully drive the development of the proposed solution, with real-time performance and low power consumption being the target metrics.

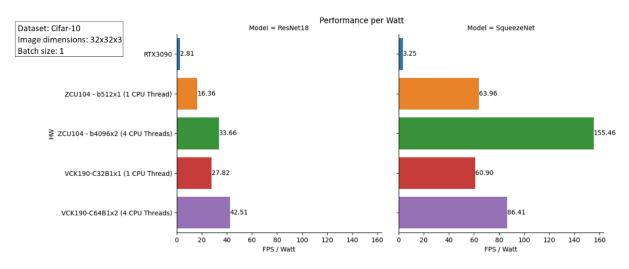

A first experiment validates the suitability of *Xilinx's Vitis-AI* tool for the deployment of deep convolutional neural networks on FPGAs. Both the *ResNet-18* and *SqueezeNet* neural networks are deployed to the *Zynq UltraScale+ MPSoC ZCU104* and *Versal ACAP VCK190* FPGAs. The results show that both networks achieve far more than the real-time requirements while consuming low power. Compared to an *NVIDIA RTX 3090 GPU*, the performance per watt during both network's inference is 12x and 47.8x higher and 15.1x and 26.6x higher respectively for the *Zynq UltraScale+ MPSoC ZCU104* and the *Versal ACAP VCK190* FPGA. These results are obtained with no drop in accuracy in the quantization step.

A second experiment builds upon the results of the first by deploying a real-time application containing the *SqueezeSegV3* model using the *Semantic-KITTI* dataset. A framerate of 11 Hz is achieved with a peak power consumption of 78 Watts. The quantization step results in a minimal accuracy and IoU degradation of 0.7 and 1.5 points respectively. A smaller version of the same model is also deployed achieving a framerate of 19 Hz and a peak power consumption of 76 Watts. The application performs semantic segmentation over all the point cloud with a field of view of 360°.

Keywords: LiDAR, Deep Learning, FPGA

### Resumo

Nos últimos anos a indústria automóvel tem cada vez mais aplicado deep learning para solucionar problemas de perceção. Dado que os sensores que produzem grandes quantidades de dados, como o LiDAR, se têm tornado standard, a tarefa de desenvolver aplicações de baixo consumo energético e com capacidades de reagir em tempo real tem-se tornado cada vez mais desafiante. Para obter a máxima eficiência computacional, deixou de ser possível focar-se apenas no software aquando do desenvolvimento de uma aplicação deixando de lado o hardware subjacente.

Nesta tese, uma abordagem de desenvolvimento simultâneo de hardware e software é usada para implementar uma aplicação de inferência usando o SqueezeSegV3, uma rede neuronal convolucional profunda, na FPGA *Versal ACAP VCK190*. São os requisitos *automotive* que guiam o desenvolvimento da solução proposta, sendo a performance em tempo real e o baixo consumo energético, as métricas alvo principais.

Uma primeira experiência valida a aptidão da ferramenta *Vitis-AI* para a implantação de redes neuronais convolucionais profundas em FPGAs. As redes *ResNet-18* e *SqueezeNet* são ambas implantadas nas FPGAs *Zynq UltraScale+ MPSoC ZCU104* e *Versal ACAP VCK190*. Os resultados mostram que ambas as redes ultrapassam os requisitos de tempo real consumindo pouca energia. Comparado com a *GPU NVIDIA RTX 3090*, a performance por Watt durante a inferência de ambas as redes é superior em 12x e 47.8x e 15.1x e 26.6x respetivamente na *Zynq UltraScale+ MPSoC ZCU104* e na *Versal ACAP VCK190*. Estes resultados foram obtidos sem qualquer perda de *accuracy* na etapa de quantização.

Uma segunda experiência é feita no seguimento dos resultados da primeira, implantando uma aplicação de inferência em tempo real contendo o modelo SqueezeSegV3 e usando o conjunto de dados *Semantic-KITTI*. Um *framerate* de 11 Hz é atingido com um pico de consumo energético de 78 Watts. O processo de quantização resulta numa perda mínima de *accuracy* e IoU com valores de 0.7 e 1.5 pontos respetivamente. Uma versão mais pequena do mesmo modelo é também implantada, atingindo uma *framerate* de 19 Hz e um pico de consumo energético de 76 Watts. A aplicação desenvolvida executa segmentação semântica sobre a totalidade das nuvens de pontos LiDAR, com um campo de visão de 360°.

Palavras-chave: LiDAR, Deep Learning, FPGA

# Table of Contents

| 1 | Intro | oduction1                                    |

|---|-------|----------------------------------------------|

|   | 1.1   | Context 2                                    |

|   | 1.2   | Motivation 3                                 |

|   | 1.3   | Objectives                                   |

|   | 1.4   | Structure of Dissertation                    |

| 2 | Tech  | nologies And Concepts5                       |

|   | 2.1   | Perception in Autonomous Driving             |

|   | 2.1.1 | Advanced Driver-Assistance Systems           |

|   | 2.1.2 | ADAS Perception Requirements and Metrics7    |

|   | 2.2   | LiDAR Sensor                                 |

|   | 2.2.1 | Working Principle                            |

|   | 2.2.2 | Point Clouds                                 |

|   | 2.3   | Deep Learning in Point Clouds                |

|   | 2.3.1 | The Deep Learning approach                   |

|   | 2.3.2 | Point Cloud Perception Tasks10               |

|   | 2.3.3 | Point Cloud Representation                   |

|   | 2.4   | Deep Neural Network Compression 15           |

|   | 2.4.1 | Quantization                                 |

|   | 2.4.2 | Other techniques                             |

| 3 | Liter | rature Review                                |

|   | 3.1   | Automotive LiDAR Refresh Rate 20             |

|   | 3.2   | Deep Learning Hardware 21                    |

|   | 3.2.1 | Central Processing Units                     |

|   | 3.2.2 | Graphical Processing Units                   |

|   | 3.2.3 | Application-Specific Integrated Circuits     |

|   | 3.2.4 | Field Programmable Gate Arrays               |

|   | 3.3   | Deep Neural Network Quantization             |

|   | 3.3.1 | Quantization Methods                         |

|   | 3.3.2 | Benefits of Quantization                     |

|   | 3.4   | Deep Learning on FPGAs 28                    |

|   | 3.4.1 | Deep Neural Network Implementations on FPGAs |

|   | 3.4.2   | High-Level Tools for Deep Neural Network Deployment on FPGAs | 30 |

|---|---------|--------------------------------------------------------------|----|

| 4 | Vitis-A | N Framework Exploration                                      |    |

|   | 4.1 E   | xperiment Description                                        | 37 |

|   | 4.1.1   | Objectives                                                   | 37 |

|   | 4.1.2   | Dataset                                                      | 37 |

|   | 4.1.3   | Deep Learning Framework                                      | 38 |

|   | 4.1.4   | Targeted Deep Neural Networks                                | 40 |

|   | 4.1.5   | Targeted Hardware                                            | 42 |

|   | 4.2 lı  | mplementation                                                | 46 |

|   | 4.2.1   | Float Model Training                                         | 48 |

|   | 4.2.2   | Model Quantization                                           | 49 |

|   | 4.2.3   | Deployment on Target Hardware                                | 50 |

|   | 4.3 R   | lesults and Analysis                                         | 53 |

|   | 4.3.1   | Quantization                                                 | 53 |

|   | 4.3.2   | Performance and Efficiency                                   | 54 |

|   | 4.4 D   | Discussion                                                   | 64 |

|   | 4.4.1   | Quantization                                                 | 64 |

|   | 4.4.2   | Performance and Efficiency                                   | 65 |

| 5 | Squee   | ezeSegV3 Deployment on an FPGA                               | 67 |

|   | 5.1 E   | xperiment Description                                        | 68 |

|   | 5.1.1   | Objectives                                                   | 68 |

|   | 5.1.2   | Dataset                                                      | 68 |

|   | 5.1.3   | Evaluation Metrics                                           | 70 |

|   | 5.1.4   | Deep Learning Framework                                      | 71 |

|   | 5.1.5   | Targeted Deep Neural Network                                 | 71 |

|   | 5.1.6   | Targeted Hardware                                            | 75 |

|   | 5.2 lı  | mplementation                                                | 75 |

|   | 5.2.1   | Architectural Changes                                        | 76 |

|   | 5.2.2   | Float Model Training                                         | 80 |

|   | 5.2.3   | Model Quantization                                           | 84 |

|   | 5.2.4   | Deployment on Target Hardware                                | 84 |

|   | 5.3 R   | Results and Analysis                                         | 85 |

|                                   | 5.3.1                                          | Quantization                                                                                                                            | 85                              |

|-----------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|                                   | 5.3.2                                          | Performance and Efficiency                                                                                                              | 86                              |

|                                   | 5.3.3                                          | Qualitative                                                                                                                             | 91                              |

| ļ                                 | 5.4                                            | Discussion                                                                                                                              | 93                              |

|                                   | 5.4.1                                          | Quantization                                                                                                                            |                                 |

|                                   | 5.4.2                                          | Performance and Efficiency                                                                                                              | 94                              |

|                                   | 5.4.3                                          | Qualitative                                                                                                                             | 95                              |

| 6                                 | Cone                                           | clusions                                                                                                                                | 97                              |

| (                                 | 6.1                                            | Synopsys                                                                                                                                | 98                              |

| 6.2 Main Contributions            |                                                | 98                                                                                                                                      |                                 |

|                                   |                                                |                                                                                                                                         |                                 |

|                                   | 6.3                                            | Research Opportunities                                                                                                                  | 99                              |

|                                   |                                                | Research Opportunities                                                                                                                  |                                 |

| Re                                | ferenc                                         |                                                                                                                                         | 101                             |

| Re <sup>†</sup>                   | ferenc<br>pendix                               | es                                                                                                                                      | 101                             |

| Re <sup>t</sup><br>Ap             | ferenc<br>pendix<br>pendix                     | es<br>I – Scale and Zero-Point Derivation                                                                                               | 101<br>115<br>116               |

| Re <sup>r</sup><br>Ap<br>Ap       | ferenc<br>pendix<br>pendix<br>pendix           | es<br>a I – Scale and Zero-Point Derivation<br>a II – Vitis-Al QAT Requirements                                                         | 101<br>115<br>116<br>119        |

| Re <sup>†</sup><br>Ap<br>Ap<br>Ap | ferenc<br>pendix<br>pendix<br>pendix<br>pendix | ses<br>x I – Scale and Zero-Point Derivation<br>x II – Vitis-AI QAT Requirements<br>x III – DPUCZDX8G and DPUCVDX8G Supported Operators | 101<br>115<br>116<br>119<br>124 |

# LIST OF FIGURES

| Figure 1. Forecast of the worldwide autonomous vehicles sales from 2019 to 2030. Retrieved from       | [10]. |

|-------------------------------------------------------------------------------------------------------|-------|

|                                                                                                       | 2     |

| Figure 2. Block diagram of an ADAS                                                                    | 6     |

| Figure 3. The effective range of Outer's OS1 LiDAR. Adapted from [25].                                | 9     |

| Figure 4. Comparison between a traditional and DL computer vision pipeline. Retrieved from [26].      | 10    |

| Figure 5. 3D object detection in a LiDAR frame.                                                       | 11    |

| Figure 6. 3D semantic segmentation of a LiDAR point cloud.                                            | 12    |

| Figure 7. Illustration of spherical, cylindrical, and bird's eye view projections of point clouds. Ad | apted |

| from [37]                                                                                             | 13    |

| Figure 8. Voxelization of a point cloud using 303 voxels. Retrieved from [40]                         | 14    |

| Figure 9. Illustration of a graph representation of a point cloud. Adapted from [48]                  | 15    |

| Figure 10. Affine quantization using signed 8-bit integers. Retrieved from [53].                      | 17    |

| Figure 11. Scale quantization using unsigned 8-bit integers. Retrieved from [53]                      | 17    |

| Figure 12. Deep learning chip revenue. Retrieved from [71].                                           | 21    |

| Figure 13. Quantization-aware training with a straight-through estimator. Retrieved from [110]        | 27    |

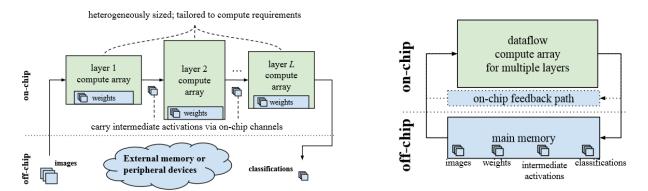

| Figure 14. Accelerator architectures: Dataflow Architecture (Left) and Multilayer Offload Archite     | cture |

| (Right). Retrieved from [23]                                                                          | 31    |

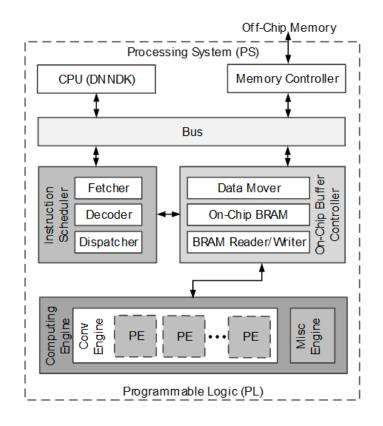

| Figure 15. DPUCZDX8G Hardware Architecture. Retrieved from [138].                                     | 34    |

| Figure 16. Example of CIFAR-10 images.                                                                | 38    |

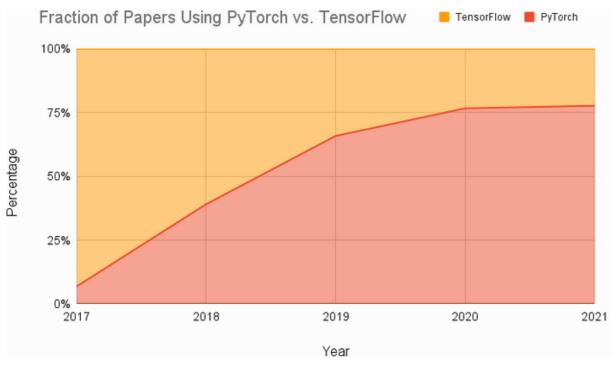

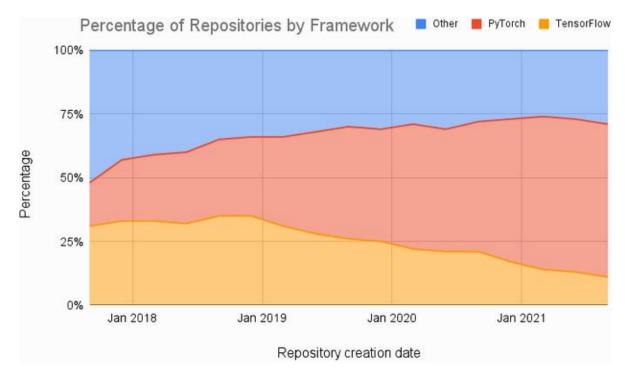

| Figure 17. Pytorch and Tensorflow usage in publications. Retrieved from [142].                        | 39    |

| Figure 18. Pytorch and Tensorflow github repository share. Retrieved from [142]                       | 39    |

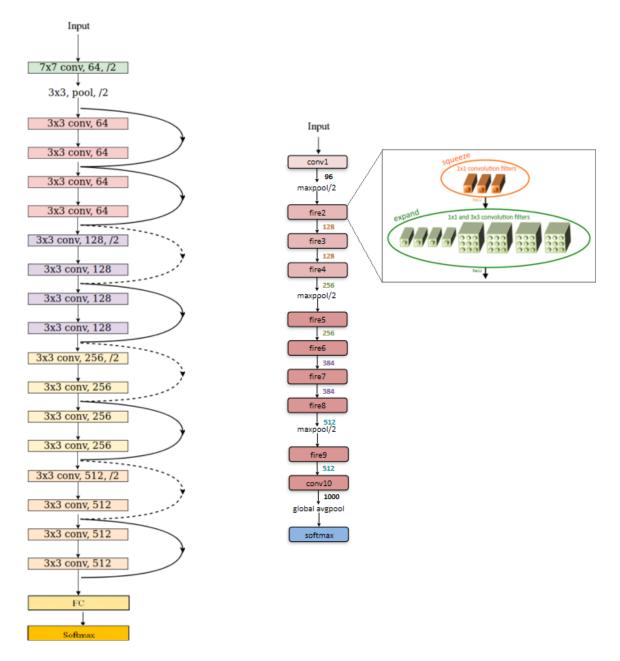

| Figure 19. ResNet-18 (Left) and SqueezeNet (Right) architectures. Retrieved from [144] and [85]       | 41    |

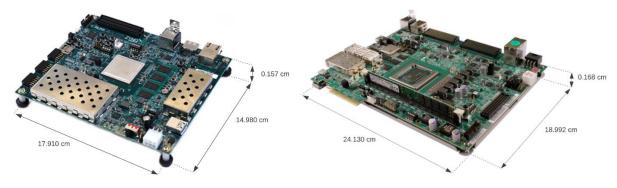

| Figure 20. Zynq UltraScale+ MPSoC ZCU104                                                              | 42    |

| Figure 21. Versal ACAP VCK190.                                                                        | 42    |

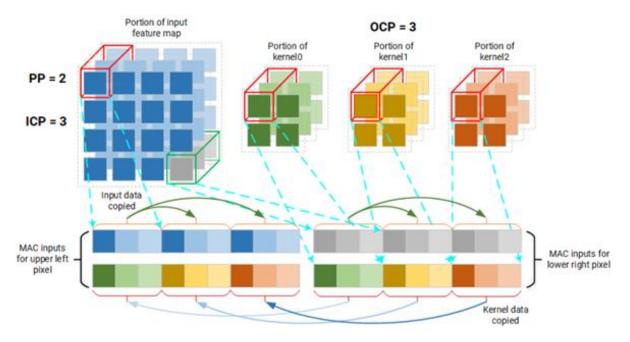

| Figure 22. Three parallelism dimensions in convolution operation. Retrieved from [138].               | 44    |

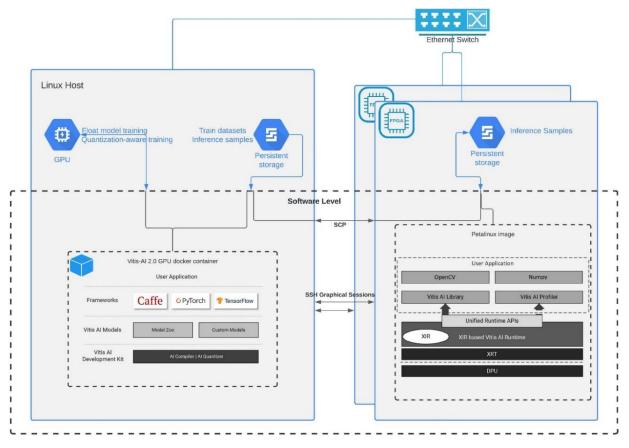

| Figure 23. Experiment setup                                                                           | 48    |

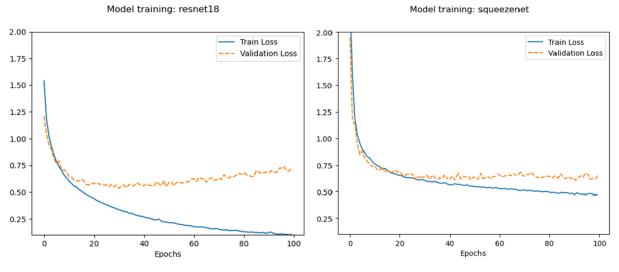

| Figure 24. ResNet-18 and SqueezeNet train plots                                                       | 49    |

| Figure 25. Visualization of ResNet-18 activation map shapes.                                          | 49    |

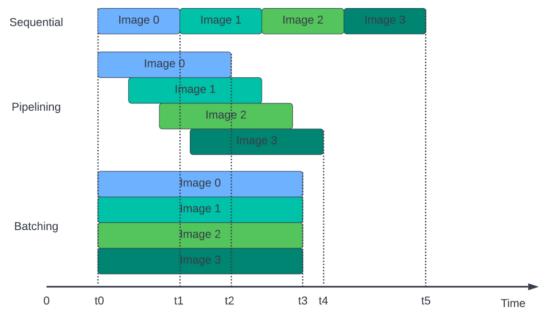

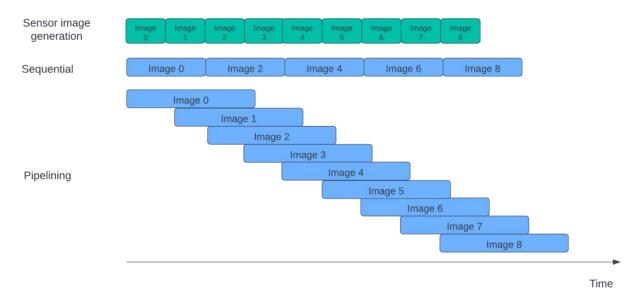

| Figure 26. Sequential, Pipelined and Batched inference.                                               | 51    |

| Figure 27. Inference latency vs temporal resolution trade-off                                         | 52    |

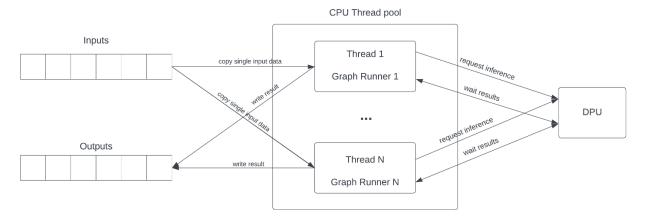

| Figure 28. | Multi-threaded application architecture.                                         | 53 |

|------------|----------------------------------------------------------------------------------|----|

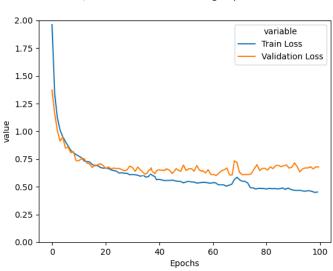

| Figure 29. | Quantization-aware training plot of SqueezeNet                                   | 54 |

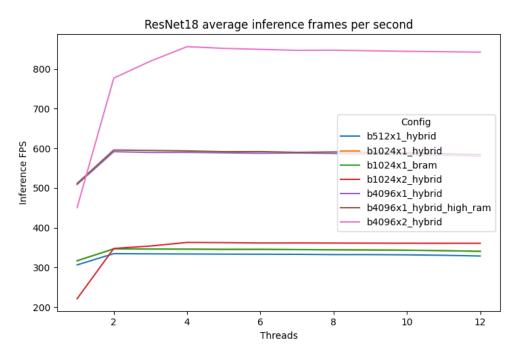

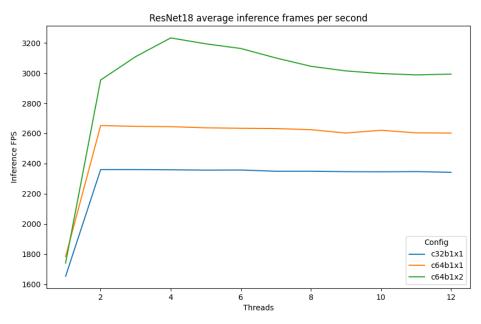

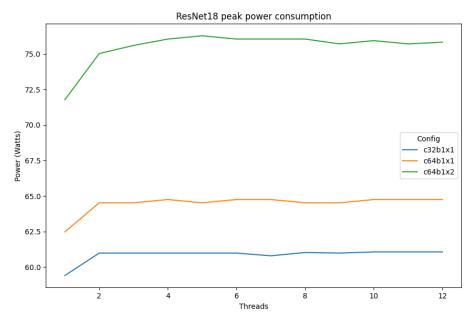

| Figure 30. | ResNet-18 average inference FPS on all ZCU104 configurations.                    | 55 |

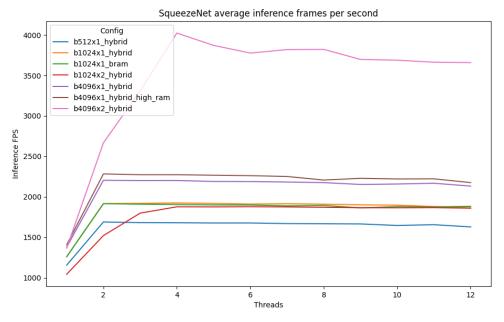

| Figure 31. | SqueezeNet average inference FPS on all ZCU104 configurations.                   | 56 |

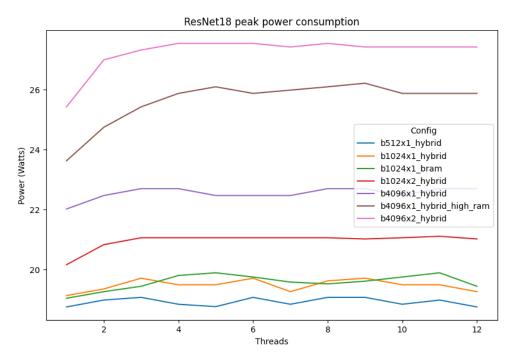

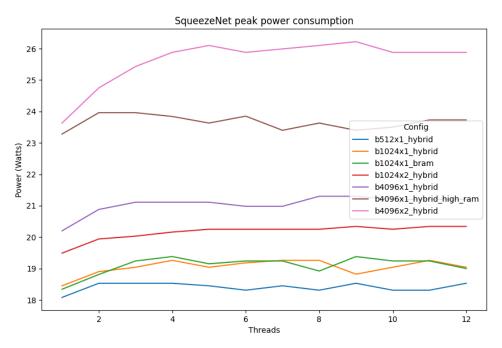

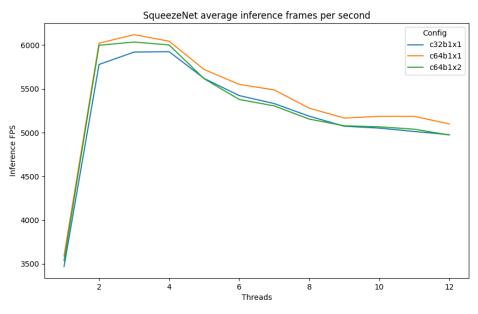

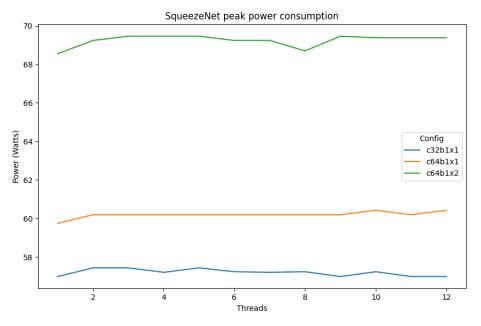

| Figure 32. | ResNet-18 peak power consumption on all ZCU104 configurations.                   | 56 |

| Figure 33. | SqueezeNet peak power consumption on all ZCU104 configurations                   | 57 |

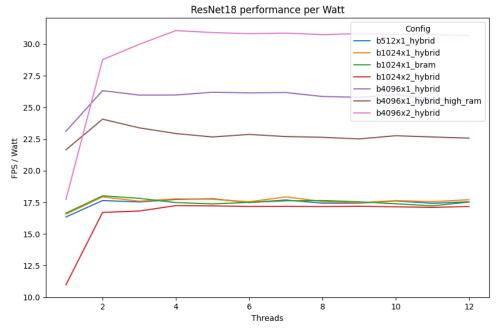

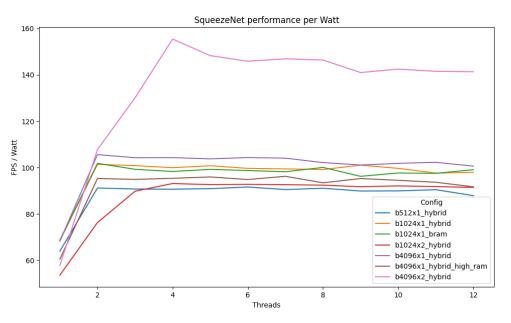

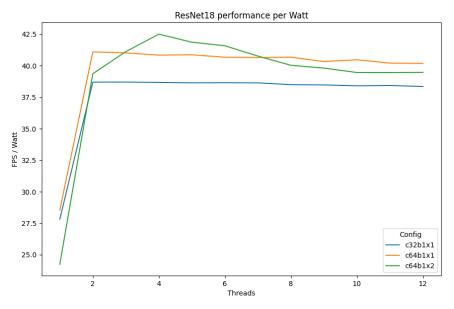

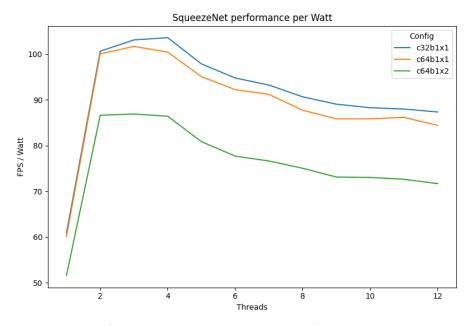

| Figure 34. | ResNet-18 performance per Watt on all ZCU104 configurations.                     | 58 |

| Figure 35. | SqueezeNet performance per Watt on all ZCU104 configurations.                    | 58 |

| Figure 36. | ResNet-18 average inference FPS on all VCK190 configurations                     | 59 |

| Figure 37. | SqueezeNet average FPS on all VCK190 configurations.                             | 59 |

| Figure 38. | ResNet-18 peak power consumption on all VCK190 configurations.                   | 60 |

| Figure 39. | SqueezeNet peak power consumption on all VCK190 configurations                   | 60 |

| Figure 40. | ResNet-18 performance per Watt on all VCK190 configurations.                     | 61 |

| Figure 41. | SqueezeNet performance per Watt on all VCK190 configurations.                    | 61 |

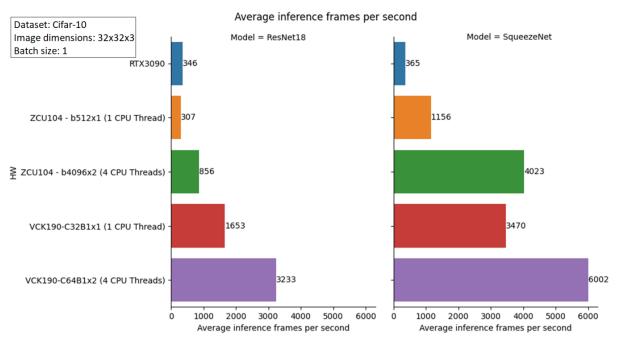

| Figure 42. | Avg inference FPS of RTX3090, ZCU104 and VCK190                                  | 62 |

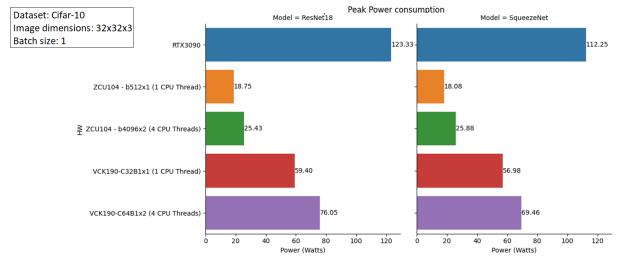

| Figure 43. | Peak power consumptions of RTX3090, ZCU104, and VCK190.                          | 63 |

| Figure 44. | Performance per Watt of RTX3090, ZCU104, and VCK190                              | 63 |

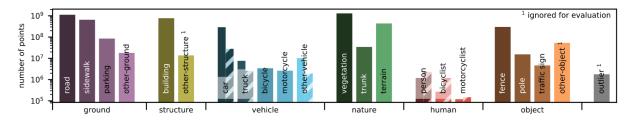

| Figure 45. | Semantic-KITTI dataset points class distribution. Retrieved from [150].          | 69 |

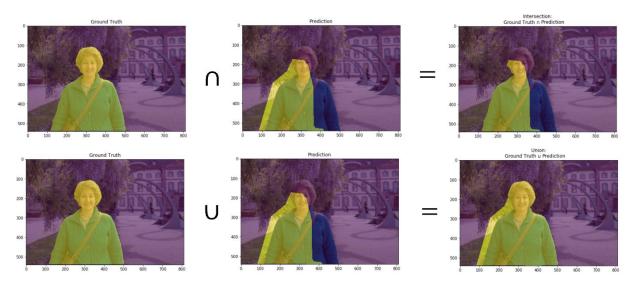

| Figure 46. | Intersection and union of ground truth and model predictions. Adapted from [156] | 71 |

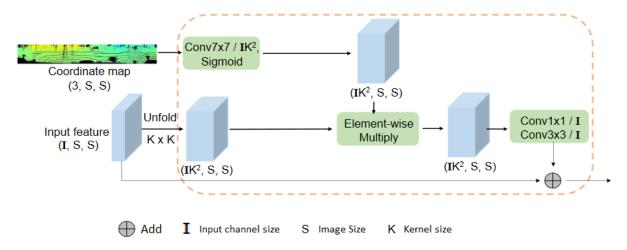

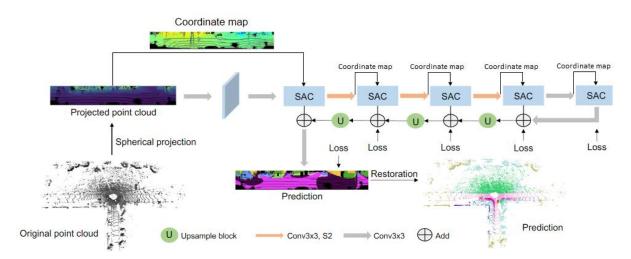

| Figure 47. | SqueezeSegV3 model's SAC block. Adapted from [157]                               | 74 |

| Figure 48. | SqueezeSegV3 model architecture with pre and post-processing. Adapted from [157] | 74 |

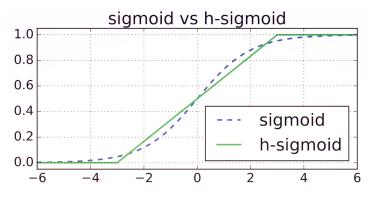

| Figure 49. | Sigmoid and hard-sigmoid activation functions                                    | 77 |

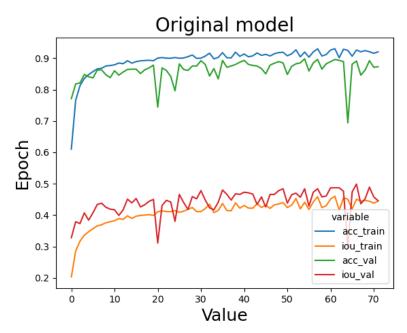

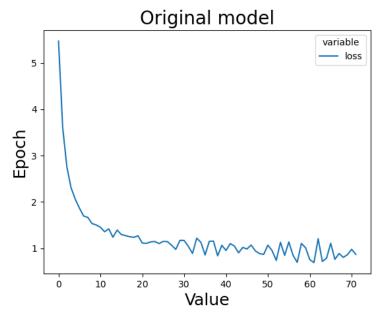

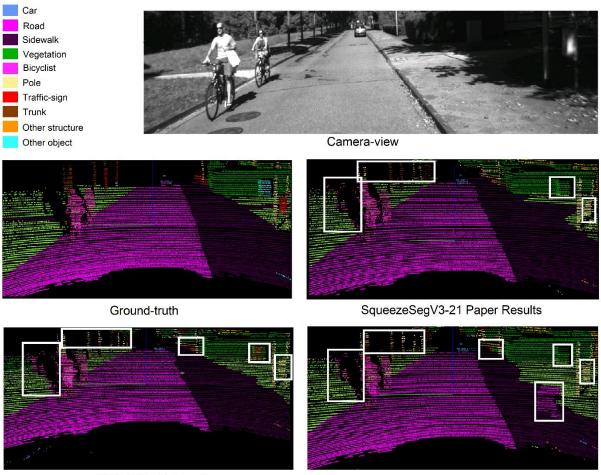

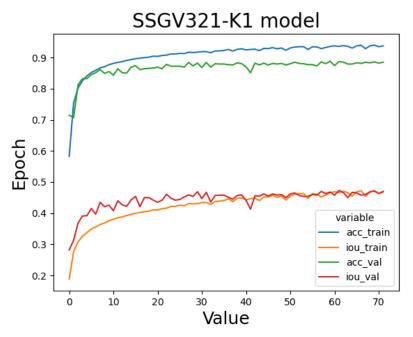

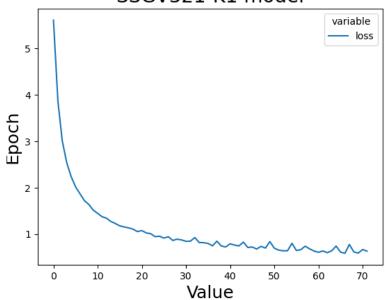

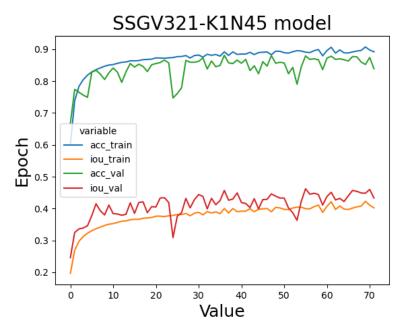

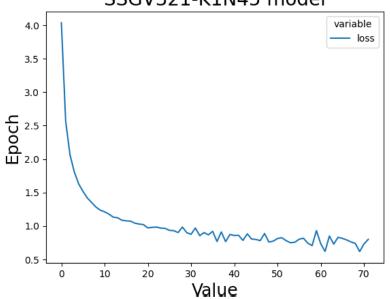

| Figure 50. | SqueezeSegV3-21 original model training: validation accuracies and IoUs.         | 81 |

| Figure 51. | SqueezeSegV3-21 original model training: training set loss.                      | 81 |

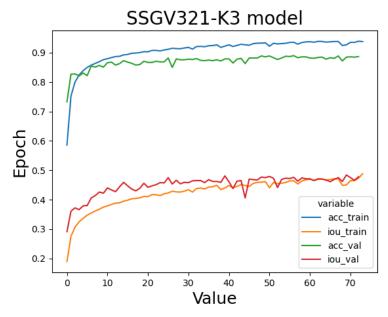

| Figure 52. | SSGV321-K3 model training: validation accuracies and IoUs.                       | 82 |

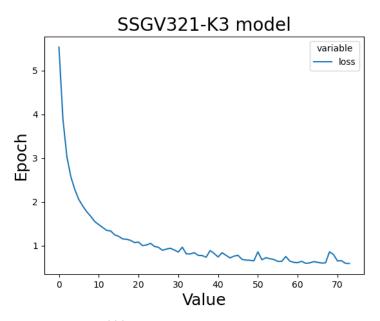

| Figure 53. | SSGV321-K3 model training: training set loss.                                    | 82 |

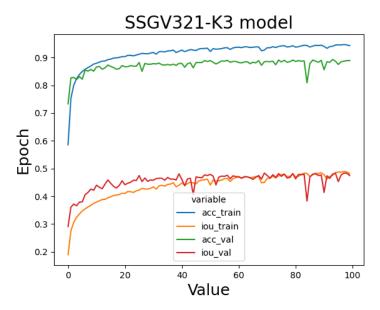

| Figure 54. | SSGV321-K3 model training: validation accuracies and IoUs (100 epochs training)  | 83 |

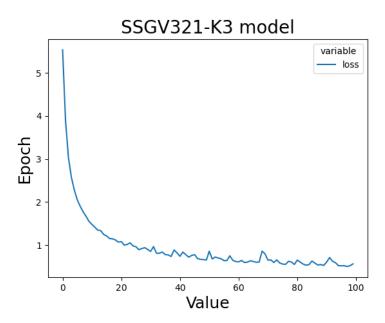

| Figure 55. | SSGV321-K3 model training: training set loss (100 epochs training)               | 83 |

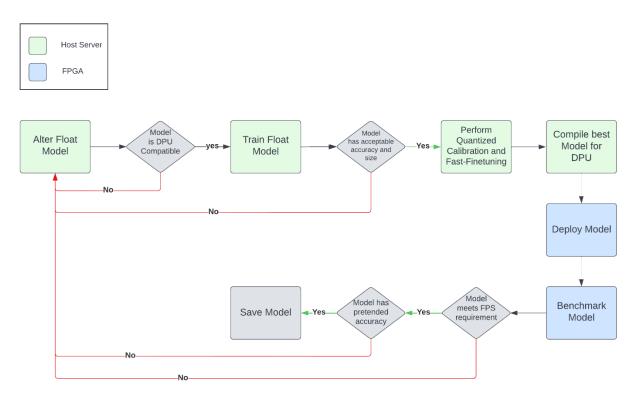

| Figure 56. | Model deployment flowchart                                                       | 85 |

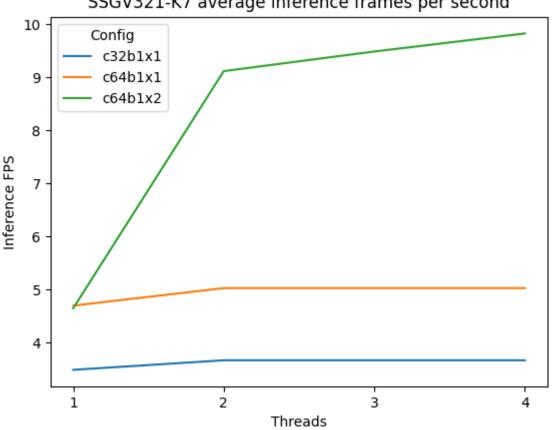

| Figure 57. | SSGV321-K7 average inference FPS on all VCK190 configurations                    | 87 |

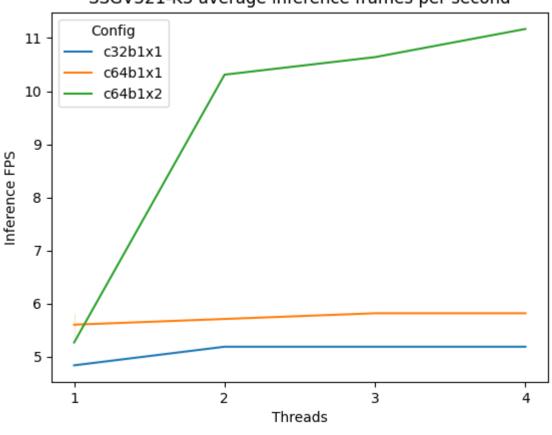

| Figure 58. | SSGV321-K3 average inference FPS on all VCK190 configurations                    | 88 |

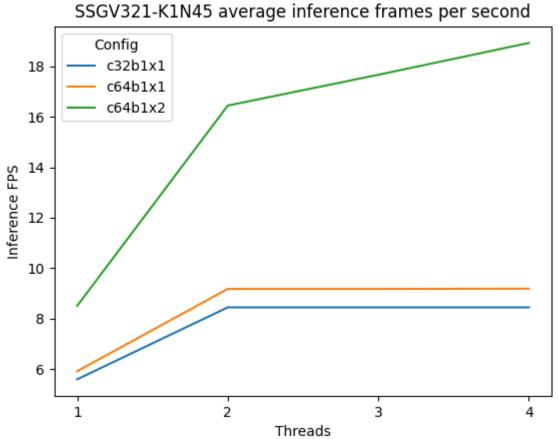

| Figure 59. | SSGV321-K1N45 average inference FPS on all VCK190 configurations.                | 89 |

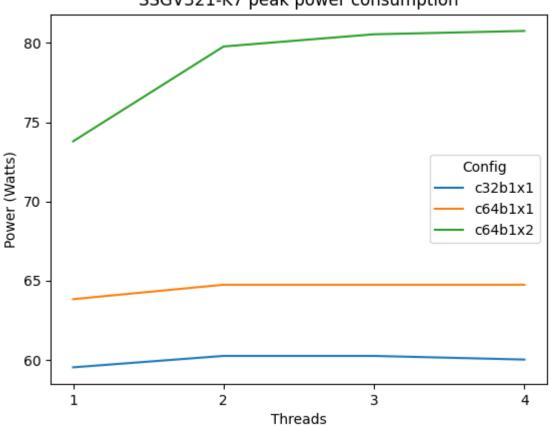

| Figure 60. SSGV321-K7 peak power consumption on all VCK190 configurations.                  | 90       |

|---------------------------------------------------------------------------------------------|----------|

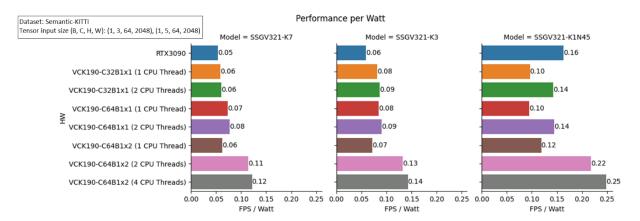

| Figure 61. Performance per Watt of RTX3090 and VCK190                                       | 91       |

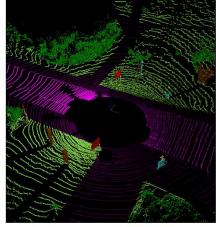

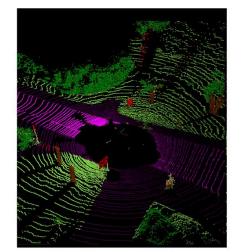

| Figure 62. Semantic-KITTI semantic segmented point clouds. Ground-truth and predictions com | parison. |

|                                                                                             | 92       |

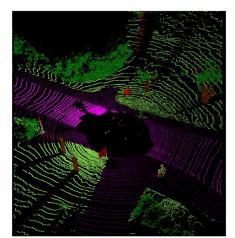

| Figure 63. Detailed semantic segmented point clouds predictions. Comparison with ground-tr  | ruth and |

| camera-view                                                                                 | 93       |

| Figure 64. Excerpt of ResNet-18's torchvision implementation                                | 117      |

| Figure 65. Excerpt of ResNet-18's QAT compatible implementation.                            | 118      |

| Figure 66. SSGV321-K1 model training: validation accuracies and IoUs                        | 143      |

| Figure 67. SSGV321-K1 model training: training set loss.                                    | 144      |

| Figure 68. SSGV321-K1N45 model training: validation accuracies and IoUs.                    | 144      |

| Figure 69. SSGV321-K1 model training: training set loss.                                    | 145      |

# LIST OF TABLES

| Table 1. Market released and future automotive LiDAR sensors (references in the table).              | . 20   |

|------------------------------------------------------------------------------------------------------|--------|

| Table 2. Vitis-Al pre-built DPUs [113]                                                               | . 35   |

| Table 3. ResNet-18 and SqueezeNet total parameter count and floating-point operations considering (  | Cifar- |

| 10                                                                                                   | . 42   |

| Table 4. Zynq UltraScale+ MPSoC ZCU104 and Versal ACAP VCK190 resource comparison                    | . 42   |

| Table 5. Relationship between DPUCZDX8G architectures' parallelism levels and peak operations        | per    |

| cycle                                                                                                | . 44   |

| Table 6. All DPUCZDX8G configurations explored and respective resources.                             | . 45   |

| Table 7. DPUCVDX8G configurations, respective resource utilization and the peak theoretical performa | ance   |

| per cycle                                                                                            | . 46   |

| Table 8. Comparison of Vitis-Al quantization methods' requirements                                   | . 50   |

| Table 9. Vitis-Al quantization accuracy and model size reduction.                                    | . 54   |

| Table 10. ResNet-18 inference DDR memory access information on ZCU104.                               | . 66   |

| Table 11. SqueezeNet inference DDR memory access information on ZCU104                               | . 66   |

| Table 12. LiDAR-based 3D semantic segmentation capable datasets.                                     | . 69   |

| Table 13. Vitis-Al unsupported operations of 3D semantic segmentation deep learning models.          | . 72   |

| Table 14. PointPillars inference latency comparison between partial and complete DPU support         | . 75   |

| Table 15. SqueezeSegV3 support-driven architectural changes.                                         | . 77   |

| Table 16. Top 4 most time-consuming layers during inference                                          | . 78   |

| Table 17. SAC block's convolution kernel size comparison                                             | . 79   |

| Table 18. SqueezeSegV3-21 model variants experimented.                                               | . 79   |

| Table 19. Quantization results of SqueezeSegV3-21 model variants                                     | . 86   |

| Table 20. Model size reduction after quantization.                                                   | . 86   |

| Table 21. SSGV3-21 models framerate comparison between RTX3090 and C64B1x2                           | . 89   |

| Table 22. C64B1x2 peak power consumption on all SqueezeSegV3-21 model variants.                      | . 91   |

| Table 23. SSGV321-K3 and SSGV321-K1N45 inference DDR memory access information on VCK                | 190.   |

|                                                                                                      | . 95   |

| Table 24. Comparison with similar works.                                                             | . 96   |

| Table 25. QAT mandatory operation replacement                                                        | 116    |

| Table 26. DPUCZDX8G and DPUCVDX8G channel parallel and bank depth possible values – Vitis-AI 2.0.   |

|-----------------------------------------------------------------------------------------------------|

|                                                                                                     |

| Table 27. DPUCZDX8G and DPUCVDX8G XIR operations and parameters support – Vitis-AI 2.0 119          |

| Table 28. Pytorch operations to XIR operations translation.    121                                  |

| Table 29. ResNet-18 and SqueezeNet average inference FPS and peak power consumption across all      |

| ZCU104 and VCK190 configurations                                                                    |

| Table 30. SqueezeSegV3-21 original implementation's list of pytorch operations and respective       |

| parameters                                                                                          |

| Table 31. Per-class IoU of the 3 SSGV3-21 variants on the validation set of Semantic-KITTI 145      |

| Table 32. SSGV321-K7, SSGV321-K3, and SSGV321-K1N45 average inference FPS and peak power            |

| consumption across all VCK190 configurations                                                        |

| Table 33. SSGV321-K7 layer-by-layer average computation time during inference on C64B1x2 with 1 CPU |

| thread                                                                                              |

| Table 34. Average accuracy and average IoU of SSGV321-K3. 72 epochs vs 100 epochs training 151      |

| Table 35. Per class IoU of SSGV321-K3. 72 epochs vs 100 epochs training                             |

# LIST OF ABBREVIATIONS AND ACRONYMS

# A

| ADAM   | Adaptive Moment                         |

|--------|-----------------------------------------|

| ADAS   | Advanced Driver-Assistance Systems      |

| API    | Application Programming Interface       |

| ASIC   | Application-Specific Integrated Circuit |

| B      |                                         |

| BEV    | Bird's Eye View                         |

| BNN    | Binary Neural Network                   |

| BRAM   | Block Random Access Memory              |

| C      |                                         |

| CNN    | Convolutional Neural Network            |

| CPU    | Central Processing Unit                 |

| CU     | Compute Unit                            |

| D      |                                         |

| DDR    | Double Data Rate                        |

| DPU    | Deep Learning Processing Unit           |

| F      |                                         |

| FLOPS  | Floating-point Operations               |

| FPGA   | Field Programmable Gate Array           |

| FPS    | Frames per Second                       |

| FV     | Front View                              |

| G      |                                         |

| GPU    | Graphical Processing Unit               |

| GOPS   | Giga Operations                         |

| GFLOPS | Giga Floating-Point Operations          |

| H      |                                         |

| HW     | Hardware                                |

| I     |                                  |

|-------|----------------------------------|

| ICP   | Input Channel Parallelism        |

| loU   | Intersection over Union          |

| IP    | Intellectual Property            |

| L     |                                  |

| Lidar | Light Detection and Ranging      |

| Μ     |                                  |

| mAP   | Mean Average Precision           |

| mloU  | Mean Intersection Over Union     |

| 0     |                                  |

| OCP   | Output Channel Parallelism       |

| Ρ     |                                  |

| PE    | Processing element               |

| PP    | Pixel Parallelism                |

| PS    | Processing Subsystem             |

| Q     |                                  |

| QAT   | Quantization-aware training      |

| R     |                                  |

| ReLU  | Rectified Linear Unit            |

| S     |                                  |

| SAC   | Spatially Adaptive Convolution   |

| SIMD  | Single Instruction Multiple Data |

| т     |                                  |

| TNN   | Ternary Neural Network           |

| TOF   | Time of Flight                   |

| TOPS  | Tera Operations                  |

| TPU   | Tensor Processing Unit           |

| U     |                                  |

| URAM | Ultra Random Access Memory         |

|------|------------------------------------|

| V    |                                    |

| VART | Vitis-Al Runtime                   |

| X    |                                    |

| XIR  | Xilinx Intermediate Representation |

| XRT  | Xilinx Runtime                     |

## GLOSSARY

- Any mathematical function used in a neural network's layers to introduce **Activation function** non-linearity in the output of the layer's neurons. Batch (Training) A hyperparameter that defines the number of instances to process before updating the internal model parameters during training of a neural network. **Batch (Inference)** The number of instances to inference over in parallel. **Bit-width** The number of bits necessary to represent an integer as a binary number. (Quantization) **Computer Vision** A field of Artificial Intelligence concerned with the extraction of high-level information from digital visual inputs such as images, videos and point clouds. **Cross-entropy Loss** A loss function used to measure the performance of a classification model that outputs probabilities between 0 and 1. Its value increases as the predicted probability diverges from the actual value. **Deep Learning** A subset of Machine Learning based on Deep Neural Networks in which multiple layers of processing are used to extract progressively higher-level features from data.

- **Deep Neural Network** In contrast with Shallow Neural Networks, typically referred to as just Neural Networks, Deep Neural Networks have multiple layers between the input and output layers.

- **Deep Learning Model** The resulting weights and biases of a Deep Neural Network fitted to the training data.

- **Feature** An individual measurable property or characteristic of the input. For example, age, gender, weight of a person or the number and location of a specific pattern in an image/point cloud.

- **Feature Map** Each feature map or activation map is the result of convolving an image using a kernel/filter of a CNN and passing it through an activation function.

- **Filter / Kernel (CNN)** Set of learnable weights spatially structured that learn to extract relevant patterns when convolved over the input.

Floating-point A system to represent, with a fixed number of digits, real numbers of

**representation** different orders of magnitude. Differs from fixed-point representation by allowing a variable number of integer and fractional digits.

- Loss Function A function that is used to evaluate how well an algorithm models a dataset.

- **Neural Network** Neural Networks are a subset of Machine Learning algorithms that combine a set of progressively learned functions to model the given training data and perform predictions. Each individual function is composed of a set of parameters, namely the weights and biases that are combined through the notion of a neuron and passed through an activation function. The way individual functions are combined is through the notion of layers.

- **Off-chip memory** Memory that resides outside the chip where the computations happen. It has higher access latency but is also bigger than on-chip memory.

- **On-chip memory** Memory that resides in the same chip where the computations happen. It has very low access latency but is also very small.

**Point Cloud** A set of points in 3D space representing one or more objects in a scene.

# **INTRODUCTION**

INTRODUCTION

## 1.1 **CONTEXT**

LiDAR (Light Detection and Ranging) sensors have been widely recognized as key components for advanced driver-assistance systems (ADAS) and autonomous driving as they enable the tri-dimensional mapping of objects. The additional information extracted by the LiDAR is critical for the central processing unit of the vehicle to perceive the surrounding scenario. Evidence for this trend is the ever-growing adoption of the LiDAR sensor in the sensor suite of autonomous driving solutions in the market [1], [2], [3], [4], [5], [6], [7].

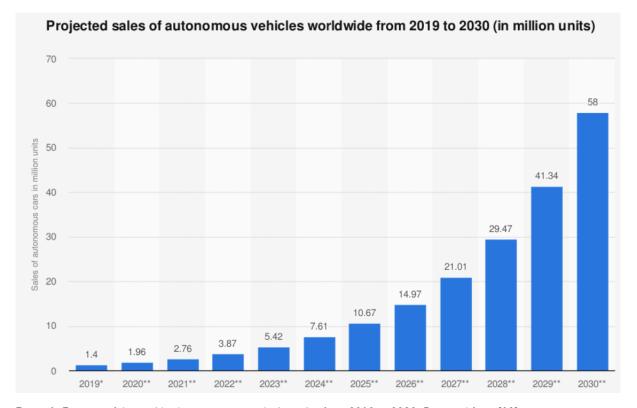

Additionally, the research in autonomous systems has seen dramatic advances in recent years, due to the increase in available computing power and reduced cost in sensing, computing technologies, and price of the necessary hardware, resulting in the maturing technological willingness to produce fully autonomous vehicles. Figure 1 shows the forecast from Statista, a company that specializes in market and consumer data, for the projected sales of autonomous vehicles worldwide from 2019 to 2030. The growth in sales evidences the wide adoption of autonomous driving solutions in the automotive market. Several other sources also estimate the increasing demand and market size of autonomous driving-related products in the automotive market [8], [9].

Figure 1. Forecast of the worldwide autonomous vehicles sales from 2019 to 2030. Retrieved from [10].

INTRODUCTION

The core competencies of an autonomous vehicle system are classified into three categories, namely perception, planning, and control [11]. While machine learning algorithms based on deep neural networks have demonstrated great performance in several complex cognitive tasks [12], [13], a significant gap in the energy and efficiency of the computational systems that implement perception algorithms still exists [14]. Most of these algorithms run on conventional computing systems such as Central Processing Units (CPUs) and General-Purpose Graphical Processing Units (GPUs). Alternatives containing embedded hardware solutions, such as Field Programmable Gate Arrays (FPGAs), have started to be explored to help develop solutions that allow more efficient computation of deep neural networks [15], [16].

### 1.2 **MOTIVATION**

Several works have demonstrated the capabilities of FPGAs for designing real-time applications that perform deep neural network inference on FPGAs [17], [18], [19]. Some works specifically focus on the implementation of such neural networks using LiDAR data [20], [21], [22]. The possibility to concurrently design hardware and software, a feature of FPGAs, allows for the exploration of more efficient solutions. Not only can one adapt the software for the underlying hardware, but the hardware itself can also be finetuned for the specific application. More, this process can be done iteratively.

With the advent of high-level tools [23], [24] that open the hardware-software co-design research to machine learning and deep learning engineers without FPGA expertise, it becomes possible to increase the efficiency of deep neural networks by reducing power consumption while maintaining the desired framerate.

## 1.3 **OBJECTIVES**

The main goal of this work is to train and deploy a deep neural network on an FPGA to perform one perception task using LiDAR sensor data, in the form of a point cloud. Power consumption should be kept to a minimum while maximizing framerate, without losing sight of accuracy metrics. Hardware limitations are also expected to heavily impact the development of a solution and so the search for fitting neural network architectures and consequent computation layers should be carried out with them in mind. A review of the available tools for deep neural network deployment on FPGAs should be conducted. Once a tool is selected, a thorough exploration of the capabilities of the tool, as well as an evaluation of its suitability for the development of a real-time, low-power inferencing application, should be validated.

3

During experiments, framerate and power consumption should be the target metrics along with the appropriate accuracy metrics of the perception task being solved.

## **1.4 Structure of Dissertation**

Chapter 2 introduces the technologies and concepts relevant to the understanding of this thesis. Chapter 3 includes a revision of past literature works that include hardware, algorithms, and works with a similar scope to this work. Chapters 4 and 5 contain the two experiments conducted in this thesis. The first explores *Vitis-AI*, the main tool used in this work, by validating its suitability for the objectives of this work. The second implements the proposed solution to the problem this thesis aims to solve. Both chapters 4 and 5 contain individual results, analysis, and respective discussions. Lastly, chapter 6 examines the work and concludes its impact on the problems it aimed to solve. It also contains a section dedicated to suggesting further research opportunities.

# 2 TECHNOLOGIES AND CONCEPTS

## 2.1 **Perception in Autonomous Driving**

A highly autonomous system must understand its environment by solving highly complex cognitive tasks that allow it to respond to every situation. As a result, self-driving cars rely heavily on software to bridge the gap between sensor information and mechanical vehicle actuation, such as steering and braking. From the collection and processing of sensory data to the control of the vehicle's actuators, there is a system that encapsulates it all.

#### 2.1.1 Advanced Driver-Assistance Systems

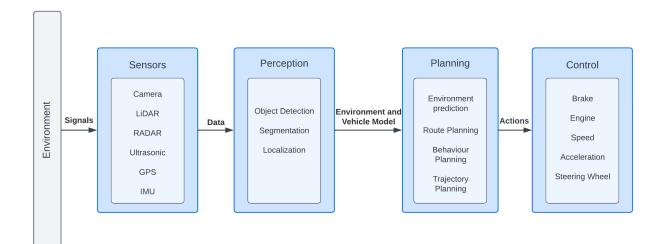

ADAS are the electronic systems in a vehicle that use advanced technologies to assist the driver. They use a combination of sensor technologies to perceive the world around the vehicle, and then either provide information to the driver by issuing warnings or actively controlling the vehicle when necessary. To do so, across the desired route, the system should be able to perceive its surroundings and extract high-level information which may be critical for safe navigation. The consequent steps consist in taking the extracted information to plan a set of actions and performing them by controlling the vehicle actuators i.e., the devices that transform an input signal into motion. Following this description, one can distinguish 3 main modules namely perception, planning, and control [11]. Figure 2 presents a diagram of an ADAS containing all 3 modules and their respective interactions.

Figure 2. Block diagram of an ADAS.

The perception module directly actuates on the raw sensory data collected by an array of sensors and is responsible for the extraction of relevant features from the multiple sensors' output. These features represent components of the vehicle's surroundings that influence the driving task. Having all these components correctly perceived is necessary for a perception module of a high-level automation ADAS and requires highly efficient and accurate perception algorithms.

#### 2.1.2 ADAS PERCEPTION REQUIREMENTS AND METRICS

Highly accurate, low response time, low energy consumption, and minimal physical size are four fundamental requirements of an ADAS identified in this work. There are other requirements, such as the relevancy of the information provided, that are also fundamental. However, these four are directly linked with performance and efficiency, the focus of this work. Metrics are usually defined to quantify how compliant an application or system is to a set of requirements. Refresh rate, which is linked to the response time requirement, directly depends on the rate at which the sensors can produce the data to be used by the perception module. It is then important to establish a value that considers the LiDAR solutions currently available in the market as well as upcoming solutions. 3.1 defines a specific value for the refresh rate by listing the LiDAR sensors currently available in the market and future solutions.

Contrarily to refresh rate, it is hard to define a maximum value for metrics associated with accuracy, energy consumption, and physical size since they either depend on the current perception algorithms, the available hardware, and the vehicle(s) that the ADAS will target. Therefore, this work will not establish specific values for these metrics. Instead, it will explore and propose solutions that keep these values as close as possible to their optimal values. This should be accomplished by carefully reviewing state-of-the-art solutions and choosing appropriate hardware architectures to deploy the best-suited perception algorithms.

## 2.2 LIDAR SENSOR

The LiDAR's ability to produce an extremely accurate three-dimensional position of surrounding objects and its innate robustness to exterior lighting conditions has pushed the adoption of this sensor in a large range of automotive perception solutions [1], [2], [3].

7

#### **2.2.1 WORKING PRINCIPLE**

LiDAR is an active remote sensing system. It is active because it generates energy, in this case, light, to collect data about its surroundings and remote because it does so by detecting the energy that is reflected from the surfaces. One of the techniques used in LiDAR to collect depth information is through what is called the time of flight (ToF). In ToF, an emitter fires short laser pulses that reflect off surrounding objects and are captured by the receiver. Since the emitter and receiver are approximately at the same position, it is possible to calculate the distance to the reflecting object using the known speed of light and the delay between the emission and reception of the laser. Usually, LiDAR sensors have multiple emitter-receiver pairs.

#### 2.2.2 POINT CLOUDS

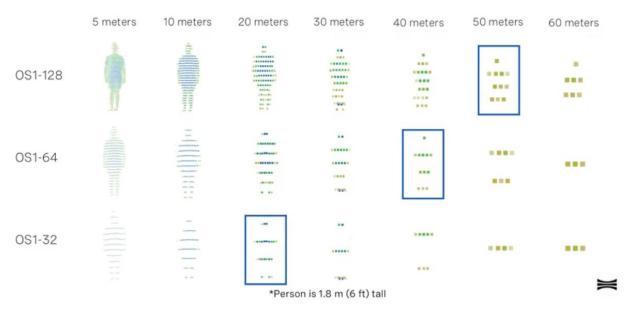

The spatially organized LiDAR data is referred to as a point cloud, a set of points with three-dimensional position and intensity information of the reflecting surfaces in the field of view. Depending on the field of view and resolution of the sensor, point clouds can easily become extremely large, usually, 100k-200k 3D points per frame, which results in a total size of around 1.6MB-3.2MB considering the usual format of 4 floating point values to represent x, y, z coordinates and intensity information. However, if the resolution of the LiDAR is not sufficiently high, the effective range is reduced i.e., objects that are distant from the sensor might become underrepresented or even completely undetectable. Figure 3 depicts a LiDAR's effective range. The same is true for the field of view which delimits, both horizontally and vertically, the surrounding volume scanned. The coordinates of objects that lie outside the field of view will naturally be absent from the point cloud.

Although point clouds are extremely useful to the perception module, several challenges emerge when processing point cloud data, and should be addressed when designing perception algorithms. These challenges include variability in point density, diversified measured intensity, inter-class reflectivity overlap, noise, sparsity, permutation and rigid transformation invariance, and occlusions.

Figure 3. The effective range of Outer's OS1 LiDAR. Adapted from [25].

## 2.3 DEEP LEARNING IN POINT CLOUDS

Advancements in device capability involving computing power, sensor resolution, and costeffectiveness, as well as the adoption of highly parallel hardware such as GPUs, have broken most of the barriers to the adoption of deep learning. Also, the increasing availability of high-quality and high-volume datasets highly benefits deep learning models contrary to more traditional approaches that struggle with high-volume data.

#### **2.3.1 THE DEEP LEARNING APPROACH**

In the last few years, deep learning approaches have achieved state-of-the-art results in multiple perception tasks involving images, sound, and text. However, a similar level of success for 3D computer vision is only now beginning to take shape, mainly due to the larger amount of data and complexity that point clouds encompass compared to images and the hardware limitations that become even more apparent with data-heavy point clouds.

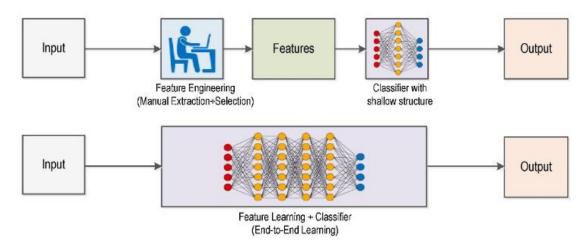

A typical computer vision pipeline consists of two distinct phases. The first phase usually called feature extraction and more recently, feature learning, consists of the extraction of descriptive or informative patches in the data called features or sometimes also called descriptors. Specifically, in point clouds, features are usually spatial and geometric attributes or relationships between points. The second phase

of the pipeline, which usually consists of a classifier or regressor, is responsible for performing classification or regression or both based on the previously extracted features.

With the adoption of deep learning, both the feature extraction and classification or regression are done "end-to-end" with a deep learning-based model, meaning that the input of the model is the point cloud, and the output is a classification or regression tensor. This leaves out the need for the cumbersome and error-prone process of manual feature extraction that usually leads to poorly generalizable models. Currently, state-of-the-art results on perception tasks in point clouds use end-to-end deep learning models as pipelines. Figure 4 compares both vision pipelines.

Figure 4. Comparison between a traditional and DL computer vision pipeline. Retrieved from [26].

#### 2.3.2 POINT CLOUD PERCEPTION TASKS

Similarly to 2D computer vision, to evaluate deep learning models on point cloud data, there are a set of established perception tasks. Particularly in autonomous driving perception, this work highlights three.

#### 2.3.2.1 3D OBJECT DETECTION

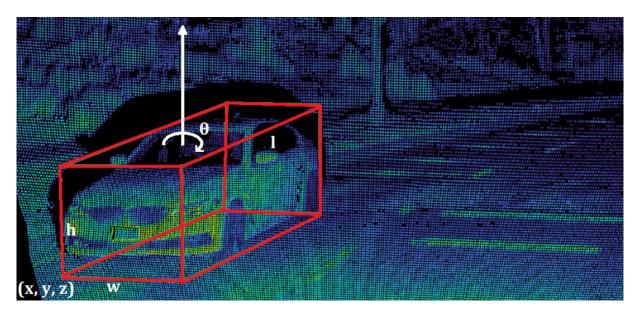

The goal of 3D Object Detection is to encapsulate every instance belonging to a set of predefined categories in the point cloud with an oriented 3D bounding box and an associated semantic label. As portrayed in Figure 5, the bounding box information can be represented using the coordinates (x, y, z) of the bounding box center, (h, w, l) representing respectively the height, width, and length of the bounding box,  $\theta$  representing the object's yaw orientation and  $y_i$  representing the class the object corresponds to. An assumption made about the bounding boxes is that the objects are on the ground plane, and so their orientation can be described only using the yaw angle.

Figure 5. 3D object detection in a LiDAR frame.

#### 2.3.2.2 3D SEMANTIC SEGMENTATION

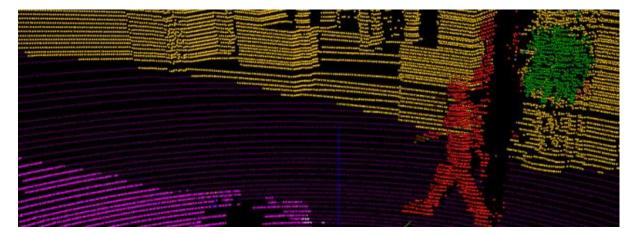

3D point cloud segmentation aims to label homogeneous regions of a point cloud according to what they are representing. A more formal definition of the task is to assign every 3D point from the point cloud  $X = \{x_1, x_2, ..., x_N\}$  with a semantic or instance label  $y_i$  from a set  $Y = \{y_1, y_2, ..., y_K\}$  representing K distinct categories. Segmentation can be subdivided into sub-tasks by the different levels of granularity. At the coarser level, there is semantic segmentation where each group of points is represented by a semantic label such as road, car, or building. This type of segmentation is illustrated in Figure 6. At the intermediate level, there is instance segmentation which is not only trying to distinguish points based on their semantic meaning but also separating different instances with the same semantic meaning. This refers to the case where the objective is to not only identify that a group of points represents a car but to be able to distinguish different cars by assigning each of the groups a different instance label. Finally, the more fine-grained sub-task is part segmentation where several parts of a semantic region are distinguished. For example, from a group of points representing a car, segment the windshield, tires, etc.

Figure 6. 3D semantic segmentation of a LiDAR point cloud.

#### 2.3.2.3 3D OBJECT TRACKING

Given the locations and labels of a set of objects in a frame, the task of object tracking is to estimate their state in subsequent frames. A naive approach to the problem could be using object detection over all frames, but one obvious problem arises from this solution. If multiple objects are in the frame, the label associated with each object should remain unchanged over the following frames and object detection treats each frame independently. So, there is no way to guarantee that the detector attributes the same label to the detected objects over all frames. To solve this issue, one possible solution is to model the motion of the object i.e., the dynamic object's heading and velocity so that the most likely position in future frames can be predicted, effectively reducing the search space of a detector.

#### **2.3.3 POINT CLOUD REPRESENTATION**

Due to the unstructured and sparse nature of the point clouds, some transformations are usually carried out to generate a structured representation. The following sections present and explain the different representations, providing examples of deep learning models that use the representations.

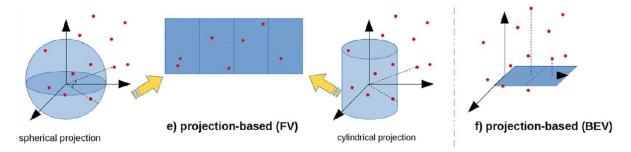

#### 2.3.3.1 PROJECTION-BASED

2D deep learning on images has achieved remarkable results using deep convolutional architectures on tasks such as image classification [27], [28], object detection [29], [30], and semantic segmentation [31]. Besides, well-established 2D datasets containing a lot of data, such as ImageNet [32], are readily available leveraging the application of deep convolutional models pre-trained on these datasets to 2D images. However, the convolution operation is performed on data that is ordered, regular, and on a structured grid. For this reason, to benefit from the performance of established 2D deep convolutional networks, a natural approach is structuring point clouds in a way that allows the application of 2D convolution operations. One way to achieve this is by performing a projection of the 3D point cloud into a 2D grid. Several projection schemes have been used in different works where predominantly two main schemes are used: Front View (FV) [33], [22] and Bird's Eye View (BEV) [34], [35], [36]. Both are illustrated in Figure 7.

Figure 7. Illustration of spherical, cylindrical, and bird's eye view projections of point clouds. Adapted from [37].

Unfortunately, there is a discretization inherent to the projection operation which results in a loss of information. Because the 2D grid has a limited resolution, several points in the point cloud are likely to end up in the same grid coordinate. There are various ways to deal with this situation. Xu, C. et. al only keep the point with the largest range value  $r = \sqrt{x^2 + y^2 + z^2}$ . Another possible approach is to combine the x, y, z, and intensity values of all the points through some average or even a small multi-layered perceptron. *PointPillars* [38] is a good example of the latter approach.

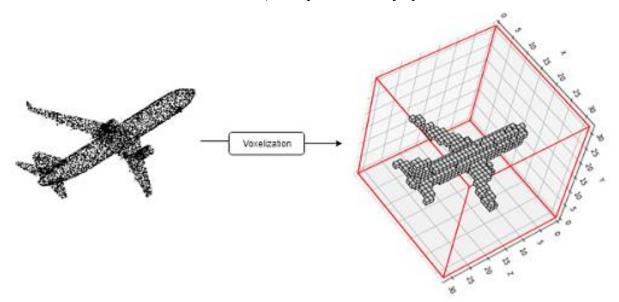

#### 2.3.3.2 VOXEL-BASED

A different approach that allows the application of convolutions directly on 3D point clouds is through what is called a voxel-based representation. However, in this approach, the convolution operations used are 3D convolutions.

A voxel is a volume element that represents a specific grid value in 3D space. Voxel-based approaches partition the [L, W, H] 3D point cloud into fixed-sized voxels through voxelization by assigning points in the point cloud to voxels according to their 3D coordinates. The voxel represents all the points assigned to itself by combining features of those points. Figure 8 portrays the voxelization process of a point cloud of an airplane.

However beneficial to the use of convolution operations, a voxel-based representation has some limitations. Firstly, not all voxels will carry important information because point clouds have denser and sparser zones. The sparser zones may contain lots of empty voxels. This results in a memory inefficient representation of the 3D space and wasted computation when applying 3D convolutions [39]. Secondly, because the computational and memory cost increases cubically with the increase in voxel resolution, there is a limit on the total number of voxels, usually around  $30^3$  [39].

Figure 8. Voxelization of a point cloud using  $30^3$  voxels. Retrieved from [40].

#### 2.3.3.3 POINT-BASED

Both projection-based and voxel-based representations discretize the point cloud resulting in a loss of information. Contrarily, the point-based approach looks to fully exploit the 3D geometry and shape of the point cloud without information loss.

As noted in the work of Shi, S. et al., projection and voxel-based representations are more computationally efficient, but lose fine-grained localization information, while point-based approaches don't lose so much information, but result in a higher computational cost [41]. Similarly, Deng, J. et al. also suggest that point-based approaches can better retain precise point positions while having a higher computational overhead compared to projection and voxel-based representations [42].

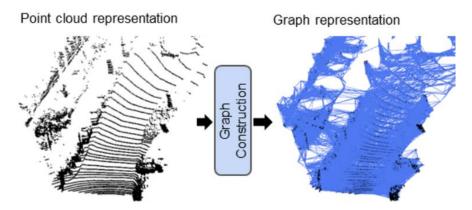

#### 2.3.3.4 GRAPH-BASED

Graph-based approaches convert the point cloud into a graph, as illustrated in Figure 9. The nodes of the graph correspond to the points and the edges represent the relationship between point neighbors

inside a fixed radius. The explicit representation of the relationship between point neighbors through the graph edges is good for modeling the correlation between points in the point cloud [40], so more local spatial correlation features can be extracted from the grouped edge relationships on each node [43]. Recently, more works explore this representation to solve 3D perception tasks [44], [45], [46], [47].

Figure 9. Illustration of a graph representation of a point cloud. Adapted from [48]

# 2.4 DEEP NEURAL NETWORK COMPRESSION

Although difficult to prove, deeper neural network parameter count has been long observed to be positively correlated with accuracy. From one extreme where natural language processing models have up to billions of parameters [12], to the other where smaller models are designed to fit in embedded hardware [49], there is a need to reduce the size of neural networks, and the computation needed to run them, without compromising accuracy.

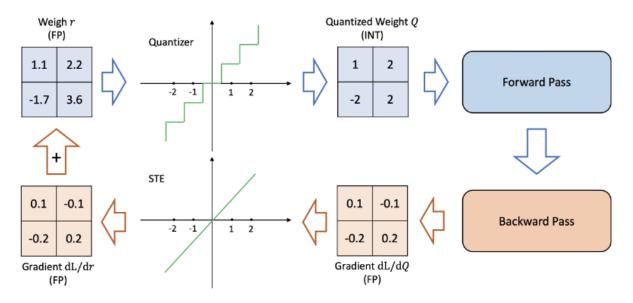

#### 2.4.1 QUANTIZATION

Historically most neural networks are trained using 32-bit floating point values. The core idea behind quantization is to reduce the representation of weights and biases, usually to 16-bit, 8-bit, 4-bit, or even 2-bit and single-bit integers. The challenge is to map the set of possible values of a neural network's parameters to a fixed discrete set of integers, effectively minimizing the number of bits required to represent the values. Since activation outputs are usually between 0 and 1 e.g., sigmoid, or at least can be bounded by a low integer value e.g., relu6, the weights of a neural network usually remain within a reasonable small range of values and consequently are good candidates for being represented using lower bit-widths [50].

Besides the obvious reduction in model size, there are added benefits of using lower-bit integer representations such as a reduction in energy consumption and inference latency. Chen, Q. et al.

compared an 8-bit fixed-point adder and multiplier to a 32-bit floating point adder and multiplier concluding that the energy and area of a fixed-point adder and multiplier scale approximately linearly and quadratically respectively with the number of bits used for representation [51]. Also, if the model does not fit on local/on-chip memory, and off-chip memory must be accessed, the lower bandwidth inherent to this access, when compared to local memory access, is a major bottleneck of inference latency [52]. Furthermore, off-chip memory accesses result in orders of magnitude higher energy consumption [23]. For these reasons, model size reduction can decrease inference latency by allowing for the exploration of memory locality. Even if it is not possible to avoid off-chip memory accesses, it is advantageous to have lower bit-width representations since it improves the memory bandwidth i.e., the cost of moving information is smaller. One last advantage of lower bit-width representations is the exploration of Single Instruction Multiple Data (SIMD) [50].

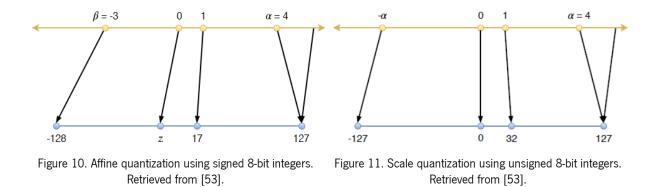

The quantization problem can be seen as the mapping operation of floating-point values in a predetermined range of values to integer values that can be represented with b bits. The quantization and de-quantization operations can be described as

$$\begin{cases} x = S(x_q + Z) \\ x_q = (\frac{1}{S} \cdot x - Z) \end{cases}$$

(Equations 1 and 2)

where  $x \in [\alpha, \beta]$  are the floating-point values, and  $x_q \in [\alpha_q, \beta_q]$  are the quantized values. For a *b*-bit representation,  $[\alpha_q, \beta_q]$  would be equal to  $[-2^{b-1}, 2^{b-1} - 1]$  and  $[0, 2^b - 1]$  respectively when using signed and unsigned integers to represent the quantized values. *S* and *Z* are variables that must be derived. Appendix I contains the derivation of *S* and *Z*. Their values are

$$\begin{cases} S = \frac{\beta - \alpha}{\beta_q - \alpha_q} \\ Z = round\left(\frac{\alpha \cdot \beta_q - \beta \cdot \alpha_q}{\beta - \alpha}\right) \end{cases}$$

(Equations 3 and 4)

The above quantization mapping is known as affine quantization. In the special case where Z is forced to have the value 0, the name scale quantization or symmetric quantization is given. Figure 10 and Figure 11 respectively depict affine and scale quantization using 8-bit integers.

There is one potential downside to quantizing neural networks. Usually, an accuracy drop can be observed, especially at lower bit-widths. This is to be expected as the range of values that can be encoded is halved with each removed bit. However, the drop in accuracy is usually not as significant and several quantization techniques have been shown to preserve accuracy, even on the more challenging models to quantize [54]. A review of the proposed quantization techniques and their results can be found in 3.3.

#### **2.4.2 OTHER TECHNIQUES**

Pruning, usually used alongside quantization, is the process of removing part of a neural network's parameters, namely the weights while ensuring that the model's performance doesn't drop below a specified threshold. Typically, a pruning pipeline consists of first training a network, then pruning the model according to a specific strategy, and finally fine-tuning the pruned network to compensate for the performance loss. This is done iteratively and in each iteration N number of parameters are removed. However, if the percentage of pruned parameters is high, the matrices representing model weights become sparse. Consequently, matrix operations become harder to accelerate and memory-bound [55].

More techniques have been proposed to reduce neural network size, improve energy efficiency and reduce inference latency, such as low-rank factorization [56] and knowledge distillation [57]. However, like quantization and pruning, those target the neural networks. A different particularly interesting approach is point cloud sampling which consists of sub-sampling the point cloud by preserving the original structure while reducing the number of points. Random sampling and farthest point sampling are the two traditional sampling algorithms [37]. Lang, Itai, Manor, Asaf, and Avidan Shai argue that traditional

sampling approaches do not consider the perception task that the network consuming the point cloud as input is performing. For this reason, they propose a technique that learns task-specific sampling, improving results significantly [58].

# 3.1 AUTOMOTIVE LIDAR REFRESH RATE

LiDAR sensors can usually be configured to operate at different frame rates, allowing them to suit different tasks and scenarios. The maximum frame rate of each sensor is of utmost importance, as it defines the minimal real-time response time that perception algorithms must adhere to. Table 1 lists LiDAR sensors' frame rate as well as information about each sensor's market release year. The selection criteria for the devices detailed in this section prioritizes devices by reputable, industry-leading LiDAR manufacturers - some of which already have commercially available devices, like Continental, Valeo, and Ouster - or startup companies that have established themselves by developing state-of-the-art LiDAR technologies, as is the case of *Innoviz* and *Baraja*. The results from Table 1 show that the frame rate is typically below 30 Hz and that the lower bound, although with some exceptions, is usually 5 Hz. From these values, one may estimate a minimum response time of 33 ms for the perception algorithms. However, it should be noted that higher frame rates result in lower resolutions, regardless of the sensor technology. A lot of the below listed LiDARs allow regulating this resolution/frame rate trade-off by having a refresh rate interval rather than a single value. Examples are Velodyne's HDL-64E and VLS-128, Ouster OS2-128, Innoviz's InnovizTwo and Innoviz 360, and Baraja Spectrum HD25. One can note that in these sensors, substantially lower resolutions result from higher frame rates. Perception systems rely heavily on the resolution of point clouds, especially for identifying small objects and road segments. For this reason, a refresh rate of 10 Hz seems to offer very reasonable resolutions on the listed LiDARs without compromising heavily on frame rate. And the data in the table does suggest that a refresh rate of 10 Hz is widely supported. Hereby, a frame rate of 10 Hz is the reference value for the perception algorithms explored throughout this work.

| LiDAR Sensor                   | <b>Refresh Rate</b> | Angular Resolution (H x V) | Market Release |

|--------------------------------|---------------------|----------------------------|----------------|

|                                | (Hz)                |                            |                |

| Velodyne HDL-64E <b>[59]</b>   | 5 - 20              | (0.08°- 0.35°) x 0.4°      | 2007           |

| Velodyne VLS-128 <b>[60]</b>   | 5 - 20              | (0.08° - 0.35°) x 0.11°    | 2017           |

| lbeo Lux <b>[61]</b>           | 25                  | 0.25° x 0.8°               | 2018           |

| Ouster 0S2-128 <b>[62]</b>     | 10 or 20            | (0.7° - 0.18°) x 0.18°     | 2020           |

| Continental HFL110 [63]        | 25                  | 0.94° x 0.94°              | 2021           |

| Luminar Iris [64]              | 1 - 30              | 0.05° x 0.05° *            | 2022           |

| Innoviz InnovizTwo <b>[65]</b> | 10/15/20            | 0.05° x 0.05° *            | 2022           |

| Innoviz 360 <b>[66]</b>        | 0.5 - 25            | 0.05° x 0.05° *            | 2022 (Q4)      |

Table 1. Market released and future automotive LiDAR sensors (references in the table).

| Baraja Spectrum HD25 <b>[67]</b> | 4 - 30 | 0.04° x 0.0125° * | > 2022  |  |

|----------------------------------|--------|-------------------|---------|--|

| Continental HRL131[68]           | 10     | 0.05° x 0.075°    | 2024 ** |  |

| Valeo Scala GEN1 <b>[69]</b>     | 25     | 0.25° x 0.8°      | 2024 ** |  |

\*Highest possible resolutions

\*\*Expected

# 3.2 DEEP LEARNING HARDWARE

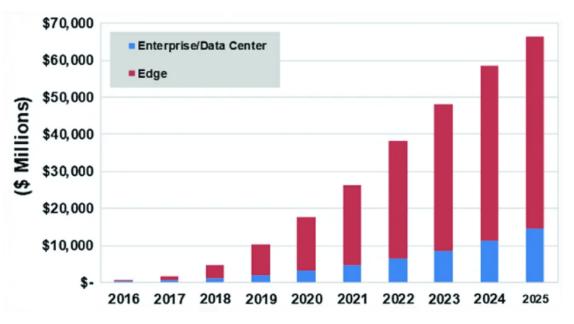

Deep learning models notoriously require lots of computation and memory during inference. With the limited energy consumption in the vehicle and the hardware limitations that it creates, it becomes natural to consider offloading some of the computation outside the vehicle through the network. However, due to network limitations in communication bandwidth, latency, and reliability, only offline tasks, usually consisting of offline model retraining and map generation, can be performed on the cloud [70]. This means that, concerning real-time perception, currently the best solution is to use the paradigm of edge computing which tries to bring the computation as close as possible to the data sources, and the sensors, effectively placing the hardware inside the vehicle. This trend is very visible in the data plot in Figure 12. Given the above-mentioned reasons, it is important to understand the different types of hardware available with especial attention to inference latency, memory, and energy consumption constraints.

Figure 12. Deep learning chip revenue. Retrieved from [71].

#### **3.2.1 CENTRAL PROCESSING UNITS**

CPUs are the most versatile of all the hardware since they can perform almost any type of computation and are unavoidably present in almost every system. This makes them the easiest and less timeconsuming hardware to deploy neural network applications on, as less effort is needed to support even the most novel and exotic neural network layers. Even the more common layers, which usually translate into vector to vector or matrix to matrix operations, are supported by low-level linear algebra routines in libraries such as *OpenBLAS* [72] and *Intel MKL* [73].

Most deep learning applications, even when accelerators are present, will inevitably use a CPU for receiving sensor data, data pre/post-processing, or control flow operations. This dependency makes CPUs a strong contender for deep learning inference since there is no latency bottleneck in transferring data like in a CPU-GPU application [74].

However, there is a tradeoff between versatility and resource efficiency. CPUs, being on one extreme of this spectrum are usually not optimized for any specific application. In some cases, where metrics such as energy consumption and inference latency are crucial, specialized hardware is the only solution.

#### **3.2.2 GRAPHICAL PROCESSING UNITS**

Although designed for graphical processing tasks, GPUs have become the standard hardware solution for training deep learning models since R. Raina, A. Madhavan, and A. Y. Ng proposed its usage over CPUs, remarkably reducing the training time of models [75]. Their highly parallel nature allows for the efficient computation of linear algebra operations, especially when transferring data in large batches [76], therefore reducing memory accesses outside the GPU and consequently optimizing GPU resource utilization. GPU programming has also become more accessible due to parallel programming tools such as *CUDA* [77] and *OpenCL* [78].

The introduction of tensor cores [79], specially designed for optimizing matrix operations and supporting various lower bit-width representations, further increased the applicability of GPUs for DNN training. Also, Nvidia reports a latency reduction in inference by utilizing tensor cores [80], which opens the usage of GPUs in latency-restricted applications such as ADAS. However, their high energy consumption is a hard limiting factor for their use in such systems. The study conducted by Gawron, H. J. et al. estimates a 3% increase in energy consumption between an autonomous and a non-autonomous vehicle with roughly half of the consumption due to the perception hardware (excluding sensors) [81]. This percentage can become more significant if the cooling of the hardware is considered as noted by

Lin. S. et al. [82]. To address these limitations, various efforts have been made to design and implement mobile GPUs with reduced power consumption, such as *Nvidia RTX* embedded GPU solutions [83] offering as low as 35W maximum power consumption.

### **3.2.3 APPLICATION-SPECIFIC INTEGRATED CIRCUITS**

Similarly to CPUs, GPUs are multi-purpose hardware solutions. This means that, despite the efforts made by graphics card manufacturers to add specialized hardware components such as tensor cores to their cards, GPUs are limited by the fact that they are a multi-purpose solution. Application-Specific Integrated Circuits (ASICs) are, as the name suggests, hardware that is specifically designed to optimize performance for a small set of applications. A well-known example of an ASIC widely used in deep learning is Tensor Processing Units (TPUs) specifically designed by Google for accelerating linear algebra computations [84]. TPUs excel when training models that are heavily dominated by matrix computations but tend to suffer from severe performance degradation when frequent branching or element-wise operations [84]. This inability to perform outside of the specific target application constraints is a typical pitfall of ASICs. Wang, Y. et al. benchmarked *Google's TPU v3* and an *Nvidia V100 GPU* in the training of DL models such as *ResNet-50* [27] and *SqueezeNet* [85], concluding that TPUs consistently provided a considerable speedup in DL model training over GPUs [86].

In the landscape of edge computing, where reduced inference latency and power consumption are the main constraints, there are several ASICs designed to optimize inference latency rather than training time, while keeping the energy consumption low. Examples are *Tesla's Full Self-Driving Chip* [87], and *Mobileye's EyeQ5* [88]. Although achieving fewer operations per second compared to the state-of-the-art general-purpose graphics cards, ASICs designed for edge computing are far more suited for automotive perception due to the high energy consumption of GPUs.

#### **3.2.4 FIELD PROGRAMMABLE GATE ARRAYS**

ASICs do not offer enough flexibility to keep up with the rapid evolution of deep learning models as the emergence of new types of layers poses a challenge to specialized hardware, especially since ASICs tend to have a high non-recurring engineering cost and time for design [89]. Field Programmable Gate Arrays (FPGAs) are integrated circuits that can be specifically optimized for a large subset of applications. Contrarily to ASICs, FPGAs are "field" reconfigurable meaning the hardware circuit can be reprogrammed to meet the requirements of the developer even when they change after manufacturing. This allows the