FACULTY OF INFORMATION TECHNOLOGY AND ELECTRICAL ENGINEERING DEGREE PROGRAMME IN ELECTRONICS AND COMMUNICATIONS ENGINEERING

# PARASITIC EXTRACTION OF A POWER MANAGEMENT INTEGRATED CIRCUIT PCB

Author Niko Alatalo

Supervisor Jan Nissinen

Second Examiner Timo Rahkonen

Technical Advisor Jari Niemelä

August 2023

**Alatalo N. (2023) Parasitic extraction of a power management integrated circuit PCB.** University of Oulu, Faculty of Information Technology and Electrical Engineering, Degree Programme in Electronics and Communications Engineering. Master's Thesis, 81 p.

#### **ABSTRACT**

In this master's thesis parasitic extraction of a power management integrated circuit was established and evaluated using Ansys Q3D. From PCB the S21 parameter was extracted between two nodes from output and input to efficiently show the parasitic properties of the PCB. Extraction was done over frequencies from 100 kHz to 100 MHz. This was done using multiple different settings for the extraction to find out the optimal settings in terms of accuracy and time to solution.

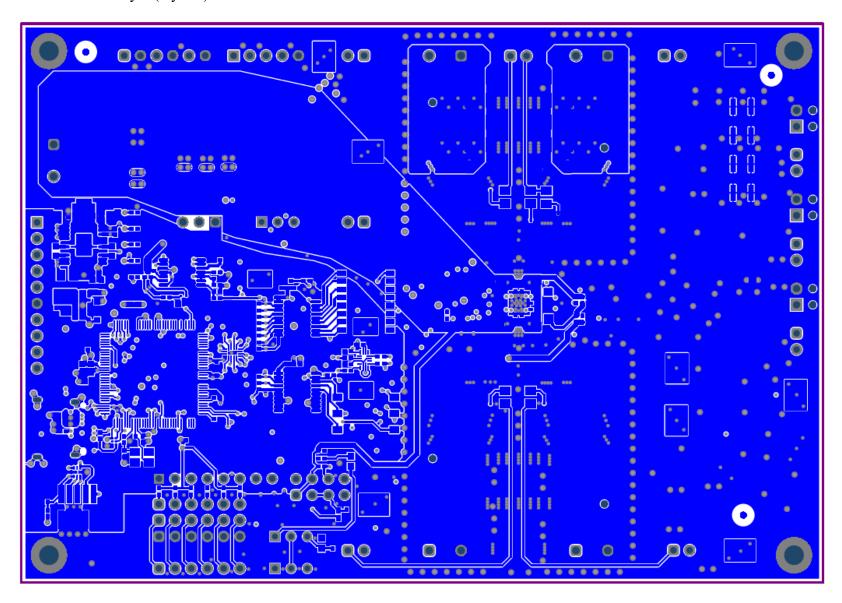

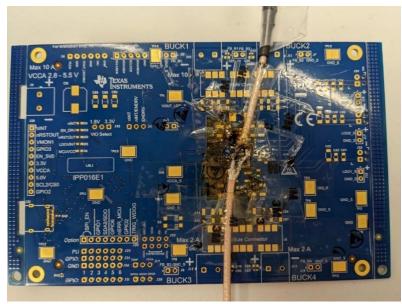

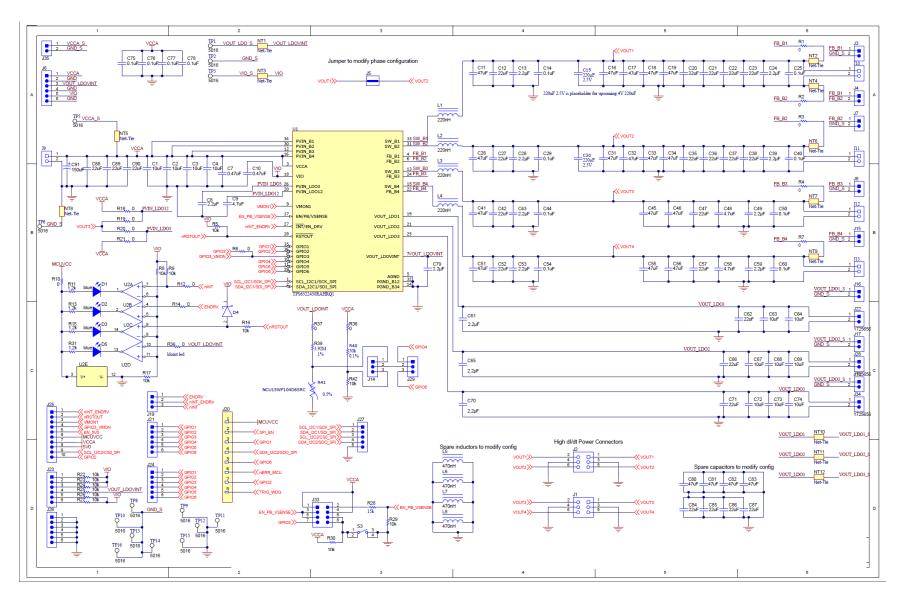

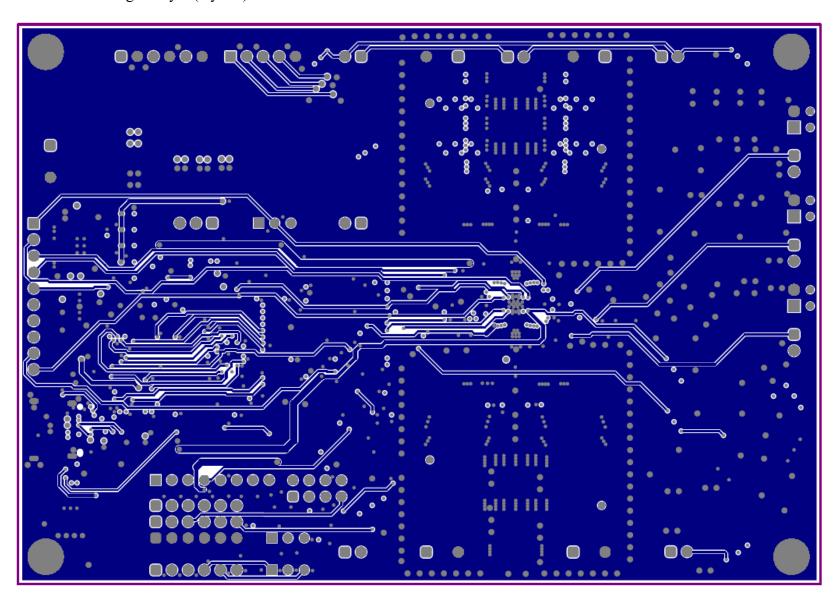

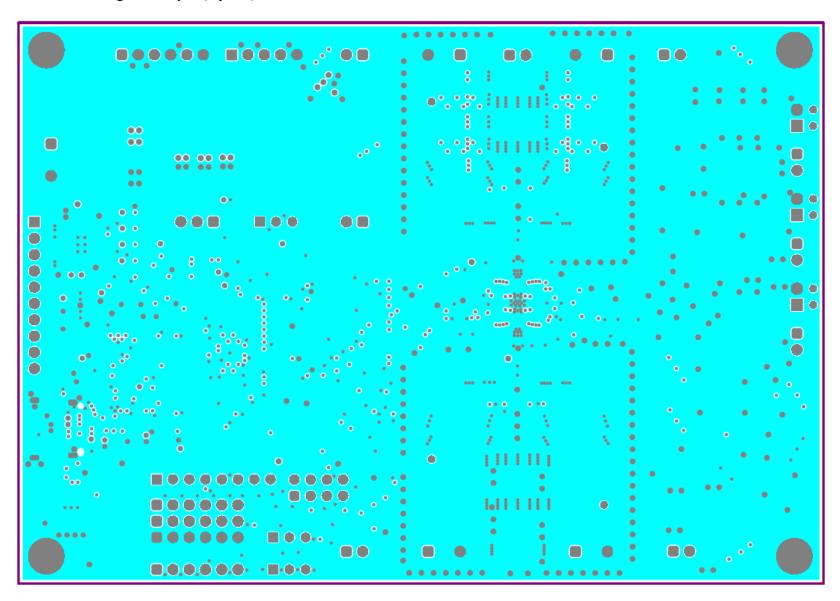

An evaluation module PCB was designed for the power management integrated circuit using Altium. In this design the best practices for PCB layout design were utilized to get the performance as good as possible. Some of the PCB design choices were evaluated with Ansys Q3D to make an informed decision of the better design choice.

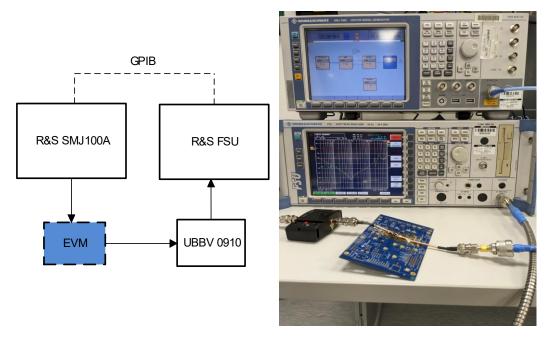

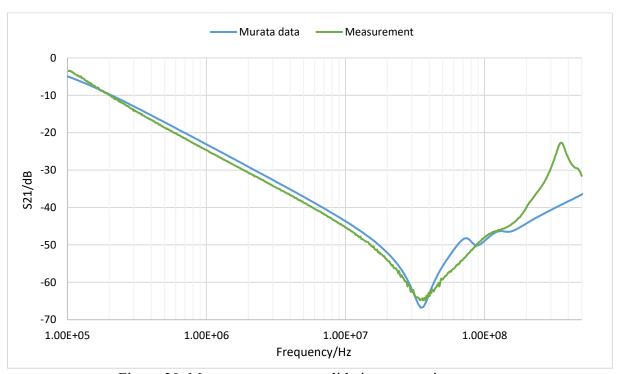

A measurement setup was established and validated by using a known component to ensure the setup is working as expected. The PCB was measured without components except the ones needed for the experiment. Measurements were taken with S<sub>21</sub> shunt-through method with spectrum analyser with built-in network option, external vector signal generator and external pre-amplifier to get more dynamic range.

The output and input were evaluated with and without a capacitor to get a broader understanding of the modelling accuracy. A case with two capacitors was tested. These models were compared with a measurement result to evaluate the accuracy of the tools and methods. It was noticed that with simple geometries the different extraction options do not significantly affect the extraction accuracy. At the same time, the time to solution varies greatly which leads to the use of the simpler extraction settings to save time. When comparing the simulation with measurement the best average error was 3.3 % and the worst 34.3 %. The simulations matched the measurements best when a capacitor was placed and worst with open termination with no components. The model accuracies obtained in this thesis reflect what has been seen in previous studies in terms of frequency range and deviation from measured results.

Key words: Parasitic extraction, power management, printed circuit board, impedance

Alatalo N. (2023) Parasiittisten ominaisuuksien ekstraktointi tehonhallinta piirilevyltä. Oulun yliopisto, tieto- ja sähkötekniikan tiedekunta, elektroniikan ja tietoliikennetekniikan tutkinto-ohjelma. Diplomityö, 81 p.

# TIIVISTELMÄ

Tässä diplomityössä parasiittisten ominaisuuksien ekstraktointityövaihe luotiin, sekä sen suorituskyky arvioitiin käyttäen Ansys Q3D ohjelmaa. Piirilevyltä ekstraktoitiin S21 parametri kahden solmun väliltä tulo- ja lähtöpuolelta käyttäen 100 kHz – 100 MHz taajuusaluetta. Tällä tavoin saatiin tehokkaasti esitettyä piirilevyn parasiittisten ominaisuuksien muodostama impedanssi. Tämä tehtiin käyttäen useita eri asetuksia, joita on saatavilla ohjelmistossa. Nämä asetukset vaikuttavat eri tavoilla ekstraktoinnin tarkkuuteen. Näitä tuloksia vertailemalla löydettiin tarkkuuden ja simulointiajan suhteen optimaaliset asetukset, joilla tehdä ekstraktointi.

Työtä varten suunniteltiin piirilevy tehonhallinta integroidulle piirille käyttäen Altium ohjelmaa. Tässä suunnittelussa käytettiin hyviä käytänteitä, jotta piirilevyn suorituskyvystä saataisiin mahdollisimman hyvä. Jotkin suunnitteluvalinnoista perustuvat Q3D:llä saatuihin tuloksiin, jotta voitiin valita useista vaihtoehdoista paras.

Mittauksia varten suunniteltiin ja toteutettiin mittausjärjestelmä, jonka toiminta varmennettiin mittaamalla tunnetun komponentin impedanssi ja vertaamalla sitä valmistajan antamaan dataan. Valmistetulta piirilevyltä mitattiin käyttäen vain niitä komponentteja, jotka olivat merkittäviä tutkimukselle. Mittaukset tehtiin käyttäen S21 shunt-through menetelmää käyttämällä spektrianalysaattoria, jossa on sisäänrakennettu verkkoanalysointioptio. Tämän kanssa käytettiin ulkoista vektorisignaaligeneraattoria ja ulkoista esivahvistinta, jotta saataisiin enemmän dynaamista aluetta.

Vertailuun valittiin piirin ulos- ja sisääntuloverkot kondensaattorilla ja ilman, jotta saataisiin laajempi käsitys mallinnuksen tarkkuudesta. Myös kahden kondensaattorin tapaus käsiteltiin. Näitä mallinnuksella saatuja tuloksia verrattiin mittaamalla saatuihin tuloksiin. Työssä huomattiin, että tässä sovelluksessa, jossa on yksinkertaisia geometrioita, eri ekstraktointi vaihtoehdot eivät vaikuttaneet tarkkuuteen huomattavasti. Ekstraktointiin kulunut aika vaihteli huomattavasti joidenkin vaihtoehtojen välillä, jonka takia valittiin yksinkertaisempi mallinnustapa, jotta säästettäisiin aikaa. Verrattaessa simuloituja ja mitattuja tuloksia, huomattiin että paras keskiarvoinen virhe oli 3,3 % ja huonoin 34,3 %. Simuloinnit vastasivat mittauksia parhaiten, kun tarkasteltiin tapauksia, joissa oli käytössä yksi kondensaattori ja huonoin, kun käytettiin avointa terminointia. Tässä työssä saadut tulokset vastaavat hyvin aikaisemmissa tutkimuksissa saatuja tuloksia sekä taajuusalueen puolesta, että eron mittauksen ja simuloinnin välillä.

Avainsanat: Parasiittiset ominaisuudet, ekstraktointi, tehonhallinta, piirilevy, impedanssi

# TABLE OF CONTENTS

| ABS  | STRA  | ACT                                         |    |

|------|-------|---------------------------------------------|----|

| TIIV | /ISTE | ELMÄ                                        |    |

| TAE  | BLE C | OF CONTENTS                                 |    |

| FOR  | REWO  | ORD                                         |    |

| LIST | ΓOF.  | ABBREVIATIONS AND SYMBOLS                   |    |

| 1    | INT   | FRODUCTION                                  | 9  |

| 2    | PAI   | RASITIC PROPERTIES OF PRINTED CIRCUIT BOARD | 10 |

|      | 2.1   | Resistance in conductors                    | 10 |

|      | 2.2   | Capacitance of a trace                      | 11 |

|      | 2.3   | Inductance in conductors                    | 14 |

|      | 2.4   | Impedance profile                           | 18 |

|      | 2.5   | Signal integrity                            | 19 |

|      | 2.6   | PCB layout guidelines                       | 20 |

| 3    | TOO   | OLS FOR PARASITIC EXTRACTION                | 23 |

|      | 3.1   | S-parameters and RLCG model                 | 23 |

|      | 3.2   | Ansys HFSS and Q3D                          | 25 |

|      |       | 3.2.1 HFSS and Q3D differences              | 25 |

|      |       | 3.2.2 HFSS and Q3D accuracy                 | 27 |

| 4    | PCE   | B DESIGN                                    | 29 |

|      | 4.1   | Evaluation module outputs                   | 29 |

|      | 4.2   | Evaluation module input and internal LDO    | 31 |

| 5    | SIM   | MULATION AND MEASUREMENT SETUPS             | 35 |

|      | 5.1   | Points of interest for extraction           | 35 |

|      | 5.2   | Measurement setup                           | 42 |

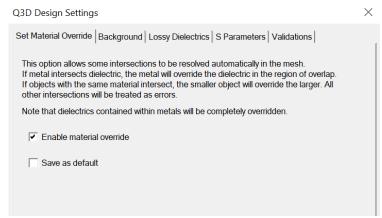

|      | 5.3   | Simulation setup                            | 45 |

|      | 5.4   | Simulation variations                       | 48 |

| 6    | RES   | SULTS                                       | 53 |

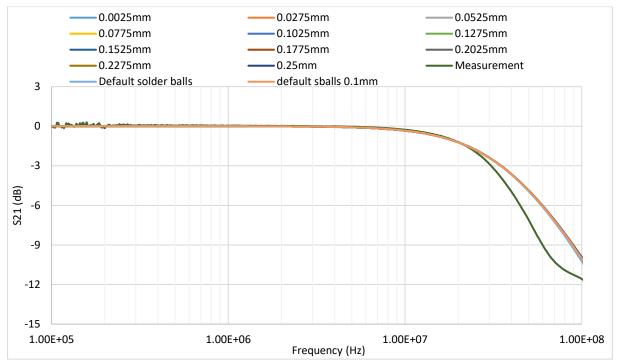

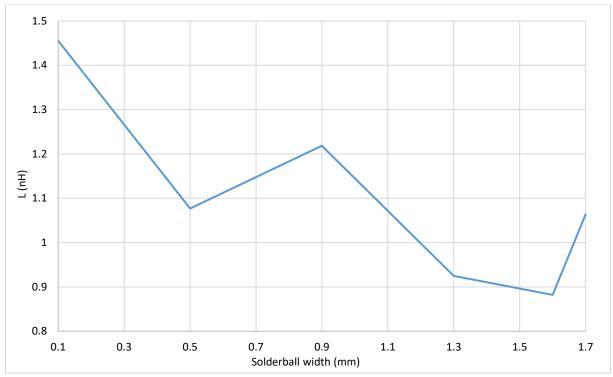

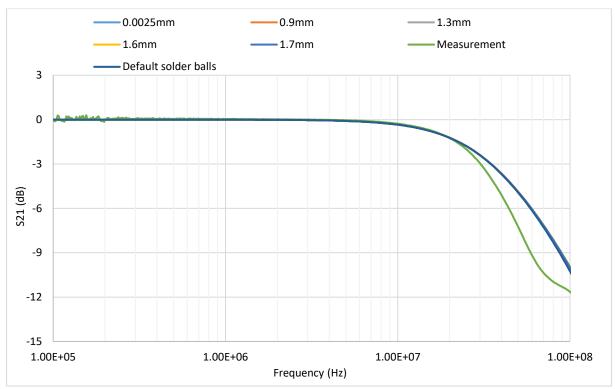

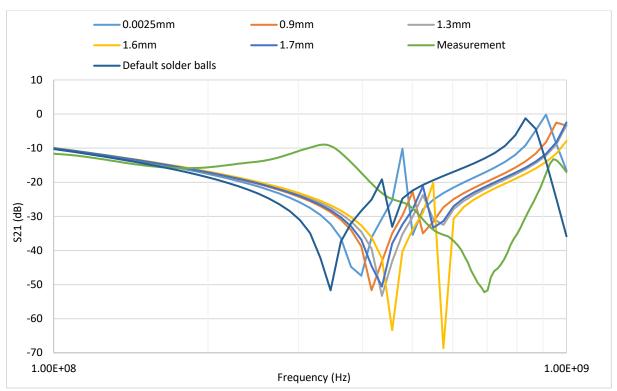

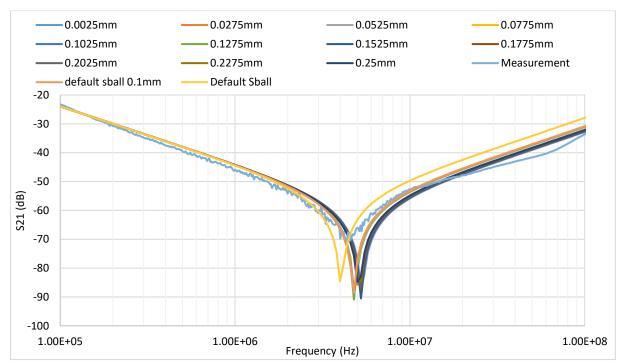

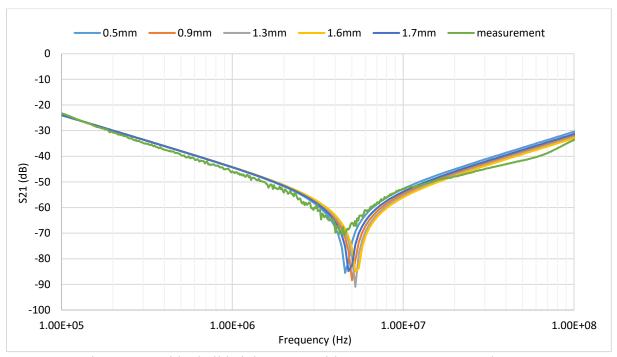

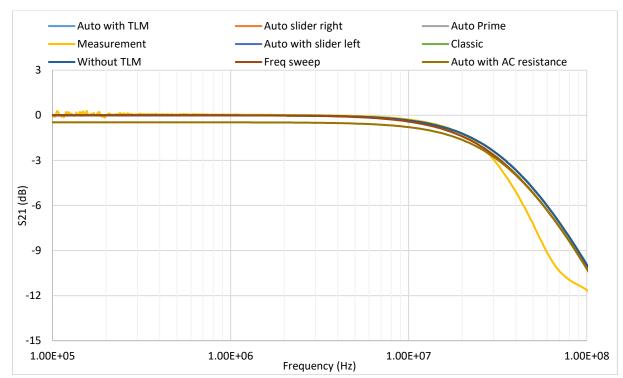

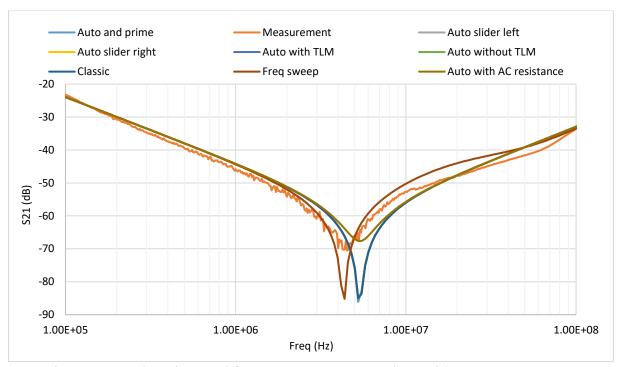

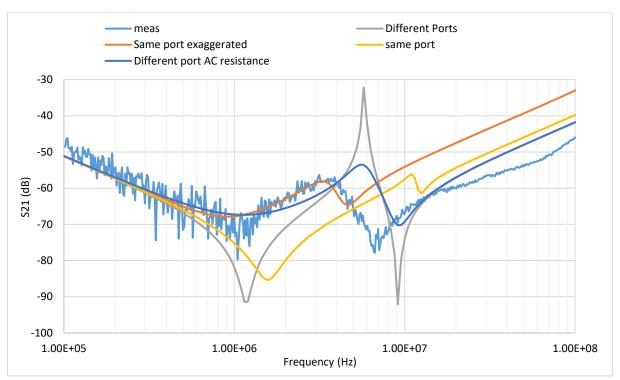

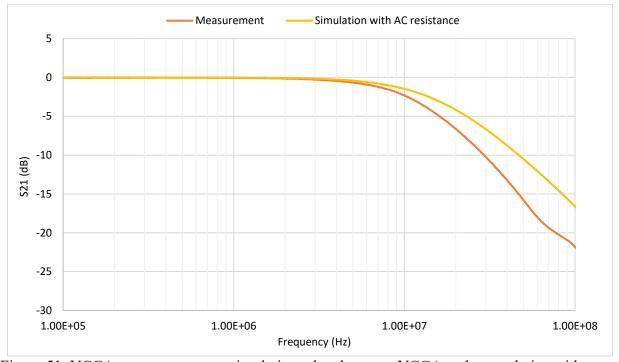

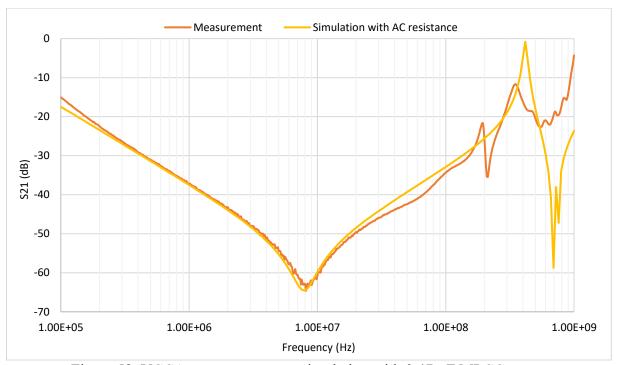

|      | 6.1   | Solder balls and mesh options               | 53 |

|      | 6.2   | Vout with two capacitors and VCCA loop      | 62 |

| 7    | DIS   | SCUSSION                                    | 66 |

| 8    | SUN   | MMARY                                       | 68 |

| 9    | REF   | FERENCES                                    | 69 |

10

#### **FOREWORD**

This master's thesis was done for Texas Instruments in Oulu to establish and study parasitic extraction and how it should be conducted in the most efficient way. Thesis examiners from university of Oulu were Jan Nissinen and Timo Rahkonen. I would like to thank them for guiding me through the thesis process and giving me advice on how to write the thesis.

This thesis was done on an area that has been utilised, but not thoroughly studied, on PMIC PCB design at Texas Instruments. This created problems and many hours were spent on determining how all the different phases should be done both on simulation and measurement sides. This area also being relatively new to me has taught me a lot of new things about PCB layout design, parasitic extraction, and measurements.

From Texas Instruments my supervisor was Jari Niemelä and I got a lot of help from Samuli Piispanen and Jussi Särkkä. I would like to thank them for the weekly meetings and all the extra advice and support they have given me these past six months on Ansys, PCB design, thesis feedback and all the help on the details of the thesis. I would also like to thank Sini Pesonen for helping me with my written English.

Last but certainly not least, I would like to thank my girlfriend for bearing with my days of studying and writing this thesis. Many weekends and holidays were spent working on the thesis one way or another, but she always stood by me even during the not-so-good parts of the process.

Oulu, August 12th, 2023

Niko Alatalo

## LIST OF ABBREVIATIONS AND SYMBOLS

3D 3- dimensional

3D-PEEC 3- dimensional partial element equivalent circuit

AC alternating current

AEDT Ansys electronics desktop

CG capacitance and conductance solver in electromagnetic solvers

CPU central processing unit

DC direct current

DUT device under test

ECM embedded capacitance material

EMC electromagnetic compatibility

EMI electromagnetic interference

ESL equivalent series inductance

EVC early voltage compensation

EVM evaluation module FEM finite element method

GM gain margin

GPIB general purpose interface bus

HF high frequency IC integrated circuit

LC circuit consisting of inductor and capacitor

LDO low dropout (regulator)

LF low frequency LSF load sharing facility

LVDS low voltage differential signalling MLCC multilayer ceramic capacitor

MoM method of moments

MOSFET metal-oxide-semiconductor field-effect transistor

PC personal computer

PCB printed circuit board

PDN power delivery network

PM phase margin

PMIC power management integrated circuit

POL point of load RF radio frequencies

RL resistance and inductance solver in electromagnetic solvers circuit with resistance, inductance, capacitance, and conductance

SMT surface-mount technology

SMPS switching mode power supply

SRF series resonance frequency

TLM transmission line model

TTL transistor-transistor logic

VCCA positive supply voltage

A cross-sectional area of a conductor

a waves flowing into a port in S-parameter measurement

$A_{\rm ol}$  overlapping area of conductors

**B** magnetic flux density

**b** waves flowing from a port in S-parameter measurement

C capacitance

$C_0$  capacitance between conductors with air as insulator

d length of a trace f frequency

$f_{RF}$  resonance frequency H magnetic field intensity

*h* separation between conductors

I current

i imaginary number  $I_I$  current in conductor 1

J current density

L inductance

$L_1$  inductance of a signal path  $L_2$  inductance of a return path

$L_{Loop}$  loop inductance

$M_{12}$  mutual inductance between traces 1 and 2  $M_{21}$  mutual inductance between traces 2 and 1

n number of squares in a trace Q charge between conductors

*R* resistance

$R_{AC}$  resistance at AC  $R_{DC}$  resistance at DC  $R_{L}$  resistance per length  $R_{sq}$  sheet resistance S S-parameter matrix  $S_{II}$  reflection coefficient

$S_{12}$  forward transmission coefficient  $S_{21}$  reverse transmission coefficient

$S_{21,ser}$   $S_{21}$  obtained by series-through measurement  $S_{21,shunt}$   $S_{21}$  obtained by shunt-through measurement

$S_{22}$  output reflection coefficient  $S_l$  area of an inductance loop

t thickness of a trace

V voltage

w width of a trace

x x-axis of a coordinate systemy y-axis of a coordinate system

**Z** Z-parameter matrix

z z-axis of a coordinate system

$Z_0$  reference impedance  $Z_{11}$  self-impedance of port 1

$Z_{12}$  transimpedance from port 2 to port 1  $Z_{21}$  transimpedance from port 1 to port 2

$Z_{22}$  self-impedance of port 2  $Z_{C}$  impedance of capacitor

$Z_{DUT}$  impedance of a device under test

$Z_{DUT,ser-thru}$  impedance of DUT obtained by series-through method  $Z_{DUT,shunt-thru}$  impedance of DUT obtained by shunt-through method

$Z_{\text{ind}}$  impedance of inductor

$Z_L$  impedance of port two in series-through or shunt-through measurement impedance of port one in series-through or shunt-through measurement

$\nabla$  nabla operator  $\delta$  skin depth

$\begin{array}{ll} \delta_{copper} & skin \ depth \ of \ copper \\ \epsilon_0 & permittivity \ of \ free \ space \\ \epsilon_r & relative \ dielectric \ constant \end{array}$

μ permeability

$\mu_0$  permeability of free space

ρ bulk resistivityσ conductivity

Φ flux of magnetic field

$\Phi_2$  magnetic flux around conductor 2

ω angular frequency

#### 1 INTRODUCTION

A PCB (Printed Circuit Board) has a significant effect on the performance of an entire system. This is why the layout designer must know how to design a well performing PCB. Due to the ever-increasing complexity of electronic systems, it can be an overwhelming task to design a PCB by only utilising the key layout design rules. This is why a computer software should be used in the design process to evaluate the performance. Software like Ansys Q3D and Siemens HyperLynx have been developed to help the designer evaluate properties such as signal integrity, power integrity and parasitic properties. Signal integrity and power integrity problems arise from the parasitic properties, and this is why by examining only the parasitic properties of the PCB, the designer can tell if the design needs improvements.

Extracting the parasitic properties is not a simple task to do properly, and the user must know which software to use and how to use it properly for the use case. The user must know the correct extraction frequencies, which properties are extracted, how many cells the equivalent circuit must contain and the accuracy of used mesh. Some software is dedicated to lower frequencies and some to higher frequencies, some are optimized for speed and some for accuracy. The user cannot increase the accuracy blindly because the time to solution increases fast and can reach calculation times up to several days.

Ansys Q3D is a part of Ansys Electronics Desktop software which specialises in fast low frequency parasitic extraction. It reduces the calculation times by not calculating full Maxwells equations but by approximating for example that the magnetic and electric fields do not change over the problem area. From the calculated results an equivalent circuit can be exported which can be used in further simulations.

In this study Ansys Q3D is used to extract parasitic properties of a power management integrated circuit evaluation module PCB, which are then compared with measurement results. From the PCB the chosen points of interest are output and input loops due to their high importance in this kind of system. Inductance in the output loop can make the device unstable and in the input loop it can cause voltage fluctuations due to the switching operation. The comparison between different extraction options is done to evaluate different extraction options and their effect on accuracy and time to solution. Comparing the simulation results with measured values shows the accuracy of the simulations.

Chapter 2 covers the basics of parasitic properties in a PCB and their effects on performance. This includes how inductance causes ground bounce and rail-collapse, capacitance causes cross talk, and resistance causes voltage drop and how it is related to frequency. It also covers how these properties contribute to the impedance profile and how these unwanted effects can be mitigated. Also, brief introduction to signal integrity is given. Chapter 3 focuses on two different extraction programs by Ansys and how they can be utilised. In chapter 4 the designed PCB is introduced and some of the design decisions are explained. Chapter 5 introduces the used simulation and measurement setups and how they were used. Chapter 6 shows the simulated results compared with the measurements after which is the chapter 7 where a broader look is given to this work and the accomplishments of this study. Finally in chapter 8 a summary of the thesis is given.

#### 2 PARASITIC PROPERTIES OF PRINTED CIRCUIT BOARD

In modern systems design designer does not only need to worry about the qualities of all the components but also take the printed circuit board into consideration as it was a component in the system. The PCB can be thought to consist of resistance, capacitance, and inductance. Good power plane design can be the difference between device achieving and not achieving the specification [1].

The only reason for signal and power integrity problems are the three basic properties of any conductor which are resistance, capacitance, and inductance. If a conductor was ideal, none of these signal and power integrity problems would exist. Ability to optimize PCB design comes down to understanding these electrical properties and their effects, as well as how to mitigate them. [2]

If a sensitive chip and its accompanying system is designed considering only signal integrity, the signals themselves might be clean. However, when there are problems in for example the power rail, this will affect the signal one way or another. Also, if there is a disturbance in the reference voltage, the chip might get false readings. [2]

#### 2.1 Resistance in conductors

Resistance is the conductor's ability to resist the flow of current at DC (Direct Current) as well as to dissipate excess energy as heat. Resistance depends on the physical geometry of the trace as well as its material property named bulk resistivity. Bulk resistivity is the materials intrinsic property to resist current flow, which means it is only dependent on the material itself and not on the amount of it. Copper is used in conductors, since it has low bulk resistivity of 1.58  $\mu\Omega\cdot\text{cm}$ . [2]

The resistance of a conductor can be manipulated by changing its geometry. Current flows more freely in a wide and thick conductor, hence resistance can be defined by resistance per length and sheet resistance if the conductor's cross section is uniform in the trace. Both are dependent on the bulk resistivity of the material used. Resistance per length  $R_{\rm L}$  is directly proportional to the length of the trace by

$$R_{\rm L} = \frac{R}{d} = \frac{\rho}{A'} \tag{1}$$

where R is resistance, d is conductor length,  $\rho$  is bulk resistivity and A is the cross-section area of the trace. [2]

Sheet resistance is determined by the thickness of the conductor and the material used. Resistance is directly proportional to the length of the conductor and inversely proportional to the width of the conductor. If both dimensions are changed the same amount, the resistance will not change. Thus, every square of the same conductor having uniform cross section will have the same resistance  $R_{\rm sq}$  of

$$R_{\rm sq} = \frac{\rho}{t'},\tag{2}$$

where t is the thickness of the trace. In the case of sheet resistance, it is assumed that the current flows uniformly from one side to the opposite side of the trace. For typical thickness of 1-ounce copper sheet, or about 35 microns, the sheet resistance is  $0.5 \text{ m}\Omega$  per square. [2]

Every trace can be made of squares and since every square in a uniform trace have the same resistance, the resistance at DC  $R_{\rm DC}$ , where the entire trace has uniform cross-sectional area, can be given by

$$R_{\rm DC} = \frac{\rho}{t} \cdot \frac{d}{w} = R_{\rm sq} \cdot n,\tag{3}$$

where w is width of the trace and n is number of squares in the trace. From equation (3) it can be concluded that if the length and width of a trace are the same, the resistance of the trace is the same as sheet resistance. Thus, the only parameters affecting the resistance are the bulk resistivity and thickness of the trace. If the length is twice as large as the width, the resistance of the trace is two times the sheet resistance. [2]

At higher frequencies the current starts to flow closer to the surface of the conductor thus not utilizing the whole cross-sectional area of the conductor [3]. This is called the skin effect. Because of this effect, the resistance of a conductor is frequency dependent [3]. Skin depth is the maximum depth at which the current flows and therefore determines the cross-sectional area which is used by the current. Skin depth  $\delta$  can be approximated with

$$\delta = \sqrt{\frac{2}{\omega\mu\sigma}},\tag{4}$$

where  $\omega$  is angular frequency,  $\mu$  is the conductor's permeability and  $\sigma$  is the conductor's conductivity [3]. With the skin depth the AC (Alternating Current) resistance  $R_{AC}$  for a rectangular conductor can be calculated by using equation

$$R_{\rm AC} = \frac{\rho}{2(w+t)\delta} \tag{5}$$

where the skin depth for copper can be calculated by using equation

$$\delta_{\text{copper}} = \frac{66 \cdot 10^{-6}}{\sqrt{f}},\tag{6}$$

where f is the frequency in megahertz [4].

These principles can be used to estimate and optimize the resistance of the trace. It must be taken into consideration that these equations assume that the current is distributed equally in the trace. If the source or sink point of the trace is narrower than the trace, the current will not flow uniformly and the resistance the current sees is higher than expected.

#### 2.2 Capacitance of a trace

Capacitance is a measure of how efficiently two conductors can store charge between them at the cost of voltage [5]. Capacitance is only dependent on the geometric attributes of the two conductors and the dielectric material between them [2]. Ideally capacitance does not change

with extrinsic properties such as voltage [2]. The Higher the charge stored for fixed voltage, the higher the capacitance. Thus, capacitance C can be expressed as

$$C = \frac{Q}{V'},\tag{7}$$

where Q is the stored charge and V is voltage between the conductors. Equation (7) shows that if a lower voltage is applied to a capacitor its capacitance does not change but the charge stored decreases [2]. The capacitance of a capacitor ideally cannot be changed by applying different voltage across it [2]. The exception to voltage dependency are high dielectric constant capacitors which are highly susceptible to the so-called DC bias effect [6]. With these capacitors having dielectric constant over 200, their capacitance decreases with higher DC bias [6]. Since the commonly used FR4 in PCBs has dielectric constant of around four, it is not susceptible to this effect in a meaningful manner. Capacitance can also be expressed with the overlapping area of the plates, separation between plates and dielectric constant by

$$C = \varepsilon_0 \varepsilon_r \frac{A_{\text{ol}}}{h},\tag{8}$$

where  $\varepsilon_0$  is the permittivity of free space,  $\varepsilon_r$  is the permittivity of medium between plates,  $A_{ol}$  is the overlapping area of the conductors and h is separation between the plates [2]. This is more useful when optimizing PCB layout.

Dielectric constant is intrinsic property of the insulator in a capacitor. Relative dielectric constant  $\varepsilon_r$  is defined as the relation between capacitance with some dielectric and capacitance with air as the dielectric between the plates with

$$\varepsilon_r = \frac{C}{C_0},\tag{9}$$

where  $C_0$  is capacitance when the insulator between two plates is air. The dielectric constant is a property which tells how well insulating material holds an electric field. The dielectric constant can change up to 10 % with frequency. Some change can also be seen with change in temperature as with water it can change from about 90 to about 55 when temperature rises from 20 degrees to 100 degrees [7]. For FR4 the effect of temperature is minor [8]. [2]

Effective dielectric constant is the dielectric constant seen by the electric fields. If a conductor is placed on the top side of a printed circuit board, some of the electric field lines will be surrounded by the surrounding medium and some by the PCB dielectric material. This causes the dielectric constant in this capacitor to be somewhere between the dielectric constant of the surrounding material and the dielectric material. This leads to two traces having different capacitance between them depending on if one of the traces is in the inside layers of a multilayer PCB or at the surface, assuming the other trace stays in the same layer in both situations and the distance between the traces stays the same. [2]

Capacitance between two traces can cause cross talk which can be divided into common impedance and electromagnetic field coupling. Common impedance coupling is the cause of using a common return path for different signals. Electromagnetic field coupling occurs mainly at high frequencies and can be divided into capacitive and inductive coupling [9]. Two traces close together will have some capacitance between them but is mainly of concern when they

are on different layers and overlap. The capacitance between two traces can be calculated by equation (8). The closer they are together and the greater the overlap is, the higher capacitance between them. Capacitive coupling is more likely to occur at high frequencies due to impedance of a capacitor  $Z_{\mathbb{C}}$  being lower according to

$$Z_C = \frac{1}{i\omega C'} \tag{10}$$

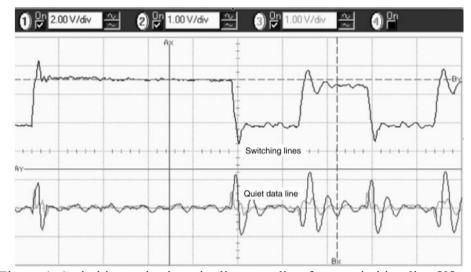

where i is the imaginary number,  $\omega$  is the angular frequency and C is the capacitance. An example of switching noise is shown in Figure 1. [2]

Figure 1. Switching noise in quiet line coupling from switching line [2].

Eliminating cross talk is an impossible task but with careful design it can be mitigated. These design considerations include reducing the length of signal traces and keeping them as wide apart as possible, by reducing dielectric thickness between signal layer and reference plane and inserting a ground trace between signal lines. [9]

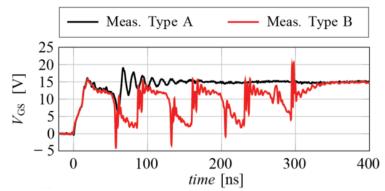

Capacitance between a switching node and a sensitive feedback trace can cause unwanted effects. In SMPS (Switching Mode Power Supply) circuit capacitance between the switching node and the input of the gate driver can cause false turn-off triggering of the power transistor [10]. Figure 2 shows the false turn off behaviour due to coupling between the output switching node and the gate driver input. This happens because a high enough voltage spike is coupled to gate driver input which causes the low side driver output to go low. Thus, the gate-source voltage goes low and turns off the low side power MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor) device as is shown in Figure 2 measurement type B and measurement type A would be the correct behaviour. This event is called a false turn-off event. This capacitance can be lowered for example by changing the layer stack up of the PCB by having the switching node of the transistor farther away from the control signal trace [10]. Capacitive coupling between a switching node and a feedback line in a power management integrated circuit weakens the performance due to false readings at the feedback input.

Figure 2. False turn-off triggering of power transistor due to parasitic capacitance [10].

Parasitic capacitance of a PCB can also be used to make capacitors for high frequency signals. The use of ECM (Embedded Capacitance Material) has been studied for use in power supplies and it was shown that capacitance of up to 10 nF/cm<sup>2</sup> can be created. According to equation (8) the capacitance is directly proportional to the dielectric constant of the dielectric material. FR4 has a dielectric constant of four and in the study the highest used dielectric constant was 2600 for ferroelectric Y5V. MC12TM, which was of interest in this study, has a dielectric constant of 10. These have capacitances per square centimetre of 6 pF and 9.5 nF respectively. The use case for ECM is for example filtering EMI (Electromagnetic Interference) or lowering the impedance of the PDN (Power Delivery Network) [11]. When comparing the use of FR4 and MC12TM ECM between the power and ground planes for minimizing the PDN impedance, it decreased the peak impedance from about 3  $\Omega$  to approximately 0.5  $\Omega$  in the frequency range from 300 MHz to 700 MHz. Also, the overall impedance over 300 MHz was lowered significantly [11]. This also reduced the simultaneous switching noise and jitter by 38.5 % and 53.9 % respectively [11]. The use of ECM can also lead to low profile converters, or the space saved can be used to populate other components. From the cost point of view embedded capacitance is no better than typical surface mount capacitors. [12]

#### 2.3 Inductance in conductors

Inductance is conductor's efficiency to create magnetic field lines per amount of current. It is an intrinsic property of a conductor and is only affected by the geometry of the conductor. In simple terms inductance L can be defined as the number of magnetic field lines generated by one amp of current flowing in the conductor as

$$L = \frac{\Phi}{I'} \tag{11}$$

where  $\Phi$  is the flux of magnetic field lines around the conductor in Webers and I is the current flowing through the conductor. While the current does not change the inductance of the conductor it does change the amount of field line rings around it and the ratio of those is the inductance. [5]

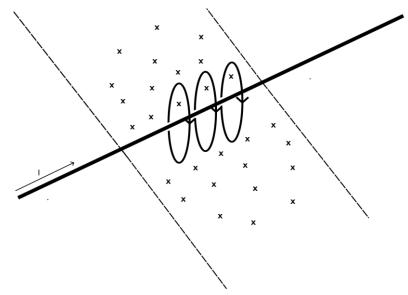

A current flowing through a conductor creates magnetic field lines around it which appear to have a direction of rotation determined by the right-hand rule. The number of magnetic field lines, also called the magnetic flux, can be counted at any point around the conductor as shown in Figure 3. [5]

Figure 3. Magnetic flux of a conductor.

The Denser the magnetic field lines are, the higher the magnetic flux density and the higher the magnetic flux around the conductor. Magnetic flux density B can be written as

$$\mathbf{B} = \mu_0 \mathbf{H},\tag{12}$$

where  $\mu_0$  is the permeability of free space and H is the density of magnetic field as a vector. Magnetic field density is measured in amperes per meter. The magnetic field density H is related to the current density J by

$$J = \nabla \times H, \tag{13}$$

where the  $\nabla$ -operator is given by

$$\nabla = \left(\frac{\partial}{\partial x}, \frac{\partial}{\partial y}, \frac{\partial}{\partial z}\right),\tag{14}$$

where x, y and z are the axes of the system. Magnetic flux  $\Phi$  can then be expressed as the line integral of the magnetic flux density by

$$\Phi = \int_{\mathcal{S}} \mathbf{B} \cdot dS_l, \tag{15}$$

where B is the magnetic field intensity vector and  $S_l$  is the area that the loop surrounds. [13] Inductance can be divided into partial and loop inductance. Loop inductance is what is always measured since measuring inductance must always include a closed loop where current can flow. Loop inductance consists of the self-inductance of that loop's sections and the mutual inductances between those sections. [5]

Partial inductance is defined like any other inductance as the efficiency to create magnetic field lines per one amp of current [5]. Loop inductance can be fully defined by only using the partial inductances of the loop's sections. Instead of focusing on the whole loop at once, which can be problematic for modelling the circuit, the magnetic field line rings produced by the current flowing in an isolated section are evaluated [14].

The partial inductances in a loop have self- and mutual inductance. Self-inductance is the inductance determined by field lines created by the current flowing in that specific section. To specify self-inductance even further, it can be divided into partial self-inductance and loop self-inductance. Partial self-inductance is the self-inductance in a section of a loop and loop self-inductance is the self-inductance of the entire current loop. [5]

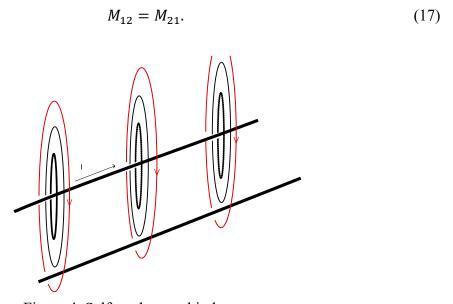

Mutual inductance is the part of the inductance which is created by another section in that current loop [5]. Mutual inductance  $M_{12}$  is therefore defined as the number of field lines around a conductor created by one amp of current in another conductor by

$$M_{12} = \frac{\Phi_2}{I_1},\tag{16}$$

where  $\Phi_2$  is the magnetic flux around the second conductor and  $I_1$  is current through the first conductor [14]. Self- and mutual inductance is shown in Figure 4 by the black and red lines, respectively. The mutual inductance of two conductors is the same either way, which can be written as

Figure 4. Self- and mutual inductance.

As with self-inductance, also mutual inductance can be divided into partial mutual inductance and loop mutual inductance. These describe how either sections of a loop or separate loops interact with each other. [5]

Mutual inductance is affected by the length of the two conductors and the distance between those conductors. Mutual inductance is directly proportional to the length of the conductors and the separation between them, so the closer the conductors are, the higher mutual inductance is. [5]

Loop inductance is determined by self-inductances and mutual inductances in that loop [5]. In Figure 4, if there was a current flowing in the lower conductor from right to left, the magnetic field lines would be in the opposite direction than the shown lines. This is often the situation with signal line and its return path. Because the field lines oppose each other, they are subtracted. We get the definition for loop inductance  $L_{\text{Loop}}$  as

$$L_{\text{Loop}} = L_1 + L_2 - 2M_{12},\tag{18}$$

where  $L_1$  is the inductance of the signal path,  $L_2$  is the inductance of the return path and  $M_{12}$  is the mutual inductance of these conductors. Mutual inductance is multiplied by two because it appears twice in the loop, first from conductor one to conductor two and then from conductor two to conductor one. In terms of PCB design, this means that the signal and return paths should be placed as close to each other as possible to get high mutual inductance and thus low loop inductance. [5]

The impedance of an inductor  $Z_L$  increases with frequency according to

$$Z_{ind} = i\omega L, \tag{19}$$

where i is the imaginary number,  $\omega$  is angular frequency and L is inductance. According to equation (19), conductors attenuate higher frequency signals more than low frequency signals thus lowering the rise time of a signal. If the rise time exceeds the period of a bit, false triggering will occur. When comparing to signals, the length of the traces carrying these signals should be matched to avoid any skew between them. [2]

Rail collapse is another effect that arises from equation (19). Rail collapse occurs when the load increases rapidly and the transient interacts with the inductance in the power rail causing the voltage to drop. This voltage drop V can be calculated by

$$V = L \frac{dI}{dt'} \tag{20}$$

where dI/dt is the current change I in time t [2]. This is a problem in modern designs since the trend has been to lower supply voltage and to increase the current consumption with faster switching meaning the load transients are faster. This causes even the smallest of inductance to be a problem because higher currents are drawn with faster transient, but the voltage cannot drop much since even a small rail collapse is a big percentage of the supply voltage. Rail collapse can be prevented by lowering the inductance in the power rail, placing power and ground plane as close together as possible and as close to the surface as possible. Also using low inductance capacitors help. [2]

The effect of rail collapse can also be mitigated by careful design of the feedback for example of a PMIC (Power Management Integrated Circuit) or by increasing the supply voltage for the duration of the initial current transient. The feedback can be single ended or differential and both have their strengths. The strength of single ended feedback is the ability to maintain more solid power or ground plane where the negative feedback line would be routed. EVC (Early Voltage Compensation) can be used to anticipate the incoming current draw from the PMIC. This might be needed since the PMIC cannot increase the power output fast enough and the voltage will drop. This can be done by the microcontroller informing the PMIC of the incoming load increase so that the PMIC can increase the voltage for the initial current draw. The voltage

is adjusted back to the original value when the current transient has passed. By doing this when the rail collapses, it does not collapse under the specification but closer to the actual rail voltage. This can decrease the voltage drop at the load side. [15]

#### 2.4 Impedance profile

Impedance profile is the impedance of a trace over some frequency span. Impedance of a trace can be depicted as RLCG (Resistance, Inductance, Capacitance, Conductance) circuit which has series resistance and inductance and parallel capacitance and conductance. [5]

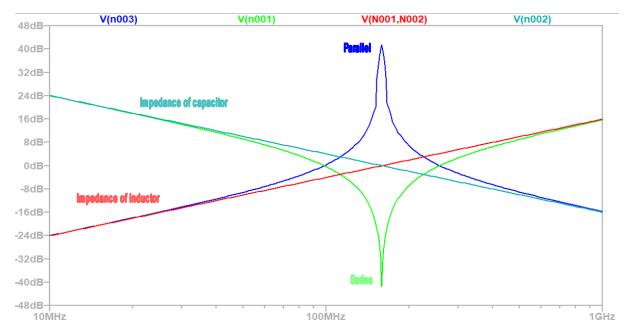

Since impedance of inductor gets larger with frequency and impedance of capacitor gets smaller, there is a resonance frequency where they are equal. The resonant frequency  $f_{RF}$  is given by

$$f_{\rm RF} = \frac{1}{2\pi} \frac{1}{\sqrt{LC'}} \tag{21}$$

where L is inductance and C is capacitance. This frequency is the same for both the series and parallel LC (Inductance, Capacitance) circuit [2]. Figure 5 shows the series and parallel resonance for 1 nF capacitor and 1 nH inductor and their impedances in series configuration. It can be seen the parallel and series resonance frequencies are the same if the values are the same.

Figure 5. Series and parallel resonance spike of 1 nH inductor and 1 nF capacitor.

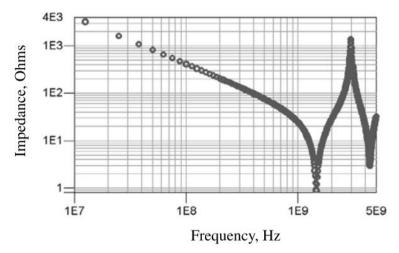

Signal plane and its return plane can interact as both series and parallel LC circuits depending on the entry and exit of the current. If the current is injected in a section with high inductance, the current interacts with inductance first and most of the capacitance is covered at the edge of plane pair. This acts as series LC circuit. If the current is injected at low inductance and high capacitance point of the plane pair and the current exits to high inductance point the structure acts as parallel LC circuit [5]. Impedance profile is formed by these interactions. As an example, an impedance profile of 1-inch-long transmission line with open termination is shown in Figure 6.

Figure 6. Measured impedance profile of 1-inch-long transmission line with open termination [2].

The understanding of impedance profile is important for designing great performing PCBs and thus better products. It should be understood what components the impedance includes and how they can be manipulated through different design choices.

#### 2.5 Signal integrity

Signal integrity considers many different effects and new ones are found all the time. Knowing all of these would be almost an impossible task. These problems can be divided into four categories which simplifies the problem. Understanding all four categories allows us to deal with any signal integrity problem without having to memorize all singular problems. These categories are signal quality of a net, cross talk between multiple nets, rail collapse in power delivery network, and electromagnetic interference from the entire system. [2]

A net consists of all of the copper that is in direct contact with each other and the signal return path. Any impedance discontinuities in this net will distort a signal, and with high enough distortion false triggering may occur. These discontinuities include for example trace cross section changes, layer change through via and connectors. The most common impedance discontinuity is at the end of the net when impedance changes from the impedance of the net to open circuit or the load impedance. When rise time of the signal decreases, or the frequency increases, the distortions caused by impedance discontinuities increase since the impedance of the inductor increases with frequency. Reflections cause under and overshoot and ringing and these can cause damage, reduce noise margin, and increase settling time which affects stability [9]. [2]

EMI is generated from all three types of noise mentioned earlier, so every design aspect lowering noise will lower EMI. Although, even if every other noise has been pushed to low enough levels, EMI can still be a problem causing the design not to pass regulations. For radiated electromagnetic interference to occur, it needs a source, a radiator, and a receiver. Often this can be high-speed data line near PCB border where there is a connector to another device. This type of EMI can be decreased using a ferrite choke around cables leaving the printed circuit board. Since modern telecommunication bands are in the gigahertz territory, the high-speed signals that reach these frequencies are a big problem. EMI is a bigger problem when higher frequencies are reached in new designs. [2]

Eliminating EMI is difficult when the design is already finalized, and it does not pass regulations. The only solutions are to try some workaround to reduce EMI or to redesign and test the whole device. Neither of these solutions is cheap, fast, or easy, so the device should be designed from the beginning with EMI in mind. A bypass capacitor can be used at DC input to reduce noise from the power line and a transient-voltage-suppression diode can be used to suppress transients in the power line. Power cables should be shielded twisted pairs. EMI filters can be enclosed in metallic enclosures to minimize radiating EMI and LC filters can be used to reduce switching noise. [16]

Electromagnetic interference, common-mode voltage bounce and crosstalk can be improved with LVDS (Low Voltage Differential Signalling). LVDS uses low-voltage swing of around 300 mV to minimize power dissipation [17]. Differential transmission mode helps with common-mode voltage bounce and crosstalk since if the same disturbance happens in both lines it is cancelled in the differential receiver [17]. Current mode transmission reduces noise in the communication [17]. LVDS has become one of the best solutions for chip-to-chip transmission and controlling optical communication [18], [19].

#### 2.6 PCB layout guidelines

These principles shown below can be used in PCB layout design using only a few simple rules. There are more guidelines and good practices but listing them all would be overwhelming. However, the following rules are a great starting point for layout design.

- Use as short as possible trace lengths to minimize inductance and resistance [2].

- Use wide traces to get larger cross-sectional area to minimize inductance and resistance [2].

- Keep distance between signal and return traces as small as possible to reduce loop inductance [2].

- Traces carrying current in the same direction should be kept as far away from each other as possible to minimize loop inductance [5].

- Capacitive coupling can be minimized by keeping traces as far from each other as possible [2].

- Power plane capacitance can be increased by bringing power and ground planes closer together. Effect of capacitance is negligible compared to inductance [5].

PCB design can be further improved by some more advanced design techniques such as making the PCB layer stack up symmetrical around the core, routing signals orthogonally on adjacent layers and interleaving the signal and return paths.

The impedance profile of a PCB can be influenced by considering the layer stack up order [20]. One scheme that can improve the performance of the PCB is making the stack up symmetrical respective to the core. An example of this can be seen in Table 1 where the core would be between SIG1 and SIG2 layers. This ensures that components on top and bottom layer can have similar current loops and thus similar loop inductances [21]. In this design the ground layers 2 and 5 are close to the surface which reduces inductance from vias. Also, by bringing power and ground layers closer together, the loop inductance can be minimized.

| - J           |        |  |  |

|---------------|--------|--|--|

| Layer number  | Domain |  |  |

| 1 (Top Layer) | POWER  |  |  |

| 2             | GND    |  |  |

| 3             | SIG1   |  |  |

| 4             | SIG2   |  |  |

| 5             | GND    |  |  |

| 6 (Bottom)    | POWER  |  |  |

Table 1. Symmetric layer stack up in PCB layout

Interleaved signal and return paths are another more advanced design technique to improve the loop inductance. A cross section of a PCB design with interleaved signal and return traces is shown in Figure 7 where layers one and three are for signal and layers two and four are return paths. The inductance L in the schematic is the parasitic inductance of the PCB. Interleaving these paths reduce the inductance by having more volume for the current to flow in, but more importantly by reducing the magnetic flux density. In a normal design with signal on one layer and return path on the next, the magnetic flux density is high in this smaller area. By using four layers instead of two and interleaving the traces as shown in Figure 7, the flux density is much lower which reduces inductance according to

$$L = \oint \mathbf{H} \cdot \mathbf{B} \ dV/I^2, \tag{22}$$

where  $\mathbf{H}$  is the magnetic field intensity and  $\mathbf{B}$  the magnetic flux density. [22]

This method of interleaving the signal and return paths reduces the inductance by up to 35 %. This also provides a significant reduction in sensitivity to the geometry of the loop with 13 % and 36 % reduction in total PCB height and distance between the devices, respectively. A 34 % improvement in overshoot was achieved, though it should be mentioned that the original overshoot was already only 3.2 %. [22]

Figure 7. Cross section of interleaved signal and return paths redrawn from [22]. Inductance L in schematic is the parasitic inductance of the PCB.

Localized reference planes can be used to improve EMC (Electromagnetic Compatibility). Localized plane is a reference plane, usually ground, used under a high frequency and thus high RF (Radio Frequency) energy emitting components such as oscillators and buffers. This plane is connected to the main reference plane by at least two vias. If ground reference is used for the localized plane, it is recommended to place the component near ground stitching so that it is surrounded by stitching vias. [23]

The main reason for using localized planes is the RF emissions created by frequency generating components due to common mode currents from the circuitry. Metal chassis of the component receives some RF components created by the circuitry and if it is connected to the ground pin of the device, the pin must conduct both DC and RF components. Due to the high inductance of the ground pin and bonding wire, the RF component might be excessive for this pin to conduct. RF emissions can occur if there is no localized reference plane, and the nearest reference plane is far away. The localized reference plane captures some of the emissions thus lowering EMI. [23]

Using SMT (Surface-Mount Technology) packages is worse for EMC since they are usually made of plastic and thus do not capture any RF signals. This way the RF currents will radiate into free space and possibly to close by components or conductors. This is why the use of localized plane is important for SMT devices with plastic enclosures. [23]

#### 3 TOOLS FOR PARASITIC EXTRACTION

There are commercial tools available for extracting parasitic properties of a printed circuit board in two- and three-dimensional geometries. Although parasitic properties can be estimated by hand with simple equations, the higher accuracy of these 3D (3- Dimensional) field solvers make them a valuable tool and for even moderately complex designs mandatory to get reasonable results [5]. 3D field solvers utilize Maxwell's equations and boundary conditions to calculate the results which can be exported for example as S-parameters or RLCG circuit which can further be used in circuit simulation [5].

These field solvers can be divided into full-wave and quasi-static field solvers. Quasi-static solvers like Ansys Q3D use quasi-static approximation which assumes that the phase of the fields does not vary over the problem area. This approximation can further be classified into electro-quasi-static and magneto-quasi-static [24] which include capacitive but not inductive effects and inductive but not capacitive effects, respectively [25]. The condition for a valid quasi-static condition is that the size of the problem area is much smaller than the smallest wavelength [26]. This approximation reduces the complexity of Maxwell's equations. When using full-wave solver like Ansys HFSS there are no restrictions to the problem but the time to solution increases. [5]

## 3.1 S-parameters and RLCG model

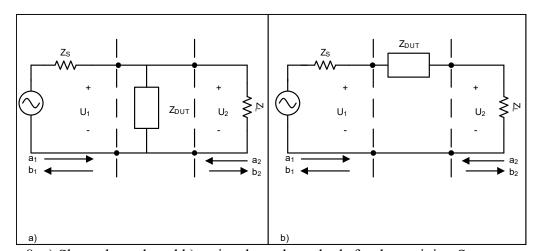

The parasitic model can be constructed using scattering parameters, also called S-parameters, or lumped model. S-parameters are widely used with high frequency signals since it is easier to depict a circuit in terms of waves rather than voltages or currents. For practical reasons a port model is used which has signal and its return path in each port rather than modelling with every node independently. This means that a model consisting of 2n nodes is modelled with a n port model. A 2-port model for shunt-through and series-through setup is shown in Figure 8. [27]

Figure 8. a) Shunt-through and b) series-through methods for determining S-parameters.

The waves flowing into the port are marked by vector a, and waves flowing from the port are marked by vector b. Now the relation between a and b can be written with S-parameters as

$$\boldsymbol{b} = \boldsymbol{S}\boldsymbol{a},\tag{23}$$

where b is the vector containing waves coming from the port, a is the vector containing waves going into the port and S is the S-parameter matrix. The S-parameter matrix S for a two-port system is

$$\mathbf{S} = \begin{bmatrix} S_{11} & S_{12} \\ S_{21} & S_{22} \end{bmatrix}, \tag{24}$$

where  $S_{11}$  is the input reflection coefficient when  $a_2 = 0$ ,  $S_{21}$  the forward transmission coefficient from port one to port two,  $S_{12}$  the reverse transmission coefficient from port two to port one and  $S_{22}$  the output reflection coefficient. [27]

The impedances of this system can be defined by the impedance matrix Z consisting of Z-parameters which relates voltages to currents as

$$\mathbf{Z} = \begin{bmatrix} Z_{11} & Z_{12} \\ Z_{21} & Z_{22} \end{bmatrix}, \tag{25}$$

where  $Z_{11}$  and  $Z_{22}$  are the self-impedances of the ports one and two, respectively.  $Z_{12}$  and  $Z_{21}$  are the transimpedances which define the voltage generated in one port when current is only applied in some other port. [5]

S-parameters and Z-parameters are related by

$$S = \begin{bmatrix} \frac{(Z_{11} - Z_0)(Z_{22} + Z_0) - Z_{12}Z_{21}}{(Z_{11} + Z_0)(Z_{22} + Z_0) - Z_{12}Z_{21}} & \frac{2Z_{12}Z_0}{(Z_{11} + Z_0)(Z_{22} + Z_0) - Z_{12}Z_{21}} \\ \frac{2Z_{21}Z_0}{(Z_{11} + Z_0)(Z_{22} + Z_0) - Z_{12}Z_{21}} & \frac{(Z_{11} + Z_0)(Z_{22} - Z_0) - Z_{12}Z_{21}}{(Z_{11} + Z_0)(Z_{22} + Z_0) - Z_{12}Z_{21}} \end{bmatrix}, (26)$$

where  $Z_0$  is the reference impedance which usually is the characteristic impedance of the line. [28]

Both shunt-through method and series-through method have their advantages in obtaining impedance of the DUT (Device Under Test). Series-through method is good for capturing high impedance values with the minimum impedance being about 30  $\Omega$ . This is due to the equation of impedance as the function of S21, when measuring with series-through method which is

$$Z_{\text{DUT,ser-thru}} = \frac{2Z_{\text{L}}}{S_{21,\text{ser}}} - Z_S - Z_L, \tag{27}$$

where  $Z_S$  is the impedance of port one,  $Z_L$  is the impedance of port two and  $S_{21, \text{ ser}}$  is obtained by the series-through method. These can be seen in Figure 8 b). In equation (27)  $S_{21, \text{ ser}}$  is given by

$$S_{21,\text{ser}} = \frac{2Z_{\text{L}}}{Z_{\text{L}} + Z_{\text{S}} + Z_{\text{DUT}}},$$

(28)

where  $Z_{\text{DUT}}$  is given by equation (27). The equation (28) shows that when  $Z_{\text{DUT}}$  goes too low, the term  $Z_{\text{L}} + Z_{\text{S}}$  starts to dominate the denominator. From this it follows that it is harder to differentiate the values of  $S_{21, \text{ ser}}$  from each other. When  $Z_{\text{DUT}}$  approaches zero, given that  $Z_{\text{L}} = Z_{\text{S}}$  which is usually the case,  $S_{21, \text{ ser}}$  approaches one. [29]

Shunt-through method is good for low impedances and thus for PDN impedance measurements. The upper limit for impedance is about 30  $\Omega$ .  $Z_{DUT}$  as a function of  $S_{21}$  in this case is given by

$$Z_{\text{DUT,shunt-thru}} = \frac{-S_{21}Z_{\text{S}}Z_{\text{L}}}{S_{21}Z_{\text{S}} + S_{21}Z_{\text{L}} - 2Z_{\text{L}}},\tag{29}$$

where  $S_{21}$  is obtained by the shunt-through method and is given by

$$S_{21,\text{shunt}} = \frac{\frac{2Z_{L}Z_{DUT}}{Z_{L} + Z_{DUT}}}{Z_{S} + \frac{Z_{L}Z_{DUT}}{Z_{L} + Z_{DUT}}},$$

(30)

where  $Z_{\text{DUT}}$  is given by equation (29). If  $Z_{\text{DUT}}$  goes too high the  $S_{21}$  approaches one, therefore with higher impedances it is difficult to differentiate the values from each other. This is the opposite behaviour when compared to the series-through method. [29]

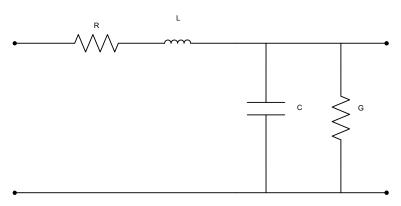

PCB properties can be modelled also by RLCG model which is a lumped model where R is the resistance of the trace, L is the inductance of the trace, C is the capacitance between signal and reference plane and G is the conductance between signal and reference plane as shown in Figure 9 [30]. These components are per unit length so multiple sections may be needed to model the whole trace [30]. Lumped models are valid only if the physical dimensions of the circuit are much smaller than the smallest wavelength. [14]

Figure 9. RLCG model.

#### 3.2 Ansys HFSS and Q3D

Two widely used field solvers are HFSS and Q3D by Ansys. The major difference between the two is that HFSS uses full-wave calculations and Q3D uses quasi-static approximations. Since full-wave simulation does not have size limits for the problem area, HFSS is used to calculate properties for structures used in high frequency signalling [31]. Q3D can be used to calculate properties of structures carrying lower frequency signals [31].

# 3.2.1 HFSS and Q3D differences

There are three common ways to model parasitic effects; FEM (Finite Element Method), 3D-PEEC (3- Dimensional Partial Element Equivalent Circuit) method and RLCG equivalent

circuit method. From these the 3D-PEEC and RLCG methods are a form of equivalent circuit modelling which employ the PEEC method although they offer different advantages. [32]

FEM usually does not use any approximations on the Maxwell's equations and uses a mesh created from the 3D model, thus very accurate broadband parasitic models can be extracted using solvers built on this method. It is challenging to model the HF (High Frequency) and LF (Low Frequency) components with the same accuracy and thus FEM based solvers usually focus more only on one of these. In FEM-based modelling a boundary condition must be used to calculate the electromagnetic effects. In addition, in solvers utilizing FEM only closed current paths can be defined as in solvers using the PEEC method non-closed current paths can be defined by the placement of ports [31]. [32]

PEEC-based solvers' biggest advantage is being usually significantly faster than FEM-based solvers while still being accurate up to some hundreds of MHz although not as accurate as FEM-based. 3D-PEEC method uses modified nodal analysis to calculate the equivalent circuit which couples the electric and magnetic field effects which are calculated based on the mesh created from the 3D model. 3D-PEEC method can calculate the effects by full-wave and quasistatic calculations. The magnetic materials can also be included in the calculation [33]. [32]

RLCG solvers are a special case of a PEEC solver. RLCG solvers calculate the resistance and inductance by solving the PEEC calculations without considering the capacitive effect using a RL (Resistance and Inductance) solver. The capacitive effects are calculated by solving the PEEC equations without considering the magnetic effects using a CG (Capacitance and Conductance) solver. RL and CG solvers use different meshes to calculate the fields and by combining these a RLCG equivalent circuit can be formed. The mesh formed in RLCG method divides the cells of the 3D PEEC method further for these calculations. Typically, 3D RLCG method is faster to solve than 3D PEEC due to much smaller matrices in the equations used. However, it can become as complex as 3D PEEC when the number of ports in RLCG method is increased. [32]

Ansys Q3D is a specialised software used for extracting parasitic properties and models from three-dimensional structures such as printed circuit boards. It uses 3D RLCG method, FEM and MoM (Method of Moments) to calculate the electromagnetic fields and their effects. A LF optimized FEM solver is used to calculate the DC solution for resistance and inductance while the MoM solver is used to calculate the AC solution of R and L with the approximation that the skin effect is fully developed. Q3D can calculate both the RLCG models and the S-parameter models, both of which can further be exported to various circuit simulators in the form of netlist [31]. In Q3D the RLCG circuit can be represented as a TLM (Transmission Line Model) which distributes the R, L, C and G components uniformly, making the model in some cases more accurate [32].

Q3D calculates the inductances with the help of ports, or excitations, at the points of interest. Capacitive coupling is calculated between nets and self-capacitance between the signal path and ground but the distributed capacitance inside a net is not modelled. The ports are modelled as equipotential surfaces so current path is defined between two ports called source and sink. Being equipotential means that the surface defined as port is at the same potential. This can cause some issues since it is not how voltage behaves in the real world. [34]

Ansys HFSS uses full-wave FEM to calculate the S-parameters of the ports using the full physics of the 3D-structure. Since HFSS uses full-wave FEM calculations to extract the S-parameters, a boundary condition is needed to limit the problem area. This calculation is computationally heavy and thus it is recommended to use the interpolating sweep. Interpolating sweep calculates the FEM solution at predefined frequency points and calculates the remaining frequencies accordingly. [31]

HFSS supports differential lumped ports as well as single-ended ports. The lumped port is defined as a port between two nets with one being a reference node. If this node happens to be a global reference node i.e., ground, it is referenced as a single-ended port. The length of these ports should be as short as possible for them not to affect the inductance extraction. [35]

#### 3.2.2 HFSS and Q3D accuracy

HFSS is mostly used to model structures involved with HF signalling due to its high accuracy and Q3D is mostly used with LF signals or when fast time to solution is valued. Both solvers come with their downsides. HFSS is significantly more performance demanding since it is up to seven times more CPU (Central Processing Unit) demanding than Q3D [36]. Q3D is not so accurate in higher frequencies. [31]

With HFSS the simulation results can be close to measurement data when simulation frequencies are over 10 MHz, but when the frequency gets below 1 MHz some mismatch occurs [31], [36]. Q3D can simulate up to 10 GHz but due to the restriction that the DUT must be much smaller than the shortest wavelength to get accurate results, the DUT should be small. The most accurate range for Q3D is up to 100 MHz but with correct settings it can be extended up to 1 GHz without significant deterioration. [36]

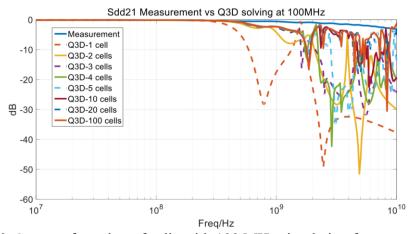

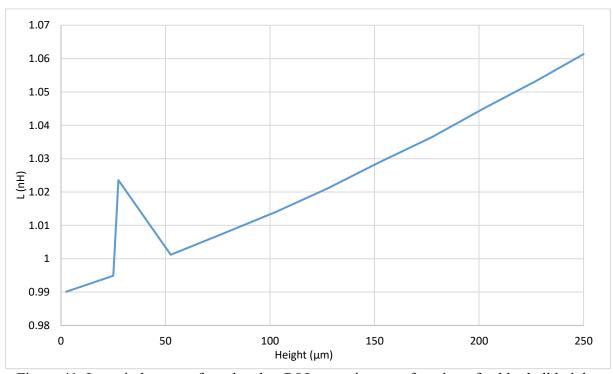

Q3D has settings to change the simulation frequency and number of cells used in the equivalent circuit export. The simulation frequency changes the frequency at which the model is simulated and from this the parasitic properties at that frequency are obtained. The model consisting of these single values can be exported and used in circuit simulator to get the impedance profile. The number of cells used to construct the equivalent circuit affects the performance of the model over 300 MHz. However, with the number of cells higher than five, the performance is improved only at frequencies over 1 GHz. To get accurate modelling for a 3000 mil (76.2 mm) DUT, a simulation frequency point of 100 MHz and equivalent circuit consisting of 5 cells can be used. This gives accurate results up to 300 MHz and with about 2 dB inaccuracy up to 1 GHz as shown in Figure 10. [36]

Figure 10. Sweep of number of cells with 100 MHz simulation frequency [36].

The accuracy of extractor tools when compared to measurements has been studied previously to validate these as a tool for estimating parasitic properties before broader manufacturing of the device [35], [37]–[39]. In study [38] it was shown that the difference between Ansys Q3D simulation and measurement can be up to 40 %. In another study this was challenged by a different way of measuring and simulating using Q3D and the results showed lower than 15 % deviation between simulation and measurement [39]. Impedance analysers

also tend to lose accuracy with low parasitic values which can affect the accuracy [39]. A maximum of 10 % deviation from measurements was shown in [37].

The accuracy and speed of simulation can be improved by segmenting the DUT and using Q3D as the simulator or by extracting the LF with Q3D and HF with HFSS [31], [36]. First method improves the accuracy by dividing the DUT into smaller sections so that the wavelength of the highest frequency would be greater than the physical dimensions of the segments. By doing this the single segments can be modelled accurately, and in post-processing these models can be joined in series to get the whole model of the DUT [36]. This also improves the time to solution since the need for HFSS is avoided. Since HFSS might not always be so accurate in the LF and Q3D not so accurate at HF, they can be used to extract the frequencies where they are accurate and then be combined in post-processing [31]. This leads to higher correlation with measured data than using just one solver [31].

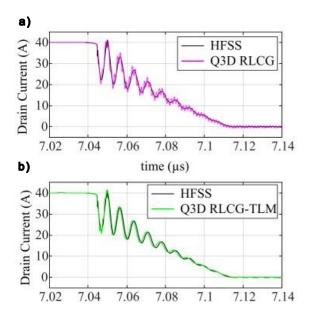

The lower accuracy at HF of Q3D models when compared to HFSS models leads to high frequency oscillations which are not present in HFSS model [32]. This effect can be seen in Figure 11 a). The curve in Figure 11 b) shows HFSS model and Q3D model when using the TLM option. In this case it seems to mostly eliminate the high frequency ringing. This behaviour will slow down transient simulations which is problematic when these models are used to evaluate circuit behaviour with parasitic effects in long simulation sets.

Figure 11. High frequency oscillations in Q3D model [32].

These studies show the strengths and weaknesses of both tools and the best use cases for both. It was also discussed how the accuracy could be improved for Q3D. From these previous studies it can be concluded that Ansys HFSS is not the right tool for the extraction in this study due to its more demanding calculations and thus longer time to solution.

#### 4 PCB DESIGN

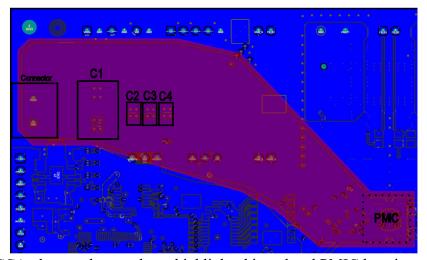

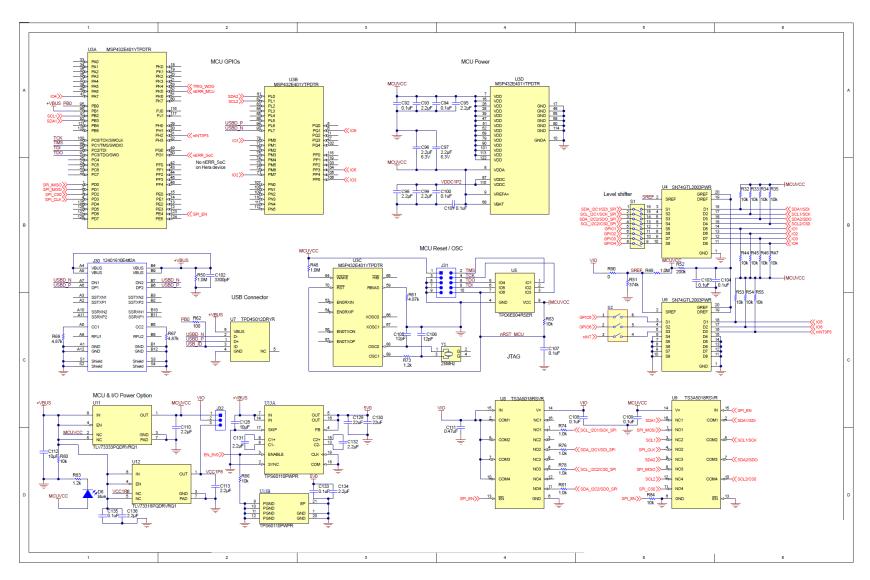

A PCB was designed for this study, which was for a PMIC that has three LDO (Low-Dropout) linear regulators and four buck converters from which two can be used in multiphase for higher output power. The specifications of buck outputs and LDO outputs are listed in Table 2 and Table 3, respectively. Due to the integrated circuit being evaluated with this board is a power management integrated circuit, closer attention is given to the power outputs and inputs of the device and their corresponding traces.

| 1          |                      |              |              |

|------------|----------------------|--------------|--------------|

| Output     | Max. f <sub>SW</sub> | Max. voltage | Max. current |

| BUCK1      | 4.4 MHz              | 3.3 V        | 5 A          |

| BUCK2      | 4.4 MHz              | 3.3 V        | 5 A          |

| BUCK3      | 4.4 MHz              | 3.3 V        | 2 A          |

| BUCK4      | 4.4 MHz              | 3.3 V        | 2 A          |

| BUCK1+BUCK | 4.4 MHz              | 1.2 V        | 10 A         |

Table 3. LDO regulator outputs

| Output | Max. Voltage | Max. current |

|--------|--------------|--------------|

| LDO1   | 3.3 V        | 300 mA       |

| LDO2   | 3.3 V        | 400 mA       |

| LDO3   | 3.3 V        | 400 mA       |

#### 4.1 Evaluation module outputs

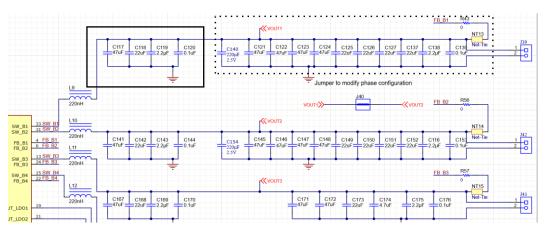

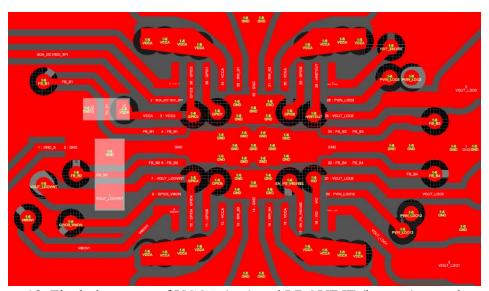

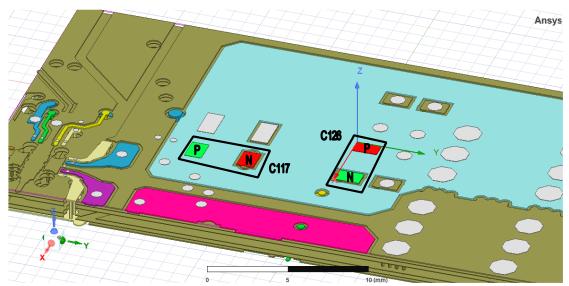

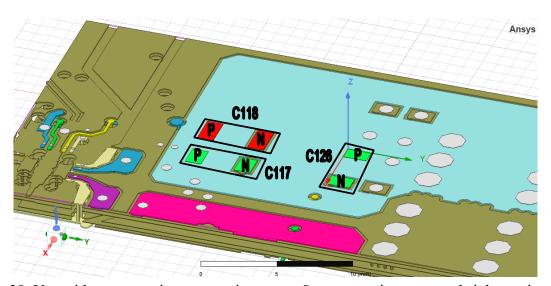

The output side schematic for the designed evaluation module is shown in Figure 12. There are more capacitors than in a typical design since this is used for evaluating the PMIC. Therefore, it is necessary to be able to configure the EVM (Evaluation Module) as needed. The output local capacitors closer to the PMIC are outlined in a solid line and the POL (Point Of Load) capacitors are outlined with a dashed line. Most of the current is assumed to go through capacitor C118. Placement for the buck1 capacitors is shown in Figure 13.

Figure 12. Part of the output side schematic showing bucks one, two and three.

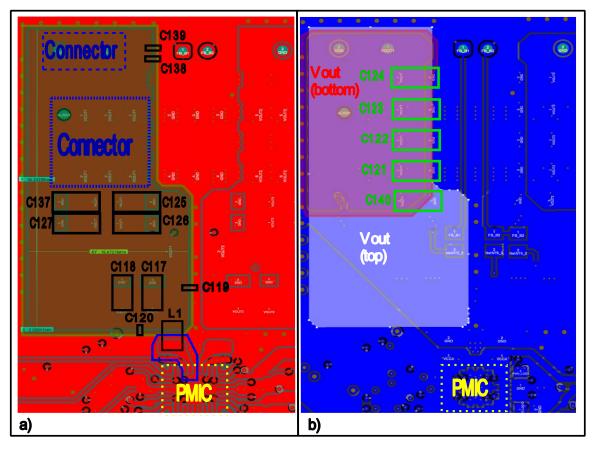

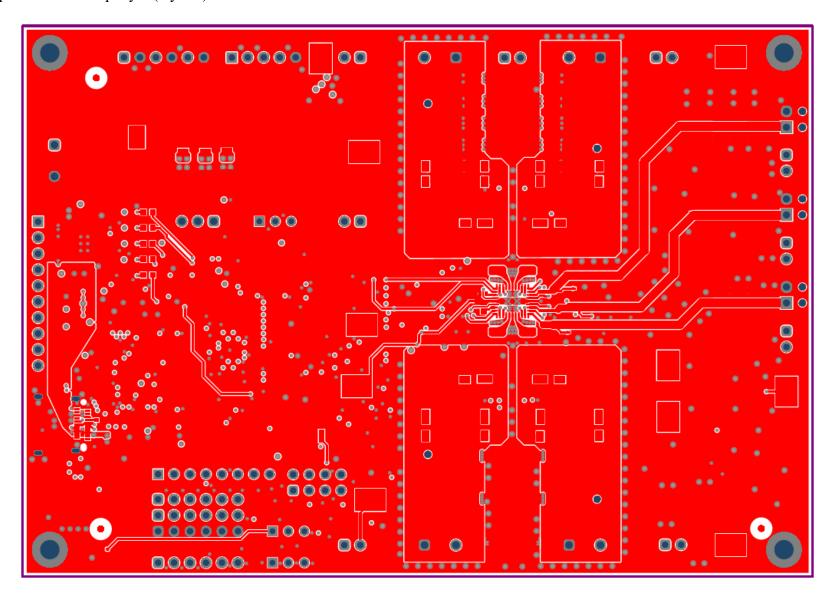

Due to high current output and high switching frequencies, the buck outputs are prone to issues from the printed circuit board parasitic properties. Figure 13 shows the top (a) and bottom (b) layers for one of the buck outputs. The top layer is shown in a) with the output plane

highlighted in green, which is the biggest area in this figure. The area is maximized to minimize parasitic inductance and resistance. Switch node is outlined in blue on the bottom part of the figure a). This is kept as short and wide as possible. Inductor placement is outlined in black, showing the connection to the switch and output nodes, and the PMIC outlined in yellow dashed line. The capacitors are outlined in black in a) and in green in b). Loading connectors are outlined in a blue dashed line with the bigger one being high dI/dt connector. Because of fast transients on this connector, the top layer POL capacitors in a) are placed closer to this connector. There are in total four similar buck outputs and one of them is shown in Figure 13 as mirror image to the right of the discussed output.

Figure 13. Buck output planes in a) top and b) bottom layers.

Trace to the inductor is kept as short as possible and made as wide as possible to minimize inductance and capacitance of that trace. Inductance of this trace is not as important since it is in series with the much higher inductance inductor, although it still contributes to the loop inductance. Capacitance between this trace and other traces should be kept low because of the fast switching. The parasitic loop inductance causes ringing and may cause overvoltage at the switching node [40]. This is highly important because of the high switching frequency and high dV/dt. In this PMIC the pins next to the switching node are the input voltage for the buck and the power ground. They all need to be as low inductance as possible, so compromises had to be made on all these trace sizes. The feedback of switching regulators is sensitive to noise since it must accurately measure the output voltage. This is why the feedback traces are kept away from any high noise traces.

Current loop in these buck outputs is designed to spread out as much as possible to lower the resistance and inductance. The current is directed to inner layers through vias. The capacitors at the middle of the plane do not have direct contact to the top layer ground plane, thus many vias had to be used. In these capacitors as many vias were used as possible and they were placed as far away from each other as possible since this minimizes the mutual inductance between vias where current is flowing in the same direction [2].

Figure 13 b) shows  $V_{out}$  plane on the bottom highlighted in red and the bigger white highlighted area is the  $V_{out}$  plane on the top layer. This is done because there are more capacitors on the bottom layer which could not fit on the top. Because of this there must be some vias going from the top layer to bottom layer. These are mainly placed on the pads of the capacitors to minimize the current loop and thus the loop inductance.

The LDO regulator outputs are not designed to supply a lot of power, so the traces do not have to be as wide as the buck regulator output traces. In this layout the capacitor placement is designed so that the current can flow in the top layer as much as possible to avoid high inductance vias. This is why the current return path is tried to maintain as wide as possible while not having to sacrifice the width of the output traces. Vias are still used so the current can spread out. LDO regulators two and three could easily be designed to have the current flow mostly on the top layer but with the regulator one some vias had to be used to get the current to return to the wanted ground pin of the device. The final design for the LDO regulator outputs is shown in Figure 14 with capacitor placement marked with black rectangles. First millimetres of the output conductor are narrower due to space restrictions near the PMIC which somewhat increases the inductance.

Figure 14. LDO regulator output traces and capacitor placements.

The LDO traces are not included in the further analyses because of their lower current capabilities. The LDO's were discussed since they are a part of the design and it had to be explained why those are not so much of interest in this study.

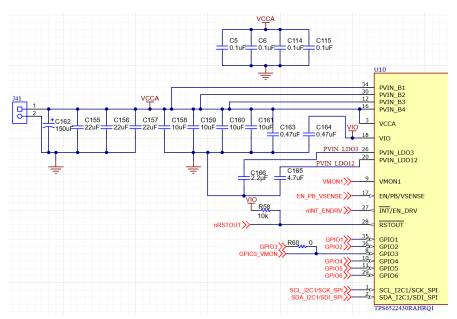

#### 4.2 Evaluation module input and internal LDO

Since the device can output high currents, it must be supplied with high currents. This leads to high current transients and thus the input traces must have low resistance and loop-inductance to avoid rail collapse and to improve efficiency. The device also has an internal LDO, labelled

LDOVINT, which is used to supply the analog and digital functions of the PMIC. This supply needs an external capacitor for which there is an output pin.

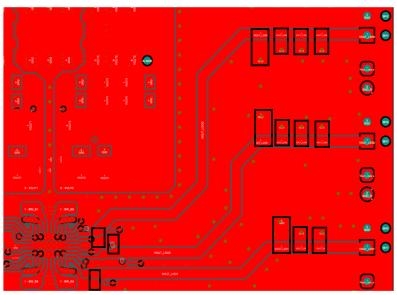

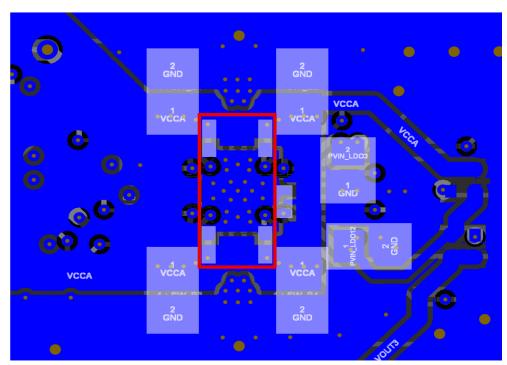

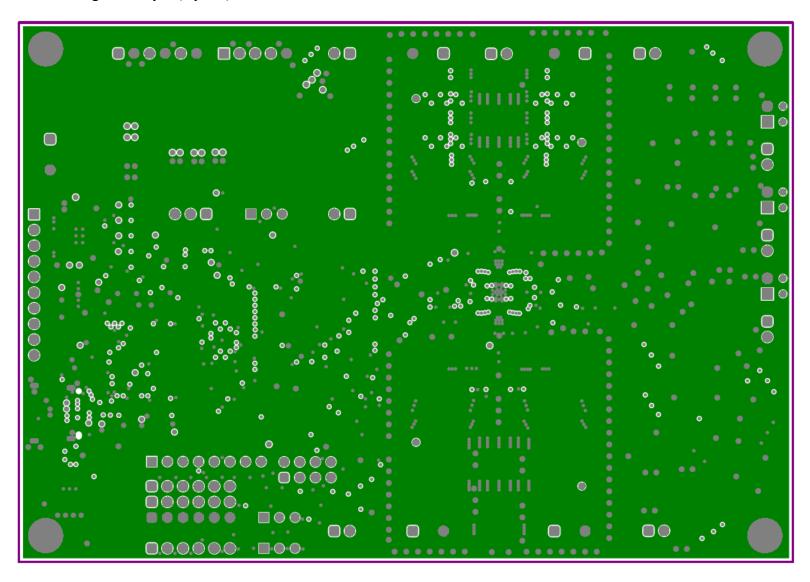

The input side capacitors are shown in Figure 15. Capacitors C5, C8, C114 and C115 are placed on the bottom side under the PVIN pins and capacitors C158, C159, C160 and C161 are placed on the bottom side a bit further from the pin as shown in Figure 16.

Figure 15. Input side schematic of the PMIC.

The Figure 16 shows the VCCA (positive power supply) plane on the bottom plane for the PMIC. The VCCA plane is highlighted in red and the PMIC is outlined with a dashed line. The VCCA plane runs on the bottom side of the PCB since there is more space for the plane and the input capacitors. These must be as close as possible to the PMIC so that the inductance between the input capacitor and PMIC is as small as possible. Capacitors closer to the PMIC are responsible for the fast transients due to low inductance between the capacitor and the pin and the bulk capacitors for the slower transients due to high inductance between the capacitors and the PMIC.

Figure 16. VCCA plane on bottom layer highlighted in red and PMIC location with dashed line.

The outlined connector on the left side of Figure 16 is the input voltage connector for the PMIC. Since this is far away from the device, the trace must be wide to avoid any rail collapse or voltage drop. The VCCA trace is tried to maintain uninterrupted to avoid any high impedance paths for the current. The four bulk capacitors are outlined in black and the local input capacitors for the PMIC are inside the dashed line.

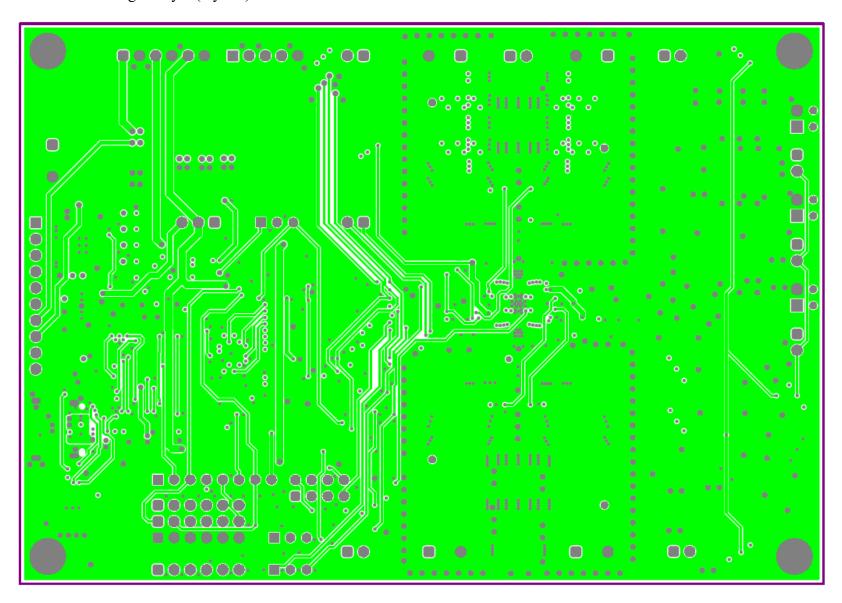

In Figure 17 the four small capacitors outlined with red are the local input capacitors for the PMIC's buck input pins and the four larger capacitors next to them are also for the same node but little further away and with higher capacitance to help with transient loads. The two big capacitors to the right are input capacitors for the LDO regulators, and the small capacitor under the PMIC is for the IO voltage of the device. All these device inputs are prone to voltage variations and thus the capacitors are placed as close to the pins as possible to minimize the loop inductance associated with them. Some of the more important pins are the buck input pins because of their high current draw. Although some vias are needed to pass the current through the layers, this is still a lower inductance path than placing the capacitors on the top layer further away from the PMIC.

Figure 17. PMIC input capacitors on the bottom layer.

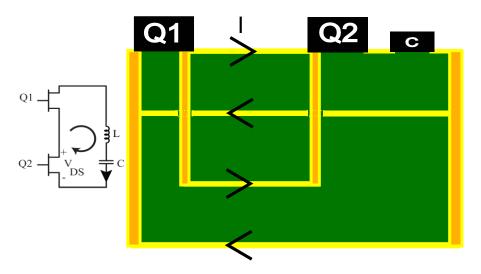

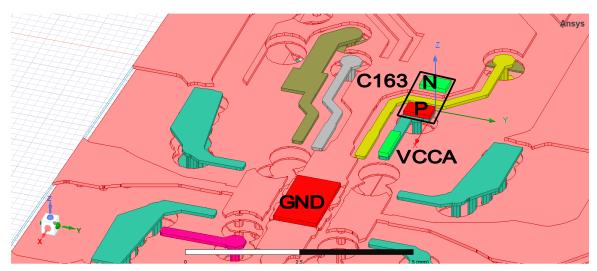

Two points of closer examination were the input pin for VCCA on the top layer and the output for the internal LDO regulator because of their high importance. These pins and their capacitors can be seen in Figure 18. The VCCA capacitor is C163 in Figure 15. Two options for the placement of these capacitors were considered which were to place them horizontally or vertically. In the vertical orientation one of the capacitors must be further away from the PMIC so the LDOVINT capacitor placement was prioritized.

The loop inductances were extracted by using Ansys Q3D software, and the loop used for both was from pin to capacitor positive terminal in series with capacitor negative terminal to ground pin of the PMIC. The extracted inductances are shown in Table 4.

| ] | Table 4. VCCA and LDOVINT | loop | inductance with | different | ca | pacitor | placements | ; |

|---|---------------------------|------|-----------------|-----------|----|---------|------------|---|

|   |                           |      |                 |           |    |         |            |   |

| Orientation | Current loop | Loop inductance |

|-------------|--------------|-----------------|

| Vertical    | LDOVINT      | 0.70 nH         |

| vertical    | VCCA         | 1.17 nH         |

| Horizontal  | LDOVINT      | 0.98 nH         |

| Horizontai  | VCCA         | 1.04 nH         |

Table 4 supports the theory that shorter loop should have less loop inductance since in the vertical layout the loop of VCCA came to be longer than in the horizontal orientation and LDOVINT loop inductance is smaller with vertical arrangement since it can be placed closer to the device. Based on these results it was decided that the LDOVINT capacitor is placed vertically and VCCA capacitor horizontally to minimize the loop inductance for both. This layout is shown in Figure 18 with the two capacitors highlighted.

Figure 18. Final placement of VCCA (top) and LDOVINT (bottom) capacitors.

Although the LDOVINT layout is important, it is not further examined in this thesis. The analysis done on VCCA and LDOVINT capacitor placement could have been done on every capacitor in the design, but this would have taken a significant amount of time and since it was not in the scope of this thesis, it was not done on any other capacitor placements.

#### 5 SIMULATION AND MEASUREMENT SETUPS

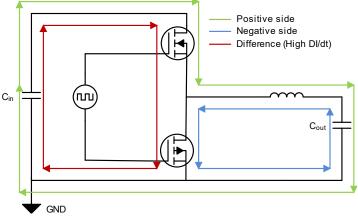

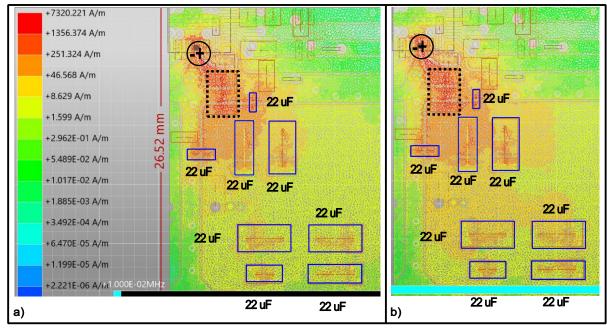

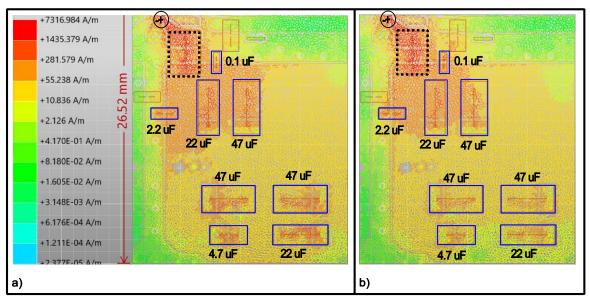

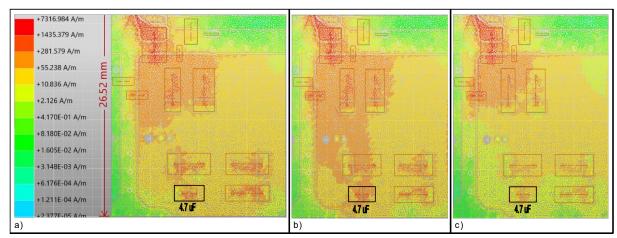

The parasitic properties of this EVM were extracted from two critical points which affect the performance of the PMIC. These points are the trace between switching regulator local and point of load capacitors, the return path associated with this and the input loop for the buck regulator.

#### 5.1 Points of interest for extraction

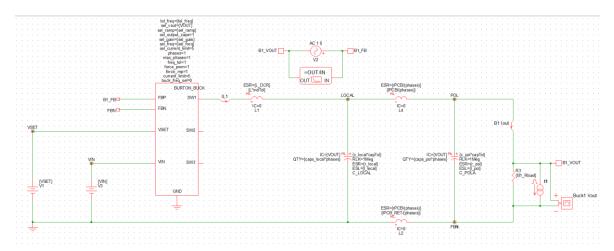

The impedance, and more specifically the inductance, between the local and POL capacitors is of interest because of the phase shift it creates. This phase shift decreases the phase margin so if the inductance is too high at this point the device can become unstable. These conditions were simulated in SIMPLIS by SIMPLIS Technologies which is a specialized simulator for switching mode power supplies. The schematic used for these simulations is shown in Figure 19. These simulations were done to demonstrate why these points were chosen for the parasitic extraction.

Figure 19. Schematic used in SIMPLIS simulations.

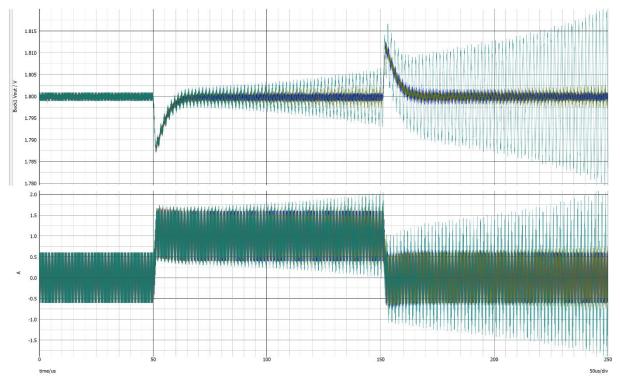

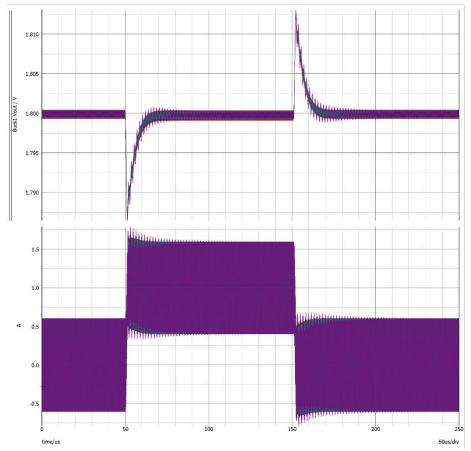

The effect of inductance in the signal path and the return path were evaluated separately. The inductance in signal path was simulated with no return path inductance so L2 in Figure 19 was shorted and the PCB inductance was simulated with a few different values. The effect of return path inductance was evaluated with signal path inductance of L1 set to 2 nH to show more prominent results and only the return path inductance L2 was swept. Local and POL capacitance was kept at a constant value and the used load transient was from 0 A to 1 A in 1 µs and the pulse duration was 100 µs.

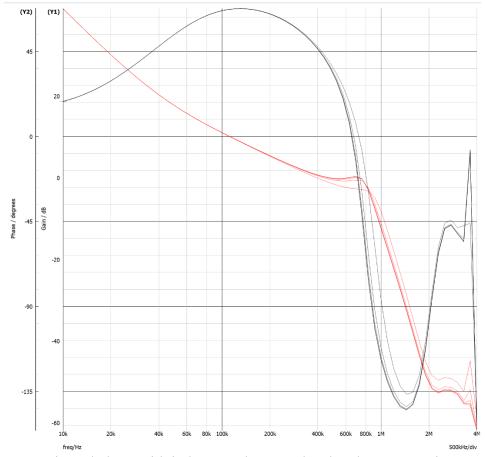

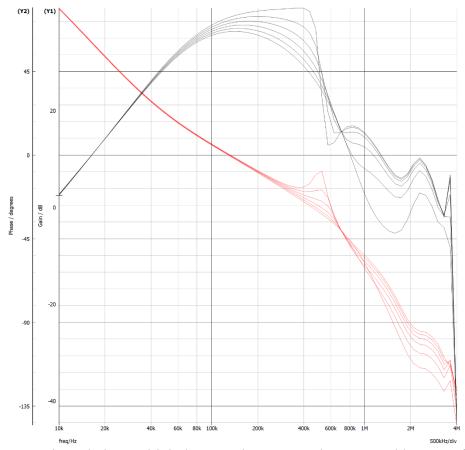

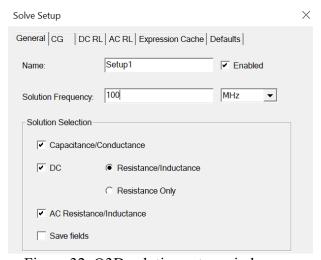

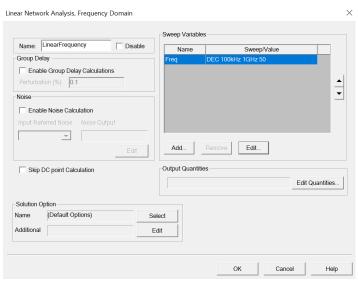

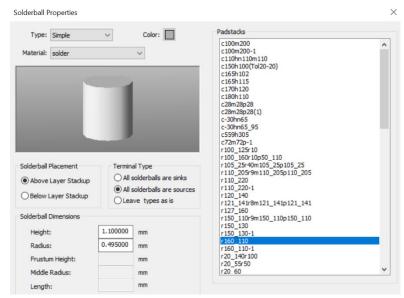

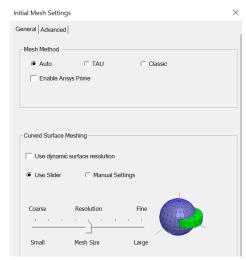

The AC simulations show the loop gain and phase of the buck converter measured between feedback pin and output. The AC simulation plots for inductance in signal path can be seen in Figure 20 with phase plotted with black and gain in red. The plots differ slightly when the inductance increases but then considering that this is only from the PCB parasitic properties which can quite easily be mitigated, it is a noteworthy difference which has to be taken into consideration. Table 5 shows the full simulated values.