# University of Arkansas, Fayetteville ScholarWorks@UARK

Graduate Theses and Dissertations

5-2023

# Advanced CMOS Process for Submicron Silicon Carbide (SiC) Device

Niloy Saha University of Arkansas-Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the Mechanical Engineering Commons

## Citation

Saha, N. (2023). Advanced CMOS Process for Submicron Silicon Carbide (SiC) Device. *Graduate Theses and Dissertations* Retrieved from https://scholarworks.uark.edu/etd/4968

This Thesis is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu.

Advanced CMOS Process for Submicron Silicon Carbide (SiC) Device

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Materials Engineering

by

# Niloy Saha Heritage Institute of Technology Bachelor of Technology in Electronics and Communication Engineering Jadavpur University Master of Technology in Nano Science and Technology, 2012

# May 2023 University of Arkansas

This thesis is approved for recommendation to the Graduate Council.

H. Alan Mantooth, Ph.D. Thesis Director Zhong Chen, Ph.D. Thesis Co-Director

Morgan E. Ware, Ph.D. Committee Member Matthew Leftwich, Ph.D. Ex-Officio Member The following signatories attest that all software used in this thesis was legally licensed for use by Niloy Saha for research purposes and publication.

Mr. Niloy Saha, Student

Dr. H. Alan Mantooth, Thesis Director

Dr. Zhong Chen, Thesis Co-Director

This thesis was submitted to http://www.turnitin.com for plagiarism review by the TurnItIn company's software. The signatories have examined the report on this thesis that was returned by TurnItIn and attest that, in their opinion, the items highlighted by the software are incidental to common usage and are not plagiarized material.

Dr. Matthew Leftwich, Program Director Dr. H. Alan Mantooth, Thesis Director

Dr. Zhong Chen, Thesis Co-Director

### Abstract

Silicon carbide (SiC) is a wide semiconductor material with superior material properties compared to other rival materials. Due to its fewer dislocation defects than gallium nitride and its ability to form native oxides, this material possesses an advantage among wide band gap materials. Despite having several superior properties its low voltage application is less explored. CMOS is extremely important in low voltage areas and silicon is the dominant player in it for the last 50 years where scaling has contributed a major role in this flourishment. The channel length of silicon devices has reached 3 nm whereas SiC is still in the micrometer ( $2 \mu m/ 1.2 \mu m$ ) range. So, SiC technology is still in its infancy which can be compared with silicon technology in the mid-1980s range. When the SiC devices would enter into the sub-micron and deep submicron range, proper device design in those ranges is necessary to rip the benefit of scaling.

In this thesis, the SiC CMOS process available from different institutes and foundries is discussed first to understand the current state of the art. Later, low-voltage conventional SiC NMOS devices in the submicron range (2 µm to 600 nm) are simulated and their key parameters and performances are analyzed. In the submicron range, one major issue in MOSFET scaling is hot carrier effects. Thus to minimize this effect, a low-doped drain (LDD) region is introduced in the conventional SiC design having a channel length of 800 nm and 600 nm. In comparison with conventional designs, LDD designs have shown better saturation current behavior, reduced threshold roll-off, reduced hot electron current density, minimized gate leakage, reduced body hole current, enhanced voltage handling capability, reduced electric field, and improved subthreshold behavior in SiC. In the end, spacer technology, dopants, doping methods, and LDD realization technique in SiC are discussed.

## Acknowledgments

I am grateful to my advisor Dr. H. Alan Mantooth for his patience, financial support, and guidance. His belief in me and his encouragement always pushed me to improve the quality of my work throughout this journey. I am indebted to my co-advisor Dr. Zhong Chen for providing much-needed advice, expertise, guidance, and knowledge throughout the course of my degree program. Without his help, I could not finish it. I appreciate Dr. Morgan E. Ware for being my committee member. I appreciate Dr. Matthew Leftwich for advising me whenever I needed it.

Special thanks to Dr. Rick Wise and Dr. Shui-Qing (Fisher) Yu for allowing me to join the Materials Science and Engineering program. I would like to thank Renee Jones-Hearon for her support.

I am grateful to John Ransom for his guidance and sharing his expertise with me. His experience and knowledge in the semiconductor field helped me to grow a little knowledge in this area.

I would like to thank my senior lab member Dr. Md. Maksudul Hossain for his time to discuss with me, train me, and help me to pass my initial research days. I am grateful to him. I am grateful to my other senior lab member Dr. Pengyu Lai to answer my silly questions and provide materials and support whenever I asked. I have learned a lot from him. I would like to thank Hui Wang to help and guide me in the simulation and helping me in my research. I would like to thank Dr. Murtadha A. Alher, Kevin Chen, Anthony Di Mauro, and Tanner Rice for providing training in the Nanofabrication lab and sharing their knowledge whenever I needed it.

Finally, I would like to appreciate my parents, wife, sister, and my nephew for providing me with motivation, encouragement, and unconditional support over the years.

# **Table of Contents**

| Chapter 1 | . Introduction                                                    |

|-----------|-------------------------------------------------------------------|

| 1.1       | Silicon Carbide as a Material1                                    |

| 1.2       | Importance of SiC CMOS                                            |

| 1.3       | Importance of Technology Scaling                                  |

| 1.4       | Challenges in MOSFET Scaling                                      |

| 1.5       | Thesis Goals10                                                    |

| Chapter 2 | Background and Literature Review                                  |

| 2.1       | CMOS Process Overview                                             |

| 2.1.1     | Cree CMOS14                                                       |

| 2.1.2     | Hitachi CMOS                                                      |

| 2.1.3     | NASA & CWRU JFET19                                                |

| 2.1.4     | Raytheon CMOS                                                     |

| 2.1.5     | Fraunhofer CMOS                                                   |

| 2.1.6     | Purdue CMOS                                                       |

| 2.2       | Hot Carrier Effects in MOSFET                                     |

| 2.2.1     | Mitigate Hot Carrier Effects                                      |

| 2.2.2     | Low-Doped Drain                                                   |

| Chapter 3 | 6. Conventional NMOSFET Device Simulation and Characterization    |

| 3.1       | Tools Overview                                                    |

| 3.2       | Device Simulation                                                 |

| 3.3       | Device Characterization                                           |

| Chapter 4 | Low-Doped Drain NMOSFET Device Simulation and Characterization 50 |

| 4.1       | Device Simulation with Low-Doped Drain                            |

| 4.2                                                            | Device Characterization                                                                   | 2  |  |  |  |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------|----|--|--|--|

| 4.3                                                            | Advantages and Disadvantages of the Proposed Solution                                     | 9  |  |  |  |

| Chapter 5                                                      | 5. Proposed Advanced CMOS Process                                                         | 2  |  |  |  |

| 5.1                                                            | Proposed Spacer structure                                                                 | 2  |  |  |  |

| 5.2                                                            | Proposed Doping Methods and Dopants for LDD                                               | 4  |  |  |  |

| 5.3                                                            | Realization of LDD structure                                                              | 6  |  |  |  |

| 5.3.1                                                          | LDD in Silicon                                                                            | 6  |  |  |  |

| 5.3.2                                                          | LDD in SiC                                                                                | 8  |  |  |  |

| Chapter 6                                                      | 5. Conclusions                                                                            | 1  |  |  |  |

| 6.1                                                            | Summary                                                                                   | 1  |  |  |  |

| 6.2                                                            | Future Work                                                                               | 2  |  |  |  |

| 6.3                                                            | Major Roadblocks                                                                          | 2  |  |  |  |

| Reference                                                      | s7                                                                                        | ′4 |  |  |  |

| Appendix                                                       | A: Description of Research for Popular Publication                                        | 0  |  |  |  |

| Appendix                                                       | B: Executive Summary of Newly Created Intellectual Property                               | 1  |  |  |  |

| Appendix                                                       | C: Potential Patent and Commercialization Aspects of Listed Intellectual Property<br>Item | 2  |  |  |  |

| Appendix                                                       | D: Broader Impact of Research                                                             | 3  |  |  |  |

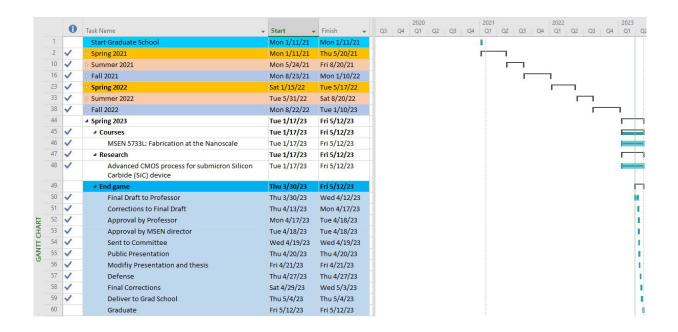

| Appendix                                                       | E: Microsoft Project for MS MATE Degree Plan 8                                            | 4  |  |  |  |

| Appendix                                                       | F: Identification of All Software Used in Research and Thesis Generation                  | 5  |  |  |  |

| Appendix G: All Publications Published, Submitted, and Planned |                                                                                           |    |  |  |  |

| Appendix                                                       | H: Simulation Deck                                                                        | ;7 |  |  |  |

# List of Figures

| Figure 1.1 | The stacking sequence of 6H-SiC, 4H-SiC, and 3C-SiC [4]                                                                                                                      | 2  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.2 | . Demand for harsh environment electronics [8]                                                                                                                               | 4  |

| Figure 1.3 | Principle of MOSFET IC scaling [14]                                                                                                                                          | 7  |

| Figure 2.1 | Basic CMOS Process (silicon) [20] 1                                                                                                                                          | 5  |

| Figure 2.2 | Cree CMOS (a) NMOS I-V characteristics, (b) PMOS I-V, (c) Doping profile of n-<br>well showing nitrogen concentration [22]                                                   | 8  |

| Figure 2.3 | (a) Schematic cross-section, (b) Field effect mobility of Hitachi's 4H-SiC BC MOSFET [24]                                                                                    | 9  |

| Figure 2.4 | (a) Schematic cross-section of CWRU 6H-SiC JFET [32], (b) Simplified cross-section of NASA 6H-JFET [33]                                                                      |    |

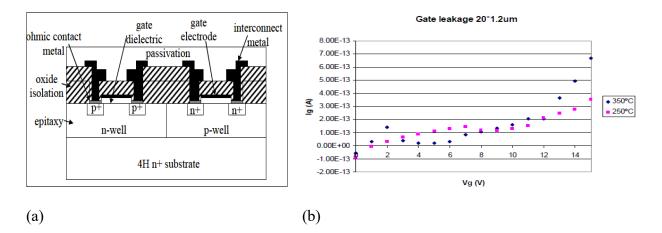

| Figure 2.5 | (a) Raytheon's CMOS process architecture, (b) Gate current vs. gate voltage for 20*1.2 μm NMOS [37]                                                                          | 3  |

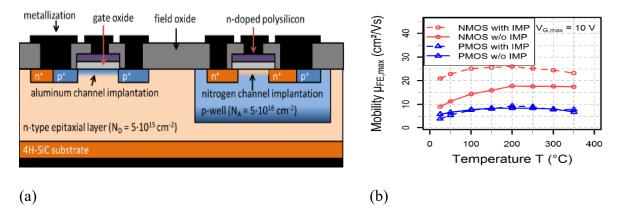

| Figure 2.6 | (a) Fraunhofer's CMOS process architecture [46], (b) Field effect mobility of NMOS and PMOS with and without channel implant [46]                                            |    |

| Figure 2.7 | Hot carrier (electrons and holes) generation [50]                                                                                                                            | 8  |

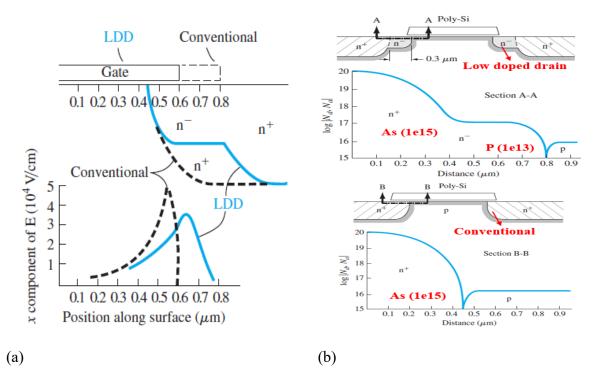

| Figure 2.8 | (a) E-field at Si-SiO <sub>2</sub> interface, (b) Doping profile LDD vs. conventional structure [52]                                                                         | 0  |

| Figure 3.1 | Sentaurus workbench used for process and device simulation                                                                                                                   | 3  |

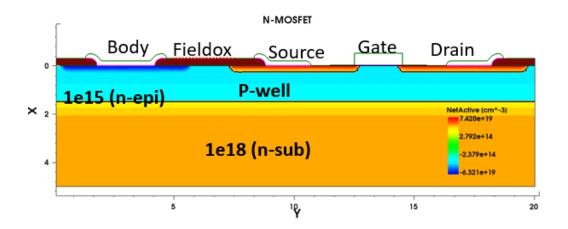

| Figure 3.2 | Conventional NMOSFET device simulatation in Sentaurus                                                                                                                        | 4  |

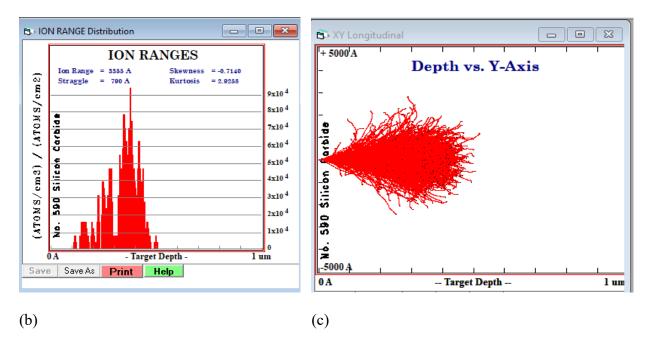

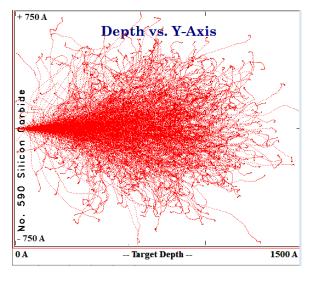

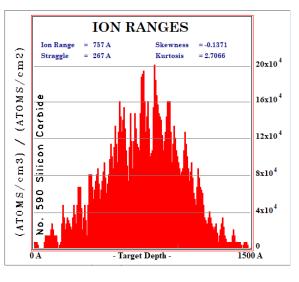

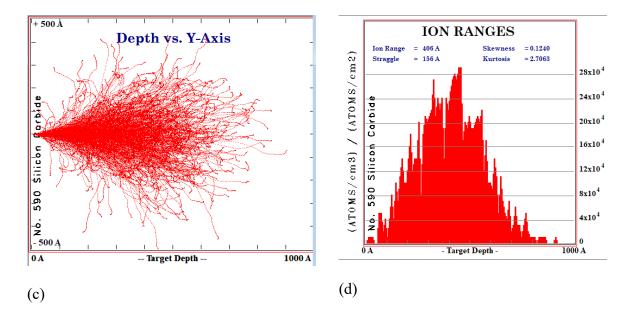

| Figure 3.3 | (a) SRIM workbench used for ion implantation, (b) Ion range distribution, (c)<br>Implantation depth analysis by SRIM                                                         | 6  |

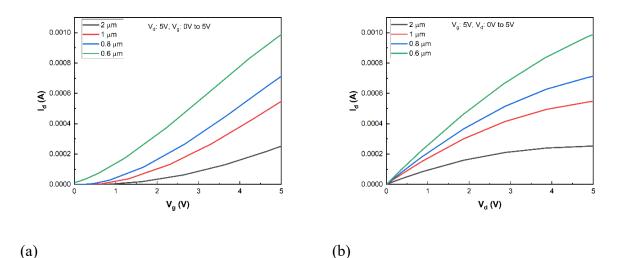

| Figure 3.4 | (a) Drain current (I <sub>d</sub> ) vs. Gate voltage (V <sub>g</sub> ), (b) Drain current (I <sub>d</sub> ) vs. Drain voltage (V <sub>d</sub> ) at different channel lengths | 8  |

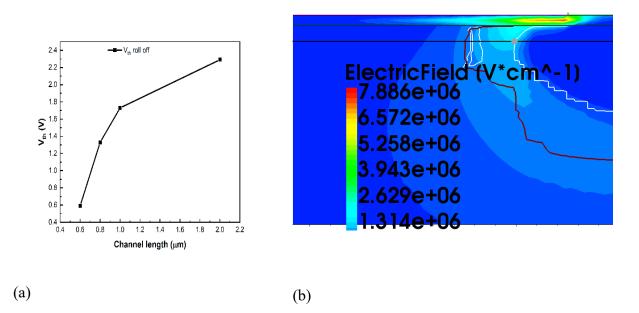

| Figure 3.5 | (a) Threshold voltage ( $V_{th}$ ) vs. Channel length ( $\mu$ m), (b) Cutline to check e-field across 2 $\mu$ m device                                                       | 8  |

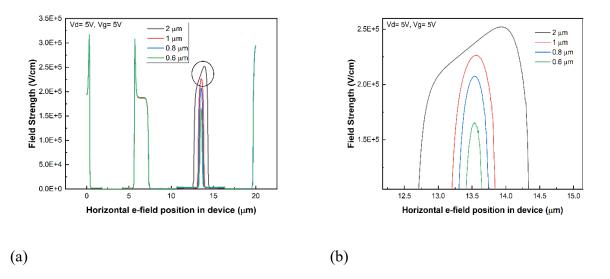

| Figure 3.6 | (a) Horizontal e-field strength vs. e-field position, (b) Zoomed area of e-field                                                                                             | 9  |

| Figure 3.7 | Horizontal e-field strength vs. channel length for Si device (1 µm, 0.5 µm) [59] 4                                                                                           | 0  |

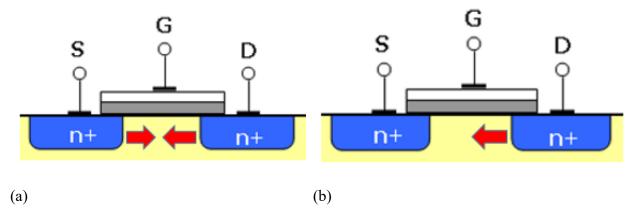

| Figure 3.8 | Channel preparation (a) First approach, (b) Second approach                                                                                                                  | -0 |

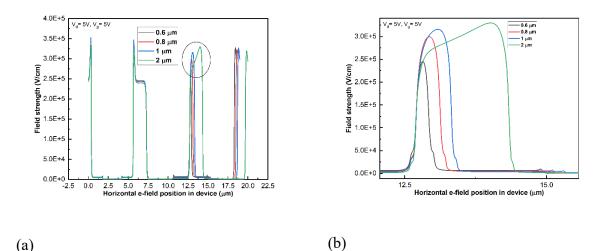

| Figure 3.9 (a) Horizontal e-field strength vs. e-field position, (b) Zoomed area of e-field                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

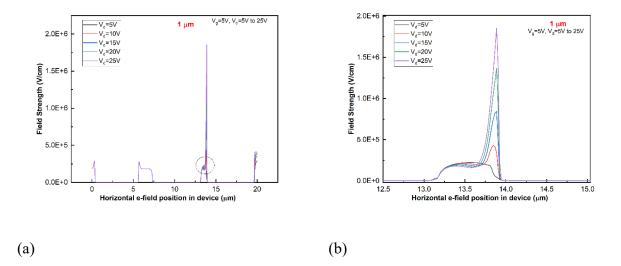

| Figure 3.10 (a) 1 $\mu$ m horizontal e-field strength vs. e-field position, (b) Zoomed area of e-field 42                                                                                                                                          |

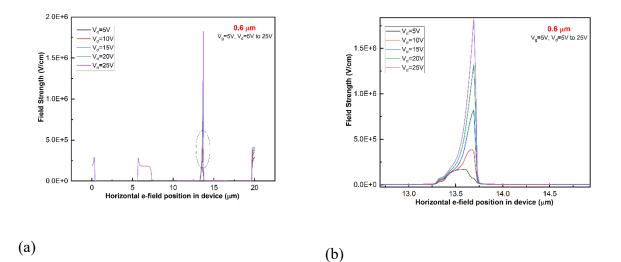

| Figure 3.11 (a) 0.6 µm horizontal e-field strength vs. e-field position, (b) Zoomed area of e-field                                                                                                                                                |

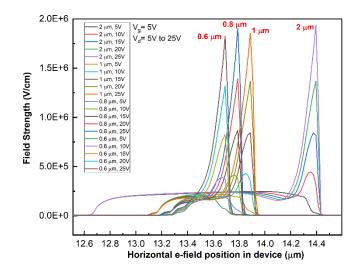

| Figure 3.12 Comparison of e-field between 2 $\mu m,$ 1 $\mu m,$ 0.8 $\mu m,$ and 0.6 $\mu m$ channel length 43                                                                                                                                     |

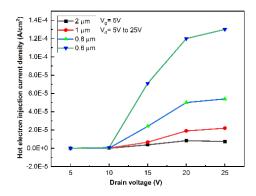

| Figure 3.13 Hot electron injection current density $(A/cm^2)$ vs. drain voltage $V_g = 5V$ , $V_d = 5V$ to 25V                                                                                                                                     |

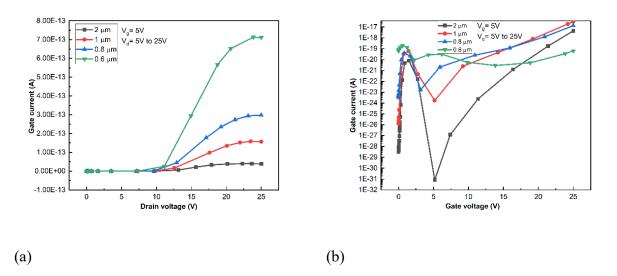

| Figure 3.14 (a) Gate current (I <sub>g</sub> ) vs. drain voltage (V <sub>d</sub> ) at $V_g = 5V$ , $V_d = 5V$ to 25V, (b) Gate current (I <sub>g</sub> ) vs. gate voltage (V <sub>g</sub> ) at $V_d = 5V$ , $V_g = 5V$ to 25V                      |

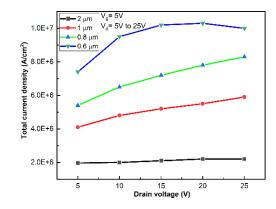

| Figure 3.15 Total current density of 2 $\mu$ m, 1 $\mu$ m, 0.8 $\mu$ m, and 0.6 $\mu$ m devices at V <sub>g</sub> = 5V, V <sub>d</sub> = 25V                                                                                                       |

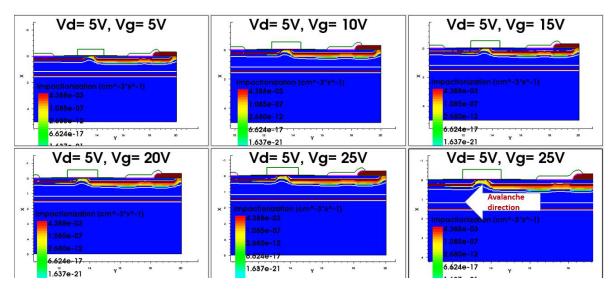

| Figure 3.16 Avalanche direction of 1 $\mu$ m device at V <sub>d</sub> =5V, V <sub>g</sub> = 5V to 25V                                                                                                                                              |

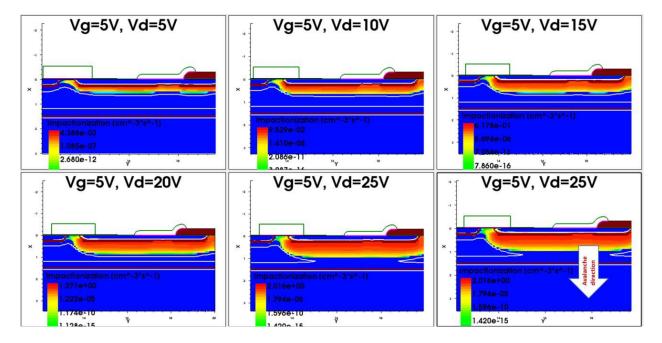

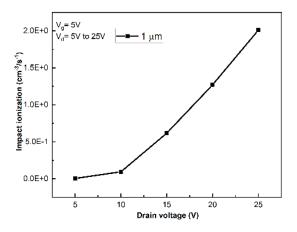

| Figure 3.17 Impact ionization of 1 $\mu$ m device at V <sub>g</sub> =5V, V <sub>d</sub> =5V to 25V48                                                                                                                                               |

| Figure 3.18 Impact ionization vs. drain voltage of 1 $\mu$ m device at V <sub>g</sub> =5V, V <sub>d</sub> = 5V to 25V 49                                                                                                                           |

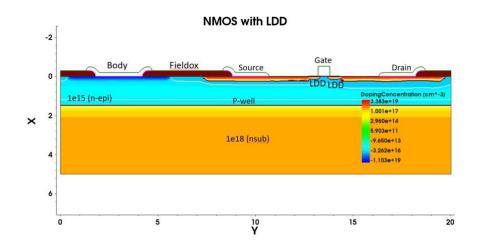

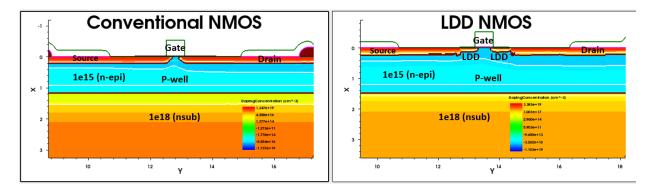

| Figure 4.1 NMOSFET (0.6 µm channel length) with LDD region                                                                                                                                                                                         |

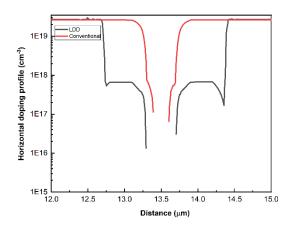

| Figure 4.2 (a) NMOS LDD structure and NMOS conventional structure, (b) Comparison of doping profile between LDD and conventional NMOSFET (0.6 μm channel length)51                                                                                 |

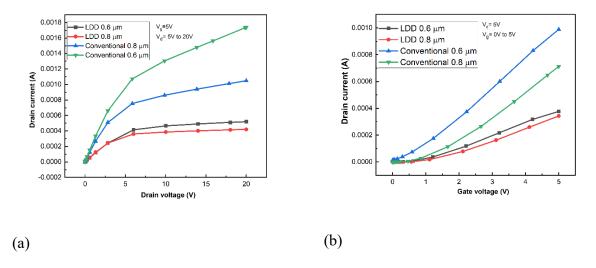

| Figure 4.3 (a) Comparison between I <sub>d</sub> V <sub>d</sub> of LDD and conventional NMOSFET, (b) Comparison between I <sub>d</sub> V <sub>g</sub> of LDD and conventional NMOSFET                                                              |

| Figure 4.4 $V_{th}$ roll-off comparison for LDD and conventional NMOSFET                                                                                                                                                                           |

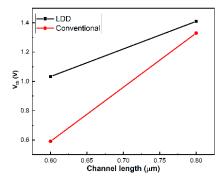

| Figure 4.5 (a) Comparison of e-field between conventional and LDD NMOSFET (0.8 μm), (b)<br>Comparison of e-field between conventional and LDD NMOSFET (0.6 μm)                                                                                     |

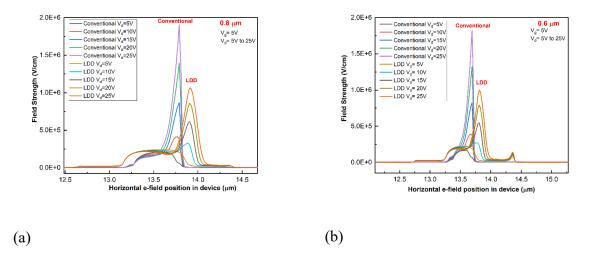

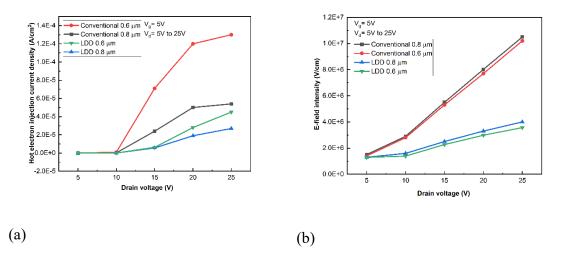

| Figure 4.6 Comparative analysis of (a) hot electron injection density, (b) e-field intensity between conventional and LDD NMOSFET (0.8 μm, 0.6 μm)                                                                                                 |

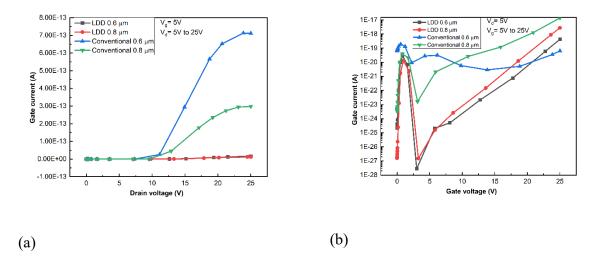

| Figure 4.7 (a) Comparative analysis of gate leakage vs. drain voltage between conventional and<br>LDD NMOSFET (0.8 μm, 0.6 μm), (b) Comparative analysis of gate leakage vs. gate<br>voltage between conventional and LDD NMOSFET (0.8 μm, 0.6 μm) |

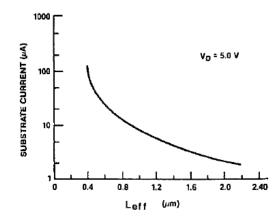

| Figure 4.8 Maximum substrate current vs. $L_{eff}$ for Si MOSFETs with $t_{ox} = 25$ nm [59]                                                                                                                                                       |

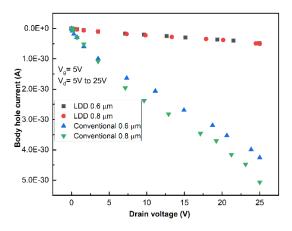

| Figure 4.9 Body hole current vs. drain voltage between conventional and LDD NMOSFET (0.8 μm, 0.6 μm)                                                                                                                                               |

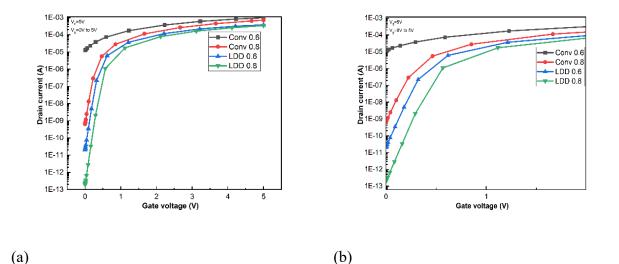

| Figure 4.10 (a) Comparative analysis of subthreshold characteristics of conventional and LDD<br>NMOSFET (0.8 μm, 0.6 μm), (b) Magnified region below the threshold voltage | 58 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

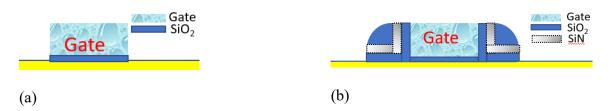

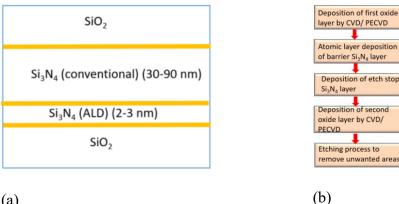

| Figure 5.1 (a) Gate without spacer, (b) Gate with spacer [63]                                                                                                              | 62 |

| Figure 5.2 (a) ONO spacer structure, (b) Proposed method of ONO spacer [62]                                                                                                | 63 |

| Figure 5.3 (a) Depth of nitrogen at 30 keV in SiC, (b) Ion range of nitrogen, (c) Depth of phosphorus at 30 keV in SiC, (d) Ion range of phosphorus                        | 66 |

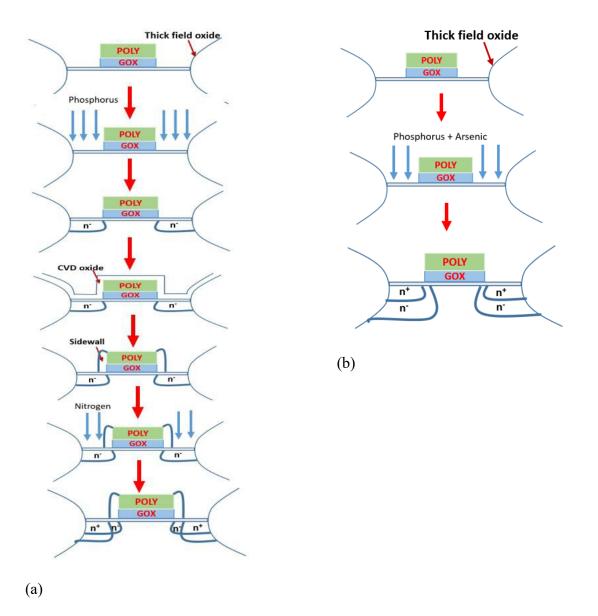

| Figure 5.4 LDD realization in Si (a) First Process, (b) Second Process                                                                                                     | 67 |

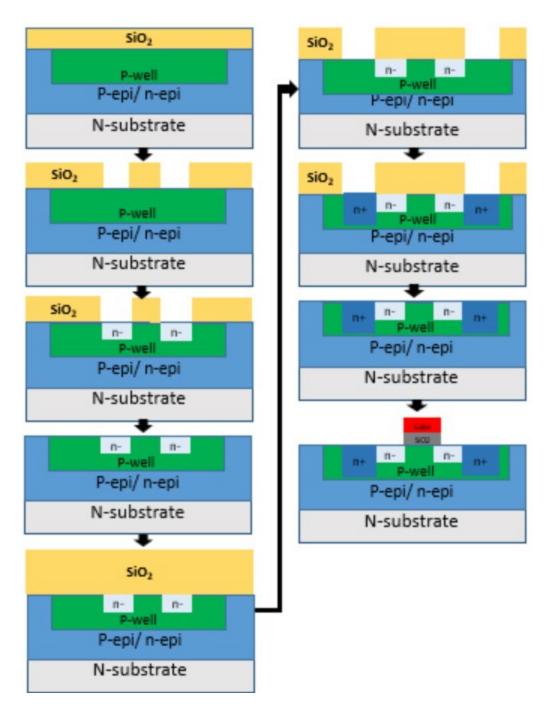

| Figure 5.5 Proposed non-self-alignment technique to realize LDD in SiC                                                                                                     | 70 |

# List of Tables

| Table 1.1 Material properties of SiC and other semiconductors [3]                                                                            | 2 |

|----------------------------------------------------------------------------------------------------------------------------------------------|---|

| Table 1.2 Scaling of MOS technology [11]    6                                                                                                | 5 |

| Table 1.3 Constant field and constant voltage scaling [15]    8                                                                              | 3 |

| Table 2.1 Process parameters used in Purdue CMOS [50]    26                                                                                  | 5 |

| Table 2.2 SiC processes    26                                                                                                                | 5 |

| Table 3.1 The channel length of NMOSFET                                                                                                      | 7 |

| Table 3.2 Comparison between e-field and hot electron density of 2 μm, 1 μm, 0.8 μm, and 0.6 μm channel length NMOSFET device                | ; |

| Table 4.1 The channel length of LDD NMOSFET                                                                                                  | ) |

| Table 4.2 Comparison between e-field and hot electron density of LDD NMOSFET vs.<br>conventional NMOSFET of channel length 0.8 μm and 0.6 μm | ł |

| Table 4.3 Comparison between subthreshold characteristics of conventional and LDD         NMOSFET         58                                 | 3 |

| Table 4.4 Comparison of device parameters between LDD and NMOSFET                                                                            | ) |

| Table 5.1 Purpose of each layer [62]    63                                                                                                   | 3 |

#### Chapter 1. Introduction

#### 1.1 Silicon Carbide as a Material

Silicon carbide (SiC) was discovered in 1824 by Jacob Berzelius, a scientist, famous for his discovery of silicon in Sweden [1]. During the experiment in his lab, he assumed a chemical bond between silicon and Carbon. Later in 1891, near Pittsburgh, Edward Goodrich Acheson, an American chemist, mixed silica and coke in a furnace and found one of the hardest and crystalline materials that can substitute diamond [1]. He named the material 'carborundum' as it was a compound of carbon and silicon and gave the proper formula as SiC. Two years later, in 1893, Henry Moissan found SiC as one of the rarest minerals on the earth in meteorite form and patented it as a highly effective abrasive [2]. According to his name, mineralogists termed it SiC moissanite [1]. To date, SiC is one of the best and most used abrasives in the world which has a hardness of 9.5/10 (on the Mohs scale), almost comparable to diamond where the diamond is the hardest material on earth having a hardness of 10. Not only as an abrasive, but SiC was also a part of many technological inventions such as light emitting diode (LED) in 1907, body armors, telescopes, and electronic elements, all of which share a form of SiC [1].

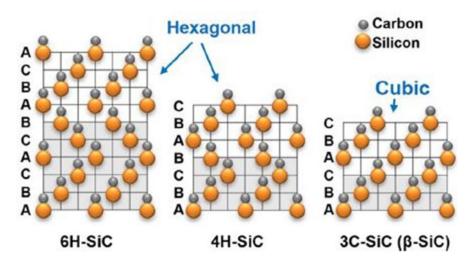

SiC has grabbed attention as a wide band gap material (WBG) due to its superior material properties compared to other rival materials used in the electronics industry. Depending on the sequence of silicon and carbon atom, SiC can have more than 250 polytypes out of which 6H-SiC, 4H-SiC, and 3C-SiC are the most popular [3]. Among these three, 4H-SiC is mostly used in the commercial perspective (as high power, high-frequency, and high-temperature device) due to its higher mobility, higher bandgap, isotropic nature, and availability of large wafer size.

Figure 1.1 The stacking sequence of 6H-SiC, 4H-SiC, and 3C-SiC [4]

Some material properties of SiC and other important semiconductors are summarized in Table 1.1 [3]. From Table 1.1, compared to Si, it can be seen that 4H-SiC has a three times wider bandgap ( $E_g$ ), three times higher thermal conductivity ( $\lambda$ ), two times higher saturation velocity ( $V_{sat}$ ), ten times higher critical e-field ( $E_c$ ). SiC has a unique advantage i.e. its native oxide (SiO<sub>2</sub>) can be thermally grown similar to silicon technology. Another major advantage of SiC MOSFET is as temperature increases from room temperature (25 °C) to 135 °C, its on-resistance increases by only 20% compared to Si MOSFET which increases by 250% [3].

| Material | Eg [eV] | n <sub>i</sub> [cm <sup>-3</sup> ] | €r   | $\mu_n  [cmV^{-1}s^{-1}]$           | Ec [MV/cm] | V <sub>sat</sub> [10 <sup>7</sup> cm/s] | λ [Wcm <sup>-1</sup> K <sup>-1</sup> ] |

|----------|---------|------------------------------------|------|-------------------------------------|------------|-----------------------------------------|----------------------------------------|

| Si       | 1.12    | $1.5*10^{10}$                      | 11.8 | 1350                                | 0.3        | 1.0                                     | 1.5                                    |

| Ge       | 0.66    | 2.4*10 <sup>13</sup>               | 16   | 3900                                | 0.1        | 0.5                                     | 0.6                                    |

| GaAs     | 1.4     | $1.8*10^{6}$                       | 12.8 | 8500                                | 0.4        | 2.0                                     | 0.5                                    |

| GaN      | 3.39    | 1.9*10 <sup>-10</sup>              | 9.0  | 900                                 | 3.3        | 2.5                                     | 1.3                                    |

| 3C-SiC   | 2.2     | 6.9                                | 9.6  | 900                                 | 1.2        | 2.0                                     | 4.5                                    |

| 6H-SiC   | 3.0     | 2.3*10 <sup>-6</sup>               | 10   | $370^{\rm a}, 50^{\rm c}$           | 2.4        | 2.0                                     | 4.5                                    |

| 4H-SiC   | 3.26    | 8.2*10 <sup>-9</sup>               | 9.7  | 720 <sup>a</sup> , 650 <sup>c</sup> | 3.0        | 2.0                                     | 4.5                                    |

| Diamond  | 5.45    | 1.6*10 <sup>-27</sup>              | 5.5  | 1900                                | 5.6        | 2.7                                     | 20                                     |

Table 1.1 Material properties of SiC and other semiconductors [3]

#### 1.2 Importance of SiC CMOS

A Complementary Metal Oxide Semiconductor (CMOS) is named as it uses two complementary transistors (PMOS and NMOS) in its circuits. In comparison to NMOS technology, although CMOS technology is more complex in terms of device physics and fabrication issues, it is still the most dominant integrated circuit (IC) technology. Unlike an NMOS inverter, in a CMOS inverter, only one transistor (either PMOS or NMOS) turns on at a time. That means when a CMOS inverter is not switching from one state to another state (high to low), a high impedance path exists from supply to ground. As a result, almost no current path exists and thus no dc power is dissipated. Another important feature of CMOS is when the inverter changes its state, the output (V<sub>out</sub>) swings fully (from V<sub>dd</sub> to 0 or 0 to V<sub>dd</sub>), which is referred to as rail to rail. The third advantage of CMOS is when V<sub>out</sub> swings from rail to rail, it gives excellent noise margins. The fourth advantage of CMOS is as CMOS devices dissipate less power, so the inherent heat generation is less which signifies a more reliable device. Usually, the packaging cost represents 25-75% of total chip manufacturing costs [5]. Since CMOS needs very low power so cheaper packaging technology can be used. Another major advantage is CMOS technology can give a 'static ratioless' logic design. It is termed 'static' because the gates are triggered by a data signal and do not need any external clock signal. Compared to NMOS which depends on the balance of the current ratio between transistors, CMOS design is termed as 'ratio less' because it does not depend on the geometric ratio of p and n-type transistors. A significant problem with NMOS is that its current ratio should be maintained when there is a change in temperature, power supply, and fabrication process. On the other hand, CMOS can give a temperature-independent logic level [6]. Silicon is still the dominant material in CMOS technology mainly due to its maturity of technology, wide research (more than 40 to 50 years),

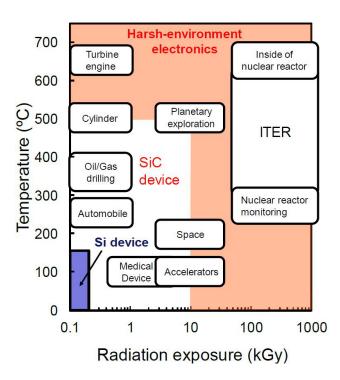

and low-cost wafers [7]. Although wide band gap technology like SiC is less mature than silicon technology, it is worth pushing the research due to several advantages. The first advantage is the demand for harsh environment electronics [8]. Harsh environment electronics signifies a system that can withstand harsh environments such as high- temperature, high pressure, high radiation, and corrosive gas environments. Such harsh environments can be found in space exploration, turbine engine, nuclear reactor, automobile sector, and so on. The plot in Figure 1.2 signifies the importance of SiC devices.

Figure 1.2. Demand for harsh environment electronics [8]

From Figure 1.2 it is clear that silicon technology cannot work at high temperatures. This is mainly because of the abundance of intrinsic carrier density in silicon devices at high temperatures. When the temperature crosses 300 °C, the number of the intrinsic carrier can exceed dopant carriers which signifies a reliability issue. At prolonged temperatures, silicon devices can be degraded or fail to operate and when temperatures cross 600 °C, it is impossible

to design any system with silicon technology [9]. Apart from that, at high temperatures, the control circuit has to reside in a cool area or needs an extra exhaust and cooling system. The cooling system can be air cooling or liquid cooling which adds extra cost and space to a system. In space aircraft, these extra overheads can pose a serious threat and reliability issues. Another significant advantage of SiC is its high-voltage transmission capability. The thickness of its drift region can be reduced by 10 times compared to the silicon device. As a result, SiC devices can be made smaller. Due to the small size of its drift region, the on-resistance decreases. The third advantage of SiC is circuit efficiency. The wide band gap and high breakdown voltage capability of SiC enable faster switching that improves system efficiency. Furthermore, due to the 100 times lower resistance and lower leakage current when the devices stay on and off, the energy losses are minimum compared to silicon devices. This is a significant advantage in hybrid electric vehicles where minimizing energy loss is important and complex cooling systems and heavy heat sinks are undesired. Among the WBG materials, gallium nitride GaN is a competitor of SiC, but SiC bulk crystal has fewer dislocation defects (order of magnitude lower) than GaN. So, SiC is more advanced in important technology areas such as making reliable ohmic contacts, and impurity doping, which are inevitable in CMOS technology. Apart from that, the ability to form native oxide (SiO<sub>2</sub>) makes SiC a reliable producer of MOSFET devices [9].

# 1.3 Importance of Technology Scaling

In the early 1970 scientists from IBM, Intel, and elsewhere decided that due to the production simplicity and low power consumption, MOSFET will facilitate the future growth of complex integrated circuits. This trend was recognized by Gordon Moore in 1965 at Intel. He stated that the number of transistors in an IC will be doubled every 24 months which became the driving force of the IC industry for the last 50 years or more. Due to this fact, the price of semiconductor

memory devices has dropped to 100 million times and the trend continues. This price drop has become the driving force behind new inventions of semiconductor devices. This is possible due to 'miniaturization' which means transistors and interconnects become smaller. Thus more circuits can be fabricated in a small wafer area which in turn reduces the cost, increases the speed, reduces the power consumption, and makes devices smaller and portable. Historically, a new technology node or new generation means a reduction of metal line width. Examples of some technology generation are 180 nm, 130 nm, 60 nm, 65 nm, and 45 nm technology nodes. At each new generation/ node feature size becomes 70% of the previous node. Eventually, 70% of the previous line width means almost 50% of area reduction (0.7 \* 0.7 = 0.49), so cost is reduced significantly [10]. On the other hand, historically it has been found that speed increases by around 30% more than its previous nodes in all generations [11].

| <b>MOSFET Technology</b> | <b>Production Year</b> | MOSFET Technology     | <b>Production Year</b> |

|--------------------------|------------------------|-----------------------|------------------------|

| (Gate length)            |                        | (Gate length)         |                        |

| 10 μm (2D technology)    | 1971                   | 65 nm                 | 2005                   |

| 6 µm                     | 1974                   | 45 nm                 | 2007                   |

| 3 µm                     | 1977                   | 32 nm                 | 2009                   |

| 1.5 μm                   | 1981                   | 22 nm (3D technology) | 2012                   |

| 0.8 μm                   | 1987                   | 14 nm                 | 2014                   |

| 0.6 µm                   | 1990                   | 10 nm                 | 2016                   |

| 350 nm                   | 1993                   | 7 nm                  | 2018                   |

| 250 nm                   | 1996                   | 5 nm                  | 2020                   |

| 180 nm                   | 1999                   | 3 nm                  | 2021                   |

| 130 nm                   | 2001                   | 2 nm                  | 2024 (future trend)    |

| 90 nm                    | 2003                   |                       |                        |

Table 1.2 Scaling of MOS technology [11]

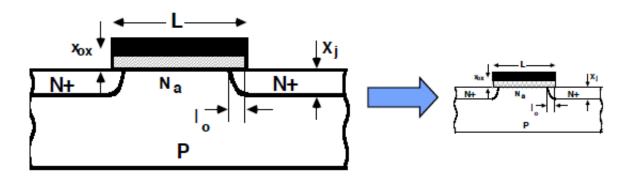

It can be said that scaling has been the most effective technique for the success of the Very Large Scale Integration (VLSI) industry [12]. This semiconductor scaling has been governed by Robert H. Dennard. In 1980, Dr. Dennard formulated some rules which are known as Dennard's law [13]. Silicon-based devices have been scaled by his classical scaling rules up to 2011. These rules are termed 'constant field scaling' and 'constant voltage scaling'. The details of 'constant field scaling' and 'constant voltage scaling' is mentioned in Table 1.3. In both approaches, device engineers take a device from a current generation and scale it horizontally (gate length) and vertically (junction depth, depletion width, gate oxide thickness) by the same factor. The main aim of this scaling is to get a scaled device that has the same transistor proportions.

Figure 1.3 Principle of MOSFET IC scaling [14]

When the voltage and all dimensions of a MOSFET are decreased by a factor ' $\alpha$ ' and charge densities and doping are increased by the same factor ' $\alpha$ ', the e-field remains constant. As a result, the circuit speed is increased by ' $\alpha$ ', and density increases by ' $\alpha^2$ '. This is known as constant field scaling. In the case of constant voltage scaling, all MOSFET dimensions are decreased by a factor ' $\alpha$ ' except the power supply and terminal voltage. As MOSFET's dimensions are scaled but the voltage is not scaled, this process can lead to some serious issues such as oxide breakdown, electrical stress, and electro-migration. On the other hand, in the case of constant field scaling, the terminal voltages and power supply gets scaled which leads to another type of problem. The reduction of voltage is not preferred because peripheral circuits and interfaces require a fixed voltage. As a result, multiple power supply is required which is not feasible in many cases. This is why constant voltage scaling is chosen in most cases.

| Parameter         | Symbol          | <b>Constant Field Scaling</b>                    | Constant Voltage Scaling |

|-------------------|-----------------|--------------------------------------------------|--------------------------|

| Gate length       | L               | $\frac{1}{\alpha}$                               | $\frac{1}{\alpha}$       |

| Gate width        | W               | $\frac{1}{\alpha}$                               | $\frac{1}{\alpha}$       |

| E-field           | E               | 1                                                | $\frac{1}{\alpha}$       |

| Oxide thickness   | t <sub>ox</sub> | $\frac{1}{\alpha}$                               | $\frac{1}{\alpha}$       |

| Substrate doping  | Na              | $\alpha^2$                                       | $\alpha^2$               |

| Gate capacitance  | Cg              | $\frac{1}{\alpha}$                               | $\frac{1}{\alpha}$       |

| Oxide capacitance | Cox             | α                                                | α                        |

| Transit time      | t <sub>r</sub>  | $\frac{1}{\alpha^2}$                             | $\frac{1}{\alpha^2}$     |

| Frequency         | f <sub>r</sub>  | α                                                | $\alpha^2$               |

| Voltage           | V               | $\frac{1}{\alpha}$                               | 1                        |

| Current           | Ι               | $\frac{1}{\alpha}$                               | α                        |

| Power             | Р               | $\frac{1}{\alpha^2}$                             | α                        |

| Power delay       | PΔt             | $\frac{\overline{\alpha^2}}{\frac{1}{\alpha^3}}$ | $\frac{1}{\alpha}$       |

Table 1.3 Constant field and constant voltage scaling [15]

The main purpose of scaling is to maximize current driving capability, mobility, and turnoff speed and at the same time, minimize output conductance. However, some of these properties are contradictory and depends on certain device application. Apart from that, the scaling theory proposed by Dennard has a lot of limitations such as it does not consider short-channel effects and the turn-off behavior of a transistor.

#### 1.4 Challenges in MOSFET Scaling

Although dimension scaling has a lot of advantages as mentioned in the previous section, a drastic reduction of dimension does not always give an expected result unless the following issues are taken care of. The main reason for this is depletion widths of the drain and source become comparable to the channel length of a MOSFET. One common observation is, due to the short channel length of the MOSFET, the drain current which is supposed to be constant in the saturation region, keeps increasing.

<u>Threshold voltage:</u> When a MOSFET is shrunk, the power supply voltage ( $V_{dd}$ ) has to decrease to keep the e-field and power dissipation within certain limits. On the other hand, threshold voltage ( $V_{th}$ ) cannot be decreased much because the higher portion of leakage current constitutes the majority of power dissipation. Therefore,  $V_{th}$  scaling needs to slow down to decrease off-state current ( $I_{OFF}$ ) [16]. On the other hand, circuit designers always want  $V_{th}$  to be invariant with biasing conditions and transistor dimensions.

<u>High electric fields:</u> The supply voltage ( $V_{dd}$ ) of a MOSFET cannot be reduced proportionally to the channel length. Thus, the electric field increases across the oxide (SiO<sub>2</sub>) layer. Due to higher e-field, carrier mobility decreases, and scattering increases. When the e-field increases significantly, it causes a breakdown in the oxide, increases leakage current, and eventually, the device is damaged.

<u>Gate oxide tunneling</u>: As MOSFET is scaled down, the ratio between electron thermal voltage (kT/q) and operating voltage reduces. This leads to a higher leakage current originating from the thermal diffusion of electrons [17]. Oxide thickness should be reduced in proportion to scaling, but when the oxide thickness is reduced too much, quantum tunneling occurs. This leads to an exponential increase in gate current which is unwanted [17].

<u>Parasitic resistance and capacitance:</u> The parasitic resistance and capacitance reduce unfavorably with transistor scaling [17]. Thus, the effects of parasitic elements reduce the performance gain obtained from transistor scaling which can lead to reduced drain current.

<u>The randomness of dopant distribution</u>: In smaller devices, it is not possible to place dopant atoms at accurate positions, which leads to the random orientation of the dopant atoms.

<u>Source to drain tunneling</u>: The channel length of a MOSFET means the distance between the source and drain. When the channel length becomes small enough, it is easier for the electrons to tunnel through the barrier even without gate bias. When this happens, the purpose of a transistor is not served i.e. it cannot act as a switch [18].

<u>Heat dissipation and interconnect delays:</u> When a MOSFET cannot dissipate heat properly to the resistive parts, hot spots can occur. This leads to an overheating of material, and eventually, the device comes to a failure. Due to scaling, the interconnect wire width is reduced which increases the resistance, thus delay is increased. [17].

<u>Hot carrier effect:</u> The carriers are termed 'hot' because when the carriers attain high energy, their effective temperature becomes greater than the lattice temperature. Due to this energy imbalance, carriers cannot release their energy to lattice atoms quickly. This is a significant problem of MOSFET operating in linear and saturation regions. In the Si device, the barrier height between Si-SiO<sub>2</sub> layers is 3.1 eV, whereas, for 4H-SiC, the barrier height between SiC-SiO<sub>2</sub> is 2.7 eV. That signifies that the chances of electrons crossing the barrier height for SiC devices are higher compared to Si devices.

#### 1.5 Thesis Goals

It has been clear that scaling is the future for any technology and that is why the silicon industry is flourished in the last 50 years. In 2022, Samsung unveiled 3 nm GAA technology in

silicon devices [19]. Also, they are focusing to bring 2 nm in 2025 and 1.4 nm in 2027. On the other hand, SiC is still in the micrometer  $(2 \mu m / 1.2 \mu m)$  range (discussed in chapter 2 of this thesis). So, SiC technology is still in its infancy which can be compared with silicon technology in the mid-1980s range. In the future, the SiC devices are expected to become more scaled i.e. they will enter into the sub-micron and then deep submicron range. Proper device design in those ranges can be necessary to rip the benefit of scaling. In parallel, the challenges of MOSFET scaling should be taken care of. Although SiC is popular in many areas such as in power electronics, high-temperature circuits, harsh environment sensing, and so on, research on low voltage areas is less explored or yet to be explored. Low voltage CMOS technology is of immense importance keeping complex circuit technology, reproducibility and cost in mind. In this thesis, a low-voltage SiC NMOS device in the submicron range (2 µm to 600 nm) is simulated and its key parameters and performance are analyzed. At the same time, hot carrier analysis is done and a new structure (using silicon topology) is proposed in SiC to mitigate hot carrier effects. In the end, the realization of this structure in terms of the CMOS process is proposed.

In Chapter 2 of this thesis, different SiC CMOS processes from foundries and other institutes are discussed to understand the current state of the art of SiC CMOS processes and their main differences. In addition, hot carrier effects on MOSFETs are discussed.

Chapter 3 provides a brief description of the tools used to simulate conventional 4H-SiC NMOSFET. Then, conventional devices are designed, characterized and results are discussed.

Chapter 4 provides simulations of the Low Doped Drain (LDD) structure in 4H-SiC to mitigate hot carrier issues. Then, LDD devices are characterized and results are discussed. The advantages and disadvantages of LDD are analyzed in the end.

Chapter 5 discusses prospective spacer technology, dopant species, and doping methods. Furthermore, a non self-alignment, and self-alignment technique to implement LDD structure in 4H-SiC CMOS is discussed.

Chapter 6 provides conclusions which include the summary, future work, and major roadblocks to implementing LDD design in the current CMOS process.

#### Chapter 2. Background and Literature Review

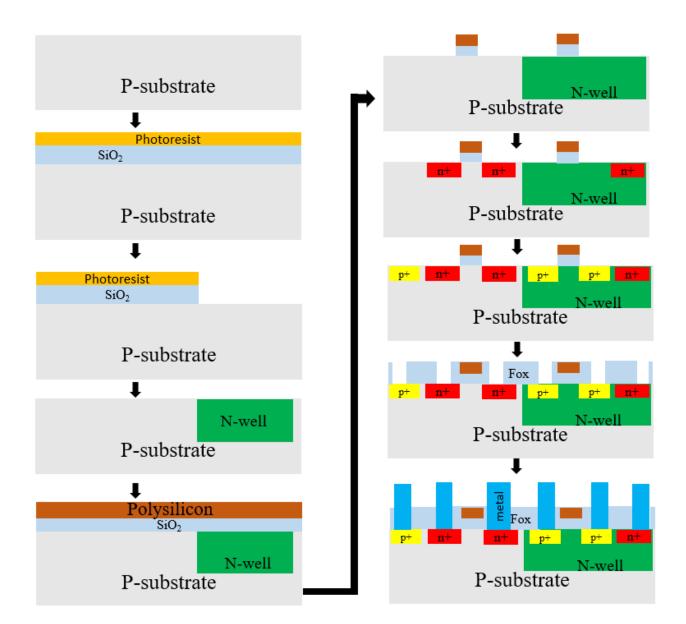

CMOS devices are used in many IC applications such as digital logic, memory devices, sensors, OPAMPs, and microprocessors. They are available for digital and mixed analog applications. The main aspect of any CMOS process is, a single substrate is capable of handling two complementary transistors (p-type/ PMOS and n-type/ NMOS). To understand a CMOS process, it is important to look into a standard silicon CMOS process first because the SiC CMOS process has evolved from the Si CMOS process. Then, the major differences between Si and SiC CMOS process will be highlighted. Gradually, SiC CMOS processes available from different manufacturers/institutes will be discussed to understand the current state of the art.

#### 2.1 CMOS Process Overview

The fabrication of the silicon CMOS process consists of a sequence of steps. In a single well process, it can consist of six masks: n-well, polysilicon, n+ diffusion, p+ diffusion, contacts, and a metal layer [20]. It can start with a p-type substrate, on top of which an n-well is made by the group - V dopant atoms. The wafer is oxidized at a high temperature to form oxide (SiO<sub>2</sub>) on the surface, and photoresist (organic material) is deposited on top of it. The oxide is patterned to form an n-well by an n-well mask and the photoresist is exposed through the n-well mask. This is called photolithography where the UV lights can only pass through where the well exists. Upon exposure to UV light, the photoresist (positive photoresist) gets softened and is removed to expose the oxide. The oxide is etched where it is not protected with photoresist. The remaining photoresist is stripped with piranha (mixture of H<sub>2</sub>O<sub>2</sub> and H<sub>2</sub>SO<sub>4</sub>) etching. Then, a thin oxide (SiO<sub>2</sub>) is grown on the surface of the wafer and placed in a chamber with Silane gas (SiH<sub>4</sub>) and heated to grow a polysilicon layer by CVD process. The wafer is then patterned with a photoresist and poly mask. The n+ region is introduced in the p-substrate and n-well through an

n+ diffusion mask after growing an oxide layer. Although ion implantation is used in recent times to implant n+, they are still known as diffusion. In the silicon CMOS process, source and drain junctions are automatically formed adjacent to the gate which is known as self-alignment. Then, the protective oxide is stripped off. For p-diffusion, the same process is repeated. A thick field oxide is grown to insulate the wafer and patterned with a contact mask. Then, a metal is sputtered over the contact cuts for making ohmic contact. Finally, metal is patterned with a metal mask. A plasma etch is used to remove metal everywhere except the contact area. Although the main structure and concept are the same for SiC CMOS, there are some major differences. In SiC, ion implantation is done at more than 500 °C and at such high temperature, no photoresist mask can exist. Thus, a metal mask or oxide mask is used. After the ion implantation process, high-temperature annealing (more than 1500 °C) is required for SiC to activate the dopants. At such high temperatures, polysilicon cannot exist because its melting point is around 1440 °C. Also, at such a high temperature, the quality of SiO<sub>2</sub>/oxide posed a question mark. For this purpose, self-alignment is not preferred by scientists in the SiC CMOS process.

The following sections are highlighting the differences between the SiC CMOS processes of different foundries and Institutes. Refer to Figure 2.1 for a cross-section processing diagram of the silicon CMOS process.

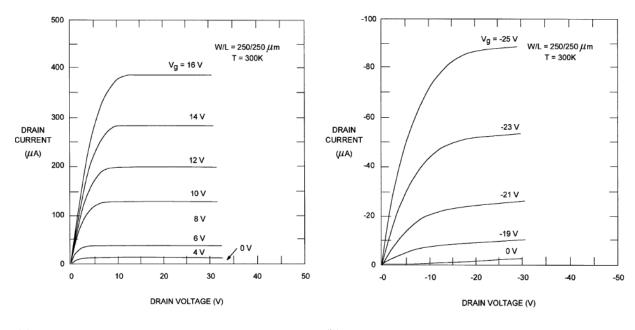

### 2.1.1 Cree CMOS

European patent (EP 0894339 B1) or US patent (US 6344663 B1) is a great source to review Cree's silicon carbide CMOS fabrication process in detail [21], [22]. Cree's CMOS process starts with a 6H-SiC p-type substrate of doping concentration 1e16 to 1e18. The preferred doping concentration of the p- epitaxial layer was 1e15 to 1e17. The well region was formed with a doping concentration of 1e15 to 1e17 by implanting nitrogen at 650 °C with energy 380 keV.

Figure 2.1 Basic CMOS Process (silicon) [20]

However, the temperature can vary from room temperature (RT) to 1300 °C and energy can vary from 250 keV to 1 MeV. The NMOS source (n+), drain (n+), and PMOS channel stop (n+) region were doped with nitrogen ion at 650 °C with a doping concentration of 1e17 to 1e20. This was done by multiple-step implantation where the energy range varied from 135 keV to 200 keV.

The wafer was then annealed at 1550 °C to activate the dopants. Next, PMOS source (p+), drain (p+), and NMOS channel stop (p+) implants were done with carrier concentrations

1e17 to 1e20. This was done by aluminum ion at an implanted temperature of about 1200 °C, but temperatures ranging up to 1300 °C can be used. Aluminum was used during multiple energy implants (energy up to 135 keV) to get an appropriate well depth. Ion implantation energy was chosen such that the depletion region of the source and the drain should not exceed the substrate region. Then the wafer was thermally annealed at 1550 °C to remove surface damage and the resulting oxides were stripped. The gate dielectric (SiO<sub>2</sub>) was deposited and then placed in an oxidized ambient for several hours before the deposition of gate metal. This process is called reoxidization and this is one of the key steps in Cree's CMOS process [23]. Re-oxidization helps to densify the oxide by oxidizing impurities such as residual carbon and dangling silicon bonds. Reoxidization also improves the oxide layer to become C/ SiC free; increases the dielectric strength of SiO<sub>2</sub> (11-12 MV/cm) and increases breakdown voltage [23]. According to Cree, as most MOSFETs face reliability issues in their oxides, a dense oxide layer is important as it strengthens the gate overlap region. Reoxidation is significant in another sense. 'Self-alignment' which is common in silicon devices, is not common in SiC. The source and drain are implanted before the gate by the ion implantation process. As a result, the surface of SiC becomes poor due to heavy implantation. So, when dielectric strength is not strong, it increases the oxide failure in the gate overlap region. According to them, the poor dielectric strength is the result of impurity segregation, rough SiC-SiO<sub>2</sub> interface, or non-stoichiometric growth. They mentioned that deposited oxide acts better than thermally grown oxide. When oxide is thermally grown it is important to consider the face. If the oxidation is in the carbon (C) face then the temperature requirement is less (900 °C - 1300 °C) than silicon (Si) face (1000 °C - 1400 °C) because C oxidizes faster than Si. The best result they got for oxidation was at around 1050  $^{\circ}C - 1100 ^{\circ}C$ . Similarly, in the case of re-oxidization, their preferred temperature is 950 °C in the presence of

water (H<sub>2</sub>O). On the other hand, in PMOS, usually, aluminum was used as a dopant and this aluminum creates a gate leakage path at a higher temperature. This problem was solved by the re-oxidization process. Molybdenum (preferable) or aluminum was used as gate material and nickel was used to create simultaneous ohmic contact in NMOS and PMOS. The contacts were annealed at 825 °C for 2 minutes. The interconnect metallization was formed by molybdenum. Then contact pads were formed with a platinum layer and a gold layer. Finally. The entire device was covered by a protective layer of SiO<sub>2</sub> or Si<sub>3</sub>N<sub>4</sub>. An operational amplifier was demonstrated in a 6H-SiC circuit with epilayer doping concentration of 6e15 to 6e16 and thickness of 3-5  $\mu$ m. 15V power supply or V<sub>DD</sub> was used. The carrier concentrations of n+ and p+ were 1e19 cm<sup>-3</sup> and 1e18 cm<sup>-3</sup> and the depths were 0.35  $\mu$ m and 0.25  $\mu$ m respectively. The gate widths were 25 to 200  $\mu$ m and gate lengths were 2 to 8  $\mu$ m. The threshold voltage of NMOS was 2.5 volts and that of PMOS was -15 to -17 volts. The open loop operational gain of the amplifier was 10<sup>4</sup> or 80 dB.

(a)

(b)

(c)

Figure 2.2 Cree CMOS (a) NMOS I-V characteristics, (b) PMOS I-V, (c) Doping profile of nwell showing nitrogen concentration [22]

# 2.1.2 Hitachi CMOS

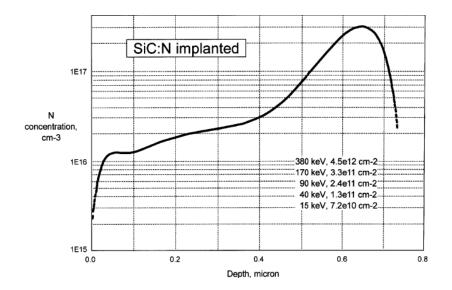

Hitachi Ltd. demonstrated buried channel (BC) MOSFET where their main focus was on channel mobility [24], [25]. It is believed that at the SiO<sub>2</sub>/ SiC surface, a high density of traps exists. As a result, the channel mobility is extremely low in 4H-SiC MOSFET. Hence, their main focus was shifting the channel from the surface to the body of MOSFET. As a result, they got higher electron mobility (140 cm<sup>2</sup>/ Vs) compared to standard inversion channel mobility which is  $25 - 35 \text{ cm}^2$ / Vs [26]. In their structure, the MOSFET's channel length and widths were 100 to  $150 \text{ }\mu\text{m}$  [24]. The buried channel was formed by nitrogen ion (N<sup>+</sup>) at room temperature implantation at a depth of 0.2 µm followed by annealing at 1500 °C. This is almost similar to Cree's process. Another noticeable point in their process is that they also mentioned the importance of wet re-oxidation (after gate oxide is grown by dry oxidation step) which significantly improves channel mobility.

Figure 2.3 (a) Schematic cross-section, (b) Field effect mobility of Hitachi's 4H-SiC BC MOSFET [24]

Apart from BC MOSFET, Hitachi focused their research on radiation resistance technology with SiC after the incident in Fukushima. They have demonstrated CMOS technology and radiation performance of op-amp. In their MOSFET, gate length and width were 100  $\mu$ m and 200  $\mu$ m. In terms of the circuit, where they have demonstrated op-amp, the length (Lg) of NMOS and PMOS was 10  $\mu$ m and 20  $\mu$ m [27]. In one of their recent work, they fabricated a trans-impedance amplifier (TIA) to measure gamma irradiation resistance [28]. They have used 8 nm thin gate oxide to reduce threshold voltage (V<sub>th</sub>). The length and width of NMOS and PMOS were 5  $\mu$ m and 400  $\mu$ m respectively. They have also reduced leakage current (42% less than conventional) during higher gamma radiation by their structure, but their main focus was making a heat and high radiation resistance technology [29].

# 2.1.3 NASA & CWRU JFET

As mentioned in the first chapter that SiC is famous for its high-temperature application and that is one of the selling points of this material. NASA has demonstrated ICs that are capable of operating at higher temperatures up to 1000 °C for a prolonged period [30]. As their main target was space exploration and extremely high temperatures (such as on Venus), making a reliable device was important. For that reason, they explored JFET instead of MOSFET as JFET is an oxide-free device, and maintaining the quality of oxide at very high temperatures is difficult. The feature size of their JFET was 24  $\mu$ m / 6  $\mu$ m [30]. In another type of work, they focused not only on the extremely high temperature but also on the lower temperature (from -190 °C to +812 °C). Such temperature can be seen in arctic conditions where an aircraft engine consisting of SiC circuits can perform at a lower temperature such as -55 °C [31].

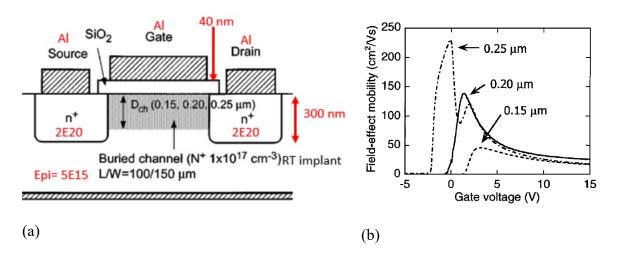

A similar kind of structure which is developed by NASA Glenn Research Center is fabricated by researchers from Case Western Reserve University (CWRU). Their W/L ratio of JFET was 100  $\mu$ m / 10  $\mu$ m [32]. Unlike MOSFET, one thing that is noticeable in this structure was the existence of three epi-layers (7  $\mu$ m, 0.3  $\mu$ m, 0.2  $\mu$ m). The doping level of the gate epi layer was two magnitudes higher than the channel (10<sup>19</sup> compared to 10<sup>17</sup>). This higher doping ensures the formation of a depletion layer in the n-epi layer when a reverse bias is applied to the gate terminal. Figure 2.4 shows the cross-section of 6H-SiC JFET.

The threshold voltage of this device is -4V which ensures complete pinch-off (depletion width becomes 0.324  $\mu$ m) of the channel and signifies the operation of JFET. Another significant step is, the gate is mesa etched (compared to MOSFET where the polysilicon gate is deposited) which ensures a defect-free gate and does not require activation at high temperatures [33].

Perhaps one of the significant differences which are embedded in this structure is the presence of a shallow low-doped region (in the 0.3  $\mu$ m layer by phosphorus atom @130 keV at room temperature implant). This also can be done by nitrogen atom @70 keV. In both cases, the dose of ion implantation is 7e12 cm<sup>-2</sup>. The main reason for this shallow low doped region is to reduce the e-field between the gate and source/ drain. This shallow low doped region also

Figure 2.4 (a) Schematic cross-section of CWRU 6H-SiC JFET [32], (b) Simplified cross-section of NASA 6H-JFET [33]

helped to reduce parasitic resistance [33]. On the other hand, like silicon scaling, CWRU researchers have mentioned the importance of channel length and feature size reduction to improve the performance of the JFET device [34]. However, JFET is a normally-on device, so despite providing lower on-resistance, the higher leakage of this device makes it less popular than MOSFET.

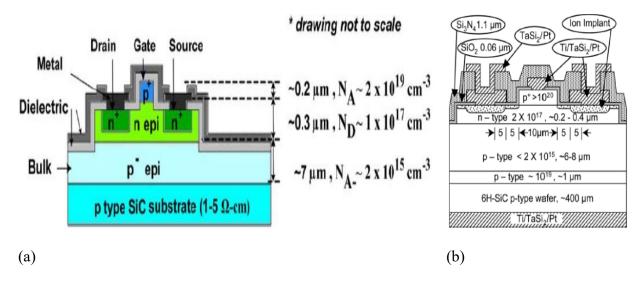

# 2.1.4 Raytheon CMOS

Raytheon Systems Limited has demonstrated 1.2  $\mu$ m 4H-SiC technology called hightemperature silicon carbide (HiTSiC<sup>®</sup>) for logic and mixed-signal ICs, however, this technology was discontinued in 2018 [35]. Their technology was mainly developed to operate at 15V at high temperatures up to 400 °C - 450 °C [36], however, they have observed excessive gate leakage (shown in Figure 2.5 (b) when the temperature crosses 350 °C [37]. They have demonstrated an inverter, NAND gate, and ring oscillator [37] in their process. Using this 1.2  $\mu$ m Raytheon process, Dr. Mantooth's group from the University of Arkansas has demonstrated a comparator, current, and voltage references, gate driver, and 8-bit digital-to-analog converter (DAC) [38]– [41]. Raytheon's main aim was to develop a process that can work in high temperatures and prolonged hours (7500 hours). For that reason, they have mentioned the use of a carbon cap during the annealing process after ion implantation and threshold implant [36]. The channel length of their designed transistors was between 20 µm to 1 µm where a short channel effect was observed with gate lengths below 1.2 µm. To overcome the short channel effects they tried high well doping which degraded the channel mobility of the device [42]. Nickel was used as an ohmic contact in both the p+ and n+ regions. Aluminum (1.02e17 cm<sup>-3</sup>) and nitrogen (1.5e17 cm<sup>-3</sup>) was used as p-channel and n-channel dopant respectively which is common in the previously mentioned CMOS processes. They pointed out that minimization of ion implantation energy can result in a good quality device. Also, they pointed out that a 4-degree off-axis along <1120> direction is better than on-axis orientation along {0001} planes or 8 degrees off-axis towards {0001} or <1120> planes [43]. Another important observation of their structure is that they have used the full depth of the epitaxial layer to fabricate different devices. As an example, when they use a p-type substrate and they need n-conductivity in the p-type substrate, they used very high implant energy (as high as 2 MeV). This is to ensure that the n-conductivity region extends the full depth of the epitaxial layer and touches the p-type substrate (vice versa is also true). By doing this, they ensured p-type epitaxial layer becomes discontinuous in the lateral direction [43]. This serves the purpose of isolation. Apart from this, they have demonstrated BiCMOS technology which consists of CMOS and bipolar transistor (npn / pnp) in a single IC [43].

Figure 2.5 (a) Raytheon's CMOS process architecture, (b) Gate current vs. gate voltage for 20\*1.2 μm NMOS [37]

# 2.1.5 Fraunhofer CMOS

Fraunhofer Institute for Integrated System and Devices Technology (IISB) reported 6 μm SiC CMOS technology where they used 1-2 μm n-type epilayer (1e18 cm<sup>-3</sup>) as a buffer layer and then again 8 μm n-type epilayer (5e14 cm<sup>-3</sup>) as a top layer [35]. They have used well-known silicon topologies to define their CMOS circuit [44]. N and P are used as dopants for the well and source and drain. The annealing temperature (1700 °C) is almost the same as what is being used in earlier mentioned processes. 50 nm thick gate oxide and 400 nm thick field oxide was used. 500 nm polysilicon layer was used as a gate. 80 / 300 nm Ti / Al stack was used as an ohmic contact in the p+ and 50 nm Ni / Al was used as an ohmic contact in the n+ region [35]. They have investigated ohmic contacts with some other materials also such as Ni/Ti/Al/W and checked the formation of silicides at different temperatures [45]. Their metallization was done with 50 nm/ 700 nm/ 20 nm using Ti/Al/Ti stack which helped to reduce their thermal budget. This 6 μm technology was built to operate at 20V supply voltage [35].

Figure 2.6 (a) Fraunhofer's CMOS process architecture [46], (b) Field effect mobility of NMOS and PMOS with and without channel implant [46]

In some research work that was published using Fraunhofer's devices, the importance of channel implants was pointed out (2e13 cm<sup>-2</sup> with Al @35keV for PMOS). This channel implant helped them to shift the threshold voltage from –5V to -3.6V [47]. For NMOS, nitrogen was used as a channel implant (5e13 cm<sup>-2</sup> @20keV) [46] (as shown in Figure 2.6 (b)). In one research, the propagation delay of SiC devices was compared with silicon technology where they showed propagation delay was 17 times longer than Si devices at a p-well doping concentration of 1e15 cm<sup>-3</sup>. The speed of the device was limited due to the lower mobility of pMOS at room temperature and higher temperatures (300 °C). The delay was seen to be 32 times when the well doping concentration is increased to 8e15 cm<sup>-3</sup> [48]<sup>.</sup>

Recently, Fraunhofer offered early access to its 2 µm SiC CMOS technology in a twin well technology [49]. Their circuits are capable of working at high temperatures of up to 600 °C. They have also worked on process modules capable of working at high voltages and harsh environments. They have mentioned using one poly and two metal (Pt) layers [49] and the oxides are capable of handling 20V. Fraunhofer only uses thermal oxidation for their oxide growth and annealing, but they did not mention wet re-oxidation in their process.

## 2.1.6 Purdue CMOS

Dr. Kornegay himself and his research group demonstrated significant process development in SiC devices. Researchers under him demonstrated a 6H-SiC CMOS process where a lightly doped epilayer ( $5e15 \text{ cm}^{-3}$ ) was used on a heavily doped n+ substrate [50]. After cleaning, they oxidized the wafer at 1200 °C in an O<sub>2</sub> environment for 30 minutes. One of the key differences in this process is the use of a hard mask. They used Ti / Au mask ( $20 \text{ nm} / 1 \mu \text{m}$ ) and used six-step implantation with Boron (B) at 650 °C to form a p-well. The total dose to form p-well was 2.5e14 cm<sup>-3</sup> (20 keV/4.5e12, 45 keV/7.5e12, 85keV/1.1e13, 140keV/1.7e13, 230 keV/3e13, 380keV/1.8e14) [50]. B was used as p-channel implant (25keV/ 8e12, 60keV/1.8e13) at 650 °C and N is used as n-channel implant at 650 °C (260KeV / 6e12). The surface was covered by Ti (20 nm) and Au (470 nm) mask and then pMOS source and drain implant were done by Al with dose 2.2e15/cm<sup>2</sup> (45 keV/2.2e14, 90 keV/3.4e14, 160keV/5.4e14, 270keV/1.1e15). Again, Ti (20 nm) and Au (470 nm) was used as nMOS mask and N was used as an implant with dose 1.05e16/cm<sup>2</sup> (40 keV/2.5e15, 90 keV/3e15, 160keV/5e15). 1550 °C temperature was used in the Ar environment for annealing. Wet oxidation was used at 1150 °C for 1 hour to grow gate oxide followed by 30 minutes of Ar anneal.

The polysilicon gate was deposited by LPCVD in the presence of silane gas for 30 minutes. Then polysilicon was doped with boron followed by dopant dive in at 900 °C for 50 minutes in nitrogen and oxygen flow. 50 nm Al and 20 nm Ni were grown by a thermal evaporator and used as p-type contact and n-type contact respectively. The isolation of the device was done by 200 nm Si<sub>3</sub>N<sub>4</sub> grown by RTA at 850 °C for 5 minutes. Refer to Table 2.1 for process parameters used in Purdue CMOS.

| Parameter                    | NMOS                                           | PMOS                                  |

|------------------------------|------------------------------------------------|---------------------------------------|

| Gate Oxide thickness         | 285 °A                                         |                                       |

| Interface state density      | $4.2 * 10^{11} \text{ eV}^{-1} \text{cm}^{-2}$ |                                       |

| Fixed charge density         | $1.0 * 10^{12} \text{ cm}^{-2}$                |                                       |

| Substrate concentration      | $1.3 * 10^{17} \text{ cm}^{-3}$                | $5 * 10^{15} \text{ cm}^{-3}$         |

| Long channel V <sub>T</sub>  | 2.6 V                                          | -6.7 V                                |

| Channel mobility             | 8 cm <sup>2</sup> /Vs                          | 5.87 cm <sup>2</sup> /Vs              |

| Source/ drain junction depth | 3000 °A                                        | 3500 °A                               |

| S/D sheet resistivity        | 3.1 kΩ/sq.                                     | 120 kΩ/sq                             |

| Specific contact resistivty  | $1.65 * 10^{-4} \Omega \text{cm}^{-2}$         | $2.9 * 10^{-2} \Omega \text{cm}^{-2}$ |

Table 2.1 Process parameters used in Purdue CMOS [50]

In their research, they used e-beam to pattern their submicron channel lengths. The rest of their fabrication was processed by optical lithography. The channel length of their CMOS was 0.8 µm [50]. As their study was based on sub-micron devices, they mentioned the importance of hot carrier effects in devices having thin gate oxide. However, the reliability of the device was unexplored [50]. They also mentioned the importance of low doped drain (LDD) in sub-micrometer MOSFET which requires more in-depth study. Dr. Kornegay's group has demonstrated an 11-bit ring oscillator, NANO, NOR, ExNOR, and Ex-OR gates.

Table 2.2 shows the summary in terms of the gate length of the SiC CMOS processes.

| Table 2.2 SiC proc | cesses |

|--------------------|--------|

|--------------------|--------|

| Inventors       | MOSFET Technology | <b>Production Year</b> | References |

|-----------------|-------------------|------------------------|------------|

|                 | (Gate length)     |                        |            |

| Cree CMOS       | 2 to 8 μm         | 2002                   | [21], [22] |

| Hitachi CMOS    | 100 μm            | 2001                   | [24]       |

| NASA JFET       | 6 μm              | 2018                   | [30]       |

| CWRU JFET       | 10 μm             | 2014                   | [32]       |

| Raytheon CMOS   | 1.2 μm            | 2014                   | [37]       |

| Fraunhofer CMOS | 2 μm              | Early Access           | [49]       |

| Purdue CMOS     | 0.8 μm            | 1998                   | [50]       |

As this thesis is focused on SiC advanced CMOS process in the submicron range, and in that range, one of the prominent issues is hot carrier effects. The next section will discuss the basics of hot carrier effects in MOSFET and its mitigation processes. Among many solutions, one prospective solution will be considered and discussed thoroughly.

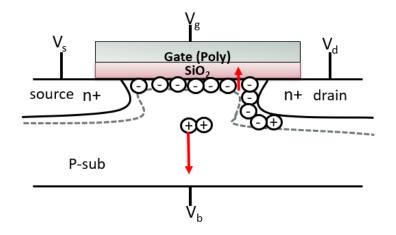

#### 2.2 Hot Carrier Effects in MOSFET

When device dimensions are decreased but supply voltage remains constant, the lateral electric field in the MOS device increases. When the electric field ( $E_M$ ) becomes too strong then carriers become energetic, thus they are termed as 'hot'. Carriers are of two types in MOSFETs – electrons and holes. So, two types of effects are possible - hot electron effects and hot hole effects. Hot electron effects are more serious than hot hole effects because of electrons' high mobility compared to holes. For this reason, hot electron effects are more serious in NMOSFETs as the carriers are electrons, and the channel is formed by them. From the operation perspective, when a MOSFET goes into the saturation region, the electric field ( $E_M$ ) becomes high near the drain. The calculation of  $E_M$  is complex [5] as it depends on the two-dimensional Poisson equation. However, the calculation of  $E_M$  can be written as

$$E_{M} = \frac{V_{d} - V_{dsat}}{m}$$

Equation 2.1

where  $m = 0.22 t_{ox}^{\frac{1}{3}} r_{J}^{\frac{1}{3}}$  for  $t_{ox} \ge 15 nm$ ;

or  $m = 1.7 * 10^{-2} * t_{ox}^{\frac{1}{3}} r_{J}^{\frac{1}{3}} L^{\frac{1}{5}}$  for  $t_{ox} < 15 nm$  and  $L < 0.5 \mu m$

From Equation 2.1, it can be seen that  $r_J$ ,  $t_{ox}$ , and L is inversely proportional to  $E_M$ . Thus, as the device dimension shrinks,  $E_M$  increases. This high  $E_M$  energizes electrons by supplying more kinetic energy. Thus they become 'hot'. This hot electron causes several effects in the

MOSFETs. Due to the high e-field, when electrons gain sufficient energy, they can lose their energy by creating other carriers. This process is known as impact ionization. The total number of carriers generated by impact ionization is equivalent to the reciprocal of e-field  $(1/E_M)$ . When

Figure 2.7 Hot carrier (electrons and holes) generation [50]

the generation of carriers reaches an extreme, it can lead to avalanche breakdown [5]. The first effect that can be seen due to the hot carrier is the generation of substrate current. Generally, electrons are attracted towards the drain (due to positive bias) and add drain current whereas the holes enter the substrate and create parasitic substrate current. These holes sometimes when absorbed by the source, can lead to a voltage drop and becomes a major reason for snapback breakdown. Excess amounts of substrate current can induce latch-up in CMOS circuits. The second effect that can be seen by hot carriers is gate leakage. Some of the carriers can move towards the gate electrode and produce gate leakage current (usually, in the pA  $(10^{-12})$  or fA  $(10^{-15})$  range), which is undesired. Sometimes, hot carriers cannot reach the gate electrode as they are absorbed by oxide vacancies or traps. As a result, negative charge density is created in the oxide layer, and thus threshold voltage (V<sub>th</sub>) deviates (V<sub>th</sub> increases for nMOS device). This situation sometimes leads to a permanent V<sub>th</sub> shift. The third effect, visible from the hot electron is device

degradation. From the Shockley equation [51], the amount of drain current in the cut-off, linear, and saturation regions can be mentioned as follows:

$$I_{ds} = 0$$

when  $V_{qs} < V_{th}$  i.e. at cutoff Equation 2.2

$$I_{ds} = \beta \left( V_{GT} - \frac{V_{ds}}{2} \right) V_{ds} \text{ when } V_{ds} < V_{dsat} \text{ i.e. at linear}$$

Equation 2.3

$$I_{ds} = \frac{\beta}{2} V_{GT}^2 \text{ when } V_{ds} > V_{dsat} \text{ i. e. at saturation}$$

Equation 2.4

Where  $V_{GT} = V_{gs} - V_{th}$ ,  $\beta = \mu C_{ox}W/L$ ,  $C_{ox} = \epsilon_{ox} / t_{ox}$  which is also termed as capacitance per unit area of the gate oxide.

As  $V_{th}$  increases,  $V_{GT}$  will decrease, so the saturation current  $(I_{ds})$  decreases. Again, when substrate leakage increases, transconductance  $(g_m)$  decreases. On the other hand, due to the accumulation of trapped charges in oxide, device performance becomes unacceptable after a certain period. When a large amount of substrate current accumulates, the device lifetime gets shortened (depending on the 10% degradation rule on  $g_m$ ) [5].

The next section discusses the mitigation processes of hot carrier effects.

## 2.2.1 Mitigate Hot Carrier Effects

Several techniques can be applied to mitigate hot carrier effects [5]. They are:

- The voltage applied across the device can be reduced, however, this solution is out of the scope of any designer or fabricator. So, this is not a possible solution.

- The stress time of the device can be decreased, however, this is not a possible solution like the previous one because this option belongs to a user.

- Appropriate drain design techniques like Double diffused drain (DDD) and Low doped drain (LDD). However, among these two, DDD is less effective in short-channel devices due to its higher overlap capacitance and deep source and drain junctions [5].

- The density of trapping oxide can be reduced which means deploying another oxide than SiO<sub>2</sub> which is out of the scope of this research.

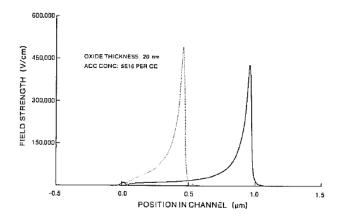

- 2.2.2 Low-Doped Drain

Lightly doped drain or (LDD) has been used extensively in silicon devices (Twin tub IV  $(L_{eff}=1 \ \mu m)$ , twin tub V  $(L_{eff}=0.75 \ \mu m)$ , twin tub VI  $(L_{eff}=0.4 \ \mu m)$ ) when the channel lengths are less than 2  $\mu m$ . The purpose of this design is that it can absorb some of the electric fields to the drain, so  $E_M$  reduces.

Figure 2.8 (a) E-field at Si-SiO<sub>2</sub> interface, (b) Doping profile LDD vs. conventional structure [52]

LDD structure is accompanied by a conventional structure where two doped regions are used (the lightly doped region and the heavily doped region as shown in Figure 2.8 (b), whereas conventional drain structure consists of only one region i.e. high doped region as shown in Figure 2.8 (a). From Figure 2.8 (a), it can be seen that in the LDD structure, the electric field intensity is reduced and also the peak position is shifted towards the drain. Figure 2.8 (b) shows the doping profile of conventional and LDD structures. In the LDD structure, the n+ region is doped with arsenic (As) with a dose of 1e15 cm<sup>-3</sup>, called highly doped, and the low doped region is doped with phosphorus with a dose of 1e13 cm<sup>-3</sup>. In the conventional structure, only As is used with a dose of 1e15 cm<sup>-3</sup>. Research says that for a silicon 5V device, the LDD structure can reduce substrate leakage as high as 90% [53].