#### DIPARTIMENTO DI INGEGNERIA DELL'INFORMAZIONE

#### CORSO DI LAUREA MAGISTRALE IN INGEGNERIA ELETTRONICA

#### "Device physics and failure mechanisms of deep submicron gate GaN HEMTs for microwave and millimeter-wave applications"

Relatore: Ch.mo Prof. Enrico Zanoni

Laureando: Andrea Carlotto

ANNO ACCADEMICO 2022 – 2023 Data di laurea 05 settembre 2023

#### DIPARTIMENTO DI INGEGNERIA DELL'INFORMAZIONE

#### CORSO DI LAUREA MAGISTRALE IN INGEGNERIA ELETTRONICA

#### "Device physics and failure mechanisms of deep submicron gate GaN HEMTs for microwave and millimeter-wave applications"

Relatore: Ch.mo Prof. Enrico Zanoni

Laureando: Andrea Carlotto

ANNO ACCADEMICO 2022 – 2023 Data di laurea 05 settembre 2023

## Contents

| Chapter 1: Gallium Nitride                                    | 1  |

|---------------------------------------------------------------|----|

| 1.1 Beyond the limits of silicon: gallium nitride             | 1  |

| 1.1.1 Optical Properties                                      | 2  |

| 1.1.2 High-Power behaviour                                    | 5  |

| 1.1.4 High-frequency operation                                | 7  |

| 1.2 Spontaneous and Piezoelectric polarizations               | 9  |

| Chapter 2: GaN-based High Electron Mobility Transistor (HEMT) | 13 |

| 2.1 Introduction to traditional FET devices                   | 13 |

| 2.2 Advanced FET devices: GaAs HEMTs                          | 14 |

| 2.3 Advanced FET devices: GaN HEMTs                           | 16 |

| 2.4 Johnson's figures of merit                                | 21 |

| 2.5 Epitaxial Structure Implementations                       | 23 |

| 2.5.1 Substrate                                               | 23 |

| 2.5.2 Nucleation layer                                        | 24 |

| 2.5.3 Buffer layer                                            | 25 |

| 2.5.4 Barrier layer and cap layer                             | 25 |

| Chapter 3: Stability and Reliability issues                   | 27 |

| 3.2 Stability and Reliability Issues                          | 27 |

| 3.2.1 Stability issues, related to trapping effects           | 28 |

| 3.2.2 Stability issue and device degradation mechanisms       | 32 |

| 3.3 Short Channel Effects                                     | 35 |

| Chapter 4: Laboratory activity                                | 38 |

| 4.1 Device Under test: QORVO                                  | 38 |

| 4.          | .2 Characterization of the devices | 42 |

|-------------|------------------------------------|----|

| 4.          | .3 Laboratory instruments          | 45 |

| 4.          | .4 Experimental set-up             | 53 |

|             | 4.4.1 DC Analysis                  | 53 |

|             | 4.4.2 Double-Pulse Analysis        | 57 |

|             | 4.4.3 Vth-transient measurements   | 61 |

| Chapter 5:  | QORVO devices                      | 65 |

| 5.          | .1 DC analysis                     | 65 |

|             | 5.1.1 DC statistics                | 66 |

|             | 5.1.2 DC characteristics:          | 69 |

| 5.          | .2 Double pulse analysis           | 76 |

| 5.          | .3 DC go and back analysis         | 88 |

| 5.          | .4 Vth transient                   | 93 |

| Chapter 6:  | Conclusi ons                       | 01 |

| Bibliograph | hy10                               | 06 |

### Abstract

This thesis presents the findings of a comprehensive characterization study on GaNbased, gate-scaled HEMTs for RF applications. The samples considered in the study are Ga-polar devices which differentiate for: (1) the adoption of substrates produced by different device supplier, (2) the presence of a back-barrier, and (3) the aluminum concentration in the back-barrier. The investigation considers performance, stability, and reliability aspects; more in detail, the analysis was focused on the investigation of the deep levels presents in the different epitaxial structures, with the aim of evaluating how the presence of a back-barrier with different Al concentration affected them. For each technology, static and dynamic measurements were conducted on the devices under test; this involved double-pulse, and V<sub>TH</sub> transient measurements performed stressing the devices both in OFF- and semi-ON-state. The observed results were compared with those reported in the literature to determine the nature and location of the traps responsible for performance variations and identify them. In the end, the results obtained showed that the devices without a back-barrier presented a greater dispersion due to the interaction with the buffer trap states (carbon and iron). On contrary, the devices with a back-barrier were able to effectively screen the traps in buffer, even though other traps were found. Further analysis are required in order to discover the nature of those traps but they seems related to the presence of interface states between the back-barrier and the GaN channel interface. This research provided the first systematic study of the impact of back-barriers on the deep levels in a HEMT devices, providing valuable insight for the optimization of the technology.

## Introduction

The progress in semiconductor materials and device development has been remarkable, with a profound impact on society. At the forefront of this advancement has been the continuous integration and development of silicon-based MOSFET devices guided by Moore's law, which predicts a doubling of device density every 18 months. This has been achieved through advanced lithographic tools that enable the production of few-nanometre gate-length transistors, the increase of silicon wafer diameter, and the implementation of innovative device designs to maintain charge control and minimise gate leakage (double-gate FET[1], super-halo ion implantations[2], strain engineering and orientation effects[3]). Looking at the future development of semiconductor devices, there are challenges to overcome in scaling conventional CMOS circuits. Additionally, power dissipation poses a thermal limitation on the size and speed of future processors. Thus, while Si-based CMOS architecture has dominated the industry in terms of chip size and dollar volume, other semiconductor technologies have also made critical advancements. The ability to grow epitaxial layers in a controlled manner, initially through Liquid Phase Epitaxy (LPE) and Vapor Phase Epitaxy (VPE), and then through Metalorganic Vapor Phase Epitaxy (MOVPE) and Molecular Beam Epitaxy (MBE), has played a crucial role in the maturation of the compound semiconductor industry. This development has had a significant impact on both photonics and electronics.

In addition, in recent decades, the growing demand for digital data has driven scientists to seek innovative solutions to enhance the transmission capacity of existing data communication and telecommunication links. In the realm of wireless communication systems, the utilization of micrometer and millimeter-wave spectrum has made possible to attain larger bandwidth communications resulting in communication rates in the range of 30-300 GHz. This can be achieved thanks to the union of Gallium Nitride (GaN), a Wide Band Gap (WBG) material, and High Electron Mobility Transistor (HEMT) structure, that with respect to traditional silicon-based transistor can lead to several advantages in terms of high voltage (high power) and high frequency applications. Research is now going in the direction of scaling the dimensions of such devices to enhance their switching frequency operations. However, when small aspect ratio (ratio

between gate width and gate length) are reached, parasitic effects named as short-channel effects can manifest: they can result in lowering the controllability of the gate contact over the channel, making the carrier velocity saturates due to increasing lateral electric field, reducing the efficiency of the device due to the formation of leakage paths under the channel region, and more [4]. To mitigate such problems, innovative structures has been adopted like back barriers, and doped buffer layers. The aim is to maintain the carriers focused in the channel region and reduce the buffer leakage. However, the implementation of such structures may also introduce traps that can limit the performance of the device and cause the insurgence of stability and reliability issues. For these reasons, significant research efforts are needed. The aim of this thesis is to evaluate the characteristics, and the stability, issues concerning GaN HEMTs with back-barrier. This has been accomplished by utilizing the data gathered during the research activity. The devices provided come from the US company QORVO, which is a partner of the University within the ONR project. On these samples, several tests have been conducted. In particular, they underwent to a series of static and dynamic measurements. This encompassed first of all a preliminary DC analysis and then double-pulse and Vth transient measurements, subjecting the devices to stress conditions in both OFF and semi-ON states. By comparing the outcomes with data from existing literature, we aimed to determine the origin and the placement of the traps contributing to performance degrading and subsequently classify them. Ultimately, the key findings are as follows: CONTROL devices, that are those lacking of a back-barrier, exhibit higher dispersion due to their interaction with trap states within the buffer. Conversely, devices equipped with a backbarrier are successful in isolating these defects, although they may introduce alternative trapping mechanisms, potentially involving interface states. The thesis will be organised as follows:

Chapter 1: A comprehensive review of gallium nitride (GaN), which includes its chemical and electrical properties, highlighting its advantages with respect to traditional semiconductors.

Chapter 2: An in-depth examination of the structure of high-electron mobility transistors (HEMTs) based on gallium nitride, demonstrating how the material properties are leveraged in the operation of these devices.

Chapter 3: An overview of the stability and reliability issues that impact GaN HEMT devices, including an analysis of short-channel effects and proposed structural enhancements.

Chapter 4: Detailed explanations of the structure of the devices used in the experiments followed by a description of the experimental setup adopted to perform the measurements.

Chapter 5: A comprehensive discussion of the experimental results obtained for QORVO devices, covering various aspects such as DC characteristics, double pulse and transient characteristics, and temperature-induced stress.

Chapter 6: The conclusions are traced and the main results obtained discussed.

## **Chapter 1: Gallium Nitride**

Gallium Nitride (GaN) has emerged as a game-changing material for microelectronics applications, revolutionising fields such as optoelectronics, power electronics, and wireless communication due to its unique combination of exceptional properties and superior device performance. In this chapter, we explore the potential of GaN in microelectronics, showcasing its chemical and electrical properties and examining its advantages over traditional semiconductors.

#### 1.1 Beyond the limits of silicon: gallium nitride

From the invention of the first transistor in December 1947, silicon has been the backbone of electronic industry. The progress in microelectronics has led to a better comprehension of the properties of semiconductor materials, and, as a consequence, to an improvement of every electronic device. Indeed, without a deep knowledge of the semiconductor properties, it would not have been possible to manufacture the integrated circuits, the memories, and all the other components, which have allowed the realisation of advanced electronic devices such as computers, smartphones, tablets and televisions. The development of a new technological solution in the electronic field was also crucial for the development and realisation of advanced communication technologies and telecommunications networks.

Silicon has been and still is the semiconductor of choice for the electronic industries; However, even silicon shows certain limitations [5], especially in the field where efficient light emission, high frequency, and high-power operation are required.

These and other constraints prevent Silicon from being a suitable material for the realization of devices for optoelectronic, high frequency and high-power applications. As a consequence, the microelectronics industry has started looking at other materials that offer higher performances, specifically compound semiconductors and Wide Bandgap materials (WBG). What has been done is to move from the IV group of the periodic table where we can find simple semiconductors as Silicon (Si) and Germanium (Ge) to elements of group III and V that can be bond together and form a unique structure,

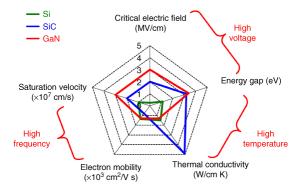

showing promising properties. Gallium nitride (GaN) and silicon carbide (SiC) are two main examples of WBG. From the performance point of view, respect to traditional semiconductors, they offer several advantages, as reported in the following Figure 1.1:

Figure 1.7 Spider plot of the physical and electronic properties of GaN compared with those of Si and SiC.[6]

Gallium Nitride (GaN) is one of the most promising binary compounds at the moment, composed by Gallium (Ga) and Nitrogen (N). In the following a comparison between GaN and Si will make clear the choice of this innovative material.

#### **1.1.1 Optical Properties**

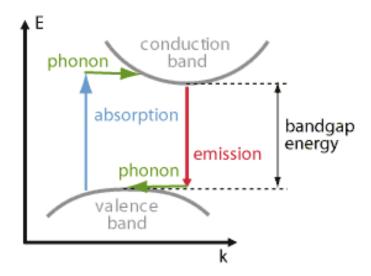

First of all, Silicon is an indirect bandgap semiconductor. This can be determined by solving Schroedinger equation for a periodic potential knowing the crystal structure of silicon and in this way finding the relation between energy and momentum which is the Band diagram of the semiconductor, an essential tool that allows to understand the physical properties of the material. The term 'indirect' refers to the fact that in the E-k diagram, as shown in Figure 1.2, the minima of Conduction Band is not aligned with the maxima of Valence Band. For this reason, it is complicated to have a photon emission. Indeed, in order to have a radiative recombination process the energy must be conserved during the transition. Since the maximum and the minimum of the valence and covalence band are not aligned, the momentum change; thus, it is essential that a carrier collides with the crystal lattice, generating a phonon (quanta of crystal lattice vibration) in order to allow the radiative recombination to occurs.

*Figure 1.2 Indirect bandgap diagram: in this case additional phonons need to be involved in absorption and emission processes in order to provide the required momentum change of electrons.*[7]

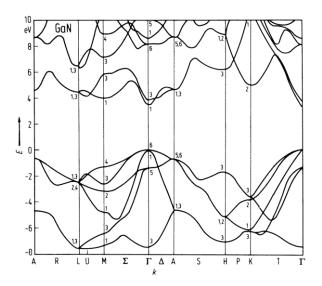

On the other hand, thanks to its crystalline structure and its chemical composition, GaN is a direct bandgap semiconductor having the maxima of Valence Band aligned with the minima of Conduction Band as reported in figure 1.3:

Figure 1.3 Band Structure of GaN (direct-bandgap). Eg = 3.39 eV [8]

The direct-bandgap configuration allows to have recombination between carriers in a more efficient way compared to Silicon; indeed, when a carrier passes from the valence band to the conduction band both energy and momentum are conservated, resulting in a high probability of having a phenomenon of radiative recombination. This property allows the realization of devices with high efficiency in light emission applications. From the figure 1.3 we can also see, as already anticipated, that the difference between the maxima and minima of the two bands, that is the energy gap, is 3.39 eV. This is a wider bandgap compared to Silicon and this was one of the best advantages that were studied from GaN discovery. There is a relation expressed by the equation 1.1 based on De Broglie hypothesis, that links the Energy Gap with the emission wavelength of the photons emitted by the devices:

$$\lambda = \frac{hc}{\Delta E} \cong \frac{hc}{E_G} \quad (1.1)$$

From this equation we can compare the results obtained for Silicon and GaN:

- $\lambda_{Si} \cong 1107 \ nm$  (IR spectra)

- $\lambda_{GaN} \cong 365 \ nm \ (UV \ spectra)$

Just comparing the region of the spectrum at which Silicon and GaN emits, we can understand that there is an important difference. With GaN it is possible to access to the most energetic portion of the electromagnetic spectrum in the visible (violet and blue), a region that would have been inaccessible just by utilizing Silicon. This result is important in the realization of white LEDs. There are several strategies to produce white light, but one of the more exploited technique is phosphorus conversion, which entails in coating a GaN-based blue LED with a phosphorus layer. When the GaN LED is activated, it emits high energetic photons that are absorbed by the phosphorus, generating electron-hole pairs. These pairs subsequently recombine, emitting photons predominantly in the yellow region of the visible spectrum, displaying a wide dispersion of colors. The resulting spectrum closely resembles the reference spectrum for white light. [9]

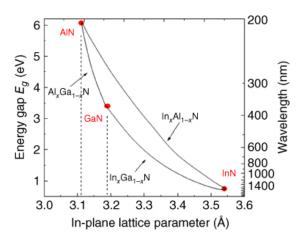

Gallium nitride is commonly alloyed with other elements such as indium or aluminium to form ternary and quaternary alloys. In the case of ternary alloys, where no crystallographic phase change occurs with varying composition, Vegard's law can be applied to predict the semiconductor's properties:

$$a(A_x B_{1-x} C) = x \cdot a (AC) + (1-x) a(BC) \quad (1.2)$$

This equation represents a weighted average of the lattice constants of the binary compounds involved, and it proves to be valuable in assessing the bandgap of the resulting ternary alloy. By carefully selecting the appropriate materials, and precisely controlling the constituent concentrations, it becomes feasible to create materials that possess an energy bandgap positioned between those of the constituent binary alloys. This technique is also known as bandgap engineering. For instance, when gallium nitride is combined with aluminium nitride, a ternary alloy called AlGaN can be formed, exhibiting a bandgap that falls within the range of 3.4 eV to 6.24 eV. Considering equation 1.2, it becomes evident that, in theory, adopting ternary alloys become possible the creation of LEDs capable of emitting photons at various frequencies, thereby producing different colours of light.

Figure 1.4 Energy band gap of nitride semiconductors (AlN, GaN, InN, and their ternary alloys) as a function on the in-plane lattice parameter. The corresponding wavelength is reported on the right axis. [6]

#### 1.1.2 High-Power behaviour

Furthermore, the maximum electric field that a silicon device can sustain before breaking is only 0.3  $\frac{MV}{cm}$ , which means that building high-voltage components (>500-1000 V) requires a larger amount of material resulting in thick components. This is due to the relatively small bandgap of silicon which is  $E_g = 1.12$  eV. As the thickness of the material increases, so does the resistance. Therefore, the applications that require devices able to operate at high power (e.g. power converters) are negatively affected, since it could lead to a reduction in the circuit efficiency. In the recent years, improving the efficiency of electronic circuit is becoming increasingly important, not only for reducing losses and costs, but also to help in reducing the carbon emissions.

On the other hand, not only the direct bandgap structure of GaN had allowed it to be extensively used in the field of illumination but numerous other important properties had enabled it to excel in various electronic application fields, such as high-power operations. In fact, the wide bandgap (WBG) of the material ( $E_g = 3.4 \text{ eV}$ ) results in a high critical electric field ( $E_{CR} = 3 - 3.75 \text{ MV/cm}$ ), representing the maximum-fieldstrength the material can endure without experiencing breakdown. As mentioned before, this high critical field plays a pivotal role in enabling the creation of electronic devices designed to operate at high voltages, while maintaining low on-resistance. These advantages allow WBG to be the best candidate for power conversion applications.

For this and also other purposes, also the impact of temperature on semiconductors must be considered, as it significantly influences carrier generation and, consequently, the electrical properties of devices as well as the ability to operate reliably in stressful environment such as the high-power one. In general, WBG allows to realize devices able to sustain higher temperature than silicon. This is due to the fact that with their bigger bandgap WBG have a smaller intrinsic carrier concentration, because the distance between Valence and Conduction band is higher. As a consequence, the quantity of minority carrier necessary to make the material degenerative is increased and happens at higher temperature respect to traditional semiconductors. This quantity of carriers is referred to as the intrinsic carrier concentration  $(n_i)$ , and it exhibits an exponential dependence on temperature (T), as shown in the equation 1.3:

$$n_i = \sqrt{N_c N_v} e^{-\frac{E_G}{2kT}} \quad (1.3)$$

Here, k denotes the Boltzmann constant, while N<sub>C</sub> and N<sub>V</sub> represent, respectively, the density of states in the conduction, and valence bands.

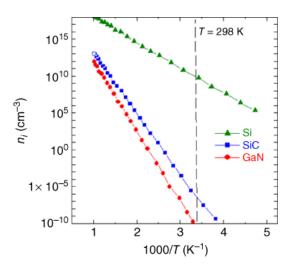

In the following figure 1.5, it is reported a comparison of intrinsic carrier concentration as a function of Temperature for Silicon, Silicon Carbide (SiC) and

Figure 1.5 Calculated intrinsic carrier concentration ni as a function of reverse of the temperature (1000/T) for GaN. For comparison, the curves of ni for Si and SiC are also reported. The dashed line indicates the room temperature (T = 298 K). [10]

As previously said the intrinsic carrier concentration in Si at temperatures above 300 °C can become comparable to or even exceed intentional dopant concentrations, making the material degenerative. In contrast, SiC and GaN exhibit much lower intrinsic carrier concentrations, making them less susceptible to issues caused by an excessive intrinsic carrier concentration even at elevated temperatures, such as 600 °C. Especially, GaN stands out with an extremely low intrinsic carrier concentration, about 19 orders of magnitude lower than Si at room temperature (T = 298 K).

#### 1.1.4 High-frequency operation

In addition, Silicon exhibits a moderate mobility of 1350  $\frac{cm^2}{v_s}$  and a relatively low saturation velocity of 700  $\frac{cm}{s}$ . These factors limit the maximum frequency at which silicon-based transistors can work (few GHz); Nevertheless, the requirement of some emerging applications in industry, like 5G and 6G telecommunication systems, will need devices able to operate at higher frequencies. Consequently, new materials with higher electron mobility and higher saturation velocity are necessary for the next generation of high-speed electronics.

Another aspect to consider concerning the electrical properties of GaN is undoubtedly the carrier saturation velocity and their mobility within the crystal lattice of the material. Mobility represents the ability of carriers to move within the material, while saturation velocity is the maximum speed they can attain under the influence of high electric fields. Gallium nitride exhibits a saturation velocity of approximately  $2.5 \cdot 10^7 \frac{cm}{s}$ , which is nearly three times higher than that of silicon. In general, carriers don't travel at their saturation velocity. When low electric fields are applied the dependence of the saturation velocity on the electric fields can be expressed, in first approximation, by the equation 1.4:

$$v = \mu \cdot E$$

(1.4)

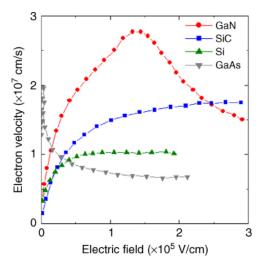

However, the dependence between v and E is more complex, as we can see in figure 1.6:

Figure 1.6 Electron velocity as a function of the electric field for GaN. For comparison, the values of the electron velocity of GaAs, Si, and SiC are also reported. [11]

We can see that at first, as the electric field increases, the carrier velocity also increases as carriers are accelerated, showing a linear behaviour. However, beyond a critical electric field, the carrier velocity starts to decrease due to a reduction in the material's mobility, which becomes dominant at high electric field values. This is attributed to the band structure of GaN, where carriers, under very high electric fields, move to higher-energy states in the conduction band. Therefore, the effective mass increases causing a reduction in the carrier mobility, as can be seen from equation 1.5:

$$\mu = \frac{q \tau}{m^*} \qquad (1.5)$$

q is the electron charge,  $\tau$  is the average scattering time, and m\* is the effective mass of the carriers. The electron mobility, in GaN, at room temperature is around  $1000 \frac{cm^2}{V \cdot s}$ , which is comparable to silicon. However, doping significantly influences mobility, as it increases the concentration of ions and impurities. Therefore, a higher concentration of defects increases the probability of collisions, leading to a reduction in scattering time; thus, to a reduction in the carrier mobility. Scattering time refers to the average time between two electron scattering events. This aspect will be discussed more in detail in the following chapter of the thesis.

#### **1.2 Spontaneous and Piezoelectric polarizations**

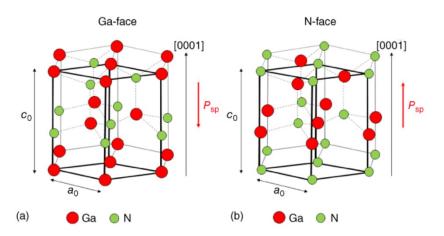

As already discussed in the previous sections, one of the most promising binary compounds at the moment is Gallium Nitride (GaN), composed by Gallium (Ga) and Nitrogen (N). The two elements are linked through covalent bonds that allow each atom to be tetrahedrally bonded to four atoms of the other type. In addition, an ionic contribution is also present because Ga and N have a large difference in electronegativity, which is a measure of the ability of an atom to attract electrons on its side of the bond. Since Nitrogen has a higher electronegativity than gallium, Ga and N atoms exhibit anionic (+) and cationic (-) characteristics, respectively; this results in a spontaneous polarization oriented along the growth-axis. In fact, while the internal polarization is balanced within the material, an asymmetry emerges at the cut face, resulting in a specific polarization along the growth-axis, known as spontaneous polarization. In III-N materials, the spontaneous polarization values have been reported as  $P_{sp,InN} = 0.032 \frac{c}{m^2}$ ,  $P_{sp,GaN} = 0.029 \frac{c}{m^2} 0.029$  and  $P_{sp,AlN} = 0.081 \frac{c}{m^2}$  for InN, GaN, and AlN, respectively, all directed from column III atoms to Nitrogen (see figure 1.7). In addition, the ionicity causes significant changes in the semiconductor properties: it increases the Coulomb interaction between the ions, and the energy of the fundamental gap in the electronic band structure, resulting in a high energy gap of  $E_G = 3.39 \ eV$  (larger than Silicon:  $E_G =$

1.12 *eV*). Moreover, the enhancement in crystal's cohesive energy owing to the Coulombic interaction between the ions promotes the rock-salt structure comprising atoms with six-fold coordination instead of tetrahedral bonds. In fact, Gallium Nitride, as well as other III-nitride materials such as AlN and InN, possess a stable crystal structure with a high melting point due to the small covalent radius and the strong bonding energy. Generally, they adopt a wurtzite crystal structure which comprises of two hexagonal close-packed sub-lattices interpenetrating each other and shifted along the c-axis (the growth-axis) by 3/8 of the cell height. The wurtzite structure possesses an ABABAB stacking sequence in the <0001> direction, as shown in Figure 1.7. [6]

Figure 1.7 Hexagonal crystal structure of GaN (wurtzite) for the Ga-face (a) and for the N-face (b). The bold lines highlight the unit cell, while the dashed lines indicate the GaN bonds. The spontaneous polarization vectors (PSP) are also drawn for the two cases. [6]

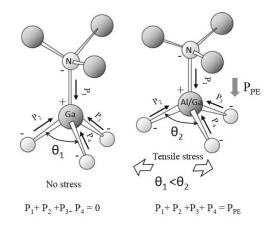

Another type of polarization occurs mostly in GaN based heterostructures, where another material like AlGaN or InAlGaN is grown or placed in contact with a GaN substrate. The presence of a mismatch in the lattice constants, between two epitaxial layer generates a new type of polarization known as piezoelectric polarization. Figure 1.8 illustrates how this polarization occurs in nitride semiconductors. In the left figure, the combined internal polarization vectors  $(P_1 + P_2 + P_3 + P_4)$  cancel out, resulting in zero polarization in a freestanding tetrahedral structure due to the crystal symmetry. However, in the right-hand side of the figure, when the crystal experiences deformation due to lattice mismatch, the angle  $\theta$  widens under tensile stress, (or the opposite if a compressive stress is applied). As a consequence, the internal electric field becomes unbalanced, leading to the appearance of the piezoelectric field  $(P_{PE})$  according to equation 1.6:

$$P_1 + P_2 + P_3 + P_4 = P_{PE} \qquad (1.6)$$

Figure 1.8 The balanced polarization of ionic bonds in the tetrahedron shape (left) cause the unbalance of polarization field under the stress originated to the difference of lattice constant of underlying material. The resultant electric field is called piezo electric one, shown as Ep in the figure (right) [6]

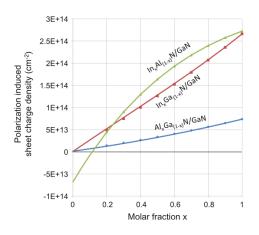

The most remarkable characteristic of Gallium Nitride and nitride semiconductors is the capacity of accumulating free carriers (electrons) at the heterointerface to counterbalance the fixed spontaneous and piezoelectric polarizations, when two WBG semiconductors with different lattice constants are putted together. In Figure 1.9, the theoretically calculated 2DEG (2-Dimensional Electron Gas) density for three types of ternary semiconductor layers coherently grown over GaN is shown.

Figure 1.9 Theoretically calculated carrier densities at the heterostructure are calculated caused by spontaneous and piezoelectric polarizations for three ternary alloys of  $Al_xGa_{(1-x)}N$ ,  $In_xGa_{(1-x)}N$ , and  $Al_xIn_{(1-x)}N$ , as a function of the their molar fraction x grown over GaN [6]

This high-density 2DEG is extensively utilized in typical nitride-based High Electron Mobility Transistors (HEMTs) since it allows the creation of an electron channel in an undoped material, by exploiting the polarization mechanisms. This feature stands as the most significant advantage of GaN-based Field-Effect Transistors (FETs). [12]

In the second chapter it will be discussed more in detail how these polarization mechanisms, that differentiate GaN from other materials, are exploited for the realization of the High Electron Mobility Transistor (HEMT)

# Chapter 2: GaN-based High Electron Mobility Transistor (HEMT)

After presenting the remarkable properties of semiconductor material, and especially Si and GaN, in this chapter the advantages of using HEMT structure based on GaN, are going to be described. These novel types of devices are able to achieve remarkable properties making the devices optimal candidates for high-frequency and high-power applications.

#### **2.1 Introduction to traditional FET devices**

The MOSFET is not the only device that can be realized using semiconductor materials for microelectronic applications. In fact, there are numerous variants generally referred to as advanced FET (Field-Effect Transistor) devices. These variants typically involve the use of materials different from Silicon to achieve advanced performance, such as high switching speed, low resistance to improve the efficiency, and high reliability for long-term operation. The basic concept for any FET device is rather straightforward: The device features an active channel, allowing the flow of electrons (or holes) from the source to the drain, which are realized by creating two ohmic contacts. Then there is a third contact which is called gate. By applying a potential to the gate, the conductivity of the channel can be controlled as we can see in Figure 2.1:

Figure 1.1 Example FET's working principle. In this example it is shown a n-MESFET. The gate metal creates a Shottcky junction. The bias applied to the gate controls the conductivity of the channel, modulating the depth of the space charge region. [13]

It is essential to isolate the gate contact from the channel to prevent current leakage to/from the gate. Various strategies for gate isolation exist; for example, in MOSFET an oxide layer is grown for this purpose.

Other strategies include:

- Schottky barrier (MESFET)

- Reverse-bias pn junction (JFET)

- Heterojunction (HFET)

However, not all structures possess the same characteristics. For this reason, there are quantities called figures of merit used to characterize the performance of devices and quantify their suitability for a particular application.

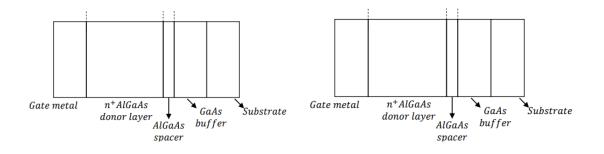

#### 2.2 Advanced FET devices: GaAs HEMTs

In traditional device structure such as, MOSFETs, MESFETs, and JFETs, the active (channel) region consists of a doped semiconductor layer. However, the adoption of doping introduces certain issues. The most important are:

- Transport takes place within the doped semiconductor, leading to scattering with ionized impurities that lower the mobility.

- Not all wide bandgap semiconductors have shallow dopants, potentially resulting in a relatively low carrier density.

In order to avoid the adoption of doping, while maintaining an elevated carrier density, new device structure have been developed such as the Heterostructure FET (HFET) also called High Electron Mobility Transistor (HEMT).

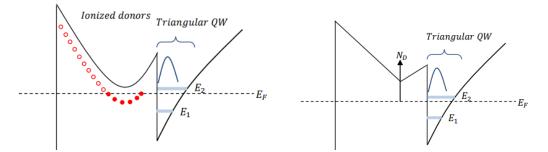

By employing this approach, the doped region (if present) and the channel region are intentionally separated in space. As result, it is possible to create a channel of free electrons with a high concentration of charges without the necessity of introducing dopant; Thus, the elevated mobility of the material is preserved. To better understand the operational principle of HEMT it is better to consider a device based on GaAs. A heterojunction is formed by growing a doped AlGaAs layer above a GaAs film. Two doping strategies can be employed: uniformly doping the entire AlGaAs layer except for a thin film or doping only a thin region of the layer while leaving the rest undoped. Electrons from the doped AlGaAs donor layer migrate into the GaAs layer, creating a dipole layer. As a result, the conduction band bends, generating a quantum well where electrons are trapped, forming the channel, also referred to as the 2DEG (two-dimensional electron gas). The band diagrams of the two approaches are reported in figure 2.2:

Figure 2.2 at the left the uniform doping approach: this scheme is easier to implement but the amount of charge introduced in the 2DEG is lower. At the right the delta-doping scheme: it introduces a much higher charge in the 2DEG and reduces the risk of introducing a parasitic channel within the barrier [14]

The key advantage of this kind of structure is the suppression of ionized impurity scattering in the channel region since, the dopants are physically separated from the free electrons. Moreover, in contrast with the devices with a doped channel, that suffer from dopant freeze-out at low temperatures, HEMTs maintain a high carrier density even in such conditions, ensuring reliable operation at colder temperatures. In the end, superior materials for the channel can be exploited. Usually, this kind of materials are challenging to process in thick layers; however, HEMTs' reduced channel layer thickness allows their use, further improving device capabilities.

#### 2.3 Advanced FET devices: GaN HEMTs

First of all, an AlxGa1-xN alloy is an hexagonal crystal, as GaN, that can be obtained by replacing a portion of Ga-atoms with Al-atoms in the GaN crystal. The lattice parameter and energy gap of AlxGa1-xN alloys can be customized by varying the Al concentration, according to Vegard's Law, yet presented in section 1.1.

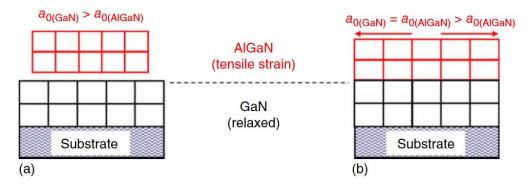

AlGaN/GaN heterostructures are then formed by growing a thin AlxGa1-xN barrier layer on a GaN substrate. The different energy gaps between the materials create an energy discontinuity in the band diagram, while the lattice mismatch induces a tensile strain in the AlxGa1-xN layer to compensate [15]. This strain leads to a piezoelectric polarization along the c-axis, as reported in the following Figure 2.3, to visualize better this mechanism:

Figure 2.3 Illustrates the schematic of isolated AlGaN and GaN crystals (a) and the resulting AlGaN/GaN heterostructure (b). After the growth of the AlGaN layer on GaN, a tensile strain is induced to compensate for the lattice mismatch between the two materials. [6]

In the strained AlGaN/GaN heterostructure, an induced piezoelectric polarization PPE along the c-axis is given by Equation 2.1:

$$P_{PE} = e_{33}\varepsilon_z + e_{31}\left(\varepsilon_x + \varepsilon_y\right) \qquad (2.1)$$

Here,  $e_{33}$  and  $e_{31}$  are the piezoelectric coefficients,  $\varepsilon_z$  represents the strain along the c-axis ( $\varepsilon_z = \frac{(c-c_0)}{c_0}$ ), and  $\varepsilon_x = \varepsilon_y = \frac{(a-a_0)}{a_0}$  denote the isotropic in-plane strains. Additionally,  $a_0$  and  $c_0$  represent the equilibrium lattice constants. By the way, the piezoelectric polarization along the c-axis can also be expressed as in equation 2.2:

$$P_{PE} = 2 \frac{(a - a_0)}{a_0} \left( e_{31} - e_{33} \frac{C_{13}}{C_{33}} \right) \quad (2.2)$$

where  $C_{13}$  and  $C_{33}$  represent the elastic constants of the material. The term  $\left(e_{31} - e_{33}\frac{c_{13}}{c_{33}}\right)$  is negative within the entire Al-concentration range commonly used in AlxGa1-xN alloys. Consequently, the piezoelectric polarization will be negative for tensile strain  $\left(a^{AlGaN} > a_0^{AlGaN}\right)$  and positive for compressive strain  $\left(a^{AlGaN} < a_0^{AlGaN}\right)$ . For a Ga-face AlGaN/GaN heterostructure with the AlGaN barrier layer under tensile strain, the piezoelectric polarization  $P_{PE}$  will be negative and aligned with the spontaneous polarization  $P_{SP}$  (directed towards the GaN substrate). The polarization

gradient at the AlGaN/GaN interface results in a polarization-induced charge density as reported in Equation 2.3, which depends on the Al-concentration x:

$$|\sigma(x)| = |[P_{SP}(Al_xGa_{1-x}N) + P_{PE}(Al_xGa_{1-x}N) - P_{SP}(GaN)]|$$

(2.3)

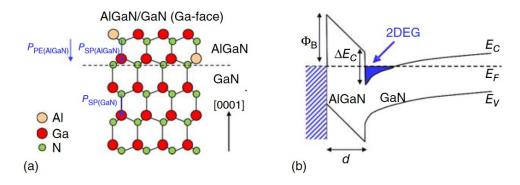

To maintain charge neutrality, free electrons migrate in order to compensate for the polarization-induced charge density at the AlGaN/GaN interface, leading to the generation of a 2D electron gas (2DEG). This 2DEG accumulates in the potential well formed at the AlGaN/GaN interface as can be seen in Figure 2.4:

Figure 2.4 (a) This diagram illustrates an AlGaN/GaN heterostructure with the spontaneous and piezoelectric polarization vectors. (b) The schematic band diagram of the AlGaN/GaN heterostructure is shown, with an arrow indicating the presence of a 2DEG (two-dimensional electron gas) in the quantum well at the interface. [6]

Specifically, in an AlGaN/GaN device, a Schottky metal electrode forms on the AlGaN surface, and a bias is applied to modulate the sheet carrier density of the 2DEG, denoted as  $n_s$ . In the presence of the Schottky metal, the maximum sheet carrier density of the 2DEG can be expressed as in Equation 2.4:

$$n_s(x) = \frac{\sigma(x)}{q} - \left[\frac{\varepsilon_0 \varepsilon_{AlGaN}(x)}{d_{AlGaN} q^2}\right] \cdot \left[q \Phi_B(x) + E_F(x) - \Delta E_c(x)\right] \quad (2.4)$$

where  $d_{AlGaN}$  is the thickness of the AlxGa1-xN barrier layer,  $\varepsilon_{AlGaN}$  is its permittivity,  $q\Phi_B$  is the Schottky barrier height of the metal contact,  $E_F$  represents the position of the Fermi level with respect to the GaN conduction band edge energy, and  $\Delta E_c$ is the conduction band offset at the AlGaN/GaN interface. Usually, the 2DEG formed in AlGaN/GaN heterostructures exhibits sheet carrier density values on the order of  $10^{13}cm^{-2}$  and a mobility within the range of  $1000 - 2000 \frac{cm^2}{V \cdot s}$  [16].

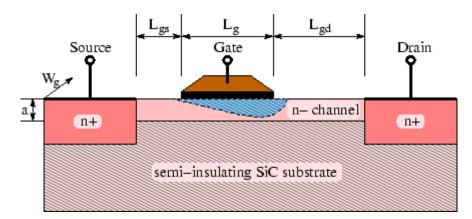

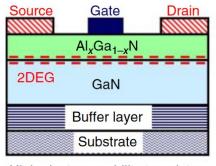

The HEMT operations are based on the presence of the 2DEG at the AlGaN/GaN heterostructure interface. In Figure 2.5, a schematic cross-section of a device is shown. In a conventional AlGaN/GaN HEMT, the current flows through the 2DEG channel between a source and a drain Ohmic electrode. The current is controlled by applying a negative bias to a Schottky contact serving as the gate electrode of the transistor.

High electron mobility transistor

Figure 2.5 Schematic cross-section of a typical AlGaN/GaN HEMT [6]

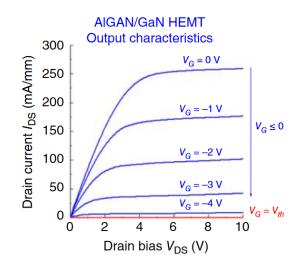

Since the 2DEG is inherently present in the AlGaN/GaN heterostructure, and the Fermi level at the interface is above the conduction band minimum (as can be seen in figure Figure 2.4 b), this device is considered "normally-on." It means that current flows between the source and drain even when the gate bias is zero (Vg = 0). A typical output IDS–VDS characteristic is illustrated in Figure 2.6:

Figure 2.6 typical output IDS-VDS characteristic of a normally-on GaN HEMT [6]

Specifically, The HEMT's output current can be regulated by applying a negative bias to the gate, gradually reducing the current until it reaches the "threshold voltage"  $(V_{th})$ . At this point, the Fermi level is pushed below the conduction band edge of the AlGaN, depleting the 2DEG channel. The threshold voltage of an AlGaN/GaN HEMT relies on the heterostructure properties, including AlGaN thickness, doping, and Al concentration. It can be expressed through Equation 2.8:

$$V_{th}(x) = \Phi_B(x) + E_F(x) - \Delta E_c(x) - \left[\frac{qN_D d_{AlGaN}^2}{2\varepsilon_0 \varepsilon_{AlGaN}(x)}\right] - \frac{\sigma(x)}{\varepsilon_0 \varepsilon_{AlGaN}(x)} d_{AlGaN}$$

(2.5)

Here,  $N_D$  represents the doping density of the AlGaN barrier layer expressed in atoms/cm<sup>3</sup>. The high saturation velocity and mobility of the 2DEG in AlGaN/GaN heterostructures enable rapid switching frequencies in HEMTs.

As we can see from the following equation, valid in general for all the FET devices:

$$f_T = \frac{v_s}{\pi L} = \frac{1}{\pi \tau} \qquad (2.6)$$

where  $v_s$  is the saturation velocity of electrons, and  $\tau = \frac{L}{v_s}$  represents the transit time for electrons to travel the gate's length at saturation velocity, to achieve high-

frequency operation, the transit time ( $\tau$ ) between the source-drain spacing ( $L_{SD}$ ) must be minimized. The cutoff frequency ( $f_T$ ) expressed by Equation 2.6 can be rewritten in terms of transconductance ( $g_m$ ) and gate capacitance ( $C_g$ ) as in Equation 2.7:

$$f_T = \frac{g_m}{2\pi C_g} \qquad (2.7)$$

Utilizing the saturation electron velocity of GaN, Equation 2.6 indicates that submicron gate HEMTs are capable of operating in the millimeter-wave (mmW) frequency range and that are suitable for Radio-frequency (RF) and telecommunication applications.

#### 2.4 Johnson's figures of merit

In microwave transistors for telecommunication applications, one of the key figures of merit is the unity gain cutoff frequency, that is the frequency at which current gain becomes unity (fT). Its expression is reported by Equation 2.6. This equation demonstrates that to maintain high-frequency operation, it is essential to minimize the transit time, and one way this could be done is by properly scaling the device's dimension (reduce gate length). In practical cases, the unity gain cutoff frequency is typically lower with respect to the one predicted by the above equation due to parasitic capacitances (such as gate fringing capacitance, interelectrode capacitances, etc.) and other parasitic effects.

In addition, each semiconductor material has a critical electric field (*Ecrit*), that represent the maximum field the material can withstand before experiencing breakdown. Therefore, there is a maximum value for *VDS* (drain-source voltage), denoted as  $V_{DS,max}$ , which is given by Equation 2.8:

$$V_{DS,max} = E_{crit} \cdot L_{DS} \quad (2.8)$$

Where  $L_{DS}$  is the physical distance between Drain and Source.

In the end, the Johnson figure of merit (*JFoM*) is the product of the maximum transit frequency and the maximum voltage for a given drain-source distance. It can be expressed as in the following Equation 2.9:

$$JFoM = f_T \cdot V_{DS,max} = \frac{v_s}{2\pi L_{DS}} E_{crit} \cdot L_{DS} = \frac{E_{crit} \cdot v_s}{2\pi}$$

(2.9)

The Johnson figure of merit offers valuable insights and considerations: it relies on material parameters, making it ideal for identifying novel semiconductors suitable for high-frequency operation. It is clear also that there exists an inverse relationship between breakdown voltage and cutoff frequency: High-frequency devices have lower breakdown voltages compared to transistors operating at lower frequencies. In the end, JFoM effectively facilitates the comparison of different material systems for high-power and high-frequency applications. It aids in determining the best material to achieve specific performance requirements [17].

In the following table 2.1 a comparison is made between various materials in order to see the advantages in terms of JFoM. The elevated JFOM and the remarkable electrical properties makes GaN an excellent material for the realization of high-power high frequency FET devices.

| Material                                | E <sub>G</sub> (eV) | ε <sub>r</sub> | μ (cm²/Vs) | ε <sub>crit</sub> (MV/cm) | v <sub>s</sub> (x10 <sup>7</sup> cm/s) | κ <sub>th</sub> (W/cmK) |

|-----------------------------------------|---------------------|----------------|------------|---------------------------|----------------------------------------|-------------------------|

| Si                                      | 1.12                | 11.7           | 1440       | 0.3                       | 1                                      | 1.3                     |

| GaAs                                    | 1.42                | 12.9           | 9400       | 0.4                       | 0.9                                    | 0.55                    |

| GaN                                     | 3.4                 | 8.9            | 1400       | 3.75                      | 2.4                                    | 2.5                     |

| 4H-SiC                                  | 3.23                | 9.66           | 950        | 2.5                       | 2                                      | 3.7                     |

| AIN                                     | 6.2                 | 8.5            | 450        | 15                        | 1.4                                    | 2.85                    |

| Diamond                                 | 5.5                 | 5.7            | 4500       | 10                        | 2.3                                    | 23                      |

| $\beta$ -Ga <sub>2</sub> O <sub>3</sub> | 4.9                 | 10             | 250        | 8                         | 1.1                                    | 0.1-0.3                 |

Table 2.1 The table presents the key electrical properties of silicon, wide bandgap semiconductors, and ultrawide bandgap semiconductors. It is evident that the significant improvement in the Johnson figure of merit (JFoM) for wide bandgap semiconductors mainly relies on  $E_{crit}$  (critical electric field). However, even ultra-wide bandgap materials achieve a JFoM that is only marginally greater than three times that of GaN, indicating that field engineering alone is approaching its limits in enhancing power performances [12].

#### **2.5 Epitaxial Structure Implementations**

The epitaxial structures of GaN HEMTs, usually, are composed of several layers, that are substrate, nucleation layer, buffer layer, barrier layer and cap layer. These layers are grown sequentially on top of a substrate using either metal organic chemical vapor deposition (MOCVD) or molecular beam epitaxy (MBE) techniques. MOCVD and MBE are two popular epitaxial growth techniques used to deposit thin films of crystalline materials on a substrate with precise control over the atomic arrangement and thickness. These techniques are extensively employed in the fabrication of advanced semiconductor devices, including GaN-based transistors. MOCVD uses metal organic precursors transported by a carrier gas, while MBE operates in ultra-high vacuum conditions, depositing atoms or molecules on a heated substrate thanks to atomic and molecular beams.

Thanks to these two and other techniques, several structures are implemented in the HEMT, starting form a substrate till reach the core of the HEMT structure which is the GaN/AlGaN heterojunction. The growth sequence from bottom to top typically includes:

#### 2.5.1 Substrate

The substrate is a crucial component in the fabrication of semiconductor-based devices, as it serves as the foundation for all other layers. The choice of substrate significantly impacts production costs and the overall device quality. Four common materials are used as substrates for GaN HEMTs:

- Silicon: Suitable for cost-effective devices due to its large area capacity (up to 12"). However, it has a significant lattice mismatch with GaN, leading to dislocation concentration and potential cracking. Strain management techniques are necessary for silicon substrates.

- Sapphire: Another cost-effective option, with a significant lattice mismatch to GaN. It introduces compressive strain and requires dislocation mitigation techniques similar to silicon. Sapphire also has an extremely low thermal

expansion coefficient and may benefit from flip-chip bonding for better heat transfer.

- Silicon carbide (SiC): A highly desirable substrate due to its high thermal conductivity, allowing efficient heat transfer and reducing the need for elaborate cooling systems. This enables smaller electronic devices and minimizes electromagnetic interference (EMI) issues. However, SiC substrates are expensive, and current fabrication techniques limit the achievable area.

- Gallium nitride (GaN): Offers the least amount of dislocation, (no lattice mismatch), making it the preferred substrate for high-quality GaN devices. However, GaN substrates have high production costs and limited achievable area, leading to very expensive devices. Despite this, they offer superior performance.

The choice of the appropriate substrate depends on device architecture and desired performance, with each material having distinct advantages and limitations as reported in the following table 3.1[18]:

| Material | Crystalline<br>structure | Typical surface orientation | In-plane lattice<br>constant (nm) | In-plane thermal<br>expansion<br>coefficient (K <sup>-1</sup> ) |

|----------|--------------------------|-----------------------------|-----------------------------------|-----------------------------------------------------------------|

| GaN      | Hexagonal                | c-Plane                     | 0.3189 [62]                       | $5.6 \times 10^{-6}$                                            |

| Sapphire | Rhombohedral             | <i>c</i> -Plane             | 0.476 [62]                        | $7.3 \times 10^{-6}$ [61]                                       |

| SiC      | Hexagonal                | <i>c</i> -Plane             | 0.308 [62]                        | $4.5 \times 10^{-6}$ [61]                                       |

| Si       | Cubic                    | {111}                       | 0.384                             | $3.6 	imes 10^{-6}$                                             |

Table 3.1 Crystalline data of sapphire, SiC, and Si which are important for epitaxial growth.

#### 2.5.2 Nucleation layer

The nucleation layer is a thin initial layer that is grown on the substrate before the deposition of other GaN-based layers. The main purpose of the nucleation layer is to facilitate the heteroepitaxial growth of subsequent layers and improve the overall crystal quality of the device. The choice of the nucleation layer material is critical because it

needs to accommodate the lattice mismatch between the substrate and the GaN layers. GaN has a significantly different lattice constant compared to common substrate materials like sapphire, silicon, and silicon carbide. This lattice mismatch can lead to defects and dislocations at the interface if not properly managed. In this way, by carefully selecting the nucleation layer material and its thickness, it is possible to minimize lattice mismatch between the substrate and GaN layers, helping in stress relaxation during growth, preventing the propagation of defects and improving the structural integrity of the device. Common materials used as nucleation layers in GaN HEMTs include AlN (aluminum nitride) and low-temperature GaN. Both materials have similar lattice constants to GaN, making them suitable choices to minimize lattice mismatch.

#### 2.5.3 Buffer layer

The buffer layer is realised by growing a thick film of high-quality GaN, on top of the nucleation layer. This is done to enhances the performance and reliability of the GaNbased devices by providing a higher-quality platform for the growth of the active layers, preventing the propagation of dislocations from the nucleation layer to the active layer. In addition, to improve the carrier confinement, the buffer layer can also be engineered to control the electron confinement in the device channel. This can be achieved by incorporating acceptor-type dopants like carbon (C) or iron (Fe) to increase resistivity or by introducing a back-barrier structure to further enhance electron confinement [19]. Usually part of the buffer is dedicated to the channel. GaN channel is an undoped film where 2DEG form. It is left undoped in order to preserve the high mobility of GaN. , the channel thickness involves a trade-off between electron confinement and trapping effects.

#### 2.5.4 Barrier layer and cap layer

For AlGaN-based devices, using ultrathin Al-rich materials in the millimiterwave (mmW) range is preferred to avoid gate recess, which can impact device reliability. The thickness and alloy composition influence mechanical strain, piezoelectric polarization, and the density of the two-dimensional electron gas (2DEG). Usually, an additional final layer is used: the cap layer that often is made of aluminum nitride (AlN). It is applied to

prevent stress relaxation at the heterointerface of the Al-rich barrier/GaN channel and passivate surface states, reducing dispersion.

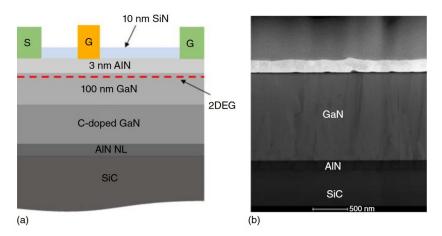

To better visualize the structure, an example is reported in Figure 3.1, comparing the theoretical cross-section and the one imaged by a real Transmission Electron Microscope:

Figure 3.1 Cross section (a) and transmission electron microscopy (TEM) of the MOCVD [6]

# Chapter 3: Stability and Reliability issues

This chapter starts with a detailed description of the main issues affecting the technology is presented: this involves stability and reliability issues as well as short channel effects. The latter are parasitic effects that manifest with a reduction in controllability of the channel, the saturation of the carrier velocity due to the lateral electric field, the presence of leakage paths below the channel, and the drain-induced barrier lowering (DIBL).

In order to mitigate stability and reliability issues, and short channel effects research is now focusing on the development of new innovative structures. In particular, to diminish short channel effect the following strategies has been considered: growth of Npolar GaN structures, use of novel materials (AIN, ScAIN, InAIN, and InAlGaN) for the barrier layer, use of doping in the buffer, usually C and/or Fe, and implementations of back barriers to obtain a better carrier confinement in the channel region. Hower, these promising structures are not able to completely eliminate the stability (temporary) and reliability (permanent) issues which degrade the device performances. In order to have a real development in the technology it is essential to understand the presence and the root causes of this problems.

# 3.2 Stability and Reliability Issues

GaN-based electronic devices have revolutionized power, frequency, and efficiency, outperforming Si- and GaAs-based devices. Ensuring successful commercialization requires reliable operation alongside enhanced performance and costeffectiveness. Stability and reliability issues have been major concerns in GaN electronics, leading to extensive research to understand and mitigate them, achieving short-term and long-term operational success. The presence of defects that may act as traps in GaN heterostructures are mainly caused by: foreign substrates, that introduces dislocations; caused by the lattice mismatch between the layers; addition of element as dopant, that may act as traps sites; and epitaxial structures that can introduces new failure mechanisms. For example, Iron and Carbon doping in the buffer layer can from one side enhance the electron confinement in the channel but at the same time they increase the trapping activity, as well as the increasing concentration of aluminum in the barrier layer can from one hand improve the confinement and on the other enhance the presence of surface states. Nevertheless, significant research efforts have improved the reliability of RF GaN HEMTs and monolithic microwave-integrated circuits (MMICs), providing a better understanding of dispersion effects, failure modes, electric field concentration, and heat distribution. This stability and reliability studies relies on monitoring the device failure rate under application-specific conditions and environment. Stability issues refers to recoverable changes in the device electrical characteristics primarily due to trapping effects, while reliability refers to unrecoverable device failure that can occur through two modes gradual changes in electrical parameters over time and sudden catastrophic failure or burnout.

#### **3.2.1** Stability issues, related to trapping effects

Initially, also due to the immature growth technology, stability issues emerged as a significant concern in AlGaN/GaN HEMTs. The most common effects are referred to the temporal variation of electrical parameters such as the drain current  $I_D$  (current collapse), threshold voltage  $V_{th}$  (threshold voltage shift), transconductance  $g_m$ , and ON-resistance  $R_{ON}$ . Another common reliability issue consists in the presence of kink, which correspond to a sudden increment in the drain current. All these effects result from the capture and emission of carriers by electrically active defects (traps), that are present in different regions of the device. During the capture process, a free carrier loses its energy and becomes localized by the defect site, characterized by its density, energy level in the semiconductor bandgap, and capture cross-section. On contrary, in the emission process, the carrier needs to acquire sufficient energy to overcome the energy barrier defined by the defect level, and the minimum of the conduction band, for electrons, or the maximum of the valence band for holes. As a result, the emission process and the associated emission time constant are typically much longer than the capture process, as the latter mainly depends on the availability of free carriers. Despite significant improvements in

growth quality, III-N heterostructures still exhibit relatively high densities of bulk defects and surface/interface states. These defects include intentionally or unintentionally introduced impurities like C or Fe in the buffer layers, extended crystallographic defects like dislocations, and point defects such as interstitials, vacancies, or antisites. For what concerns the location, the presence of traps under the gate region typically leads to changes in the threshold voltage that results in a reduction of the drain current (current collapse), whereas variations in the transconductance and on resistance are often associated with traps in the gate-to-drain access region [20].

In general, HEMT have a low concentration of holes; thus, the stability issues are mainly related to trapping or detrapping of electrons. Considering trapping of electrons under the gate region, the trapping of electrons directly influences the threshold voltage of the device. Indeed, if acceptor-like-traps are considered, the trapping activity lead a to the formation of a small depletion region that disperses charges. As a result, the negative voltage required at the gate to fully deplete the channel is reduced causing a variation in the voltage shift called threshold voltage shift. The voltage at which the channel is fully depleted is the threshold voltage  $V_{th}$  which for GaN HEMT devices is usually negative (normally-on devices, as discussed in section 2.2. If we consider traps located between the gate and drain regions, what primary can be observed is a variation in the ON-resistance of the device, while the threshold voltage remains almost constant. This happens because of a mechanism called "virtual gate". To better explain it lets analyse the case where we have only surface defects.

The degradation of drain current that occurs is also known as frequency dispersion effect because the reduction of the current is higher as the switching frequency from the OFF to the ON-state is increased. In this case, the surface traps located in the gate to drain access region are considered primarily responsible for this phenomenon. When the gate voltage experiences high-frequency excursions, the surface levels fail to follow the imposed variations, resulting in a decrease in current of the device. The theorized explanation is as follows: in the off-state bias condition, a high gate-to-drain voltage induces the injection of electrons into surface states from the gate edge. The high density of surface traps allows for electron redistribution through hopping towards the drain, causing negative charge to extend over a long region from the gate edge until a steadystate condition is achieved due to electrostatic feedback of the accumulated negative charge. These electrons create the "virtual gate" effect, expanding the depletion region of the two-dimensional electron gas (2DEG) channel. In fact, the phenomenon can be modelled with a second gate, called a virtual gate, in series with the real gate. It can be understood that the potential of the real gate is controlled by the applied voltage, while the potential of the virtual gate is controlled by the level of trapped charge. When the gate bias is switched to the on-state, the trapped electrons cannot be immediately removed (the channel formation speed is greater than the de-trapping speed), and the extended virtual gate section of the channel remains depleted for a period determined by the characteristic emission time constant. The dynamic emission of electrons from surface/interface states, leads to a transient change in drain current, resulting in a dynamic variation in ON-resistance that increases and a consequent diminishing in peak transconductance [21]. In this way the output current is reduced since the slope of the characteristic goes as  $\sim \frac{1}{Rov}$ .

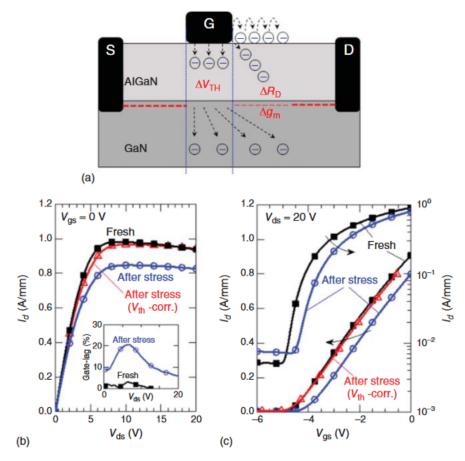

The last effect related to trapping is called kink effect. The term "kink" refers to the phenomenon which manifests with a sudden increase in drain current under DC conditions resulting from the application of high Drain-Source voltages. In fact, increasing the sweep of the voltage  $V_{DS}$  creates a distortion in the initial part of the saturation region of the output characteristic, caused by the drop in current, which would not occur with a smaller sweep. This happen because, when the sweep of the voltage  $V_{DS}$ increase, from a certain point there is an immediate liberation of charges that were trapped by defects. This degradation of the DC characteristics is considered to be related to the presence of traps, for example in the buffer layer, that when activated by the high electric field, capture electrons, resulting in a decrease in current. This leads to a decrease in charge carriers in the channel and, therefore, a reduction in current until a certain voltage is reached. Under that condition there is a sudden release of the trapped electrons. Another interpretation from Meneghesso et al., proposed that the kink could be caused by intraband impact ionization in the buffer layer, involving electrons trapped in acceptor-like deep levels with energies 0.9 eV above the valence band of GaN. Nevertheless, in RF devices, the electric field is usually not sufficient to induce impact ionization; thus, the most accredited hypothesis associates the kink with trapping and detrapping of electrons The trapping behavior of GaN-based HEMTs can be rapidly assessed using pulsed  $I_D$  –  $V_D$  and  $I_D - V_G$  characterization[22], also known as pulsed IV or double pulse measurements, where the I-V characteristics are measured in gate and drain-pulsed mode and compared to DC characteristics. An example is shown in Figure 3.2 b,c, which displays the output and transfer characteristics of an RF AlGaN/GaN HEMT before and after off-state stressing. While stress-induced positive  $V_{th}$  shift was observed from DC measurements (Figure 3.2c), indicating trap generation under the gate, pulsed gate-lag measurement (inset of the left panel) clearly depicts dynamic  $R_{DS,ON}$  degradation, suggesting trap generation in the gate-to-drain access region. To gain a more comprehensive understanding of trapping effects, a dual-channel pulsing system with different sets of quiescent bias conditions, known as drain-lag measurement, can be employed [23]. Despite the effectiveness of pulsed I–V characterization, these techniques do not provide specific information about the properties of traps responsible for device degradation under stressing.

Figure 3.2 (a) A diagram illustrating surface and bulk traps in the AlGaN barrier and GaN buffer layers, affecting Vth, RD, and gm. (b) Output characteristics of an AlGaN/GaN HEMT before and after off-state stress.(c) Transfer characteristics of the same AlGaN/GaN HEMT before and after the off-state stress. After correcting the I–V characteristics for Vth shift, significant degradation of  $R_{ON}$  is evident in the linear part of the ID–VD characteristic. Furthermore, a much stronger degradation of dynamic  $R_{ON}$  is observed from the gate-lag measurement before and after OFF-state stress (inset)[24]

To mitigate trap-related phenomena, particularly the frequency dispersion caused by surface traps, various solutions can be employed. The most commonly used approach is passivation, which involves depositing an insulating film, typically Silicon Nitride (Si<sub>3</sub>N<sub>4</sub>). This creates a nearly optimal dielectric/semiconductor interface that neutralizes surface charge arising from dangling bonds, surface defects, and residual charges generated by lattice disruptions. However, uniform results are not always guaranteed, making the deposition process and the quality of materials and surfaces crucial for the device's proper functioning. Nevertheless, improvements in final characteristics are typically achieved, depending on the frequency.

Another technique employed is the use of a field plate, a gate shaped like a T or  $\Gamma$  that partially covers the gate-drain region. This redistributes the electric field between the gate and drain, which is the primary cause of charge migration from the gate to traps. This improvement in the metallization helps in limiting the peak field above the gate and distributes it, to a lesser extent, across the entire extension of the field plate. A third method to mitigate surface effects is gate recess, a technique that involves moving the barrier layer deeper by inserting additional layers of AlGaN or GaN. This effectively distances the surface from the channel [25].

#### 3.2.2 Stability issue and device degradation mechanisms

In addition to charge trapping, there are permanent degradation mechanisms in devices fabricated in GaN, primarily attributed to the high electric fields that can be developped between the gate and drain. These fields can lead to the deterioration of the crystalline structure of the materials, with negative consequences for the device operations. Specifically, the elevated electric fields achievable due to the small device dimensions can give rise to degradation mechanisms related to the presence of a strong inverse piezoelectric effect (gate edge degradation) and hot electrons (degradation due to hot electrons).

An important degradation mechanism known as "gate-edge degradation" was identified through tests conducted on GaN HEMT devices by applying high negative voltages to the gate, maintaining the device in the OFF-state (avoiding the formation of a carrier-conducting channel) [26]. Specifically, this degradation involves a catastrophic,

sudden, and irreversible increase in gate leakage currents  $(I_G)$ , accompanied by a slight and more gradual degradation of DC characteristics such as a decrease in drain currents  $(I_D)$ , transconductance  $(g_m)$ , and an increase in drain resistance  $(R_D)$ . The voltage value at which degradation begins is generally referred to as the critical voltage  $(V_{critical})$ . Electroluminescence measurements have evidenced that the sudden increase in leakage current happens simultaneously with an increment of electroluminescence emission. This increment in the number of photons emitted is caused by the formation of hot spots, which are localized regions emitting an elevated number of photons, along the gate edges, these emission spots are attributed to localized defects formed during reverse bias step-stress tests in the crystalline lattice. Their origin is attributed to the inverse piezoelectric effect (IPE), which manifests when an intense longitudinal electric field is applied to the device (usually, there is an elevated potential difference between gate and drain). According to this hypothesis the inverse piezoelectric effect introduces additional tensile stress to the AlGaN barrier with respect to the one already presents due to the lattice mismatch between the strained AlGaN, and the relaxed GaN layer. Thus, the elastic energy of the barrier increases, and if it surpasses a critical value, crystallographic defects can form. Therefore, an increase in the leakage facilitating tunnelling between the gate and the channel through the AlGaN barrier, and these defects can become traps for electrons (degrading the DC characteristics). The defects formed in the lattice provide a path for carriers and have the equivalent effect of lowering the Schottky barrier height of the gate (percolative paths).

From environmental studies it was also noticed the environment contribute into enhancing the gate edge degradation. Pits were found to contain gallium and aluminum oxides in the form of oxygen (O), probably introduced in the device structure as part of the epitaxial fabrication process. However, moisture's role, rather than O, was found to be pivotal in the degradation process. Experiments showed that moisture clearly enhanced pit formation, leading to the hypothesis of moisture-induced electrochemical oxidation causing pits at the gate's edge. Connections were also drawn between pit formation and material quality. Pits were observed to nucleate at threading dislocations with a screw component in AlGaN/GaN HEMTs on Si, characterized by a relatively high density of dislocations due to the great lattice mismatch. Under high reverse gate bias conditions, threading dislocations migrated toward the gate edges, resulting in higher pit density and hastened device degradation. Mitigating this failure mode involves effective electric field management through proper field plate design, addressing material quality to manage traps and dislocations, minimizing residual moisture, and ensuring a highly hermetic passivation [27]. Another common degradation phenomenon affecting HEMT is named "hot electrons" degradation. Early on, the degradation pattern in the ON -state closely matched that of the OFF -state. However, detailed ON -state studies were complicated by device self-heating. Increasing structural degradation was observed along the gate finger's edge toward the device's center, where the temperature is highest and studies on nominally identical devices under closely matched junction temperature and electric field conditions showed increased  $I_D$  change under ON -state stress compared to OFF -state stress, suggesting a different mechanism of degradation.

In fact, by biasing a device in the saturation region of operation (ON state) and subjecting it to high drain-source voltages, the resulting strong electric field can give rise to the formation of hot electrons in the channel. Hot electrons are highly accelerated electrons that interact with the lattice, causing deformation and generating trap states. Their presence can be detrimental to the device, leading to degradation and the formation of traps and defects in the lattice. The high energies attained by these electrons, strongly accelerated by the electric field, enable them to generate electron-hole pairs through impact ionization upon interacting with the lattice. This phenomenon is also known as avalanche multiplication, as the electrons and holes generated from one collision are accelerated by the electric field and can acquire enough energy to ionize other atoms. The secondary carriers thus created are collected at the drain alongside the primary carriers, while the holes are accelerated toward the source and the gate. Given that impact ionization occurs in the region where the electric field is highest, near the Drain-side of the Gate, the majority of the produced holes are drawn toward the Gate by the electric field. Hot electrons can generate traps, consequently increasing current collapse and frequency dispersion. They can also become trapped in the surface, GaN, or AlGaN due to pre-existing traps, modifying the internal electric field and altering performance.

# **3.3 Short Channel Effects**

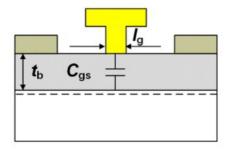

Even from section 2.1 it was possible to understand that the unity gain cut-off frequency becomes greater when device dimensions are reduced, enlarging the bandwidth and the switching frequency operation of the device. To enhance HEMT frequency performance through transistor scaling, it's essential to maintain the aspect ratio  $\frac{L_G}{d}$ , where gate length ( $L_G$ ) to gate-to-channel distance (d), while reducing resistances, capacitances and conductance (Figure 3.4).

Figure 3.4 Guiding principle of transistor scaling [28]

In fact, considering the following equations:

$$f_T = \frac{g_m}{2\pi C_{gs}} = \frac{v}{2\pi L_G} \qquad (3.1)$$

$$f_{max} = \frac{f_T}{2\sqrt{(R_i + R_G + R_S)g_{ds} + 2\pi f_T C_{gd} R_G}}$$

(3.2)

$$C_{gs} \sim \frac{\varepsilon}{t_B} L_G$$

(3.3)  $g_{ds} = \frac{q \mu n_s(t_B)}{L_G}$  (3.4)  $g_m = \frac{\varepsilon}{t_B} v$  (3.5)

It is possible to understand that high frequency optimization involves [28]:

- Down-scaling the gate length (to reduce  $C_{gs}$ )

- Down-scaling the barrier thickness (to reduce  $g_{ds}$  and increase  $g_m$ )

- Improve the electron confinement (to reduce  $g_{ds}$ )

- Improve electron transport properties (to increase  $f_T$  and  $g_m$ )

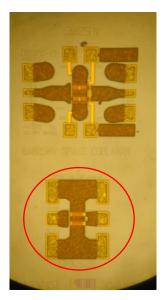

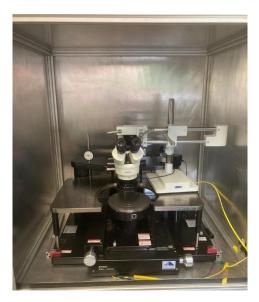

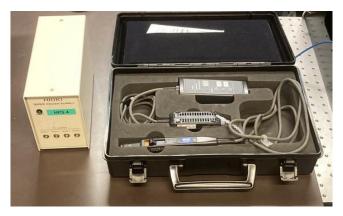

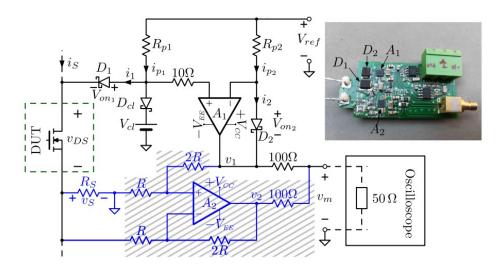

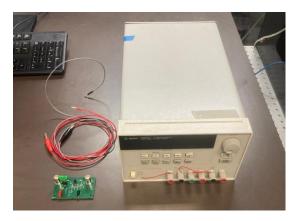

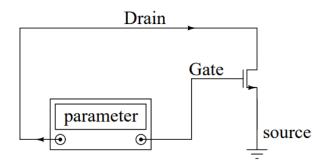

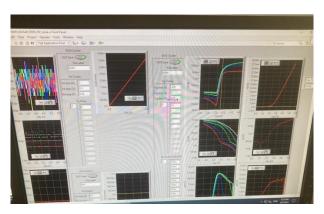

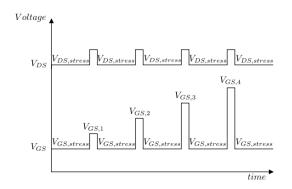

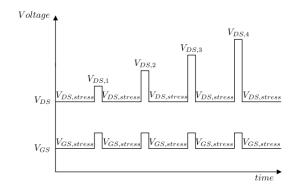

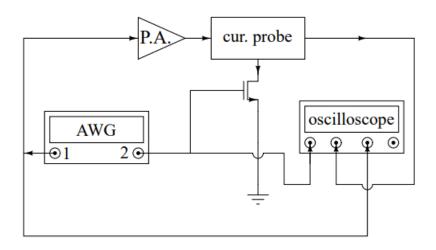

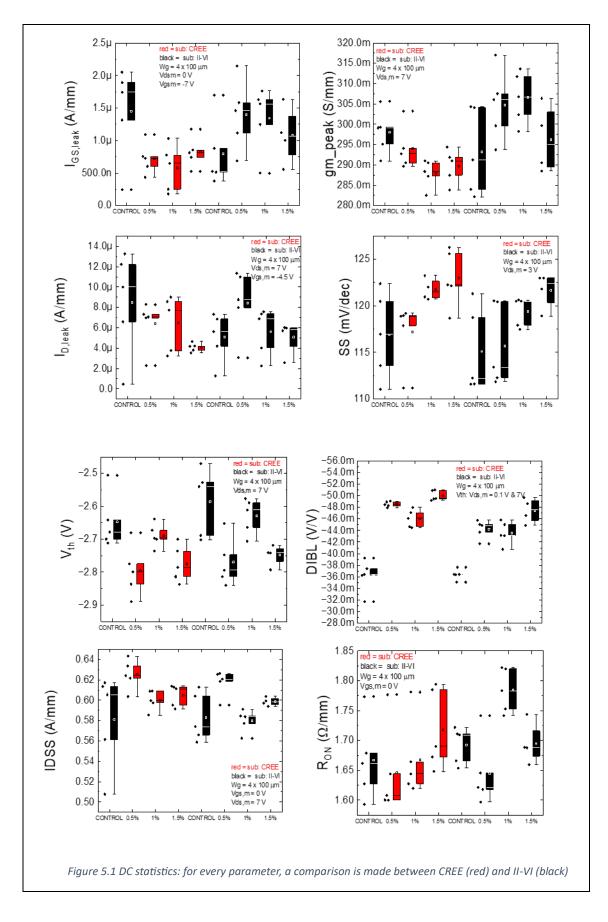

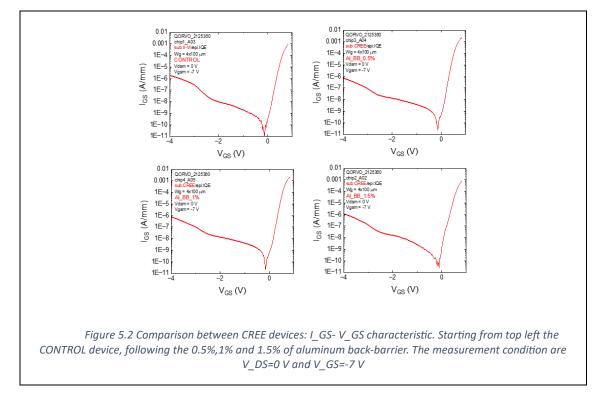

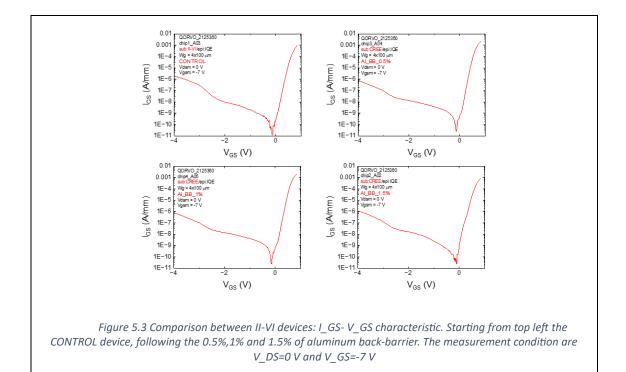

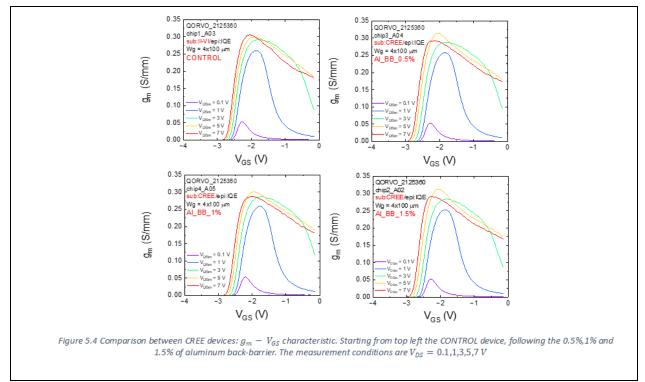

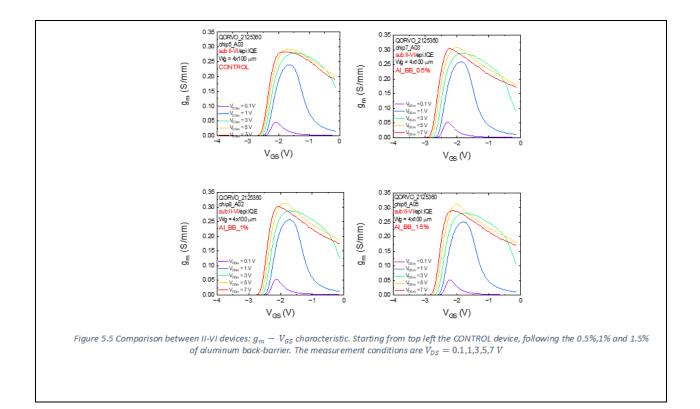

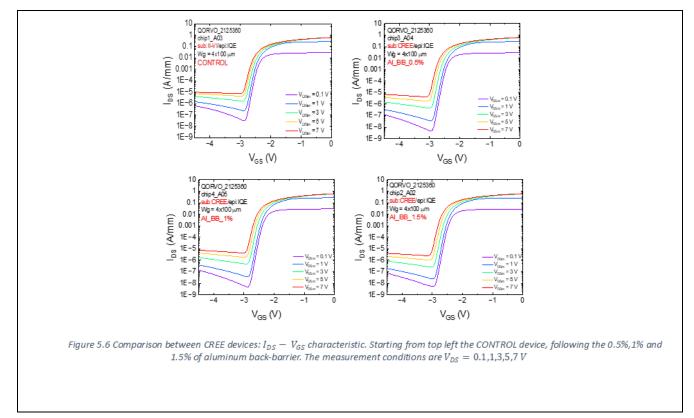

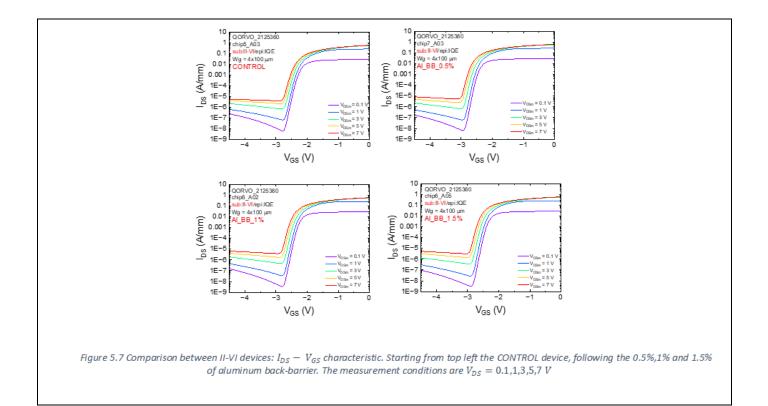

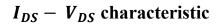

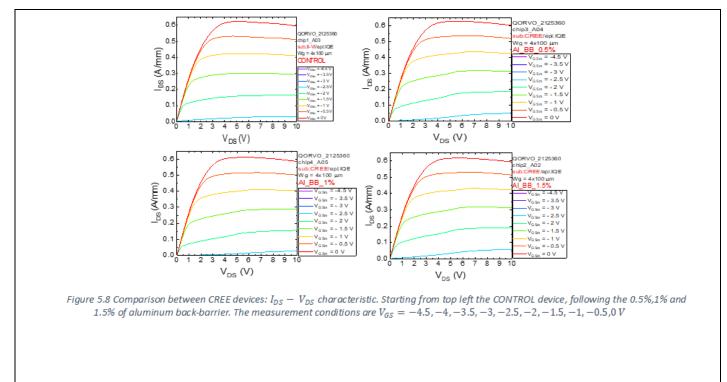

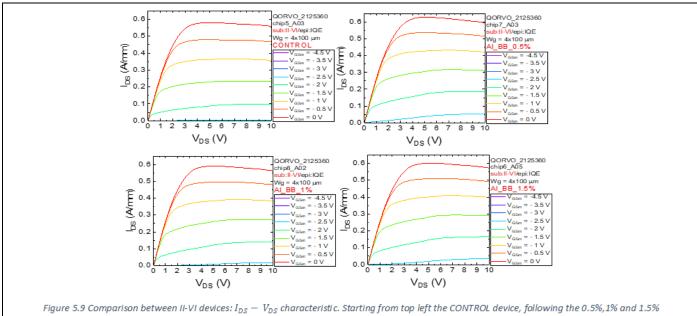

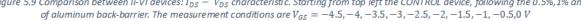

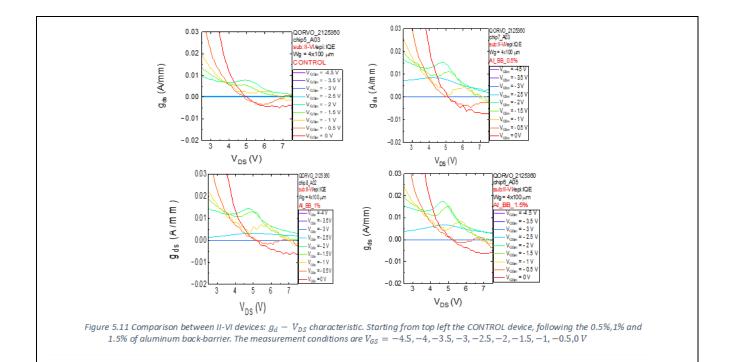

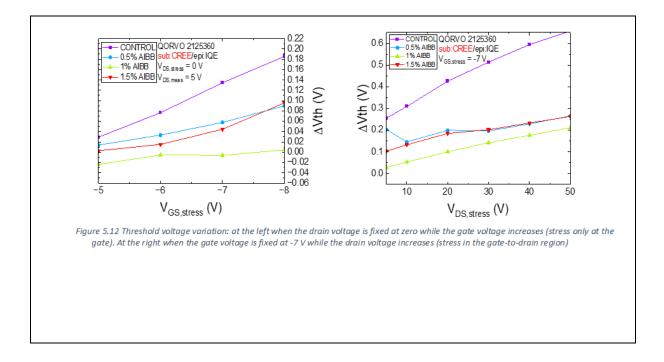

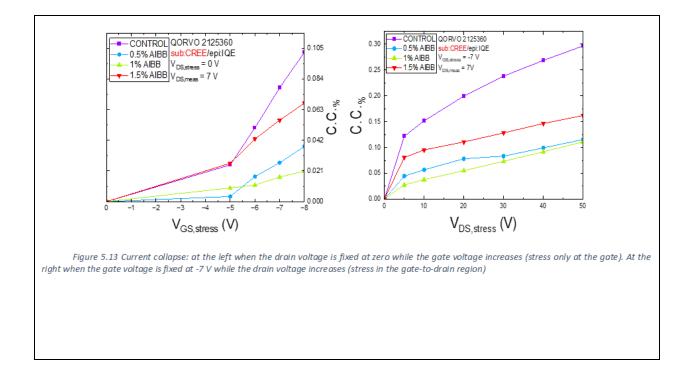

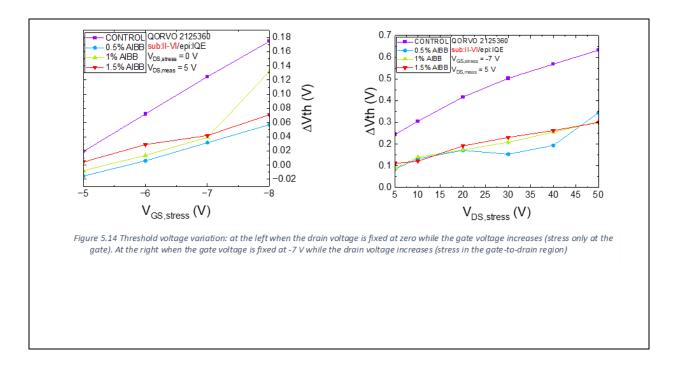

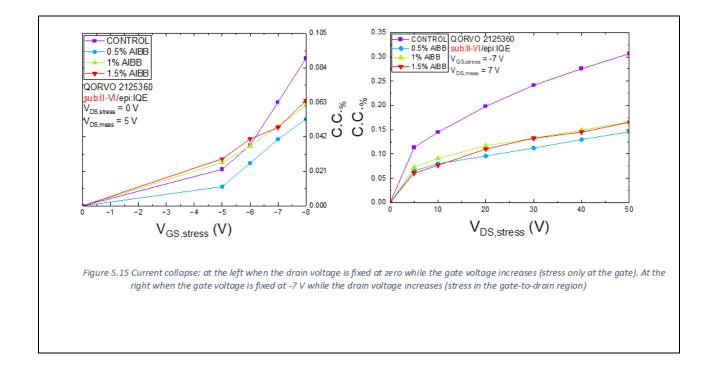

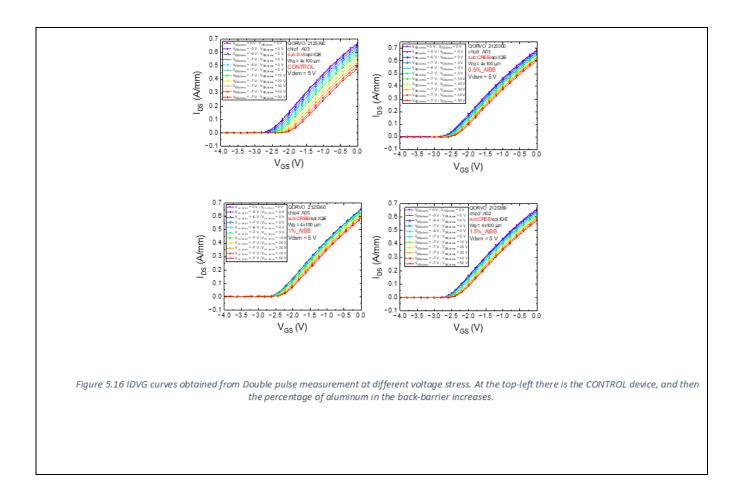

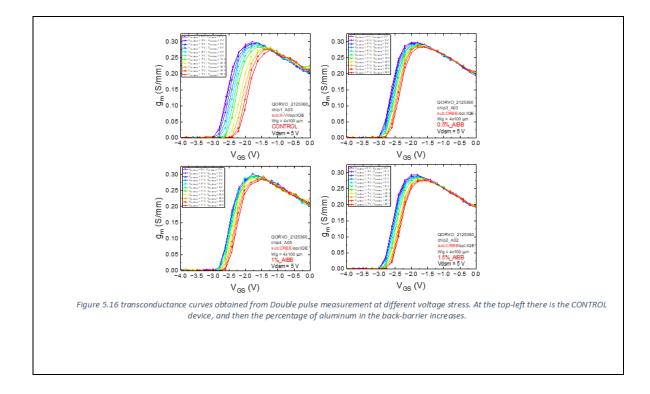

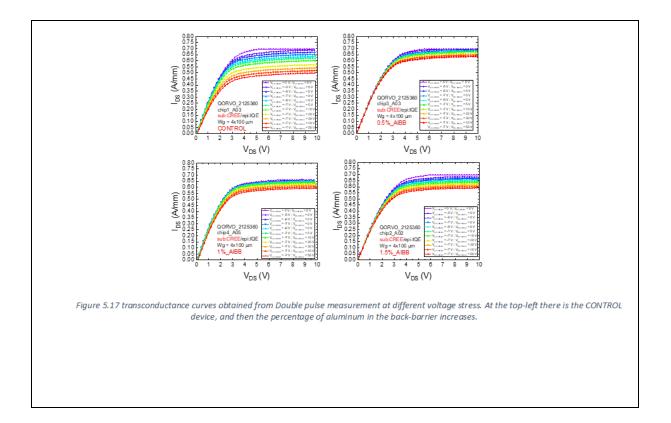

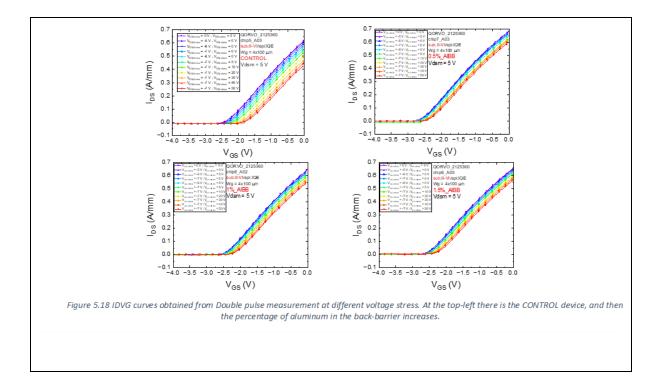

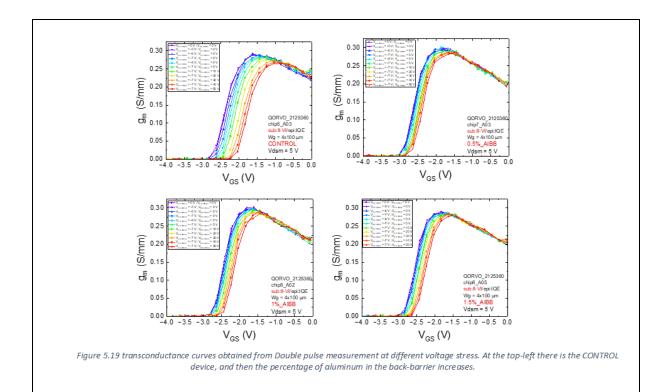

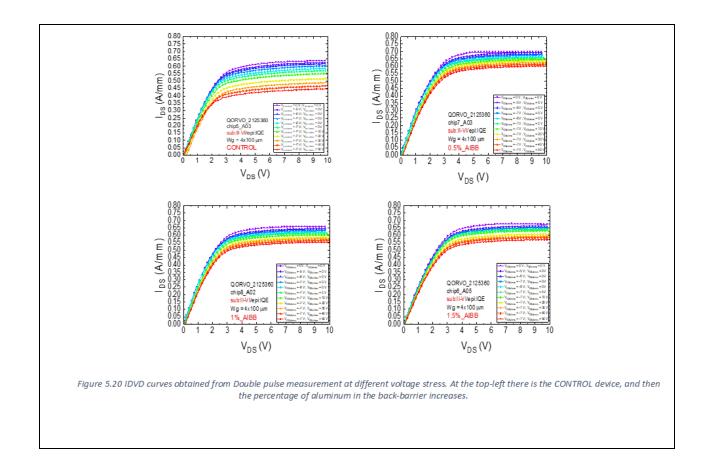

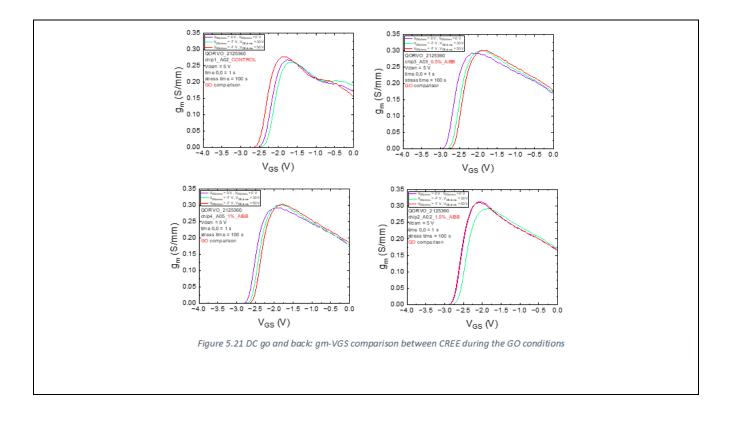

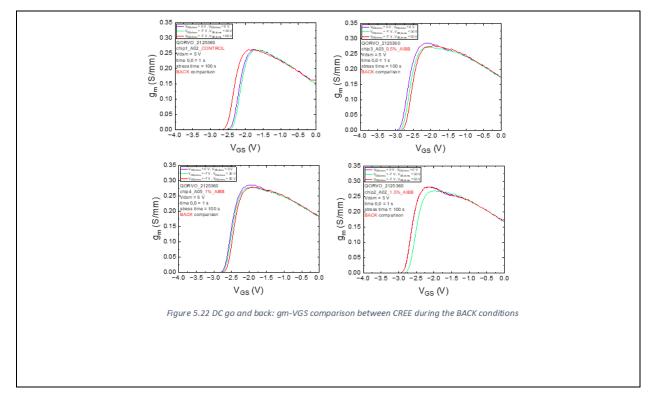

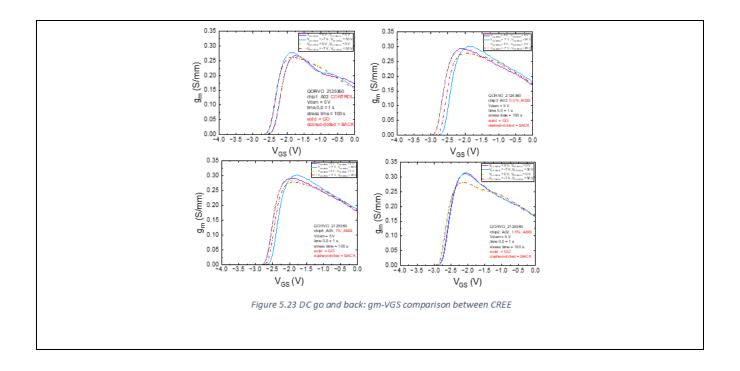

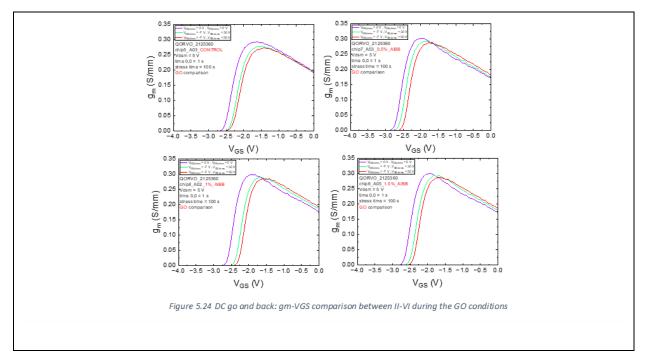

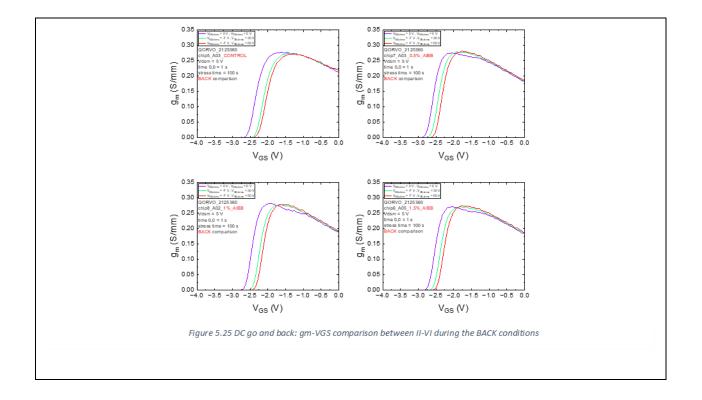

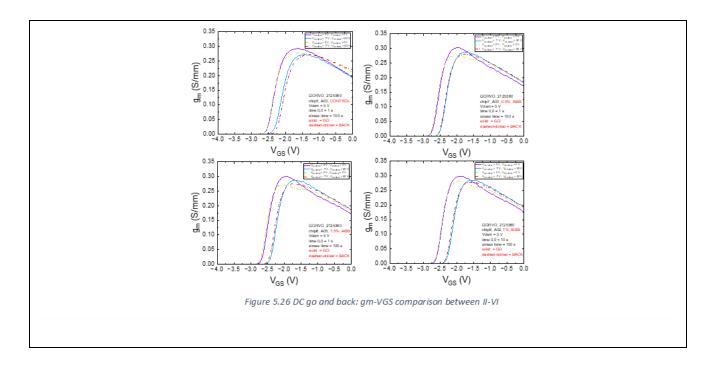

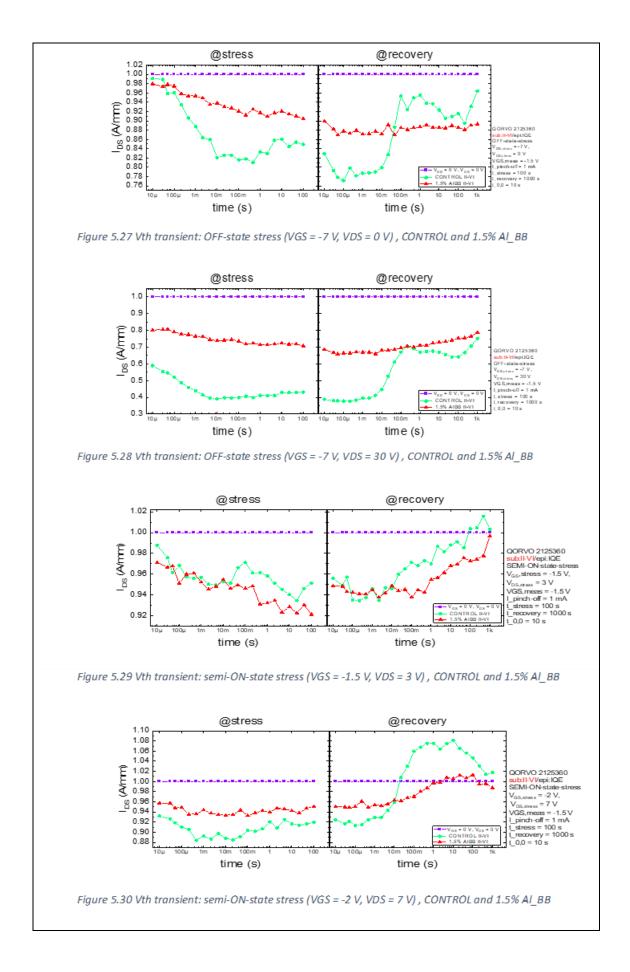

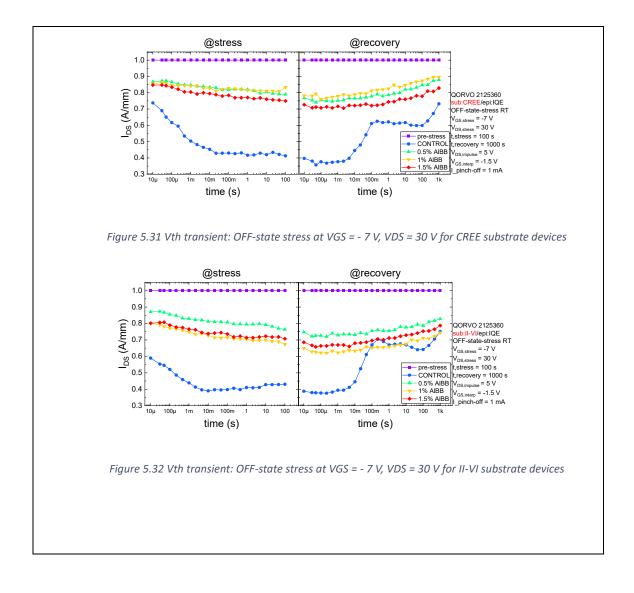

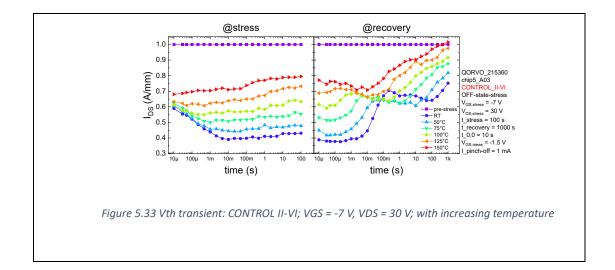

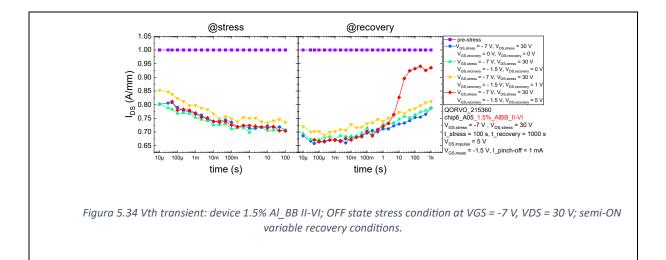

In simple terms, doubling the cutoff frequency  $(f_T)$  and maximum oscillation frequency  $(f_{max})$  requires halving the lateral and vertical dimensions while reducing resistances per unit gate width (in  $\Omega$ ·mm) by half and doubling conductances per unit gate width (in  $\frac{s}{mm}$ ). This scaling approach ensures that the electrostatic potential profile (and consequently the behaviour of electrons) within the transistor remains consistent. The channel aspect ratio, represented as the ratio of gate length  $(L_G)$  to gate-to-channel distance (d), i.e.,  $\frac{L_G}{d}$ , serves as a structural parameter to gauge transistor scaling behavior. A small channel aspect ratio compromises the gate's control over drain current due to incomplete electrostatic isolation between the source and drain. This results in reduced transconductance  $(g_m)$ , negative threshold voltage (Vth) shifts, increased drain-induced barrier lowering (DIBL), and amplified output conductance  $(g_d)$ . These phenomena collectively termed "short-channel effects" are notably observed in ultrashort gate HEMTs with gate lengths below 100 nm. The requirement to avert severe short-channel effects has been both theoretically (Awano et al., 1989) and experimentally (Jessen et al., 2007) confirmed. It's been shown that an aspect ratio of  $Lg/d \ge 5$  is necessary to mitigate these effects. Short-channel effects pose significant constraints on high-frequency transistor scaling as the reduction in  $g_m$  and increase in  $g_d$  directly impact both  $f_T$  and  $f_{max}$ , as indicated in the equations above.