# FUNCTION IMPLEMENTATION IN A MULTI-GATE

# JUNCTIONLESS FET STRUCTURE

A Dissertation in Electrical and Computer Engineering and Physics

Presented to the Faculty of the University of Missouri–Kansas City in partial fulfillment of the requirements for the degree

# DOCTOR OF PHILOSOPHY

by Sehtab Hossain

M. S., University of North Dakota, Grand Forks, USA, 2015 B. Sc., Islamic University of Technology, Dhaka, Bangladesh, 2008

Kansas City, Missouri 2023

©2023

Sehtab Hossain

ALL RIGHTS RESERVED

# FUNCTION IMPLEMENTATION IN A MULTI-GATE JUNCTIONLESS FET STRUCTURE

Sehtab Hossain, Candidate for the Doctor of Philosophy Degree University of Missouri–Kansas City, 2023

#### ABSTRACT

This dissertation explores designing and implementing a multi-gate junctionless field-effect transistor (JLFET) structure and its potential applications beyond conventional devices. The JLFET is a promising alternative to conventional transistors due to its simplified fabrication process and improved electrical characteristics. However, previous research has focused primarily on the device's performance at the individual transistor level, neglecting its potential for implementing complex functions. This dissertation fills this research gap by investigating the function implementation capabilities of the JLFET structure and proposing novel circuit designs based on this technology.

The first part of this dissertation presents a comprehensive review of the existing literature on JLFETs, including their fabrication techniques, operating principles, and performance metrics. It highlights the advantages of JLFETs over traditional metal-oxide-semiconductor field-effect transistors (MOSFETs) and discusses the challenges associated with their implementation. Additionally, the review explores the limitations of conventional transistor technologies, emphasizing the need for exploring alternative device architectures.

Building upon the theoretical foundation, the dissertation presents a detailed analysis of the multi-gate JLFET structure and its potential for realizing advanced functions. The study explores the impact of different design parameters, such as channel length, gate oxide thickness, and doping profiles, on the device performance. It investigates the trade-offs between power consumption, speed, and noise immunity, and proposes design guidelines for optimizing the function implementation capabilities of the JLFET. To demonstrate the practical applicability of the JLFET structure, this dissertation introduces several novel circuit designs based on this technology. These designs leverage the unique characteristics of the JLFET, such as its steep subthreshold slope and improved on/off current ratio, to implement complex functions efficiently. The proposed circuits include arithmetic units, memory cells, and digital logic gates. Detailed simulations and analyses are conducted to evaluate their performance, power consumption, and scalability.

Furthermore, this dissertation explores the potential of the JLFET structure for emerging technologies, such as neuromorphic computing and bioelectronics. It investigates how the JLFET can be employed to realize energy-efficient and biocompatible devices for applications in artificial intelligence and biomedical engineering. The study investigates the compatibility of the JLFET with various materials and substrates, as well as its integration with other functional components.

In conclusion, this dissertation contributes to the field of nanoelectronics by providing a comprehensive investigation into the function implementation capabilities of the multi-gate JLFET structure. It highlights the potential of this device beyond its individual transistor performance and proposes novel circuit designs based on this technology. The findings of this research pave the way for the development of advanced electronic systems that are more energy-efficient, faster, and compatible with emerging applications in diverse fields.

## APPROVAL PAGE

The faculty listed below, appointed by the Dean of the School of Graduate Studies, have examined a dissertation titled "Function Implementation in a Multi-Gate Junctionless FET Structure," presented by Sehtab Hossain, candidate for the Doctor of Philosophy degree, and certify that in their opinion it is worthy of acceptance.

## Supervisory Committee

Mostafizur Rahman, Ph.D., Committee Chair Department of Electrical & Computer Engineering

Masud Chowdhury, Ph.D. Department of Electrical & Computer Engineering

Mahbube Khoda Siddiki, Ph.D. Department of Electrical & Computer Engineering

> Paul Rulis, Ph.D. Department of Physics & Astrophysics

Jejung Lee, Ph.D. Department of Geoscience & Geoengineering

| Contents                                   |

|--------------------------------------------|

| ABSTRACTiii                                |

| ILLUSTRATIONS ix                           |

| TABLES xi                                  |

| ACRONYMS xii                               |

| ACKNOWLEDGEMENTS xiv                       |

| 1. INTRODUCTION                            |

| 1.1 Problem Statement1                     |

| 1.1.1 End of Moore's Law2                  |

| 1.1.2 Quantum Mechanical Problem6          |

| 1.2 Motivation and Scope                   |

| 1.3 Summary9                               |

| 1.4 Organization10                         |

| 2. LITERATURE REVIEW12                     |

| 2.1 Related Work                           |

| 2.2 Review of Gate Material & Gate Oxide14 |

| 2.2.1 Importance of Gate Material15        |

| 2.2.2 Importance of Gate Oxide18           |

| 2.3 Advanced Technology Nodes20            |

| 3 | . CROSSTALK PRINCIPLE                    | 29 |

|---|------------------------------------------|----|

|   | 3.1 Crosstalk Terminology                | 29 |

|   | 3.2 Kinds of Crosstalk                   | 30 |

|   | 3.3 Crosstalk Location                   | 31 |

|   | 3.4 Capacitive Crosstalk                 | 32 |

|   | 3.5 Inductive Crosstalk                  | 35 |

|   | 3.6 Switching Noise                      | 37 |

|   | 3.7 Effects of Crosstalk                 | 38 |

|   | 3.8 Crosstalk Mitigation Techniques      | 38 |

| 4 | . EXPERIMENT OF CROSSTALK                | 41 |

| 5 | . DEVICE ARCHITECTURE                    | 53 |

|   | 5.1 Device Physics of 2D Architecture    | 54 |

|   | 5.2 Device Physics Of 3D Architecture    | 56 |

|   | 5.2 Elementary Logic Device Architecture | 57 |

|   | 5.3 Complex Logic Device Architecture    | 61 |

|   | 5.4 Polymorphic Behavior of the Devices  | 62 |

| 6 | . SIMULATION & RESULTS                   | 64 |

|   | 6.1 Simulation Environment               | 64 |

|   | 6.1.1 Device Architecture Simulation     | 64 |

|   | 6.1.2 Device Characterization Simulation | 67 |

|   | 6.2 Methodology                              | 73  |

|---|----------------------------------------------|-----|

|   | 6.3 Result & Discussion                      | 74  |

|   | 6.3.1 2 D Devices Result & Discussion        | 74  |

|   | 6.3.2 3 D Devices Result & Discussion        | 77  |

|   | 6.4 Random Dopant Fluctuation (RDF) Analysis | 82  |

|   | 6.5 Polymorphism Analysis                    | 85  |

|   | 6.6 System-Level Integration                 | 85  |

|   | 6.7 Crosstalk Circuits Comparison            | 87  |

| 7 | . CONCLUSION                                 | 89  |

| R | EFERENCES                                    | 95  |

| V | /ITA                                         | 118 |

# ILLUSTRATIONS

| Figure | Pag                                                                  | е |

|--------|----------------------------------------------------------------------|---|

| 1      | Evolution of CPU transistor count and gate length                    | 7 |

| 2      | Evolution of CPU and GPU1                                            | 8 |

| 3      | Evolution of Transistor count in CPU1                                | 8 |

| 4      | Performance and Power consumption Improvement over Technology node19 | 9 |

| 5      | Energy Quantization in the substrate                                 | ) |

| 6      | Electron Concentration Distribution                                  | 1 |

| 7      | Crosstalk Phenomena                                                  | 5 |

| 8      | Far End and Near End location of Crosstalk40                         | 5 |

| 9      | Capacitive Crosstalk4                                                | 7 |

| 10     | Capacitive Crosstalk mechanism                                       | 8 |

| 11     | Inductive Crosstalk                                                  | ) |

| 12     | Crosstalk AND circuit                                                | 7 |

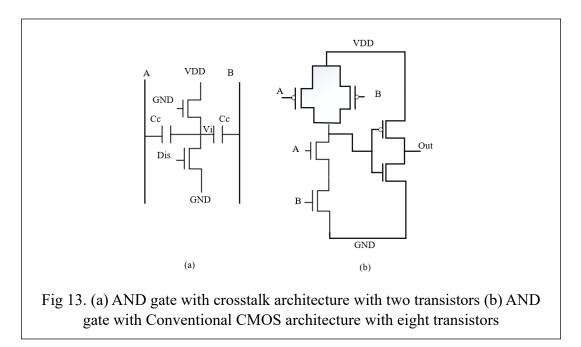

| 13     | And gate with crosstalk with two transistors                         | 8 |

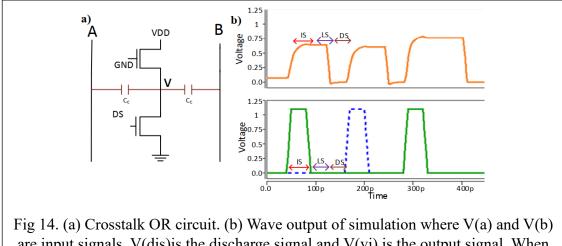

| 14     | Crosstalk OR circuit                                                 | 9 |

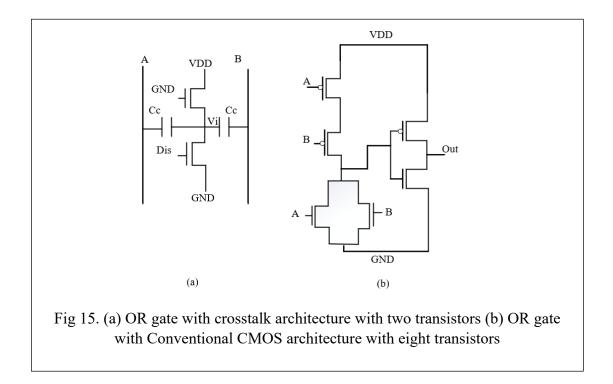

| 15     | OR gate with crosstalk with two transistors                          | ) |

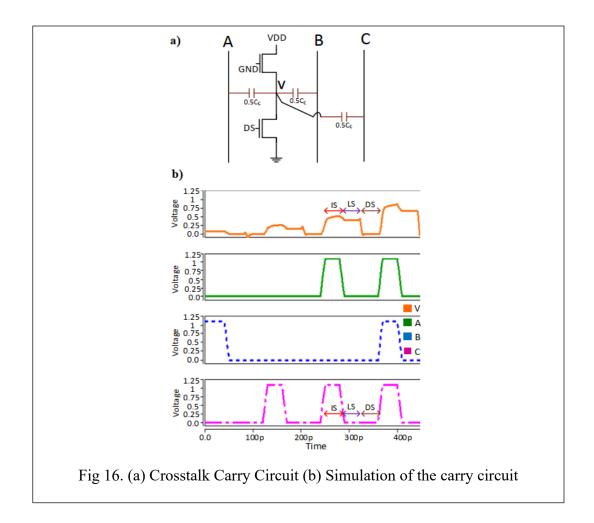

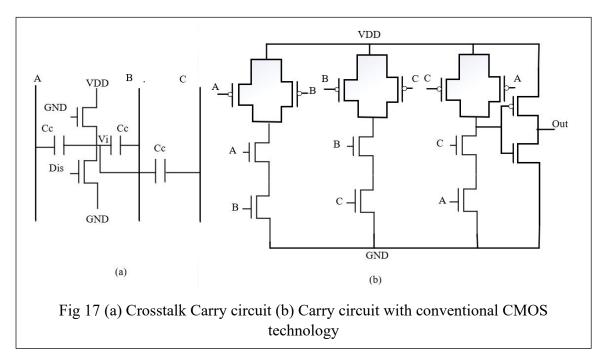

| 16     | Crosstalk Carry circuit                                              | 1 |

| 17     | Crosstalk Carry circuit with CMOS circuit Comparison                 | ; |

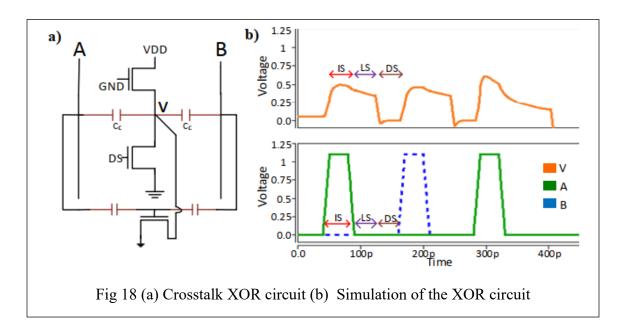

| 18     | Crosstalk XOR circuit                                                | 4 |

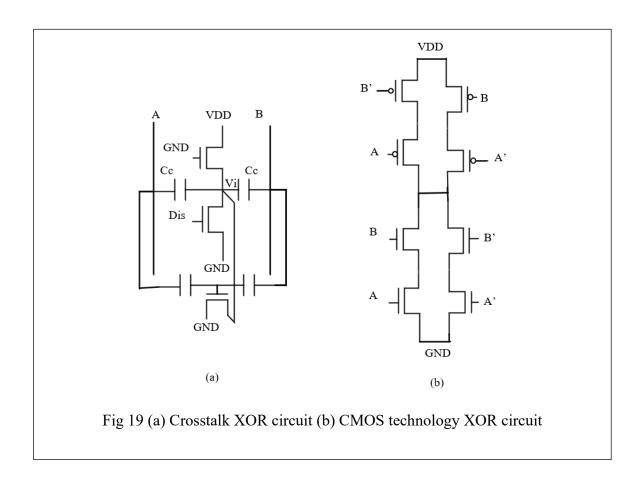

| 19     | Comparison of Crosstalk and CMOS XOR circuit                         | 6 |

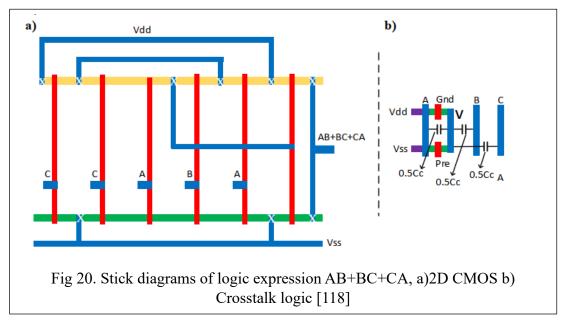

| 20     | Stick Diagram of logic expression AB+BC+CA                           | 8 |

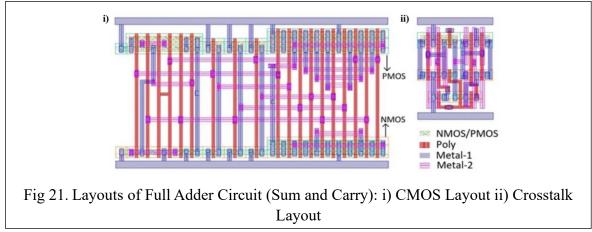

| 21     | Layout of Full Adder                                                 | 8 |

| 22     | Device structure and characteristics of Planar Double Gate FET7      | 1 |

| 23     | Switching Mechanism of Elementary gates7                             | 3 |

| 24     | Device structure of proposed JLFET                                   | 5 |

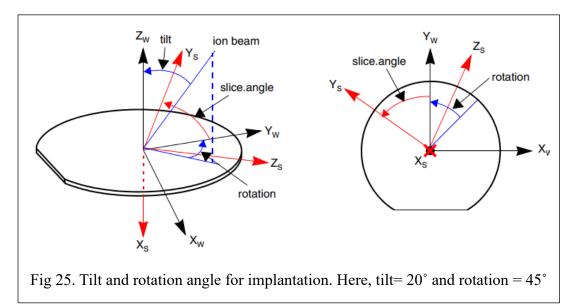

| 25     | Tilt and Rotation Angle                                              | 1 |

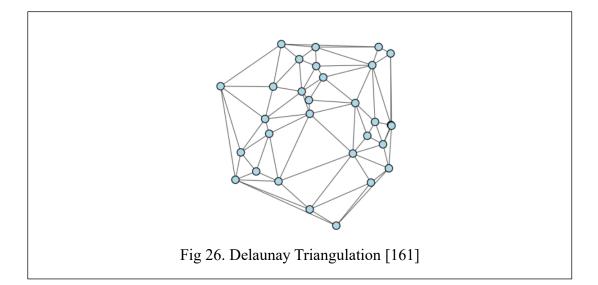

| 26     | Delaunay Triangulation                                               | 2 |

| Figure | Pa                                    | age |

|--------|---------------------------------------|-----|

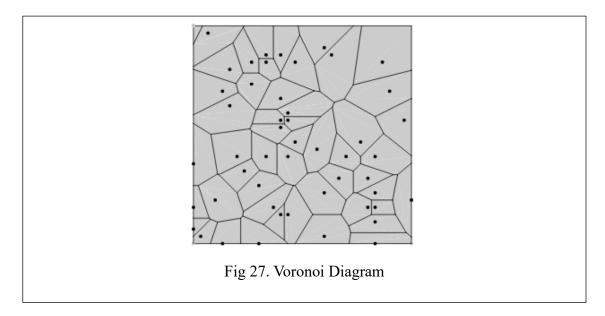

| 27     | Voronoi Diagram                       | 82  |

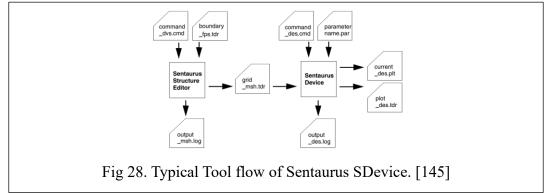

| 28     | Tool flow of SDevice                  | .83 |

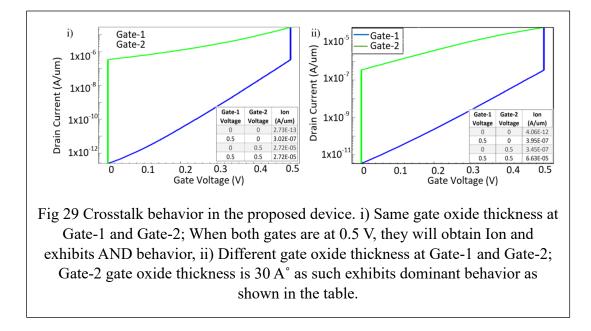

| 29     | Crosstalk Behavior of 2D Device       | .91 |

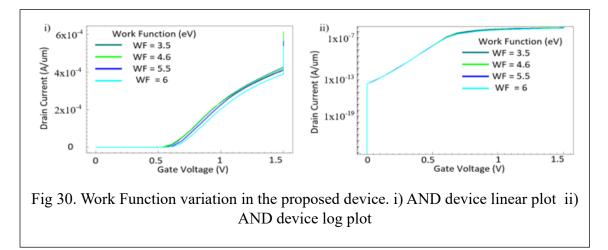

| 30     | Work Function variation               | .91 |

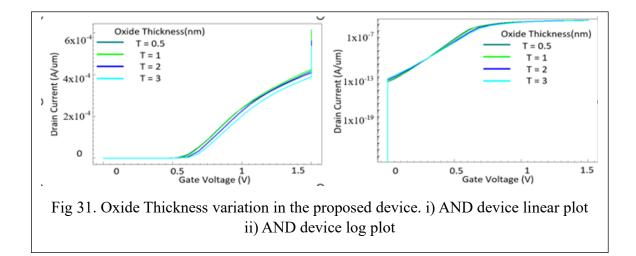

| 31     | Oxide Thickness Variation             | .92 |

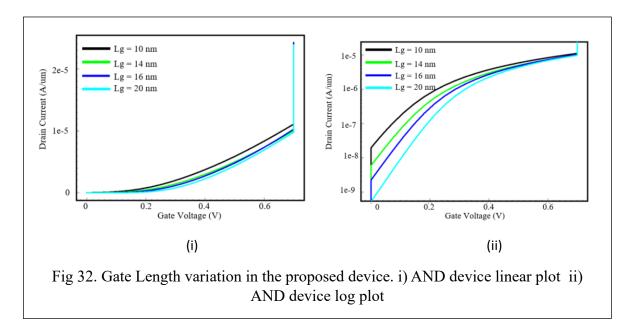

| 32     | Gate Length Variation                 | .92 |

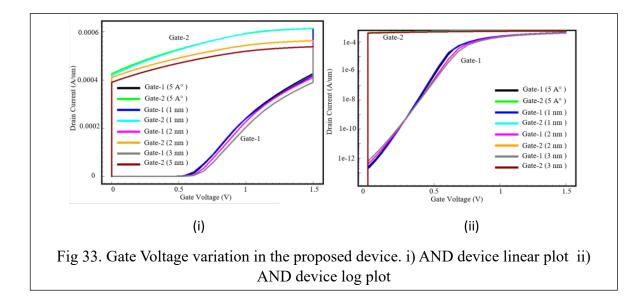

| 33     | Gate Voltage Variation                | .93 |

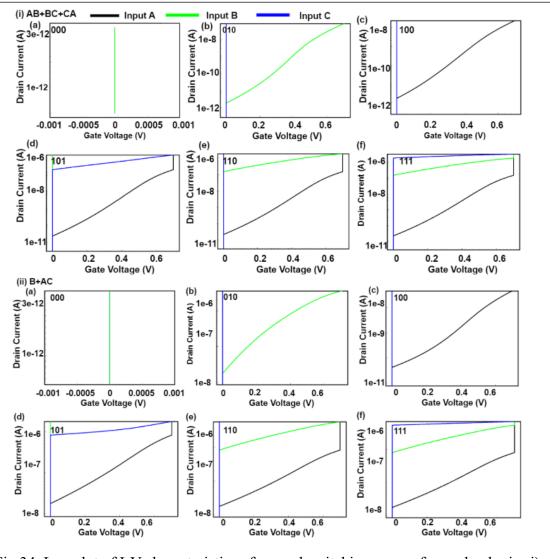

| 34     | IV of several switching cases         | .94 |

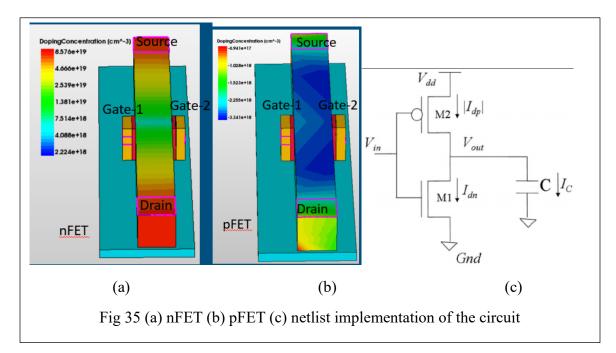

| 35     | nFET, pFET and netlist implementation | 102 |

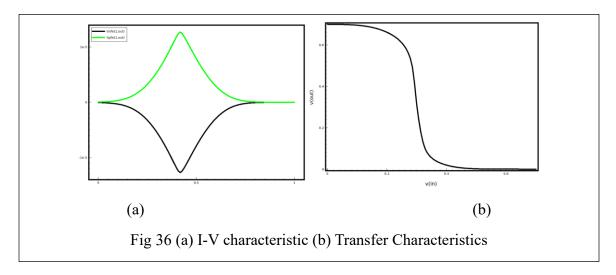

| 36     | I-V and Transfer Characteristics      | 102 |

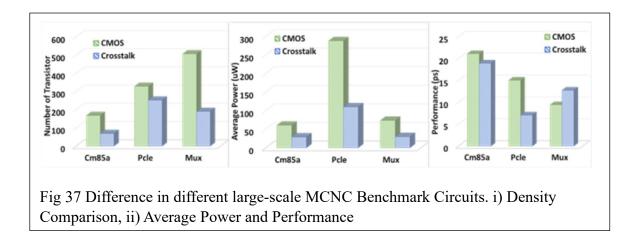

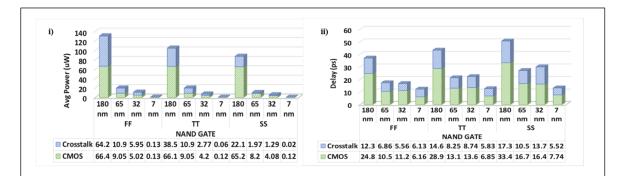

| 37     | MCNC Benchmark circuits               | 103 |

| 38     | Technology Scaling impact             | 104 |

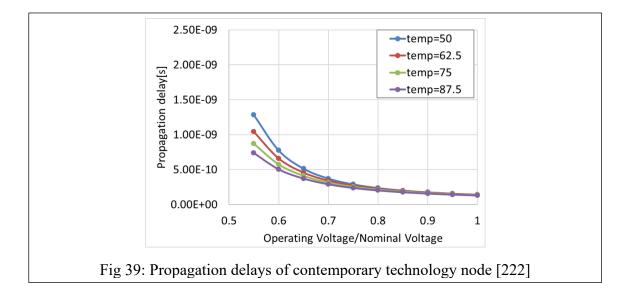

| 39     | Propagation Delay                     | 106 |

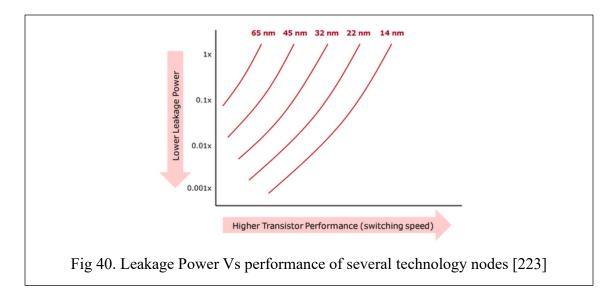

| 40     | Leakage Power Vs Performance          | 107 |

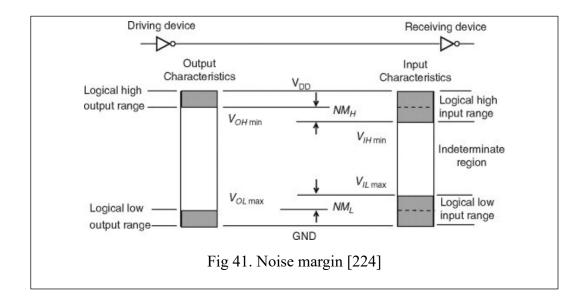

| 41     | Noise margin                          | 108 |

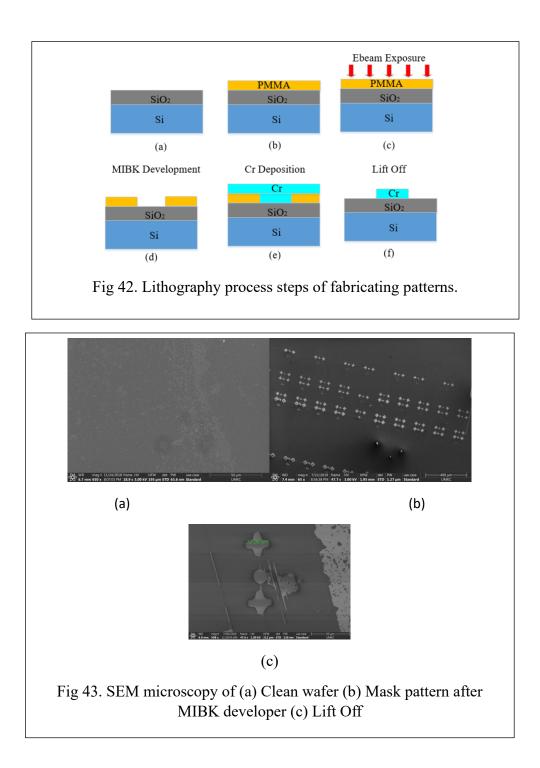

| 42     | Lithography Process                   | 109 |

| 43     | SEM Microscopy1                       | 109 |

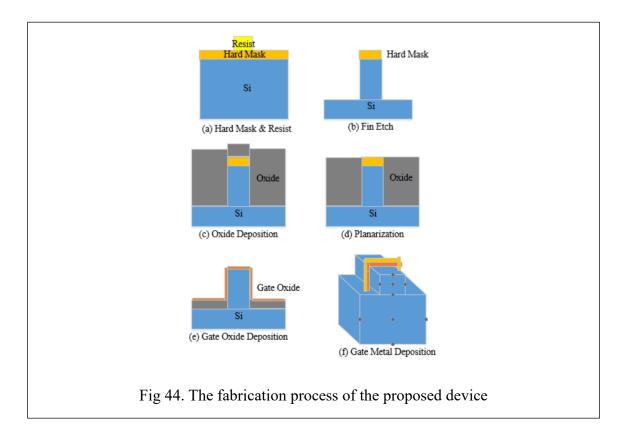

| 44     | Fabrication Process                   | 110 |

# TABLES

| Tables | I                                                               | Page |

|--------|-----------------------------------------------------------------|------|

| 1      | List of Gate material along with work function                  | 31   |

| 2      | Dielectric Constant of some Gate materials                      | 34   |

| 3      | Different Technology Node                                       | 42   |

| 4      | 2D Device Architecture                                          | 70   |

| 5      | Device Dimension for implementing the different logic functions | 75   |

| 6      | Elementary Logic Total Output Current                           | 76   |

| 7      | Complex Logic Total Output Current                              | 96   |

| 8      | Power, delay and Density Comparison of Elementary Logics        | 97   |

| 9      | Power, delay and Density Comparison of Complex Logics           | 97   |

| 10     | Comparison of regular AND device and RDF-affected Device        | 99   |

| 11     | Comparison of regular AB+BC+CA device and RDF-affected Devic    | .102 |

# ACRONYMS

| JLFET  | Junctionless Field Effect Transistor              |

|--------|---------------------------------------------------|

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |

| MVL    | Multi Valued Logic                                |

| IC     | Integrated Circuit                                |

| GIDL   | Gate Induced Drain Leakage                        |

| DIBL   | Drain Induced Barrier Lowering                    |

| ALU    | Arithmetic Logic Unit                             |

| TCAD   | Technology Computer Aided Design                  |

| DOE    | Design Of Experiment                              |

| NIR    | Near Infrared Region                              |

| MTJ    | Magnetic Tunneling Junction                       |

| STT    | Spin Transfer Torque                              |

| IoNT   | Internet of Nano-Things                           |

| SCE    | Short Channel Effect                              |

| RDF    | Random Dopant Fluctuation                         |

| WFV    | Work Function Variance                            |

| DMG    | Dual Metal Gate                                   |

| XRD    | X-ray Diffraction                                 |

| AFM    | Atomic Force Microscopy                           |

| SEM    | Scanning Electron Microscopy                      |

| ADC    | Analog Digital Converter                          |

| SOI    | Silicon On Insulator                              |

| MHK    | Metal High K                                      |

| DSL    | Dual Stress Liner                                 |

| HARP   | High Aspect Ratio Process                         |

| ULK   | Ultra Low K                           |

|-------|---------------------------------------|

| RF    | Radio Frequency                       |

| NBTI  | Negative Bias Temperature Instability |

| BTI   | Bias Temperature Instability          |

| EOL   | End Of Life                           |

| СР    | Central Process                       |

| SC    | System Control                        |

| BTBT  | Band To Band Tunneling                |

| HCD   | Hot Carrier Degradation               |

| TAT   | Trap Assisting Tunneling              |

| NSFET | Nano Sheet Field Effect Transistor    |

| HNM   | Hold Noise Margin                     |

| RNM   | Read Noise Margin                     |

| WM    | Write Margin                          |

| FEOL  | Front End Of Line                     |

| BEOL  | Back End Of Line                      |

| LFET  | Lateral FET                           |

| VFET  | Vertical FET                          |

| FDSOI | Fully Depleted Silicon On Insulator   |

| QCL   | Quantum Cascaded LASER                |

| ALD   | Atomic Layer Deposition               |

| CVD   | Chemical Vapor Deposition             |

#### ACKNOWLEDGEMENTS

I would like to express my deepest gratitude and appreciation to all those who have contributed to the completion of this dissertation.

First and foremost, I am immensely grateful to my advisor, Mostafizur Rahman, Ph.D. for his guidance, expertise, and unwavering support throughout this research journey. His insightful feedback, constructive criticism, and encouragement have been invaluable in shaping this dissertation. I am grateful for his mentorship and the trust he placed in me to undertake this project.

I sincerely thank the members of my dissertation committee, Masud Rahman, Ph.D., Mahbube Khoda Siddiki, Ph.D., Paul Rulis, Ph.D., and Jejung Lee, Ph.D. for their valuable insights, thoughtful suggestions, and critical evaluations. Their expertise and academic rigor have significantly enriched the quality of this dissertation. I am grateful for their time, dedication, and willingness to share their knowledge.

I would like to acknowledge the staff and faculty of the University of Missouri Kansas City for providing an intellectually stimulating environment and access to resources that have facilitated the progress of this research. The assistance and cooperation of the library staff, research facilities, and administrative personnel have been instrumental in conducting experiments, accessing relevant literature, and managing the administrative aspects of this project.

My heartfelt appreciation goes to my family for their unwavering support, love, and encouragement throughout my academic journey. Their understanding, patience, and belief in my abilities have been a constant source of motivation. I am grateful for their sacrifices and the countless ways they have contributed to my personal and professional growth.

I am indebted to my friends and colleagues who have been a constant source of inspiration and motivation. Their stimulating discussions, insightful feedback, and camaraderie have played a significant role in shaping my ideas and enhancing my research capabilities. Their support and encouragement during challenging times are deeply appreciated. I would also like to acknowledge the financial support provided by UMKC. Their support has enabled me to pursue this research and achieve the goals outlined in this dissertation. I am grateful for their investment in my education and research endeavors.

Lastly, I would like to express my gratitude to all those who have contributed to this research field, both directly and indirectly. The collective efforts of researchers, scholars, and scientists have laid the foundation for this dissertation. I am grateful for their groundbreaking work, which has paved the way for further exploration and advancements in this field.

In conclusion, the completion of this dissertation would not have been possible without the guidance, support, and contributions of the aforementioned individuals and organizations. Their involvement has shaped my academic journey and enriched my research experience. I am deeply grateful for their assistance and encouragement, and I acknowledge their profound impact on the successful completion of this dissertation.

#### **CHAPTER 1**

### INTRODUCTION

With the Integrated Circuit (IC) burgeoning, Moore's law has slowed down. Relentless scaling down of IC appears to be difficult to follow Moore's law. To address this problem, some solutions are provided. Some alternate solutions provide novel devices like Multi-Valued Logic (MVL), and Magnetic Transistors. But these devices have their limitations. Embedding logic devices is one of the solutions. We propose embedding logic standalone device. Instead of multiple devices to implement a Boolean logic, the embedding logic device has only one device to perform Boolean logic. However, a standalone device was capable of performing elementary Boolean functions like NAND/NOR. In this research, we extend our research to complex Boolean Logic which will be capable of performing multiple Boolean Logic operations.

### **1.1 Problem Statement**

Integrated Circuit (IC) has changed the socio-economic perspective of the electronics industry. The advent of IC leads to the electronics device revolution and paved the path for advanced technologies. The advancement of IC leads to scaling down transistors to reduce power consumption and increase transistor counts. Transistor count plays a crucial role in processor speed and IC throughput. The transistor industry follows the rules of Moore's law as a standard for IC production and the advancement of IC. Progress was made gracefully until the advent of the 20 nm technology node. From 20 nm technology, scaling down the technology pode becomes very complex with excessive

complex manufacturing processes along with circuit integration. In the case of manufacturing, oxide thickness becomes a problem. As advanced technology nodes have much thinner gate oxide, it was very difficult to grow a one or two nm Silicone dioxide  $(SiO_2)$  layer. To address this problem, the gate oxide is changed to Hafnium Oxide (HfO<sub>2</sub>). Along with manufacturing problems, device physics problems also arise. The advanced node transistors suffer from short channel effects like Gate Induced Drain Leakage (GIDL), Drain Induced Barrier Lowering (DIBL), punch through, etc. The short channel effects problems are resolved eventually but new problems appear. The problem of integration in the circuit appears to be greater in this regard. As transistors' gate pitch is getting smaller, integrating whole transistors as a circuit becomes a challenge. After integration, power consumption increases as the transistor number increases. Aggressive scaling down makes the gate size so short that it is very close to an atomic distance of Silicon. Increasing transistor number also raises the problem of excessive heat and heat transfer becomes an issue. As the scaling down process scales down all physical parameters, each technology node demands complete alternation of manufacturing processes.

## 1.1.1 End of Moore's Law

The major milestone in semiconductor electronics is the invention of CMOS in 1963. In 1971, Intel introduced the first commercial CPU (Intel 4004) and in 1976 RCA started the fabrication of CDP 1802, the first Si CMOS CPU. Since then, the transistor count doubled every two years – a trend known as Moore's law. In his 1975 IEDM paper, Gordon Moore discussed the three measures to be taken to continuously increase the number of transistors per chip, which are (i) shrinking the size of the individual transistors (scaling), (ii) increasing the chip area, and (iii) improving device and circuit design. At this point, we are very close to the edge of scaling and it is feared that Moore's may no longer be applicable.

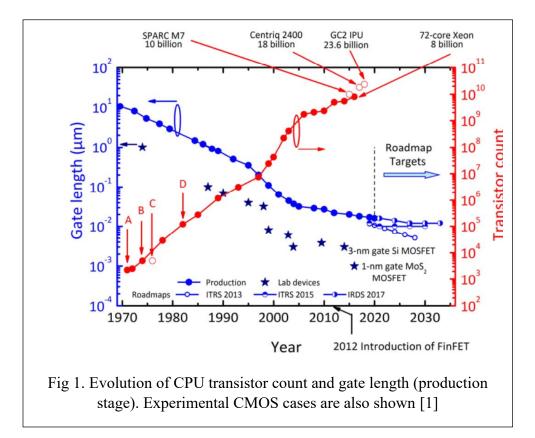

Fig. 1 shows the evolution of CPU transistor count and MOSFET gate length, indicating that Moore's Law and CMOS scaling are still alive.

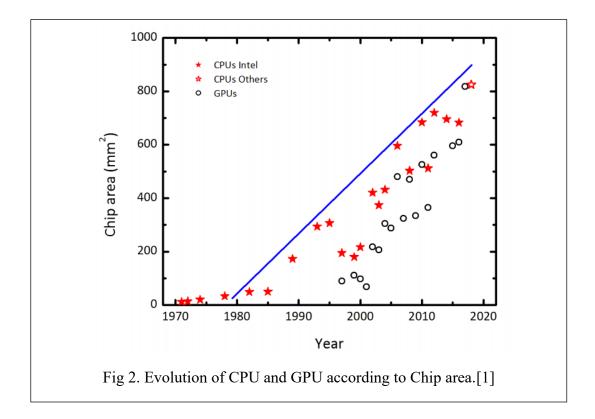

Gate length scaling represents an achievement of engineering art. Conversely, it is a kind of "steamroller tactic" that sooner or later will become inappropriate. With the increasing demand for computation and processing density and transistor count increased relentlessly not only for CPU but also for GPU. As GPU has a different architecture than CPU, its architecture and circuit are different. Fig. 2 depicts the chip area for CPU and GPU. It is noticed that after 2010 CPU and GPU areas increased parallelly.

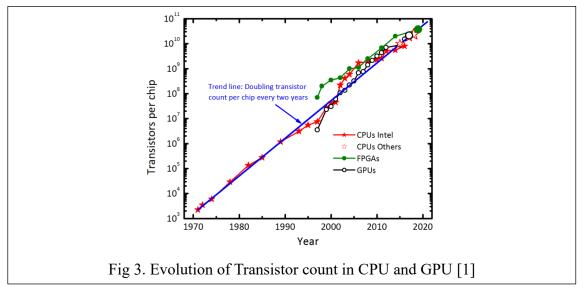

The sole purpose of scaling is to increase performance and decrease cost. With the increment of transistor count, increase the performance. With the advent of FinFET, transistor count skyrocketed as well as performance. Fig. 3 exhibits the evolution of transistor count for CPU and GPU.

Amid this situation, the alternate solution is a hardware accelerator and alternate channel material.

Hardware accelerators are not general-purpose CPUs. GPU, TPU, and FPGA will be categorized as hardware accelerators. Because of special architecture, hardware accelerators are used for heavy computation. Specially TPU is used for heavy computation. TPU has a special architecture of tensor that is suitable for matrix multiplication to speed up the computation. Several alternate material were examined to replace silicon channel. One path of this research is directed to replacing the Si nMOS and pMOS channels with channel materials with light electron/hole effective masses leading to enhanced electron and hole mobilities. Options are (i) using Ge for pMOSFETs (Ge has the highest hole mobility of all semiconductors) and III-V semiconductors for nMOSFETs. (ii) using Ge channels for both nMOS and pMOS (iii) keeping Si as the channel material of choice for nMOSFETs and using Ge for the pMOS channels. Among alternate materials Graphene, MoS<sub>2</sub> WS<sub>2</sub>, and WSe<sub>2</sub> are notable. Semiconducting 2D materials such as MoS<sub>2</sub>, WS<sub>2</sub>, or WSe<sub>2</sub> exhibit several features for ultra-short MOSFET channels: (i) They are ultimately thin, which leads to excellent electrostatics and superior suppression of short-channel effects. (ii) While the carrier mobility in most semiconducting 2D materials is lower compared to bulk Si, it is higher than in ultra-thin body Si. (iii) some 2D materials offer much heavier carrier effective masses meff than bulk Si, Ge, and III-V semiconductors.

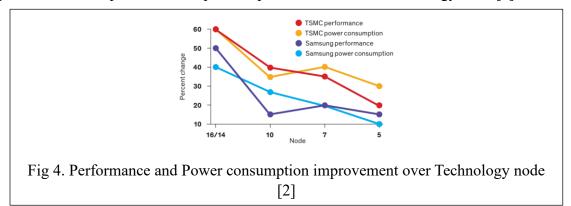

Although an alternate approach to replace Si transistors is relentless it is still not suitable for industrial applications. Now semiconductor companies like TSMC and Samsung broke Moore's law and progressed to 2 nm technology node. Fig. 4 depicts the performance and power consumption improvement over the technology node [2].

#### **1.1.2 Quantum Mechanical Problem**

The major quantum mechanical effects are gate oxide tunneling, energy quantization in substrate and polygate, and source-drain tunneling.

**A. Quantum mechanical tunneling from source to gate oxide:** Due to the aggressive scaling down of transistor, gate oxide is ultra thin. For ultra thin oxide layer electric field is very high. Hence, the charge carriers in the channel will directly tunnel through the interface barrier to the gate oxide.

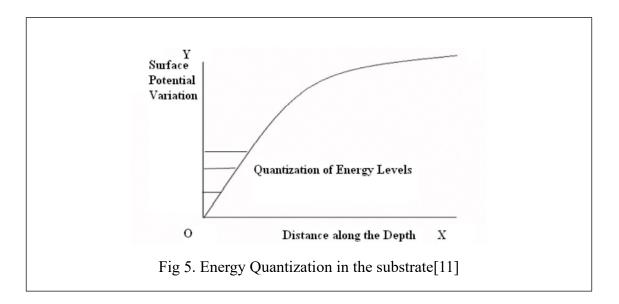

**B. Energy Quantization in the Substrate:** Ultra thin gate oxide results in very high electric fields in the silicon/silicon oxide interface and hence the potential at the interface becomes steep. As a result, formed a potential well between the oxide field and the silicon potentials. During the inversion condition, the electrons are confined in this potential well. Due to confinement, the electron energies are quantized and hence the electrons occupy only the discrete energy levels. This results in the electrons residing in some discrete energy levels which are above the classical energy level by some fixed value of energy as shown in Fig 5.

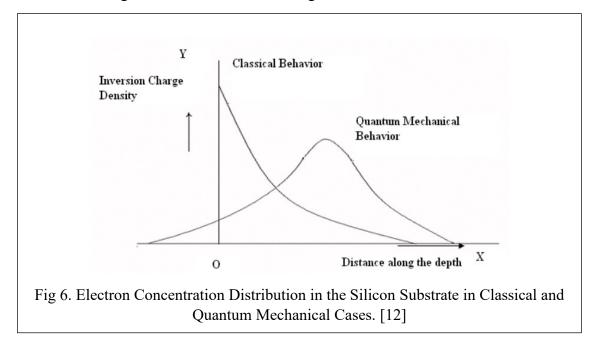

**C. Displacement of inversion charge density into the bulk:** Due to Energy Quantization, charge carrier density at the surface becomes less than the desired value from the classical analysis. The charge distribution in the case of classical charge distribution and Quantum Mechanical Charge distribution is shown in Fig. 6

**D.** The quantum mechanical tunneling from source to drain in the substrate: In sub 10nm channel length, the charge carriers are no longer obstructed in the source potential well and start tunneling quantum mechanically through the barrier between the source and drain. So, the gate voltage has no control over the MOSFET operation.

**E. Threshold voltage and drain saturation voltage shift:** The shift in the surface potential due to the quantum mechanical effects changes the threshold voltage as the effective oxide thickness increases. Operating the MOSFET at such a low dimension will cause energy quantization in the oxide/substrate interface. The confining of the charged carriers in the potential well will raise the energy of the electrons because of the quantization of energy and electrons will occupy much higher energy levels for which a different potential is required to turn on the transistor. The energy quantization process will decrease the drain current also. The drain to source saturation voltage will fall under such conditions.

#### **1.2 Motivation and Scope**

To enact Moore's in the advanced nodes, several forms of nanodevices have been introduced. But all alternate nanodevices have their drawbacks. Some beyond CMOS devices like Ferroelectronic transistors and Graphine spintronics are noted to be mentioned. An alternate approach like Beyond CMOS technology has its fair share of limitations [14]. Keeping up with Moore's law is crucial for the semiconductor industry for the production and development of IC chips. Our research is inspired by the downfall of Moore's Law. With the downfall of Moore's law, the semiconductor industry is facing a challenge in circuit integration and the scaling down of IC. To keep up with Moore's law, a different paradigm is required for circuit integration. Each technology node requires a different fabrication process (lithography) along with different circuit integration rules. Implying Moore's law needs a specific protocol and paradigm to be compatible with all technology nodes. This problem interested us to work on a special paradigm that will be compatible with a specific technology node and after development, it will be advent as a generic paradigm for all technologies. There is plenty of room left for working on this paradigm and protocol.

The paradigm requires extensive insight into the specific technology node. After selecting the technology node, the standard rule should be enforced for the devices. After envisioning the design for the device, at first elementary devices like NAND, and NOR will be put into the examination. Achieving successes from the elementary devices by examining AC and DC characteristics of the devices, the design of the experiment will be forwarded to the complex logic like carry circuit, Adder, etc. After achieving elementary and complex devices, the research will be moved to greater circuit integration like

Arithmetic Logic Unit (ALU). Examining greater circuit integration deals with extensive calibration of power and distribution of clock frequency. In the case of power, for each elementary and complex device, the maximum, minimum, and typical power must be determined. The same goes for the frequency. High, low and typical frequencies for each device need to be determined to get the process flow of the whole technology node. After achieving the process flow of a technology node, device integration in the whole circuit along with clock frequency distribution should be taken to account. While implementing clock frequency distribution, a lot of complexities arise. Circuit ringing, white noise generation, and crosstalk are a few to mention. This research initiates from device designing to characterization and implementation of the circuits.

## 1.3 Summary

In this research, elementary and complex logic devices are being designed and studied for AC and DC characteristics. At first, the paradigm is initiated and elementary logic devices are presented with their AC and DC characteristics to validate the research. Then the research moved on to the complex logic. After several rounds of tuning complex logic is achieved. After examining AC and DC characteristics the devices are integrated with circuits with TCAD. The devices are integrated with an inverter to form a circuit. The purpose of an inverter is to get a full swing of one and zero from the output. A full swing will produce a strong one and zero output which is very important for logic output. A noisy input will produce noisy output. That is why an inverter plays a very crucial role in the circuit. The whole circuit integration part is done in TCAD. Applying circuit integration

and generating netlists from TCAD is a very novel approach. After circuit integration, the whole design of the experiment (DOE) will be examined with pulse input to determine the gain and efficiency of the circuit. In this stage, several rounds of examination are done to fine-tune the gain and accuracy of the DOE. Ensuring gain and accuracy, the circuit will be targeted for greater integration of circuits like the Arithmetic Logic Unit (ALU). Several series of tuning for gain and accuracy will be performed over ALU. Then the ALU design will be sent to some Microchip company to fabricate chips. Receiving the batch of chips, will be examined to check the functionality.

# 1.4 Organization

In this dissertation, we propose a paradigm that is compatible with contemporary technology nodes and keeps Moore's law implemented. With this new paradigm, elementary and complex logic devices are designed and AC and DC characteristics are examined. The dissertation is organized like this: chapter one is Introduction with a Problem statement, motivation, and summary.

Chapter 2 describes an extensive elaboration of literature analysis. At first, starts with related work that is related to embedded devices. The device itself can work as a Boolean logic device. Standalone devices are extensively discussed in this section. Then Insight into gate material and gate oxide is discussed. Each gate material has its features and for standalone devices, high work function material is selected. For the gate oxide, a high dielectric material is always desired. Our device is based on a 14 nm technology node.

In this chapter, we discussed some advanced nodes like 7 nm, 5 nm, 3 nm, and 2 nm technology nodes.

Chapter 3 discussed the principle of crosstalk. As crosstalk is the main principle for this research, it is discussed very elaborately in this chapter. The mechanism and outcome of crosstalk are discussed in this chapter. Chapter 4 discusses the implementation of crosstalk in logic circuits with the outcome and circuit performance.

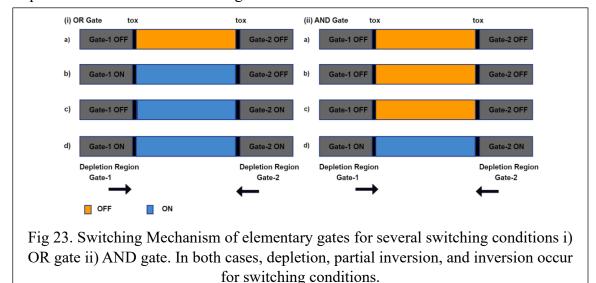

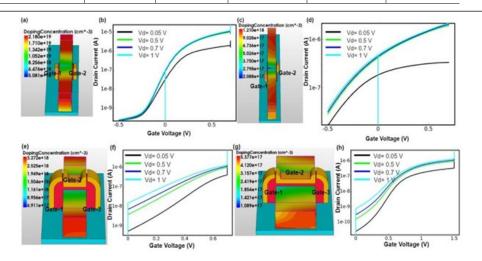

Chapter 5 is about device architecture. At first, device parameters and material descriptions are discussed. Device physics mechanisms along with some crucial principles like the Schrodinger equation, Poisson Equation, and continuity equations are elaborated. Device architecture for elementary logic devices and complex logic devices are discussed here. The devices also possess polymorphic properties. After changing the frequency of the device, the device behaves differently and shows a polymorphic property. It is found that each device shows different polymorphic properties.

Chapter 6 is about the environmental setup for simulation. The environment set up for elementary and complex logic circuits is discussed here. After discussing the environment, elementary and complex logic device parameters along with AC and DC characteristics are illustrated with I-V characteristics. Chapter 7 is Conclusion and Future Research. For future research, a roadmap of chip fabrication and chip batch process analysis is in process. This research has a roadmap for fabrication along with the mass production of chips. After getting a batch of chips, chips will be examined for performance and validity.

#### **CHAPTER 2**

## LITERATURE REVIEW

In this chapter, we discussed literature discussion. In Chapter 1 it is stated that this research is on standalone device nanodevice. This chapter is divided into three parts. In this chapter, state of art-related works on standalone devices is discussed. Nanodevices are strongly dependent on the material property for performing a specific function and gate material and gate oxide are very crucial in this regard. In the second part of the chapter, these materials are discussed. The last part of this chapter is about advanced technology nodes and their pivotal specialization and parameters. In each section, we presented related works, how our research is related to that research, and how our research is novel.

#### 2.1 Related Work

The early research of standalone devices is predominantly in the health sector [15-20]. Most of the standalone devices in the biology sector are to measure vital parameters like pH and others. A plasmonic nanodevice is fabricated whose input is all-optical and the purpose of the device is to measure pH. Embedding this pH meter inside a sample like a plant or animal cell to monitor the biological change[15]. Au nanoshell works as a whole as a standalone device to perform as a pH meter. In some literature [15-18], quantum dots, and nanowires are used for a standalone device. QD along with other materials is used for photoluminescence. The size and surface-to-volumes ratios of QD as a standalone device are used for displaying biologicals like protein, peptides, and DNA. Photocatalyst is also

regarded as a standalone device [18]. This photocatalyst work in Near Infrared Region (NIR). There is plenty of room left for improvement. Chemical variation will come up with completely different functions. The authors designed and integrated multiple functional components into a single nanostructure which offered a new avenue in the field of photocatalyst[17]. Pt/Si/Ag is used as the catalyst. Pt/Si/Ag catalyst with TiO<sub>2</sub> produces the most stable photocatalyst. This heterostructure with different ratios varies in efficiency. But TiO<sub>2</sub> based photocatalyst is only active in UV and near UV regions and thermodynamics uphills and downhills.

Magnetic Tunneling Junction (MTJ) is also used as a standalone device [18]. MTJ is used as Spin Transfer Torque Magnetic Random Access Memory (STT - MRAM) which is considered a pivotal breakthrough in embedded standalone memory. MTJ's basic cell is used in low-energy stochastic regimes and implements a stochastic function. This device is then used as a neuromorphic chip that retains memory and performs logic functions. From this device, an artificial synapse is built for higher functionality. The MTJ device was arranged in one transistor-one resistor architecture. Although this architecture has area benefits, it is suppressed by other difficulties like in need for complex read circuitry and break down of crossbar.

In this era of the Internet of Things (IoT) nanodevice is also used in this regime [19,20]. Nanodevice is realized in this IoT regime and addressed as the Internet of Nano-Things (IoNT). This idea utilizes the performance of nanosensors, nano processors, nanoantenna, nanobots, and nano memory and is implemented mostly in the healthcare field to revolutionalize the healthcare system. The nanodevice acts as a standalone device that will measure the vital signs of a patient and sends them to the servers for further

examination. This nanodevice is constrained by limited power, communication range, and processing. This standalone device, the IoNT is connected with the nanonetworks. These nanonetworks are responsible for communication and processing to overcome the limitation of a standalone device. Conventional TCP/IP protocol is not suitable for this nanonetwork as TCP/IP protocol is for general-purpose processing and nanonetworks have a limitation in this issue. So new networks with nanoantenna and nanodevices are deployed and IoNTs' are worked as a single node in this network. For nanonetworks, a layer-based model as network protocol is deployed. The purpose of this IoNT is drug delivery and disease detection. [20] discussed the deployment of IoNT networks. In their research, they addressed the scalability and complexity of the architecture. A layered approach of Software Defined Network (SDN), Internet of Things (IoT), and Fog network is realized to deploy IoNT. Secondly, they proposed a set of functions and used cases to realize the network. Lastly, they came out with several avenues of research in the field of IoNT and pointed out some problems and limitations in this IoNT field.

## 2.2 Review of Gate Material & Gate Oxide

Aggressive scaling down of the technology node depends on several pivotal parameters. Gate material and gate oxide are one of them. With the advent of the latest technology node, gate material and gate oxide are altered sometimes. In this section, the importance of gate material and gate oxide for a device is discussed. The advancement of technology nodes needs optimization of physical parameters like dielectric constant, and work function. As these parameters are intrinsic parameters of materials, materials need to be altered. Gate materials are chosen for the specific value of work function and gate oxide is chosen for the specific value dielectric constant. At first, the importance of gate material is discussed then gate oxide.

#### **2.2.1 Importance of Gate Material**

With the progression of technology nodes, device architecture is changed. From micron technology to nanotechnology, a transistor device is changed from CMOS to FinFET. In [21] 35 nm CMOS device is fabricated where Silicon On Insulator (SOI) is the platform for the bottom-up approach. The paper gave directions toward the advanced node by suggesting that changing gate oxide will increase the performance. In this paper, the gate oxide is in Armstrong range to control the gate. The gate length was 35 nm and Co-silicide is used as the gate material. The device appears to perform well with On current of 500  $\mu$ A/ $\mu$ m and Off current of 600 nA/ $\mu$ m. Technology from 45 nm, polysilicon is used as gate material [22].

Different gate materials appear with different Short Channel Effects (SCE) [23]. In [23] authors compared several gate materials' performance. They studied from polysilicon to TiN and Ta/Mo. TiN has a problem with Random Dopant Fluctuation (RDF) and Work Function Variance (WFV). TiN and Dual Metal Gate (DMG) like Ta/Mo suffer severely from WFV [22]. The source of WFV is granularity difference. TiN has a small granularity difference but Ta/Mo has a granularity difference of 10 nm. As a result, Ta/Mo gate suffers from WFV more than TiN. Observing these findings, they fabricated a finFET with DMG of TA/Mo and examined the analog performance of the finFET. Parasitic resistance ( $R_p$ ) is the main problem for this device. The reason for  $R_p$  is the fluctuation of fin thickness,  $T_{Fin}$ . The device suffered from other problems like Gate length fluctuation, granularity difference, RDF, and WFV.

In [24] authors reviewed different architecture and materials for FinFET. The authors discussed different gate materials and gate oxides. After rigorous reviews, they came out with their Multigate FinFET (MuGFET) of 22 nm technology. Their FinFET had a gate length of 22 nm and the source and drain were heavily doped but the Chanel was undoped. To ensure better On current, the gate is surrounded by spacers of Si<sub>3</sub>N<sub>4</sub>.

To tune gate metal work function, several procedures can be addressed [26]. In [26] the authors fabricated a P-type double gate FinFET. The FinFET had a gate length of 20 nm

and was made from Mo. The authors tuned the work function of gate material, Mo to tune the threshold voltage,  $V_t$ . Applying the device in a Nitrogen environment for special treatment and then etching the device with Hydrogen gave the authors got the freedom to tune Mo's work function. For regular Mo, the work function is 5 eV and after treating their device with N<sub>2</sub> and H<sub>2</sub>, they got the work function dropped to 4.4 eV which is an ideal Work function for FinFET. With gate work function tuning, they tuned V<sub>t</sub>. After treating V<sub>t</sub>, On current improved by a large amount. In conclusion, the authors suggested that this fabrication process can be adapted to achieve N-type dual gate FinFET.

Sometimes aggressive scaling down of the gate length occurred [27]. Here the authors fabricated FinFet with a 10 nm gate length. This aggressive scaling down came out with the cost of a very steep subthreshold swing and Drain Induced Barrier Lowering (DIBL). Although On current and Off current value is within the limit but the device got some severe issues and will be a fabrication nightmare for the device physicists.

The researchers came out with new fabrication approaches [28]. Here the researchers appeared with a self-aligned double gate along the source drain with a gate length of 17 nm. In addition, they experimented with  $Si_{0.4}Ge_{0.6}$  as gate material and  $SiO_2$  as spacers. The fabrication segment is complex with Boron doped  $Si_{0.4}Ge_{0.6}$ , electron beam lithography several steps of  $SiO_2$  hard mask to protect some parts of the device. The extremely meticulous procedure was followed in every step of fabrication. As a result, parasitic resistance decreased drastically. The device came out with better DIBL, GIDL, and subthreshold swing. After rigorous examination, the researchers suggested that a self-aligned double gate can suppress SCE effectively,  $Si_{0.4}Ge_{0.6}$  can produce proper  $V_t$  even in the ultrathin Fin body and if a gate is aligned with the source-drain,  $R_p$  will be much lesser. With these findings, the authors envisioned the next generation of FinFET.

In summary, the gate material, and gate length play a crucial role in device operation. They influence  $V_t$  roll off and the gate length ratioed with Fin width can lessen parasitic resistance to a great extent. As a result, from planar CMOS architecture to FinFET design gate material is changed quite frequently. Table 1 is a list of gate materials along with their work function [29].

| Gate Material                     | Work Function |

|-----------------------------------|---------------|

| Mg                                | 3.66          |

| Mg/Al <sub>2</sub> O <sub>3</sub> | 3.6           |

| Mg/SiO <sub>2</sub>               | 3.45          |

| Mg/ZrO <sub>2</sub>               | 4.15          |

| Al                                | 4.28          |

| Al/Al <sub>2</sub> O <sub>3</sub> | 3.9           |

| Al/SiO <sub>2</sub>               | 4.14          |

| Al/Si3N4                          | 4.06          |

| Al/ZrO <sub>2</sub>               | 4.25          |

| Та                                | 4.25          |

| Ta/SiO2                           | 4.2           |

| W                                 | 4.63          |

| W/SiO <sub>2</sub>                | 4.6-4.7       |

| Мо                                | 4.95          |

| Mo/SiO2                           | 5.05          |

| Mo/Si <sub>3</sub> N <sub>4</sub> | 4.76          |

| Mo/HfO <sub>2</sub>               | 4.76          |

| Pt                                | 5.65          |

| Pt/SiO <sub>2</sub>               | 5.59          |

| Pt/HfO2                           | 5.23          |

| Pt/ZrO <sub>2</sub>               | 5.05          |

| Ni                                | 5.04          |

| Ni/Al <sub>2</sub> O <sub>3</sub> | 4.5           |

| Ni/ZrO <sub>2</sub>               | 4.75          |

| Au                                | 5.31-5.47     |

Table 1. List of Gate material along with work function

| Gate Material                     | Work Function |

|-----------------------------------|---------------|

| Au/Al <sub>2</sub> O <sub>3</sub> | 5.1           |

| Au/ZrO <sub>2</sub>               | 5.05          |

| Hf                                | 3.95          |

| Hf/SiO <sub>2</sub>               | 4             |

| Ti                                | 4.33          |

| TiC                               | 5.0           |

| TiN                               | 4.4-4.6       |

## 2.2.2 Importance of Gate Oxide

Since the era of planar CMOS, gate oxides are used as a dielectric between the body/ Fin and the gates. With a polysilicon gate,  $SiO_2$  is used as a gate oxide. With the advent of modern technology nodes, the gate oxide is also changed. The purpose of gate oxide is to build electrostatic. By controlling electrostatic, we control gates.

In [30] the author discussed the importance of gate oxide. Here the performance of SiO<sub>2</sub> and La<sub>2</sub>O<sub>3</sub> is compared as the gate dielectric. According to the author's claim, La<sub>2</sub>O<sub>3</sub> is better than SiO<sub>2</sub>. As the research progresses, he claimed that La<sub>2</sub>O<sub>3</sub> has a problem with getting hydroxide as the oxide is hydrophilic. This rare earth element with ternary oxide has another problem of changing chemical composition in varying temperatures. With varying the chemical composition, their permittivity also changes which also affects the dielectric constant. Examination with X-ray Diffraction (XRD) and Atomic Force Microscope (AFM), confirms the varying crystallization for lanthanum-based tertiary oxide. This report gave a deep insight into lanthanum-based oxide as a dielectric.

In [31] the authors discussed the effects of dielectric in a charge pump circuit. A charge pump circuit is a vital part of some memories like EEPROM. The gate oxide is responsible for junction breakdown voltage and operation of the charge pump circuit. The authors proposed a new charge pump circuit that will optimize supply voltage and efficiency. The authors went through several circuit architectures and compared the performance. With this research, they realized that their pump circuit is suitable for only low voltage. With a specific value of oxide thickness, they can reach maximum pump gain.

The ultra-thin oxide is used for the semi-empirical model and physics is analyzed [32]. The authors examined the effective mass of electrons in an ultra-thin gate oxide and came out with an electron model based on the device physics. The model can accurately describe electrons from the valence band (EVB), electrons from the Conduction band (ECB), and holes from the valence band. For this model a dual gate model with varying oxide thickness as well as gate polysilicon composition,  $Si_{1-x}Ge_x$ . The ultra-thin region's I-V and C-V profile is examined for continuous equation and Quantum correction is implied to get ballistic transport as well as quasi ballistic transport. The Quantum mechanical simulation is also addressed in this work to get a compact formula for the device. The prime reason for ultra-thin gate oxide is to increase the tunneling current. This research work emphasizes two main points:

- 1. The relative significance of different tunneling components

- 2. The sensitivity of tunneling current on oxide thickness

The device performed well with significant tunneling current increment but was not free from other short channeling effects.

Gate oxide defects can cause severe defects in the nanodevice [33]. The uneven thickness will cause an electron trap that is detrimental to any device. The Defected oxide layer like gate oxide short will cause stuck an error problem. As a result, the device needs to be discarded. The authors suggested several examinations to detect this defect. One is the measurement of I<sub>DD</sub>. An increment of I<sub>DD</sub> denotes gate oxide short. The authors suggested that IC designers should take this issue into account.

| Material                       | Dielectric Constant, k |

|--------------------------------|------------------------|

| SiO <sub>2</sub>               | 3.9                    |

| Si3N4                          | 7                      |

| Al <sub>2</sub> O <sub>3</sub> | 9                      |

| Ta2O5                          | 22                     |

| TiO <sub>2</sub>               | 80                     |

| SrTiO <sub>3</sub>             | 2000                   |

| ZrO <sub>2</sub>               | 25                     |

| HfO <sub>2</sub>               | 25                     |

| HfSiO <sub>4</sub>             | 11                     |

| La <sub>2</sub> O <sub>3</sub> | 30                     |

| Y2O3                           | 15                     |

| a-LaAlO3                       | 30                     |

Table 2. Dielectric Constant of Some Gate Materials [34]

Table 2 contains a list of Gate materials and corresponding dielectric constant. From Table2. We can select gate material to get a specific amount of electrostatic potential.

## 2.3 Advanced Technology Nodes

With the progress of technology, technology nodes moved from micron to nanotechnology. In micron technology, transistors are comparatively simpler in paradigm and gate length was regarded as technology node identity. Day by day the gate length decreases in microns as well as technology node is changing. The micron technology nodes are based on CMOS technology and the gate length is in microns. With the advent of nanotechnology, the gate length plummets in nanometer. As the name suggests, the gates are in nanometers. But in the nanotechnology node, the transistors architecture gets complicated due to SCE. As a result, with the progress of technology node architecture is changed rapidly. From micron technology to nanotechnology CMOS was the dominant device up to 22 nm technology node. For analog applications, 45 nm is a very popular and well-matured technology. 45 nm technology analog devices like Analog to Digital Converter (ADC) and analog filters give high gain and steady performance. From 22 nm technology node, FinFET is dominant as nanodevices. 14 nm technology is very popular in commercial avenues, especially in the processor industry. At this moment 7 nm technology is already commercialized in all processors including desktop processors, cell phone processors, and other electronic devices. In this section, FinFET of some major and advanced technologies are discussed below.

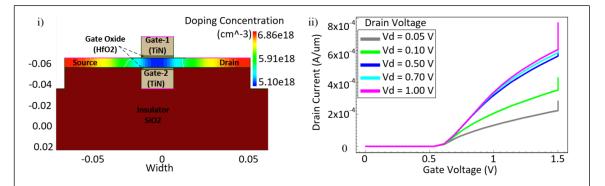

Advanced MOSFET with several architectures related to gate engineering is analyzed in detail [35]. To decrease SCE, several architectures ranging from Double gate CMOS, Trigate CMOS, and Gate All Around are being studied along with their On state current, Off state current, and  $I_{On} - I_{Off}$  ratio. Besides these analog and RF characteristics were examined. The authors also examined several insulator physics like Silicon On Insulator (SOI), Bulk CMOS, and Junctionless CMOS. The authors claimed that GAA architecture is most proficient in channel utilization and channel width can be utilized in this paradigm most graciously. Polysilicon and dual gate material  $Si_{1-x}GE_x$  was used and it is noticed that different architecture are proficient in different parameters. Junctionless Double Gate had the lowest SS and the highest  $I_{On}$ - $I_{Off}$  ratio. The lowest DIBL is obtained from graded channel dual gate material junctionless CMOS. The authors remarked that multi-material gate transistors had high potential as next-generation technology nodes.

SRAM with low power was built with 45 nm technology [36]. The authors pioneered a new technology of third optional gate-oxide for high-speed performance. The device operates in 1.1V and with low K gate oxide. The whole device is developed on (100) orientation of the substrate with a focus on process simplicity. Strain engineering was also implied to get reliability. With a meticulous manufacturing process, the device showed excellent performance in mixed-signal applications.

The authors studied with Silicon-Germanium source/drain for investigating layout dependencies. Stress engineering was extensively used through SiGE to examine the performance with the paradigm of the nested transistor. The authors claimed that increased recess depth and Ge concentration gave higher stress and there is an optimal recess for that optimal stress can be applied. Stress is very crucial for increasing the mobility of the carriers. The Mobility of carriers is dependent on channel stress. With these modifications, p-type transistor gained a higher saturation current [37].

32 nm technology node consisted of extreme level stress engineering and some other device physics engineering like Metal High K (MHK), Ultra Shallow Junction (USJ), Dual Stress Liner (DSL), High Aspect Ratio Process (HARP), Ultra Low K (ULK) integration, etc. For the case of MHK with different stacks, introduced some problems in the device like Vt roll-off, device reliability, mobility degradation, etc. [38]

The effect of alpha particles in 32 nm technology nodes is researched extensively [39]. By introducing radiation particles like alpha particles and neutrons, the upset time of an SRAM is addressed [39]. The upset time is responsible for the stability of SRAM. The appearance of noise particles affects the storage capacity of SRAM and produces logical errors in transient time which is considered a Single Upset Event (SEU). This research studied elaborately about this SEU. Masking like electrical masking, and logical masking block the propagation for SET. The upset time is more vital for combinational logic than sequential logic. The radiation is applied to four batches of chips, and it was observed that the sequential SER is independent of the clock speed, but combinational SER is dependent on clock speed. The neutron combinational SER is 2x time higher than the alpha particle SER [39].

The breakthrough happened in the 22 nm technology node. The transistor paradigm shifted from planar architecture to 3D architecture and FinFET architecture gave the cutting-edge technology in this regard [27]. Several variants of FinFET like Pi, Trigate, Gate All Around (GAA), etc. were studied in detail and it was noticed that vertical transistor offered 50% improvement in the area of density, reduced capacitance, and enablement of new materials. Due to new architecture and new fabrication processes in the area of lithography and annealing are introduced. With these improvements, some

problems arise like Random Dopant Fluctuation. 22 nm technology node also makes a bridge between analog and digital signals. This node can produce a better cut-off frequency to implement in the Radio Frequency (RF).

The change of architecture appears with several problems in the 22 nm technology node [28]. To follow Moore's law dimension is reduced. As a result, the drain comes close to the source and increases DIBL. Thinner gate oxide causes gate leakage current. As a solution, High K dielectric materials are proposed. Another problem is the Vt roll-off. For low Vt, Off current increases but for high Vt On current decreases. So The On-Off ratio is needed to be adjusted. These problems' solutions are provided by the authors. Adopting those solutions, SRAM with FinFET was developed and for drain leakage current, the Fin ratio was optimized. In these ways, robust FinFET was produced.

Stress engineering was implemented to increase the performance of 22 nm node [29]. The authors tried different materials rather than Silicon for their transistors and they examined III-V materials like GaAs. In this research [42], the authors implied stress through wafer bending. At first, a Silicon wafer was used as a substrate, and stress is introduced to it then GaAs layer is imprinted on the wafer. On top of the device layer, FinFET is introduced that had InGaAs channel. After that, the Density of State (DOS) was examined. It is observed that electron density is much higher in X and L valleys than in  $\Gamma$  valley. It was also noticed that under large uniaxial stresses, a saturation point appears, and after that DOS becomes degraded which is the opposite of biaxial composite stress. Hole mobility was also examined and found that both cases of electron and hole mobility are similar to Silicon ones. Applying this stress, PMOS performs better than NMOS.

With advanced nodes like 22nm and 14 nm, some new problems also come to the surface. Negative Bias Temperature Instability (NBTI) is one of them [30]. NBTI is responsible for Vt shift ( $\Delta$ Vt) and subthreshold slope shift ( $\Delta$ SS). Various benchmark circuits are synthesized to analyze the effect. MOSFET aging like Bias Temperature Instability (BTI) is a pivotal reliability issue and NBTI is one of them. NBTI is predominantly governed by the generation of interface traps( $\Delta$ N<sub>IT</sub>). The examination of NBTI is important for determining the device's end of life (EOL) and also measuring timing violations. To prevent this violation tiny time guard band is provided. As timing

violation happens for NBTI Vt increase with time and makes the transistor slower and the static power also degrades. With TCAD, authors examined NBTI and improved aging aware cell library, considering problems like  $\Delta$ SS,  $\Delta$ Vt, transconductance, linear drain current (I<sub>DLIN</sub>), saturation drain current (I<sub>DSAT</sub>), and gate-drain capacitance (C<sub>GD</sub>) [43].

IBM modified its z14 microprocessor with 14 nm technology node. With this advanced node, many improvements are implied on z14. Most of the improvements were arranged in Central Processor (CP) and System Control (SC). There were also improvements in the area of design methodology, hierarchy optimization, hierarchy management, and timing optimization. Using 14 nm technology, IBM managed to have a breakthrough in their z series microprocessor[44].

Defects in 14 nm technology nodes are elaborated [44]. NBTI is responsible for the defects like Off current leakage and GIDL. GIDL is mainly caused from the Band to band (BTBT) tunneling. For NBTI GIDL increases as NBTI causes Hot Carrier Degradation (HCD). It has been confirmed that by eliminating HCD, GIDL will be still present for Trap Assisting tunneling (TAT). The authors claimed that when  $V_{GD}$  is low, the energy bands will not have enough potential to bend. As a result, GIDL will happen and also claimed that t negative bias current Stress Induced Leakage Current (SILC) may be produced. SILC leads to gate leakage current. The authors examined their devices batch on different temperatures and every time GIDL happened. These are the findings from the authors' report [45].

The major updates happened in the 7 nm technology node. This node outdid all its predecessors in terms of RC control electrostatic discharge and made a path for its successors of the 5 nm technology node [46]. A compact model was built and analyzed with one dimension Poisson equation where the device is three-dimensional. The general model efficient extraction, high accuracy, strong scaling capability, and excellent transfer capability. And the performance of ESD improved dramatically. With the change of some crucial parameters like geometric parameters for all advanced technology nodes, it is very difficult to maintain a compact model. The authors offered a novel general compact model based on TCAD simulation. Fine-tuning the gate length and Fin width, the authors presented their BSIM-CMG model. They proved that the trade-off between Lg and W<sub>fin</sub> of

FinFET greatly strengthen the performance of the power clamp while keeping the area compact and finally proved that their framework is effective for accurate circuit optimization under state-of-the-art technology and made a roadmap for the successors of advanced technology nodes.

Several attempts were made to make new approaches in 7 nm technology node. The authors experimented on this technology node by using Nano Sheet FET (NSFET) instead of FinFET. The band structure was calculated with the help of TCAD and the device was examined for DC characteristics and applied to the Ring Oscillator by taking into account electrostatics, parasitic components, and layout configurations. After examination, it is noticed that NSFET produces 5% more drive current compared to NW FET. The reason for the higher drive current is several nanosheets. The authors claimed that NSFET will compete with other FET architectures and NSFET circuits will be much more robust at heavy loads by stacking channels. By introducing EUV, the designers will get the freedom to tune the geometric parameters and have quantized channels [47].

With rounds of improvement in 7 nm, some authors applied this technology to build 6T SRAM. They achieved 56.7% reduction in leakage current, 7.9% improvement in hold noise margin (HNM), 8.6% improvement in read noise margin (RNM), and 10.8% improvement in write margin (WM) and cost them 19.3% increase in delay under design speculations. Quantization of Lg and Wfin leads to limited improvement of SRAM. A few improvements in the avenue of circuits were being done by the authors [48]. They tuned the gate pitch and Fin pitch to increase the accuracy. They researched with advanced TCAD modeling considering seven crucial parameters and in some cases, they made some tradeoffs in parameters to examine the performance. After implying those updates, the authors got high-speed. Cost-effective SRAM cell that is optimized for architecture and peripheral circuits [48].

Sometimes new architecture like Hexagonal nanowire and NanoRing were imposed in 5 nm node for higher current drivability and lower parasitic capacitance compared to conventional NW. The multiple vertical stacks with 1-fin-per-device and 2-fin-per-device were evaluated. Parasitic capacitances are more serious in Back-End-Of\_Line (BEOL) than Front-End-Of\_Line (FEOL) for N5. And it is the major limitation, in terms of power and performance at the cell level. The author studied comprehensively all the geometric and physical parameters [36]. According to the authors' clime, NR architecture with 3 stacks exhibited the highest performance in terms of drive current and parasitic capacitances.

Speed and power performance are evaluated for N5 Gate All Around FETs and Ultra thin FinFET architecture. Corresponding architectures are also applied to 6T SRAM to examine the area layout. GAAFET is capable of getting better control of SCE, hence better electrostatic control. The severe processing complexity was described in the reports and the author claimed that PFET performed better than NFET in FDSOI architecture [50].

Physics-based Quantum mechanical models were studied for P and NMOS with specific channel thickness and the research is also extended to 1) k.p model with Poisson solver for bandgap variations and confined charge distributions 2) Kubo-greenwood model for low field mobility with considering surface roughness and stress 3) multi sub-band Boltzmann transport equation based on a state-of-the-art phase space approach is employed to evaluate device IV characteristics 4) Vt variation with different channel variation. The authors' research indicated that {110} wafer Ge would be the most viable option [51]. A systematic assessment of the mobility of electrons and holes of NSFET considering the quantum mechanical effect was presented. The device characteristics were analyzed by the Boltzmann Transport equation and also with the semiclassical Drift-Diffusion approach. The authors demanded that their framework express the details of quantum confinement in Ge channel.

The performance of two GAA device configurations: Lateral FET (LFET) and vertical FET (VFET) is benchmarked and analyzed at analyzed using an ARM core processor. The tradeoffs among energy, frequency, leakage, and area are evaluated in the avenue of multi-Vth optimization flow. After tuning with several device parameters, the authors came to the conclusion that LFET had a higher frequency compared with VFET [52].

Multi-stacked NSFET showed a lot of potential as an advanced node as it draws much more driving current and much more controllability. The device was designed through TCAD and then BSIM-CMG library was created. Punch-through and subthreshold swings were studied extensively in this paper [53]. To stop punch-through leakage current,

a Punch-Through Stopper (PTS) was introduced [53]. TCAD calibration carried out two main directions: 1) the value calculated at the lower level of material properties and carrier transport is used as a calibration target, and 2) the measured value of the made device is used as a calibration target. In presence of bottom oxide, each N/PMOS was improved by 17.6% to 6.3% in SS, 59.9% to 31.3% in DIBL. In addition, circuit characteristics were analyzed by a five-stage ring oscillator and parasitic capacitance dropped significantly [53].

Ferroelectric metal FET was realized in 3 nm node. Although it showed some potential, it consumes very large amount of power. Multigate FeFET is being realized. After examining several stacks of nanosheet, the authors concluded that it had some potential to contribute to the advanced node [54].

N2 is the latest technology node in the semiconductor industry. It has replaced many fabrication technologies and introduced new technologies in the avenue of process, fabrication, and circuits. The authors compared four methods to compare for N2 fabrication. After fabrication, the device appeared to be a low-power device of 0.4 V. The analysis of RO behavior including MOL parasitic, all major variability sources suggested that there was a difference between FinFET and NSFET. The authors worked on a device that differs in processes. The 2fin-no-cut design exhibits ~3x better PPA products because of the high PMOS stress level. Single fin device suffers in PPA but consumes the lowest power [55].

The experiment on different channel materials played a vital role in N2 family. The authors came out with Ge channel and the device showed better electrical performance and reliability. Although, Ge has the higher electron and hole mobility it has a problem with interlayer oxide. Gate stack and vertically stacked strain are discussed in detail [56]. A combination of low Ge:P S/D and low C Si:P as a liner in the contact module further improves Ge nFinFET performance.

The scaling potential of Negative Capacitance FinFET and FDSOI are studied for the 2 nm technology node [65]. TCAD simulation justified the NC version of FinFET to a 2 nm node. NC version of FinFET and FDSOI have higher drive currents than their FinFET and FDSOI counterparts. NCFinFET with HfZrO<sub>2</sub> showed much higher electric field of 2 MV/cm that indicating a high potential of next-generation device. This device showed higher driving current with better SS and Vt roll-off.

| Node | Gate   | Gate             | Gate     | Gate  | Interconnect | ЕОТ  | Fin   | Fin    | Fin   |

|------|--------|------------------|----------|-------|--------------|------|-------|--------|-------|

| nm   | Length | Dielectric       | Material | Pitch | Pitch nm     |      | Width | Height | Pitch |

|      |        |                  |          | nm    |              |      |       |        |       |

| 45   | 45     | SiON,            | TiN      | 180   | 160          | 1.1- |       |        |       |

|      |        | HfO <sub>2</sub> |          |       |              | 1.5  |       |        |       |

| 32   | 30     | HfO <sub>2</sub> | TiN      | 112   | 160          | 1.1- |       |        |       |

|      |        |                  |          |       |              | 1.5  |       |        |       |

| 22   | 26     | HfO <sub>2</sub> | TiN      | 90    | 90           | 0.9  | 8     | 34     | 60    |

| 14   | 20     | HfO <sub>2</sub> | TiN      | 70    | 70           | 0.5- | 8     | 42     | 42    |

|      |        |                  |          |       |              | 0.8  |       |        |       |

| 7    | 12-18  | HfO <sub>2</sub> | TiN      | 64    | 64           | 0.8  | 6     | 52     | 30    |

| 5    | 14     | HfO <sub>2</sub> | TiN      | 48    | 28           | 0.5  | 5     | 46     | 22-   |

|      |        |                  |          |       |              |      |       |        | 25    |

| 3    | 16     | HfO <sub>2</sub> | TiN      | 40    | 32           | 0.3  |       |        |       |

| 2    | 12     | HfO <sub>2</sub> | TiN      | 30    | 20           | 0.9  | 4     | 50     | 44    |

**Table 3 Different Technology Nodes**

Table 3 summarizes different technology nodes. As 45nm and 32 nm technology node is based on planar technology, there is no fin. From 22 nm technology, FinFET architecture was initiated. FinFET has a completely different architecture than planar CMOS technology. Even some technology node has several variants. For the case of the 45 nm node, the fast variant had a smaller gate length than the regular and slow variants. The same case happened to 7 nm technology, with different gate lengths for different variants. Nodes like 5 nm, 3 nm, and 2 nm are not matured yet. There is plenty of room for development for those nodes.

My proposed devices' architecture is influenced by 14 nm technology node with junctionless FET.

#### CHAPTER 3

### **CROSSTALK PRINCIPLE**

In electronics, crosstalk is the occurrence of any noise phenomenon by which a signal transmitted on one circuit or channel creates an undesired effect/noise in another circuit or channel. Crosstalk is generally caused by undesired capacitive, inductive, or conductive coupling from one circuit or channel to another. The term Crosstalk comes from the early analog phone lines where one could hear voices from neighboring lines due to Electromagnetic coupling. Due to "Mutual Capacitance ( $C_M$ )" and "Mutual Inductance ( $L_M$ )" in the transmission line, the crosstalk phenomena occur.

Crosstalk is based on the principle of Superposition :

- 1) Multiple signals can exist on the same line same time without affecting each other.

- 2) A random signal can be coupled onto a line independent of what may already exist in the line

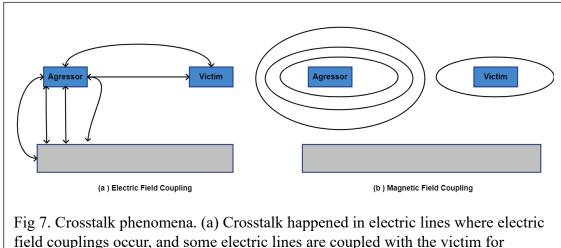

### 3.1 Crosstalk Terminology

In crosstalk, two main terminologies are aggressor and victim. The line which is carrying the signal is called the aggressor and the line which is receiving noise from the aggressor is addressed as the victim. Fig 7. depicts the crosstalk phenomena. In Fig 7. The victim and the aggressor are in close proximity. When a signal transfers through the aggressor and the victim is idle, the aggressor inducts the same magnitude of electrical signal in the victim line. As a result, crosstalk occurs as a form of noise. From the aggressor line, six electric field lines emit, and four of them are connected with the ground, and the rest two lines are connected with the victim and considered crosstalk noise.

proximity and considered as crosstalk noise (b) In a magnetic circuit crosstalk occurred for proximity with the victim and aggressor

In Fig 7(b), crosstalk is happening in a magnetic circuit. As the aggressor and the victim are in proximity, magnetic field lines from the aggressor induce the same magnetic flux in the victim line.

## **3.2 Kinds of Crosstalk**

Crosstalk may happen for several reasons. But all kinds of crosstalk can be categorized into two kinds - Signal X-talk and Switching Noise.

(a) Signal X-talk

This kind of crosstalk happens in transmission lines where  $C_M$  and  $L_M$  produce the same magnitude of noise in a close transmission path. This kind of crosstalk happens in PCB and on chips.

### (b) Switching Noise

When the return path is highly inductive and inductive noise is dominant in the circuit, then this kind of crosstalk occurs. This is also known as Ground Bounce / Power Supply Droop", "Simultaneous Switching Noise (SSN)" or "Simultaneous Switching Output (SSO) Noise".

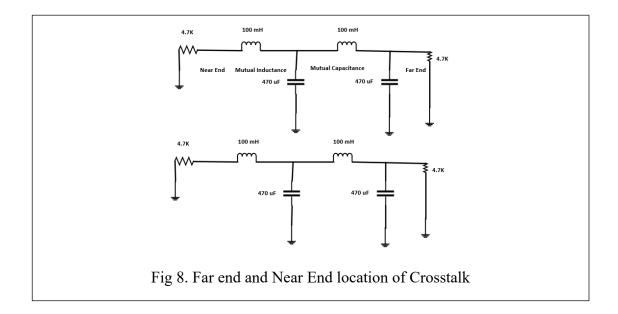

## **3.3 Crosstalk Location**

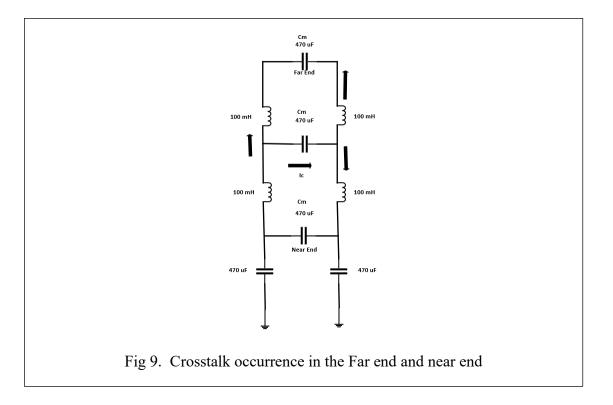

Crosstalk happens in specific two locations: Near End, and Far End. Near end location can be realized as the location closest to the driving source resistor and the far end can be realized as the location closest to the termination resistor.

# 3.4 Capacitive Crosstalk

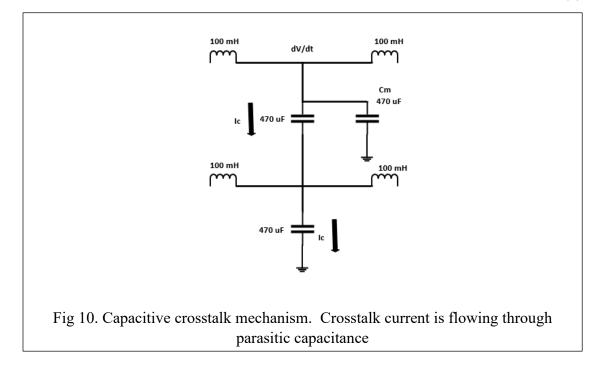

As the aggressor current propagates through the line, it will inject the current into the victim line according to

τ...

$$I_{\rm C} = C_{\rm M} \quad dV/dt \tag{1}$$

As the current is injected into the victim line, it will see an equal impedance in the forward and backward directions and will flow in both directions. The current injected is related to the spatial extent of the rise time that can be described using the per unit length value for Mutual capacitance.

$$C_{M} = C_{M}' .\Delta x$$

$$C_{M} = C_{M}' (vel.t_{rise})$$

(2)

Then the total current becomes:

$$I_{C} = C_{M} \quad dV/dt$$

=  $C_{M}'$  (vel.t<sub>rise</sub>) V/t<sub>rise</sub>

=  $C_{M}'$ . vel. V (3)

Half of the current injected into the victim as the incidence voltage step travels down the aggressor travels back to the Near End. In the Near end, only a fixed amount of current is present. The maximum amount of current injected is reduced by a factor of  $\frac{1}{2}$  to account for the injected energy dividing in both the forward and reverse directions. It is again spread out with a factor of  $\frac{1}{2}$  over the period of 2 T<sub>D</sub>.

$$I_{C} = \frac{1}{2} \frac{1}{2} C_{M}'. \text{ vel. V}$$

=  $\frac{1}{4} C_{M}'. \text{ vel. V}$  (4)

dv/dt occurs in the aggressor node that affects the victim line and is seen across Cl and Cm as shown in Fig 10. For the change of voltage, the Ic current will flow through both of them. Applying KCL it can be realized that the same magnitude of current will flow through both of them.

Applying KCL in the node:

$$Ic = Im$$

<sup>1</sup>/<sub>4</sub> C<sub>L</sub>'. vel. V<sub>A</sub> = <sup>1</sup>/<sub>4</sub> C<sub>M</sub>'. vel. V<sub>B</sub>

$$V_B/V_A = C_M/C_L$$

(5)

This is the total voltage created at the injection before the inductors start to conduct and allow the current to flow through both directions. Now applying Eq.5 in the near field crosstalk location, it becomes:

$$V_{\rm NE}/V_{\rm A} = \frac{1}{4} C_{\rm M}/C_{\rm L} \tag{6}$$

The term <sup>1</sup>/<sub>4</sub> term appears as the current propagates both in the forward and backward directions. For the case of Far end crosstalk

$$I_{CL} = C_L .\Delta x \ dV/dt$$

$$= C_L .(Vel. t_{rise}) \ 0.8 \ V_B/t_{rise}$$

Applying KCL in the node:

$$Im = Ic$$

$$C_{L}'.(\text{length}) \ 0.8. \ V_{A} / t_{\text{rise}} = C_{M}'. \ \text{vel. } t_{\text{rise}} \ 0.8. \ V_{B} / t_{\text{rise}}$$

$$V_{B} / V_{A} = C_{M} / C_{L} \ (\text{length/vel. } t_{\text{rise}})$$

(7)

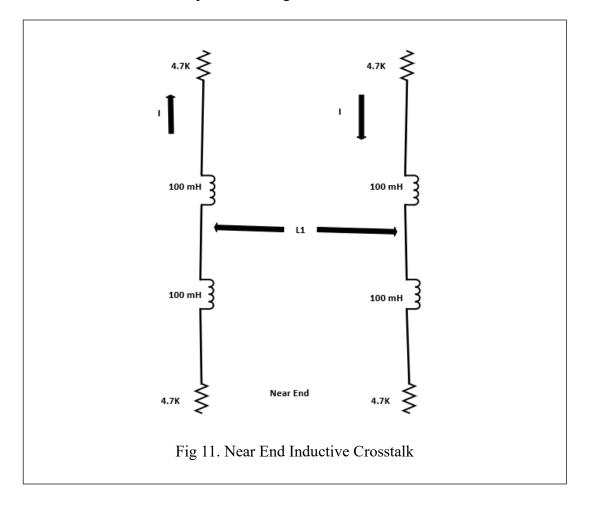

## **3.5 Inductive Crosstalk**

Current transfers through a wire will cause a magnetic field and a magnetic field can also create current flow. When the aggressor has a magnetic field and the victim is in proximity, then it will create a current in the victim. The direction of the B-field lines in the victim is opposite of the aggressor. The direction of the current creates a negative current in the far end and a positive voltage in the near end.

The current that flows through the self-inductance of the aggressor line causes a voltage on the victim line as follows:

$$V_{\rm M} = L_{\rm M} \, \, dI_{\rm A}/dt \tag{8}$$

This voltage appears across the inductance of the victim which causes current to flow:

$$V_{\rm L} = L_{\rm L} \, dI_{\rm B}/dt \tag{9}$$

Since the coupled voltage  $(V_M)$  is the same as the Victim line voltage  $(V_L)$  which creates the current, we can relate the currents of the Aggressor and Victim.

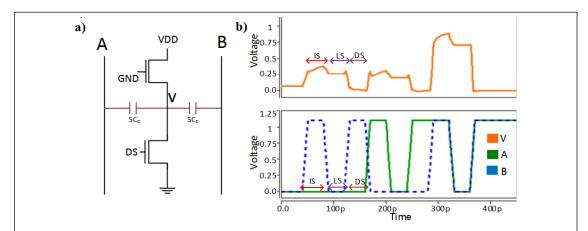

$$V_{M} = V_{L}$$