# An SOPC Based Image Processing System

A THESIS SUBMITTED TO THE UNIVERSITY OF LIVERPOOL FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN THE FACULTY OF ENGINEERING

By

Fan Wu

Department of Electrical Engineering and Electronics

September 2007

### Abstract

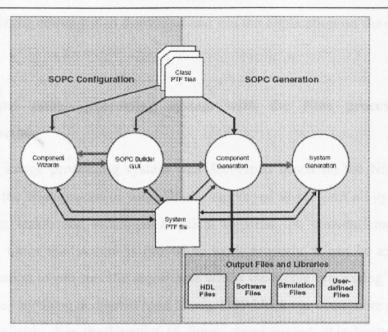

Recent advances in semiconductor technology have made it possible to integrate an entire system including processors, memory and other system units into a single programmable chip - FPGA, these configurations are called "System-on-a-Programmable-Chip" (SOPC). SOPCs have the advantage that they can be designed quicker than existing technologies and are cheap to produce for low volume (<10,000) applications. Also, SOPCs are of great benefit as they offer compact and flexible system designs due to their reconfigurable nature and high integration of features. One processor intensive application, which is ideal for SOPC technology, is that of image processing where there is a repeated application of operations on the 2D data. This research investigated the use of SOPC technology for image processing by developing a modular system capable of real-time video acquisition, processing and display.

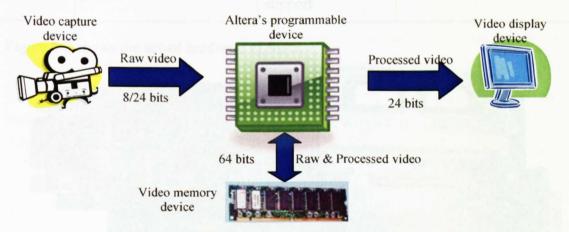

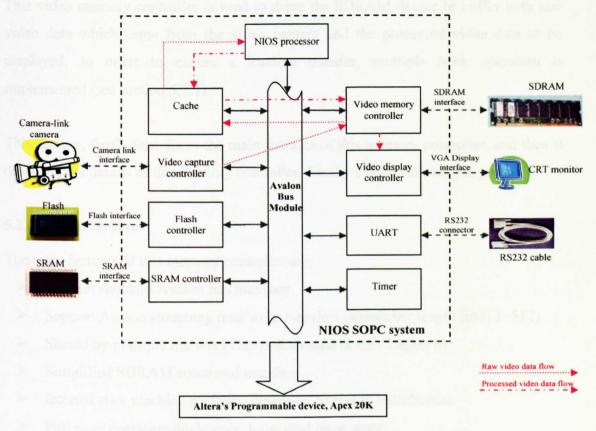

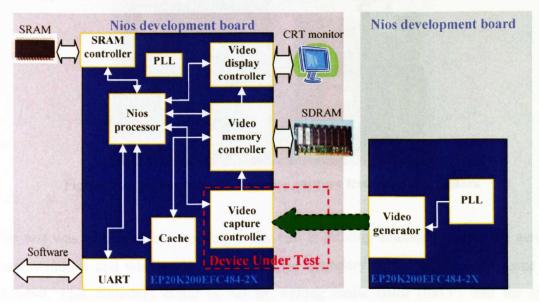

This system is comprised of a CameraLink CMOS camera with a custom designed camera interface card for video acquisition, a VGA mode CRT monitor with a Lancelot VGA card for video display, an industrial SDRAM device for video data buffering, and an Altera Apex 20K FPGA for evaluating the SOPC design. Four custom designed IP components have been developed and integrated with other Altera provided standard IP components to drive all off-chip peripherals and perform the required video functions such as processing the images. These custom designed IPs are the video capture controller, video display controller, video memory controller and Cache. A Nios processor was chosen to perform the actual image processing, and the whole system was developed on the Altera Nios development board. In order to solve the complex on-chip data communication, while not degrading the transferring speed of largeamounts of video data, an effective solution called Simultaneously Multi-Mastering Avalon Streaming Transfer with Peripheral-Controlled Waitrequest was raised. Rather than using the software approach to initialise DMA-like transfers, this solution takes advantage of the FPGA hardware resource to perform bus arbitration and hence increases the system efficiency.

The system produced is an alternative to conventional desktop-based, i.e. a visionbased closed loop process control system for welding, or microprocessor-based vision systems.

Fan Wu

ì

## Acknowledgement

I would like to express my gratitude to my supervisor Professor Jeremy S. Smith for his guidance and help for my research work. I would like to thank my parents for their support. I would like to thank my university colleagues James Buckle, Mr. Gordon Cook and Andrew Tickle for their help especially in improving my English. I would like to thank Kenjin Wong, Yanwei Shou and Lihua Yang for lending me some experimental equipment. I would like to thank all of my friends both in Liverpool and China for their encouragement. Finally I would like to thank my wife Liang Wen for her understanding and support during my PhD studies.

Sincerely yours, Fan Wu, 2007

# Declaration

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institution of learning.

# Contents

| ABS  | TRAC  |                                                                                                    | I   |

|------|-------|----------------------------------------------------------------------------------------------------|-----|

| ACK  | NOW   | LEDGEMENT                                                                                          | 11  |

| DEC  | LAR   | ATION                                                                                              | 111 |

| CON  | ITEN  | ΓS                                                                                                 | IV  |

| LIST | OF F  | FIGURES                                                                                            | X   |

| LIST | OF 1  | TABLES                                                                                             | XIV |

| CHA  | PTEF  | R 1. INTRODUCTION                                                                                  | 1   |

| 1.1  | Motiv | vation and objectives                                                                              | 1   |

| 1.2  | Over  | view                                                                                               | 3   |

|      |       | R 2. INTRODUCTION TO IMAGE PROCESSING, COMPUTER VISION & WOF AN PC BASED VISION SYSTEM FOR WELDING | 5   |

| 2.1  | Comj  | puter vision & image processing                                                                    | 5   |

| 2.2  | Visio | on-based closed loop process control system for welding                                            | 7   |

| 2.   | 2.1   | General description                                                                                | 7   |

| 2.   | 2.2   | Image capture and processing                                                                       | 8   |

| 2.   | 2.3   | Weld image-processing software development                                                         | 9   |

|      | 2.2.3 | .1. Feature correlation design                                                                     | 9   |

|      | 2.2.3 | .2. Front view image processing program (FVIPP)                                                    | 12  |

|      | 2.2.3 | .3. Side view image processing program (SVIPP)                                                     | 15  |

| СНА  | PTEF  | R 3. AN INTRODUCTION TO SYSTEM-ON-A-PROGRAMMABLE-CHIP (SOF                                         | PC) |

#### TECHNOLOGY 16

| 3.1 | SOPO  | C histo | ory                    | 16 |

|-----|-------|---------|------------------------|----|

| 3   | .1.1  | SOC     | design                 | 16 |

| 3   | .1.2  | ASIC    | C/SOC versus FPGA/SOPC | 17 |

|     | 3.1.2 | .1.     | Integration            | 17 |

|     | 3.1.2 | 2. Flexibility                                             | 18 |

|-----|-------|------------------------------------------------------------|----|

|     | 3.1.2 | 3. Performance                                             | 18 |

|     | 3.1.2 | 4. Power dissipation                                       | 19 |

|     | 3.1.2 | 5. Design flow                                             | 19 |

|     | 3.1.2 | 6. Time-to-market                                          | 19 |

|     | 3.1.2 | 7. Costs                                                   | 19 |

|     | 3.1.2 | 8. Conclusion                                              | 20 |

|     |       |                                                            |    |

| 3.2 | SOPO  | C architecture                                             | 21 |

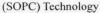

| 3.3 | SOPO  | C design flow                                              | 22 |

| 3.  | .3.1  | Design specification                                       |    |

| 3.  | .3.2  | Hardware (HW) / Software (SW) partition                    |    |

| 3.  | .3.3  | Design entry                                               |    |

| 3.  | .3.4  | Simulations                                                |    |

| 3.  | .3.5  | Synthesis                                                  | 25 |

| 3.  | .3.6  | Place & route                                              |    |

| 3.  | .3.7  | Download & verify in circuit                               | 25 |

| 3.  | .3.8  | Software development                                       |    |

| 3.  | .3.9  | Software compilation                                       |    |

|     |       | •                                                          |    |

| 3.4 | Real  | time image processing system based on SOPC                 | 26 |

| 3.  | .4.1  | On-chip vs. off-chip                                       | 27 |

| 3.  | .4.2  | Hard logic fabric vs soft logic fabric                     | 28 |

| 3.  | .4.3  | Hardware vs software                                       | 29 |

| 3.5 | Com   | mon SOPC Processor overview                                | 20 |

|     |       | Soft processor                                             |    |

| 5.  | 3.5.1 | -                                                          |    |

|     | 3.5.1 |                                                            |    |

|     | 3.5.1 |                                                            |    |

|     | 3.5.1 | -                                                          |    |

| 3   | .5.2  | Hard processor                                             |    |

| 2.  | 3.5.2 | •                                                          |    |

|     | 3.5.2 |                                                            |    |

|     | 3.5.2 |                                                            |    |

|     | 3.5.2 |                                                            |    |

|     |       |                                                            |    |

| 3.6 | Intro | duction to the Nios processor system and development tools | 34 |

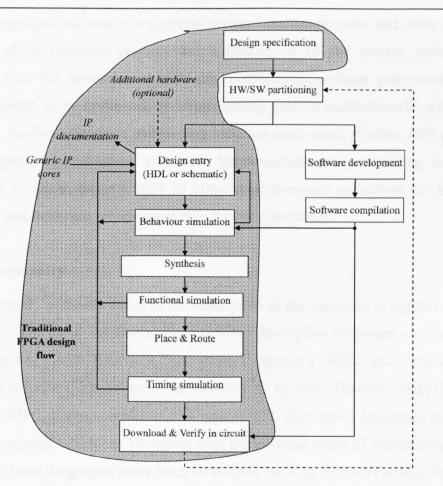

| 3.  | .6.1  | Nios system architecture                                   | 34 |

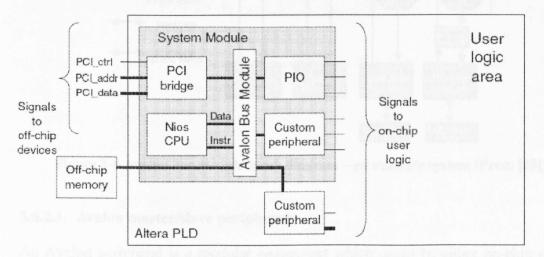

| 3.  | .6.2  | Avalon bus module                                          | 35 |

|     | 3.6.2 | 1. Avalon master/slave peripherals                         | 35 |

| 3.6.2.2. Avalon master/slave ports                                                 | 36 |

|------------------------------------------------------------------------------------|----|

| 3.6.3 Avalon bus transfers                                                         | 38 |

| 3.6.3.1. Avalon slave transfers                                                    | 39 |

| 3.6.3.2. Avalon master transfers                                                   | 42 |

| 3.6.4 Development tools overview                                                   | 43 |

| 3.6.4.1. Quartus II software                                                       | 43 |

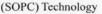

| 3.6.4.2. SOPC Builder                                                              | 44 |

| 3.6.4.3. ModelSim                                                                  | 46 |

| 3.6.4.4. Programming tool                                                          | 46 |

| 3.6.4.5. Software download tool                                                    | 46 |

| 3.6.5 Proposed image processing system with the Nios processor system architecture | 47 |

| CHAPTER 4. THE NIOS INTEGRATED REAL-TIME IMAGE PROCESSING SYSTEM -<br>HARDWARE     |    |

| 4.1 Overview of the system hardware architecture                                   | 48 |

| 4.2 Video display device & interface                                               |    |

| 4.2.1 CRT monitor                                                                  |    |

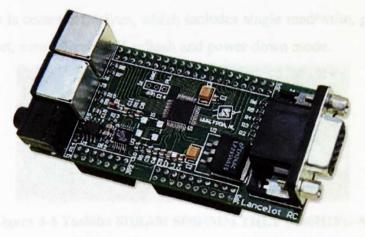

| 4.2.2 Lancelot VGA board                                                           |    |

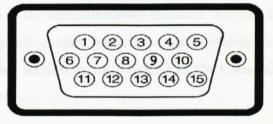

| 4.2.3 VGA connector                                                                | 51 |

| 4.3 Video memory device & interface                                                | 51 |

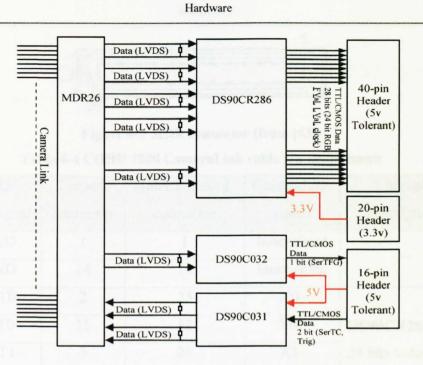

| 4.4 Video capture device & interface                                               | 52 |

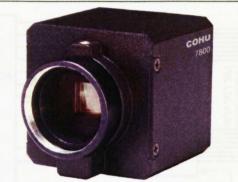

| 4.4.1 CameraLink camera                                                            | 52 |

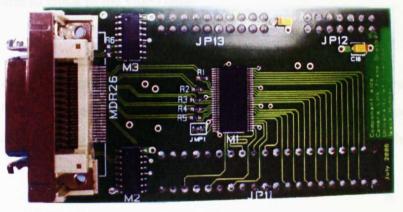

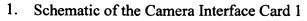

| 4.4.2 Camera interface card (custom designed)                                      | 53 |

| 4.5 Altera's Apex device                                                           | 56 |

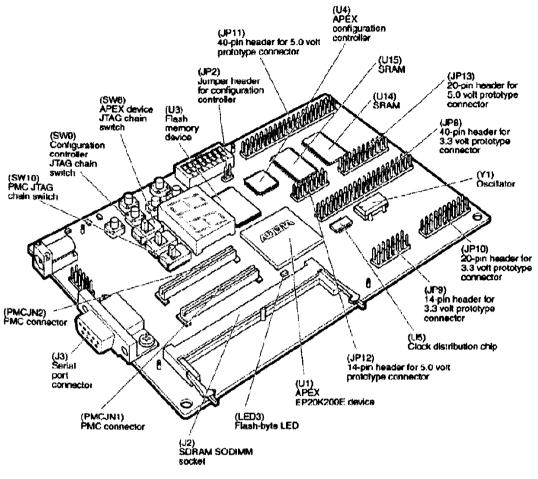

| 4.6 Nios development board                                                         | 57 |

| 4.7 Summary                                                                        | 58 |

| CHAPTER 5. THE NIOS INTEGRATED REAL-TIME IMAGE PROCESSING SYSTEM -                 |    |

| SOFT SYSTEM CORE                                                                   | 61 |

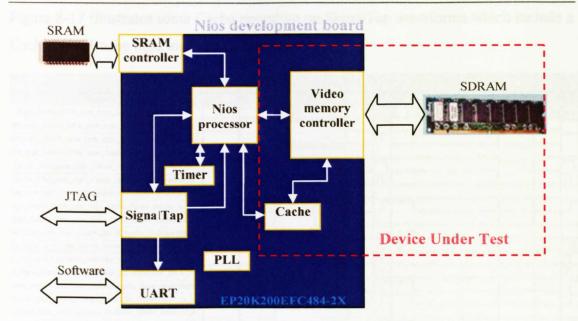

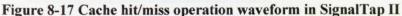

| 5.1 Overview of the system core architecture                                       | 61 |

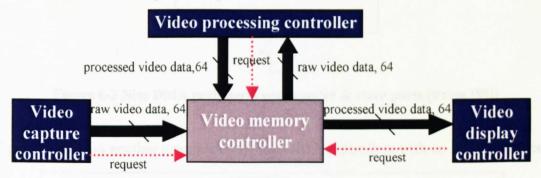

| 5.2 Video memory controller                                                        | 64 |

| 5.2.1 Main features                                                                | 64 |

| 5.2.2 Description of the video memory controller                                   | 64 |

| 5.2.2.1. Avalon interface                                                          | 68 |

|     | 5.2.2          | .2. SDRAM controller                                                                                                      | 71  |

|-----|----------------|---------------------------------------------------------------------------------------------------------------------------|-----|

|     | 5.2.2          | .3. SDRAM data path                                                                                                       | 79  |

| 5   | 5.2.3          | Summary                                                                                                                   | 80  |

| 5.3 | Vide           | o display controller                                                                                                      | 81  |

|     | 5.3.1          | Main features                                                                                                             |     |

|     | 5.3.2          | Video graphic arrays (VGA)                                                                                                |     |

|     | 5.3.3          | Description of the video display controller                                                                               |     |

| 2   | 5.3.3          | -                                                                                                                         |     |

|     | 5.3.3          |                                                                                                                           |     |

|     |                | Summary                                                                                                                   |     |

| 2   | 5.3.4          | Summary                                                                                                                   | 93  |

| 5.4 | Vide           | o capture controller                                                                                                      | 94  |

| 5   | 5.4.1          | Main features                                                                                                             | 94  |

| 4   | 5.4.2          | CameraLink                                                                                                                | 94  |

| 4   | 5.4.3          | Description of the video capture controller                                                                               | 96  |

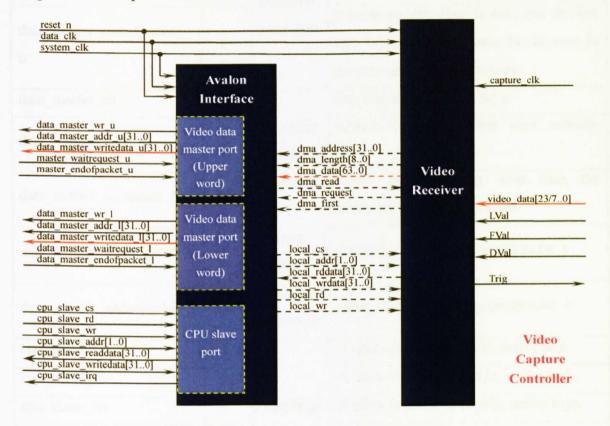

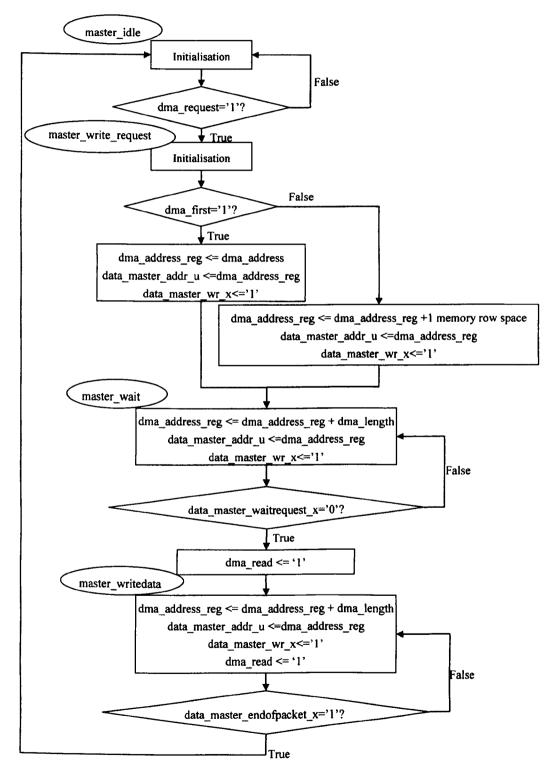

|     | 5.4.3          | .1. Avalon interface                                                                                                      | 98  |

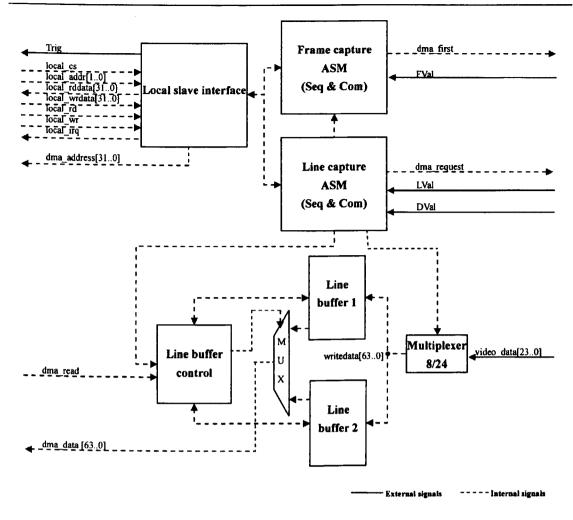

|     | 5.4.3          | 2.2. Video receiver                                                                                                       | 101 |

| 5   | 5.4.4          | Camera serial controller (UART)                                                                                           | 103 |

| 4   | 5.4.5          | Summary                                                                                                                   | 104 |

| 5.5 | Cach           | ıe                                                                                                                        | 105 |

|     | 5.5.1          | Main features                                                                                                             |     |

| 4   | 5.5.2          | Overview of the Cache                                                                                                     |     |

| 4   | 5.5.3          | Description of the Cache                                                                                                  |     |

| 4   | 5.5.4          | Summary                                                                                                                   |     |

|     |                |                                                                                                                           |     |

| 5.6 | Syste          | em clock generator                                                                                                        | 114 |

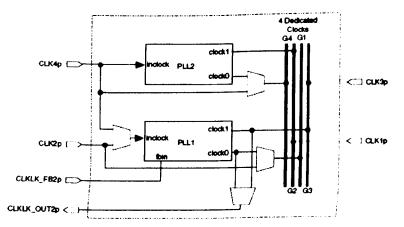

| :   | 5.6.1          | Data clock                                                                                                                | 115 |

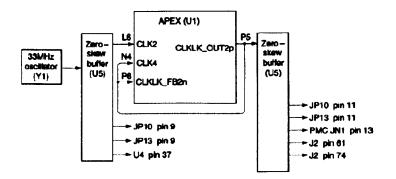

| 4   | 5.6.2          | System clock                                                                                                              | 116 |

| -   | 5.6.3          | Video display clock                                                                                                       | 116 |

| 4   | 5.6.4          | Video capture clock                                                                                                       | 117 |

| -   | 5.6.5          | Discussions                                                                                                               | 117 |

| 5.7 | Expl           | anation of some design issues                                                                                             | 118 |

|     | 5.7.1          | Multiple-bank operation                                                                                                   |     |

| •   | 5.7.1          |                                                                                                                           |     |

|     | 5.7.1          |                                                                                                                           |     |

|     | 5.7.1<br>5.7.2 |                                                                                                                           |     |

|     |                | Double line buffer in the video display & capture controller                                                              | 120 |

|     | 572            | Double line buffer in the video display & capture controller                                                              |     |

|     | 5.7.3<br>5.7.4 | Double line buffer in the video display & capture controller<br>Synchronisation of multiple clock domains<br>Other issues | 121 |

| WIT   | H PERIPHE    | RAL-CONTROLLED WAITREQUEST                                                        | 123 |

|-------|--------------|-----------------------------------------------------------------------------------|-----|

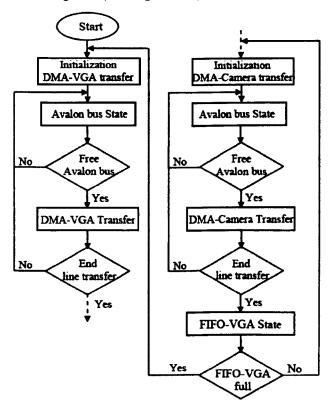

| 6.1   | Synchronis   | ation of DMA controllers solution                                                 | 123 |

| 6.2   | Avalon bus   | arbitration                                                                       | 126 |

| 6.3   | Implementa   | ation of simultaneous multi-mastering streaming Avalon transfer with peripheral-  |     |

| conti | olled waitre | quest                                                                             | 130 |

| 6.4   | Another so   | lution                                                                            | 135 |

| СНА   | PTER 7.      | SYSTEM CORE GENERATION, SYNTHESIS & IMPLEMENTATION                                | 136 |

| 7.1   | System cor   | e generation                                                                      | 136 |

| 7.    | 1.1 PTF      | files                                                                             | 136 |

| 7     | 1.2 Syste    | m generation                                                                      | 137 |

| 7.2   | System cor   | e synthesis                                                                       | 140 |

| 7     | 2.1 Syste    | em core synthesis                                                                 | 141 |

| 7     | 2.2 Synth    | hesis results & discussions                                                       | 143 |

|       |              | SYSTEM TESTS, IMAGE PROCESSING ALGORITHM IMPLEMENTATI                             |     |

| 8.1   | -            | ts                                                                                |     |

| 8     | .1.1 Simu    | lations                                                                           |     |

|       | 8.1.1.1.     | Video memory controller simulation results & discussions                          | 147 |

|       | 8.1.1.2.     | Video display controller simulation results and discussions                       | 153 |

|       | 8.1.1.3.     | Cache simulation results and discussions                                          | 153 |

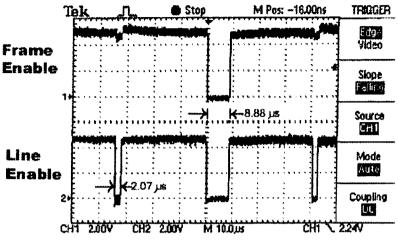

|       | 8.1.1.4.     | Video capture controller simulation results and discussions                       | 154 |

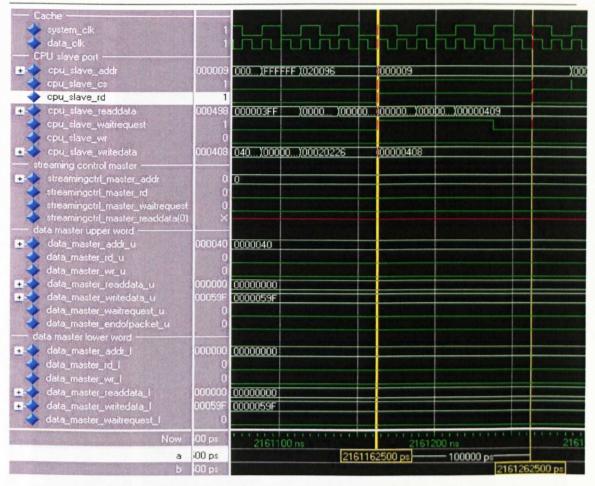

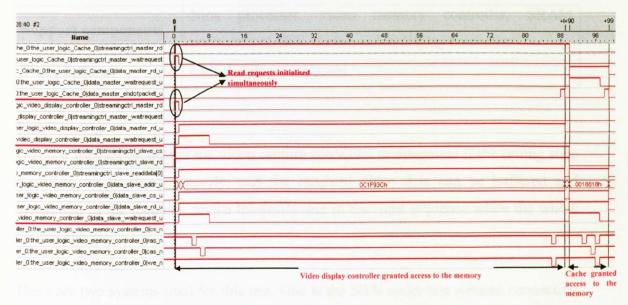

|       | 8.1.1.5.     | Full system simulations results and discussions                                   | 162 |

| 8     | .1.2 Hard    | Iware verifications                                                               | 164 |

|       | 8.1.2.1.     | Video memory test                                                                 | 164 |

|       | 8.1.2.2.     | Video display test                                                                | 167 |

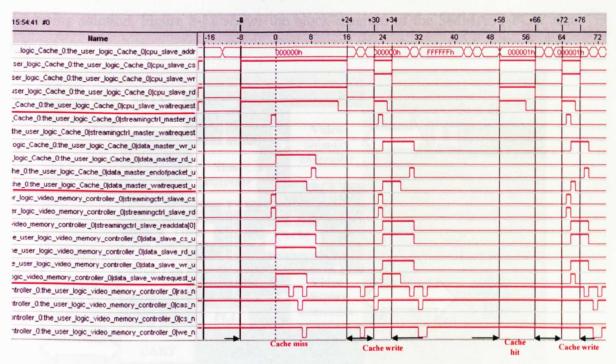

|       | 8.1.2.3.     | Cache test                                                                        | 170 |

|       | 8.1.2.4.     | SMMAST-PCW test                                                                   | 173 |

|       | 8.1.2.5.     | Video capture test                                                                | 174 |

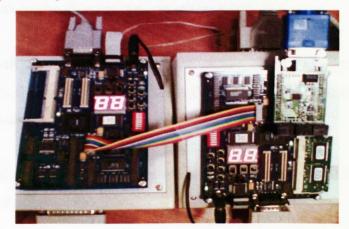

|       | 8.1.2.6.     | Full system test                                                                  | 176 |

| 8.2   | Implement    | tation of various image processing algorithms and real-time performance analysis. | 179 |

| 8     | .2.1 Gen     | eral software development                                                         | 179 |

|       | 8.2.1.1.     | Setting up video display & capture                                                | 179 |

|       |              |                                                                                   |     |

CHAPTER 6. SIMULTANEOUS MULTI-MASTERING AVALON STREAMING TRANSFER

|     | 8.2.1   | .2.     | Implementing multiple bank operation & interrupt services              |     |

|-----|---------|---------|------------------------------------------------------------------------|-----|

|     | 8.2.1   | .3.     | Memory read/write operations                                           |     |

|     | 8.2.1   | .4.     | Timer function                                                         | 181 |

| 8   | .2.2    | Discu   | ssion of software coding style – optimisation issue                    | 181 |

| 8   | .2.3    | Syste   | m performance analysis                                                 | 184 |

| 8   | .2.4    | Imple   | mentation of five image processing algorithms and performance analysis |     |

|     | 8.2.4   | .1.     | Inversion                                                              | 184 |

|     | 8.2.4   | .2.     | Sobel edge detector                                                    |     |

|     | 8.2.4   | .3.     | Gaussian blur filter (a low pass filter)                               |     |

|     | 8.2.4   | .4.     | Sharpness filter – (a high pass filter)                                | 193 |

|     | 8.2.4   | .5.     | Feature correlation                                                    | 195 |

| 8.3 | Sumi    | mary    |                                                                        | 197 |

| СН  | APTER   | R 9.    | CONCLUSIONS AND FUTURE WORK                                            | 198 |

| 9.1 | Conc    | lusion  | s                                                                      | 198 |

| 9.2 | Futu    | re worl | κ                                                                      | 200 |

| 9   | 9.2.1   | Optin   | nisation/improvements                                                  | 200 |

|     | 9.2.1   | .1.     | Later generation FPGA                                                  | 201 |

|     | 9.2.1   | .2.     | FPGA Hardware processing                                               | 201 |

| 9   | .2.2    | Appli   | cation                                                                 | 201 |

| REI | FEREN   | NCES    |                                                                        | 203 |

| API | PENDI   | XES.    |                                                                        | 212 |

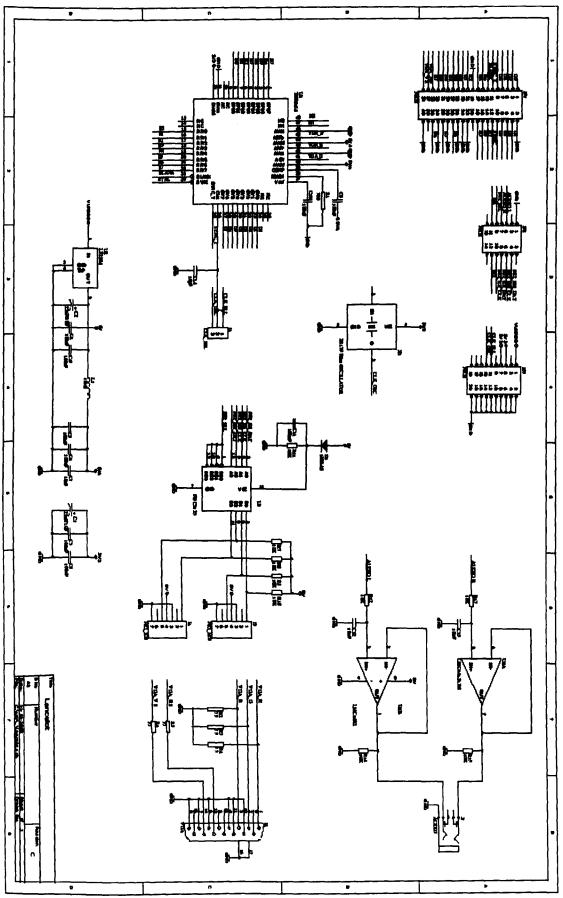

| Арр | endix A | A Sche  | ematics                                                                | 212 |

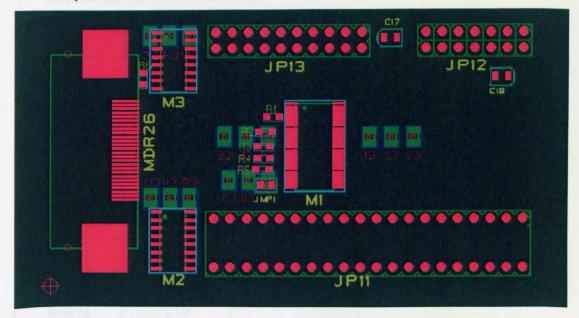

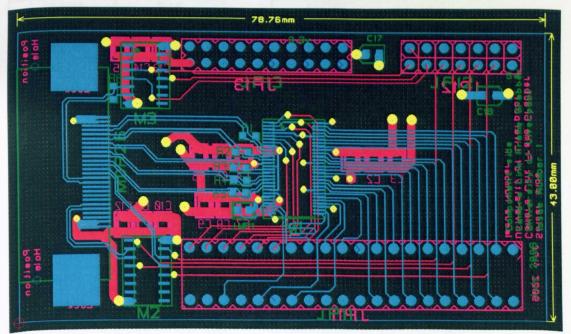

| Арр | endix l | B Cam   | era interface card PCB details                                         | 215 |

| Арр | endix ( | C Pin a | assignments for video components                                       | 216 |

| Арр | endix l | D Trut  | h table for the operation commands of SDRAM                            | 219 |

| Арр | endix I | E Regi  | ster maps                                                              | 220 |

| Арр | endix l | F PTF   | Files – An example of Cache                                            | 224 |

# **List of Figures**

| Figure 2-1 Common steps in real-time image processing system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2-2 Closed loop weld process control (From [3])7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 2-3 Real time image capture and analysis (From [3])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Figure 2-4 Image edge feature correlation (From [3])10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 2-5 Front view measured Items                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 2-6 Front view image processing program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 2-7 Configuration mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 2-8 Calibration mode14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

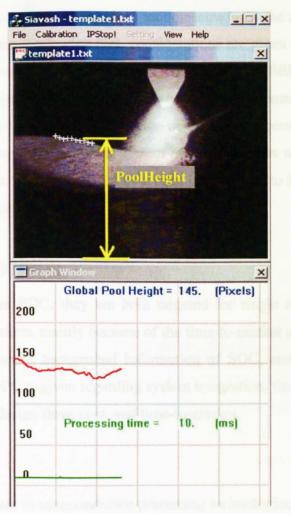

| Figure 2-9 Side view image processing program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

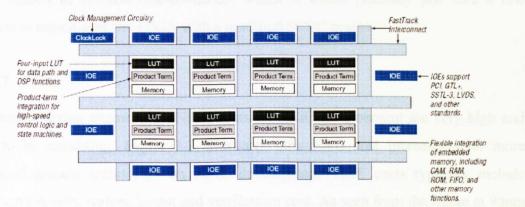

| Figure 3-1 Apex 20K device block diagram (From [27])18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

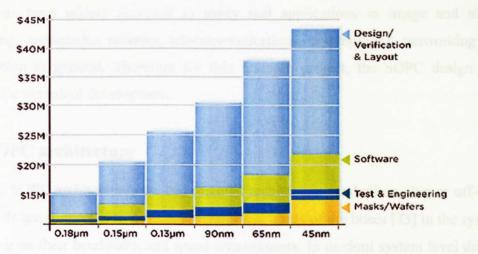

| Figure 3-2 NRE cost of developing ASICs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 3-3 Overall SOPC design flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Figure 3-4 System module integrated with user logic into an Altera PLD (From [35]) 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 3-5 Avalon bus module block diagram – an example system (From [35])35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

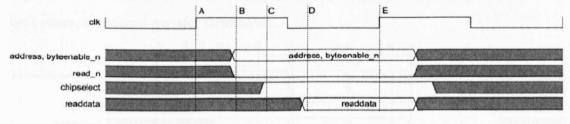

| Figure 3-6 Fundamental slave read transfer (From [35])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

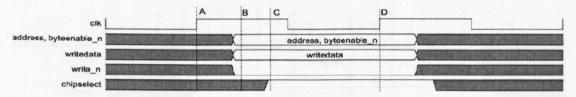

| Figure 3-7 Fundamental slave write transfer (From [35])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

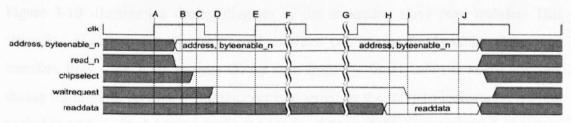

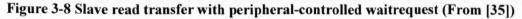

| Figure 3-8 Slave read transfer with peripheral-controlled waitrequest (From [35])40                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 3-8 Slave read transfer with peripheral-controlled waitrequest (From [35])40                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Figure 3-8 Slave read transfer with peripheral-controlled waitrequest (From [35])40<br>Figure 3-9 Slave write transfer with peripheral-controlled waitrequest (From [35])41                                                                                                                                                                                                                                                                                                                                                                                       |

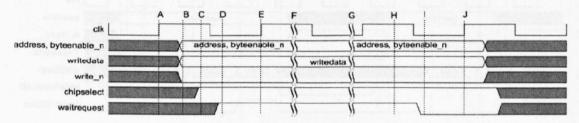

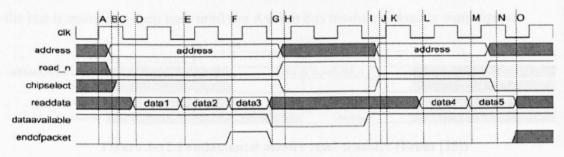

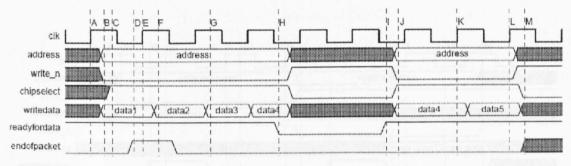

| Figure 3-8 Slave read transfer with peripheral-controlled waitrequest (From [35])40<br>Figure 3-9 Slave write transfer with peripheral-controlled waitrequest (From [35])41<br>Figure 3-10 Streaming slave read transfer (From [35])42                                                                                                                                                                                                                                                                                                                            |

| Figure 3-8 Slave read transfer with peripheral-controlled waitrequest (From [35])40<br>Figure 3-9 Slave write transfer with peripheral-controlled waitrequest (From [35])41<br>Figure 3-10 Streaming slave read transfer (From [35])                                                                                                                                                                                                                                                                                                                              |

| Figure 3-8 Slave read transfer with peripheral-controlled waitrequest (From [35])40Figure 3-9 Slave write transfer with peripheral-controlled waitrequest (From [35])41Figure 3-10 Streaming slave read transfer (From [35])                                                                                                                                                                                                                                                                                                                                      |

| Figure 3-8 Slave read transfer with peripheral-controlled waitrequest (From [35])40Figure 3-9 Slave write transfer with peripheral-controlled waitrequest (From [35])41Figure 3-10 Streaming slave read transfer (From [35])42Figure 3-11 Streaming slave write transfer (From [35])                                                                                                                                                                                                                                                                              |

| Figure 3-8 Slave read transfer with peripheral-controlled waitrequest (From [35])40Figure 3-9 Slave write transfer with peripheral-controlled waitrequest (From [35])41Figure 3-10 Streaming slave read transfer (From [35])                                                                                                                                                                                                                                                                                                                                      |

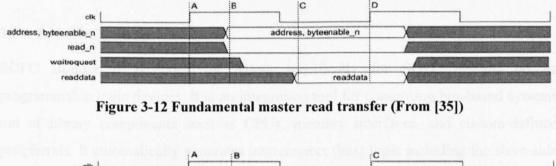

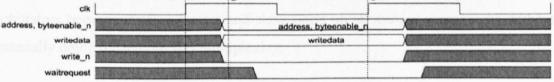

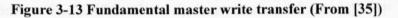

| Figure 3-8 Slave read transfer with peripheral-controlled waitrequest (From [35])40Figure 3-9 Slave write transfer with peripheral-controlled waitrequest (From [35])41Figure 3-10 Streaming slave read transfer (From [35])42Figure 3-11 Streaming slave write transfer (From [35])42Figure 3-12 Fundamental master read transfer (From [35])43Figure 3-13 Fundamental master write transfer (From [35])                                                                                                                                                         |

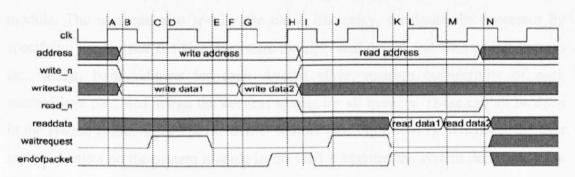

| Figure 3-8 Slave read transfer with peripheral-controlled waitrequest (From [35]) 40Figure 3-9 Slave write transfer with peripheral-controlled waitrequest (From [35]) 41Figure 3-10 Streaming slave read transfer (From [35]) 42Figure 3-11 Streaming slave write transfer (From [35]) 42Figure 3-12 Fundamental master read transfer (From [35]) 43Figure 3-13 Fundamental master write transfer (From [35]) 43Figure 3-14 Streaming master R/W transfer (From [35]) 43Figure 3-15 SOPC Builder system contents page (From [55])                                |

| Figure 3-8 Slave read transfer with peripheral-controlled waitrequest (From [35]) 40Figure 3-9 Slave write transfer with peripheral-controlled waitrequest (From [35]) 41Figure 3-10 Streaming slave read transfer (From [35]) 42Figure 3-11 Streaming slave write transfer (From [35]) 42Figure 3-12 Fundamental master read transfer (From [35]) 43Figure 3-13 Fundamental master write transfer (From [35]) 43Figure 3-14 Streaming master R/W transfer (From [35])                                                                                            |

| Figure 3-8 Slave read transfer with peripheral-controlled waitrequest (From [35]) 40Figure 3-9 Slave write transfer with peripheral-controlled waitrequest (From [35]) 41Figure 3-10 Streaming slave read transfer (From [35]) 42Figure 3-11 Streaming slave write transfer (From [35]) 42Figure 3-12 Fundamental master read transfer (From [35]) 43Figure 3-13 Fundamental master write transfer (From [35]) 43Figure 3-14 Streaming master R/W transfer (From [35])                                                                                            |

| Figure 3-8 Slave read transfer with peripheral-controlled waitrequest (From [35]) 40Figure 3-9 Slave write transfer with peripheral-controlled waitrequest (From [35]) 41Figure 3-10 Streaming slave read transfer (From [35]) 42Figure 3-11 Streaming slave write transfer (From [35]) 42Figure 3-12 Fundamental master read transfer (From [35]) 43Figure 3-13 Fundamental master write transfer (From [35]) 43Figure 3-14 Streaming master R/W transfer (From [35]) 43Figure 3-15 SOPC Builder system contents page (From [55])                                |

| Figure 3-8 Slave read transfer with peripheral-controlled waitrequest (From [35])40Figure 3-9 Slave write transfer with peripheral-controlled waitrequest (From [35])41Figure 3-10 Streaming slave read transfer (From [35])42Figure 3-11 Streaming slave write transfer (From [35])42Figure 3-12 Fundamental master read transfer (From [35])43Figure 3-13 Fundamental master write transfer (From [35])43Figure 3-14 Streaming master R/W transfer (From [35])43Figure 3-15 SOPC Builder system contents page (From [35])45Figure 3-16 SOPC Builder (From [42]) |

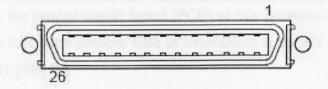

| Figure 4-8 Block diagram of the camera interface card                            | 54    |

|----------------------------------------------------------------------------------|-------|

| Figure 4-9 MDR connector (from [63])                                             | 55    |

| Figure 4-10 Nios development board (From: [58])                                  | 58    |

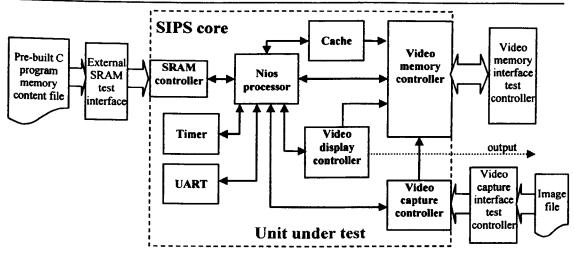

| Figure 5-1 Top level block diagram of SIPS core                                  | 63    |

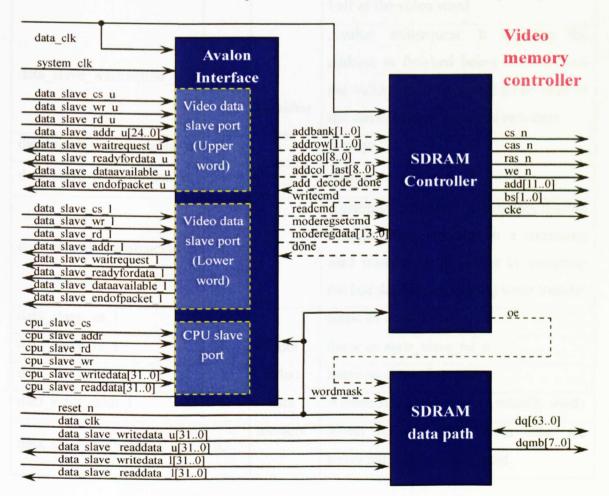

| Figure 5-2 Block diagram of the video memory controller                          | 65    |

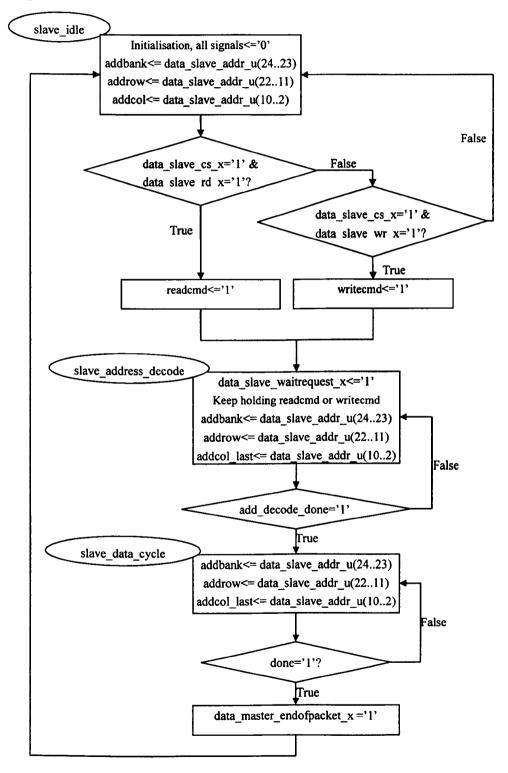

| Figure 5-3 ASM chart of the Avalon streaming slave transfer                      | 70    |

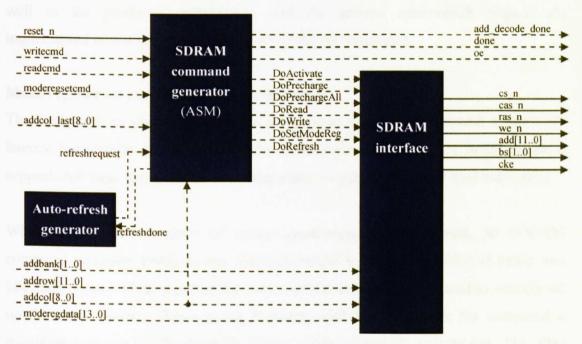

| Figure 5-4 Block diagram of the SDRAM controller                                 | 71    |

| Figure 5-5 Mode Register Set cycle (From [62])                                   | 73    |

| Figure 5-6 Page Mode Read/Write (Burst Length = 8, CAS Latency = 3) (From [62]   | ])76  |

| Figure 5-7 Timing chart for Burst Stop cycle (From [62])                         | 77    |

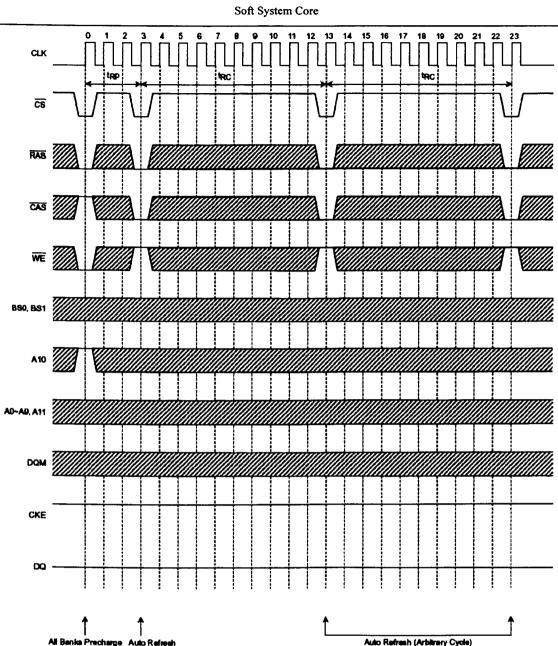

| Figure 5-8 Auto Refresh cycle (From [62])                                        | 78    |

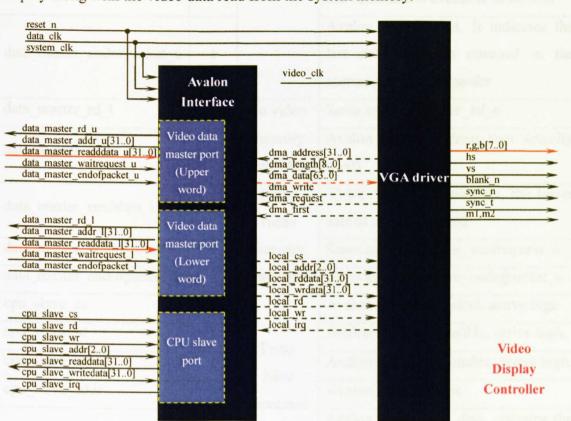

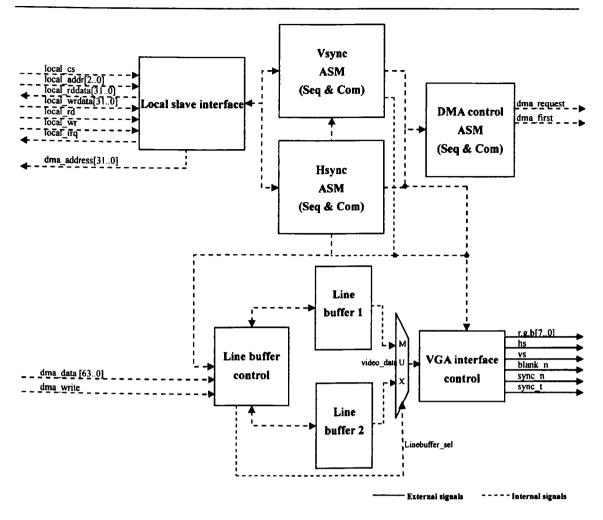

| Figure 5-9 Block diagram of the video display controller                         | 83    |

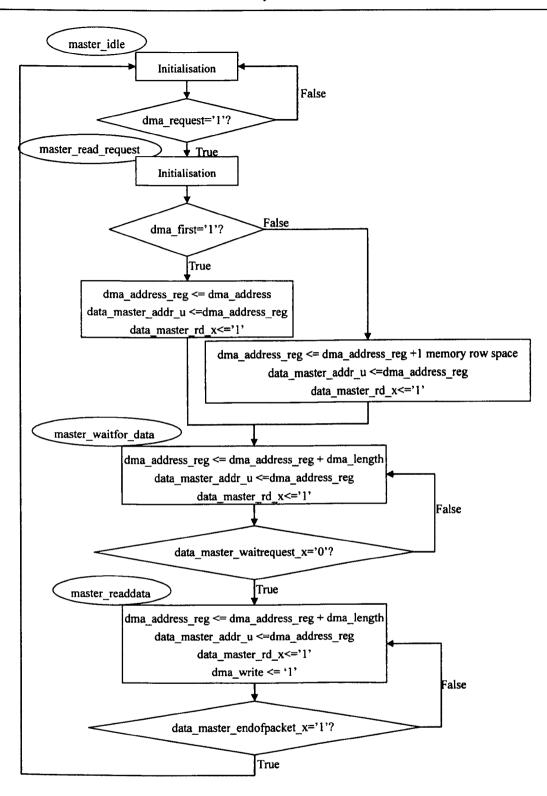

| Figure 5-10 ASM chart of the Avalon streaming master read transfer               | 88    |

| Figure 5-11 Block diagram of the VGA driver                                      | 89    |

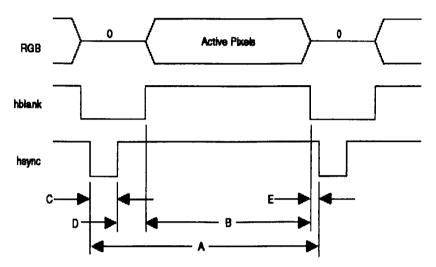

| Figure 5-12 640×480 VGA horizontal timing (From [73])                            | 90    |

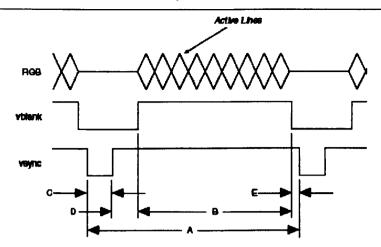

| Figure 5-13 640×480 VGA vertical timing (From [73])                              | 91    |

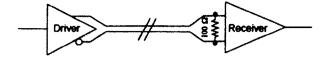

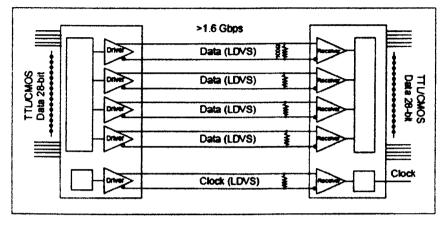

| Figure 5-14 Channel Link operation (From [60])                                   | 95    |

| Figure 5-15 Block diagram of the video capture controller                        | 96    |

| Figure 5-16 ASM chart of the Avalon streaming master write transfer              | . 100 |

| Figure 5-17 Block diagram of the video receiver                                  | . 102 |

| Figure 5-18 Camera timing (From [63])                                            | . 103 |

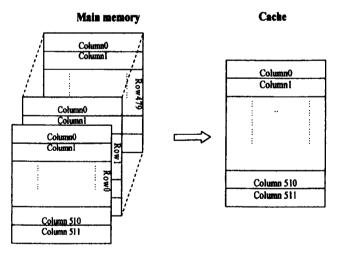

| Figure 5-19 Cache mapping to the main memory                                     | . 106 |

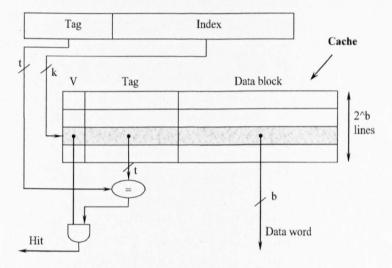

| Figure 5-20 Cache structure (From [83])                                          | . 107 |

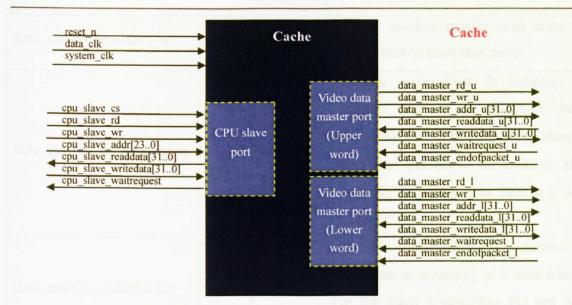

| Figure 5-21 Block diagram of the Cache                                           | . 108 |

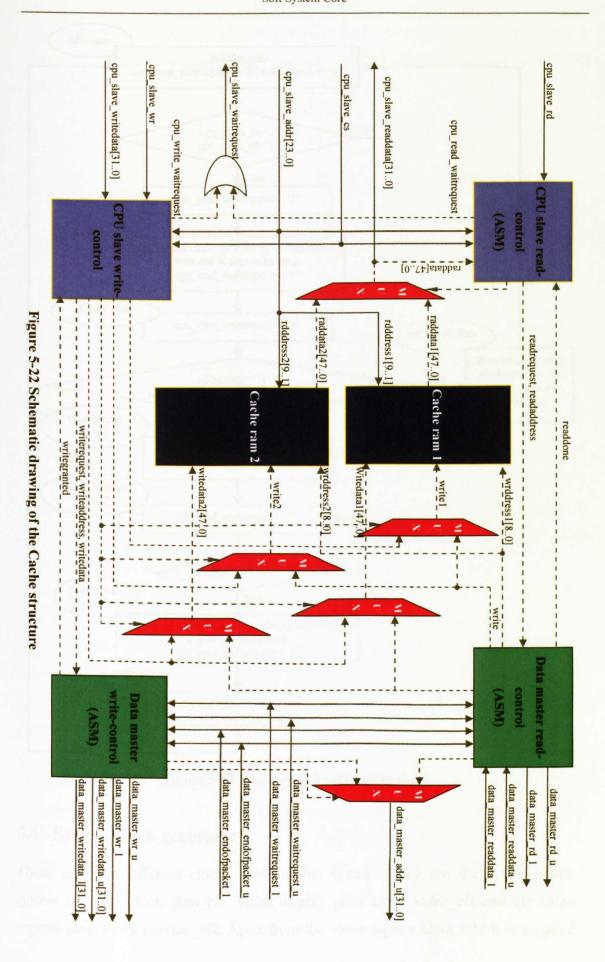

| Figure 5-22 Schematic drawing of the Cache structure                             | . 113 |

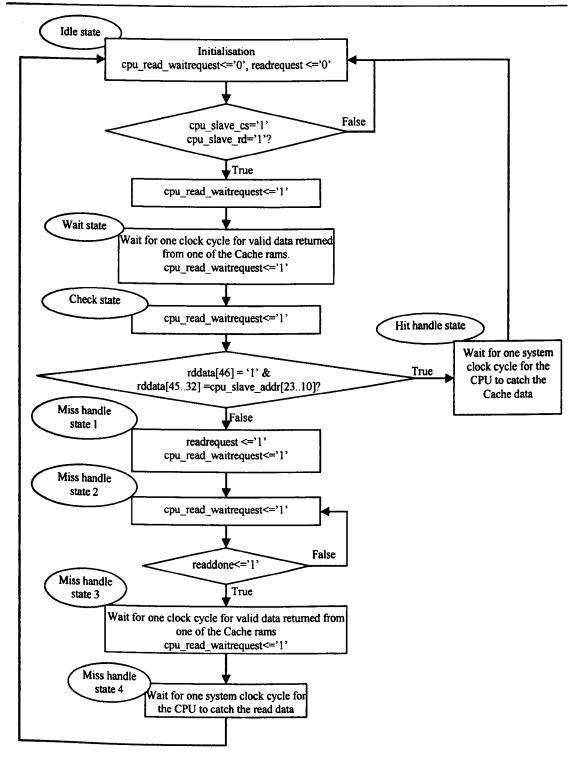

| Figure 5-23 Cache read handle ASM chart                                          | . 114 |

| Figure 5-24 Dedicated global clock pin connections to PLL & dedicated clock line | s for |

| EP20K30E, EP20K60E, EP20K100E, EP20K160E & EP20K200E devices (from [             | [84]) |

|                                                                                  | .115  |

| Figure 5-25 Clock circuitry (From [58])                                          | .117  |

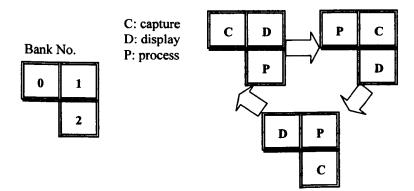

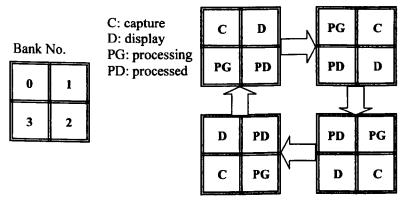

| Figure 5-26 Triple-bank operation                                                | .119  |

| Figure 5-27 Quad-bank operation                                                  | .119  |

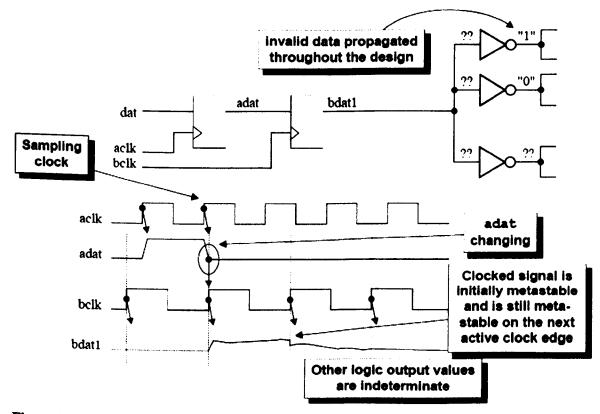

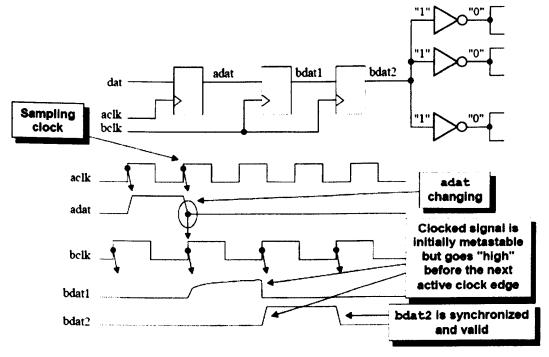

| Figure 5-28 Metastable output propagating invalid data throughout the design (   | from  |

| [86])                                                                            | . 121 |

| Figure 5-29 Two flip-flop synchroniser (from [86])122                                    |

|------------------------------------------------------------------------------------------|

| Figure 6-1 Triple-ported video memory slave                                              |

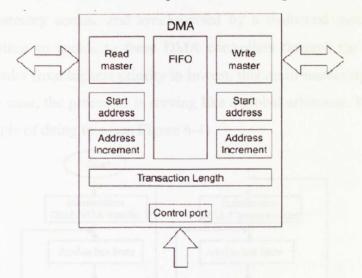

| Figure 6-2 Nios DMA peripheral with master & slave ports (From [88])124                  |

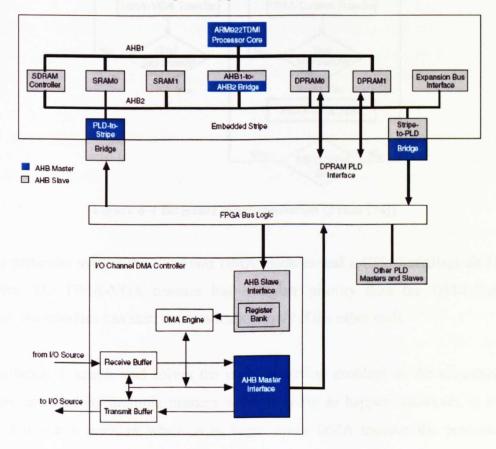

| Figure 6-3 I/O to memory DMA controller – Excalibur (From [73])124                       |

| Figure 6-4 Interface synchronisation (From [74])125                                      |

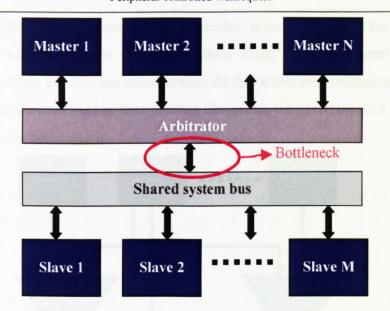

| Figure 6-5 Centralised, parallel arbitration bus architecture                            |

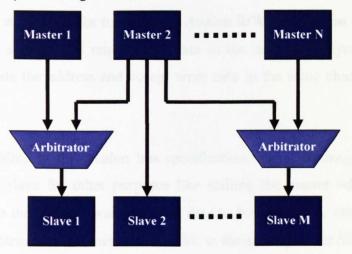

| Figure 6-6 Simultaneous multi-mastering Avalon bus arbitration128                        |

| Figure 6-7 Successive fundamental read transfers to a common slave (From [90]) 128       |

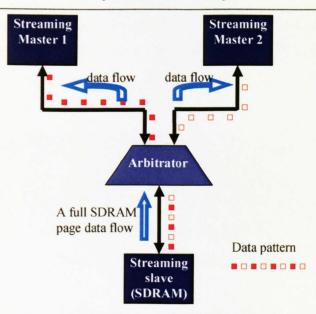

| Figure 6-8 An arbitration view during conflict between two streaming masters130          |

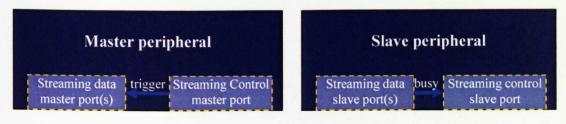

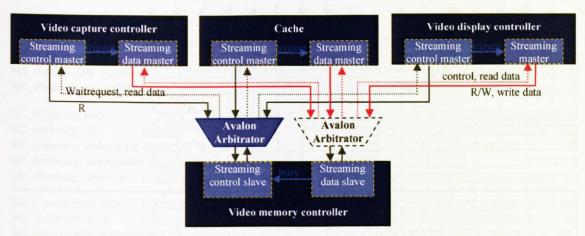

| Figure 6-9 Master peripheral and slave peripheral with streaming control feature131      |

| Figure 6-10 Block diagram of simultaneous multi-mastering image processing system        |

|                                                                                          |

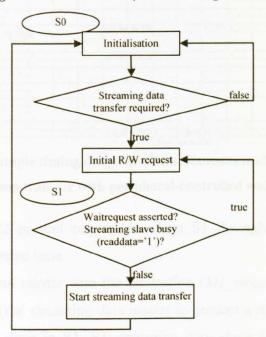

| Figure 6-11 ASM chart of streaming control master                                        |

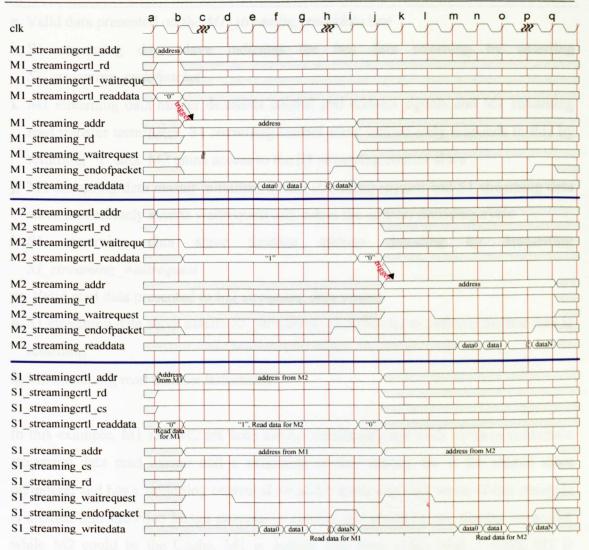

| Figure 6-12 An example timing diagram of simultaneous multi-mastering Avalon             |

| streaming transfer with peripheral-controlled waitrequest                                |

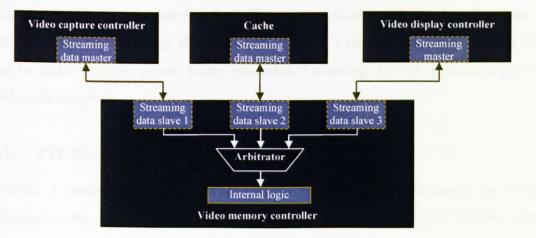

| Figure 6-13 Multi-ported memory slave solution                                           |

| Figure 7-1 Custom defined library components                                             |

| Figure 7-2 Top-level system view in SOPC Builder                                         |

| Figure 7-3 System generation results                                                     |

| Figure 7-4 Top system module view                                                        |

| Figure 7-5 Block diagram of the SIPS core                                                |

| Figure 8-1 SIPS simulation scheme147                                                     |

| Figure 8-2 Video memory controller simulation result – burst write $(BL = 1)$ 149        |

| Figure 8-3 Video memory controller simulation result – burst write $(BL = 80) \dots 150$ |

| Figure 8-4 Video memory controller simulation result – burst read (BL =1)151             |

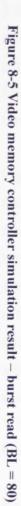

| Figure 8-5 Video memory controller simulation result – burst read ( $BL = 80$ )152       |

| Figure 8-6 Video display controller simulation result 1                                  |

| Figure 8-7 Video display controller simulation result 2                                  |

| Figure 8-8 Cache simulation result – Cache write157                                      |

| Figure 8-9 Cache simulation result – Cache miss (BL=1)158                                |

| Figure 8-10 Cache simulation result – Cache hit                                          |

| Figure 8-11 video capture controller simulation result 1                                 |

| Figure 8-12 video capture controller simulation result 2                                 |

| Figure 8-13 Full system simulation result                                                |

| Figure 8-14 Video memory test scheme                                              | 65 |

|-----------------------------------------------------------------------------------|----|

| Figure 8-15 Video display test scheme                                             | 67 |

| Figure 8-16 Cache test scheme                                                     | 71 |

| Figure 8-17 Cache hit/miss operation waveform in SignalTap II1                    | 72 |

| Figure 8-18 SMMAST-PCW test scheme                                                | 73 |

| Figure 8-19 simultaneously multi-mastering operation waveform in SignalTap II 1   | 74 |

| Figure 8-20 Video capture test scheme                                             | 74 |

| Figure 8-21 system view of the video capture test without a camera1               | 75 |

| Figure 8-22 video capture test result                                             | 76 |

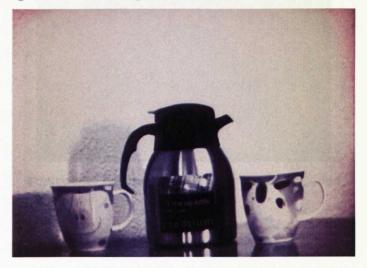

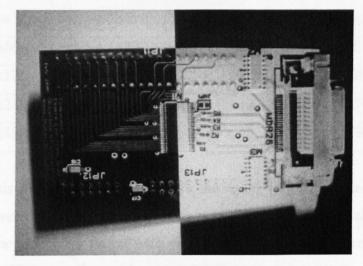

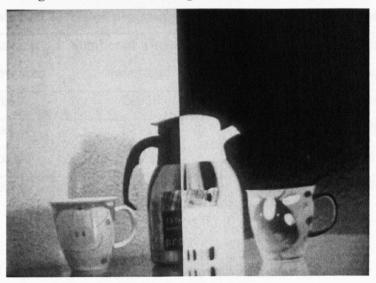

| Figure 8-23 Test image – camera interface card (original)1                        | 77 |

| Figure 8-24 Test image – mugs and jug (original)                                  | 77 |

| Figure 8-25 An example of the testing background                                  | 78 |

| Figure 8-26 Inversion image – camera interface card                               | 85 |

| Figure 8-27 Inversion image – mugs and jug                                        | 85 |

| Figure 8-28 Sobel edge detector image - camera interface card (threshold=60) 18   | 87 |

| Figure 8-29 Sobel edge detector image – mugs and jug (threshold=60)18             | 87 |

| Figure 8-30 Sobel convolution kernels                                             | 87 |

| Figure 8-31 Gaussian blur filter image – camera interface card (mask size 7x7) 19 | 90 |

| Figure 8-32 Gaussian blur filter image – mugs and jug (mask size 7x7)             | 90 |

| Figure 8-33 Gaussian filters coefficients (from [104])                            | 91 |

| Figure 8-34 Sharpness filter image –camera interface card                         | 93 |

| Figure 8-35 Sharpness filter image –camera interface card                         | 93 |

| Figure 8-36 Feature correlation image (measured on pool edges & wire edges) 19    | 95 |

# List of Tables

| Table 2-1 Measurements of the front view image processing program      | 12           |

|------------------------------------------------------------------------|--------------|

| Table 3-1 World SOC Market, 2003, 2004, 2009 and AAGR ('04-'09)        | 17           |

| Table 3-2 Avalon slave port signals                                    | 37           |

| Table 3-3 Avalon master port signals                                   | 38           |

| Table 4-1 Device table                                                 | .49          |

| Table 4-2 VGA connector pin assignment                                 | .51          |

| Table 4-3 COHU 7800 series camera specifications                       | . 52         |

| Table 4-4 COHU 7800 CameraLink cable pin assignments                   | .55          |

| Table 4-5 Apex 20K200E device features (From [27])                     | .57          |

| Table 5-1 Video memory controller top level signals                    | .66          |

| Table 5-2 Internal signals of the video memory controller              | .68          |

| Table 5-3 SDRAM address mapping                                        | .69          |

| Table 5-4 Mode register set command                                    | .72          |

| Table 5-5 Streaming read command                                       | .74          |

| Table 5-6 Streaming write command                                      | .75          |

| Table 5-7 Auto refresh command                                         | .77          |

| Table 5-8 Description of the word mask                                 | . 80         |

| Table 5-9 Video display controller top level signals                   | . 83         |

| Table 5-10 Internal signals of the video display controller            | .85          |

| Table 5-11 Pixel assignment in 8-bit monochrome mode for video display | . <b>8</b> 6 |

| Table 5-12 Pixel assignment in 24-bit RGB mode for video display       | . 86         |

| Table 5-13 640×480 VGA horizontal timing                               | .90          |

| Table 5-14 640×480 VGA vertical timing                                 | .91          |

| Table 5-15 Alternating operations of the double line buffer            | .92          |

| Table 5-16 CameraLink signals                                          | .95          |

| Table 5-17 Video capture controller top level signals                  | .96          |

| Table 5-18 Internal signals of the video capture controller            | . 98         |

| Table 5-19 Pixel assignment in 8-bit monochrome mode for video capture | .99          |

| Table 5-20 Pixel assignment in 24-bit RGB mode for video capture       | .99          |

| Table 5-21 Cache top level signals                                     | 108          |

| Table 7-1 Synthesis result in 8-bit mode                               | 143          |

| Table 7-2 Estimated performance on various FPGAs                       | 145          |

#### **Chapter 1. Introduction**

#### 1.1 Motivation and objectives

Real time vision systems have been widely used in security, quality control and automatic handling etc. Conventional vision systems can be classified into two different types of architecture [1].

One is a board type device for a host computer (i.e. personal computer PC). Every function module can be implemented as a separate board with a computer expansion interface, for example a video acquisition card and graphic card. J.Kang and R. Doraiswami developed such a system with an add-on universal serial bus (USB) interface board to allow the PC to capture video from an external web-cam for endoscopic applications [2]. C. Balford, J. S. Smith and S. Amin-Nejad present a vision-based closed loop control system for weld application where a PC associated with a video capture card and a graphic card was used to perform real-time video acquisition, image analysis and display [3]. Although some systems use hardware accelerated approaches, for example, by incorporating an array of processing elements (or computing elements) built from Application Specific Integrated Circuits (ASICs) or Field Programmable Gate Arrays (FPGAs) into a video acceleration board with the ability of providing parallel processing to handle some or all of the complex image processing tasks, such as systems using a Splash 2 board [4], other applications for discrete-time cellular neural network (DTCNN) use a highly parallel integrated circuits (HiPIC) add-on board [5]. Generally most computer based vision systems use the software approach – by using the generic Central Processing Unit (CPU) to perform all image processing tasks for cost reasons. With the rapid increase of the speed and functionality of the generic processors, like Intel processors, the software approach now offers more processing power to handle more complex image processing tasks in real-time. These PC based vision systems can offer distinct performance and expandable functionality, however, they are not ideal for compact vision systems because a host computer is required to connect and control all peripherals.

Another type of vision systems are embedded systems which consist of one or more microprocessors to control the whole system and perform image processing tasks.

These microprocessors could be general purpose microprocessors (e.g. Motorola 68030) or digital signal processing (DSP) microprocessors (e.g. TI 320 series) [6]. This type of architecture allows the whole system to be built into a single standalone device. For example, a vision-based target tracking system was developed for an embedded application of surveillance with a drone by using two-processor including a microprocessor for camera control and a DSP processor for implementing the block matching algorithm [7]. Another example is a mobile mini robot with embedded CMOS vision system designed for an indoor soccer game scenario, image processing algorithms including feature extraction and object classification are performed by a PIC microcontroller [8]. However, the significant increase of hardware complexity results in a much less significant speed-up for microprocessors. Therefore in the future, further development of the complex superscalar processors is unlikely [9]. Besides the performance issue, the lack of flexibility and optimisation, and complexities of firmware coding on some particular microprocessors [10] are other issues that system developers may encounter. In fact the obsolescence of microprocessors has been a major concern for many companies with regards of the difficulties of further development and upgrades [11].

Recent advances in semiconductor technology have made it possible to integrate the entire embedded/computer system including processors, memory and other system units into a single programmable chip - FPGA, and this technology is called "System-on-a-Programmable-Chip" (SOPC) [12]. This solution therefore offers an alternative architecture to implement the standalone vision system. In fact, as the rapid increase of FPGA density (about 10 times in two years [9]) has already made it expand quicker than microprocessors, taking into account the silicon area and throughput, the FPGAs significantly outperform microprocessor [13], and in the future the performance gap will further increase.

Due to the reconfigurable ability and compact nature, SOPC offers high performance and flexibility with low risks. SOPC designs can be very easy migrated into different kinds of FPGAs to provide various performances without worrying problems such as the changes of the system architecture, because all components can be implemented as a separate non-device specific soft Intellectual Properties (IP) core including the processors. This is a feature that conventional microprocessor systems can't easily fulfill. By using the soft processor core such as Nios processor from Altera and Microblaze from Xilinx [14], the system architecture is configurable allowing a tradeoff between performance and area by changing the architecture [15]. Designs can be customised and further optimised to suit different system platforms by changing Cache size and type, optimising processor instructions and so on. Furthermore, the SOPCs have other advantages like low cost and short development time [16].

One processor intensive application which is ideal for SOPC technology is that of image processing where there is a repeated application of operations on the twodimensional (2D) data. Therefore, the objectives of this research were to investigate the use of SOPC technology in building a real time image processing system with the capability of performing video acquisition, display and processing. To achieve this requires solutions to problems that would occur under this new system architecture like the multi-mastering burst transfers. This system is named "an SOPC based image processing system" (SIPS) as it aims at implementing general image processing, whilst further development into a complete computer vision system, for various applications, can be achieved by integrating more system controllers.

This research was motivated from an existing PC based vision system for welding application [3]. One of the improvements for this system was to provide a complete computer vision-based sensor capable of delivering the required measurements on demand without the use of a host computer, so that it allows easier integration of the vision sensing system with commercial welding process controllers.

#### 1.2 Overview

This thesis is organised as nine chapters and a brief introduction for each chapter is now given as follows:

Chapter Two firstly gives some explanations of fundamental concepts regarding image processing and computer vision. Then an overview of the conventional PC based vision system used for welding applications is presented. The software implementation detail of the specific image processing algorithm called 'feature correlation' is presented.

Chapter Three gives a general introduction to the SOPC technology in terms of its development history, architecture and design flow. Concerns are given specifically for applying SOPC technology in constructing an image processing system. Following that, a brief overview of commonly used processors in SOPC design is given. Finally this chapter gives the background information of the system architecture, bus protocol and development tools that SIPS used.

Chapter Four starts to describe SIPS from the hardware side. All hardware components including the custom fabricated units are introduced, and the reasons for their choices are also presented.

Chapter Five continues to describe SIPS but mainly focus on explaining the SOPC design. All video IP architectures are described in detail; some typical design issues regarding the implementation details are also discussed.

Chapter Six explains a novel solution to a multi-mastering problem. A classic approach is given before explaining the solution used in SIPS. Finally an alternative method is also introduced.

Chapter Seven describes how the whole system is generated, synthesised and implemented on the actual hardware. Generation and synthesis results are given as well as discussions.

Chapter Eight describes system test details and discusses the results. The system tests include system level simulation and hardware verification. This chapter also presents the software implementation details. Several image processing algorithms are given as examples and a performance analysis is presented for each of them to help better understanding the performance of SIPS.

Chapter Nine presents a conclusion to this system and indicates the potential areas for future work.

Fan Wu

# Chapter 2. Introduction to Image Processing, Computer Vision & Overview of an PC Based Vision System for Welding

This chapter consists of two sections. The first section explains some fundamental disciplines involved in developing the SIPS. The second section presents a PC based vision system for a welding application. The feature correlation algorithm applied in processing the weld images is described.

#### 2.1 Computer vision & image processing

Vision allows humans to perceive and understand the world surrounding them. With the development of modern electronics, the effect of human vision can be imitated by electronically perceiving images and understanding their contents with modern computers and this, as a science, is called computer vision. It is concerned with extracting information about a scene by analysing images of that scene [17]. This scene could be two-dimensional or three-dimensional (3D) depending on the practical applications. As a technological discipline, computer vision seeks to apply the theories and models of computer vision to the construction of computer vision systems. Examples of applications of computer vision systems include systems for controlling processes (e.g. an industrial robot or an autonomous vehicle), detecting events (e.g. for visual surveillance), organising information (e.g. for indexing databases of images and image sequences), modeling objects or environments (e.g. industrial inspection, medical image analysis or topographical modeling) and interaction (e.g. as the input to a device for computer-human interaction) etc.

Computer vision is now recognised as an interdisciplinary research field that is chiefly dependant on image processing but also spans processor design, graphical and communication techniques, control, information handling and computer aided design processes. The typical tasks of computer vision systems are recognition, motion detection, scene reconstruction and image restoration etc. It is very often the case that the general goal of a computer vision system is to recognise objects of various types that may be presented in the scene.

Machine vision (MV) is the application of computer vision to industry and

manufacturing. Whereas computer vision is mainly focused on machine-based image processing, machine vision often requires digital input/output devices and computer networks to control other manufacturing equipment such as robotic arms. Machine vision is a subfield of engineering that encompasses computer science, optics, mechanical engineering, and industrial automation.

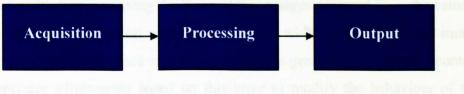

Image processing is the collation of spatially arranged intensity data, forming an image, which is processed to extract information about the scene [18]. The input of image processing is an image such as a frame of video, while the output could be an image or a set of features of the image. Image processing is rather independent of an application domain. However, it plays an essential role in computer vision systems such as a vision based robot control system because a robust image processing algorithm is required. Because of this, a real-time image processing system is often required to be set up to verify specific image processing algorithms and estimate its performance in a real-time manner before being applied into a complete (computer) vision system to perform particular vision task. The real time goal is to process all the required data in a given time interval before the next image is ready for processing. To estimate the performance of a real-time image processing system it is required to analyse how much data it can handle in real time. Such a system generally provides three main functions which are video acquisition, processing and output (see Figure 2-1), and the video data transfer in this system is one way. The video data can be acquired by an analogue/digital camera or a video recording device. As described in Chapter 1, the image processing can be performed by using general processors such as CPU, general purpose microprocessor, DSP processor, synthesised processor running on a FPGA, or processing elements built into FPGAs or ASICs. The video output generally refers to video display on monitors which gives a visual indication of the image processing results. Furthermore, a data storage function is normally required to buffer the data output from each level before being sent to the next due to the existence of speed differences between each function module.

6

The next section gives an example of how image processing is integrated into a visionbased system for automated welding.

#### 2.2 Vision-based closed loop process control system for welding

The vision-based closed loop process control system was designed to improve the weld quality. In this system, image analysis and processing are applied to the images captured by the camera for supplying real-time measurements on the weld, in order to provide additional information to the process operator [3]. The description of this system, in the next several sections, focuses on the image acquisition and processing parts as the author has been involved in developing the image processing software, and more importantly its application to the research described in this thesis. More details regarding the post processing and how the whole system functions can be obtained in [3].

#### 2.2.1 General description

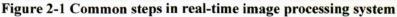

Figure 2-2 illustrates a simplified diagram of the closed loop weld process control system.

The real-time molten pool width is one of the measurements extracted by this vision based system. As seen from the figure, this system aims to extract the real-time measured pool width from analysing the live welding images captured from the camera and compares the measured result with the target pool width supplied into the image processing software. If a difference exists then an error is generated, the process control algorithm generates adjustments based on this error to modify the behaviour of the welding process such as changing the current via the welding hardware interface. This process is then repeated when the next measurement is available from the imageprocessing software thereby controlling or regulating the welding characteristics.

In this vision-based system, the image processing has been specified for welding applications and integrated with the welding control software. Apart from the process control, one of the key features of this system is to process the weld images captured from the camera in real time. This process is undertaken by running image processing software programs in a standard PC.

#### 2.2.2 Image capture and processing

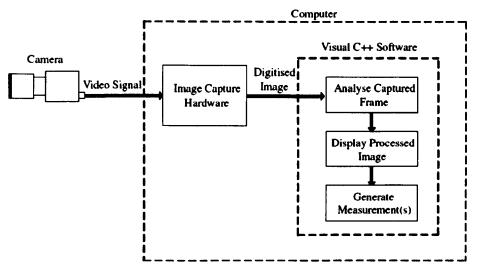

The basic layout of the weld image capture and analysis system is shown in Figure 2-3.

Figure 2-3 Real time image capture and analysis (From [3])

The analogue composite video signal is captured from two commercial CCD cameras and then fed into a Pentium class PC running Microsoft Windows 2000 for analysing and processing the weld images via the image capture hardware interfaces. These interfaces include a Picolo [19] capture board for the front view image processing program (FVIPP) [20] and a 'WinTV' [21] card for the side view image processing program (SVIPP). The FVIPP and SVIPP were written in Microsoft Visual C++. They supply separate measurements and are used together to provide a comprehensive analysis on the weld images from different views. The FVIPP used the Picolo device driver to access the digitised images or video from the Picolo board while the SVIPP used the standard 'Video for Windows' (VFW) interface [22]. In order to provide a visual indication of the operation of the image processing software, the modified video with the key features highlighted are displayed on a standard PC monitor along with the relevant measured results. Following this, the final phase of the image analysis process is to provide the relevant image measurements to the welding control system software VEE, which has been designed to run concurrently with the image processing programs in the same computer. They run as different threads and communicate with each other through pipes [23]. Such a measurement will allow a controller, as and when required, to modify the welding process parameters in order to regulate or maintain a desired set of weld characteristics.

The image processing system is capable of working in real-time at the frame rate of the video capture device, provided that the associated processing algorithm can be executed during the time between the capture of successive pictures or 'frames'. This time is typically 40ms for the standard 25Hz interlaced CCD camera system that has been used.

A Control Area Network (CAN) [24] interface has been developed and integrated into the VEE software. This allows alteration of the welding process parameters at speeds of up to 25Hz via a distributed network of embedded controllers.

#### 2.2.3 Weld image-processing software development

The general requirement of the image processing algorithm is to identify target edges such as the left and right edges of the molten weld pool or the weld wire, so that a corresponding width measurement can be achieved and made use in real-time with the feedback control system. A feature correlation algorithm was developed to implement these edge detections.

#### 2.2.3.1. Feature correlation design

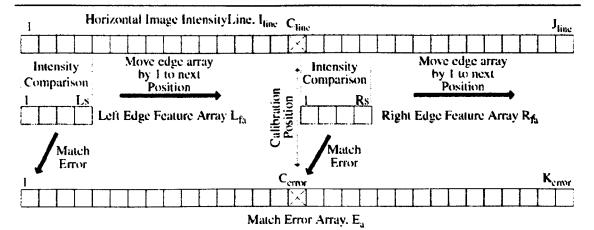

The basic idea of this algorithm is firstly to extract some sample image features such as the weld pool edge features ( $L_{fa}$  and  $R_{fa}$  in Figure 2-4) in the calibration stage.

An SOPC Based Image Processing System Chapter 2 Introduction to Image Processing, Computer Vision & Overview of an PC Based Vision System for Welding

Figure 2-4 Image edge feature correlation (From [3])

Then copy a horizontal ( $I_{line}$ ) or vertical line at the specified calibration position from a live captured frame, use these typical edge feature intensities to compare with specific positions at that line along the array of weld image pixel intensities, and then use the comparison results to generate a match error array ( $E_a$ ). The equation of calculating the match error array for the left edge feature is given in Equation 2-1.

$$E_{a}[i] = \sum_{x=1}^{L_{s}} \left| L_{fa}[x] - I_{line}[x + (i-1)] \right| \text{ for } 1 \le i \le (C_{line} - L_{s}) \quad (\text{Equation 2-1})$$

Where  $E_{\sigma}$  is the error array at position or index *i*,  $C_{line}$  is the captured line calibration position and  $L_{\sigma}$  is the left feature array size. The right feature error array can be calculated by a similar manner.

Once the error array is calculated, by searching where the minimum error is in the error array the position of highest association with the edge features can be obtained as shown in Equation 2-2.

$$L_{match\_min} \longleftarrow \min \left\{ E_a[i] | 1 \le i \le (C_{error} - L_s) \right\}$$

(Equation 2-2)

Where *Lmatch\_min* is the minimum left feature correlation error.

The position of the minimum left feature match error  $i_{min_l}$  is then recorded as shown in Equation 2-3.

$$L_{match \min} = E_a[i_{\min}]$$

(Equation 2-3)

The location of the best match for the centre of the left edge feature match Lmatch\_centre is given in Equation 2-4

$$L_{match\_centre} = E_a [i_{min\_l} + (\frac{L_s}{2})]$$

(Equation 2-4)

Fan Wu

Following the same method the best match for the centre of the right edge feature  $R_{match, centre}$  can be located by using Equation 2-5.

$$R_{match\_centre} = E_a[i_{min\_r} + (\frac{R_s}{2})]$$

(Equation 2-5)

Finally the weld pool width  $PW_{pix}$  in pixels can be achieved by using Equation 2-6.

$$PW_{pix} = i_{\min_{r}} - i_{\min_{l}}$$

(Equation 2-6)

This value will then be translated into a measurement in mm for use with the weld software by taking into account the resolution of the image capture system and the field of view of the weld imaging optics.

This algorithm was originally developed by C. Balfour, J. S. Smith and S. Amin-Nejad. The calculations listed above are taken from [3]. By applying this algorithm into different welding situations, a sequence of measurements and the welding status can be obtained. The next two sections describe the two programs with the feature correlation algorithm applied to achieve the measurements. An SOPC Based Image Processing System Chapter 2 Introduction to Image Processing, Computer Vision & Overview of an PC Based Vision System for Welding

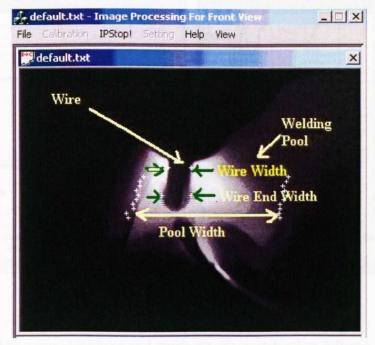

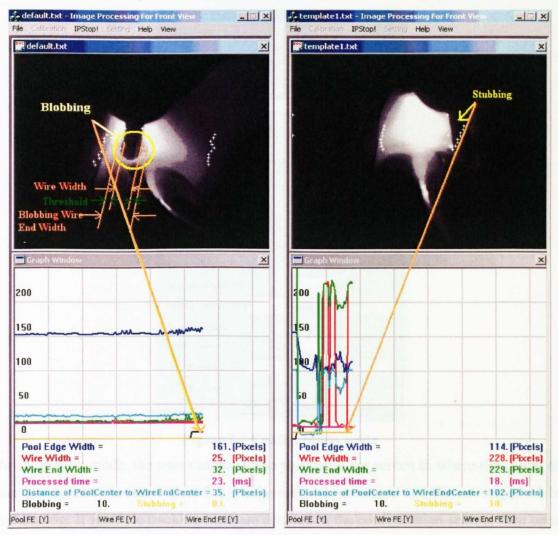

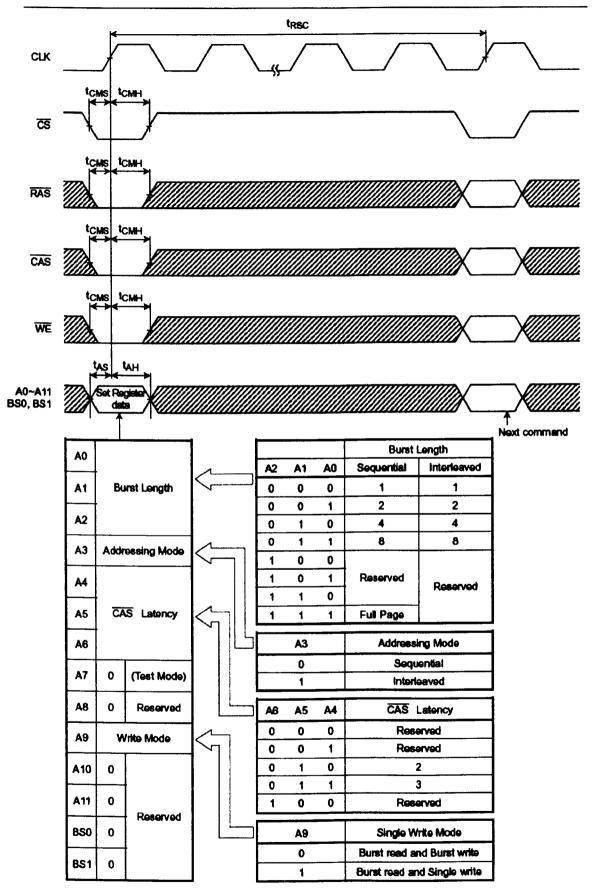

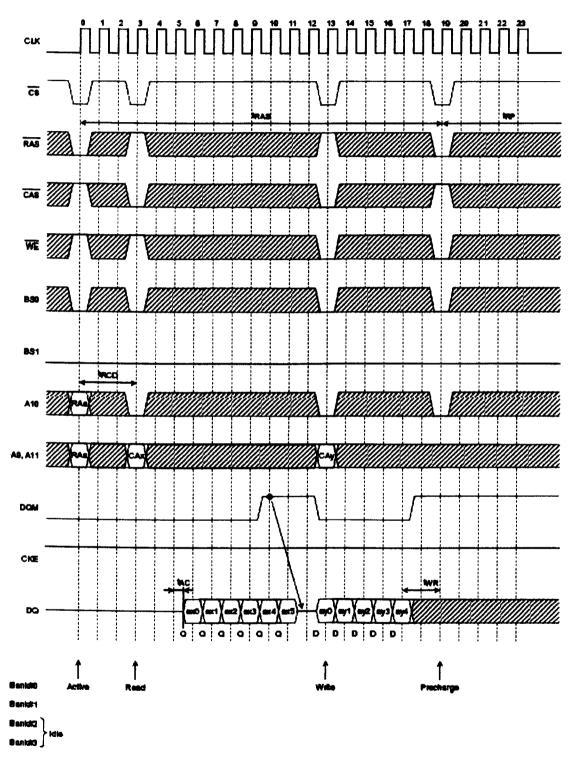

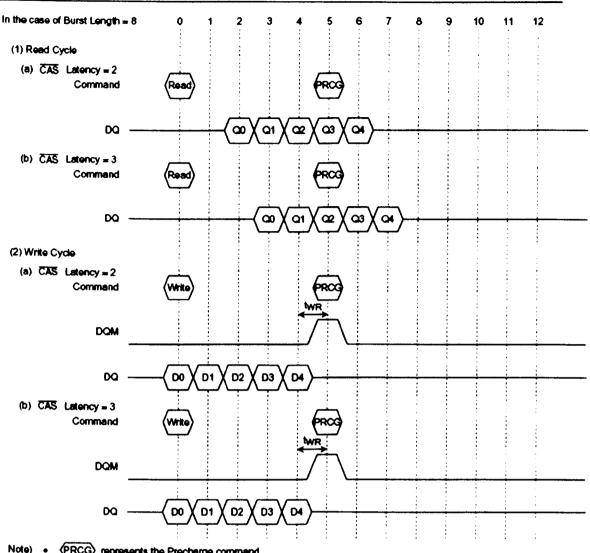

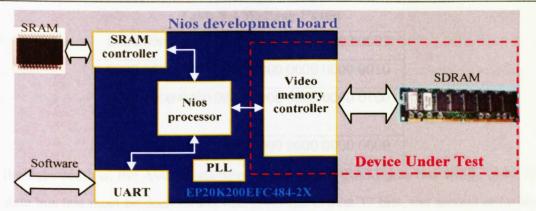

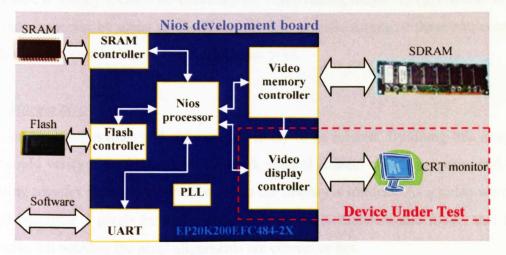

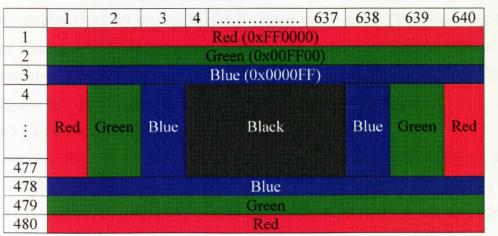

#### 2.2.3.2. Front view image processing program (FVIPP)