# **Utah State University**

# DigitalCommons@USU

All Graduate Theses and Dissertations, Spring 1920 to Summer 2023

**Graduate Studies**

8-2023

# Reclaiming Fault Resilience and Energy Efficiency With Enhanced Performance in Low Power Architectures

Noel Daniel Gundi Utah State University

Follow this and additional works at: https://digitalcommons.usu.edu/etd

Part of the Electrical and Computer Engineering Commons

### **Recommended Citation**

Gundi, Noel Daniel, "Reclaiming Fault Resilience and Energy Efficiency With Enhanced Performance in Low Power Architectures" (2023). All Graduate Theses and Dissertations, Spring 1920 to Summer 2023. 8894. https://digitalcommons.usu.edu/etd/8894

This Dissertation is brought to you for free and open access by the Graduate Studies at DigitalCommons@USU. It has been accepted for inclusion in All Graduate Theses and Dissertations, Spring 1920 to Summer 2023 by an authorized administrator of DigitalCommons@USU. For more information, please contact digitalcommons@usu.edu.

# RECLAIMING FAULT RESILIENCE AND ENERGY EFFICIENCY WITH ENHANCED PERFORMANCE IN LOW POWER ARCHITECTURES

by

# Noel Daniel Gundi

A dissertation submitted in partial fulfillment of the requirements for the degree

of

# DOCTOR OF PHILOSOPHY

in

**Electrical Engineering**

| Approved:                                 |                                                           |

|-------------------------------------------|-----------------------------------------------------------|

| Sanghamitra Roy, Ph.D.<br>Major Professor | Koushik Chakraborty, Ph.D.<br>Committee Member            |

| Greg Droge, Ph.D.<br>Committee Member     | Zhen Zhang, Ph.D. Committee Member                        |

| Vicki H Allan, Ph.D.<br>Committee Member  | D. Richard Cutler, Ph.D. Vice Provost of Graduate Studies |

UTAH STATE UNIVERSITY Logan, Utah Copyright © Noel Daniel Gundi 2023 All Rights Reserved

iii

#### ABSTRACT

Reclaiming Fault Resilience and Energy Efficiency with Enhanced Performance in Low Power Architectures

by

Noel Daniel Gundi, Doctor of Philosophy Utah State University, 2023

Major Professor: Sanghamitra Roy, Ph.D.

Department: Electrical and Computer Engineering

Shrinking technology node and the massive increase in data workloads has witnessed a swift migration of the system towards the Low-Power Computing (LPC) paradigm. Additionally, to accelerate the redundant yet mammoth AI instructions, novel ASIC design architectures have been explored. Google's Tensor Processing Unit (TPU) is one such architectural innovation deployed in the commercial space to speedup the processing of AI workloads.

In an effort to achieve a superior energy efficiency, Near-Threshold Computing (NTC) has been marginalized to be an efficient LPC paradigm. Due to an underscaling of voltage, NTC offers quadratic savings is power consumption in comparison to operating the system at its nominal counterpart i.e., Super-Threshold Computing (STC). However, NTC exhibits an extreme sensitivity to Process Variation (PV). Moreover, the reduced speed of transistors at NTC exacerbates the overall performance of the system. Hence, the integration of NTC into the conventional semiconductor workspace has been restricted. In this work, distinct methodologies are explored to provide improved performance at NTC. Furthermore, effects of PV, which are unnoticed at STC but posing a severe threat to the reliability of the low-power AI computing is addressed. This dissertation exploits the disparate computational delays of arithmetic units to provide up to  $2.5\times$  improved performance and  $1.35\times$  better energy efficiency at NTC. Additionally, the distinct dataflow patterns of the TPU are statistically analyzed to employ selective voltage levels and further enhance the performance of the TPU. Also, the homogeneous architecture of the TPU systolic array is thoroughly investigated to design a low-overhead faulty Processing Element (PE) detection scheme. The locality of the faulty PE is later utilized to tackle the impending faults.

(105 pages)

### PUBLIC ABSTRACT

Reclaiming Fault Resilience and Energy Efficiency with Enhanced Performance in Low

Power Architectures

Noel Daniel Gundi

Rapid developments of the AI domain has revolutionized the computing industry by the introduction of state-of-art AI architectures. This growth is also accompanied by a massive increase in the power consumption. Near-Theshold Computing (NTC) has emerged as a viable solution by offering significant savings in power consumption paving the way for an energy efficient design paradigm. However, these benefits are accompanied by a deterioration in performance due to the severe process variation and slower transistor switching at Near-Threshold operation. These problems severely restrict the usage of Near-Threshold operation in commercial applications. In this work, a novel AI architecture, Tensor Processing Unit, operating at NTC is thoroughly investigated to tackle the issues hindering system performance. Research problems are demonstrated in a scientific manner and unique opportunities are explored to propose novel design methodologies.

| vi |  |

|----|--|

|    |  |

To the Almighty God, Mummy, Daddy, friends and all my loved ones whom I have lost in the past years.

#### **ACKNOWLEDGMENTS**

First and foremost, I want to thank GOD — The LORD Almighty, for giving me a wonderful life and caring for me all the while.

I would like to offer my sincere heartfelt gratitude to everyone who have helped and guided me in this Ph.D. journey. I would like to thank my major advisor Dr. Sanghamitra Roy and co-advisor Dr. Koushik Chakraborty for giving me the opportunity to join the USU Bridge Lab. I thank them for consistently encouraging and guiding me with their valuable insight, constant encouragement, and helping me to give my full effort and strive towards a meaningful research. Additionally, thank you to my advisors for all their constructive criticism and enabling me to envision the future possibilities in a research. Also, I want express my gratitude to them for always hosting me with hospitality and ensuring I am not alone in Logan. I want thank my Ph.D. committee members Dr. Greg Droge, Dr. Zhen Zhang and Dr. Vicki Allan for all their valuable feedback on my research and motivating presence. I would like to thank Tricia Brandenburg, Diane Buist and Kathy Phippen for assisting me with all documentation work and always willing to address my doubts. I also appreciate and thank Brady for always helping me out with the lab and computer work. A special thank you to the ECE Department for all the support.

I am very thankful and extremely delighted to work with all the members of the BRIDGE lab. I want to thank Tahmoures for all the intellectual insight bestowed on me during the initial days. Pramesh and Prabal, for being wonderful research partners, correcting and encouraging me every time. Sourav, for instilling in me the confidence when I was down. Chidham, for the calm and intellectual demeanor. Aatreyi, for being the strict class teacher/sister. Rajesh for introducing me to the world of schematic drawing. I also want to thank all my labmates with whom all I have associated with, Heidi, Mitchell, Jyotirmoy, Bishal, Zinnia, Andrew C., Bijoy, Andrew G., Mason and Tim for making my journey memorable.

Thanks to all my colleagues at Tata Elxsi, Nagesh, Aditya, Raghu, Prakash, Ganesh, Abhijit, Teena and Rohit. Thanks again to Rohit, Hitesh, YK, Nevin, Mamta and Anshuman from AMD for guiding me during my internship. Special thanks to Dr. Acken, Dr. Johnson, Dr. Samarakoon and Dr. Stine from my days at Oklahoma State University.

I want to thank all my friends Surya, Spandan, Pradeep, Rohit, Rakshit, Theja, Libin, Naveen, Santosh J., Avinash, Robin, Swithin, Praveen, Prashant, Pavan, Makutum, Shiva, Utpal, Santosh M., Varun, Ricky, Vivian, Eldho, Ryan, Chris, Isaac, Krishnaprasad, Anirudh, Rupesh, Dilip, Rajashekar, Sujit and Steve for being there for me. Additionally, thanks to all the friends I gained during my Ph.D. journey, Avik, Vedang, Jatin, Akshat, Ashu, Vaibhav, Supratik, Saju, Raushan, Rejoy, Supriyo and Colby. Special thanks to my little friend Deep for being a great geography partner. Big thanks to my church family, Matthew, Joseph, Derek, Jonathan S., Thomas, Jonathan B., Pastor Dane, Jason, Drew, Dan, Jordan, Benny, Jim and Ann, Ibukun, Bolaji, Olusola, Yessica, Alban, Preeti, Susan, entire EU, GCCF, ACF, The Shofar Call and Navigators. Special thanks to Dr. McGee, Dr. Bond, Hy, Don, Joel and the Oklahoma City bible study group for always remembering me in prayers. Thanks to brothers Varghese, Oberon, uncles Anthony, Ernst, Prakash, Naveen, Joaquim, Robert, K.G. Samuel, aunty Lalitha, Gay, sister Autumn and their respective families. Thanks again to Pastor Zac. Thank you again to sister Lakshmi and brother Peter for always hosting me. Thank you to brothers Prem, Shekhar, Daniel K., sister Ranjini and Pastors Saji, Stephen, Molly and Joy.

I thank my parents Kamala and Madhukar for their love and unconditional support. Thank you to my brothers and sisters, Jenet, Chandrakala, Pradeep, Steven, Sabina, Mamta, Solomon, Vishal, Simon, Archana, Shirlin, Sherlock, Praveen, Ullas, Anet, Alvita and Adrian. Thanks again to my uncles and aunts Sulochana, Pamela, Sara, Vanita, Vijaykumar H., Janet, David, Lata and Shaila. Remembering all my loved ones, grandparents Simon, Rosa, John, Emily, aunts Hilda, Margaret, Sundra and Advin, uncles Sadashiv, Suresh, Vijaykumar and Stanley, sister Seema and brothers Daniel, Naveen and Sam.

Thank you everyone for making my journey memorable.

Noel Daniel Gundi

# **CONTENTS**

|         |              |                    | P                                                                                                         | age              |

|---------|--------------|--------------------|-----------------------------------------------------------------------------------------------------------|------------------|

| A       | BSTRA        | ACT                |                                                                                                           | iii              |

| PU      | JBLIC        | ABSTI              | RACT                                                                                                      | V                |

| A       | CKNC         | OWLED              | GMENTS                                                                                                    | vii              |

| LI      | ST OF        | TABLI              | ES                                                                                                        | xiii             |

|         |              |                    | RES                                                                                                       |                  |

|         |              |                    |                                                                                                           |                  |

| A       | CRON         | IYMS.              |                                                                                                           | xvii             |

| 1       | INTI<br>1.1  |                    | butions of This Dissertation                                                                              | 1<br>2<br>2<br>3 |

| 2       | LITE 2.1 2.2 | Explor 2.1.1 2.1.2 | RE REVIEW                                                                                                 | 4<br>4<br>4<br>5 |

|         | 2.2          |                    | ure and memory                                                                                            | 6                |

|         | 2.3          | Impro              | ving the reliability at LPC for extreme PV                                                                | 10               |

| 3<br>PF |              |                    | NG THE ENERGY EFFICIENCY OF A NEAR-THRESHOLD TENSOR<br>UNIT WITH TIMING ERROR RESILIENCE AND CLOCK GATING |                  |

|         | 3.1          |                    | ound and Contributions of This Work                                                                       | 14               |

|         | 3.2          |                    | ation                                                                                                     | 16               |

|         |              | 3.2.1              | Background                                                                                                | 17               |

|         |              | 3.2.2              | Methodology                                                                                               | 18<br>18         |

|         | 3.3          | 3.2.3              | Results and Significance                                                                                  | 20               |

|         | 0.0          | 3.3.1              | Design Overview                                                                                           | 20               |

|         |              | 3.3.2              | Costless Correction (CostCo)                                                                              | 21               |

|         |              | 3.3.3              | Systolic Clock Gating                                                                                     | 22               |

|         |              | 3.3.4              | EFFORT Variants                                                                                           | 26               |

|         |              | 3.3.5              | Design Summary                                                                                            | 27               |

|         | 3.4          |                    | dology                                                                                                    | 28               |

|         |              | 3.4.1              | Device Layer                                                                                              | 28               |

|         |              | 3.4.2              | Circuit Layer                                                                                             | 29<br>29         |

|         |              | 3 44 3             | Architecture Laver                                                                                        | / <b>U</b>       |

|        |        |                                                         | X  |

|--------|--------|---------------------------------------------------------|----|

| 3.5    | Exper  | rimental Results                                        | 30 |

|        | 3.5.1  | Comparative Schemes                                     | 30 |

|        | 3.5.2  | Inference Accuracy                                      | 31 |

|        | 3.5.3  | Energy Efficiency                                       | 32 |

|        | 3.5.4  | Implementation Overhead                                 | 34 |

| 4 REC  | CLAIMI | ING THE PERFORMANCE OF A NEAR-THRESHOLD TENSOR PRO-     |    |

| CESSIN | IG UNI | IT WITH SELECTIVE VOLTAGE BOOSTING                      | 35 |

| 4.1    | Backg  | ground and Contributions of This Work                   | 35 |

| 4.2    | Motiv  | vation                                                  | 37 |

|        | 4.2.1  | Background and Limitations                              | 37 |

|        | 4.2.2  | Predictive Systolic Array Dataflow                      | 39 |

|        | 4.2.3  | Methodology                                             | 39 |

|        | 4.2.4  | Results and Significance                                | 40 |

| 4.3    | Desig  | n                                                       | 41 |

|        | 4.3.1  | Design Overview                                         | 41 |

|        | 4.3.2  | Modified Razor Flip Flop (MRFF)                         | 42 |

|        | 4.3.3  | Error Collection Unit (ECU)                             | 43 |

|        | 4.3.4  | Voltage Control Unit (VCU)                              | 44 |

| 4.4    |        | odology                                                 | 48 |

|        | 4.4.1  | Device Layer                                            | 48 |

|        | 4.4.2  | Circuit Layer                                           | 49 |

|        | 4.4.3  | Architecture Layer                                      | 49 |

| 4.5    |        | rimental Results                                        | 50 |

| 2.0    | 4.5.1  | Comparative Schemes                                     | 50 |

|        | 4.5.2  | Error Resilience                                        | 51 |

|        | 4.5.3  | Inference Accuracy and Voltage Boost                    | 53 |

|        | 4.5.4  | Is NTC TPU worth it?                                    | 54 |

|        | 4.5.5  | Hardware Overheads                                      | 55 |

| 5 REC  | T.AIMI | ING THE RELIABILITY OF A NEAR-THRESHOLD TENSOR PROCESS- |    |

|        |        | DELAY FAULT DETECTION AND MITIGATION                    | 56 |

| 5.1    |        | ground and Contributions of This Work                   | 56 |

| 5.2    | _      | vation                                                  | 58 |

| J      | 5.2.1  | TPU Systolic Array                                      | 59 |

|        | 5.2.2  | Impact of PV at Low-Power: LP-faults                    | 59 |

|        | 5.2.3  | Results                                                 | 61 |

|        | 5.2.4  | Significance                                            | 62 |

| 5.3    |        | Design                                                  | 62 |

| 0.0    | 5.3.1  | Challenges                                              | 63 |

|        | 5.3.2  | Design Overview                                         | 64 |

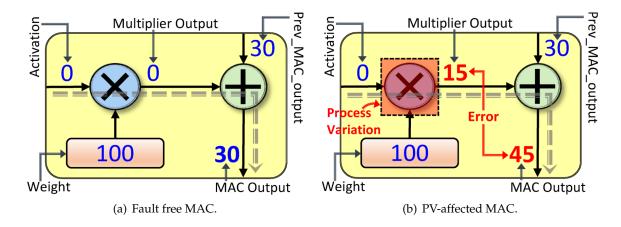

|        | 5.3.3  | Illustrative example for an LP-fault                    | 64 |

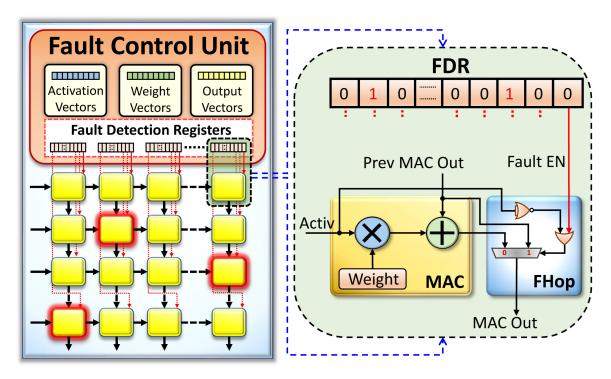

|        | 5.3.4  | Fault Hop (FHop)                                        | 65 |

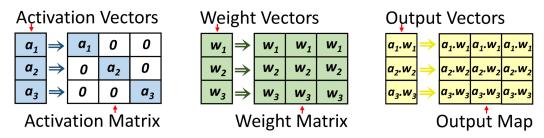

|        | 5.3.5  | Fault Control Unit (FCU)                                | 65 |

|        | 5.3.6  | Fault Hop Time-Borrow (FHop-TB)                         | 68 |

| 5.4    |        | odology                                                 | 69 |

| 5.5    |        | rimental Results                                        | 70 |

| 0.0    | - APCI |                                                         |    |

|    |             |                          | xii |

|----|-------------|--------------------------|-----|

|    | 5.5.1       | Comparative Schemes      | 71  |

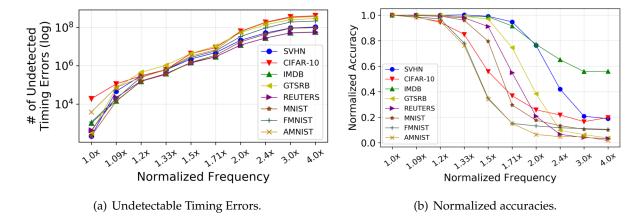

|    | 5.5.2       | Inference Accuracy       | 71  |

|    | 5.5.3       | Energy Efficiency        | 73  |

|    | 5.5.4       | Implementation Overheads | 74  |

| 6  | Conclusion  |                          | 75  |

| RI | EFERENCES . |                          | 77  |

| CI | URRICULUM   | I VITAE                  | 86  |

# LIST OF TABLES

| Table |                                                         | Page |

|-------|---------------------------------------------------------|------|

| 3.1   | List of DNN benchmarks used and the error free accuracy | 29   |

| 4.1   | List of DNN datasets                                    | 49   |

| 5.1   | List of DNN benchmarks and their error-free accuracy    | 70   |

# LIST OF FIGURES

| Figure |                                                                                                                                                                                                                                                                                                                                                                                                      | Page |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

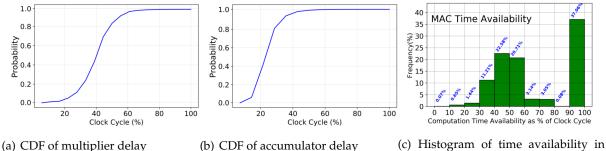

| 3.1    | CDFs of the delay distributions for multiplier (Figure 3.1(a)) and accumulator (Figure 3.1(b)) show that the multiplier has higher computational delay compared to the accumulator. Accumulator takes less than a half clock cycle for its part of computation. Figure 3.1(c) shows the time available for recomputation in downstream MACs when timing errors occur in the respective upstream MACs |      |

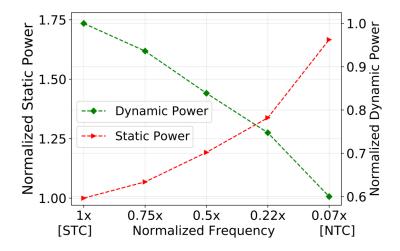

| 3.2    | Figure 3.2 portrays the increase in static power and decrease in dynamic power for decreasing frequencies. Voltages are scaled accordingly to depict the shift from STC to NTC.                                                                                                                                                                                                                      |      |

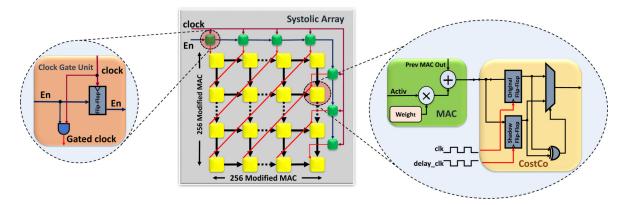

| 3.3    | CostCo implemented inside the MAC unit to detect and correct timing violations.                                                                                                                                                                                                                                                                                                                      |      |

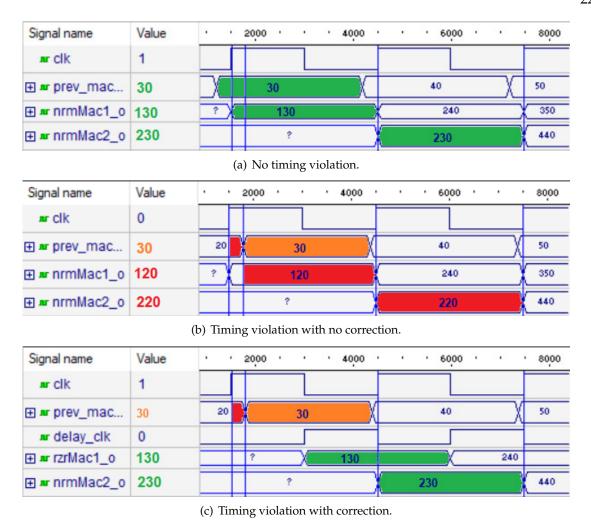

| 3.4    | CostCo can diagnose timing violation and propagate the corrected value within one clock cycle                                                                                                                                                                                                                                                                                                        |      |

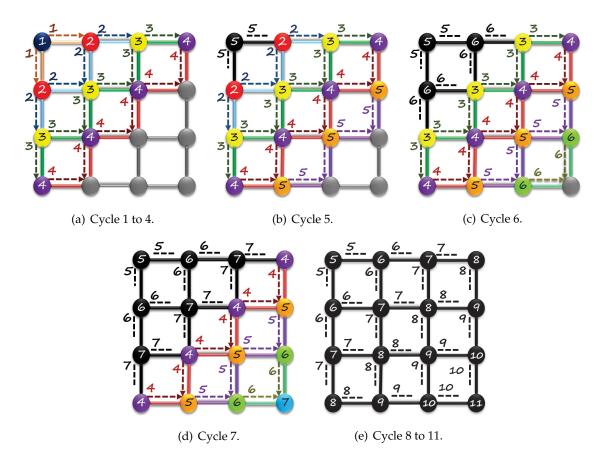

| 3.5    | Data flow pattern in a $4 \times 4$ systolic array for 11 consecutive cycles. Gray MACs are yet to receive their inputs, black MACs have completed their operations, while the rest of the MACs are presently computing their respective outputs.                                                                                                                                                    |      |

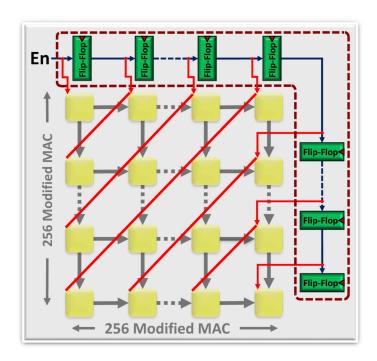

| 3.6    | Serially connected flip-flops in the Clock Gate units effectively exhibit the characteristics of Right Shift Register, thereby suitably enabling/disabling the MAC units along the diagonal of the systolic array.                                                                                                                                                                                   |      |

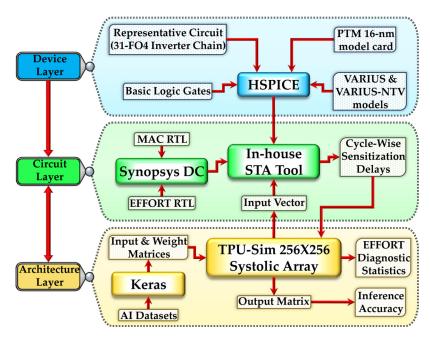

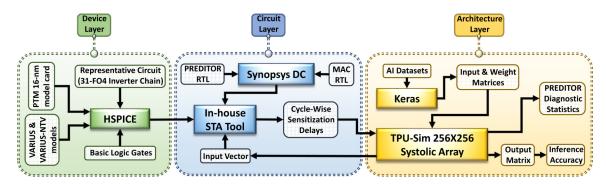

| 3.7    | Cross Layer Methodology                                                                                                                                                                                                                                                                                                                                                                              | . 28 |

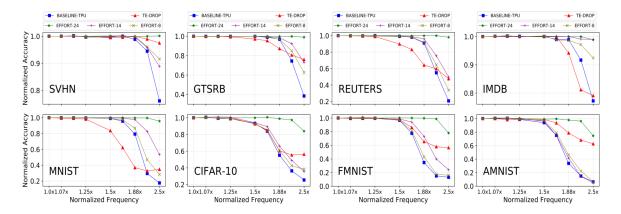

| 3.8    | Normalized inference accuracies of the 8 DNN benchmarks for different comparative schemes.                                                                                                                                                                                                                                                                                                           |      |

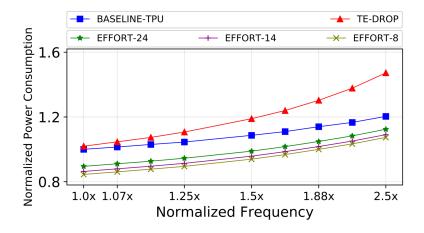

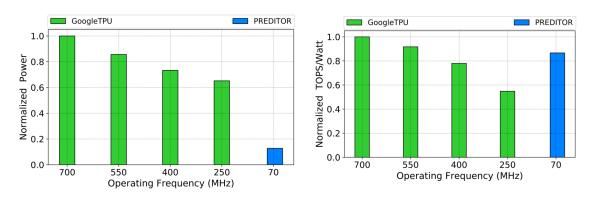

| 3.9    | Power Consumption (Lower is better)                                                                                                                                                                                                                                                                                                                                                                  | . 32 |

| 3.10   | TOPS/Watt (Higher is better)                                                                                                                                                                                                                                                                                                                                                                         | . 33 |

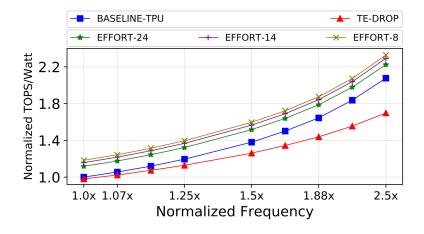

| 4.1    | Figure depicts multiple data latching scenarios as the frequency of operation increases and the timing error detection window diminishes. In Figure 4.1(a) baseline frequency is in operation. Frequency of operation is same for Figures 4.1(b) and 4.1(c) but higher than Figure 4.1(a). Highest frequency of operation is employed in Figure 4.1(d).                                              |      |

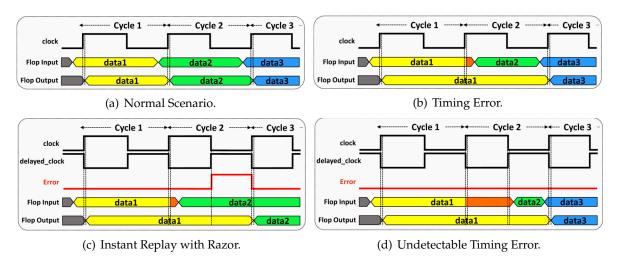

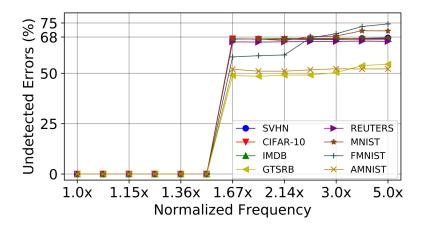

| 4.2  | Figure 4.2(a) shows the rise in undetected timing errors with an increase in the operational frequency. The effects of the increasing timing errors is depicted in Figure 4.2(b), where the classification accuracy drops drastically. This experimentation is performed on the Baseline TPU (Section 4.5.1)      | 39 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.3  | Figure 4.3 depicts the various timing error profiles during the high frequency operations of the TPU                                                                                                                                                                                                              | 40 |

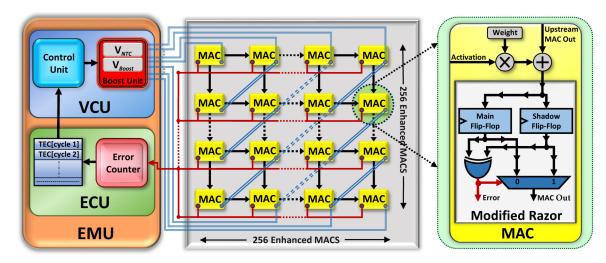

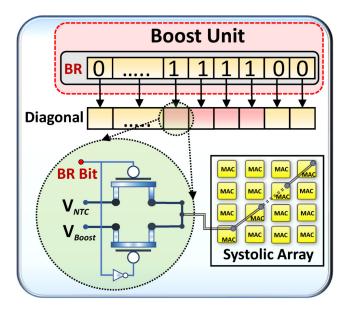

| 4.4  | Each MAC in the systolic array is enhanced with an MRFF. EMU comprises of ECU and VCU. ECU collects and stores timing error count from each cycle. VCU queries the timing error information from ECU to predict the operational clock cycles and boost the operating voltage during the predicted cycle interval. | 41 |

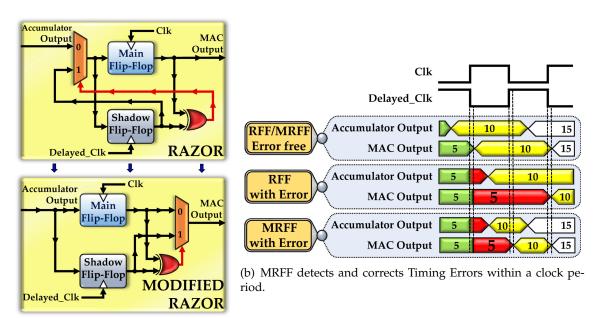

| 4.5  | Figure 4.5(a) depicts the conversion of Razor Flip Flop to Modified Razor Flip Flop by altering the multiplexer input/output connections. The timing error correction capability of MRFF is shown in Figure 4.5(b).                                                                                               | 43 |

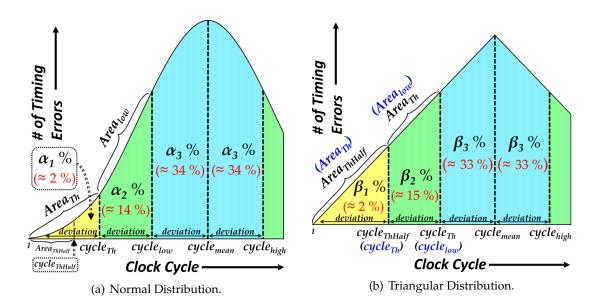

| 4.6  | Representative Timing Error Profiles                                                                                                                                                                                                                                                                              | 44 |

| 4.7  | Interaction of BU with MACs along the diagonal                                                                                                                                                                                                                                                                    | 47 |

| 4.8  | Cross Layer Methodology                                                                                                                                                                                                                                                                                           | 48 |

| 4.9  | Percentage of undetected timing errors mitigated by PREDITOR for 8 different datasets                                                                                                                                                                                                                             | 51 |

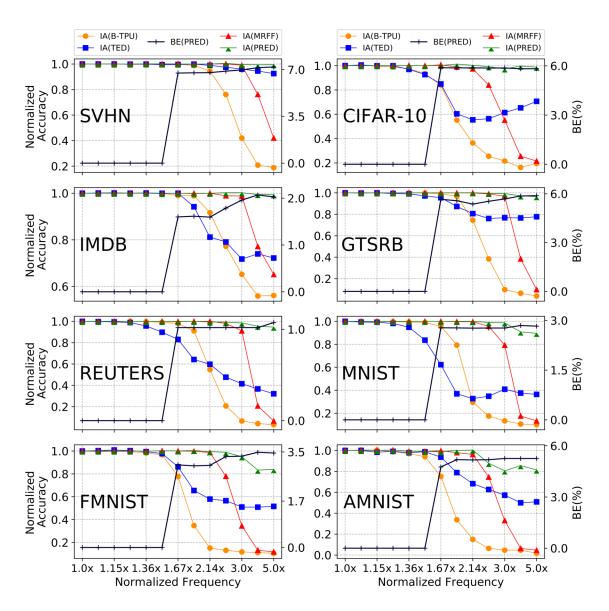

| 4.10 | Normalized Inference Accuracy (IA) of different comparative schemes and Voltage Boost Energy (BE) of Preditor for 8 DNN datasets at various normalized frequencies.                                                                                                                                               | 52 |

| 4.11 | Power and performance comparison of PREDITOR with GoogleTPU                                                                                                                                                                                                                                                       | 54 |

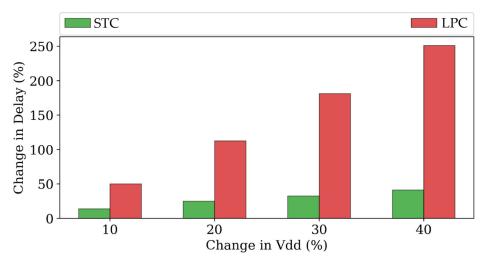

| 5.1  | Delay sensitivity for power supply at STC vs LPC. HSPICE simulations shown for a 31 fan-out-of-four (FO4) inverter chain at the 14nm multi-gate technology node [107].                                                                                                                                            | 56 |

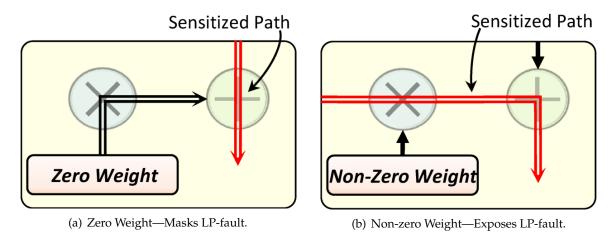

| 5.2  | Sensitized paths in a MAC unit for zero and non-zero weights, respectively.                                                                                                                                                                                                                                       | 60 |

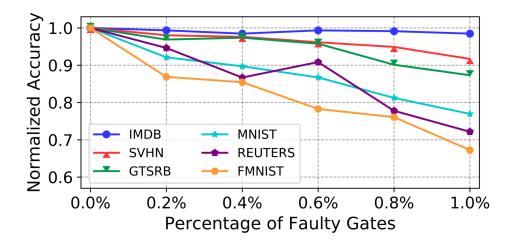

| 5.3  | Increasing number of faulty gates increases the magnitude of LP-faults, thereby deteriorating the inference accuracy.                                                                                                                                                                                             | 61 |

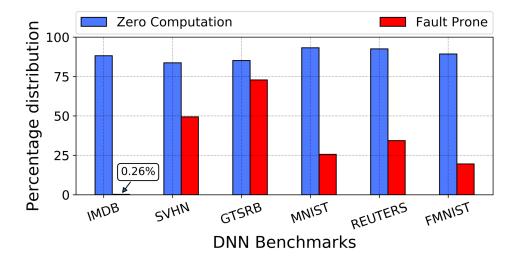

| 5.4  | Zero computations and Fault Prone zero computations elaborated as a percentage of total computations for 6 different DNN benchmarks                                                                                                                                                                               | 62 |

| 5.5  | Design block and dataflow of STRIVE                                                                                                                                                                                                                                                                               | 63 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | xvi |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.6  | Working of a PV-free and PV-affected MAC                                                                                                                                                                                                                                                                                                                                                                                                                                              | 64  |

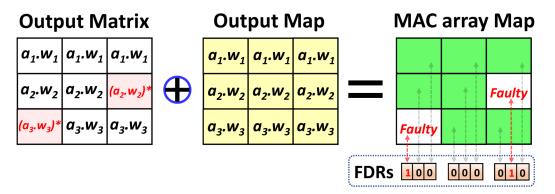

| 5.7  | Development of input matrices and output map—correct outputs—by FCU.                                                                                                                                                                                                                                                                                                                                                                                                                  | 66  |

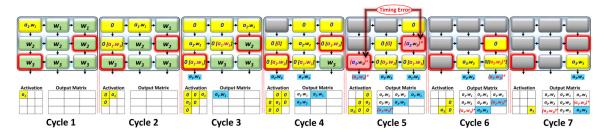

| 5.8  | Green MACs are yet to receive the activation, yellow MACs are in operation and faulty MACs are highlighted with a dark red outline. Red MACs denote the occurrence of a timing error. Grey MACs have completed their execution. Only the final operation from each MAC is shown on the yellow MACs for space constraints. $"0[a_n.w_n]"$ operation on a yellow MAC indicates that the activation input is $"0"$ and accumulator input $"a_n.w_n"$ will be forwarded to the next stage | 66  |

| 5.9  | Comparing the entries of the Output Matrix and the Output Map yields the locality of the Faulty MACs                                                                                                                                                                                                                                                                                                                                                                                  | 68  |

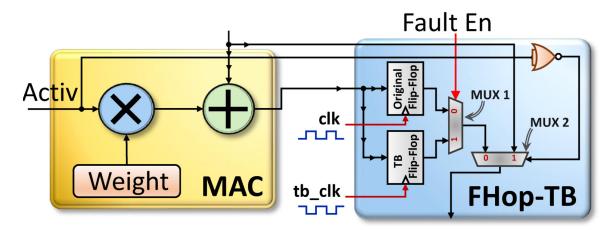

| 5.10 | Detection and correction of timing errors by FHop-TB, using the Time-Borrow technique.                                                                                                                                                                                                                                                                                                                                                                                                | 69  |

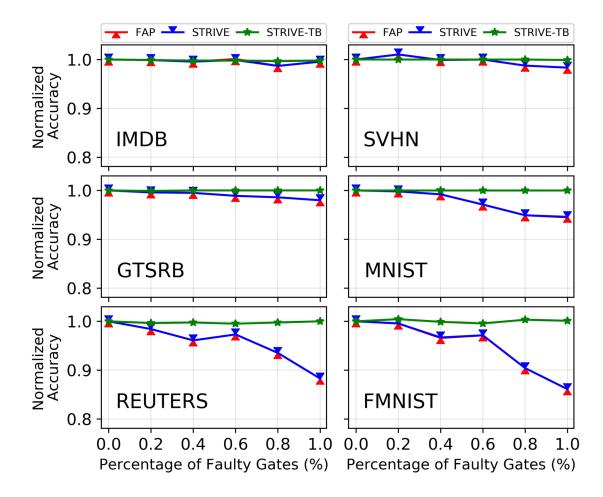

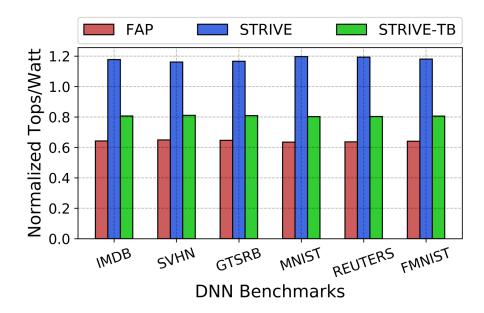

| 5.11 | Normalized Inference accuracies of FAP, STRIVE and STRIVE-TB across 6 DNN benchmarks for different percentages of faulty gates ( <b>under low-power</b> ) affected in a TPU systolic array. The Y-axis values are normalized to the corresponding error-free accuracy at the baseline LPC TPU operation                                                                                                                                                                               | 72  |

| 5.12 | Energy Efficiency comparison of FAP, STRIVE and STRIVE-TB (higher is better).                                                                                                                                                                                                                                                                                                                                                                                                         | 73  |

xvii

### **ACRONYMS**

VLSI Very Large Scale Integration

LPC Low-Power Computing

TPU Tensor Processing Unit

CPU Control Processing Unit

GPU Graphics Processing Unit

AI Artificial Intelligence

ASIC Application Specific Integrated Circuit

DNN Deep Neural Network

PE Processing Element

NTC Near-Threshold Computing

NTV Near-Threshold Voltage

STC Super-Threshold Computing

FPGA Field Programmable Gate Array

RTL Register Transfer Level

PV Process Variation

MAC Multiplier-and-Accumulate

CDF Cumulative Distribution Function

CostCo Costless Correction

MUX Multiplexer

EXOR Exclusive-OR

SIPO Serial Input Parallel Output

SPICE Simulation Program with Integrated Circuit Emphasis

FinFET Fin Field-Effect Transistor

MSB Most Significant Bit

LSB Least Significant Bit

STA Static Timing Analysis

TOPS Tera Operations Per Second

DVS Dynamic Voltage Scaling

DVFS Dynamic Voltage and Frequency Scaling

TB Time-Borrow

EMU Error Management Unit

ECU Error Collection Unit

VCU Voltage Control Unit

MRFF Modified Razor Flip Flop

RFF Razor Flip Flop

TEC Total Error Count

CU Control Unit

BU Boost Unit

CF Curve Factor

BR Boost Register

PTM Predictive Technology Model

BE Boost Energy

FO4 Fan-Out-of-Four

LP-fault Low-Power Fault

FCU Fault Control Unit

FHop Fault Hop

FHop-TB Fault Hop Time-Borrow

FDR Fault Detection Register

SRAM Static Random Access Memory

DRAM Dynamic Random Access Memory

#### CHAPTER 1

#### INTRODUCTION

Deployment of Artificial Intelligence (AI) into various spheres of the daily life and the massive developments in the domain-specific architectures has witnessed a remarkable growth in the usage of Deep Neural Networks (DNNs) in the computing ecosystem. Additionally, the utilization of AI models has seen a significant rise in multiple domains ranging from infotainment, academia and biomedical applications. However, the proliferation of AI workloads has also been accompanied by a larger carbon footprint [1]. Furthermore, the advent of Edge Computing has further pushed the energy efficiency limits by narrowing the thermal budget. Hence, the adoption of Low-Power Computing (LPC) into the computing paradigm has been inevitable.

For semiconductor devices, dynamic power in the is linearly dependent on the signal switching and frequency, and quadratically dependent on the operating supply voltage. Additionally, static power is dependent on the leakage current. Therefore, lowering of voltage closer the device's threshold region can aid in lowering power consumption. Hence, to facilitate LPC, Near-Threshold Computing (NTC) can be a singled out as viable solution to cater the system power restrictions. In NTC, the device is operated at a voltage slightly above the device threshold voltage. While NTC offers quadratic benefits in energy efficiency, it is accompanied by noticeable degradation in performance. Computational delays of electronic circuits are inversely proportional to the operating voltage. Hence, a lower operating voltage significantly increases the switching delays due to which the clock frequency is appropriately scaled to meet the timing requirements of computation. Furthermore, NTC is extremely sensitive to Process Variation (PV) due to which faults which completely concealed during nominal operation become massive bottlenecks at NTC. To overcome these performance and reliability concerns, enhancements in the circuit-architectural level are of utmost importance. Moreover, these innovations will aid

in the migration of LPC into the computing paradigm.

In this dissertation, two bodies of work propose enhancements in timing error resilience and energy efficiency by uncovering distinct component delay profiles and workflow. Chapter 3 provides an in-depth investigation on the unequal delay characteristics of the arithmetic units, the unique systolic dataflow pattern and provides orders of improvements in performance. Chapter 4 further exploits the unique dataflow and uses a mathematical approach to tackle the errors at higher frequency points. The third body of work presented in Chapter 5, addresses the hidden threat due to PV which manifests itself at NTC and demonstrates a innovative solution to marginalize the fault locally and tackle it using minor additions in the processing unit.

Additionally, Chapter 2 provides the literature survey of the various research efforts relevant to this dissertation. Chapter 6 summarizes all the works demonstrated through Chapter 3 to Chapter 5 and concludes this dissertation. Section 1.1 presents all the conference and journal publications stemming from this dissertation and serve as formal contributions to the academic field.

# 1.1 Contributions of This Dissertation

The works presented in this dissertation have been published in several conference proceedings and journal articles, including 2020 IEEE Asia and South Pacific Design Automation Conference (ASPDAC), 2023 IEEE Design Automation Conference (DAC), 2020 and 2022 Journal of Low Power Electronics and Applications (JLPEA) and 2021 IEEE Transactions on Very Large Scale Integration (TVLSI).

# 1.1.1 Conference Papers

STRIVE: Enabling Choke Point Detection and Timing Error Resilience in a Low-Power Tensor Processing Unit, Noel Daniel Gundi, Zinnia Muntaha Mowri, Andrew Chamberlin, Sanghamitra Roy and Koushik Chakraborty, Accepted for publication in IEEE/ACM Design Automation Conference (DAC), 2023.

EFFORT: Enhancing energy efficiency and error resilience of a near-threshold tensor processing unit, Noel Daniel Gundi, Tahmoures Shabanian, Prabal Basu, Pramesh Pandey, Sanghamitra Roy, Koushik Chakraborty and Zhen Zhang, IEEE Asia and South Pacific Design Automation Conference (ASPDAC), 2020.

# 1.1.2 Journal Articles

- Implementing a Timing Error-Resilient and Energy-Efficient Near-Threshold Hardware Accelerator for Deep Neural Network Inference, Noel Daniel Gundi, Pramesh Pandey, Sanghamitra Roy and Koushik Chakraborty, Journal of Low Power Electronics and Applications (JLPEA), vol. 12, no. 2, p. 32, 2022.

- EFFORT: A comprehensive technique to tackle timing violations and improve energy efficiency of near-threshold tensor processing units, Noel Daniel Gundi, Tahmoures Shabanian, Prabal Basu, Pramesh Pandey, Sanghamitra Roy and Koushik Chakraborty, IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 29, no. 10, pp. 1790–1799, 2021.

- Challenges and Opportunities in Near-Threshold DNN Accelerators around Timing Errors, Pramesh Pandey, Noel Daniel Gundi, Prabal Basu, Tahmoures Shabanian, Mitchell Patrick, Koushik Chakraborty and Sanghamitra Roy, *Journal of Low Power Electronics and Applications*, 10(4), 33, 2020.

#### **CHAPTER 2**

#### LITERATURE REVIEW

This chapter presents the comprehensive literature survey on the research related to the works in this dissertation. The include the contemporary research on NTC, low-power computing, schemes to increase energy efficiency and error resilience in DNN accelerators, and works to reduce the impact of faulty elements in low-power computing. Consequently, the works listed in the chapter demonstrates the research efforts in embracing the low-power realm and the corresponding methodologies facilitating the adoption of this migration. Section 2.1 present works adopting the benefits and challenges in NTC. Section 2.2 addresses the research pertaining to enhancement techniques centered on improving the performance and energy efficiency of for AI architectures. Section 2.3 discusses the works on the impact of faults on various PEs and the improvement schemes to reduce the effect of such faults.

# 2.1 Exploring the works at NTC:

Although the benefits of utilizing NTC as a prominent LPC paradigm are massive, the vulnerabilities accompanying NTC are quite noticeable. Section 2.1.1 present the works highlighting the evident benefits provided by the NTC paradigm. Section 2.1.2 addresses the research efforts in facilitating the mitigation of the problems plaguing the NTC realm.

# 2.1.1 Opportunities at NTC

• **Dreslinski et al. [2]:** This work introduces and proposes low-voltage operation as solution to the problem of power consumption and the deployment of NTC across all computing domains. They demonstrate 10× or higher energy efficiency due to the employment of NTC. The authors also highlight a 5× increase in performance variation and an increase in memory failure rates. However, adoption of enhancements

at the circuit architecture levels and other areas can aid in overcoming the barrier of utilization of NTC for all the computing platforms. This work provides a in-depth analysis of the impact of NTC on the various device parameters.

- Markovic et al. [3]: This work develops a energy-delay modeling framework to study the various inversion regions and analyze the effect of operating voltage and transistor sizing on the overall performance of the system, while operating in a subthreshold region. The authors propose the utilization of a pass-transistor based logic for operating in subthreshold region. The authors indicate the usage of time-multiplexing in leakage dominated designs to facilitate lower energy consumption.

- Friedberg et al. [4]: This work tackles the negative effect on circuit performance due the variations introduced during manufacturing process. The authors propose to lower the variations in device attributes by applying a newer approach on the process control. They also propose to adopt simulation based approaches to reduce the PV sensitivity for circuits.

- Stine et al. [5]: This work presents modeling techniques to analyze the contributions

at distinct levels of manufacturing towards spatial variation. They propose filtering,

spine and regression schemes for wafer-level estimations, Fourier transformations

for die-level estimations and spline and frequency oriented methods for wafer-die

estimations.

- **Karpuzcu et al. [6]:** This work elaborate the impacts of PV at NTC using an architecture model. The authors present the drawbacks of employing the enhancement techniques for STC in tackling the PV at NTC. They also present a roadmap to be followed to design efficient techniques to overcome the impacts of PV at NTC.

### 2.1.2 Challenges at NTC

• **Borkar et al.** [7]: This work proposes to tackle the problem PV using design and CAD based approach. The authors emphasize on the usage of design flows incorporating

probabilistic and statistical based tools. They also elaborate a change from continuous to discreet due to the adoption of stricter regulation for device parameters such as interconnect pitches, spacings, lengths etc.

- Karpuzcu et al. [8]: This work introduces a microarchitectural model of PV at NTC. The model elaborates the impact of variations on the operating frequency, power usage by the processing cores, memory types in NTC and various faults in the memories while operating at NTC. They present a gate-delay model, specific memory for NTC, memory failure modes and effect on the various models by the leakage current.

- Pinckney et al. [9]: This work analysis the energy minimum point for parallelized NTC systems. The authors investigate the energy benefits, operating voltage and process of tasks being parallelized. They study the Leakage overhead, Amdahl overhead and Architectural overhead, and conclude that these overheads are interrelated and restrict the possible energy efficiency gains due to voltage underscaling.

- Kaul et al. [10]: The authors in this paper strongly uplift the usage of NTC for energy efficiency purposes. The design challenges associated with NTC (i.e., circuit performance variations, subthreshold leakage etc.,) are thoroughly investigated. Additionally, improvements in memories, gates and level converters are proposed. The paper also places a unique emphasis on Design Automation tools to aid in the efficient design of devices operating at Near-Threshold Voltage (NTV).

- Kaul et al. [11]: This work presents the challenges associated with the NTV operation of complex System-on-Chip (SOC) designs. The authors design an IA processor capable of working at NTC and investigate the power performance, operation of the processor at different process skews, improvements in register files and logic, and the power and performance of NTV Single-Instruction-Multiple-Data (SIMD) engine.

- 2.2 Improving the performance and energy efficiency with enhancements in architecture and memory

- Reagen et al. [12]: This work presents a co-design technique across the algorithm, architecture and circuit level to improve the energy efficiency of DNN by applying selective pruning through lowering SRAM voltages without compromising the accuracy. The authors use cross layer optimization to the baseline design and obtain up to 8 × reduction in power.

- Chen et al. [13]: This work proposes a run-time pruning technique, called row stationary, that enhances the efficiency of a convolutional neural network by re-configuring the spatial architecture, in order to map its computations. They optimize the energy efficiency by ensuring a maximum reusage of local data to lower the data movement.

- Wang et al. [14]: This work presents an elastic DNN accelerator architecture to detect

the adversary sample attacks by organizing the execution of DNN and the detect

algorithm concurrently.

- **Zhang et al. [15]:** This work introduces an aggressive voltage underscaling method to improve the energy efficiency of DNN accelerators while keeping accuracy drop less than 1%. Their architecture drops the subsequent MAC operation utilizing the erroneous data and uses the extra cycle to correct the error-prone operation.

- Chandramoorthy et al. [16]: This paper proposes a technique to enable neural network acceleration at low voltages. The technique provides low voltage operation for almost the entire application run, thereby increasing the energy efficiency and also ensures the mitigation of failures at low voltages. The authors propose to dynamically boost supply voltage during the SRAM read/write accesses.

- Yu et al. [17]: This work presents a hardware pruning technique which applies SIMD-aware weight and node pruning synergistically at the design time to improve the energy efficiency of the DNN by reducing the size of the underlying hardware. The authors propose to remove the redundant nodes in each layer, in order to compress the DNN model and thereby avoid the overhead of sparsity.

- Ozen et al. [18]: This work presents a highly resilient DNN using modified algorithms by comparing the reductions in the vulnerability surface through appropriate quantization techniques using efficient training methods.

- Salami et al. [19]: This work investigates the vulnerability due to permanent and transient faults on the neural network accelerator components and proposes a technique to reduce the faults by retrieving the corrupted bits. They analyze the resilience of the Neural Network model at Register-Transfer level (RTL) and segregate the vulnerability of RTL components. The methodology corrects the bit flips by 47 %, in comparison to the other state-of-art techniques.

- **Kim et al. [20]:** This work demonstrates a memory adaptive training with in-situ canaries, which improves the energy efficiency by enabling an aggressive voltage scaling of DNN accelerator weight memories.

- Libano et al. [21]: This work analyzes the impact of radiation-induced errors for

a neural network in FPGAs and employ a selective triple modular redundancy on

more vulnerable neural network layers to mask the faults efficiently. The authors

classify the errors due to radiation as critical errors and triplicate only the most vulnerable layers of the neural network using the proposed technique.

- Ghodrati et al. [22]: This work addresses the problems in mixed-signal circuitry

caused by the limited range of information encoding, noise susceptibility and Analogto-Digital conversion overhead by bit-partitioning the vector dot-product into groups

of lower bandwidth operations operating in parallel and distributed across various

vector elements.

- Mackin et al. [23]: This work demonstrates the execution of MAC operations in the

data location using the NVM crossbar arrays. The weights are simultaneously programmed at optimal hardware conditions and its efficacy is inspected under notable

NVM variability.

- Shafiee et al. [24]: This work proposes a pipelined architecture, with each layer of the neural network being assigned specific crossbars and eDRAM buffers used to accumulate the data between pipe stages. The Analog-to-Digital conversion overhead is reduced using a novel data encoding technique and the balance between memristor storage/compute, buffers and ADCs on the chip is handled by performing a design space inspection.

- Eshraghian et al. [25]: This work reduces the power/area using a frequency oriented approach to generate analog weights, by utilizing the switching factor of digitized conductance. The authors allocate the kernel information to the device conductance and time-varying input frequency by exploiting the dependency of *v-i* plane hysteresis on frequency.

- Whatmough et al. [26]: This work proposes a bypass operation to prevent an erroneous value from entering an adder chain by implementing a logic consisting of Razor flip-flop, multiplexer and delay register in between a pipeline stage of two multiply-accumulate operations.

- Yang et al. [27]: This work exploits the error resilience of Convolutional Neural Networks to achieve energy efficiency gains by operating the system at reduced power.

- Mauro et al. [28]: This work proposes a hybrid memory scheme to improve the energy efficiency of the Binay Neural Networks by replacing the error prone SRAMs with reliable standard-cell memories. They characterize the SRAM memories at ultra-low voltages using a self-test strategy to measure the Bit Error Rate on larger SRAMs.

- Whatmough et al. [29,30]: This work achieves improved throughput by reusing the

data and exploiting the sparsity in DNN data structures. Additionally, the timing

error tolerance is realized by utilizing DNN algorithmic resilience in DNNs and

demonstrating circuit-level time borrowing in the datapath. They have also proposed a time borrow tracking technique using Razor and approximate error correction methodology to tackle timing errors.

The work (i.e., *EFFORT*) in this dissertation is the first one to explore the disparate combinational delays of arithmetic units, exploit the systolic dataflow pattern and employ a minimal circuit-architectural manipulation to detect and correct the impeding timing errors, along with lowering the dynamic power usage. Additionally, the work (i.e., *PRED-ITOR*) in the first work to reduce the impact of *undetectable timing errors* using the statistical based approach.

# 2.3 Improving the reliability at LPC for extreme PV

- **D.Xu et al.** [31]: This work proposes a hybrid computing architecture to recompute the operations mapped to the faulty PEs in arbitrary locations using dot-production processing units (DPPUs). They show the toleration of faulty PEs at random locations by the DPPU and at various fault distributions. The authors demonstrate the utilization of parallel processing in each operation the sequential processing of the network operations.

- Zhang et al. [32]: This work prunes the weights mapped to the faulty MAC units to mitigate the impact of permanent faults on a TPU. They also retrain the weight based on the positional knowledge of the MAC units to restore the classification accuracy to the baseline, but with requires an extra time for each TPU chip.

- Spyrou et al. [33]: This work demonstrates a fault-tolerant Spiking Neural Network

architecture with simplified error detection and recovery scheme. The authors propose to nullify the effect of specific faults using passive fault tolerance modeled on

dropout.

- Salami et al. [34]: This work evaluates an undervolting technique for Neural Network acceleration in Field Programmable Gate Arrays (FPGAs) to improve the power-efficiency. They investigate the multiple components of real FPGAs at reduced voltage operation and identify reliability behavior of the CNN accelerators. The authors propose to integrate optimization techniques with undervolting to lower the short-comings of reduced-voltage operation.

- **Givaki et al. [35]:** This work experimentally evaluates the effect of aggressive voltage underscaling of block RAMs in an FPGA by emulating the real fault maps of SRAM memories. The authors proposed to increase the training iteration by 10 % to fit the gap in accuracy, arising due to the undervolting the memories.

- Tang et al. [36]: This work investigates the impact of GPU dynamic voltage and frequency scaling on the energy consumption and performance of DNNs. They observed that in comparison to the core frequency operation, operating at optimal frequency can conserve  $8.7\% \sim 23.1\%$  energy for DNN training and  $19.6\% \sim 26.4\%$  energy for inference.

- Lee et al. [37]: This work explores the optimization methods for hardware architectures for energy-efficient DNN processing on edge devices. The authors also explore hardware architecture optimization and data-path structure, in addition to hardware co-designed ASICs and DNN algorithm.

- Nguyen et al. [38]: This work presents a stretchable DRAM refresh control technique to replace non-critical bits with parity bits of error correction schemes resulting in improved energy efficiency without performance degradation of DNNs. The DRAM chip consists of an error-free zone and an error zone, with the error-free zone having the same refresh time as the normal ones and the error zone having its refresh time stretched adaptively based on the bit-error-rate of the users.

- Koppula et al. [39]: This work proposes a general framework that reduces DNN

energy consumption by using approximate DRAM devices while meeting the userspecified DNN accuracy requirements. They propose increasing the DNN's error

tolerance by retraining the DNN for the approximate DRAMs and mapping the error

tolerance of DNN data types with the appropriate DRAM partitions.

- **Jiang et al. [40]:** This work develops a Dynamic Voltage and Frequency Scaling (DVFS) framework on FPGAs to analyze the impact of DVFS on CNNs in terms of performance, power, energy efficiency and accuracy.

- Elbtity et al. [41]: This work introduces approximate PEs to replace the direct quantization of inputs and weights, utilized per-approximate units and shared them with approximate PEs to reduce the overhead arising from the element-wise operation. The authors demonstrate a reduction in the critical path delay in a PE required for the different types of multiplication and lower the processing time in a large scale multi-element arrays for a forward pass of data.

- Ruospo et al. [42]: This work reduces the fault simulation times for DNN inference execution using a fault injector framework, which replicates the pipeline flow. They elaborate the Neural Network (NN) layers as a pipeline in a processor core and utilize a process to ensure the synchronization of individual computations involved in an inference phase.

- Hosseini et al. [43]: This work proposes algorithms to approximate the value of

fault-free bits in the defective DNN weight memories and reduce the drop in DNN

accuracy due to faulty Non-volatile memories. The authors utilized the algorithms to

lower the deviations in the DNN weights and perform the deviation minimization

process at weight deployment stage to reduce the overheads due to hardware and

runtime.

Hoang et al. [44]: This work demonstrates a technique to develop a unified fault map

from smaller fault maps lower the retraining rounds and reduce the retraining overhead. The authors investigate the different quantization methodologies and provide

a detailed analysis on the DNNs error resilience for permanent faults present in the

on-chip weight memory.

To the best of knowledge, the work (i.e., *STRIVE*) in this dissertation is the first one to emphasize the impact of the PV in transforming a zero computation to a non-zero value and design a low-overhead fault detection and mitigation scheme to mitigate the effect of PV in a TPU systolic array containing faulty gates.

#### CHAPTER 3

# RECLAIMING THE ENERGY EFFICIENCY OF A NEAR-THRESHOLD TENSOR PROCESSING UNIT WITH TIMING ERROR RESILIENCE AND CLOCK GATING

# 3.1 Background and Contributions of This Work

Advancements in artificial intelligence have entered a new realm owing to the development of domain specific architectures dedicated to neural networks (NN) processing. Tensor processing unit (TPU), a custom application specific integrated circuit (ASIC) built by Google, is one such accelerator, which is exclusively built to handle most of the deep neural networks (DNN) inference workloads in their servers.

The rapidly increasing workloads calls for an increase in the processing speed and deployment volume [45]. It, however, comes at a cost of a heavy power usage, thus affecting the energy efficiency of the system. In order to preserve the energy efficiency, the TPU is operated at the near-threshold computing (NTC) region, where the transistor supply voltage is scaled down to just above its threshold voltage [2].

Accelerators like TPUs are designed to offer a very high throughput for DNN inference workloads. Although NTC operating conditions can ensure a low energy consumption, the throughput is heavily declined due to the slower transistors and longer computational delays. As the technology nodes shrink in size, inefficiency in strictly controlling the fabrication process introduces Process Variation (PV) into the system. PVs are caused due to a combination of systematic and random effects, which induces undesired delays in the computation paths [4,5,7,46]. Shabanian et al and Bal et al, demonstrated that both NTC-GPU and NTC-CPU are highly susceptible to PV, which cause timing violation induced performance bottleneck [47,48]. NTC-TPU is not an exception, this sensitivity can impact the DNN inference accuracy significantly [2,6]. This work underlines the significance of the computational delays and order of execution of the arithmetic units, to handle

timing violations in NTC TPUs. Additionally, the energy efficiency of the TPU is enhanced by exploring the predictable data flow pattern in its systolic array, thereby promoting an error-resilient and energy-efficient TPU design paradigm.

Several timing error resilient schemes have been explored for CPUs and custom ASICs [15,49–65]. However, these schemes are inefficient for combating timing violation in TPUs. Razor is one such popular timing violation detection method which uses a double sampling flip-flop to detect the errors [49]. Using instruction replay, the erroneous data is recomputed and the correct value is propagated to the next stage of the pipeline. TPU has a massive systolic array of 256 × 256 multiplier-and-accumulate (MAC) units. So, using an instruction replay in one MAC unit, results in stalling the operation of the entire systolic array, leading to a massive drop of throughput and increase in the energy consumption. TE-Drop is a recently proposed technique to handle timing violations in TPU-like systolic arrays. In this technique, the MAC unit encountering a timing error, steals an execution cycle from its downstream MAC, and recomputes the correct value [15]. In the process, the downstream MAC's computation is bypassed. However, there will be multiple levels of bypassing, in case of timing errors in consecutive rows of the same column of MACs, in the same clock cycle. Bypassing multiple computations can cause a severe drop in the inference accuracy. Additionally, the timing errors encountered in the last row of MACs will not be tackled by TE-Drop, also resulting in an accuracy drop. A naive approach to tackle timing violations is to allow the erroneous data to flow through the successive stages of operations [50, 66]. This technique undermines the effects of the erroneous data in DNN computations, as a large number of timing errors causes a significant drop in the inference accuracy [67].

In order to overcome the drawbacks of these error handling schemes, this work proposes a unique timing error correction technique which handles timing errors in the same cycle of the execution while enhancing the energy efficiency of the TPU. It is observed that in a MAC, multiplier takes relatively higher execution time than accumulator (Section 3.2.3). Additionally, it is observed that a predictable data flow pattern in the TPU systolic

array (Section 3.3.3). Analyzing these computational delays, data flow patterns, and utilizing the computational order of the arithmetic units, this work proposes EFFORT—an error resilient, low-power, novel TPU design paradigm. Following are the specific contributions of this work:

- It is experimentally demonstrated that a 8-bit multiplier takes higher computation time than a 24-bit accumulator (Section 3.2.3). The computational delays and operational order of these arithmetic units are exploited to tackle the timing errors.

- A predictable data flow pattern is observed in the TPU and this data flow pattern is utilized to reduce the energy consumption in the systolic array (Section 3.3.3).

- EFFORT—an energy efficient dynamic timing error detection/correction technique is proposed, that detects the timing errors, obtains the corrected data and propagates it to preserve the output accuracy(Section 3.3.2), while simultaneously employing a low-overhead clock gating technique to improve the energy efficiency (Section 3.3.3) of the TPU.

- In comparison to TE-Drop [15] and the Baseline-TPU, EFFORT delivers 2.5× better performance for 6 out of 8 DNN benchmarks, while incurring only 4% loss in inference accuracy (Section 3.5.2).

- It is demonstrated that EFFORT consumes up to 6% and 27% less power and gives up to 1.06× and 1.35× better performance per unit power, than Baseline-TPU and TE-Drop (Section 3.5.3).

# 3.2 Motivation

In this section, the unseen opportunities that can be availed to tackle timing errors in a TPU systolic array are illustrated. Section 3.2.1 sheds light on the background of the TPU systolic array and inherent opportunities which can be exploited for an improved performance. Using the cross-layer methodology in Section 3.2.2, the MAC units' delay profiles

are investigated. Section 3.2.3 elaborates the significance of the results and establishes the ground work for the timing error correction and dynamic power management scheme.

# 3.2.1 Background

#### **DNN Accelerators**

DNN obtains inference using multiple layers of computation. Outputs of neurons from each layers are referred to as activation streams. An activation matrix is multiplied with the weight matrix in each layer. To accelerate the matrix multiplication, a systolic array of MAC units are employed in DNN accelerators [68]. TPU–a DNN accelerator–uses a 256×256 systolic array of MACs. The weight matrices are pre-loaded into the MACs. The activation streams flow from left to right in consecutive clock cycles. The activation and weight matrices maintain an 8-bit integer precision, while the accumulator maintains a 24-bit integer precision.

# Opportunities in a Systolic Array

The asymmetric delay distributions of the multiplier and accumulate blocks in a MAC unit, open up a unique opportunity to tackle timing errors in a systolic array. The accumulate operation in a MAC, adds the output of the upstream MAC to the output of its own multiplier block. Due to a relatively large computation time of the multiplication operation, the output from the upstream MAC has ample time to reach the current accumulate unit, presuming the synchronization takes place at the primary output of the MAC. Exploiting this available timing window, correcting an erroneous operation at the upstream MAC can be overlapped with the multiplication operation of the current MAC, without paying any additional performance penalty.

The wavefront propagation of data in a systolic array leads to a static pattern of busy and idle phases. Such predictable pattern creates an avenue to conserve power of the idle MAC units. The experimental methodology used to demonstrate these opportunities in the systolic array of an NTC TPU is briefly discussed in the next section.

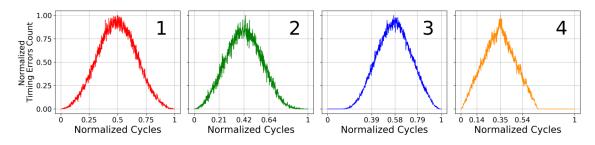

- distribution.

- distribution.

- (c) Histogram of time availability in MAC computations.

Fig. 3.1: CDFs of the delay distributions for multiplier (Figure 3.1(a)) and accumulator (Figure 3.1(b)) show that the multiplier has higher computational delay compared to the accumulator. Accumulator takes less than a half clock cycle for its part of computation. Figure 3.1(c) shows the time available for recomputation in downstream MACs when timing errors occur in the respective upstream MACs.

# 3.2.2 Methodology

A multiplier and an accumulator unit at NTC are synthesized, using 15-nm FinFET library from NanGate [69]. To model the PV at NTC for FinFET, VARIUS-NTV models [70] are used. PV-induced delays in randomly chosen 2% of the gates in the circuit is considered for a conservative estimate [71,72]. The in-house statistical timing analysis tool is used to investigate the delay distribution of the sensitized path for different inputs to the multiplier and accumulator unit. The computational time availability in the MAC units in real time is analyzed by simulating the in-house TPU systolic array simulator in a real time environment. Section 3.4 provides further elaboration on the cross-layer methodology.

## Results and Significance

Figures 3.1(a) and 3.1(b) show the delay distributions of the multiplier unit and accumulate unit, respectively. The multiplier unit is tested for a set of all possible 8-bit activation streams created against all possible 8-bit weight streams, which results in a total of 65536, 16-bit output combinations. Each one of these 65536 outputs serve as one of the inputs for the accumulator while the other input of the accumulator is fed with its own output from the previous cycle.

The cumulative distribution functions (CDFs) for the multiplier and accumulator in

Figures 3.1(a) and 3.1(b) indicate that the multiplier utilizes between 20-60% of the clock cycle and the accumulator uses less than 40% of the clock cycle. From Figure 3.1(a) and 3.1(b), it can be inferred that, even if the output of multiplier unit is sensitized only to the activation stream due to the preloaded weight, the multiplier unit still induces a higher combinational delay to the MAC operation in comparison to the accumulator, during a clock period of operation. Figure 3.1(b) shows that the accumulation requires less than half cycle of the clock period. This disparate timing characteristics of the multiplier and accumulate operations create an opportunistic timing window to correct any timing violation in an upstream MAC, thereby preventing any erroneous value to be propagated down the column of the systolic array.

Figure 3.1(c) demonstrates the computational time available in the downstream MACs, when the respective upstream MACs encounter a timing error. The TPU simulator is tested using the appropriate activation inputs and trained weights extracted from the MNIST [73] dataset. The computational time availability pattern of a MAC unit in a timing error scenario is depicted as a histogram in Figure 3.1(c). The X-axis is split into ten bars, with each bar indicating the percentage of MAC computations having time availability in the particular range of the clock cycles. From Figure 3.1(c), it is evident that more than 60% of the clock cycle period is available for re-computation process in a downstream MAC in the event of a timing error. The time availability is majorly attributed to the minuscule accumulator operation and also to the large number of zero-skip operations [12,13,74].

Figure 3.2 depicts the decrease in dynamic power and domination of static power in a MAC unit as the region of operation is changed from super-threshold computing (STC) to NTC. The X-axis is normalized to 1GHz. Operating voltage is set at 0.85V and scaled linearly to depict the shift in operating conditions. Static energy consumption can be reduced by operating the systolic array at frequencies, above the nominal NTC frequency. However, increasing the operating frequency linearly increases the dynamic energy consumption of the MAC units. In order to curb the increase in dynamic energy, an in-situ clock gating technique can be employed in the systolic array. With this opportunistic win-

Fig. 3.2: Figure 3.2 portrays the increase in static power and decrease in dynamic power for decreasing frequencies. Voltages are scaled accordingly to depict the shift from STC to NTC.

dow in-sight, the performance enhancing TPU systolic array design–EFFORT, is analyzed next.

# 3.3 EFFORT Design

<u>Energy eFFicient and errOr Resilient TPU (EFFORT)</u>, is a novel design paradigm to improve the performance of an NTC TPU by enhancing the timing error resilience of its MAC units and managing the dynamic energy consumption of the systolic array. The overview of EFFORT is described in Section 3.3.1. The detailed components of EFFORT are explained from Section 3.3.2 to Section 3.3.5.

# 3.3.1 Design Overview

Figure 3.3 demonstrates the high-level design of EFFORT. Two key modifications are added to the baseline NTC TPU. First, each MAC unit is augmented with a novel penalty-free error detection and correction logic, thus preserving a high performance. Second, a low-overhead clock gating technique is implemented to conserve the dynamic power of the systolic array. These two components are discussed next.

Fig. 3.3: CostCo implemented inside the MAC unit to detect and correct timing violations.

## 3.3.2 Costless Correction (CostCo)

In this section, costless correction (CostCo) is introduced. The conventional Razor [49] is augmented with a multiplexer (MUX) and an Exclusive-OR (XOR) gate, as demonstrated in Figure 3.3. Since CostCo controls its output with the comparison of the shadow latch and the main latch, it is capable of propagating the correct value to the downstream logic within the same clock cycle that timing error detection happens. Figure 3.4 demonstrates the RTL simulation waveforms for two consecutive MAC units within a column, in a systolic array, both in absence and presence of a timing violation. Note that, *only* the primary output of the MAC units is synchronized with the system clock, to enable the proposed CostCo design.

Figure 3.4(a) demonstrates the normal output waveforms of two consecutive column MACs in absence of any timing violation. Figure 3.4(b) shows how a small additional delay in the input of the first MAC, engenders timing violation in its immediate downstream MAC, leading to an erroneous result. Figure 3.4(c) exhibits how CostCo can detect the timing violation and propagate the correct value to its succeeding downstream MAC, within the same clock cycle. CostCo can be employed as a competent method to tackle timing violation if the downstream combinational logic has sufficient time-window before the next rising edge of the clock, to replay its logical operations on the corrected data.

In case of a timing error, 24 CostCo flip-flops are considered at the output of each MAC to provide the correct values to the downstream MACs. The output of each MAC

Fig. 3.4: CostCo can diagnose timing violation and propagate the corrected value within one clock cycle.

is utilized in the accumulation operation in its succeeding MAC. As accumulation in each MAC requires less than 50% of the clock cycle (Section 3.2.2), a 50% shift in the system clock is considered to provision the CostCo flip-flop clock. This shift of clock provides an opportunity to detect timing errors up to 50% beyond the system clock, while it guarantees the succeeding MACs to have adequate time to accomplish their accumulation operations in the remaining time window. The hardware overhead and performance gain of this design is discussed in Section 3.5.

## 3.3.3 Systolic Clock Gating

Fig. 3.5: Data flow pattern in a  $4 \times 4$  systolic array for 11 consecutive cycles. Gray MACs are yet to receive their inputs, black MACs have completed their operations, while the rest of the MACs are presently computing their respective outputs.

In EFFORT, the operating frequency is increased, while keeping the supply voltage at the nominal NTC value, in order to provide a better performance compared to a baseline NTC TPU. To reduce the power consumption due to a high-frequency operation, the application independent data-flow pattern within the TPU systolic array is exploited, and employ a low-overhead clock gating technique.

# **Application Independent Data Flow**

Figure 3.5 demonstrates the pattern of data flow inside a  $4 \times 4$  systolic array for 11 consecutive clock cycles. In this figure, the gray nodes represent the MACs that have not received their data yet, the nodes in black denote the MACs that completed their opera-

tions, and other colored nodes demonstrate the MACs which are doing their operations. Numbers on black nodes show the cycle when they completed their operations, numbers on other colored nodes represent the cycle in which they received their first data, and numbers on each edge display the cycle in which the preceding node attempts to activate or deactivate its subsequent nodes either on the right-hand side or down a row. As Figure 3.5(a) exhibits, considering the upper left node as the start point from cycle 1 to 4, all the MACs from start point down to the main diagonal, receive their data respectively in a sequential fashion, while the rest of them are yet to receive their data. After cycle 4 (Figure 3.5(b) through Figure 3.5(d)), as a new set of MACs receive their data in each cycle, another set of MACs accomplish their tasks. Figure 3.5(e) displays the systolic array after 11 clock cycles, when the entire systolic array operation is completed. It is observed that all the MACs on the same diagonal of the systolic array, are active or idle in the same cycles.

# **Clock Gating Components**

Based on the activity pattern of a systolic array, a low overhead clock gating technique is proposed, to shutdown the clock of idle MACs, improving the dynamic energy consumption of the TPU. Since all of the MACs on the same diagonal of the systolic array are active or idle in the same clock cycle, instead of endowing a separate clock gating unit for each MAC, only one clock gating unit for each set of MACs on each diagonal. Since an  $n \times n$  matrix has (2n-1) diagonals, the total number of required clock gating units is reduced from  $n^2$  to (2n-1). Figure 3.3 shows that each clock gating unit consists of one flip-flop to register the *enable signal* for the downstream clock gating unit, and an AND gate to control the clock for its corresponding group of MACs.

## **MAC Activity Analysis**

Generalizing from Figure 3.5, an  $n \times n$  systolic array needs (3n-2) cycles to complete its operation. However, not all MACs are active during each clock cycle. For an  $n \times n$  systolic array, at each clock cycle in the range [Cycle 1, Cycle n] and [Cycle (2n-1), Cycle (3n-2)], the total number of active MACs is  $\frac{n \times (n+1)}{2}$ . Furthermore, in the interval [Cycle